### **AN-1199 GreenPAK™ RPS Counter**

This GreenPAK RPS (revolutions per second) counter is designed to count revolutions of rotating objects with blades such as fidget spinner, drone propeller, fan etc. It is able to count up to 199 RPS, which is 11940 RPM (revolutions per minute). Basically, it is a frequency counter (<u>described</u> <u>here</u>) modified to meet the requirements:

- Contactless sensor to avoid contact with rotating parts.

- Frequency divider, since the sensor "sees" every blade, the output pulses must be divided by the number of blades.

- Start button, after pressing the button, the device will start counting for one second and then display the counted value for one more second or until the next pressing.

- Low power 7-segment LCD. In order to reduce power consumption, the LED display was replaced with the LCD.

The current consumption (Icc) of the device is determined by two phases:

- Counting phase. Icc depends on IR sensor emitter and is set to 20 mA. However, Icc can be reduced by increasing resistance of R1 (see Figure 1), but this will also reduce sensor sensitivity. Counting phase lasts for 1 second after power on or after pressing button "Start".

- Displaying phase. Icc depends on GreenPAK's internal blocks and 7-segment LCD, and is about 70 uA. Displaying phase starts right after counting and lasts until power is off or button "Start" is pressed again.

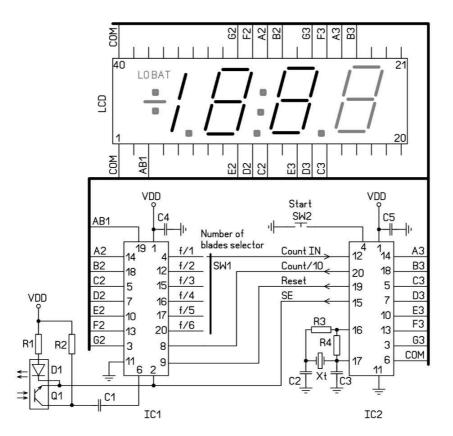

Figure 1. GreenPAK RPS Counter Schematic Diagram

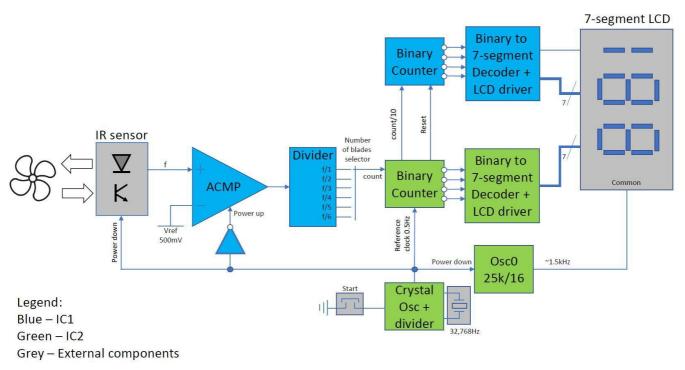

Figure 2 shows the block diagram of the device. It consists of:

- Reflective sensor which includes an infrared emitter and phototransistor. It converts reflections from the blades' infrared light into electrical pulses.

- ACMP (analog comparator) detects pulses higher than 500 mV.

- Frequency divider is used to divide input pulses by the number of the blades (set manually from 1 to 6).

- Two binary counters along with two 7-segment decoders count and convert divided pulses and display the result on the 7-segment LCD.

- Crystal oscillator together with the frequency divider form a 0.5 Hz reference clock. It is also used to power down the IR sensor and ACMP after counting is done.

- Osc 0. An internal 25 kHz oscillator divided by 16 ( $\sim$ 1.5 kHz) provides the AC current to drive the 7-segment LCD. It is powered down while counting.

Figure 2. GreenPAK RPS Counter Block Diagram

To build the RPS counter, two GreenPAK ICs are needed. The SLG46533 was chosen because of the great variety of internal blocks. For full schematic diagram and BOM refer to Figure 1 and Table 1 respectively.

| #  | Symbol     | Value (Type)                        | Quantity |

|----|------------|-------------------------------------|----------|

| 1  | IC1, IC2   | SLG46533V                           | 2        |

| 2  | LCD        | VI302-DPRC                          | 1        |

| 3  | D1, Q1     | TCRT5000L                           | 1        |

| 4  | R1         | 160 Ohm (±5%, 0.1W)                 | 1        |

| 5  | R2         | 100 kOhm (±5%, 0.1W)                | 1        |

| 6  | R3         | 20 kOhm (±5%, 0.1W)                 | 1        |

| 7  | R4         | 20 MOhm (±5%, 0.1W)                 | 1        |

| 8  | C1, C4, C5 | 100 nF (10V, ±10%, X7R)             | 3        |

| 9  | C2         | 330 pF (50V, ±10%, X7R)             | 1        |

| 10 | C3         | 10 pF (50 V, ±10%, C0G/NP0)         | 1        |

| 11 | Xt         | 32,768 Hz (R26-32.768- 12.5)        | 1        |

| 12 | SW1        | CK1035 (Rotary Switch, 6 Position)  | 1        |

| 13 | SW2        | PTS645SL50-2 LFS (12V, 50mA, 130gf) | 1        |

Table 1. BOM

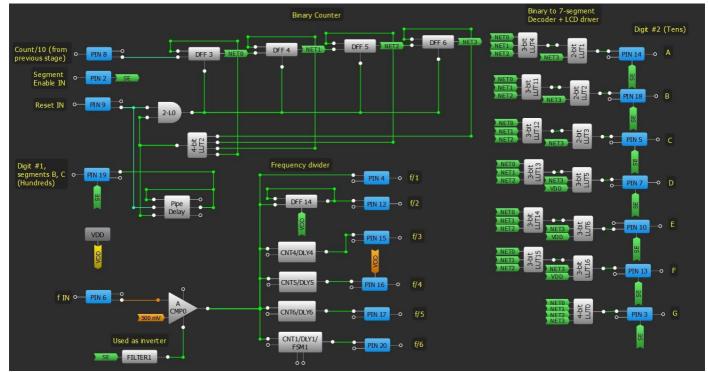

For project screenshots refer to Figures 3 and 4.

Figure 3. GreenPAK Designer Project, IC1

| Properties     | PINs 2, 8, 9                             | PINs 3, 5, 7, 10, 13,<br>14, 18, 19   | PIN 6                  | PINs 4, 12, 15, 16, 17,<br>20 |

|----------------|------------------------------------------|---------------------------------------|------------------------|-------------------------------|

| I/O selection  | Digital input                            | Digital input/output                  | Analog<br>input/output | Digital Output                |

| Input mode     | Digital in<br>without Schmitt<br>trigger | Digital in without Schmitt<br>trigger | Analog<br>input/output | None                          |

| Output mode    | None                                     | 1x open drain NMOS                    | Analog<br>input/output | 1x push pull                  |

| Resistor       | Floating                                 | Floating                              | Floating               | Floating                      |

| Resistor value | Floating                                 | Floating                              | Floating               | Floating                      |

Table 2. IC1 Pin Settings

| ING | IN2 | INI | INO | 2-bit<br>LUT0<br>OUT | 2-bit<br>LUT1<br>OUT | 2-bit<br>LUT2<br>OUT | 2-bit<br>LUT3<br>OUT | 3-bit<br>LUT4<br>OUT | 3-bit<br>LUT11<br>OUT | 3-bit<br>LUT12<br>OUT | 3-bit<br>LUT13<br>OUT | 3-bit<br>LUT14<br>OUT | 3-bit<br>LUT15<br>OUT | 3-bit<br>LUT16<br>OUT | 3-bit<br>LUT5<br>OUT | 3-bit<br>LUT6<br>OUT | 4-bit<br>LUT0<br>OUT | 4-bit<br>LUT2<br>OUT |

|-----|-----|-----|-----|----------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|----------------------|----------------------|----------------------|

| 0   | 0   | 0   | 0   | 0                    | 0                    | 1                    | 1                    | 1                    | 1                     | 1                     | 0                     | 0                     | 0                     | 0                     | 1                    | 1                    | 1                    | 1                    |

| 0   | 0   | 0   | 1   | 0                    | 1                    | 1                    | 1                    | 1                    | 1                     | 1                     | 1                     | 0                     | 0                     | 0                     | 0                    | 1                    | 1                    | 1                    |

| 0   | 0   | 1   | 0   | 0                    | 0                    | 0                    | 0                    | 1                    | 0                     | 1                     | 1                     | 0                     | 1                     | 1                     | 1                    | 1                    | 1                    | 1                    |

| 0   | 0   | 1   | 1   | 1                    | 0                    | 0                    | 0                    | 0                    | 1                     | 1                     | 0                     | 0                     | 0                     | 1                     | 1                    | 1                    | 0                    | 1                    |

| 0   | 1   | 0   | 0   | -                    | -                    | -                    | -                    | 1                    | 0                     | 1                     | 1                     | 1                     | 1                     | 0                     | 1                    | 0                    | 1                    | 1                    |

| 0   | 1   | 0   | 1   | -                    | -                    | -                    | -                    | 1                    | 1                     | 0                     | 1                     | 1                     | 0                     | 0                     | 0                    | 0                    | 0                    | 0                    |

| 0   | 1   | 1   | 0   | -                    | -                    | -                    | -                    | 0                    | 1                     | 1                     | 0                     | 0                     | 1                     | 0                     | 0                    | 0                    | 0                    | 1                    |

| 0   | 1   | 1   | 1   | -                    | -                    | -                    | -                    | 1                    | 1                     | 1                     | 1                     | 1                     | 1                     | 0                     | 0                    | 0                    | 1                    | 1                    |

| 1   | 0   | 0   | 0   | -                    | -                    | -                    | -                    | -                    | -                     | -                     | -                     | -                     | -                     | -                     | -                    | -                    | 1                    | 1                    |

| 1   | 0   | 0   | 1   | -                    | -                    | -                    | -                    | -                    | -                     | -                     | -                     | -                     | -                     | -                     | -                    | -                    | 0                    | 1                    |

| 1   | 0   | 1   | 0   | -                    | -                    | -                    | -                    | -                    | -                     | -                     | -                     | -                     | -                     | -                     | -                    | -                    | 1                    | 1                    |

| 1   | 0   | 1   | 1   | -                    | -                    | -                    | -                    | -                    | -                     | -                     | -                     | -                     | -                     | -                     | -                    | -                    | 0                    | 1                    |

| 1   | 1   | 0   | 0   | -                    | -                    | -                    | -                    | -                    | -                     | -                     | -                     | -                     | -                     | -                     | -                    | -                    | 1                    | 1                    |

| 1   | 1   | 0   | 1   | -                    | -                    | -                    | -                    | -                    | -                     | -                     | -                     | -                     | -                     | -                     | -                    | -                    | 0                    | 1                    |

| 1   | 1   | 1   | 0   | -                    | -                    | -                    | -                    | -                    | -                     | -                     | -                     | -                     | -                     | -                     | -                    | -                    | 0                    | 1                    |

| 1   | 1   | 1   | 1   | -                    | -                    | -                    | -                    | -                    | -                     | -                     | -                     | -                     | -                     | -                     | -                    | -                    | 1                    | 1                    |

#### Table 3. IC1 LUT Settings

| Properties                    | DFF3      | DFFs 4, 5, 6, 14 |

|-------------------------------|-----------|------------------|

| Туре                          | DFF/LATCH | DFF/LATCH        |

| Mode                          | DFF       | DFF              |

| 2 consecutive<br>DFFs for ASM | Disable   | -                |

| nSET/nRESET<br>option         | nRESET    | nRESET           |

| Initial polarity              | Low       | Low              |

| Q output polarity             | Inverted  | Inverted         |

Table 4. IC1 DFF Settings

| Properties       | CNT4/DLY4 CNT5/DLY5 CNT6 |                         | CNT6/DLY6               | CNT1/DLY1/FSM1             |

|------------------|--------------------------|-------------------------|-------------------------|----------------------------|

| Туре             | CNT/DLY                  | CNT/DLY                 | CNT/DLY                 | CNT/DLY                    |

| Mode             | Counter                  | Counter                 | Counter                 | Counter/FSM                |

| Counter data     | 2                        | 3                       | 4                       | 5                          |

| Edge select      | Falling                  | Falling                 | Falling                 | Falling                    |

| Output polarity  | Inverted (nOUT)          | Inverted (nOUT)         | Inverted (nOUT)         | Inverted (nOUT)            |

| Q mode           | None                     | None                    | None                    | Reset                      |

| Stop and restart | None                     | None                    | None                    | Disable                    |

| Clock            | Ext. Clk. (From matrix)  | Ext. Clk. (From matrix) | Ext. Clk. (From matrix) | Ext. Clk. (From<br>matrix) |

Table 5. IC1 CNT/DLY Settings

| Properties               | ACMP0       |  |  |  |  |

|--------------------------|-------------|--|--|--|--|

| 100uA pullup on<br>input | None        |  |  |  |  |

| Hysteresis               | 50 mV       |  |  |  |  |

| Low bandwidth            | Disable     |  |  |  |  |

| IN+ gain                 | Disable     |  |  |  |  |

| Conne                    | ections     |  |  |  |  |

| IN+ source               | PIN 6 (IO4) |  |  |  |  |

| IN- source               | 500 mV      |  |  |  |  |

Table 6. IC1 ACMP0 Settings

| Properties      | FILTER1/EDGE DET1 |

|-----------------|-------------------|

| Туре            | FILTER            |

| Output polarity | Inverted          |

Table 7. IC1 FILTER1 Settings

| Properties           | 3-bit LUT10/Pipe Delay |

|----------------------|------------------------|

| Туре                 | Pipe Delay             |

| OUT0 PD num          | 1                      |

| OUT1 PD num          | 1                      |

| OUT1 output polarity | Inverted (nOUT)        |

| Table 8 | 8. | IC1 | Pipe | Delay | Settings |

|---------|----|-----|------|-------|----------|

|---------|----|-----|------|-------|----------|

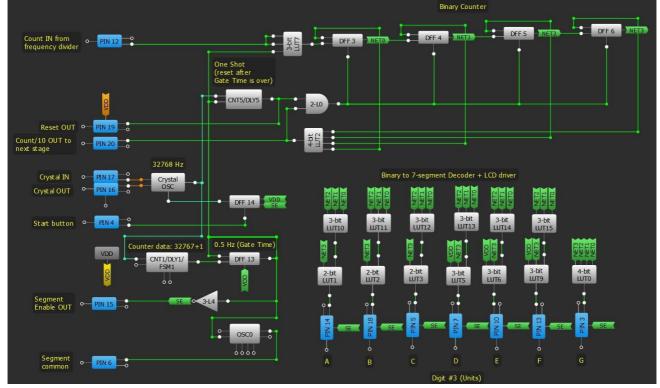

Figure 4. GreenPAK Designer Project, IC2

| Properties                                                                | PINs 12                                  | PINs 4                             | PINs 3, 5, 7, 10, 13,<br>14, 18       | PINs 6, 15, 19, 20 |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------|------------------------------------|---------------------------------------|--------------------|--|--|--|--|

| I/O selection                                                             | Digital input                            | Digital input                      | Digital input/output                  | Digital Output     |  |  |  |  |

| Input mode                                                                | Digital in<br>without Schmitt<br>trigger | Digital in with Schmitt<br>trigger | Digital in without<br>Schmitt trigger | None               |  |  |  |  |

| Output mode                                                               | None                                     | None                               | 1x open drain NMOS                    | 1x push pull       |  |  |  |  |

| Resistor                                                                  | Floating                                 | Pull UP                            | Floating                              | Floating           |  |  |  |  |

| Resistor value                                                            | Floating                                 |                                    |                                       |                    |  |  |  |  |

| Note: PINs 16 and 17 will be set automatically after Crystal OSC enabled. |                                          |                                    |                                       |                    |  |  |  |  |

Table 9. IC2 Pin Settings

| IN3 | IN2 | INI | INO | 2-bit<br>LUTO<br>OUT | 2-bit<br>LUT1<br>OUT | 2-bit<br>LUT2<br>OUT | 2-bit<br>LUT3<br>OUT | 3-bit<br>LUT4<br>OUT | 3-bit<br>LUT11<br>OUT | 3-bit<br>LUT12<br>OUT | 3-bit<br>LUT13<br>OUT | 3-bit<br>LUT14<br>OUT | 3-bit<br>LUT15<br>OUT | 3-bit<br>LUT5<br>OUT | 3-bit<br>LUT6<br>OUT | 3-bit<br>LUT7<br>OUT | 3-bit<br>LUT9<br>OUT | 3-bit<br>LUT10<br>OUT | 4-bit<br>LUTO<br>OUT | 4-bit<br>LUT2<br>OUT |

|-----|-----|-----|-----|----------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|----------------------|----------------------|

| 0   | 0   | 0   | 0   | 0                    | 0                    | 1                    | 1                    |                      | 1                     | 1                     | 0                     | 0                     | 0                     | 1                    | 1                    | 0                    | 0                    | 1                     | 1                    | 1                    |

| 0   | 0   | 0   | 1   | 0                    | 1                    | 1                    | 1                    |                      | 1                     | 1                     | 1                     | 0                     | 0                     | 0                    | 1                    | 1                    | 0                    | 1                     | 1                    | 1                    |

| 0   | 0   | 1   | 0   | 0                    | 0                    | 0                    | 0                    |                      | 0                     | 1                     | 1                     | 0                     | 1                     | 1                    | 1                    | 0                    | 1                    | 1                     | 1                    | 1                    |

| 0   | 0   | 1   | 1   | 1                    | 0                    | 0                    | 0                    |                      | 1                     | 1                     | 0                     | 0                     | 0                     | 1                    | 1                    | 0                    | 1                    | 0                     | 0                    | 1                    |

| 0   | 1   | 0   | 0   | -                    | -                    | -                    | -                    |                      | 0                     | 1                     | 1                     | 1                     | 1                     | 1                    | 0                    | 0                    | 0                    | 1                     | 1                    | 1                    |

| 0   | 1   | 0   | 1   | -                    | -                    | -                    | -                    |                      | 1                     | 0                     | 1                     | 1                     | 0                     | 0                    | 0                    | 0                    | 0                    | 1                     | 0                    | 0                    |

| 0   | 1   | 1   | 0   | -                    | -                    | -                    | -                    |                      | 1                     | 1                     | 0                     | 0                     | 1                     | 0                    | 0                    | 0                    | 0                    | 0                     | 0                    | 1                    |

| 0   | 1   | 1   | 1   | -                    | -                    | -                    | -                    | Inverter             | 1                     | 1                     | 1                     | 1                     | 1                     | 0                    | 0                    | 0                    | 0                    | 1                     | 1                    | 1                    |

| 1   | 0   | 0   | 0   | -                    | -                    | -                    | -                    | Inve                 | -                     | -                     | -                     | -                     | -                     | -                    | -                    | -                    | -                    | -                     | 1                    | 1                    |

| 1   | 0   | 0   | 1   | -                    | -                    | -                    | -                    |                      | -                     | -                     | -                     | -                     | -                     | -                    | -                    | -                    | -                    | -                     | 0                    | 1                    |

| 1   | 0   | 1   | 0   | -                    | -                    | -                    | -                    |                      | -                     | -                     | -                     | -                     | -                     | -                    | -                    | -                    | -                    | -                     | 1                    | 1                    |

| 1   | 0   | 1   | 1   | -                    | -                    | -                    | -                    |                      | -                     | -                     | -                     | -                     | -                     | -                    | -                    | -                    | -                    | -                     | 0                    | 1                    |

| 1   | 1   | 0   | 0   | -                    | -                    | -                    | -                    |                      | -                     | -                     | -                     | -                     | -                     | -                    | -                    | -                    | -                    | -                     | 1                    | 1                    |

| 1   | 1   | 0   | 1   | -                    | -                    | -                    | -                    |                      | -                     | -                     | -                     | -                     | -                     | -                    | -                    | -                    | -                    | -                     | 0                    | 1                    |

| 1   | 1   | 1   | 0   | -                    | -                    | -                    | -                    |                      | -                     | -                     | -                     | -                     | -                     | -                    | -                    | -                    | -                    | -                     | 0                    | 1                    |

| 1   | 1   | 1   | 1   | -                    | -                    | -                    | -                    |                      | -                     | -                     | -                     | -                     | -                     | -                    | -                    | -                    | -                    | -                     | 1                    | 1                    |

### Table 10. IC2 LUT Settings

| Properties                    | DFF3      | DFFs 4, 5, 6,<br>13, 14 |

|-------------------------------|-----------|-------------------------|

| Туре                          | DFF/LATCH | DFF/LATCH               |

| Mode                          | DFF       | DFF                     |

| 2 consecutive<br>DFFs for ASM | Disable   | -                       |

| nSET/nRESET<br>option         | nRESET    | nRESET                  |

| Initial polarity              | Low       | Low                     |

| Q output polarity             | Inverted  | Inverted                |

Table 11. IC2 DFF Settings

| Properties       | CNT5/DLY5               | CNT1/DLY1/FSM1          |

|------------------|-------------------------|-------------------------|

| Туре             | CNT/DLY                 | CNT/DLY                 |

| Mode             | One Shot                | Counter/FSM             |

| Counter data     | 1                       | 32767                   |

| Edge select      | Rising                  | Rising                  |

| Output polarity  | Inverted (nOUT)         | Non-inverted (OUT)      |

| Q mode           | None                    | Reset                   |

| Stop and restart | None                    | Disable                 |

| Clock            | Ext. Clk. (From matrix) | Ext. Clk. (From matrix) |

Table 12. IC2 CNT/DLY Settings

| Properties                   | Crystal OSC        |

|------------------------------|--------------------|

| Enable crystal<br>oscillator | Enable             |

| Power down enable            | PD for crystal OSC |

| Properties                  | OSC0           |

|-----------------------------|----------------|

| Control pin mode            | Power down     |

| OSC power mode              | Force Power On |

| Clock selector              | OSC            |

| EXT CLK Pin selector        | PIN 20 (IO17)  |

| Fast start-up               | Disable        |

| RC OSC Frequency            | 25 kHz         |

| 'CLK' predivider by         | 8              |

| `OUT0' second<br>divider by | 2              |

| `OUT1' second divider by    | 1              |

Table 14. IC2 OSC0 Settings

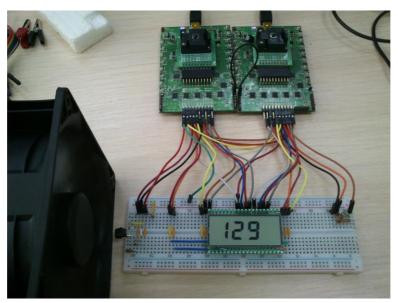

Figure 5. GreenPAK RPS Counter Prototype

### Conclusion

The GreenPAK RPS Counter is designed to count revolutions of moderately slow objects. However, adding another GreenPAK IC will allow increasing the counting limit to 1999 RPS (119940 RPM). This design is easy to scale and can be used as a reference for many similar applications.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.