# RZ/A1H グループ

R01AN3430JJ0100 Rev.1.00

QE for Video Display Controller 5 サンプルプログラム

2016.09.14

### 要旨

本アプリケーションノートでは、ルネサス製マイコンに対応する統合開発環境"e2 studio"用のプラグインである"QE for Video Display Controller 5"と連携する Video Display Controller 5 (VDC5)サンプルアプリケーションについて説明します。"QE for Video Display Controller 5"は、表示機器を搭載した繰み込みシステム開発において、表示制御をグラフィカルな I/F でサポートするツールになります。

### 動作確認デバイス

RZ/A1H グループ

## 目次

| 1. 概要                                                       | 3  |

|-------------------------------------------------------------|----|

| 2. 動作条件                                                     | 4  |

| 3. ハードウェア説明                                                 |    |

| 3.1 ハート・ノエア (構成                                             | 3  |

| 4. ソフトウェア説明                                                 |    |

| 4.1 動作概要                                                    |    |

| 4.2 サンプルソフトウェア詳細                                            |    |

| 4.3 メモリマップ                                                  | 8  |

| 4.4 使用する周辺機能                                                | 8  |

| 4.5 使用割り込み一覧                                                | 8  |

| 4.6  関数仕様                                                   | 8  |

|                                                             |    |

| 5. サンプルプログラムと"QE for Video Display Controller 5"の使用方法       |    |

| 5.1 "QE for Video Display Controller 5"で生成したヘッダファイルでの表示確認手順 | 9  |

| 5.1.1 サンプルプロジェクトのインポート                                      | 9  |

| 5.1.2 "QE for Video Display Controller 5"の起動                |    |

| 5.1.3 表示機器情報の設定                                             | 12 |

| 5.1.4 ヘッダファイルの生成                                            | 19 |

| 5.1.5 サンプルプロジェクトのビルド                                        | 20 |

| 5.1.6 デバッガの設定と表示確認                                          | 21 |

| 5.2 "QE for Video Display Controller 5"を使用したリアルタイム調整機能      | 24 |

| 5.3 "QE for Video Display Controller 5"のイメージダウンロード機能        |    |

|                                                             |    |

| 6. ユーザ環境に適応するには                                             | 26 |

| 6.1 CPU 及びボードの初期化                                           | 26 |

| 6.2 VDC5 の動作設定                                              | 26 |

| 6.2.1 パネルクロックの設定                                            | 27 |

| 6.2.2 LVDS PLL を使用したパネルクロックの生成                              | 28 |

| 6.3 GPIO の設定                                                |    |

|                                                             |    |

| 7. 参考ドキュメント                                                 | 30 |

### 1. 概要

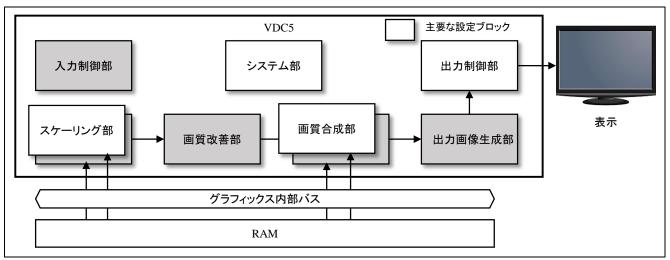

VDC5 は、図 1-1 に示すように複数のブロックで構成されている為、表示確認を行うだけでも VDC5 の仕様を理解しいくつもの設定を行う必要があります。そこで、本サンプルプログラムと"QE for Video Display Controller 5"を使用する事で VDC5 の仕様を理解する必要なく短期間で表示機器の接続確認ができる環境を準備しました。"QE for Video Display Controller 5"は、表示制御をグラフィカルな I/F でサポートするツールになり、使用する表示機器の情報を入力することで、表示制御に必要な情報をヘッダファイルで出力します。そのヘッダファイルをもとに本サンプルプログラムが VDC5 の設定を行います。また、ツールには、リアルタイムでタイミングを調整する機能があり、使用する表示機器を接続したまま微調整を行ってから、ヘッダファイルを出力する事も可能です。以降に本サンプルプログラムについて記載します。

図 1-1 VDC5 ブロック構成

### 2. 動作条件

本アプリケーションノートのサンプルプログラムは、下記の条件で動作を確認しています。

表 2-1 動作確認条件

| 項目               | 内容                                                         |  |  |  |  |

|------------------|------------------------------------------------------------|--|--|--|--|

| 使用マイコン           | RZ/A1H                                                     |  |  |  |  |

| 動作周波数            | CPU クロック(Iφ) : 400MHz                                      |  |  |  |  |

|                  | 画像処理クロック(G ∅) : 266.67MHz                                  |  |  |  |  |

|                  | 内部バスクロック(Bφ) : 133.33MHz                                   |  |  |  |  |

|                  | 周辺クロック 1(P1 φ ) :66.67MHz                                  |  |  |  |  |

|                  | 周辺クロック 0(P0φ) : 33.33MHz                                   |  |  |  |  |

| 動作電圧             | 電源電圧(I/O) : 3.3V                                           |  |  |  |  |

|                  | 電源電圧(内部): 1.18V                                            |  |  |  |  |

| 統合開発環境           | 統合開発環境                                                     |  |  |  |  |

|                  | Renesas "e2 studio" Version: 4.3.1.0001                    |  |  |  |  |

| Cコンパイラ           | GNUARM-NONE-EABI Toolchain v14.02                          |  |  |  |  |

| 動作モード            | ブートモード 0(注 1)                                              |  |  |  |  |

|                  | (CS0 空間 16 ビットブート)                                         |  |  |  |  |

| 使用ボード            | ボード                                                        |  |  |  |  |

|                  | RSK CPU board(YR0K77210C000BE)                             |  |  |  |  |

|                  | • RSK TFT APP Board(YROK77210C000BE)                       |  |  |  |  |

| エミュレータ           | J-Link LITE ARM debugger                                   |  |  |  |  |

| ボード設定            | RSK CPU board(YR0K77210C000BE)                             |  |  |  |  |

| ( ジャンパー / スイッチ ) | SW4-1 OFF, SW4-2 OFF, SW4-3 OFF, SW4-4 OFF,                |  |  |  |  |

|                  | SW4-5 OFF, SW4-6 OFF, SW4-7 OFF, SW4-8 OFF                 |  |  |  |  |

|                  | SW6-1 ON, SW6-2 ON, SW6-3 ON, SW6-4 ON, SW6-5 ON, SW6-6 ON |  |  |  |  |

|                  | JP11 2-3, JP12 1-2, JP21 1-2, JP18 1-2                     |  |  |  |  |

|                  | RSK TFT APP Board(YROK77210C000BE)                         |  |  |  |  |

【注】1. 本サンプルプログラムは内蔵 RAM にロードして動作します。CSO 空間は使用していません。

### 3. ハードウェア説明

## 3.1 ハードウェア構成

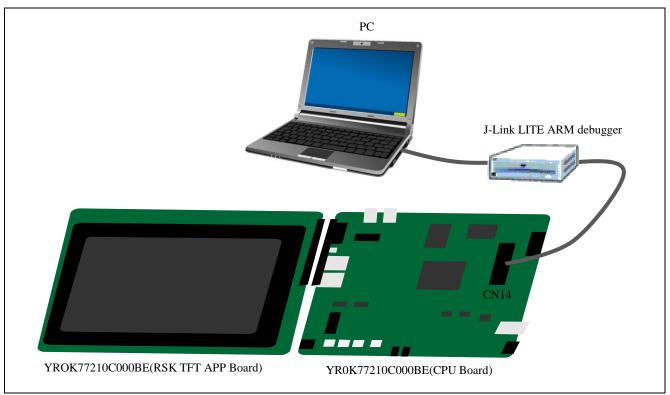

図 3-1 にサンプルプログラムのハードウェア構成を示します。

図 3-1 サンプルプログラムのハードウェア構成

## 4. ソフトウェア説明

### 4.1 動作概要

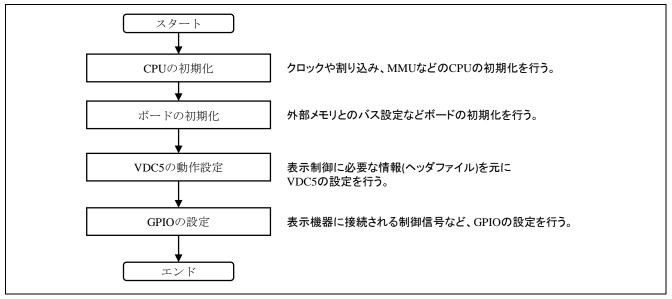

サンプルプログラムでは図 4-1 に示すように、クロックや割り込み、MMU などの CPU の初期化や、外部メモリとのバス設定などボードの初期化を行い、"QE for Video Display Controller 5"から出力されたヘッダファイルをもとに VDC5 の動作設定を行った後、表示制御に使用される GPIO 設定を行っています。

図 4-1 サンプルプログラムの動作概要

### 4.2 サンプルソフトウェア詳細

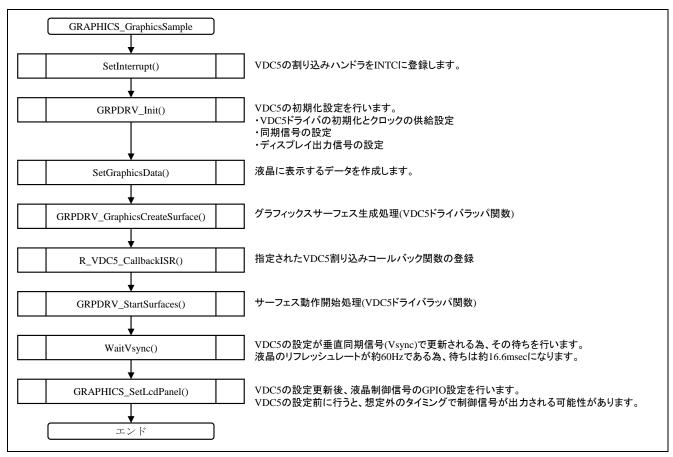

図 4-2 に VDC5 の動作設定の詳細を記載します。 VDC5 の動作設定は、"QE for Video Display Controller 5" が出力したヘッダファイルをもとに行います。

図 4-2 VDC5 の動作設定フロー

表示機器の設定が正しく行われた場合、図 4-3 に示す画面が表示されます。

図 4-3 表示画面

### 4.3 メモリマップ

本、サンプルプログラムで使用する固有セクションは以下の通りです。

表 4-1 サンプルプログラムで使用する固有セクション

| 領域の名前          | タイプ     | 内容                                                                |

|----------------|---------|-------------------------------------------------------------------|

| VRAM_SECTION_1 | ZI Data | 表示データが格納されるバッファ<br>大容量内蔵 RAM の固定アドレス(0x60500000)に<br>非キャッシュ領域で配置。 |

### 4.4 使用する周辺機能

表 4-2 にサンプルプログラムが使用する周辺機能と用途を示します。

表 4-2 使用する周辺機能と用途

| 周辺機能                    | 用途                    |

|-------------------------|-----------------------|

| ビデオディスプレイコントローラ 5(VDC5) | ディスプレイ表示              |

| チャネル 0                  | ● グラフィックス(2)を使用       |

|                         | ● 色形式 RGB888          |

| 割り込みコントローラ(INTC)        | VDC5 チャネル 0 の割り込み制御   |

|                         | ● レジスタ更新待ち            |

| 大容量内蔵 RAM               | VRAM                  |

|                         | ● 表示バッファとして内蔵 RAM を使用 |

### 4.5 使用割り込み一覧

表 4-3 にサンプルプログラムで使用する割り込みを示します。VDC5 のレジスタ設定が垂直同期信号 (Vsync)で更新される為、その更新待ちにこの割り込みを使用します。液晶のリフレッシュレートが約 60Hz である為、割り込みの間隔は約 16.6msec になります。

表 4-3 サンプルプログラムで使用する割り込み

| 割り込み(要因 ID)      | 優先度 | 要因説明                        |

|------------------|-----|-----------------------------|

| VDC5 チャネル 0      | 5   | グラフィックス(3)パネル出力の指定ライン信号     |

| (GR3_VLINE0: 78) |     | (画面合成部から出力する映像信号のライン 0 と同期) |

### 4.6 関数仕様

本サンプルで使用されている関数については、関連アプリケーションノート『RZ/A1H グループ Video Display Controller 5 Sample Driver (R01AN1822JJ/EJ)』を参考にしてください。

## 5. サンプルプログラムと"QE for Video Display Controller 5"の使用方法

本サンプルプログラムは、RSK CPU board(YR0K77210C0000BE)を想定した環境で動作します。この環境を使用し RSK TFT APP Board(YROK77210C000BE)の接続確認を"QE for Video Display Controller 5"で行った場合の手順について記載します。尚、"e2 studio"及び"QE for Video Display Controller 5"のインストールについては、各ツールのマニュアルを参考に行ってください。

### 5.1 "QE for Video Display Controller 5"で生成したヘッダファイルでの表示確認手順

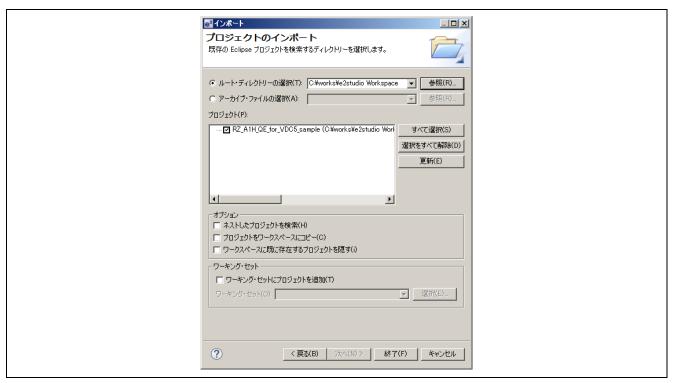

### 5.1.1 サンプルプロジェクトのインポート

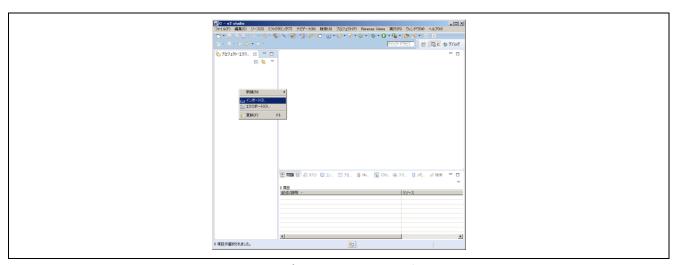

"e2 studio"を起動後、図 5-1 に示すようにマウスの右クリックで『インポート』を選択しインポートダイアログを表示します。

図 5-1 プロジェクトのインポート

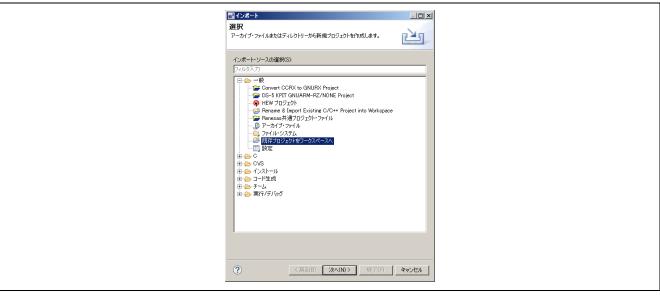

インポートダイアログ(図 5-2)では、『既存プロジェクトをワークスペースへ』を選択し次へボタンを押下してください。

図 5-2 インポートダイアログ

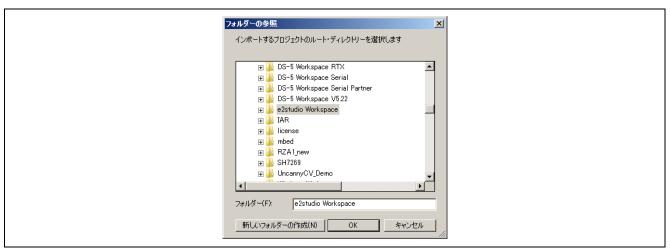

フォルダーの参照ダイアログ(図 5-3)では、サンプルプログラムが含まれているフォルダを選択し OK ボタンを押下してください。

図 5-3 フォルダーの参照

本サンプルプロジェクトが見つかると図 5-4 のようにプロジェクト欄に 『RZ\_A1H\_QE\_for\_VDC5\_sample』が表示されます。チェックボックスにチェックを入れ終了ボタンを押下してください。

図 5-4 インポートプロジェクトの確認

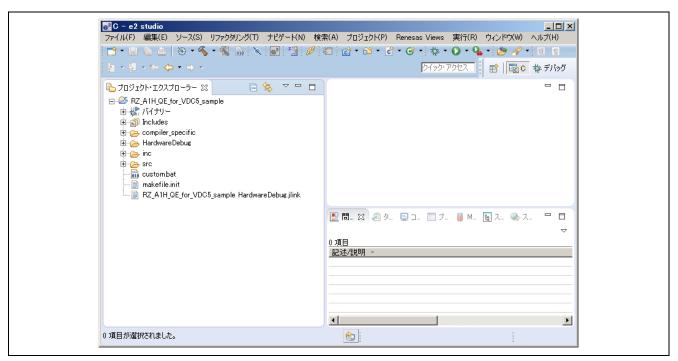

以上の作業により、本サンプルプログラムが"e2 studio"にインポートされます(図 5-5)。

図 5-5 インポートされたサンプルプロジェクト

### 5.1.2 "QE for Video Display Controller 5"の起動

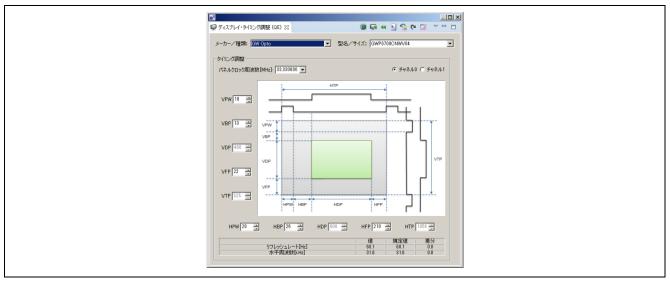

"e2 studio"のメニューから『Renesas Views』  $\rightarrow$  『Renesas QE』  $\rightarrow$  『ディスプレイ・タイミング調整(QE)』 を選択すると"QE for Video Display Controller 5"が起動します(図 5-6)。

図 5-6 "QE for Video Display Controller 5"の起動画面

#### 5.1.3 表示機器情報の設定

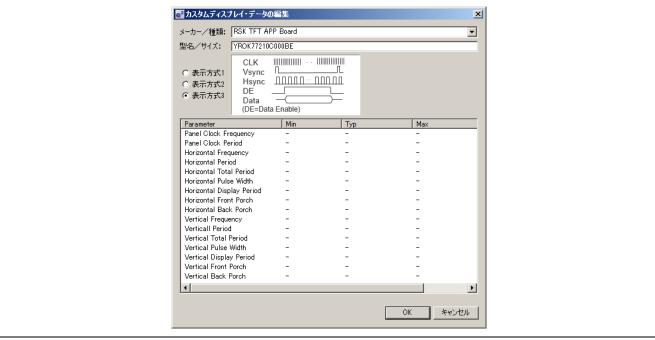

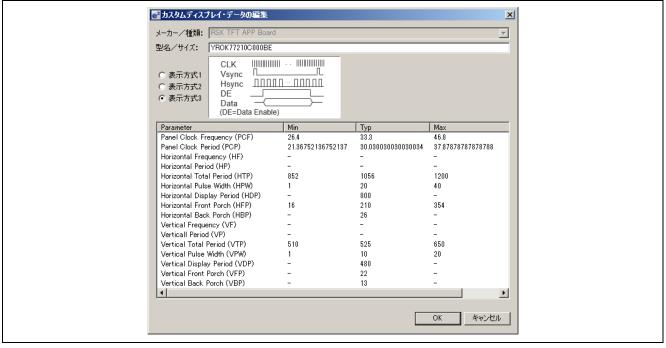

図 5-6 のダイアログ上部にある『メーカ/種類』のプルダウンリストからカスタムを選択するとカスタムディスプレイ・データの編集ダイアログ(図 5-7)が表示されます。このダイアログに表示機器の情報を入力します。今回、使用する RSK TFT APP Board(YROK77210C000BE)には、GW Opto 製の TFT 液晶 (GWP0700CNWV04)が搭載されており、この TFT 液晶の仕様にあわせて情報を入力します。

図 5-7 カスタムディスプレイ・データの編集ダイアログ

#### (a) 登録名称の記入

カスタムディスプレイ・データの編集ダイアログ(図 5-8)の『メーカー/種類』、『型名/サイズ』項目に、任意の名称を入力してください。この名称がドロップダウンリストに登録され選択する事が可能になります。

図 5-8 名称の登録

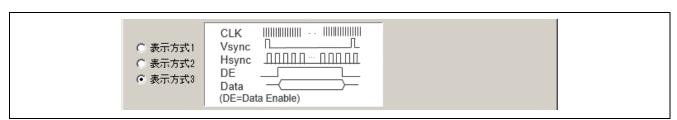

#### (b) 表示方式の選択

表示機器を接続する為に必要な主な制御信号を表 5-1 に示します。今回、"QE for Video Display Controller 5"では、これらの制御信号を組みあわせた3つの方式の表示機器をサポートしています。

名称機能概略水平同期信号(Hsync)表示する1ラインのタイミングを作る信号垂直同期信号(Vsync)表示する1画面のタイミングを作る信号パネルクロック(CLK)表示される画素レベルの表示周波数表示イネーブル(DE)有効なデータが出力されていることを示す信号データ(Data)表示するデータ

表 5-1 主な制御信号

使用する表示機器の仕様からどの制御信号が必要か、ユーザが確認し表 5-2 に示す 3 つの表示方式から選択する必要があります。

名称 表示方式1 表示方式2 表示方式3 CLK |||||||||| ·· ||||||| Vsvnc | Vsvnc Data — DE \_\_\_\_\_ Data \_\_\_\_\_ (DE=Data Enable) (DE=Data Enable) 水平同期信号(Hsync) 使用 未使用 使用 垂直同期信号(Vsync) 使用 未使用 使用 パネルクロック(CLK) 使用 使用 使用 表示イネーブル(DE) 未使用 使用 使用 使用 データ(Data) 使用 使用

表 5-2 使用する制御信号

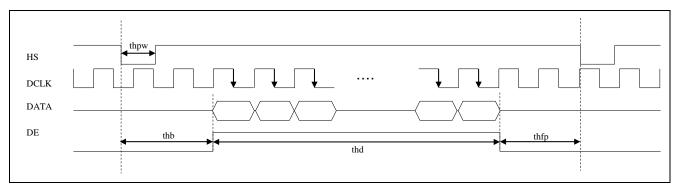

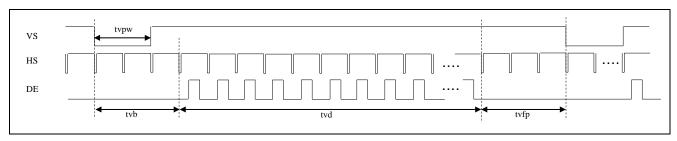

今回、使用する RSK TFT APP Board(YROK77210C000BE)の水平/垂直方向のタイミングチャートを図 5-9、図 5-10 に記載します。このタイミングチャートより水平同期信号(Hsync)、垂直同期信号(Vsync)、表示イネーブル(DE)信号が必要である為、表示方式の選択では、表示方式 3 を選択します(図 5-11)。

図 5-9 Horizontal input timing diagram

図 5-10 Vertical input timing diagram

図 5-11 表示方式の選択

#### (c) 制御タイミングの入力

今回、使用する RSK TFT APP Board(YROK77210C000BE)の水平/垂直方向のタイミングチャート図 5-9、図 5-10。水平/垂直同期信号のタイミングを示す表 5-3、表 5-4。これらの制御タイミングを入力した結果を図 5-12 に示します。Typ.に入力された値がタイミング制御に使用され、Min、Max については、"QE for Video Display Controller 5"のタイミング調整を GUI で行った時、範囲内で収まるかの確認に使用されます。

図 5-12 制御タイミング入力結果

以下項目については、表 5-3 を参考に入力しています。

- Panel Clock Frequency

- Horizontal Total Period

- Horizontal Pulse Width

- Horizontal Display Period

- Horizontal Front Porch

- Horizontal Back Porch

以下項目については、表 5-4 を参考に入力しています。

- Vertical Total Period

- Vertical Pulse Width

- Vertical Display Period

- Vertical Front Porch

- Vertical Back Porch

- 【注】 図 5-12、Horizontal/Vertical Pulse Width の Typ.については、Min.と Max.の中間値としています。また、Horizontal/Vertical Back Porch の Typ.については、表 5-3、表 5-4、HS/VS Blanking の値を入力しますが、HS/VS Blanking の値には、HS/VS pulse width が含まれている為、Horizontal/Vertical Pulse Width の Typ.を減算した値を Horizontal/Vertical Back Porch の Typ.に入力しています。

### 表 5-3 Horizontal imput timing

| Item                    | Symbol | Value |      | Unit | Note |  |

|-------------------------|--------|-------|------|------|------|--|

|                         |        | Min.  | Тур. | Max. |      |  |

| Horizontal display area | thd    | -     | 800  | -    | DCLK |  |

| DCLK Frequency          | fclk   | 26.4  | 33.3 | 46.8 | MHz  |  |

| One Horizontal Line     | th     | 862   | 1056 | 1200 | DCLK |  |

| HS pulse width          | thpw   | 1     | -    | 40   | DCLK |  |

| HS Blanking             | thb    | 46    | 46   | 46   | DCLK |  |

| HS Front Porch          | thpf   | 16    | 210  | 354  | DCLK |  |

### 表 5-4 Vertical input timing

| Item                  | Symbol | Value |      | Unit | Note |  |

|-----------------------|--------|-------|------|------|------|--|

|                       |        | Min.  | Тур. | Max. |      |  |

| Vertical display area | tvd    | -     | 480  | -    | TH   |  |

| VS period time        | Tv     | 510   | 525  | 650  | TH   |  |

| VS pulse width        | tvpw   | 1     | -    | 20   | TH   |  |

| VS Blanking           | tvb    | 23    | 23   | 23   | TH   |  |

| VS Front Porch        | tvpf   | 7     | 22   | 147  | TH   |  |

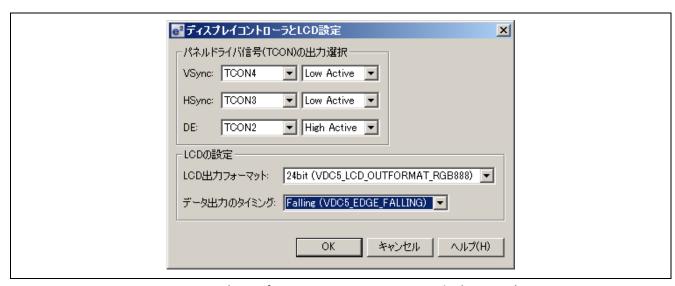

### (d) 制御信号の出力設定

"QE for Video Display Controller 5"のディスプレイコントローラと LCD 設定アイコン(図 5-13)を押下することで Display Controller and LCD setting ダイアログ(図 5-14)が表示されます。

図 5-13 ディスプレイコントローラと LCD 設定のアイコン

このダイアログでは、以下に記載する制御信号の出力設定を行います。

#### [Panel Driver Signal (TCON) Output Selection]

出力端子の選択:

LCD\_TCON0~LCD\_TCON6 端子~出力(TCON0~TCON6)

制御信号の極性:

正極性(High Active)

負極性(Low Active)

#### [LCD Setting]

出力データフォーマットの選択:

24bit RGB888 出力 (24bit(VDC5\_LCD\_OUTFORMAT\_RGB888))

18bit RGB666 出力 (18bit(VDC5 LCD OUTFORMAT RGB666))

16bit RGB565 出力 (16bit(VDC5\_LCD\_OUTFORMAT\_RGB565))

データの出力タイミング:

パネルクロックの立ち上がりで出力 (Rising(VDC5\_EDGE\_RISING))

パネルクロックの立下りで出力 (Falling(VDC5\_EFGE\_FALLING))

図 5-14 ディスプレイコントローラと LCD 設定ダイアログ

今回、使用する RSK TFT APP Board(YROK77210C000BE)での出力端子の選択については、ボード仕様より以下となります。

#### 出力端子の選択

Vsync : TCON4Hsync : TCON3DE : TCON2

制御信号の極性については、図 5-9、図 5-10 より以下となります。

#### 制御信号の極性:

Vsync: 負極性(Low Active)

Hsync: 負極性(Low Active)

DE: 正極性(High Active)

出力データフォーマットについては、ボードの仕様より以下となります。

出力データフォーマットの選択:

24bit RGB888 出力 (24bit(VDC5\_LCD\_OUTFORMAT\_RGB888))

データの出力タイミングについては、図 5-9 より DCLK 信号の立下りでデータをサンプリングしている為、VDC5 側からは、パネルクロックの立ち上がりのタイミングでデータを出力します。

データの出力タイミング:

パネルクロックの立ち上がりで出力 (Rising(VDC5\_EDGE\_RISING))

以上で表示機器情報の設定が完了します。

### 5.1.4 ヘッダファイルの生成

"QE for Video Display Controller 5"のヘッダファイルの生成アイコン(図 5-15)を押下することで設定した制御タイミングを反映したヘッダファイルを生成する事が可能です。ヘッダファイル名と出力先は、任意で設定可能です

図 5-15 ヘッダファイルの生成

サンプルプログラムでは、生成されたヘッダファイルを参照し VDC5 の設定を行います。以下に記載したフォルダ/ファイル名で保存してください。

#### 【フォルダ】

- RZ\_A1H\_QE\_for\_VDC5\_sample\inc\lcd 【ファイル名】

- RSK\_TFT\_ch0.h

### 5.1.5 サンプルプロジェクトのビルド

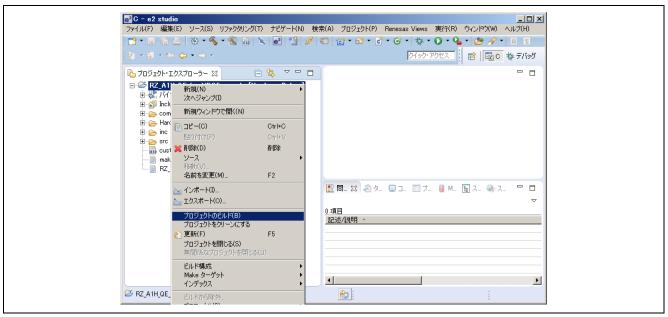

"QE for Video Display Controller 5"に表示機器情報の設定が完了し、ヘッダファイルを出力した後、図 5-16に示すようにインポートしたプロジェクトを右クリックし『プロジェクトのビルド』を選択してください。

図 5-16 プロジェクトのビルド

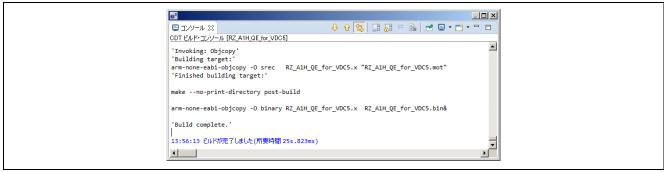

正常にビルドが終了すると図 5-17 のようなコンソール出力が確認出来ます。

図 5-17 コンソール出力結果

### 5.1.6 デバッガの設定と表示確認

RSK CPU board(YR0K77210C000BE)を使用し RSK TFT APP Board(YROK77210C000BE)の表示確認を行います。使用するデバッガは、RSK CPU board(YR0K77210C000BE)に付随する JLINK LITE ARM debugger を使用します。以下にそのデバッガの設定を記載します。

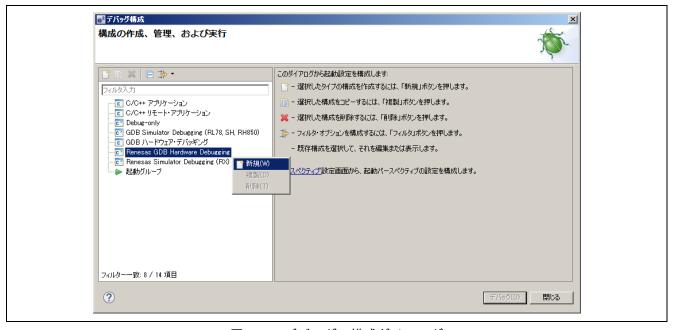

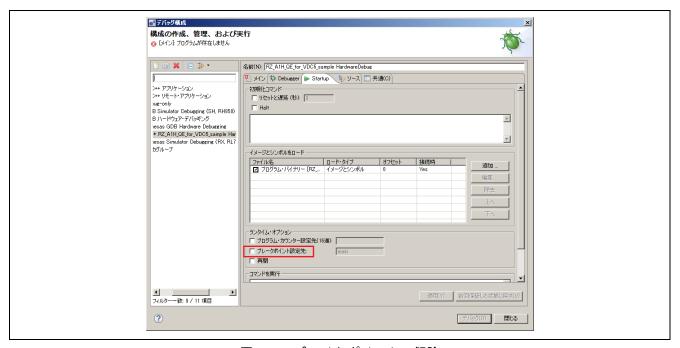

"e2 studio"のメニューから『実行』 $\rightarrow$ 『デバッグの構成』を選択しデバッグ構成ダイアログを表示します(図 5-18)。『Renesas GDB Hardware Debugging』を選択しマウスの右クリックから新規を選択します。

図 5-18 デバッグの構成ダイアログ

新規作成されたデバッグ構成を図 5-19 に示します。プロジェクトの参照ボタンを押下し『RZ\_A1H\_QE\_for\_VDC5\_sample』を選択してください。

図 5-19 新規に作成されたデバッグ構成

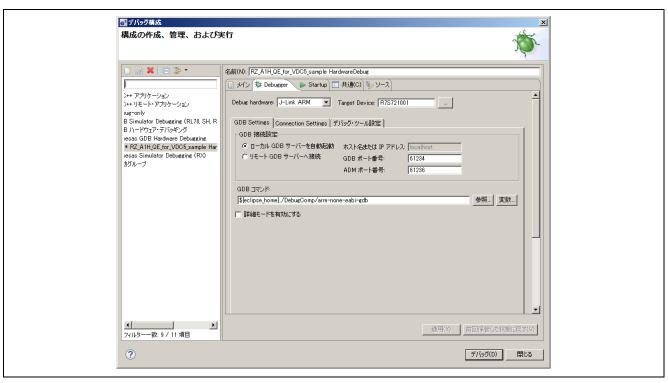

次に Debugger タブを選択し以下の設定を行い(図 5-20)、適応ボタンを押下してください。

[Debug hardware] : J-Link ARM [Target Device] : R7S721001

図 5-20 デバッガの設定

次に Startup タブを選択しデフォルトで設定されているブレイクポイントの解除を行います。図 5-21 の チェックボックスを外してください。これを解除しないと起動時に必ず main で 1 度停止してしまいます。

図 5-21 ブレイクポイントの解除

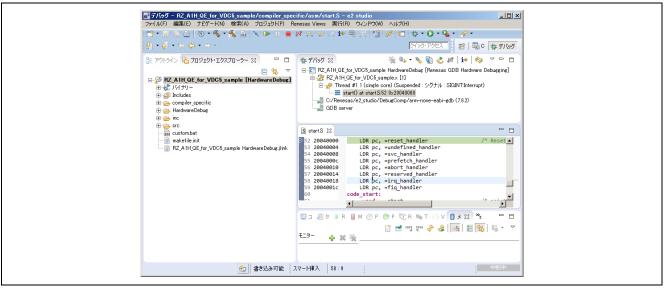

以上の設定後、デバッガが接続されている状態であれば、デバッグボタンを押下することで、プログラムのロードが始まりデバッグ環境が立ち上がります(図 5-22)。

図 5-22 デバッグ環境起動の画面

デバッガの起動後、正常に表示機器の設定が行われた場合、周辺に1ピクセルのラインを描画した図 5-23 が示されます。この画面は、"QE for Video Display Controller 5"から生成されたヘッダ情報の表示サイズ からプログラムで生成しています。尚、この画面が左右にずれるなど、正常な確認が出来なかった場合、"QE for Video Display Controller 5"を使用し、制御信号タイミングの調整を行います。

図 5-23 起動画面

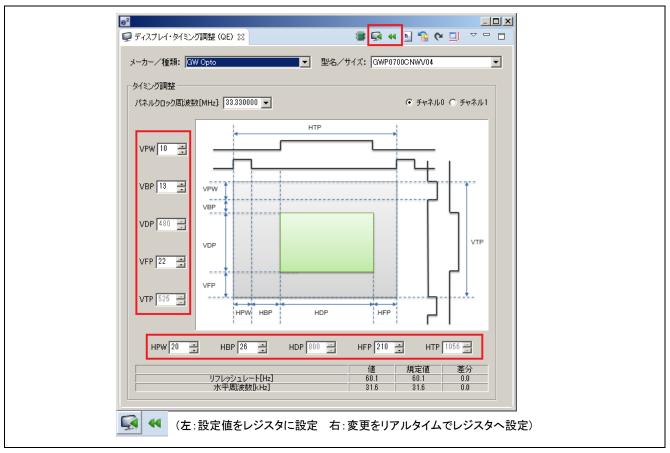

### 5.2 "QE for Video Display Controller 5"を使用したリアルタイム調整機能

デバッガを接続し本サンプルプログラムを起動後、図 5-24 に示す設定値を変更することで制御信号タイミングの変更が可能です。接続した表示機器の画面を見ながら調整しヘッダファイル再度出力してください。

図 5-24 制御信号タイミングのデバッグ

【注】 制御信号タイミングのデバッグは、デバッガを経由し VDC5 のレジスタを直接変更しています。 VDC5 のグラフィックス(2)を想定している為、ユーザでサンプルアプリケーションを変更し、他の グラフィックス(0)(1)(3)を使用した場合、想定の動作が出来ない場合があります。

### 5.3 "QE for Video Display Controller 5"のイメージダウンロード機能

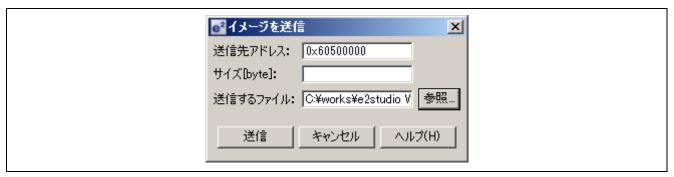

図 5-23 の画面を確認後、"QE for Video Display Controller 5"のイメージダウンロード機能を使用しユーザが表示したいイメージを表示させることも可能です。図 5-25 のアイコンにてイメージダイアログ(図 5-26)を表示してください。

図 5-25 イメージダウンロード起動アイコン

図 5-26 イメージダウンロードダイアログ

Address :表示データを格納するバッファアドレスを設定

Size[byte] : イメージファイルのサイズ(指定しない場合、ファイルサイズ)

Sending File : イメージファイル(バイナリ形式)

"Address"には、0x60500000 を設定してください。サンプルプログラムでは、表示データを格納するバッファを配列変数(FrameBuffer\_1[])で確保し VRAM\_SECTION\_1 セクション(0x60500000)に割り振っています。

"Sending File"には、サンプルプログラムで設定している表示データ形式にあわせたバイナリイメージを使用してください。サンプルプログラムでは、表示データ形式に RGB888 を設定しています。尚、ダウンロードするイメージファイルの生成には、同梱する ImagePackager(注 1)をご活用ください。

【注 1】 ImagePackager の詳細については、関連アプリケーションノート『RZ/A1H グループ グラフィックスライブラリ RGA (R01AN2162JJ/EJ)』を参考にしてください。

### 6. ユーザ環境に適応するには

本サンプルは、RSK CPU board(YR0K77210C000BE)及び RSK TFT APP Board(YROK77210C000BE)にあわせて作成されており、ユーザ環境で液晶表示の確認を行う為には、本サンプルをユーザ環境にあわせて修正する必要があります。以降に修正箇所について記載します。

### 6.1 CPU 及びボードの初期化

本サンプルプログラムは、RSK CPU board(YR0K77210C000BE)にあわせた初期化を行っています。その為、ユーザ環境にあわせて修正する必要があります。本サンプルでは、使用しておりませんが、SDRAM などの外部メモリの設定を行っております。ユーザ環境にあわせて修正してください。

### 6.2 VDC5 の動作設定

表示機器の制御に関する項目で"QE for Video Display Controller 5"で指定するものと、指定できないものがあり、この項目については、本サンプルプログラムで代用して行っています。その為、ユーザ環境に適応する為には、以下に記載する3つの項目を、ユーザ環境にあわせて修正する必要があります。

#### - 表示機器のタイミング制御

本サンプルでは、『RSK\_TFT\_ch0.h』を参照し VDC5 の設定を行っています。このヘッダファイルは、 "QE for Video Display Controller 5"で生成するファイルになります。

#### ― パネルクロックの設定

本サンプルでは、『RSK\_TFT\_panel\_clk.h』で行っています。ユーザ環境に合わせて修正する必要があります。尚、本項目は、"QE for Video Display Controller 5"では設定できません。

### — GPIO の設定

本サンプルでは、『lcd\_display\_ch0.c』の『GRAPHICS\_SetLcdPanel\_Ch0()』で行っています。ユーザ環境に合わせて修正する必要があります。尚、本項目は、"QE for Video Display Controller 5"では設定できません。

以降に"QE for Video Display Controller 5"では設定できない、パネルクロックの設定及び GPIO の設定について記載します。

### 6.2.1 パネルクロックの設定

VDC5 では、様々な入力クロックをソースクロックとしてパネルクロックを生成する事が可能です。以下に選択できるソースクロックを記載します。また、選択したソースクロックを分周( $1/1\sim1/32$ )して使用します。

- [ソースクロック]

- 映像クロック(VIDEO\_X1)

- 映像クロック(DV CLK)

- 外部クロック 0 (LCD0\_EXTCLK)

- 外部クロック 1 (LCD1\_EXTCLK)

- 周辺クロック1(P1φ)

- LVDS PLL のクロック

- LVDS PLL の 7 分周クロック

本サンプルでは、RSK TFT APP Board(YROK77210C000BE)の仕様にあわせ、図 5-12 に設定した『Panel Clock Frequency』33.3MHz を作成する為に、以下を選択しています。

- 周辺クロック 1 (P1 φ) 66.6MHz

- 1/2 分周

設定箇所は、『RSK\_TFT\_panel\_clk.h』で行っています。

• #define LCD\_CH0\_PANEL\_CLK (VDC5\_PANEL\_ICKSEL\_PERI)

• #define LCD\_CH0\_PANEL\_CLK\_DIV (VDC5\_PANEL\_CLKDIV\_1\_2)

### 6.2.2 LVDS PLL を使用したパネルクロックの生成

前項で複数のソースクロックから選択してパネルクロックの生成が行える内容について記載しましたが、ソースクロックに『LDCS PLL のクロック』を選択することで更に柔軟性のあるパネルクロックを生成する事が可能です。『LDCS PLL のクロック』は、LVDS の液晶を使用しない場合でも使用可能です。以下にいくつかの設定例を記載します。

本サンプルでは、『LDCS PLL のクロック』を選択し『周辺クロック  $1 (P1 \phi)$ 』 66.6 MHz をソースクロックとし 40 MHz を生成する設定するヘッダを参考に添付しています。

設定箇所は、『RSK\_HDMI\_800x600\_panel\_clk.h』になります。ソースクロックは、LVDS PLL で生成したクロックで分周は(1/1)になります。

#define LCD\_CH0\_PANEL\_CLK (VDC5\_PANEL\_ICKSEL\_LVDS)

#define LCD\_CH0\_PANEL\_CLK\_DIV (VDC5\_PANEL\_CLKDIV\_1\_1)

LVDS PLL の設定については、以下を設定しています。LVDS PLL へのソースクロックは、周辺クロック  $1(P1\phi)$  66.6MHz を選択しています。

• #define LVDS\_PLL\_INPUT\_CLK (VDC5\_LVDS\_INCLK\_SEL\_PERI)

以降の設定は、LVDS PLL の設定になります。設定値の詳細については、『RZ/A1H グループ、RZ/A1M グループ ユーザーズマニュアル』『40.5.1 LVDS PLL 設定』を参考してください。

#define LVDS\_PLL\_NIDV (VDC5\_LVDS\_NDIV\_4)

#define LVDS\_PLL\_NODIV (VDC5\_LVDS\_NDIV\_4)

#define LVDS\_PLL\_NFD (384u)#define LVDS\_PLL\_NRD (5u-1u)

• #define LVDS\_PLL\_NOD (VDC5\_LVDS\_PLL\_NOD\_8)

その他のパネルクロックを設定したい場合の設定例を表 6-1 に記載します。

#### 表 6-1 LVDS PLL を使用したパネルクロック設定例

| 生成するパネルクロック           | 25.175 [MHz]             | 40.0[MHz]              | 65.0[MHz] | 83.5[MHz] | 85.5[MHz] |  |  |

|-----------------------|--------------------------|------------------------|-----------|-----------|-----------|--|--|

| LCD_CH0_PANEL_CLK     | VDC5_PANEL_              | VDC5_PANEL_ICKSEL_LVDS |           |           |           |  |  |

| LCD_CH0_PANEL_CLK_DIV | VDC5_PANEL_              | CLKDIV_1_1             |           |           |           |  |  |

| LVDS_PLL_INPUT_CLK    | VDC5_LVDS_INCLK_SEL_PERI |                        |           |           |           |  |  |

| LVDS_PLL_NIDV         | VDC5_LVDS_NDIV_4         |                        |           |           |           |  |  |

| LVDS_PLL_NODIV        | VDC5_LVDS_NDIV_4         |                        |           |           |           |  |  |

| LVDS_PLL_NFD          | 145                      | 384                    | 312       | 481       | 82        |  |  |

| LVDS_PLL_NRD          | (3u-1u)                  | (5u-1u)                | (5u-1u)   | (6u-1u)   | (1u-1u)   |  |  |

| LVDS_PLL_NOD          | 8                        | 8                      | 4         | 4         | 4         |  |  |

### 6.3 GPIO の設定

RZ/A1 の各ポートは、周辺モジュールの端子とマルチプレクスされており、レジスタの設定により、マルチプレクス端子の機能(兼用機能)を選択できます。今回、表示機器の出力端子に以下を設定しましたが、複数の端子にマルチプレクスされています。以下に RZ/A1H でマルチプレクスされているポートを記載します。

出力端子の選択 (マルチプレクスされているポート)

• Vsync: TCON4 (P3\_5, P11\_10, P11\_13)

Hsync: TCON3 (P3\_4, P11\_11)DE: TCON2 (P3\_3, P11\_12)

本サンプルは、RSK CPU board(YR0K77210C000BE)及び RSK TFT APP Board(YROK77210C000BE)にあわせている為、以下のポートを選択しています。

出力端子の選択 (選択したポート)

Vsync : TCON4 (P11\_10)

Hsync : TCON3 (P11\_11)

DE : TCON2 (P11\_12)

これら各ポートの設定は、『lcd\_display\_ch0.c』の『GRAPHICS\_SetLcdPanel\_Ch0()』で行っています。その他、表示機器制御に必要な以下端子についても同様に行っています。

出力端子の選択 (選択したポート)

• パネルクロック: LCD0\_CLK (P11\_15)

• データ : LCD DATA23~LCD DATA0 (P11\_7~P11\_0、P10\_15~P10\_0)

これらの設定についても、ユーザの使用する表示機器にあわせて設定してください。

以上の修正でユーザの使用する表示機器の動作確認が可能になります。

### 7. 参考ドキュメント

ユーザーズマニュアル

- RZ/A1H グループ ユーザーズマニュアルハードウェア編

- RZ/A1H グループ Renesas Starter Kit+ ユーザーズマニュアル "e2 studio"版 (最新の情報をルネサスエレクトロニクスホームページから入手してください。)

アプリケーションノート

- RZ/A1H 初期設定例(R01AN1864JJ/EJ)

- RZ/A1H グループ Video Display Controller 5 Sample Driver (R01AN1822JJ/EJ)

- RZ/A1H グループ グラフィックスライブラリ RGA (R01AN2162JJ/EJ) (最新の情報をルネサスエレクトロニクスホームページから入手してください。)

## ホームページとサポート窓口

ルネサス エレクトロニクスホームページ

http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/contact/

すべての商標および登録商標は、それぞれの所有者に帰属します。

# 改訂記録

|      |            | 改訂内容 |      |  |  |  |

|------|------------|------|------|--|--|--|

| Rev. | 発行日        | ページ  | ポイント |  |  |  |

| 1.00 | 2016/09/14 |      | 初版   |  |  |  |

|      |            |      |      |  |  |  |

### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本ドキュメントおよびテクニカルアップデートを参照してください。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセット のかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレス(予約領域)のアクセス禁止

【注意】リザーブアドレス(予約領域)のアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレス(予約領域)があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。

リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子 (または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

同じグループのマイコンでも型名が違うと、内部ROM、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ輻射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器・システムの設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因して、お客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 2. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報 の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 3. 本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権 に対する侵害に関し、当社は、何らの責任を負うものではありません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許 諾するものではありません。

- 4. 当社製品を改造、改変、複製等しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、

各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、

家電、工作機械、パーソナル機器、産業用ロボット等 高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、

防災・防犯装置、各種安全装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(原子力制御システム、軍事機器等)に使用されることを意図しておらず、使用することはできません。 たとえ、意図しない用途に当社製品を使用したことによりお客様または第三者に損害が生じても、当社は一切その責任を負いません。 なお、ご不明点がある場合は、当社営業にお問い合わせください。

- 6. 当社製品をご使用の際は、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他の保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に 関して、当社は、一切その責任を負いません。

- 9. 本資料に記載されている当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。また、当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途に使用しないでください。当社製品または技術を輸出する場合は、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。

- 10. お客様の転売等により、本ご注意書き記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は何らの責任も負わず、お客様にてご負担して頂きますのでご了承ください。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 注1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数 を直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサスエレクトロニクス株式会社

http://www.renesas.com

■営業お問合せ窓口

※営業お問合せ窓口の住所は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス株式会社 〒135-0061 東京都江東区豊洲3-2-24 (豊洲フォレシア)

■技術的なお問合せおよび資料のご請求は下記へどうぞ。 総合お問合せ窓口: http://japan.renesas.com/contact/

© 2016 Renesas Electronics Corporation. All rights reserved.

Colophon 4.0