# Application Note Powering Xilinx Zynq with DA9061/2/3

# **AN-PM-087**

# Abstract

Xilinx® Zynq<sup>™</sup> All-Programmable<sup>™</sup> UltraScale+<sup>™</sup> is complemented by the programmable architecture of Dialog power management ICs, providing the system developer with flexibility throughout the design cycle. This application note outlines how to determine the power requirements of a Zynq UltraScale+ MPSoC-based system and select a suitable PMIC from the Dialog DA9061, DA9062, and DA9063 family.

# AN-PM-087

# Powering Xilinx Zynq with DA9061/2/3

# Contents

| Ab | strac | t                                                   | . 1 |

|----|-------|-----------------------------------------------------|-----|

| Co | ntent | S                                                   | . 2 |

| 1  | Tern  | ns and Definitions                                  | . 3 |

| 2  | Refe  | erences                                             | . 3 |

| 3  | Intro | oduction                                            | . 4 |

| 4  | Crea  | ating a Power Management Solution                   | . 4 |

|    | 4.1   | Calculate the Processor Power Requirements          | . 4 |

|    | 4.2   | Map the Power Requirements to the PMIC Capabilities | . 5 |

|    | 4.3   | Power-up Sequence                                   | . 7 |

|    | 4.4   | OTP Programming                                     |     |

| 5  | Pow   | er Solution Examples                                | . 8 |

|    | 5.1   | ZU3EG                                               | . 8 |

|    | 5.2   | ZU7EV                                               | . 9 |

|    | 5.3   | ZU9CG                                               | 10  |

| 6  | Con   | clusions                                            | 12  |

| Ap | pend  | ix A SmartCanvas Software Overview                  | 13  |

| Re | visio | n History                                           | 14  |

# **1** Terms and Definitions

| ADAS   | Advanced Driver Assistance Systems          |

|--------|---------------------------------------------|

| GUI    | Graphical User Interface                    |

| PMIC   | Power Management Integrated Circuit         |

| DA906x | Dialog DA9061, DA9062, DA9063, and DA9063L. |

| DVC    | Dynamic Voltage Control                     |

| DVS    | Dynamic Voltage Scaling. Analogous to DVC.  |

| MPSoC  | Multiprocessor System-on-Chip               |

| OTP    | One-Time Programmable (memory)              |

| RTC    | Real-Time Clock                             |

| SoC    | System-on-Chip                              |

# 2 References

- [1] Xilinx Power Estimator (XPE), http://www.xilinx.com/products/technology/power/xpe.html [Accessed 4th Oct 2016]

- [2] Philofsky, B., 'Seven Steps to an Accurate Worst-Case Power Analysis Using Xilinx Power Estimator (XPE)', WP353, v1.0, Xilinx Inc., 2008.

- [3] DA9061, Datasheet, Dialog Semiconductor

- [4] DA9062, Datasheet, Dialog Semiconductor

- [5] DA9063, Datasheet, Dialog Semiconductor

- [6] DA9063L, Datasheet, Dialog Semiconductor

- [7] AN-PM-080, 'In-Circuit Programming of DA9061/2/3', Dialog Semiconductor, 2016

- [8] UM-PM-008, SmartCanvas™ DA9061/2 User Manual, Dialog Semiconductor

# 3 Introduction

The Xilinx Zynq All-Programmable UltraScale+ MPSoC portfolio integrates the flexibility of software and hardware programmability of an FPGA. The Zynq processors are therefore ideally complemented by the software-configurable and programmable power management solution provided by the advanced architecture of Dialog PMICs.

The UltraSCale+ MPSoC processors require dedicated power management for a stable and reliable system. However, system power consumptions vary greatly due to the differing demands of the SoC and non-integrated peripherals. This application note outlines how to calculate the power demands of a Zynq system which then enables selection of a suitable system PMIC from the Dialog DA906x family. The features of the DA906x family enable significant power saving, such as Dynamic Voltage Control (DVC) which intelligently manages voltage changes. Section 4 describes the procedure, followed by examples in Section

# 4 Creating a Power Management Solution

A key point of this application note is that the choice of power management solution can only be determined after the power requirements of a system have been estimated. With FPGA-based processors, the power requirements may vary greatly. This means it is not possible for PMIC suppliers to provide a single power management reference design for these systems. Therefore the following procedure is recommended:

- 1. Calculate the system power requirements contributed by:

- a. the Zyng MPSoC

- b. other peripherals

- 2. Map the power requirements to the PMIC capabilities.

#### 4.1 Calculate the Processor Power Requirements

The Zynq power requirements can be estimated using the 'Xilinx Power Estimator' (XPE). The XPE tool is available for download from the Xilinx website [1]. For the purposes of defining PMIC requirements, a worst-case analysis should be performed by setting the 'Process' variable to 'maximum'. See the Xilinx application note [2] for further details.

The worst-case load currents should then be calculated for those peripherals not integrated into the SoC.

For each supply rail, the worst-case load current should be noted.

#### 4.2 Map the Power Requirements to the PMIC Capabilities

The next step is to map the load currents onto PMIC supply rails. A worksheet to assist with this step is presented in Table 1. One or more products may be chosen from the DA906x family, listed below in order of increasing capability:

- 1. DA9061 PMIC supplying up to 6 A

- 2. DA9062 PMIC supplying up to 8.5 A

- 3. DA9063L High power PMIC supplying up to 13 A

- 4. DA9063 High power PMIC supplying up to 14 A

Several of the above system PMICs can be used together as a master system PMIC and slave, or can be supplemented by one or more of the following sub-PMICs:

- 1. DA9210 12 A buck with programmable control

- 2. DA9211 Multiphase 12 A buck with programmable control

- 3. DA9212 Multiphase 2 x 6 A bucks with programmable control

- 4. DA9213 Multiphase 20 A buck with programmable control

- 5. DA9214 Multiphase 2 x 10 A bucks with programmable control

- 6. DA9215 Multiphase 15 A and 5 A bucks with programmable control

The DA9062 is pin-compatible with the DA9061 and provides additional features often required by systems such as a real-time clock (RTC), a dual-phase (5 A) buck configuration, DDR memory termination (DA9062 VTT supply), and VTTR memory reference voltage.

Where current monitoring is required but not performed by a Zynq System Controller, the ADC and rail monitoring integrated into the DA9063 and DA9063L can be used.

Spare bucks can be used as part of the programmable logic (PL) solution, to drive additional peripherals, or to drive LDO VDDs which can improve system efficiency.

Dialog sub-PMICs are designed to operate as slaves to the system PMIC, with integrated control. Configuration of the system is no more complex than when a system PMIC is used alone. This also applies when two system PMICs are used together. If one or more discrete regulators are required to supplement the capabilities of the Dialog PMICs, then these can often be incorporated into the programmable start-up and shutdown sequences within the Dialog system PMIC by using the general purpose outputs (GPOs) which can be sequenced.

**Application Note**

#### Table 1: Example Worksheet for Mapping System Power to PMIC Options (ZU9EG - Processing System (PS) only)

| Zynq System Supply Name          | Voltage (V)      | Load (from XPE calculation) (A) | Mapping Option A<br>(PMIC#[regulators]) | Mapping Option B<br>(PMIC[regulators]) | Mapping Option C<br>(PMIC[regulators]) |

|----------------------------------|------------------|---------------------------------|-----------------------------------------|----------------------------------------|----------------------------------------|

| VCC_PSINTFP +<br>VCC_PSINTFP_DDR | 0.85             | 4.70                            | DA9062_#1[Buck1+Buck2]                  | DA9062[Buck1+Buck2]                    | DA9063[BUCKCORE1+BUCKCORE2]            |

| VCCDDR4                          | 1.2              | 2.00                            | DA9062_#2[Buck 1]                       | DA9061[Buck2]                          | DA9063[BUCKPRO]                        |

| VCCO_DDR                         | 1.1/1.2/1.35/1.5 | 1.80                            | DA9062_#1[Buck3]                        | DA9061[Buck1]                          | DA9063[BUCKMEM+BUCKIO]                 |

| VCC_PSINTLP                      | 0.85             | 1.50                            | DA9062_#1[Buck 4]                       | DA9062[Buck3]                          | DA9063[BUCKPERI]                       |

| VCC_PSIO[0-2]                    | 1.8/2.5/3.3      | 0.35                            | DA9062_#1[LDO1+LDO2]                    | DA9062[LDO1+LDO2]                      | DA9063[LDO3+LDO4]                      |

| VCC_PSIO[n]                      | 1.8/2.5/3.3      | 0.10                            | DA9062_#2[LDO1]                         | DA9061[LDO1]                           | DA9063[LDO5]                           |

| VPS_MGTRAVCC                     | 0.85             | 0.30                            | DA9062_#2[Buck 4]                       | DA9062[Buck4]                          | DA9063[LDO1+LDO2]                      |

| VCCAUX                           | 1.8              | 0.2                             | DA9062_#1[LDO3]                         | DA9062[LDO3]                           | DA9063[LDO10]                          |

| VCC_PSDDR_PLL                    | 1.8              | 0.20                            | DA9062_#1[LDO4]                         | DA9062[LDO4]                           | DA9063[LDO6]                           |

| VCC_PSPLL                        | 1.2              | 0.07                            | DA9062_#2[LDO2]                         | DA9061[LDO2]                           | DA9063[LDO7]                           |

| VMGTRAVTT                        | 1.8              | 0.03                            | DA9062_#2[LDO3]                         | DA9061[LDO3]                           | DA9063[LDO8]                           |

| spare                            |                  |                                 | DA9062_#2[Buck 2]                       | DA9061[Buck3]                          | DA9063[LDO9]                           |

| spare                            |                  |                                 | DA9062_#2[Buck 3]                       | DA9061[LDO4]                           | DA9063[LDO11]                          |

| spare                            |                  |                                 | DA9062_#2[LDO4]                         |                                        |                                        |

### 4.3 **Power-up Sequence**

The sequence described in the Xilinx datasheets is readily programmed into the DA906x PMICs using Dialog's <u>SmartCanvas</u><sup>™</sup> GUI, see Appendix A. Sequencing of a slave PMIC or sub-PMICs can be included in the same sequence. The completed sequence is saved with other configuration settings into an ini file. After testing the configuration using the <u>SmartCanvas</u><sup>™</sup> Power Commander Mode, the ini file can then be used to program the PMIC OTP memory.

# 4.4 **OTP Programming**

Various options are available for OTP programming. The most suitable option depends on the number of devices, see Table 2. Details of the evaluation kits are available on the Dialog website and can be ordered via distributors.

| Programming Method       | Suitability                                                                                            | Volume<br>(units) | Comments                                                                                                            |

|--------------------------|--------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------|

| Evaluation kit           | Development of PMIC configuration<br>using SmartCanvas software (Note<br>1) and 'Power Commander Mode' | 1                 | Avoids the need to program<br>the OTP. See the<br>SmartCanvas user manual [8]                                       |

|                          | Prototype builds or bespoke small volume manufacture                                                   | ≤ 30              | Evaluation kit and 'socket board' (Note 2)                                                                          |

| In-circuit programming   | Volume manufacturing                                                                                   | < 30k             | See AN-PM-080 [7]                                                                                                   |

| Dialog custom variant    | High volume manufacturing                                                                              | > 30k             | Usually supplied directly from<br>Dialog as a custom OTP<br>variant.                                                |

| Dialog standard variants | Platform-specific                                                                                      | ≥ 1               | Supplied with OTP<br>programmed for specific<br>platforms such as NXP i.MX<br>5 / 6, Atmel SAMA5, Renesas<br>R-Car. |

#### **Table 2: OTP Programming Options**

**Note 1** SmartCanvas is the GUI software included with the Dialog PMIC Evaluation Kits. The software can be downloaded separately from the Dialog Support website.

Note 2 Sockets boards are 'DA9063-EVAL6', ' DA9061-SOCKETBOARD' and 'DA9062-SOCKETBOARD'

# **5 Power Solution Examples**

The above procedure was used to create solutions for the following Xilinx processors.

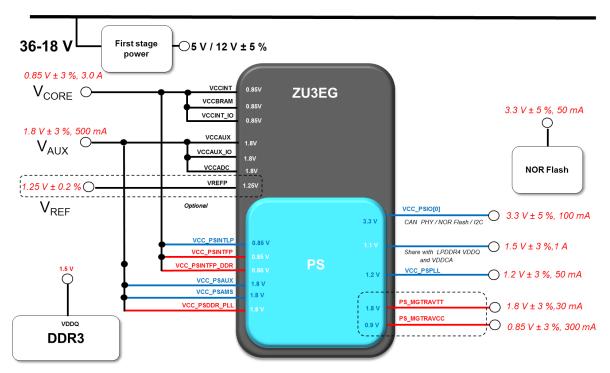

### 5.1 **ZU3EG**

The following mapping was optimized for industrial networking applications.

Figure 1. ZU3EG Supply Requirements

| Supply Rail       | Voltage (V) | Load (A) | Regulator     | Max Load (A) | DA9062<br>Power-up<br>Sequence |

|-------------------|-------------|----------|---------------|--------------|--------------------------------|

| V <sub>CORE</sub> | 0.8         | 3.0      | Buck1 + Buck2 | 5.0          | 1                              |

| V <sub>AUX</sub>  | 1.8         | 0.5      | Buck4         | 1.5          | 2                              |

| VCC_PSPLL         | 1.2         | 0.05     | LDO1          | 0.1          | 3                              |

| VCCO_PSDDR        | 1.5         | 1.0      | Buck3         | 2.0          |                                |

| VCC_PSIO[0]       | 3.3         | 0.2      | LDO4          | 0.3          | 4                              |

| PS_MGTRAVTT       | 1.8         | 0.1      | LDO2          | 0.3          |                                |

| PSMGTRAVCC        | 0.85        | 0.3      | LDO3          | 0.3          |                                |

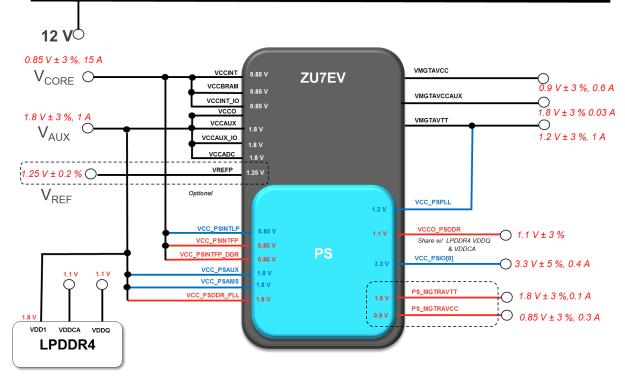

# 5.2 ZU7EV

The following mapping was optimized for automotive ADAS applications.

Figure 2. ZU7EV Supply Requirements

| Supply Rail | Voltage<br>(V) | Load<br>(A) |  | Device | Regulator      | Max Load (A) | Power-up<br>Sequence |

|-------------|----------------|-------------|--|--------|----------------|--------------|----------------------|

| VCORE       | 0.85           | 15          |  | DA9213 |                | 20           | 1                    |

| Vaux        | 1.8            | 1           |  | DA9062 | Buck4          | 1.5          | 2                    |

| VMGTAVCC    | 0.9            | 0.6         |  |        | Buck1          | 2.5          | 1                    |

| VMGTAVCCAUX | 1.8            | 0.03        |  |        | LDO2           | 0.3          |                      |

| VMGTAVTT    | 1.2            | 1           |  |        | Buck3          | 2.0          | 3                    |

| VCCO_PSDDR  | 1.1            | TBA         |  |        | Buck2          | 2.5          |                      |

| VCC_PSIO[0] | 3.3            | 0.4         |  |        | LDO1 +<br>LDO4 | 0.4          | 4                    |

| PS_MGTRAVTT | 1.8            | 0.1         |  |        | LDO2           | 0.3          |                      |

| PSMGTRAVCC  | 0.85           | 0.3         |  |        | LDO3           | 0.3          |                      |

| VDDCA       | 1.1            |             |  |        | Buck2          | 2.5          |                      |

| VDDQ        | 1.1            |             |  |        | Buck2          | 2.5          |                      |

#### Table 4: DA9062 and DA9213 Mapping to ZU7EV (12 V to 5 V Input Regulator Not Shown)

| A | ad  | licat | tion | Note | e |

|---|-----|-------|------|------|---|

|   | PP' | - Cu  |      |      | - |

## 5.3 ZU9CG

Mapping of the DA9063 system PMIC with DA9213 sub-PMIC is shown in Figure 3. The configuration for this mapping is given by Table 5. The designator 'User' means these are spare regulators that can be configured by the system developer.

| Vsys  |        |           |                  |                          |

|-------|--------|-----------|------------------|--------------------------|

|       | DA9213 | ]         | 0.85/0.9V, 20.8A | Rail 1b                  |

|       |        | -         | -                |                          |

|       |        | BuckCore1 | 0.85/0.9V, 2.55A | Rail 1a                  |

|       |        | BuckCore2 | 1.2V, 2.1A       | Rail 3                   |

|       |        | BuckIO    | 1.8V, 1.34A      | Rail 2                   |

|       |        | BuckPro   | 0.9V, 2A         | Rail 7                   |

|       |        | BuckMem   | User, 0.5A       | Rail 4                   |

|       |        | LDO1 & 2  | 0.85V, 0.3A      | Rail 6                   |

| VDDIO | DA9063 | BuckPeri  | User, 1.0A       | rail 13                  |

| VDDIO |        | LDO3      | 1.8V, 0.2A       | Rail 8                   |

|       |        | LDO4      | User, 0.1A       | Rail 9                   |

|       |        | LDO5      | User, 0.1A       | Rail 10                  |

|       |        | LDO6      | User, 0.1A       | Rail 11                  |

|       |        | LDO9&10   | User, 0.5A       | Rail 12                  |

|       |        | LDO8      | User, 0.2A       | Dialog VDDIO<br>supplies |

|       |        |           | L                | Subbues                  |

External VTT device required for DDR4

Rail 5

Figure 3. System Rail Mapping of DA9063 and DA9213 to ZU9CG

# Table 5: DA9063 and DA9213 Mapping to ZU9CG (12 V to 5 V Input and DDR4 Regulators are Not Shown)

| System Rail | ZU9CG Rail      | Voltage (V) | ZU9CG Rail Load<br>(A) | Total<br>Load (A) |

|-------------|-----------------|-------------|------------------------|-------------------|

|             | VCC_PSINTFP     | 0.85/0.9    | 1.4                    | 2.55              |

| Dail 1a     | VCC_PSINTLP     | 0.85/0.9    | 0.4                    |                   |

| Rail 1a     | VCC_PSINTFP_DDR | 0.85/0.9    | 0.75                   |                   |

|             | VCCINT_VCU      | 0.85/0.9    | -                      |                   |

|             | VCCINT          | 0.85/0.9    | 20                     | 20.8              |

| Rail 1b     | VCCINT_IO       | 0.85/0.9    | 0.2                    |                   |

|             | VCCBRAM         | 0.85/0.9    | 0.6                    |                   |

|             | VCC_PSAUX       | 1.8         | 0.1                    | 1.34              |

|             | VCC_PSDDR_PLL   | 1.8         | 0.1                    |                   |

|             | VCC_PSADC       | 1.8         | 0.02                   |                   |

| Rail 2      | VCCAUX          | 1.8         | 0.9                    |                   |

|             | VCCAUX_IO       | 1.8         | 0.2                    |                   |

|             | VCCADC          | 1.8         | 0.02                   |                   |

|             | DDR_VPP1        | USER        |                        |                   |

|             | VMGTAVTT        | 1.2         | 2                      | 2.1               |

|             | VMGTYAVTT       | 1.2         | -                      |                   |

| Rail 3      | VCC_PSPLL       | 1.2         | 0.1                    |                   |

|             | VCC_VCU_PLL     | 1.2         | -                      |                   |

|             | VCCO_PSDDR      | USER        | 0.5                    | 0.5               |

|             | DDR_VDD2        | USER        |                        |                   |

|             | DDR_VDDQ        | USER        |                        |                   |

|             | DDR_VTT         | USER        |                        | 0                 |

| Rail 5      | DDR_VREF        | USER        |                        |                   |

| Rail 6      | VPS_MGTRAVCC    | 0.85        | 0.3                    | 0.3               |

|             | VMGTAVCC        | 0.9         | 2                      | 2                 |

| Rail 7      | VMGTYAVCC       | 0.9         | -                      |                   |

|             | VMGTVCCAUX      | 1.8         | 0.1                    | 0.2               |

| Rail 8      | VMGTYVCCAUX     | 1.8         | -                      |                   |

|             | VPS_MGTRAVTT    | 1.8         | 0.1                    |                   |

| Rail 9      | VCCO_PSIO[0]    | USER        | 0.1                    | 0.1               |

| Rail 10     | VCCO_PSIO[1]    | USER        | 0.1                    | 0.1               |

| Rail 11     | VCCO_PSIO[2]    | USER        | 0.1                    | 0.1               |

| Rail 12     | HDIO VCCO       | USER        | 0.5                    | 0.5               |

| Rail 13     | HPIO VCCO       | USER        | 1                      | 1                 |

|             | VCC_PSBATT      | 0           | -                      |                   |

# 6 **Conclusions**

The flexibility and programmability of Dialog PMICs make them an ideal partner to the Xilinx Zynq All-Programmable SoCs. System power requirements can be calculated using the Xilinx Power Estimator (XPE) tool from which a regulator mapping can be made to Dialog PMIC(s).

# Appendix A SmartCanvas Software Overview

SmartCanvas is included in the Dialog DA906x evaluation kits and is the GUI used with the kit evaluation board. The GUI provides a visual representation of the device registers and of the PMIC operation state. The software (Figure 4) allows interaction with the PMIC, and can be used to read or write to device registers, for testing prototype configurations and to program socketed devices. The user manual [8] is accessible via the GUI 'Help' menu and is also available from the Dialog support site.

Power Commander Mode ('PC Mode') is a powerful feature of Dialog PMICs that allows prototyping of OTP configurations without having to burn a device's OTP. PC Mode starts a device using the configuration from an external ini file instead of the device's own programmed (or blank) configuration. These ini files are compatible with the In-Circuit Programmer and gang programmer, and therefore the same ini files can be used to program parts for volume manufacturing.

| 🖸 DA9062                                                                                                                                                                                                                                                                                                   |                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Ele Options Iools Search View Help                                                                                                                                                                                                                                                                         |                                                        |

| DA9062 USB_Ports ADC plot                                                                                                                                                                                                                                                                                  | Control ×                                              |

| Front Panel Controls Config Events/Status/IRQ GPIOs LDOs Bucks Power Sequencer RTC Customer OTP Table View                                                                                                                                                                                                 | <b>S</b> smartcanvas                                   |

|                                                                                                                                                                                                                                                                                                            | Sillar (Calivas                                        |

| GPL0 0 GPL0 0 Alas tow Input Isolate   BL0C1   BL0C2   BL0C3   BL0C4                                                                                                                                                                                                                                       | Raw I/O                                                |

| CPIO 1         GPIO 1 Alias         Low         Input         Isolate         1.372V         1.519V         3.338V         1.812V                                                                                                                                                                          | Advanced 0x80 + Dev Addr                               |

| GPIO 2 GPIO 2 Alias Low Input Isolate     BUCK 1 Alias     BUCK 2 Alias     BUCK 2 Alias     BUCK 3 Alias     BUCK 4 Alias                                                                                                                                                                                 | Batch Mode 0x0000 + Reg Addr                           |

| GPIO 3 GPIO 3 Alas Low Input Isolate<br>GPIO 4 GPIO 4 Alas Low Input Isolate Control                                                                                                                                                                                                                       | Send 0x00 Send Data                                    |

| UDOS LOO 1 LOO 1 Alias 3.282V                                                                                                                                                                                                                                                                              | Read 0x00 Read Data                                    |

| Sync 01/01/2000 00:05:47 LD0 2 LD0 2 Alias 1.795V                                                                                                                                                                                                                                                          | Bus Interface                                          |

| DA9062 INI File Control LDO 3 LDO 3 Allas 2.987V                                                                                                                                                                                                                                                           | DA9062 0x80 on bus 11 : Bus_0x80_DE  Disable Interface |

| Start Device Open LDO 4 LDO 4 Alias 2.788V                                                                                                                                                                                                                                                                 |                                                        |

| Save                                                                                                                                                                                                                                                                                                       | Communication                                          |

| DA9062_single_phase_basic_v07-5983.ini                                                                                                                                                                                                                                                                     | Communication                                          |

| Reset PD Sys Pwr Act Pwr 1                                                                                                                                                                                                                                                                                 |                                                        |

|                                                                                                                                                                                                                                                                                                            | USB connection                                         |

| Power Sequencer                                                                                                                                                                                                                                                                                            | USB device A>dev0 v                                    |

|                                                                                                                                                                                                                                                                                                            | Reconnect to device                                    |

|                                                                                                                                                                                                                                                                                                            | Power Commander Mode Refresh Enabled                   |

|                                                                                                                                                                                                                                                                                                            |                                                        |

|                                                                                                                                                                                                                                                                                                            | DA9062 INI File Control                                |

| Power Commander Mode                                                                                                                                                                                                                                                                                       | Start Device Save                                      |

| Refresh Enabled                                                                                                                                                                                                                                                                                            | DA9062_single_phase_basic_v07-5983.i                   |

|                                                                                                                                                                                                                                                                                                            | Status: 17:ACTIVE                                      |

|                                                                                                                                                                                                                                                                                                            | Reset PD Sys Pwr Act Pwr 1                             |

|                                                                                                                                                                                                                                                                                                            |                                                        |

|                                                                                                                                                                                                                                                                                                            | Enable/Disable Polling<br>Enabled                      |

|                                                                                                                                                                                                                                                                                                            |                                                        |

|                                                                                                                                                                                                                                                                                                            | I/O<br>Read all registers (excluding event)            |

| Status x Info                                                                                                                                                                                                                                                                                              | Read Event/Status/Fault regs                           |

| Console Log Register Info                                                                                                                                                                                                                                                                                  | Save Register Dump                                     |

|                                                                                                                                                                                                                                                                                                            | Load Register Dump                                     |

| Clear         Mark         Save to file         Filter (reg expr):         Log level:         Info         V           2015-10-26, 11152-96 (:) pritest Loranes part to that perce, pry: 30/114+01 (read register(outs=42, gaine=0x00-4) accress=0x00-40) = 0xaa         Log level:         Info         V | USB Interface Info<br>Interface: ATMEL_SAM3U           |

| 215:10-26, 11:52:50 [C:gittest[knreinge]]bhaldevice.pr;337!HFO] read_register[bus=Ac_k_sdave=Abb, address=0x0049] = 0xaa<br>215:10-26, 11:52:51 [C:gittest[knreinge]]bhaldevice.pr;337!HFO] read_register[bus=Ac_k_sdave=Abb, address=0x0049] = 0xab                                                       | USB device: 0<br>Firmware version: 1.12                |

| 2015-10-25, 11:52:52 (Crightest/Lbranes/pci_lb/hal/device.py:307.11/FO] read_register(bus=12x, daive=bobk), address=bx0040) = 0xac<br>2015-10-25, 11:52:53 (Crightest/Lbranes/pci_lb/hal/device.py:307.11/FO] read_register(bus=12x, daive=bx0b, address=bx0040) = 0xac                                    | Firmware Dev. version: 70144                           |

| 2015-10-26, 11:52:54 [c: gittest/branespoi lib/ha/giewce, py:307.IHF0 [read_register[bu==26, siave=bubb, address=bub040] = 0xae<br>2015-10-26, 11:52:55 [c: gittest/branespoi lib/al/giewce, py:307.IHF0 [read_register[bus=26, siave=bubb, address=bub040] = 0xaf                                         |                                                        |

|                                                                                                                                                                                                                                                                                                            | 1                                                      |

Figure 4: SmartCanvas Front Panel

# AN-PM-087

# Powering Xilinx Zynq with DA9061/2/3

# **Revision History**

| Revision | Date        | Description                                                |

|----------|-------------|------------------------------------------------------------|

| 2.2      | 25-Feb-2022 | File was rebranded with new logo, copyright and disclaimer |

| 2.1      | 06-Feb-2017 | Reviewer minor comments addressed                          |

| 2.0      | 09-Jan-2017 | Added section on Power Solution Examples                   |

| 1.0      | 15-Nov-2016 | Initial version.                                           |

**Application Note**

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.