R20TS0546ES0100

Rev.1.00

Feb. 01, 2020

# [Notes] e<sup>2</sup> studio Smart Configurator Plug-in,

# Smart Configurator for RX

### Outline

When using the products in the title, note the following point.

- 1. When using the PLL frequency synthesizer of the clock

- 1. When Using the PLL Frequency Synthesizer of the Clock

### 1.1 Applicable Products

- > e<sup>2</sup> studio V5.2.0 (Smart Configurator Plug-in V1.0.0) or later

- Smart Configurator for RX V1.0.0 or later

### 1.2 Applicable Devices

RX family: RX64M, RX651, RX65N, RX66T, RX71M, and RX72T groups

#### 1.3 Details

When PLL frequency synthesizer uses main clock as input, the input frequency range for PLL frequency synthesizer of the applicable products is incorrect and the input frequency can be set lower than 8MHz.

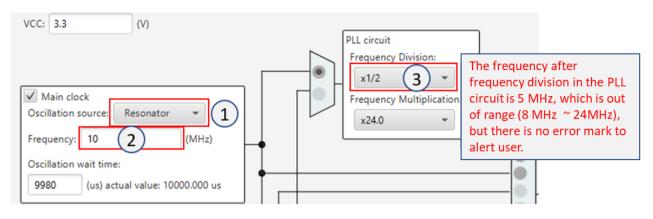

- (a) External oscillator is used as the oscillation source of main clock. (See Figure 1.1)

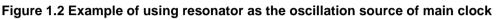

- (b) Resonator is used as the oscillation source of main clock. (See Figure 1.2)

| VCC: 3.3 (V)                                                       | PLL circuit                                                                                                                                                                                                                              |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main clock<br>Oscillation source: External o<br>Frequency: 6 (MHz) | Frequency Division:<br>x1 3<br>Frequency Multiplication:<br>x20.0<br>The frequency after<br>frequency division in the PLL<br>circuit is 6 MHz, which is out<br>of range (8 MHz ~ 24MHz),<br>but there is no error mark to<br>alert user. |

| Oscillation wait time:<br>9980 (us) actual value: 10000.000 us     |                                                                                                                                                                                                                                          |

#### Figure 1.1 Example of using external oscillator as the oscillation source of main clock

# **RENESAS TOOL NEWS**

### 1.4 Workaround

Set the input frequency for PLL frequency synthesizer <sup>(Note)</sup> within the correct range (8 MHz ~ 24 MHz). Note: Main clock frequency after frequency division in the PLL circuit.

### 1.5 Schedule for Fixing the Problem

This problem will be fixed in the Smart Configurator for RX V2.5.0 /  $e^2$  studio V7.8.0 (Scheduled to be released in March 2020.)

#### **Revision History**

|      |           | Description |                      |  |

|------|-----------|-------------|----------------------|--|

| Rev. | Date      | Page        | Summary              |  |

| 1.00 | Feb.01.20 | -           | First edition issued |  |

Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

The past news contents have been based on information at the time of publication. Now changed or invalid information may be included.

URLs in Tool News also may be subject to change or become invalid without prior notice.

## Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061 Japan www.renesas.com

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

## Contact information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

> $\ensuremath{\textcircled{\sc 0}}$  2020 Renesas Electronics Corporation. All rights reserved. TS Colophon 4.1