## **NEC**

# 用户手册

# 78K0R/KF3

16 位单片机微控制器

μPD78F1152 μPD78F1153 μPD78F1154 μPD78F1155 μPD78F1156

#### 78K0R/KF3 具有片上调试功能。

大规模生产时不要使用本产品,因为在使用片上调试功能后,从 flash 存储器可重写的次数受到限制这一点来看,它的可靠性不能保证。NEC Electronics 不接受对于本产品的任何投诉。

文档编号 U17893CA5V0UD00 (第五版) 发行日期 2008年1月 NS CP(K)

© NEC Electronics Corporation 2008 日本印制

## [备忘录]

#### -CMOS设备的注释 —

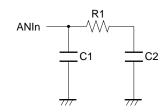

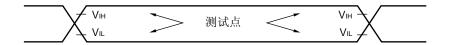

## ① 输入引脚处的电压波形

输入噪音或一个反射波引起的波形失真可能导致错误发生。如果由于噪音等的影响使CMOS设备的输入电压范围保持在 $V_{\rm IL}$ (最大值)和 $V_{\rm IH}$ (最小值)之间,设备可能发生错误。在输入电平固定时以及输入电平从 $V_{\rm IL}$ (最大值)过渡到 $V_{\rm IH}$ (最小值)时的传输期间,要防止散射噪声影响设备。

#### ② 未使用的输入引脚的处理

CMOS设备的输入端保持开路可能导致误操作。如果一个输入引脚未被连接,则由于噪音等原因可能会产生内部输入电平,从而导致误操作。CMOS设备的操作特性与Bipolar或NMOS设备不同。CMOS设备的输入电平必须借助上拉或下拉电路固定在高电平或低电平。每一个未使用引脚都应该通过附加电阻连接到V<sub>DD</sub>或GND。如果有可能尽量定义为输出引脚。对未使用引脚的处理因设备而异,必须遵循与设备相关的规定和说明。

#### ③ ESD 防护措施

如果MOS设备周围有强电场,将会击穿氧化栅极,从而影响设备的运行。因此必须采取措施,尽可能防止静电产生。一旦有静电,必须立即释放。对于环境必须有适当的控制。如果空气干燥,应当使用增湿器。建议避免使用容易产生静电的绝缘体。半导体设备的存放和运输必须使用抗静电容器、抗静电屏蔽袋或导电材料容器。所有的测试和测量工具包括工作台和工作面必须良好接地。操作员应当佩戴静电消除手带以保证良好接地。不能用手直接接触半导体设备。对于装配有半导体设备的PW板也应采取类似的静电防范措施。

#### ④ 初始化之前的状态

在上电时MOS设备的初始状态是不确定的。在刚刚上电之后,具有复位功能的MOS设备并没有被初始化。因此上电不能保证输出引脚的电平,I/O设置和寄存器的内容。设备在收到复位信号后才进行初始化。具有复位功能的设备在上电后必须立即进行复位操作。

#### ⑤ 电源开关顺序

在一个设备的内部操作和外部接口使用不同的电源的情况下,按照规定,应先在接通内部电源之后再

接通外部电源。当关闭电源时,按照规定,先关闭外部电源再关闭内部电源。如果电源开关顺序颠倒,可能会导致设备的内部组件过电压,产生异常电流,从而引起内部组件的误操作和性能的退化。 对于每个设备电源的正确开关顺序必须依据设备的规范说明分别进行判断。

#### ⑥ 电源关闭状态下的输入信号

不要向没有加电的设备输入信号或提供I/O上拉电源。因为输入信号或提供I/O上拉电源将引起电流注入,从而引起设备的误操作,并产生异常电流,从而使内部组件退化。

每个设备电源关闭时的信号输入必须依据设备的规范说明分别进行判断。

Windows 和 Windows NT 是 Microsoft Corporation 在美国/或其他国家的注册商标或商标。 PC/AT 是 International Business Machines Corporation 的商标。

EEPROM 是 NEC 电子公司的注册商标。

SuperFlash 是 Silicon Storage Technology, Inc 公司的注册商标。包括美国和日本在内的几个国家。

注意事项:该产品使用的 SuperFlash b 技术获得了 Silicon Storage Technology, Inc.公司的授权。

- 本文档所登载的内容有效期截至 2008 年 1 月。将来可能未经预先通知而更改。在实际进行生产设计时,请参阅各产品最新的数据表或数据手册等相关资料以获取本公司产品的最新规格。

- 并非所有的产品和/或型号都向每个国家供应。请向本公司销售代表查询产品供应及其他信息。

- 未经本公司事先书面许可,禁止复制或转载本文件中的内容。否则因本文件所登载内容引发的错误,本公司概不负责。

- 本公司对于因使用本文件中列明的本公司产品而引起的,对第三者的专利、版权以及其它知识产权的侵权行为概不负责。本文件登载的内容不应视为本公司对本公司或其他人所有的专利、版权以及其它知识产权作出任何明示或默示的许可及授权。

- 本文件中的电路、软件以及相关信息仅用以说明半导体产品的运作和应用实例。用户如在设备设计中应用本文件中的电路、软件以及相关信息,应自行负责。对于用户或其他人因使用了上述电路、软件以及相关信息而引起的任何损失,本公司概不负责。

- 虽然本公司致力于提高半导体产品的质量及可靠性,但用户应同意并知晓,我们仍然无法完全消除出现产品缺陷的可能。为了最大限度地减少因本公司半导体产品故障而引起的对人身、财产造成损害(包括死亡)的危险,用户务必在其设计中采用必要的安全措施,如冗余度、防火和防故障等安全设计。

- 本公司产品质量分为:

- "标准等级"、"专业等级"以及"特殊等级"三种质量等级。

"特殊等级"仅适用于为特定用途而根据用户指定的质量保证程序所开发的日电电子产品。另外,各种日电电子产品的推荐用途取决于其质量等级,详见如下。用户在选用本公司的产品时,请事先确认产品的质量等级。

"标准等级": 计算机,办公自动化设备,通信设备,测试和测量设备,音频·视频设备,家电,加工机械以及产业用机器人。

"专业等级": 运输设备(汽车、火车、船舶等),交通用信号控制设备,防灾装置,防止犯罪 装置,各种安全装置以及医疗设备(不包括专门为维持生命而设计的设备)。

"特殊等级: 航空器械, 宇航设备, 海底中继设备, 原子能控制系统, 为了维持生命的医疗设备、用于维持生命的装置或系统等。

除在本公司半导体产品的数据表或数据手册等资料中另有特别规定以外,本公司半导体产品的质量等级均为"标准等级"。如果用户希望在本公司设计意图以外使用本公司半导体产品,务必事先与本公司销售代表联系以确认本公司是否同意为该项应用提供支持。

#### (注)

- (1) 本声明中的"本公司"是指日本电气电子株式会社(NEC Electronics Corporation)及其控股公司。

- (2) 本声明中的"本公司产品"是指所有由日本电气电子株式会社开发或制造,或为日本电气电子株式会社(定义如上)开发或制造的产品。

## 引言

读者对象

本手册适用于那些希望了解 78K0R/KF3 功能,并设计开发应用系统和程序的工程师。

目标产品如下。

78K0R/KF3:  $\mu$ PD78F1152, 78F1153, 78F1154, 78F1155, 78F1156

目的

本手册用于帮助用户了解下面组件中描述的功能。

组件

78K0R/KF3 手册主要分为两个部分:手册和指令(与 78K0R 系列通用)。

78K0R/KF3 用户手册 (本手册) 78K0R 微控制器 用户手册 指令

- 引脚功能

- 内部模块功能

- 中断

- 其它内置外设功能

- 电气特性(目标值)

- CPU 功能

- 指令集

- 指令扩展

手册使用方法

在阅读本手册前,读者应掌握电子工程、逻辑电路和微控制器等方面的一般知识。.

- 如果读者要了解产品功能:

- → 请按**目录**顺序阅读本手册。标记 "<R>" 为主要修订处。在 PDF 文件中只要将 "<R>" 复制到 "查找"中,就可以很容易找到修订处。

- 如何解释寄存器格式:

- ightarrow 括号中的位名在 RA78K0R 中被定义为保留字,并且在 CC78K0R 中直接通过 #pragma sfr 伪指令定义为一个特殊功能寄存器(sfr)变量。

- 如果读者希望了解 78K0R 系列指令的详细信息:

- → 可参阅 78K0R 系列指令用户手册 ( (U17792E)。

规定 数据规则: 数据的高位部分在左边,低位部分在右边

有效低电平表示法: xxx (在引脚和信号名称上划一条线)

注:文中用注标注的术语脚注注意事项:需要特别关注的信息

**备注:** 补充信息

数的表示法: 二进制 ····×××× 或 ××××B

十进制 ····×××× 十六进制 ····××××H

**相关文档** 本手册中指出的相关文档可能会包括初稿版本。但是并未对初稿版本作特殊标注。

## 设备文档

| 文档名称                     | 文档编号    |

|--------------------------|---------|

| 78K0R/KF3 用户手册           | 本手册     |

| 78KOR 微控制器指令用户手册         | U17792E |

| 78KOR 微控制器自编程库类型 01 用户手册 | U18706E |

开发工具的相关文档 (软件) (用户手册)

| 文档名称                       |     | 文档编号    |

|----------------------------|-----|---------|

| CC78K0R Ver. 1.00 C 编译器    | 操作篇 | U17838E |

|                            | 语言篇 | U17837E |

| RA78K0R Ver. 1.00 汇编包      | 操作篇 | U17836E |

|                            | 语言篇 | U17835E |

| SM+ 系统模拟器                  | 操作篇 | U18010E |

| PM+ Ver. 6.20              |     | U17990E |

| ID78K0R-QB Ver. 3.20 集成调试器 | 操作  | U17839E |

## 开发工具的相关文档 (硬件) (用户手册)

| 文档名称                    | 文档编号    |

|-------------------------|---------|

| QB-MINI2 具有编程功能的片上调试仿真器 | U18371E |

| QB-78K0RKX3 在线仿真器       | U17866E |

#### 与 Flash 存储器编程相关文档

| 文档名称                    | 文档编号    |

|-------------------------|---------|

| PG-FP4 Flash 存储器编程器用户手册 | U15260E |

注意事项 对以上列出的相关文档所做修改恕不另行通知,在设计时请使用每个文档的最新版本。

#### 其他文档

| 大心人口                |         |

|---------------------|---------|

| 文档名称                | 文档编号    |

| 半导体选择指南 一产品和封装一     | X13769X |

| 半导体设备安装手册           | 注       |

| NEC 半导体设备质量等级       | C11531E |

| NEC 半导体设备可靠性/质量控制系统 | C10983E |

| 半导体设备防静电 ESD 保护指南   | C11892E |

注 浏览"半导体设备安装手册"网站(<a href="http://www.necel.com/pkg/en/mount/index.html">http://www.necel.com/pkg/en/mount/index.html</a>)。

注意事项 对以上列出的相关文档进行修改时恕不另行通知,在设计时请使用每个文档的最新版本。

## 目录

| 第一章 | 概述                                     | 17 |

|-----|----------------------------------------|----|

| 1.1 | 特性                                     | 17 |

| 1.2 | 应用                                     | 18 |

| 1.3 | 订购信息                                   | 18 |

| 1.4 | 引脚配置(俯视图)                              | 19 |

| 1.5 | 78K0R 系列单片机列表                          | 21 |

| 1.6 | 框图                                     | 22 |

| 1.7 | 功能概述                                   | 23 |

|     | THE LAN                                |    |

| 第二草 | 引脚功能                                   | 25 |

|     | 引脚功能列表                                 |    |

| 2.2 | 引脚功能描述                                 | 31 |

|     | 2.2.1 P00~P06(端口 0)                    | 31 |

|     | 2.2.2 P10~P17(端口 1)                    | 32 |

|     | 2.2.3 P20~P27(端口 2)                    | 33 |

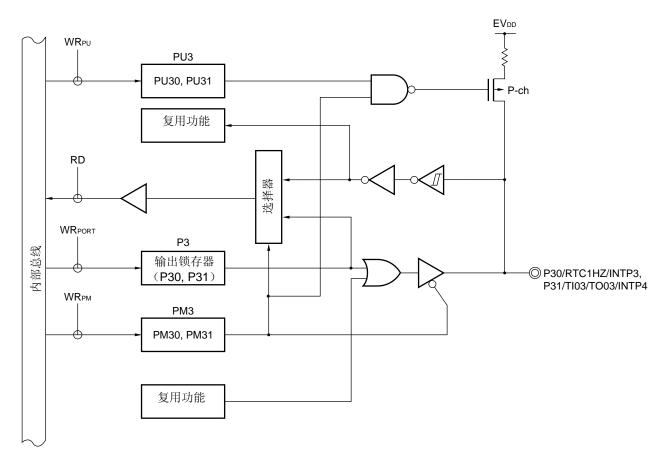

|     | 2.2.4 P30~P31 (端口 3)                   | 33 |

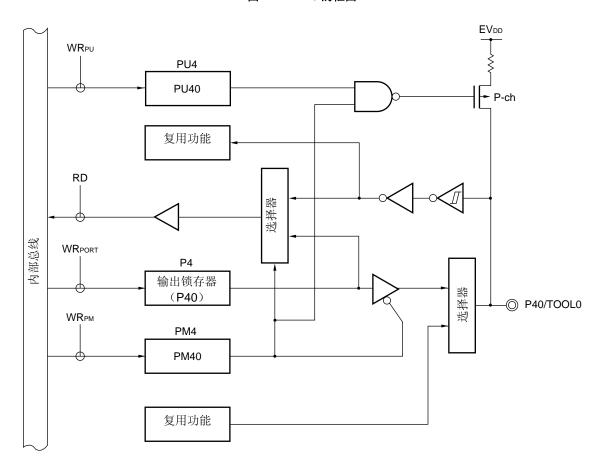

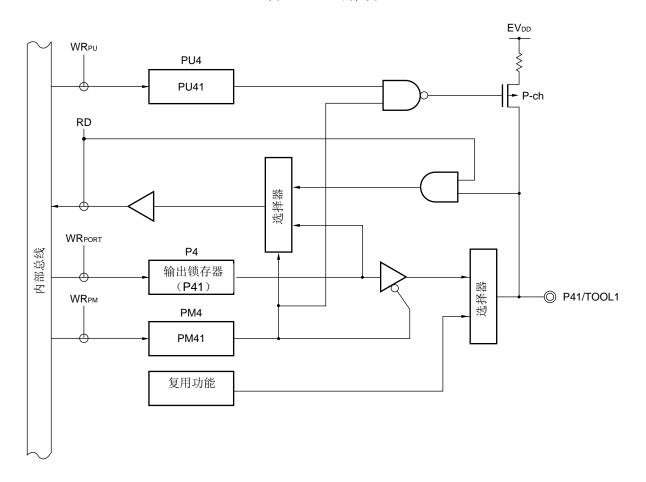

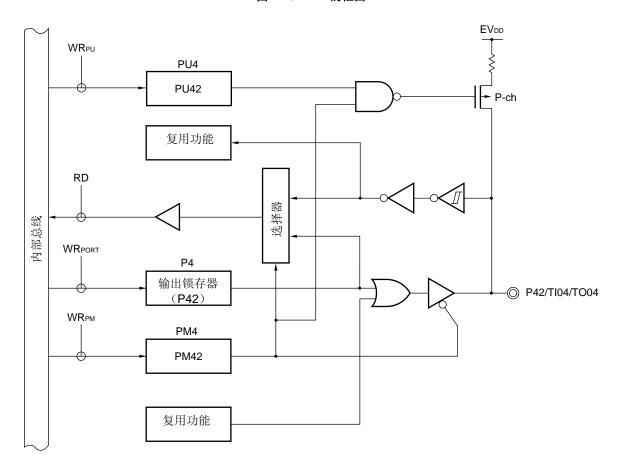

|     | 2.2.5 P40~P47(端口 4)                    | 34 |

|     | 2.2.6 P50~P55 (端口 5)                   | 35 |

|     | 2.2.7 P60~P67(端口 6)                    |    |

|     | 2.2.8 P70~P77(端口 7)                    |    |

|     | 2.2.9 P90 (端口 9)                       |    |

|     | 2.2.10 P110,P111(端口 11)                |    |

|     | 2.2.11 P120~P124 (端口 12)               |    |

|     | 2.2.12 P130 (端口 13)                    |    |

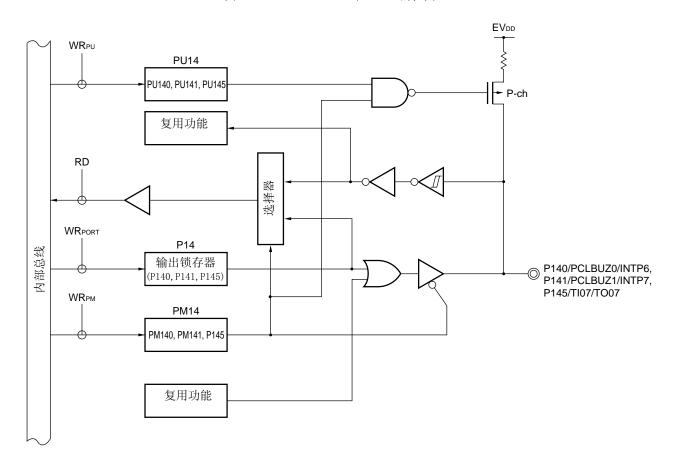

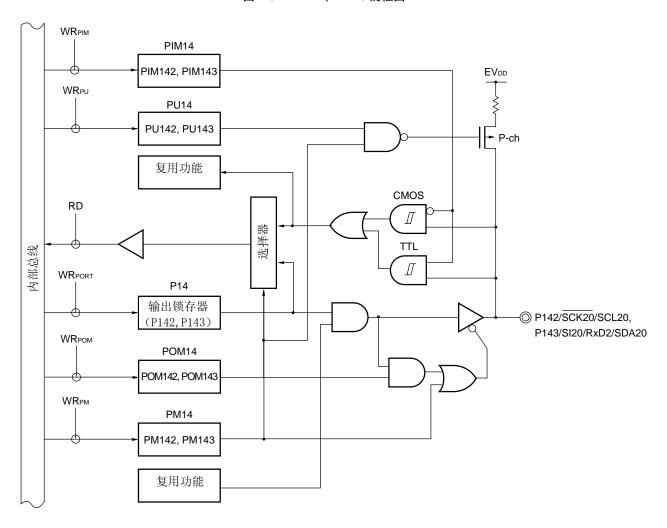

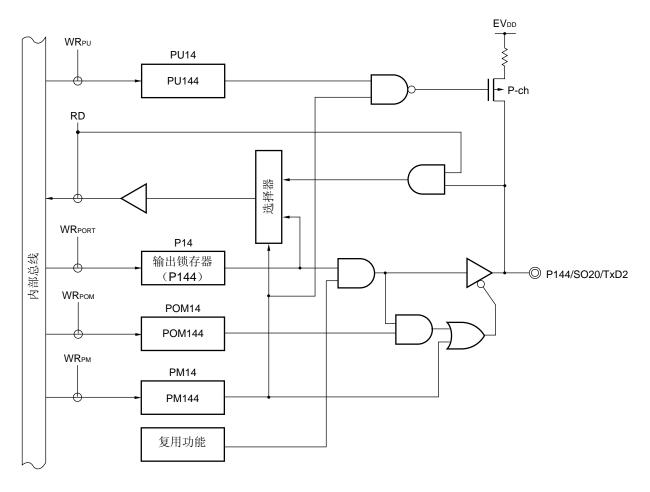

|     | 2.2.13 P140~P145 (端口 14)               | 38 |

|     | 2.2.14 AVREF0                          |    |

|     | 2.2.15 AVREF1                          |    |

|     | 2.2.16 AVSS                            |    |

|     | 2.2.17 RESET                           |    |

|     | 2.2.18 REGC                            |    |

|     | 2.2.19 VDD, EVDD                       |    |

|     | 2.2.20 VSS, EVSS                       |    |

|     | 2.2.21 FLMD0                           |    |

| 2.3 | 引脚 I/O 电路和未使用引脚的推荐连接方式                 | 41 |

| 第三章 | CPU 结构                                 | 46 |

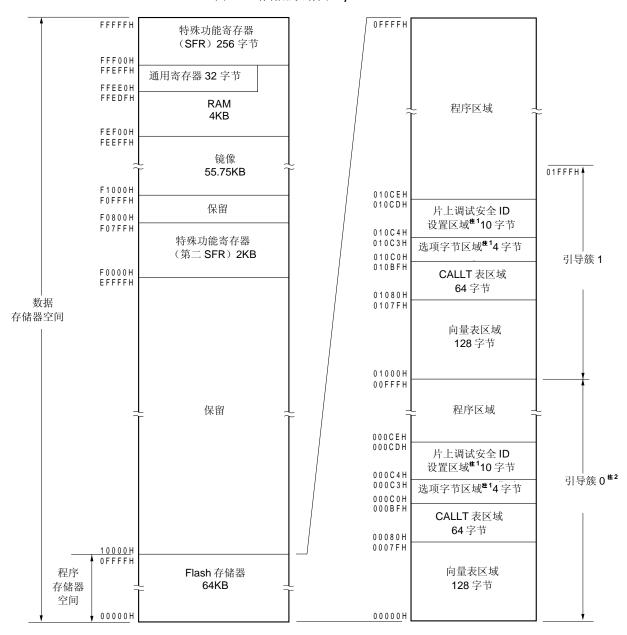

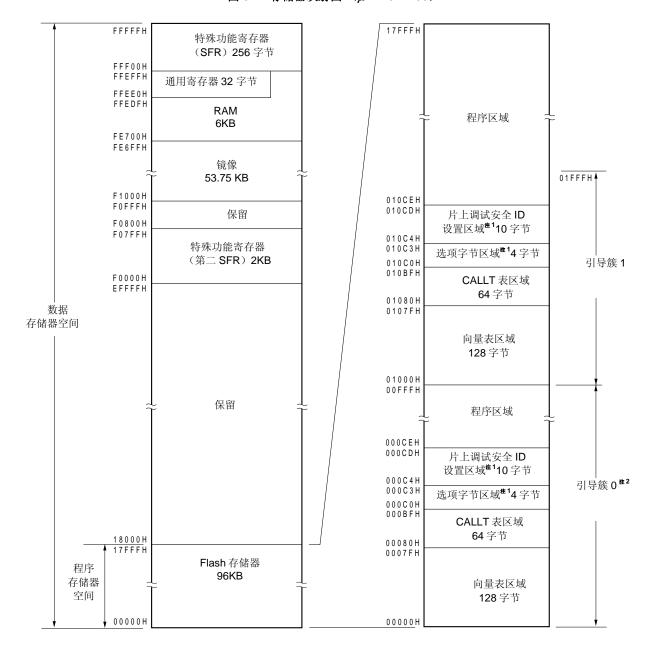

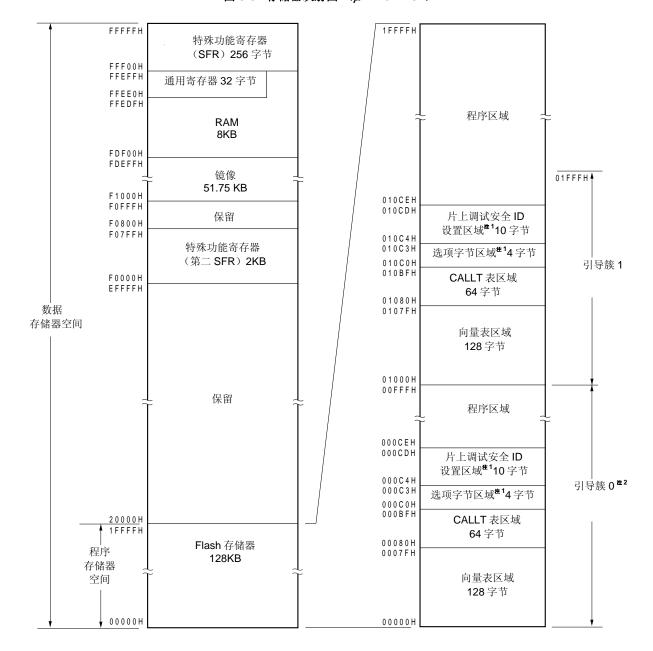

| 2.1 | 存储器空间                                  | 46 |

| 3.1 | <b>3.1.1</b> 内部程序存储器空间                 |    |

|     | 3.1.1 内部柱庁仔储益至间                        |    |

|     | 3.1.3 内部数据存储器空间                        |    |

|     | 3.1.3 內部                               |    |

|     | 3.1.4 特殊功能奇存器(SFR)区域                   |    |

|     | 3.1.5 扩展特殊功能奇存器 (第一 SFK: 第一特殊功能奇存器) 区域 |    |

| 2 2 | 3.1.6                                  |    |

| 3.2 | <b>3.2.1</b> 控制寄存器                     |    |

|     | 3.2.1 控制前任裔                            |    |

|     | V.C.C NB/11 円 TT III                   | 00 |

|     | 3.2.3 ES 和 CS 寄存器                  | 67  |

|-----|------------------------------------|-----|

|     | 3.2.4 特殊功能寄存器 (SFR)                | 68  |

|     | 3.2.5 扩展特殊功能寄存器(第二 SFR: 第二特殊功能寄存器) | 74  |

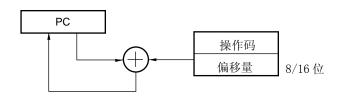

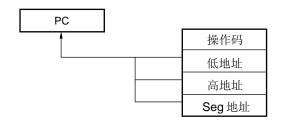

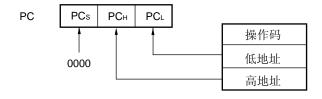

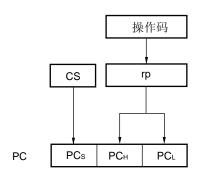

| 3.3 | 指令地址寻址                             | 80  |

|     | 3.3.1 相对寻址                         | 80  |

|     | 3.3.2 立即寻址                         | 80  |

|     | 3.3.3 表间接寻址                        | 81  |

|     | 3.3.4 寄存器直接寻址                      | 82  |

| 3.4 | 处理数据地址寻址                           | 83  |

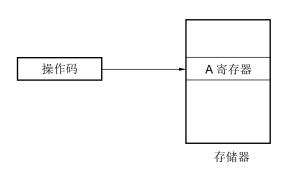

|     | 3.4.1 隐含寻址                         | 83  |

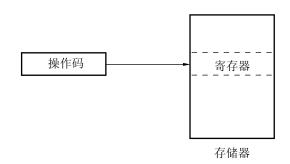

|     | 3.4.2 寄存器寻址                        | 83  |

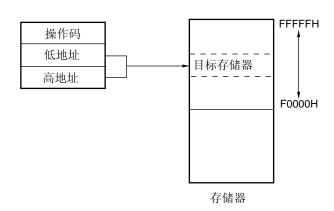

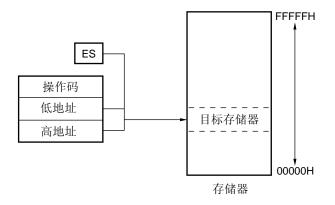

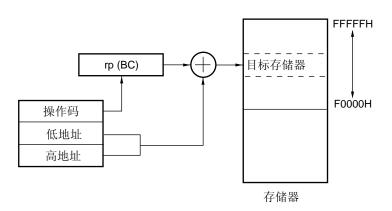

|     | 3.4.3 直接寻址                         | 84  |

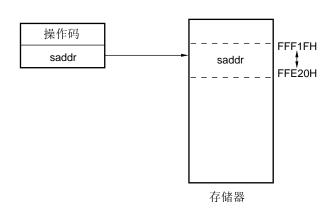

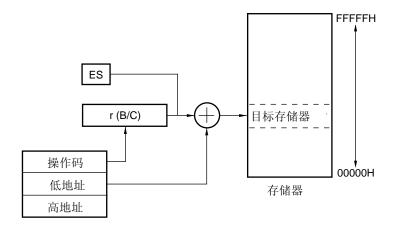

|     | 3.4.4 短直接寻址                        | 85  |

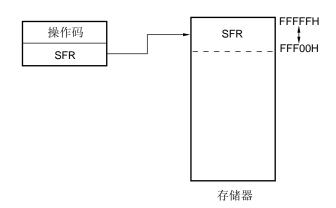

|     | 3.4.5 SFR 寻址                       | 86  |

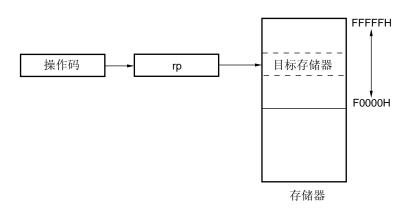

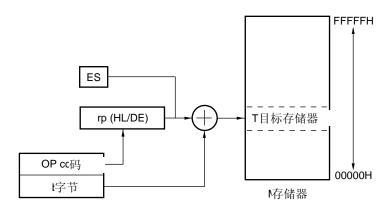

|     | 3.4.6 寄存器间接寻址                      | 87  |

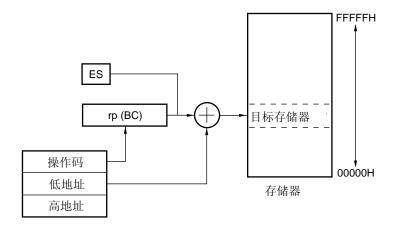

|     | 3.4.7 基址寻址                         | 88  |

|     | 3.4.8 基址变址寻址                       | 91  |

|     | 3.4.9 堆栈寻址                         | 92  |

| 第四章 | 端口功能                               | 93  |

| 4.1 | 端口功能                               | 93  |

|     | 端口配置                               |     |

|     | 4.2.1 端口 0                         |     |

|     | 4.2.2 端口 1                         |     |

|     | 4.2.3 端口 2                         |     |

|     | 4.2.4 端口 3                         |     |

|     | 4.2.5 端口 4                         |     |

|     | 4.2.6 端口 5                         |     |

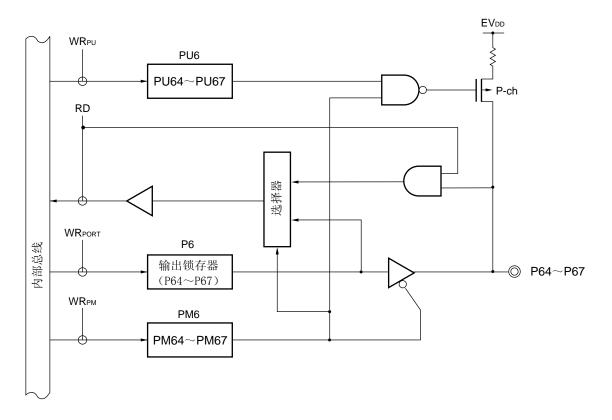

|     | 4.2.7 端口 6                         |     |

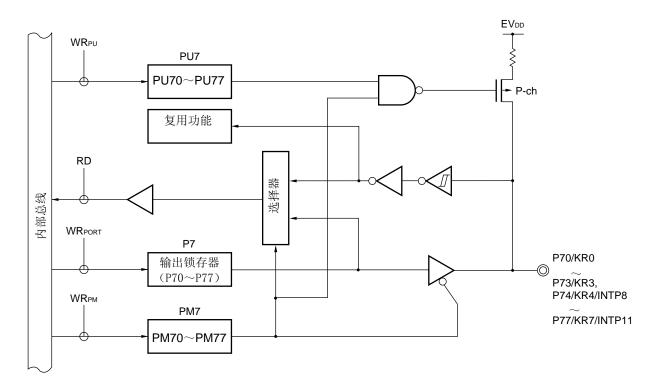

|     | 4.2.8 端口7                          |     |

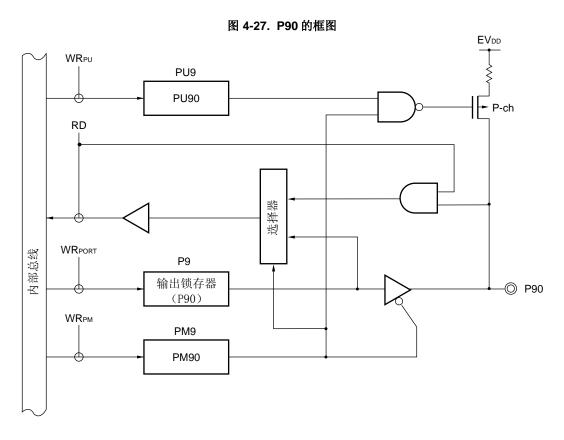

|     | 4.2.9 端口 9                         |     |

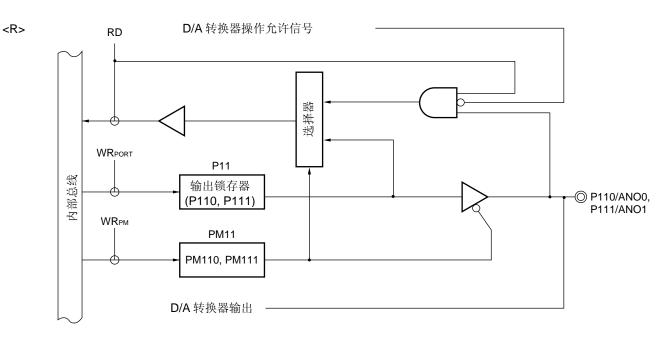

|     | 4.2.10 端口11                        |     |

|     | 4.2.11 端口12                        |     |

|     | 4.2.12 端口13                        |     |

|     | 4.2.13 端口14                        |     |

| 4.3 | 控制端口功能的寄存器                         |     |

|     | 端口功能操作                             |     |

|     | 4.4.1 写入 I/O 端口                    | 143 |

|     | 4.4.2 从 I/O 端口读取                   |     |

|     | 4.4.3 I/O 端口的操作                    |     |

|     | 4.4.4 连接到不同的供电电压(2.5V, 3V)的外部设备    |     |

| 4.5 | 使用复用功能时端口模式寄存器和输出锁存的设置             |     |

|     | 端口寄存器 n (Pn)的 1 位操作指令的注意事项         |     |

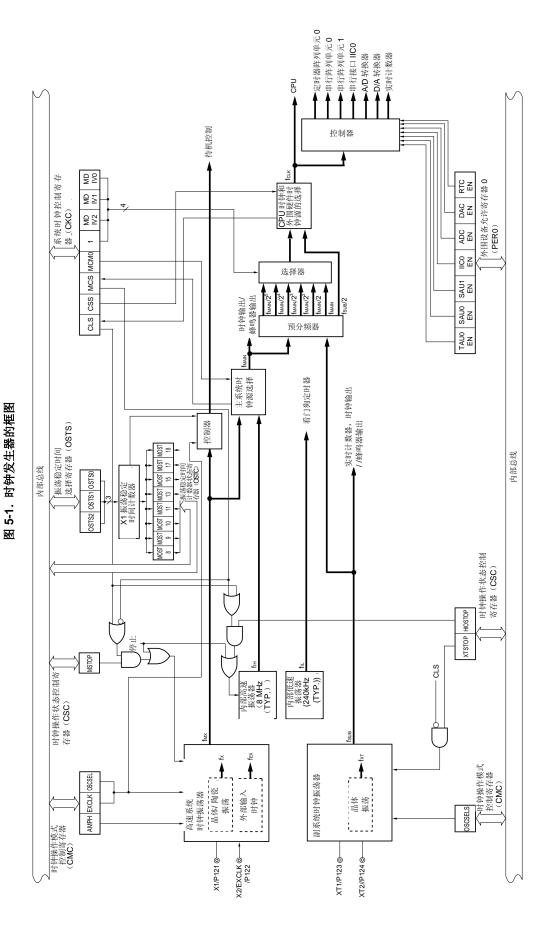

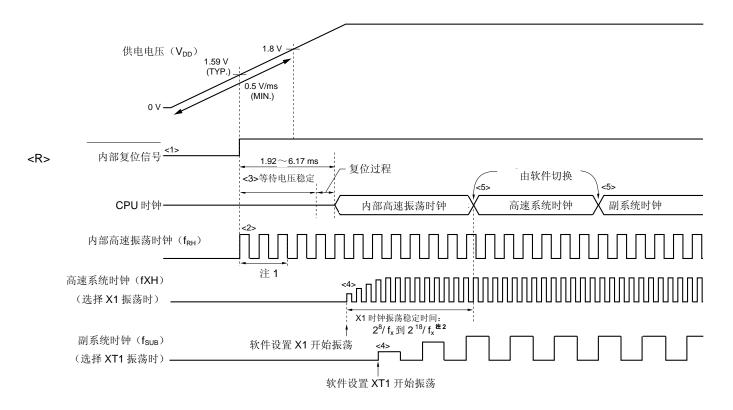

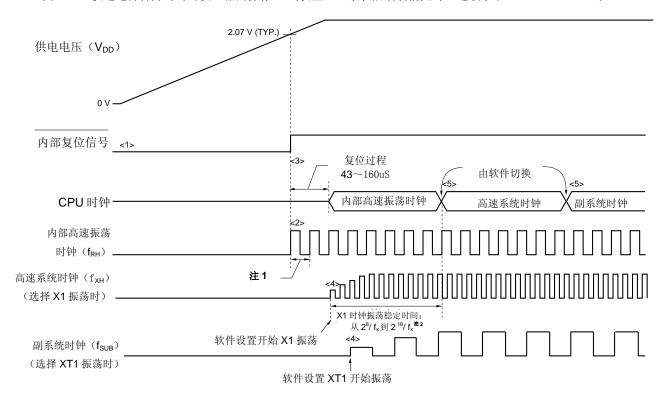

| 第五章 | 时钟发生器                              | 150 |

|     | 时钟发生器的功能                           |     |

|     | 时钟发生器的配置                           |     |

|     | 控制时钟发生器的寄存器                        |     |

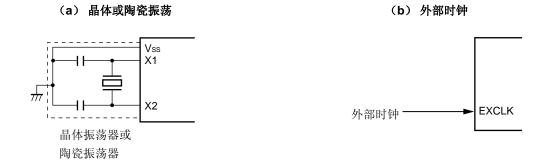

|     | 系统时钟振荡器                            | 167 |

|     | 5.4.1 X1 振荡器                | 167 |

|-----|-----------------------------|-----|

|     | 5.4.2 XT1 振荡器               | 167 |

|     | 5.4.3 内部高速振荡器               | 170 |

|     | 5.4.4 内部低速振荡器               | 170 |

|     | 5.4.5 预分频器                  | 170 |

| 5.5 | 时钟发生器操作                     | 171 |

| 5.6 | 控制时钟                        | 175 |

|     | 5.6.1 控制高速系统时钟的示例           | 175 |

|     | 5.6.2 控制内部高速振荡时钟的示例         | 178 |

|     | 5.6.3 控制副系统时钟示例             | 180 |

|     | 5.5.4 内部低速振荡时钟的控制示例         | 182 |

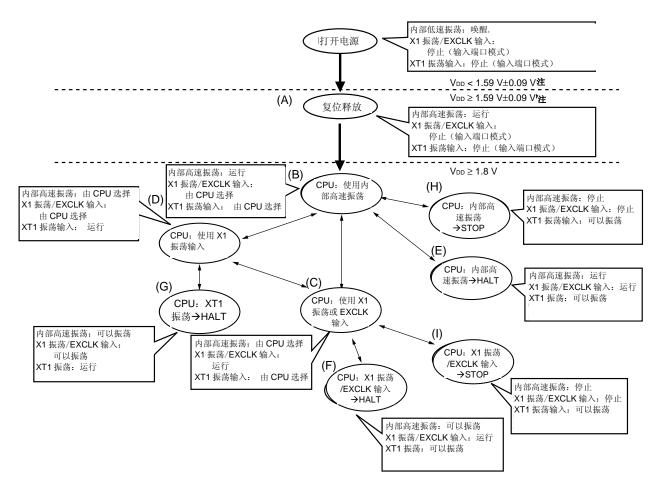

|     | 6.5.5 CPU 时钟状态迁移图           | 183 |

|     | 5.6.6 CPU 时钟切换之前的条件与切换之后的处理 | 188 |

|     | 5.6.7 CPU 时钟和主系统时钟切换所需的时间   | 189 |

|     | 5.6.8 时钟振荡停止前的条件            | 190 |

|     |                             |     |

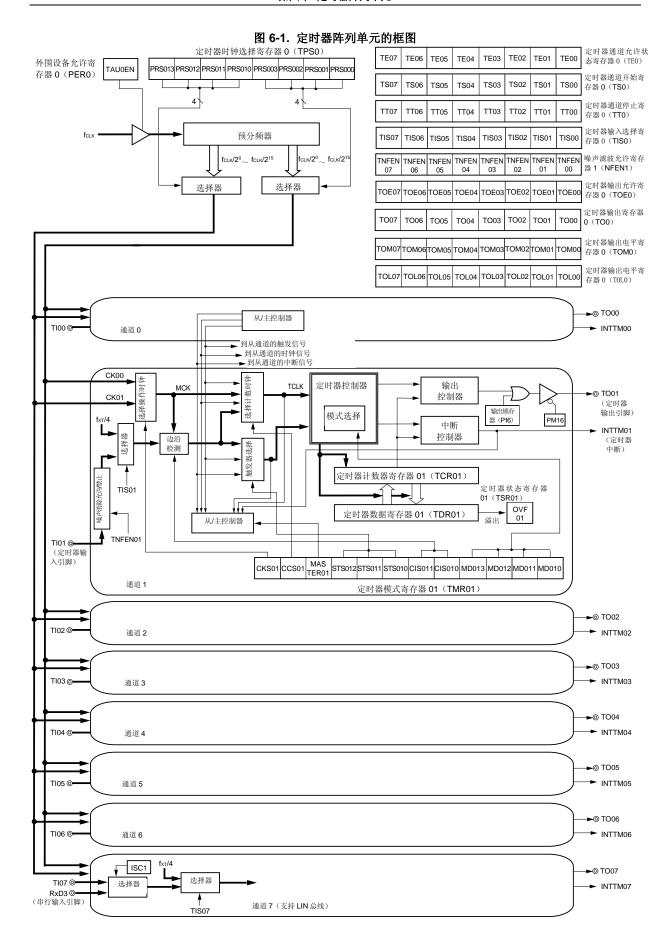

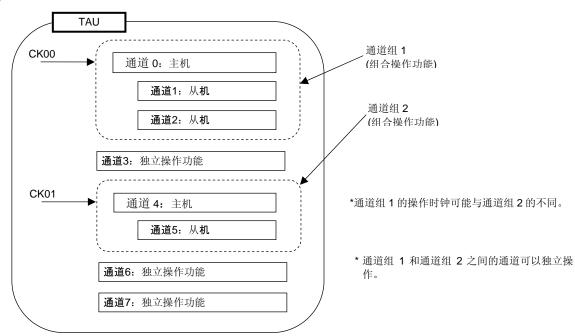

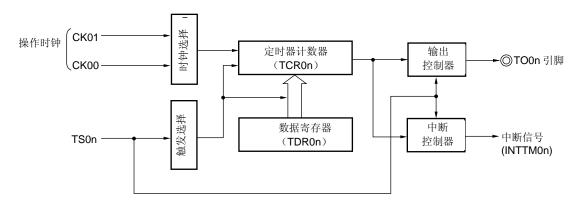

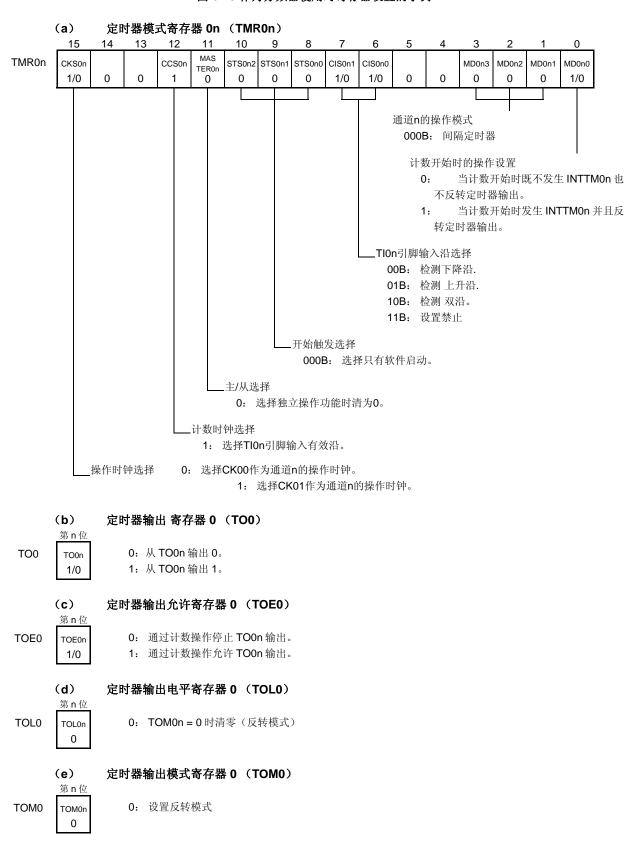

| 第六章 | 定时器阵列单元                     | 191 |

| 6.1 | 定时器阵列单元的功能                  | 101 |

| 0.1 | 6.1.1 独立操作时每通道的功能           |     |

|     | 6.1.2 和其他通道操作时每个通道的功能       |     |

|     | 6.1.3 LIN 总线支持功能(仅限通道 7)    |     |

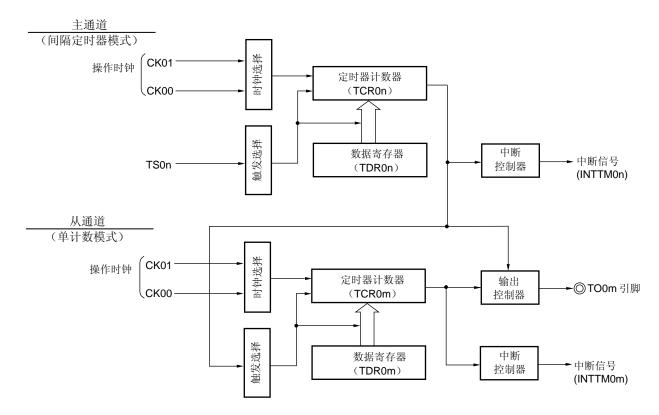

| 6.2 | 定时器阵列单元的配置                  |     |

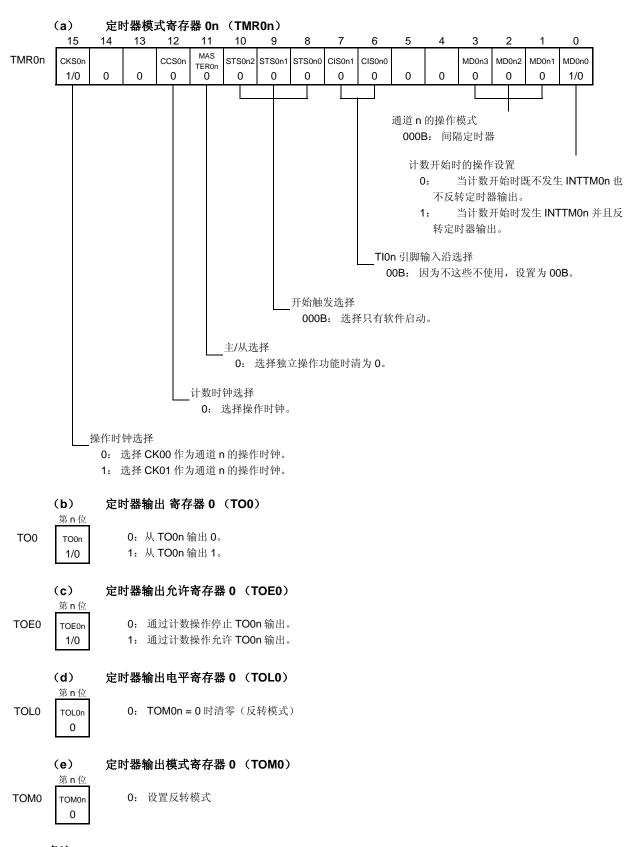

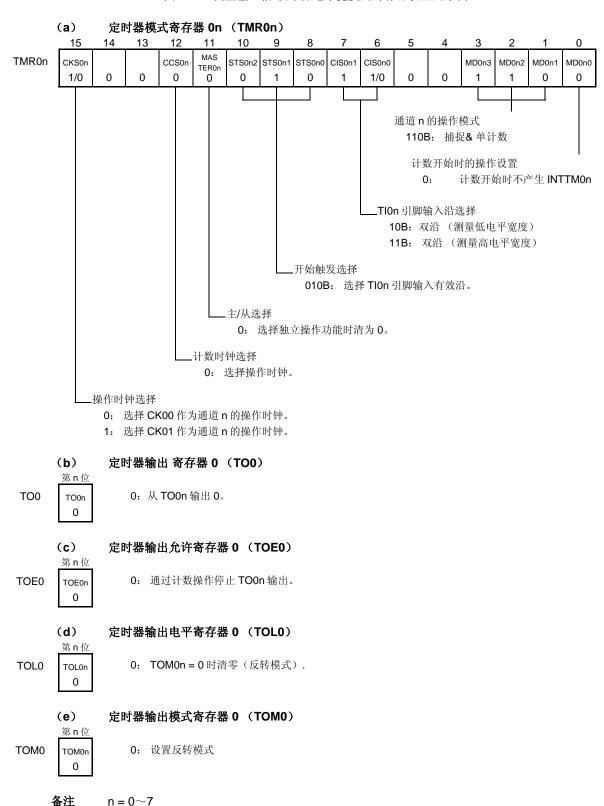

|     | 控制定时器阵列单元的寄存器               |     |

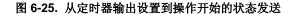

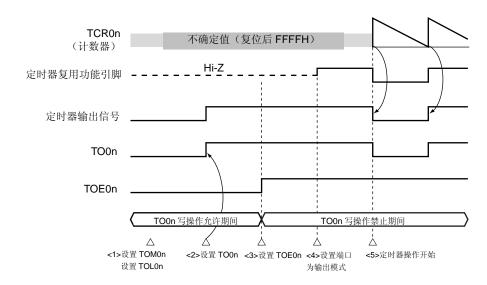

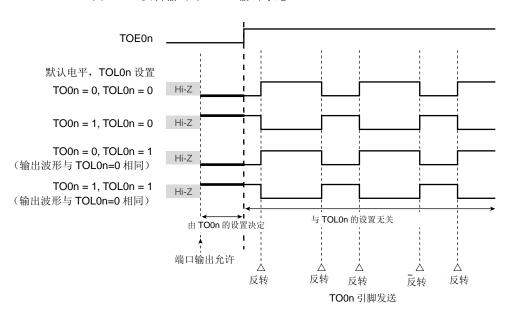

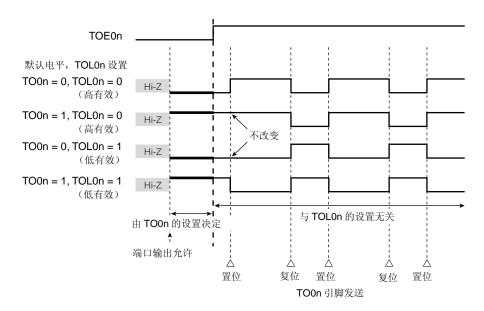

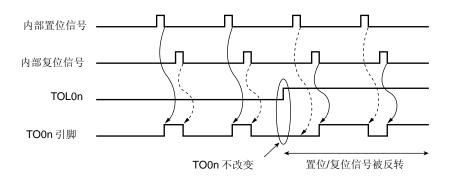

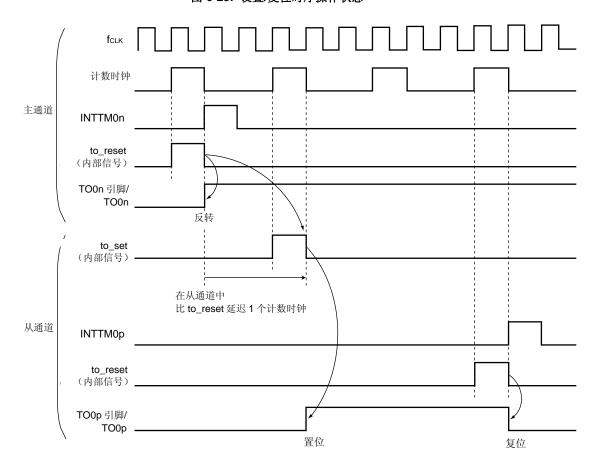

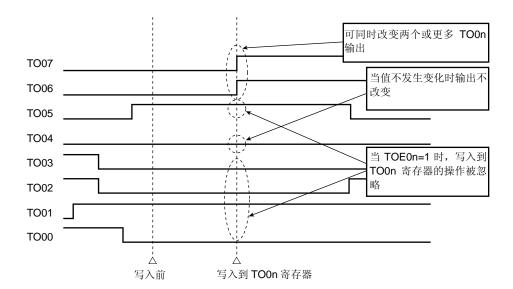

|     | 通道输出 (TO0n 引脚) 控制           |     |

| •   | 6.4.1 TOOn 引脚输出电路配置         |     |

|     | 6.4.2 TO0n 引脚输出设置           |     |

|     | 6.4.3 通道输出操作的注意事项           |     |

|     | 6.4.4 TO0n 位的集中操作           |     |

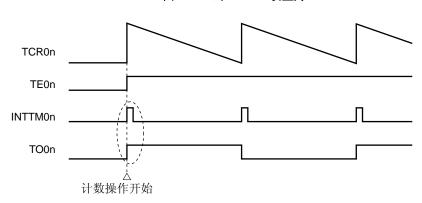

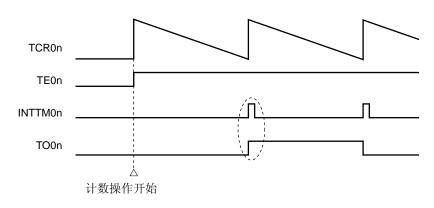

|     | 6.4.5 定时器中断和操作开始时 TO0n 引脚输出 |     |

| 6.5 | 通道输入(TI0n 引脚)控制             |     |

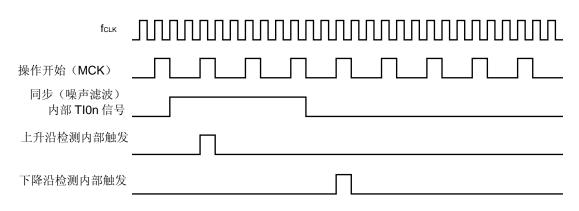

|     | 6.5.1 TlOn 沿检测电路            | 226 |

| 6.6 | 定时器阵列单元的基本功能                |     |

|     | 6.6.1 独立操作功能和组合操作功能的概述      | 227 |

|     | 6.6.2 组合操作功能的基本规则           |     |

|     | 6.6.3 组合操作功能的基本规则应用范围       | 228 |

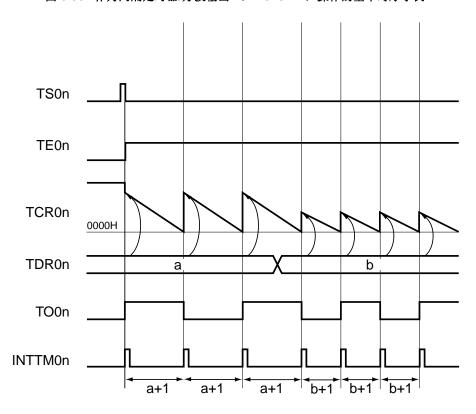

| 6.7 | 定时器阵列单元作为通道的操作              | 229 |

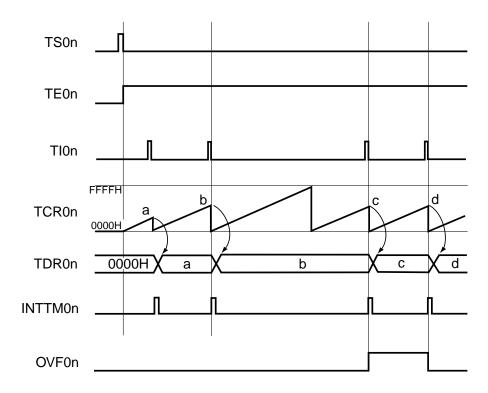

|     | 6.7.1 作为间隔定时器/方波输出操作        | 229 |

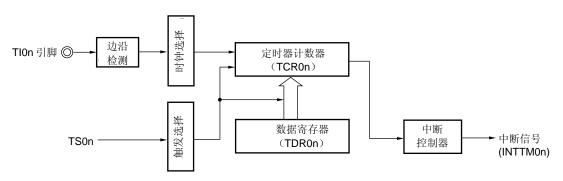

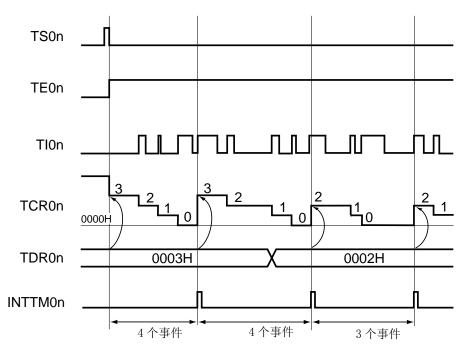

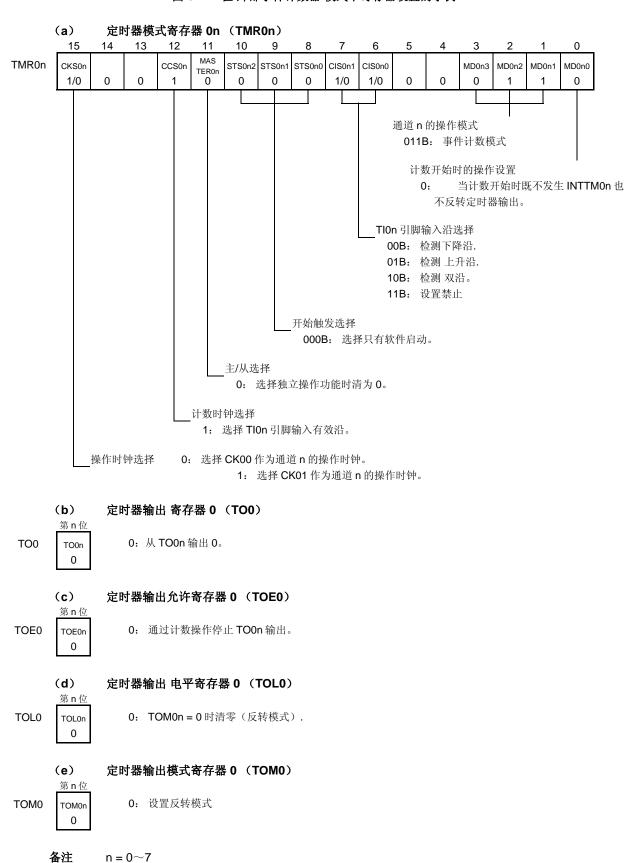

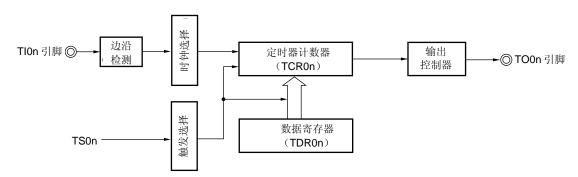

|     | 6.7.2 作为外部事件计数器操作           | 233 |

|     | 6.7.3 用作分频操作                | 236 |

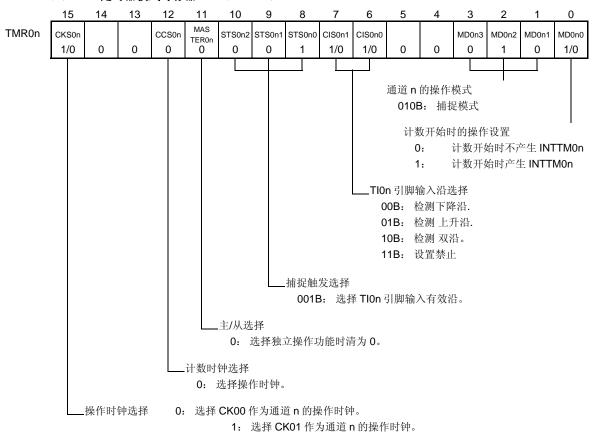

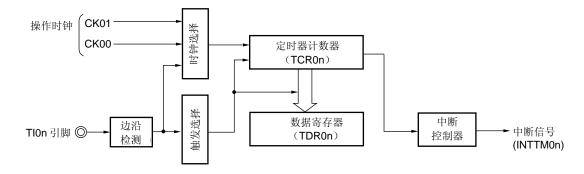

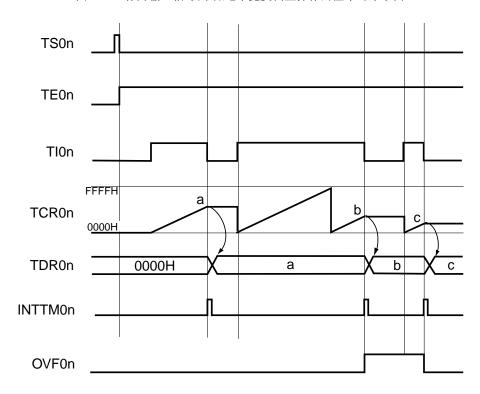

|     | 6.7.4 作为输入脉冲间隔测量操作          | 240 |

|     | 6.7.5 用作输入信号高/低电平宽度测量操作     | 244 |

| 6.8 | 定时器阵列单元的多通道操作               | 248 |

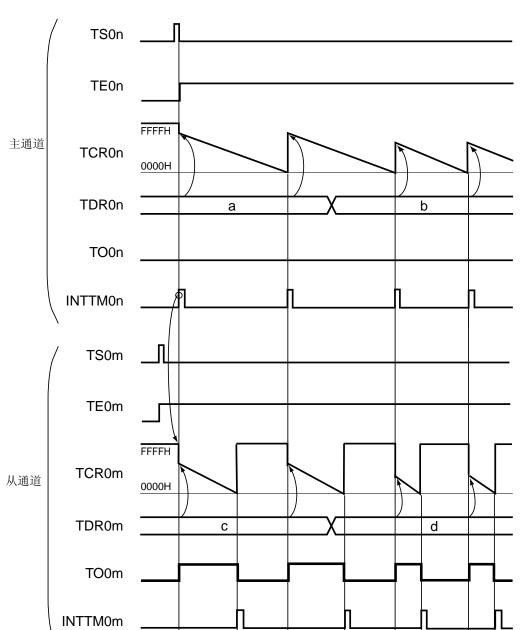

|     | 6.8.1 作为 PWM 功能操作           | 248 |

|     | 6.8.2 作为单脉冲输出功能操作           | 255 |

|     | 6.8.3 作为多路 PWM 输出功能操作       | 262 |

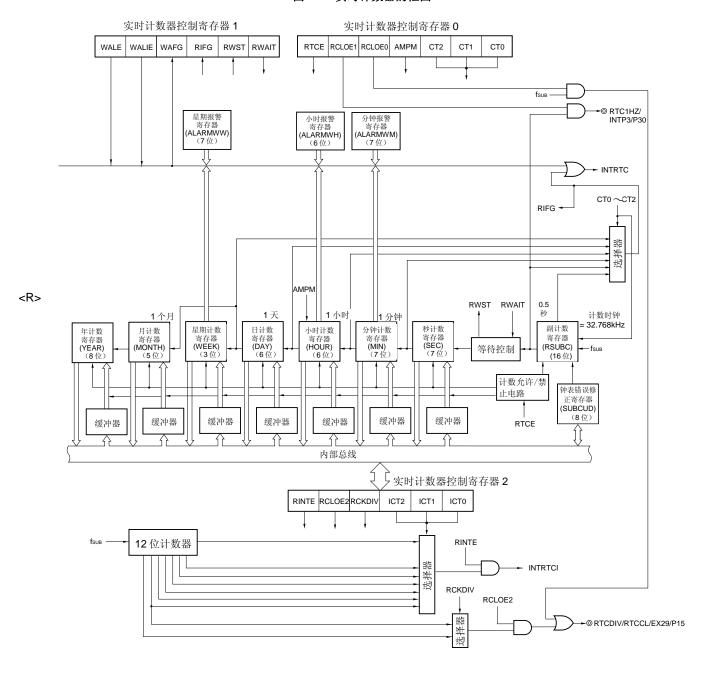

| 第七章 | 实时计数器                       | 269 |

| 7.1 | 实时计数器的功能                    | 269 |

| 7.2 | 实时计数器的配置                    | 269 |

|     |                             |     |

| 1.3                                                  | <b>3</b> 控制实时计数器的寄存器       | 271               |

|------------------------------------------------------|----------------------------|-------------------|

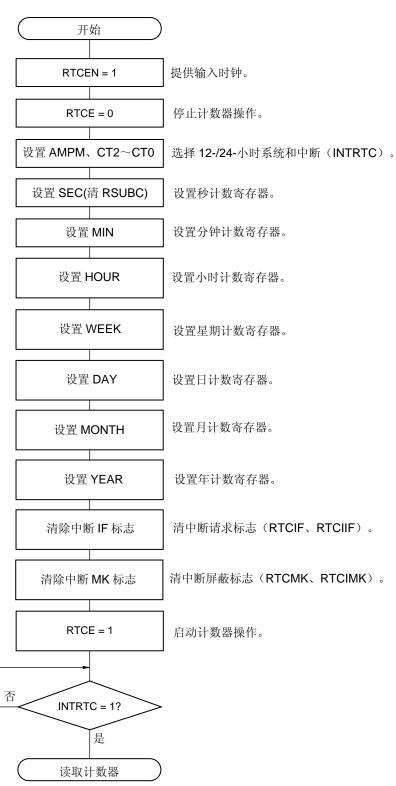

| 7.4                                                  | 1 实时计数器操作                  | 283               |

|                                                      | 7.4.1 启动实时计数器的操作           | 283               |

|                                                      | 7.4.2 读/写实时计数器             | 284               |

|                                                      | 7.4.3 设置实时计数器报警            | 286               |

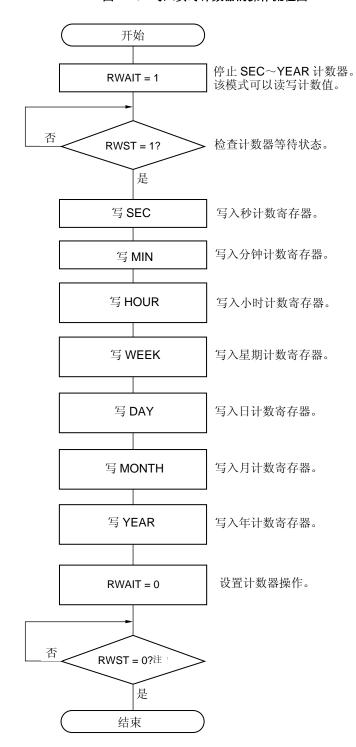

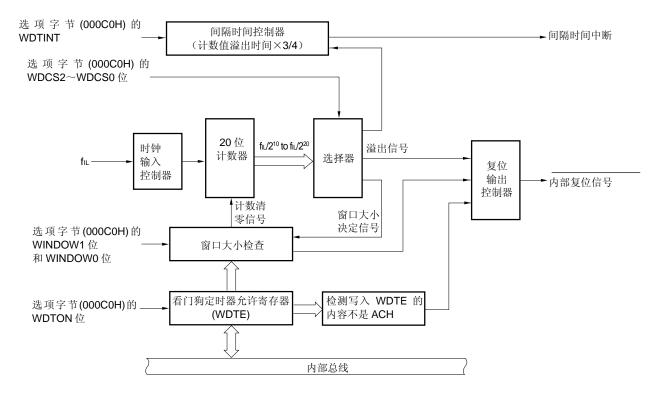

| 第八章                                                  | 〔 看门狗定时器                   | 287               |

| 8.1                                                  | Ⅰ 看门狗定时器的功能                | 287               |

| 8.2                                                  | 2 看门狗定时器的配置                | 288               |

| 8.3                                                  | 3 控制看门狗定时器的寄存器             | 289               |

| 8.4                                                  | <b>1</b> 看门狗定时器的操作         | 290               |

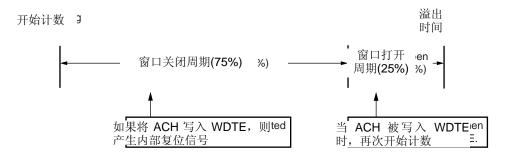

|                                                      | 8.4.1 看门狗定时器的控制操作          | 290               |

|                                                      | 8.4.2 看门狗定时器溢出时间的设置        | 291               |

|                                                      | 8.4.3 看门狗定时器窗口打开比例的设置      | 292               |

|                                                      | 8.4.4 设置看门狗定时器间隔中断         | 293               |

| 第九章                                                  | f 时钟输出/ 蜂鸣器输出控制器           | 294               |

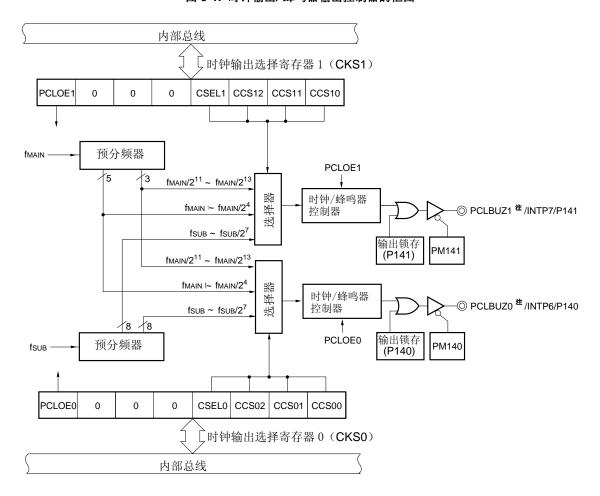

| 9.1                                                  | 时钟输出/ 蜂鸣器输出控制器的功能          | 294               |

| 9.2                                                  | 2 时钟输出/ 蜂鸣器输出控制器 的配置       | 295               |

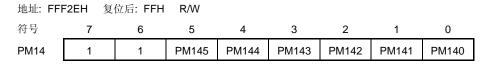

| 9.3                                                  | 3 控制时钟输出/ 蜂鸣器输出控制器的寄存器     | 295               |

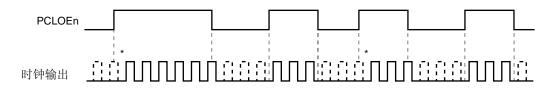

| 9.4                                                  | <b>1</b> 时钟输出/ 蜂鸣器输出控制器的操作 | 297               |

|                                                      | 9.4.1 作为输出引脚操作             | 297               |

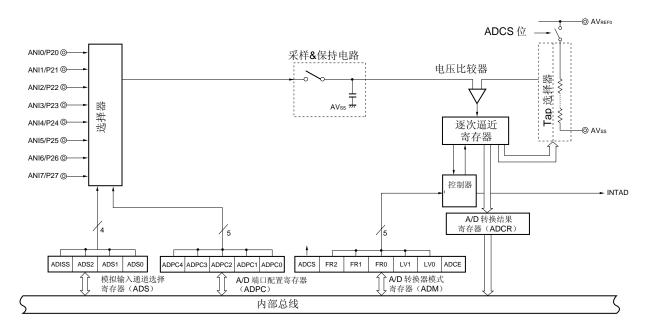

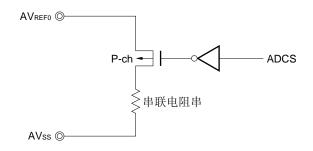

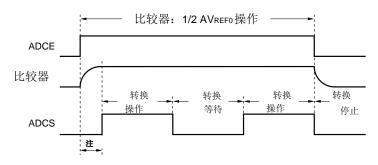

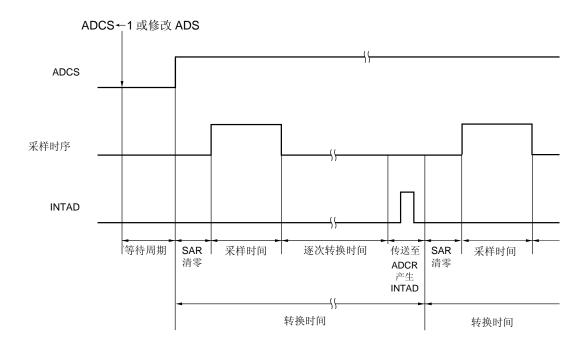

| 第十章                                                  | 〔 A/D 转换器                  | 298               |

|                                                      |                            |                   |

|                                                      | .1 A/D 转换器的功能              |                   |

| 10.                                                  | .2 A/D 转换器的配置              | 299               |

| 10.<br>10.                                           | .2 A/D 转换器的配置              | 299<br>301        |

| 10.<br>10.                                           | .2 A/D 转换器的配置              | 299<br>301<br>309 |

| 10.<br>10.                                           | .2 A/D 转换器的配置              |                   |

| 10.<br>10.                                           | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.                                    | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.                                    | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.<br>10.                             | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.<br>10.<br>第十一                      | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.<br>10.<br>第十一<br>11.               | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.<br>10.<br>第十一<br>11.<br>11.        | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.<br>10.<br>第十一<br>11.<br>11.<br>11. | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.<br>11.<br>11.<br>11.<br>第十二        | .2 A/D 转换器的配置              |                   |

| 10.<br>10.<br>10.<br>11.<br>11.<br>11.<br>第十二        | .2 A/D 转换器的配置              |                   |

|      | 12.1.3 简易 I2C (IIC10,IIC20)             | 326 |

|------|-----------------------------------------|-----|

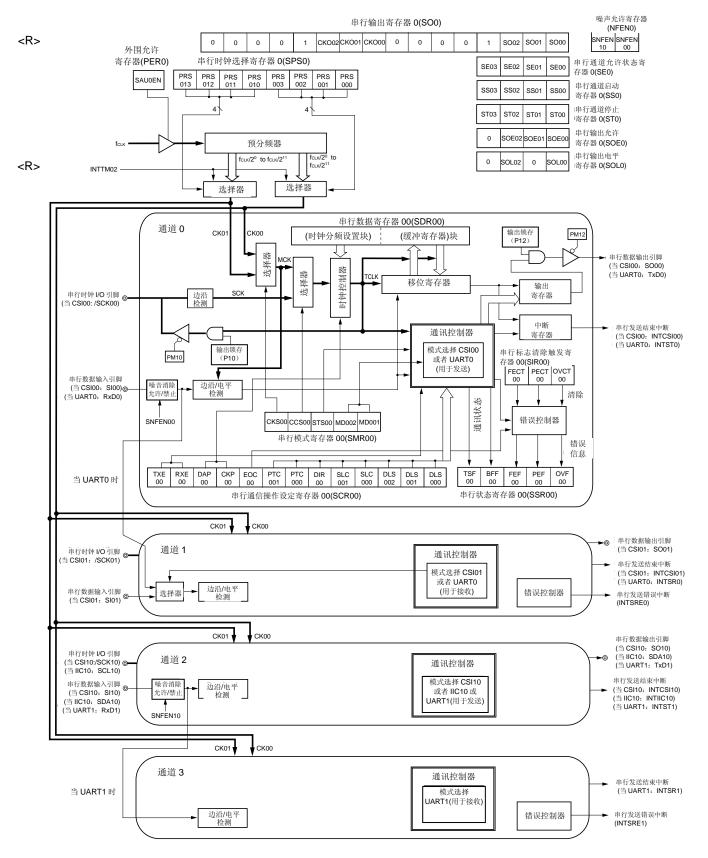

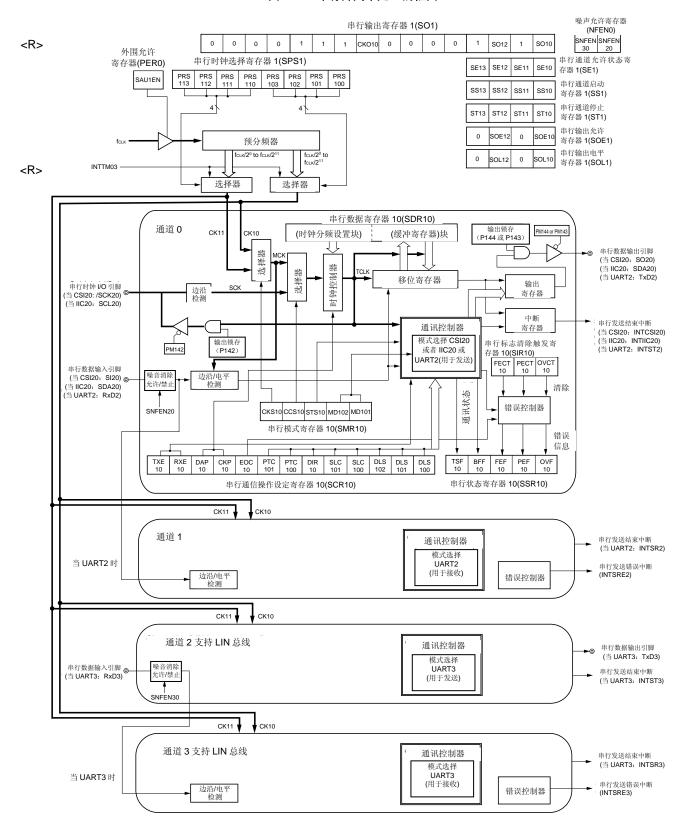

| 12.2 | 串行阵列单元的配置                               | 327 |

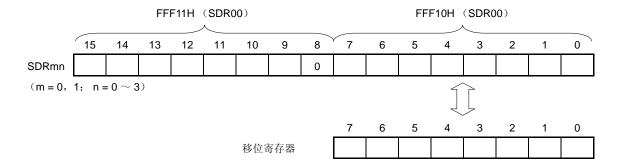

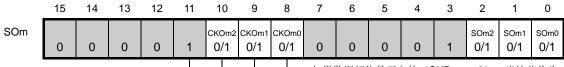

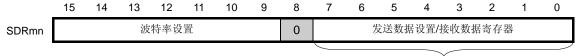

| 12.3 | 控制串行阵列单元的寄存器                            | 332 |

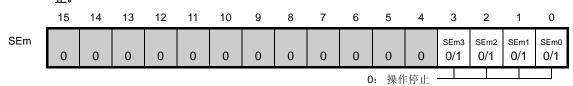

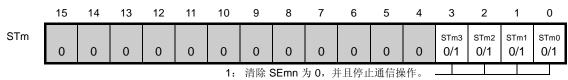

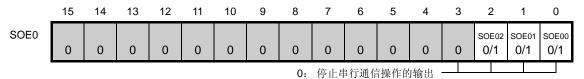

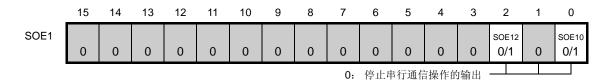

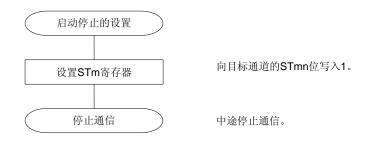

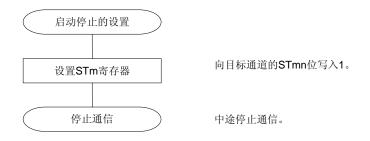

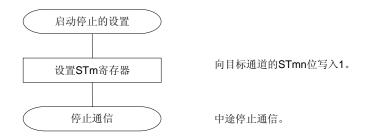

| 12.4 | 操作停止模式                                  | 354 |

|      | 12.4.1 按照单元停止操作                         | 354 |

|      | 12.4.2 按照通道停止操作                         | 355 |

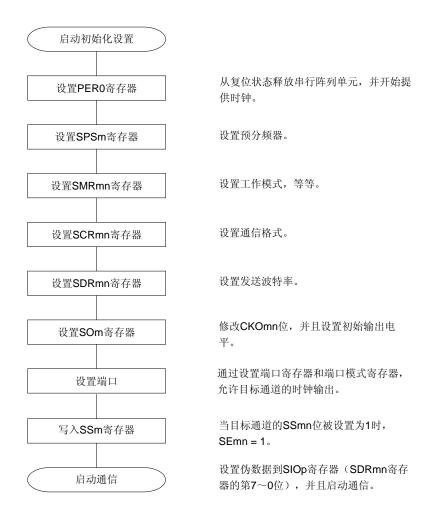

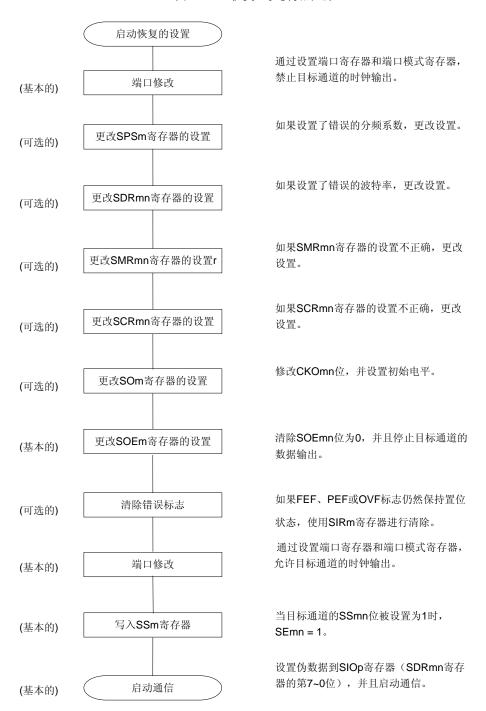

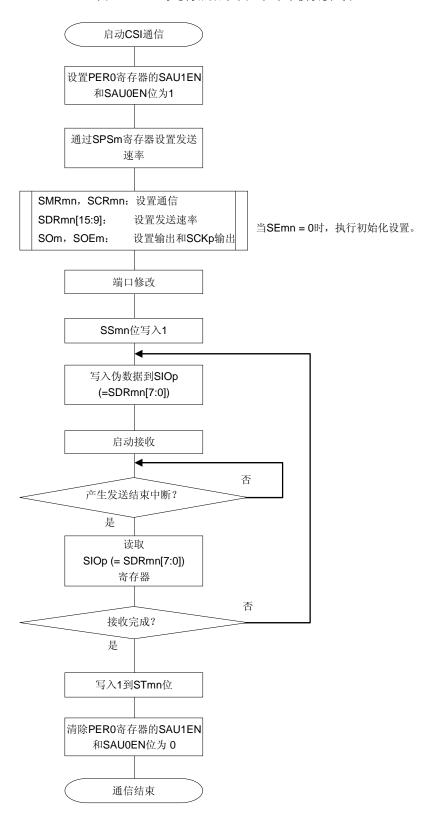

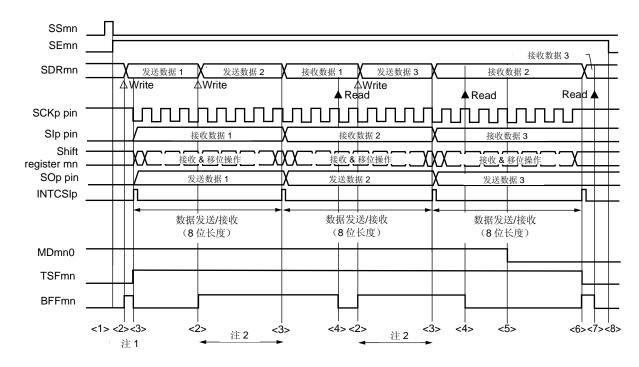

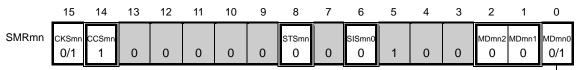

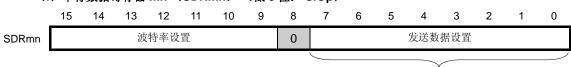

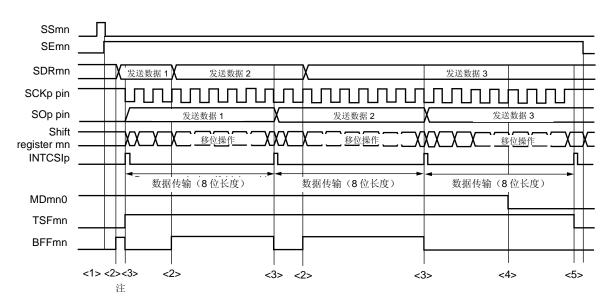

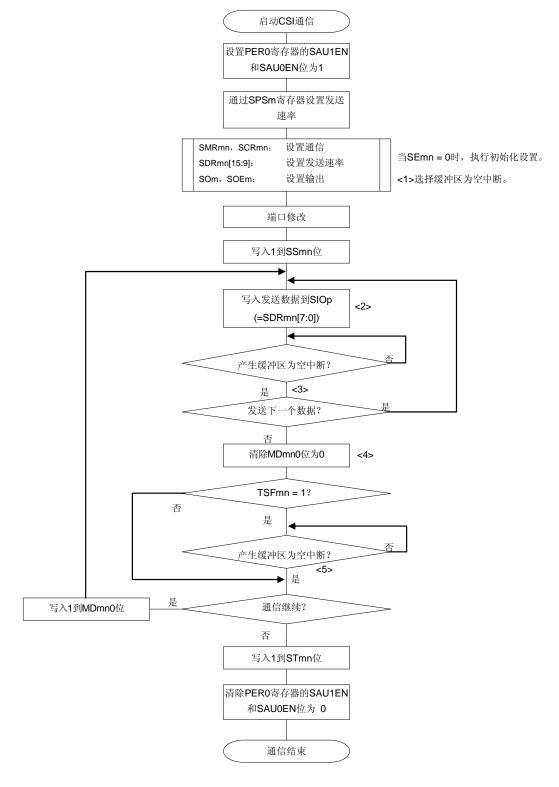

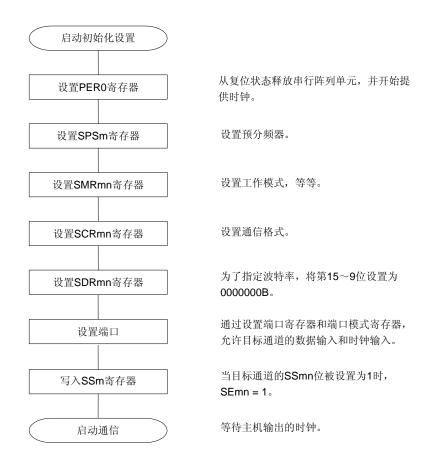

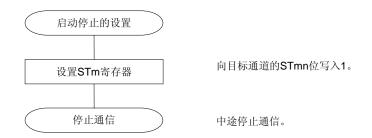

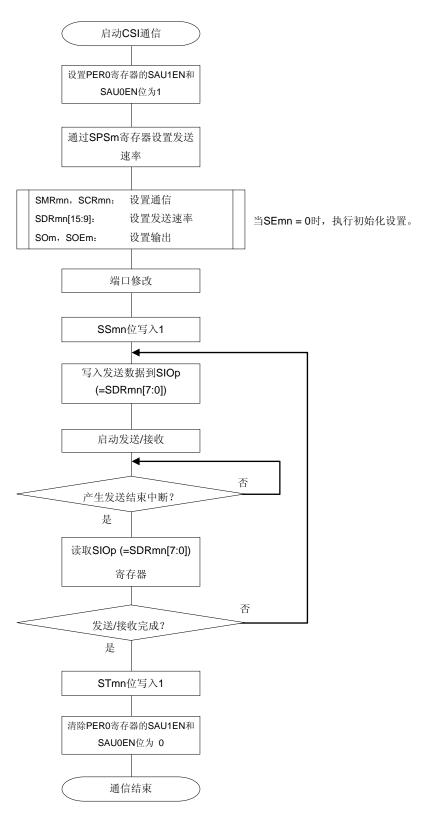

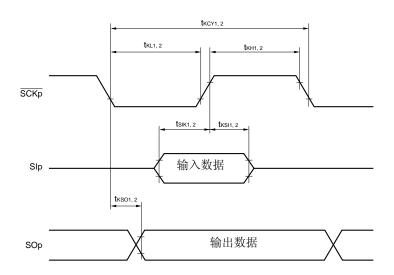

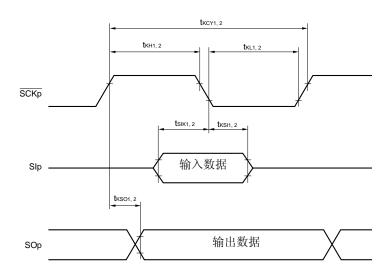

| 12.5 | 3 线串行 I/O(CSI00,CSI01,CSI10,CSI20)通信的操作 | 357 |

|      | 12.5.1 主机发送                             | 358 |

|      | 12.5.2 主机接收                             | 367 |

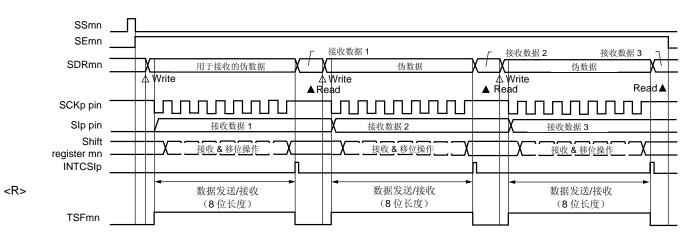

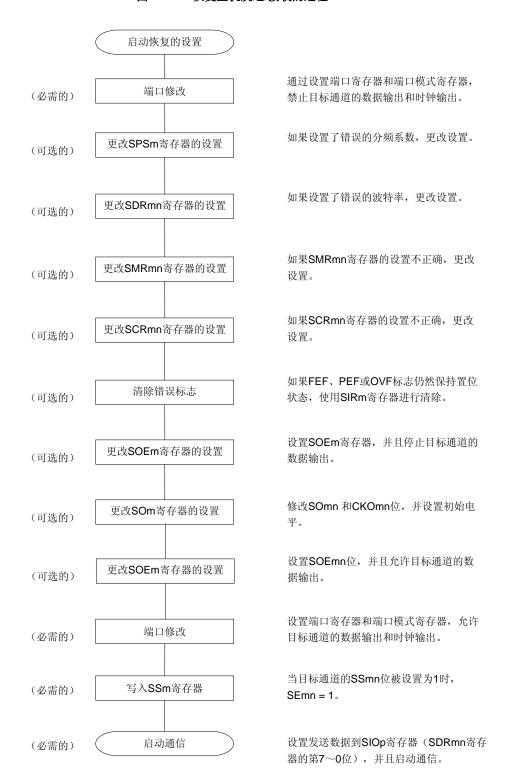

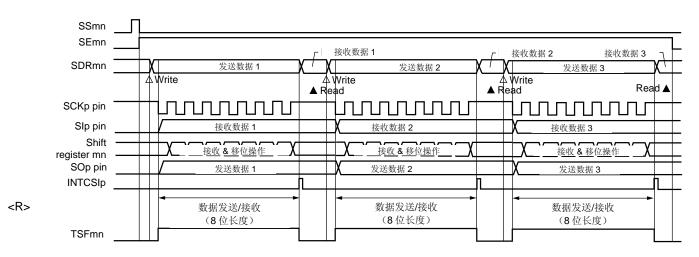

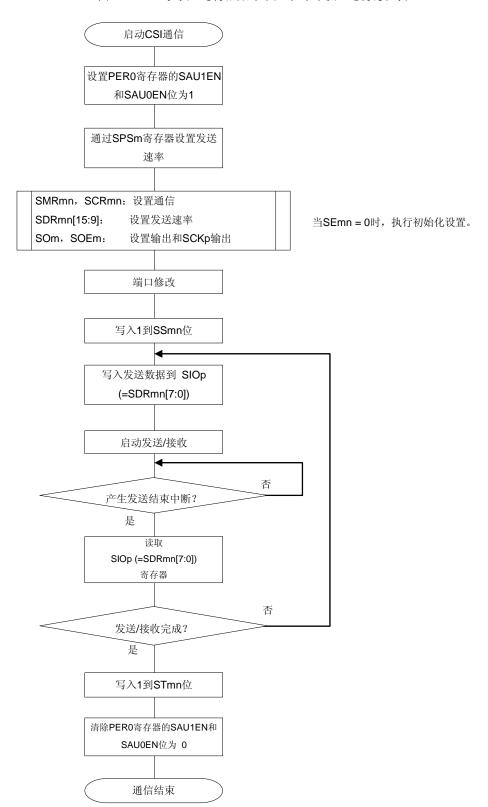

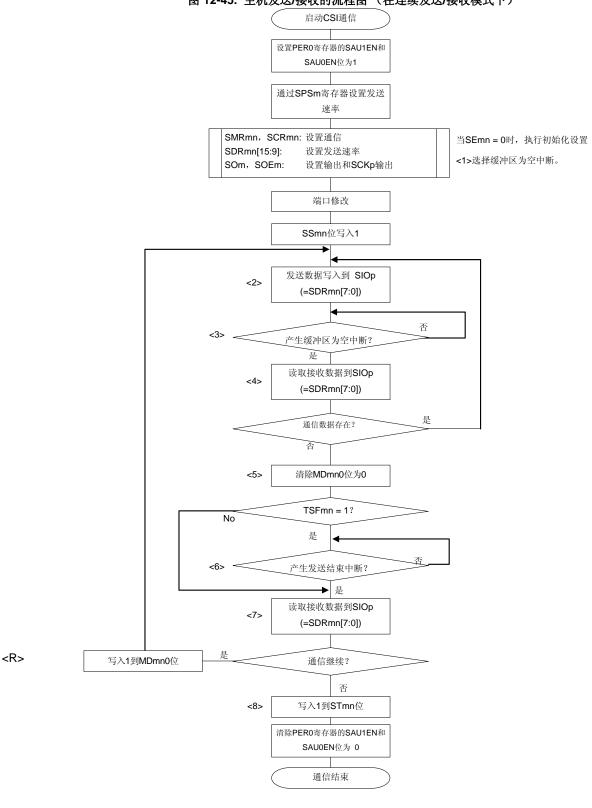

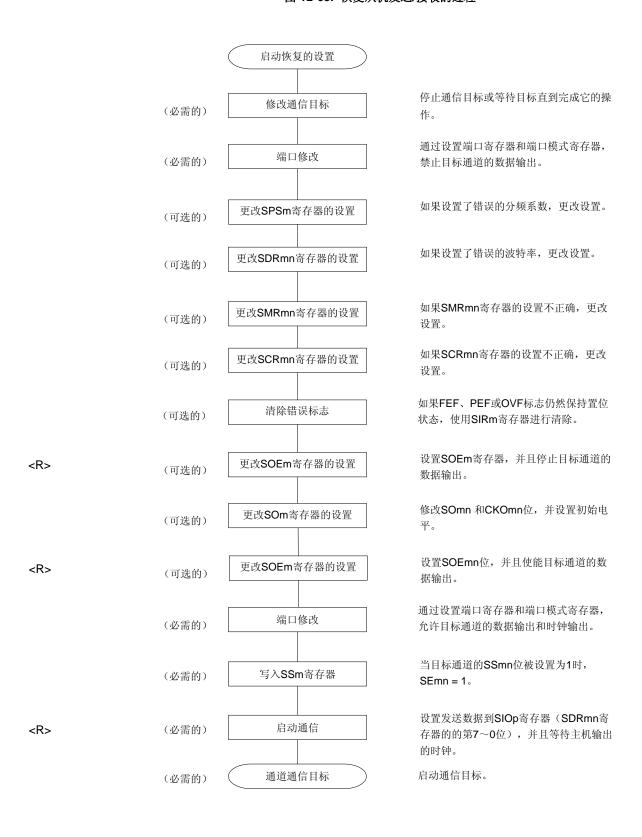

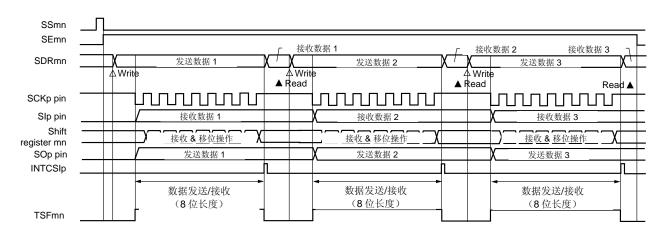

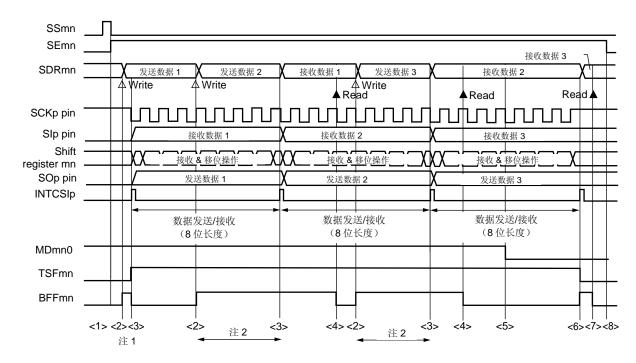

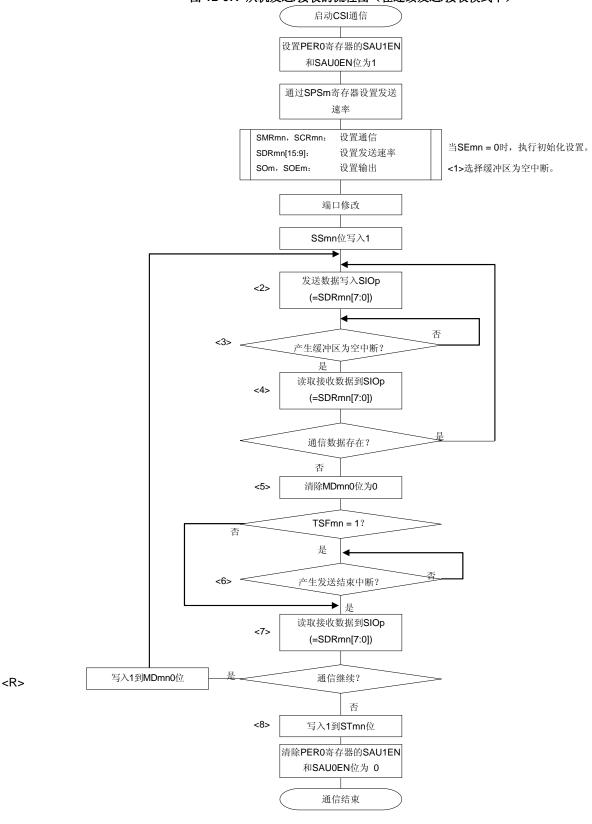

|      | 12.5.3 主机发送/接收                          | 373 |

|      | 12.5.4 从机发送                             | 381 |

|      | 12.5.5 从机接收                             | 390 |

|      | 12.5.6 从机发送/接收                          | 396 |

|      | 12.5.7 计算发送时钟的频率                        | 405 |

| 12.6 | UART (UART0, UART1, UART2, UART3) 通信的操作 | 407 |

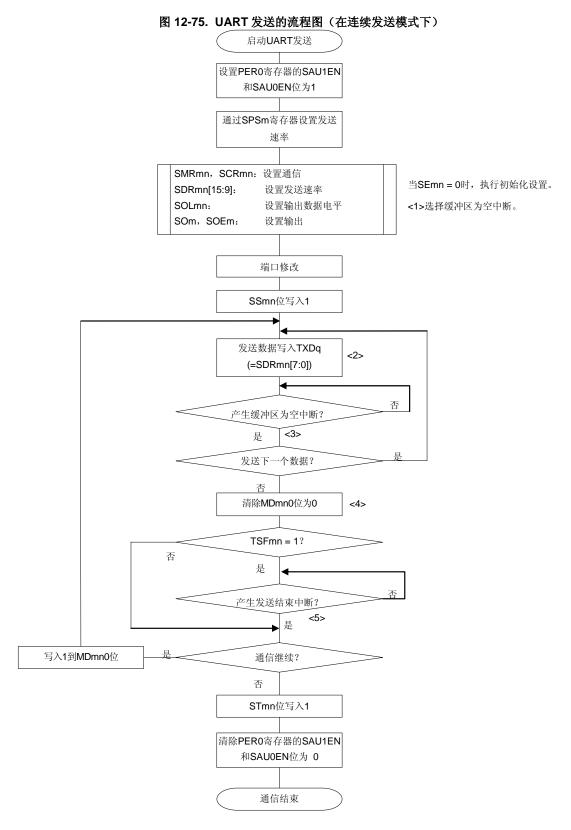

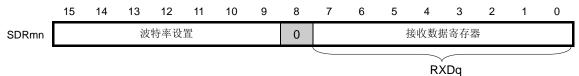

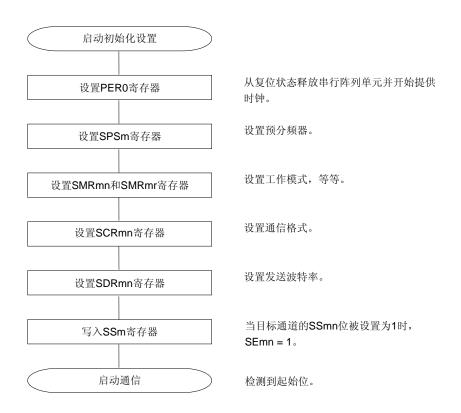

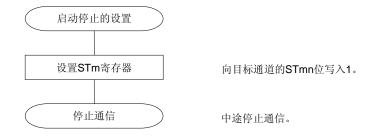

|      | 12.6.1 UART 发送                          | 408 |

|      | 12.6.2 UART接收                           | 418 |

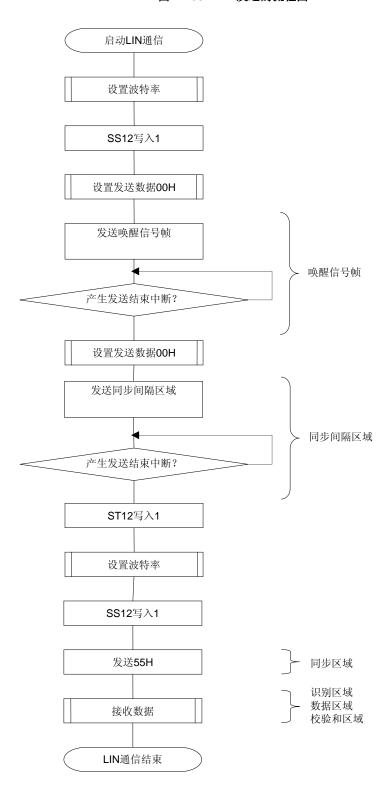

|      | 12.6.3 LIN 发送                           | 425 |

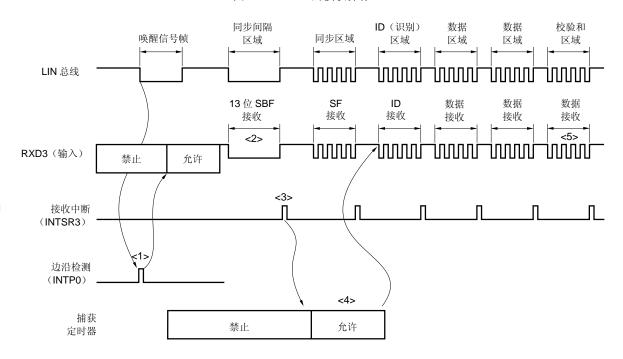

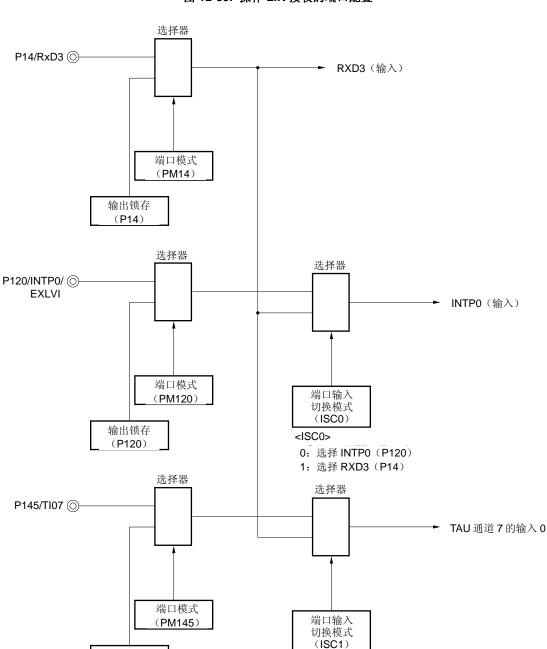

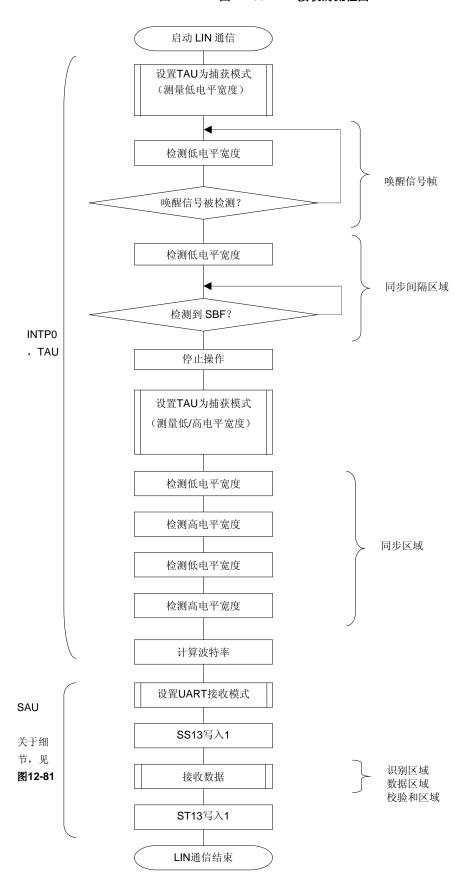

|      | 12.6.4 LIN 接收                           | 428 |

|      | 12.6.5 计算波特率                            | 433 |

| 12.7 | 简易 I2C (IIC10,IIC20)通信操作                | 437 |

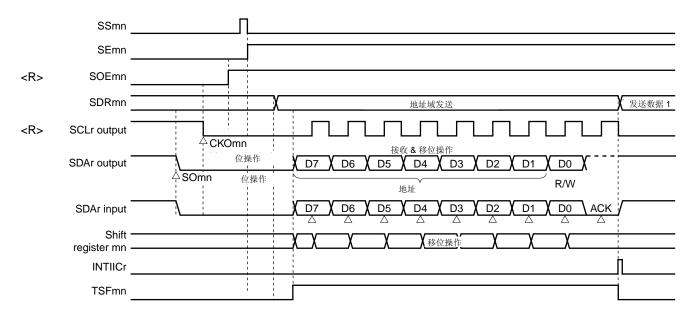

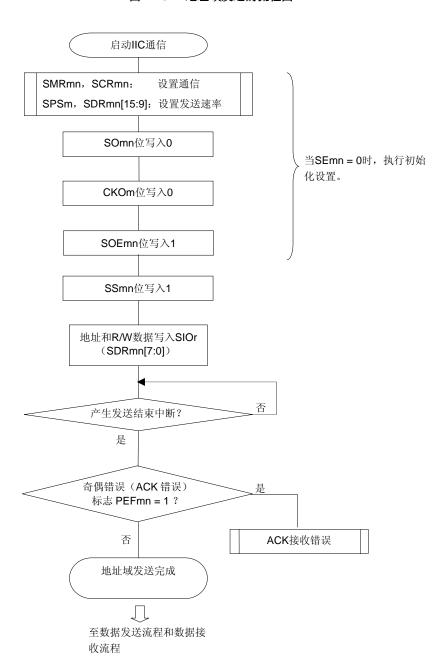

|      | 12.7.1 地址区域发送                           | 438 |

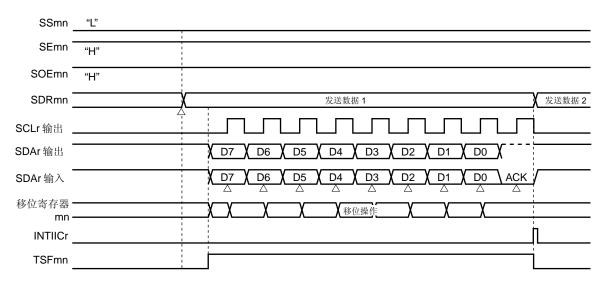

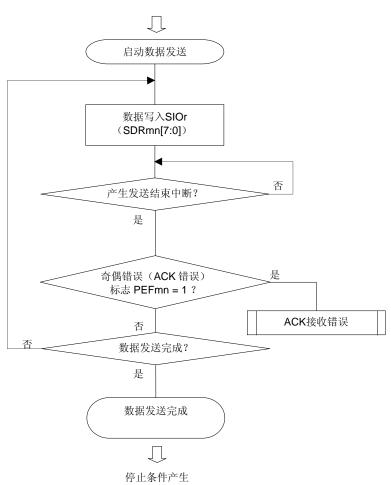

|      | 12.7.2 数据发送                             | 443 |

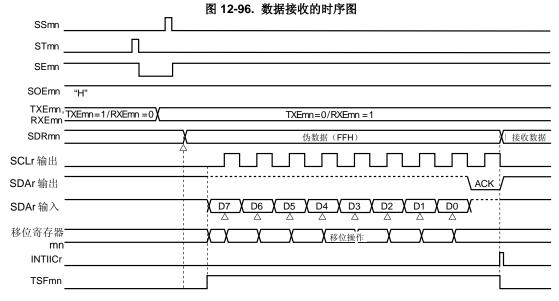

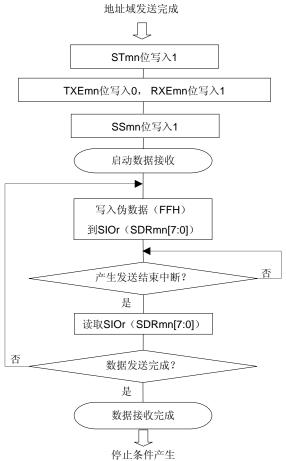

|      | 12.7.3 数据接收                             | 446 |

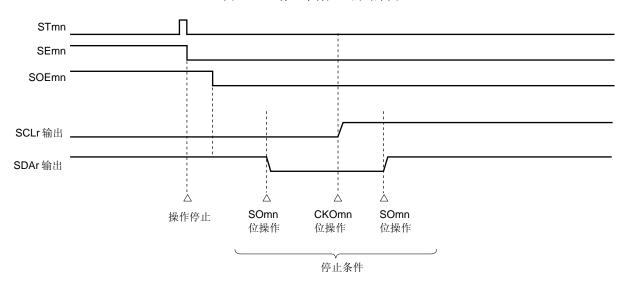

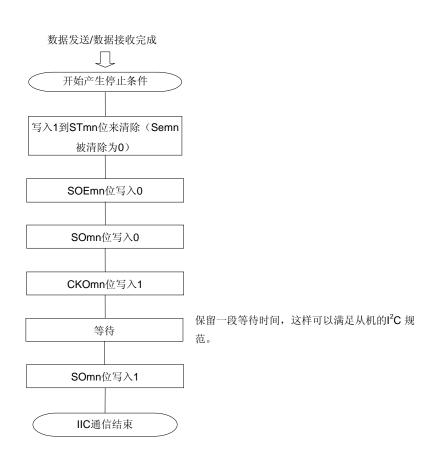

|      | 12.7.4 产生停止条件                           | 449 |

|      | 12.7.5 计算发送速率                           | 450 |

| 12.8 | 在错误情况下的处理过程                             | 453 |

| 12.9 | 寄存器设置和引脚之间的关系                           | 455 |

|      |                                         |     |

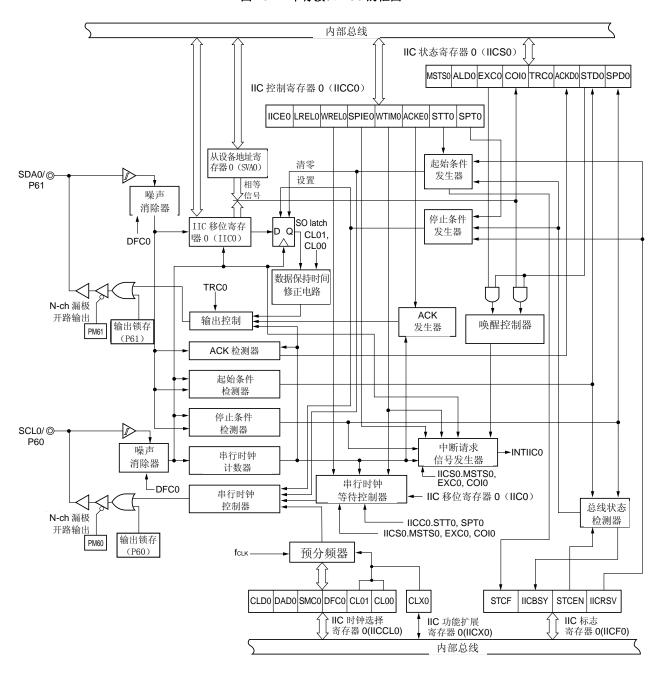

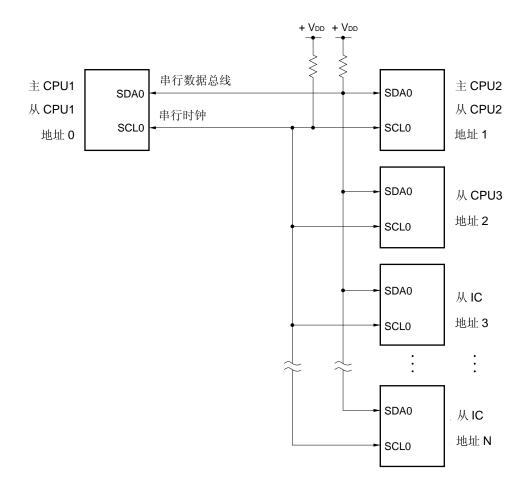

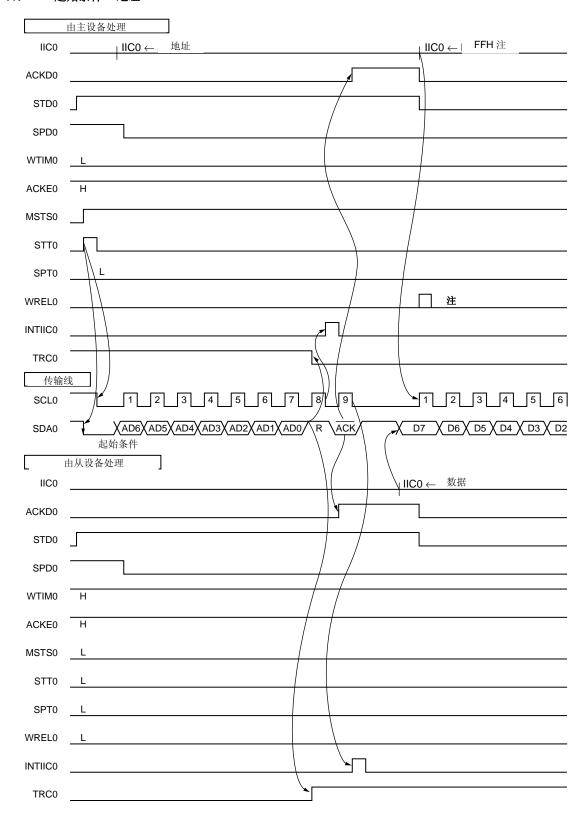

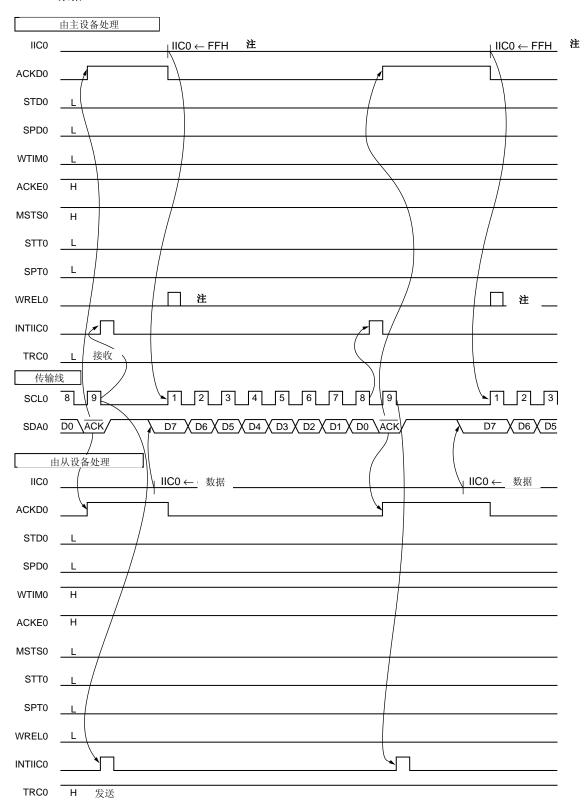

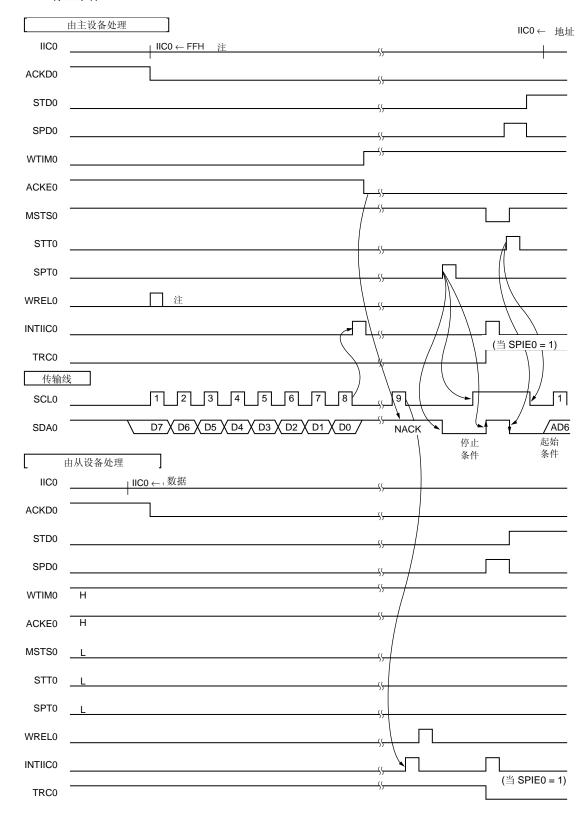

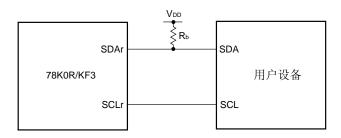

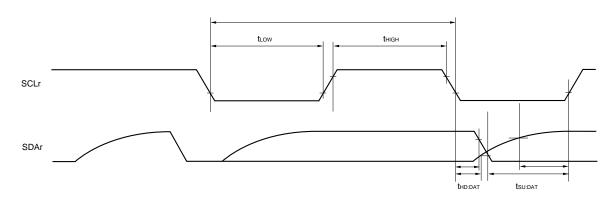

| 第十三章 | 章 串行接口 <b>ⅡC0</b>                       | 462 |

| 13 1 | 串行接口 <b>IIC0</b> 的功能                    | 462 |

|      | 申行接口 IIC0 的配置                           |     |

|      | 中行按口 IICO 的配置                           |     |

|      | 12C 总线模式功能                              |     |

| 13.4 | 13.4.1 引脚配置                             |     |

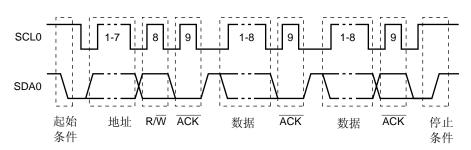

| 13.5 | 12C 总线定义和控制方法                           |     |

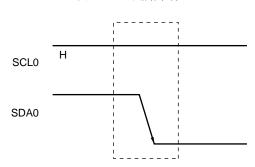

| 13.3 | 13.5.1 起始条件                             |     |

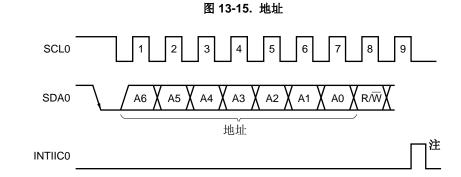

|      | 13.5.2 地址                               |     |

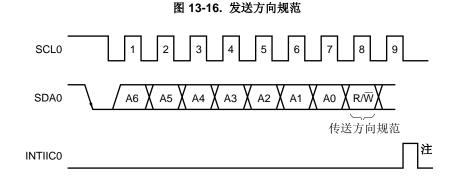

|      | 13.5.3 发送方向规范                           |     |

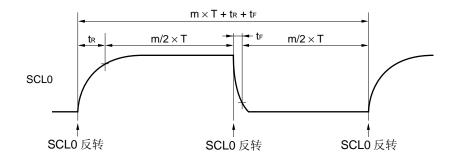

|      | 13.5.4 发送时钟设置方法                         |     |

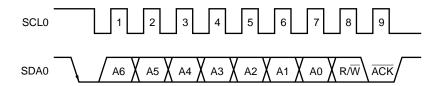

|      | 13.5.5 应答信号(ACK)                        |     |

|      | 13.5.6 停止条件                             |     |

|      | 13.5.7 等待                               |     |

|      | 13.5.8 取消等待                             |     |

|      | 13.5.9 中断请求 (INTIIC0) 产生时序和等待控制         |     |

|      | 13.5.9 中断请求 (INTIICU) 产生的序和等待拴制         |     |

|      | 13.5.11 错误检测                            |     |

|      | 13.5.11 错误位侧                            |     |

|      | 13.5.12 分 展時                            |     |

|      | 10.0.10   下                             | 492 |

|      | 13.5.14 唤醒功能                    | 493 |

|------|---------------------------------|-----|

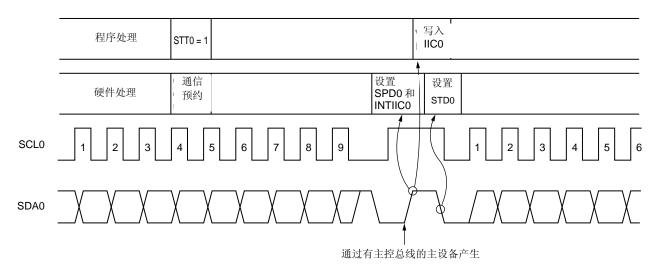

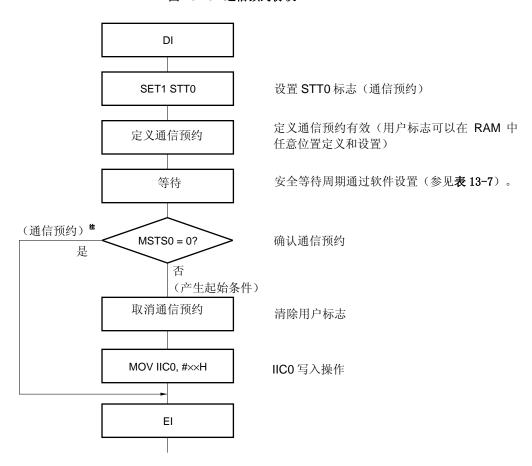

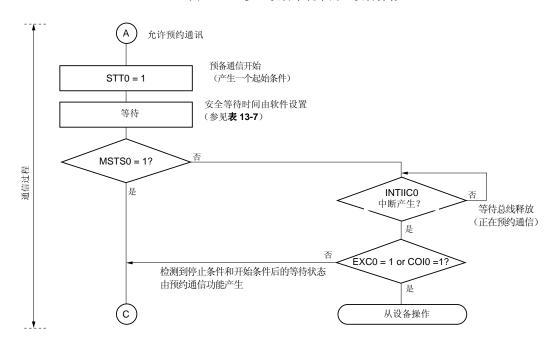

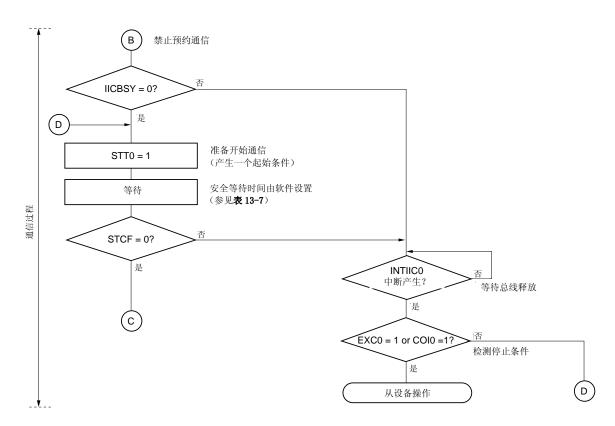

|      | 13.5.15 通信预约                    | 494 |

|      | 13.5.16 注意事项                    | 498 |

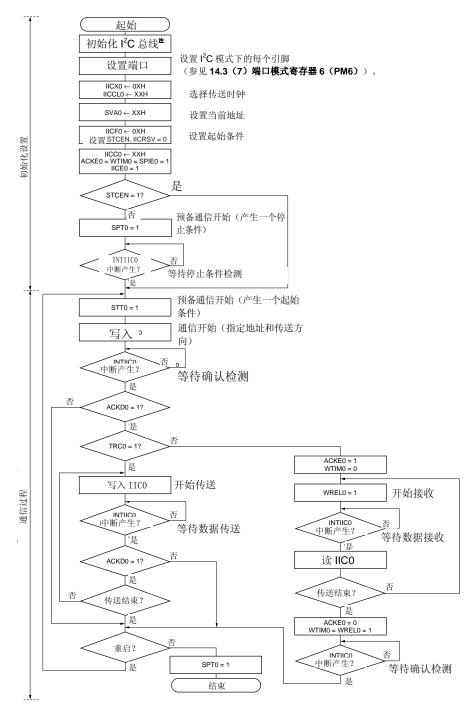

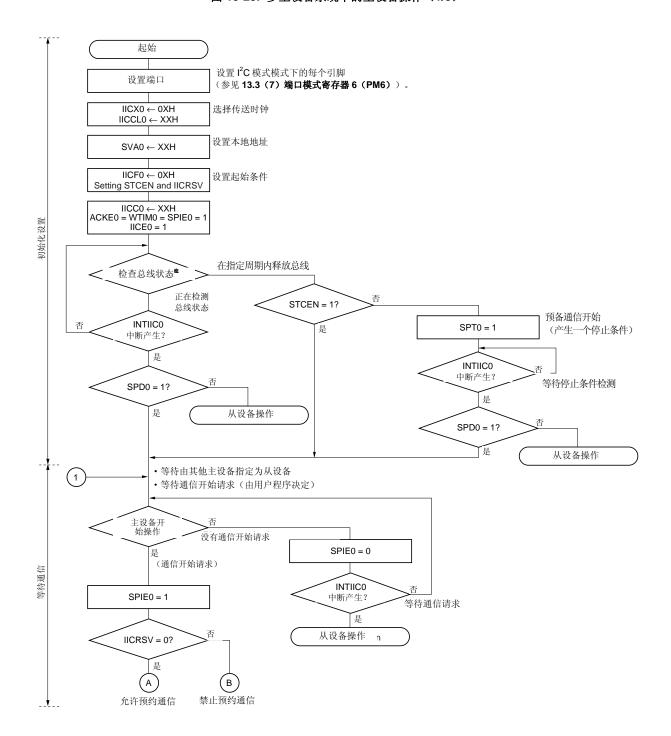

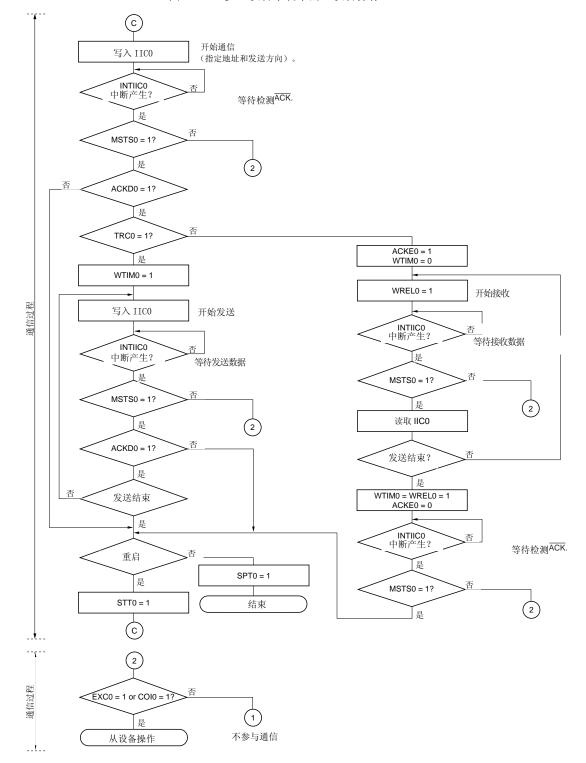

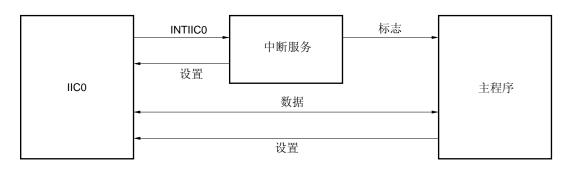

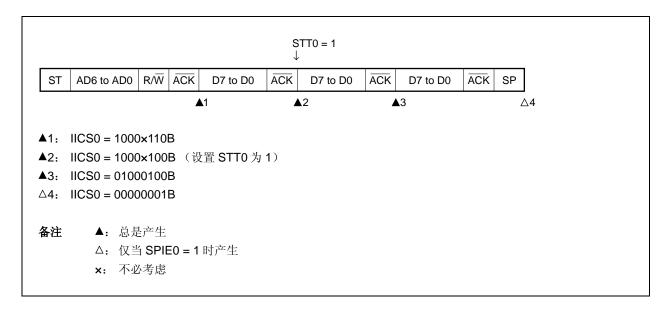

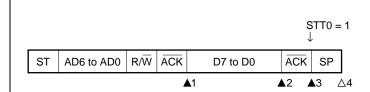

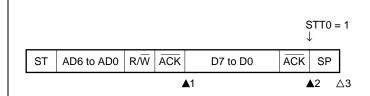

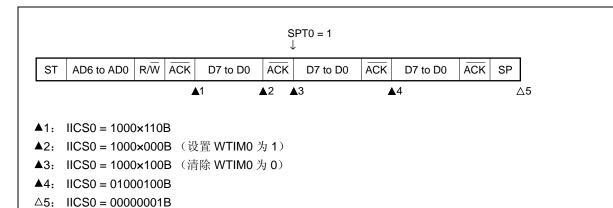

|      | 13.5.17 通信操作                    | 499 |

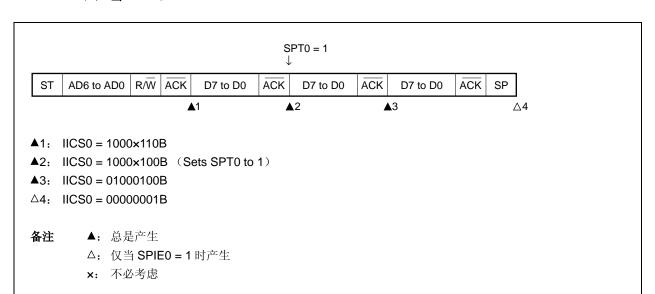

|      | 13.5.18 产生 I2C 中断请求(INTIICO)的时序 | 507 |

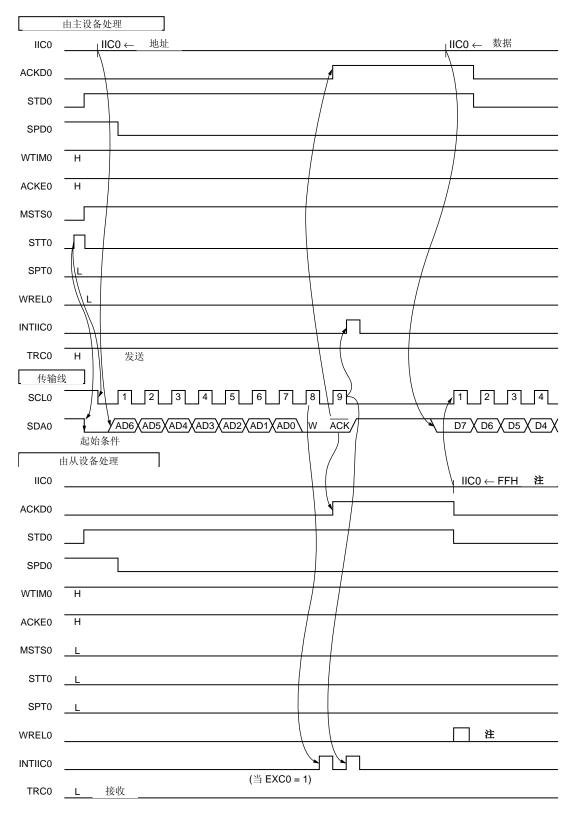

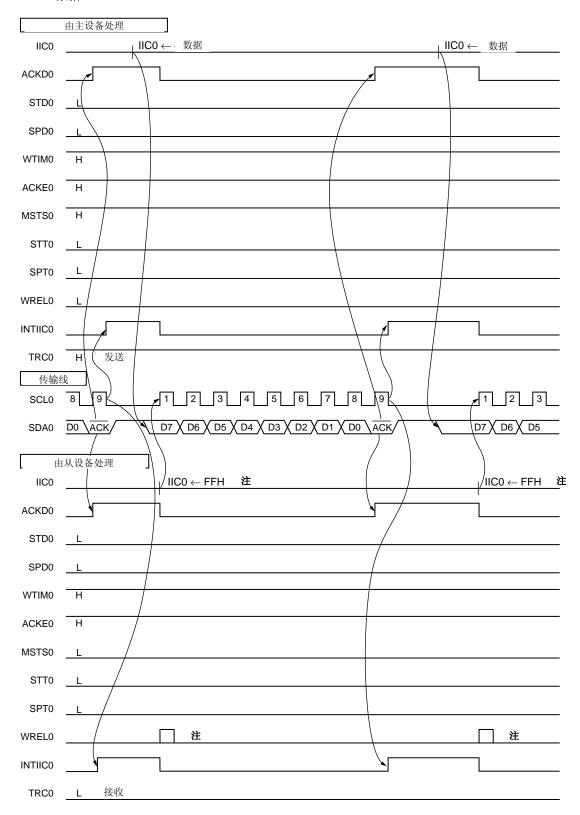

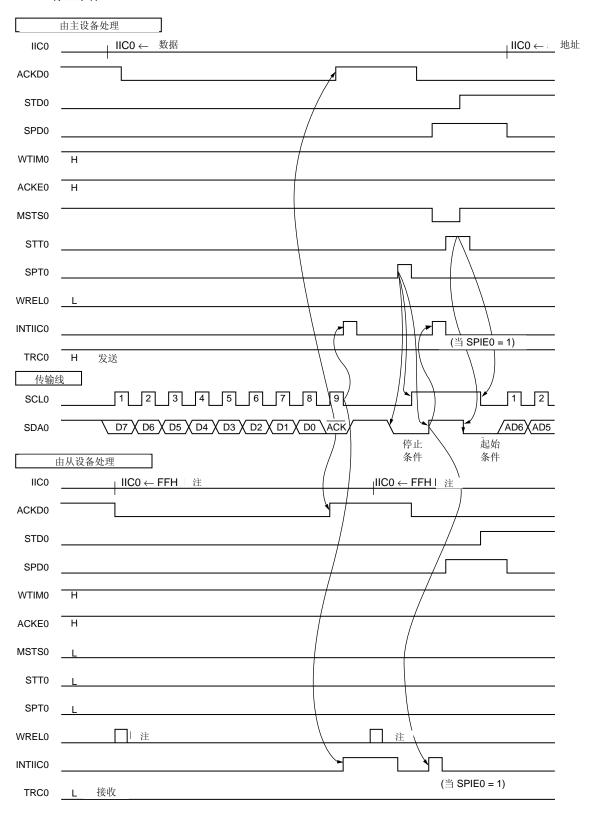

| 13.6 | 时序图                             | 528 |

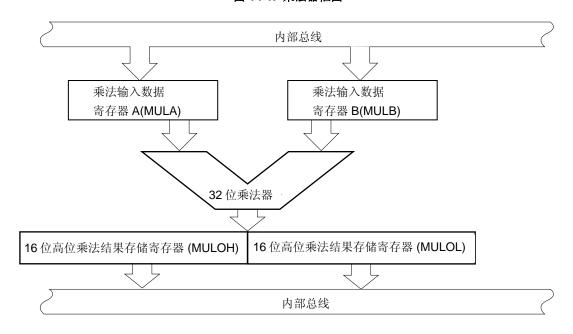

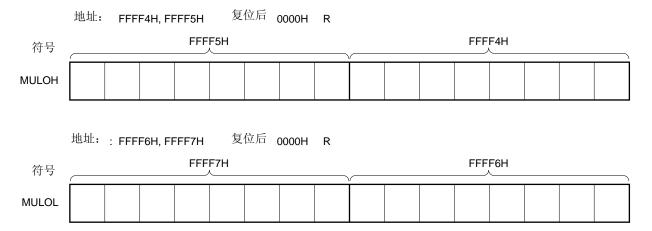

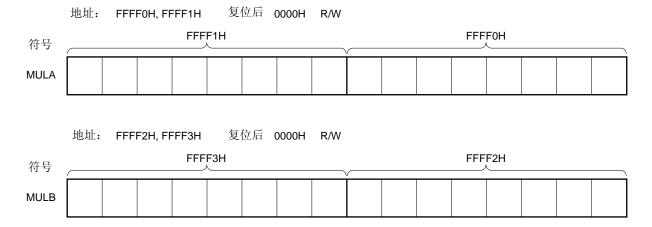

| 第十四章 | 章乘法器                            | 535 |

| 14.1 | 乘法器的功能                          | 535 |

| 14.2 | 乘法器的配置                          | 536 |

| 14.3 | 乘法器的操作                          | 537 |

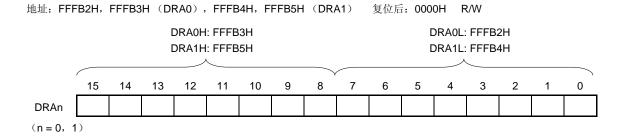

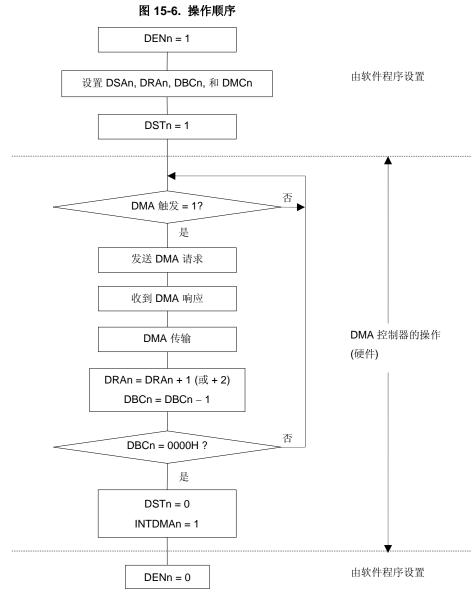

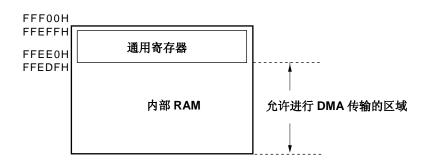

| 第十五章 | <b>DMA 控制器</b>                  | 538 |

| 15.1 | DMA 控制器                         | 538 |

| 15.2 | DMA 控制器的配置                      | 539 |

| 15.3 | 控制 DMA 控制器的寄存器                  | 542 |

| 15.4 | DMA 控制器的操作                      | 545 |

|      | 15.4.1 操作顺序                     | 545 |

|      | 15.4.2 传输模式                     | 546 |

|      | 15.4.3 DMA 传输中止                 | 546 |

| 15.5 | DMA 控制器设置的示例                    | 547 |

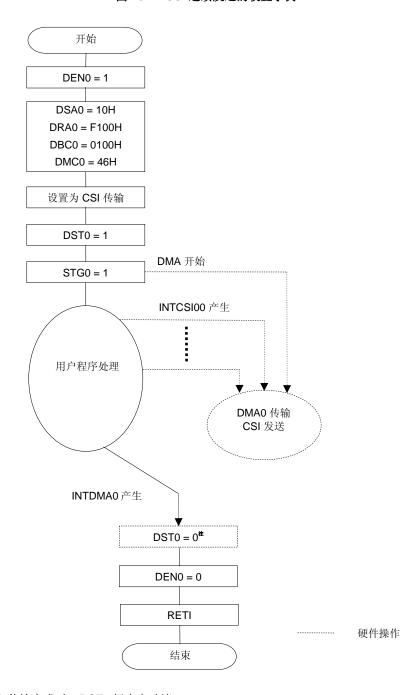

|      | 15.5.1 CSI 连续发送                 | 547 |

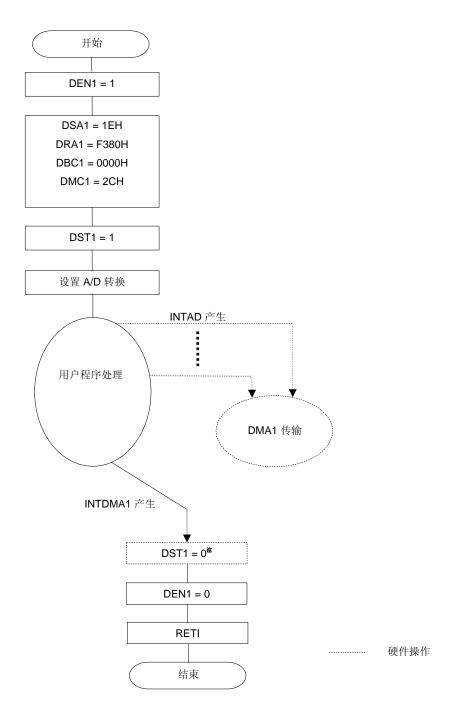

|      | 15.5.2 A/D 转换结果的连续捕获            | 549 |

|      | 15.5.3 UART 连续接收 + ACK 发送       | 551 |

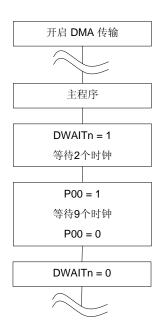

|      | 15.5.4 通过 DWAITn 保持 DMA 传输挂起    | 553 |

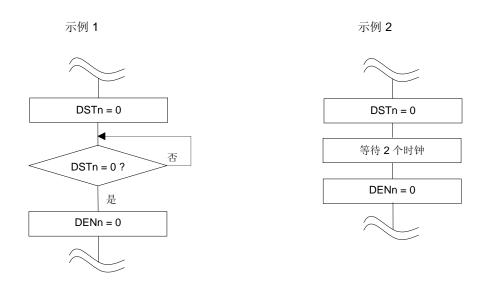

|      | 15.5.5 软件强行中止                   | 554 |

| 15.6 | 使用 DMA 控制器的注意事项                 | 555 |

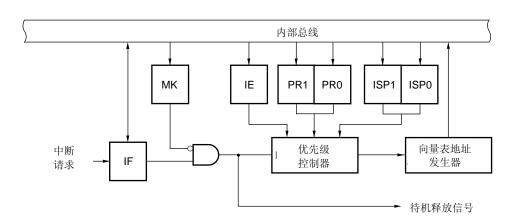

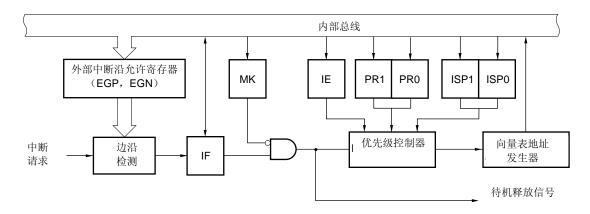

| 第十六章 | 章 中断功能                          | 557 |

| 16.1 | 中断功能的类型                         | 557 |

| 16.2 | 中断源及配置                          | 558 |

| 16.3 | 控制中断功能的寄存器                      | 561 |

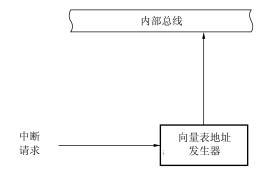

| 16.4 | 中断服务操作                          | 571 |

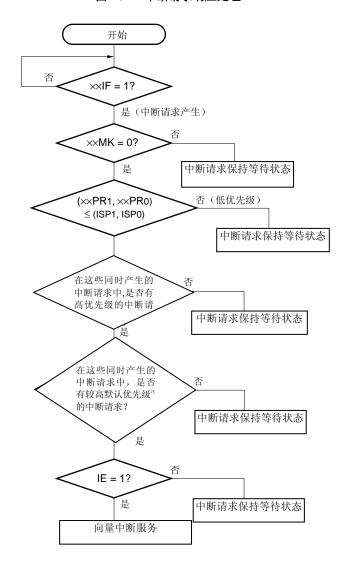

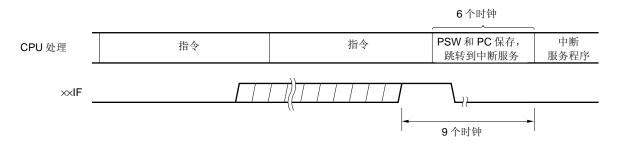

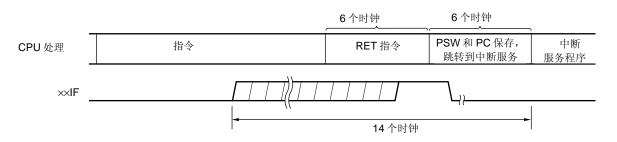

|      | 16.4.1 可屏蔽的中断响应                 | 571 |

|      | 16.4.2 软件中断请求响应                 | 573 |

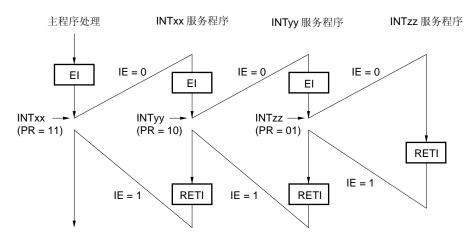

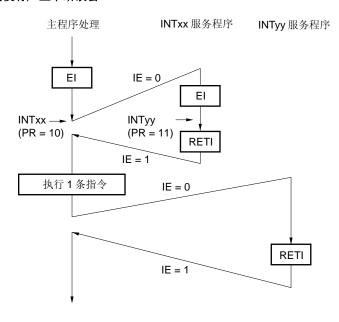

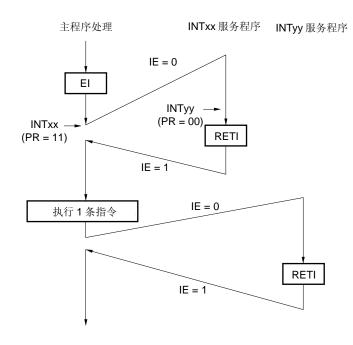

|      | 16.4.3 多重中断嵌套                   | 574 |

|      | 16.4.4 保持中断请求                   | 577 |

| 第十七章 | 章 按键中断功能                        | 578 |

|      | 按键中断的功能                         |     |

|      | 按键中断的配置                         |     |

| 17.3 | 控制按键中断的寄存器                      | 579 |

| 第十八章 | 章 待机功能                          | 580 |

| 18.1 | 待机功能及配置                         | 580 |

|      | 18.1.1 待机功能                     |     |

|      | 18.1.2 控制待机功能的寄存器               | 580 |

|                                                                      | 待机功能的操作                                                                                                                                                                                                                                                        | 583                             |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

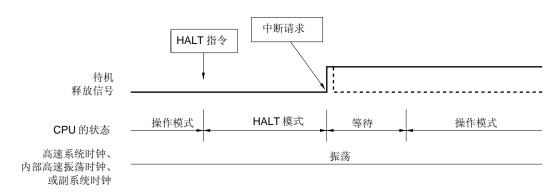

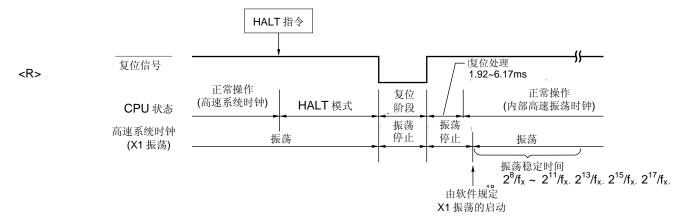

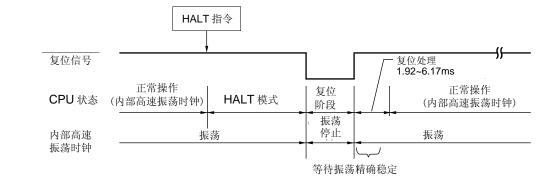

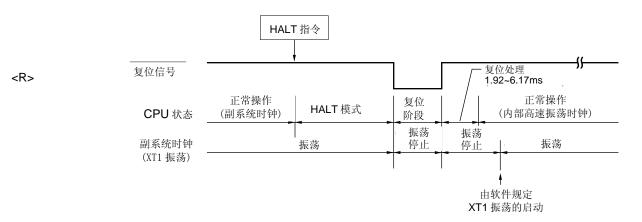

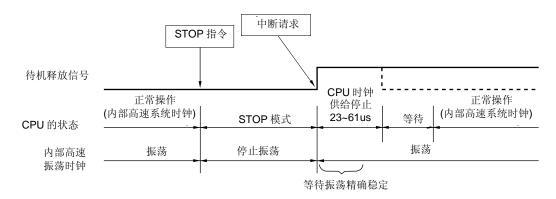

|                                                                      | 18.2.1 HALT 模式                                                                                                                                                                                                                                                 | 583                             |

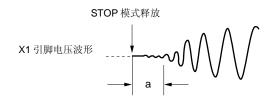

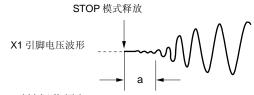

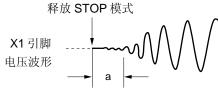

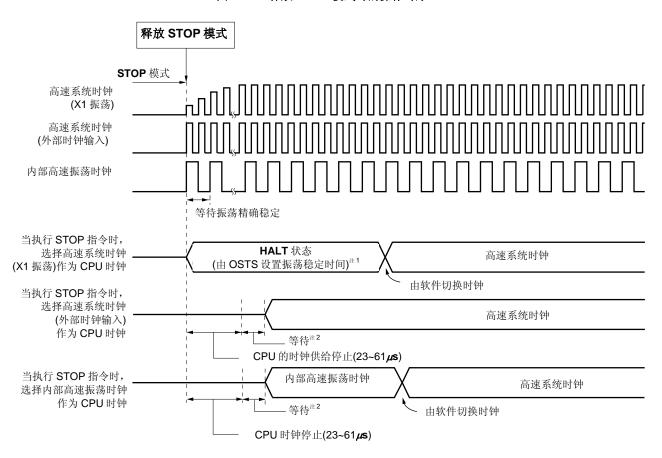

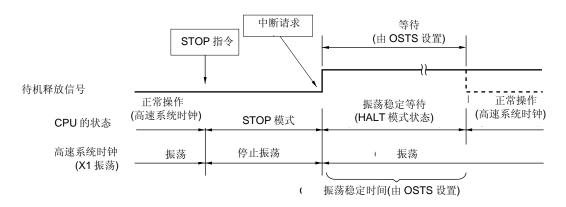

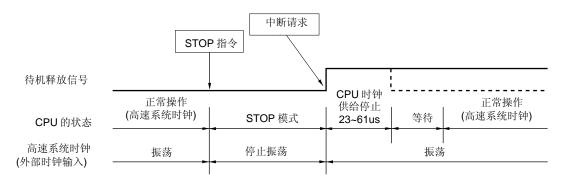

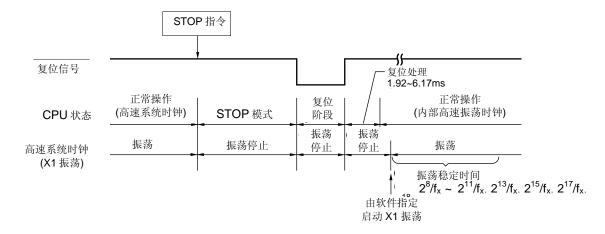

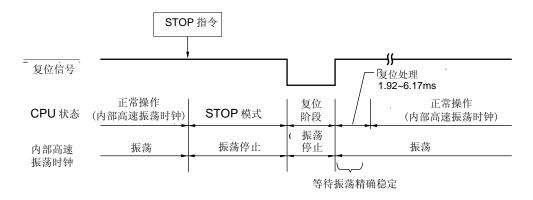

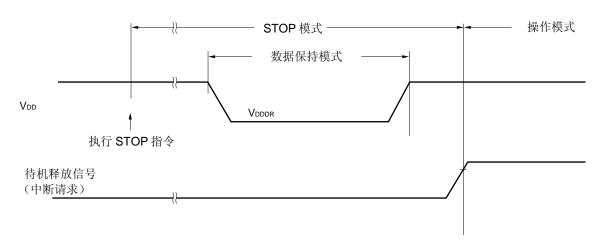

|                                                                      | 18.2.2 STOP 模式                                                                                                                                                                                                                                                 | 588                             |

|                                                                      |                                                                                                                                                                                                                                                                |                                 |

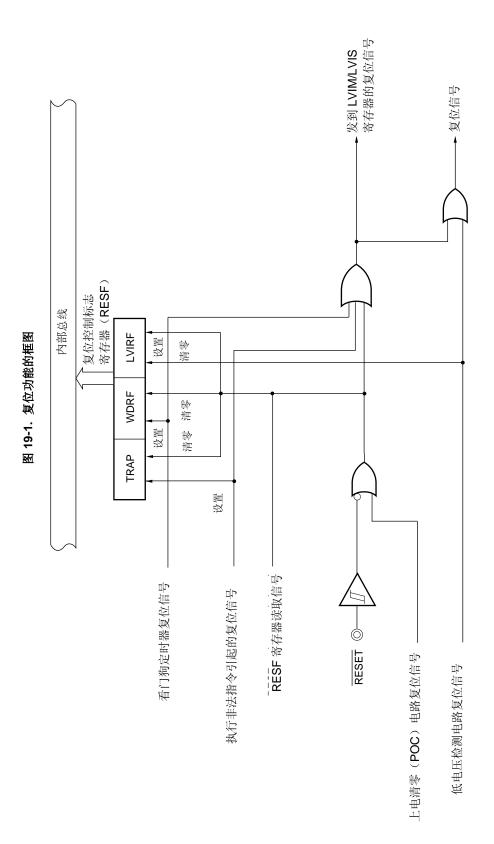

| 第十九章                                                                 | 〔 复位功能                                                                                                                                                                                                                                                         | 594                             |

| 19.1                                                                 | 确认复位源的寄存器                                                                                                                                                                                                                                                      | 602                             |

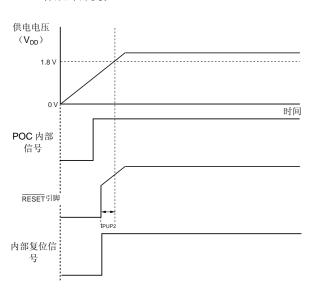

| 第二十章                                                                 | 〔 上电清零电路                                                                                                                                                                                                                                                       | 603                             |

| 20.1                                                                 | 上电清零电路的功能                                                                                                                                                                                                                                                      | 603                             |

| 20.2                                                                 | 上电清零电路的配置                                                                                                                                                                                                                                                      | 604                             |

| 20.3                                                                 | 上电清零电路的操作                                                                                                                                                                                                                                                      | 604                             |

| 20.4                                                                 | 上电清零电路使用注意事项                                                                                                                                                                                                                                                   | 607                             |

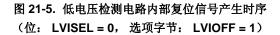

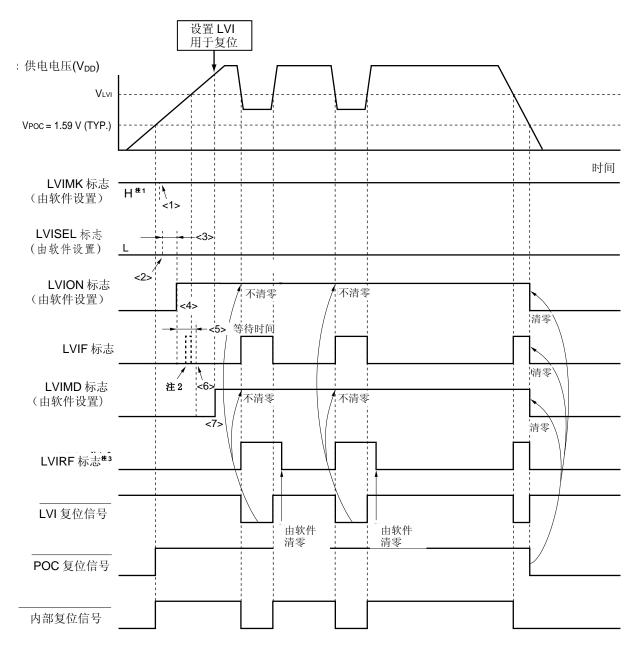

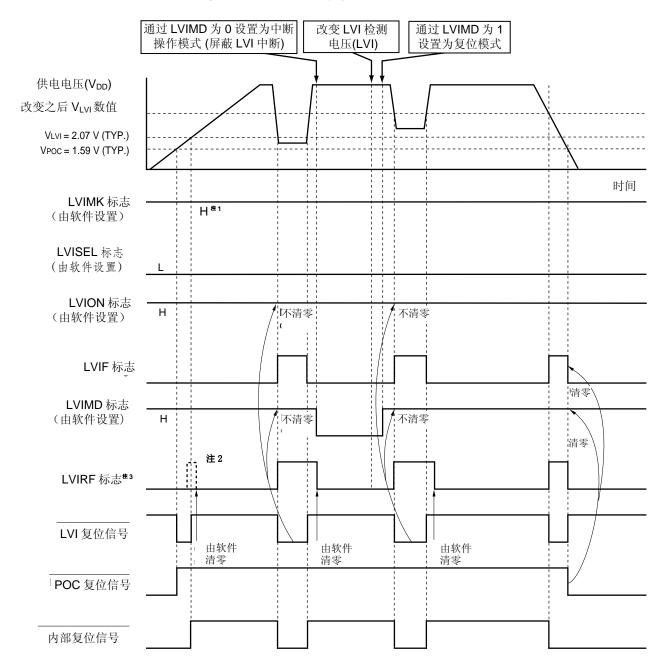

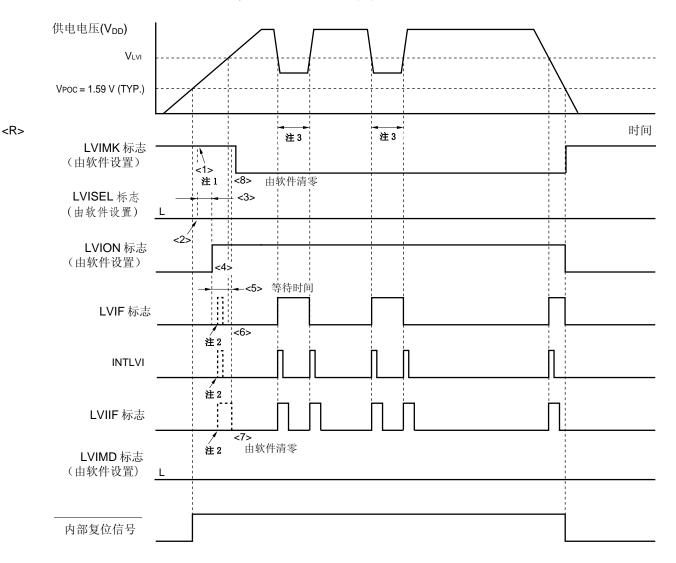

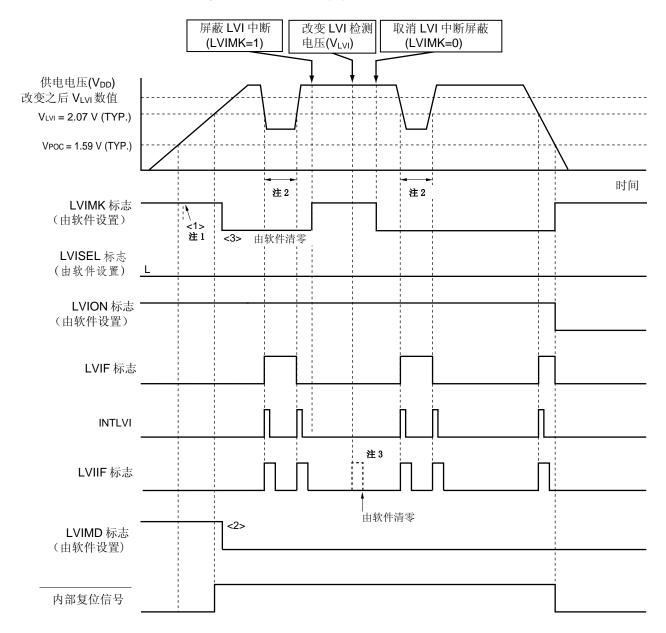

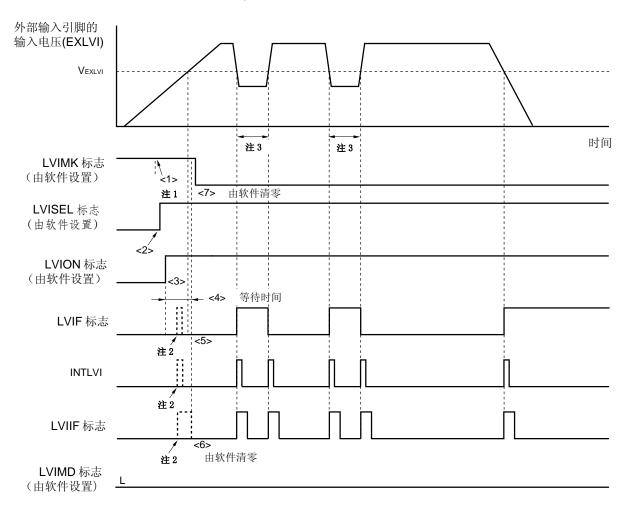

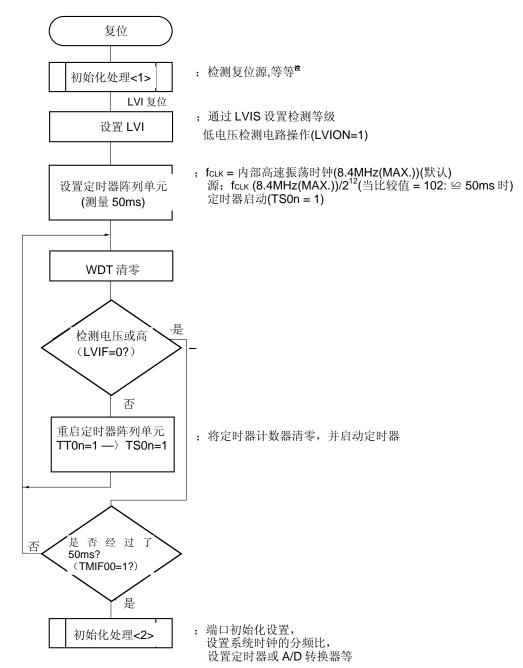

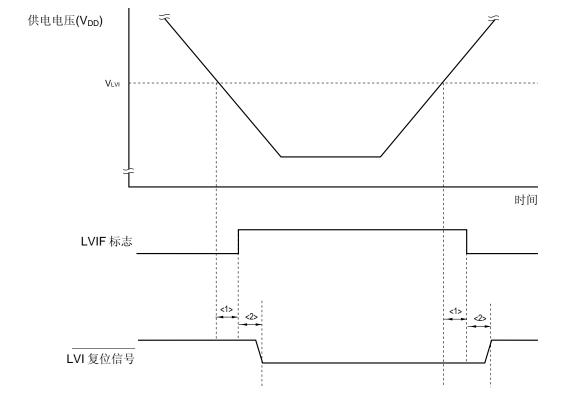

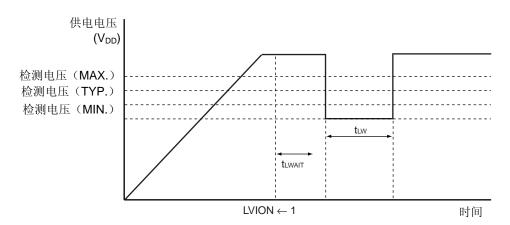

| 第二十-                                                                 | ·章 低电压检测电路                                                                                                                                                                                                                                                     | 609                             |

| 21.1                                                                 | 低电压检测电路的功能                                                                                                                                                                                                                                                     | 609                             |

|                                                                      | 低电压检测电路的配置                                                                                                                                                                                                                                                     |                                 |

|                                                                      | 控制低电压检测电路的寄存器                                                                                                                                                                                                                                                  |                                 |

|                                                                      | 低电压检测器的操作                                                                                                                                                                                                                                                      |                                 |

|                                                                      | 21.4.1 用作复位时                                                                                                                                                                                                                                                   |                                 |

|                                                                      | 21.4.2 用作中断时                                                                                                                                                                                                                                                   |                                 |

| 21.5                                                                 | 低电压检测电路的注意事项                                                                                                                                                                                                                                                   |                                 |

|                                                                      | IN OPPERATOR 4. V.                                                                                                                                                                                                                                             |                                 |

| 第二十二                                                                 | <u> </u>                                                                                                                                                                                                                                                       | 632                             |

| 22.1                                                                 | 稳压器概述                                                                                                                                                                                                                                                          |                                 |

| 22.2                                                                 | 控制稳压器的寄存器                                                                                                                                                                                                                                                      | 632                             |

| 第一十=                                                                 |                                                                                                                                                                                                                                                                |                                 |

|                                                                      | · 音 · 选项字节                                                                                                                                                                                                                                                     | 634                             |

| ., ,                                                                 | E章 选项字节                                                                                                                                                                                                                                                        |                                 |

| ., ,                                                                 | 选项字节的功能                                                                                                                                                                                                                                                        | 634                             |

| ., ,                                                                 | <b>选项字节的功能</b>                                                                                                                                                                                                                                                 | <b>634</b>                      |

| 23.1                                                                 | <b>选项字节的功能</b> 23.1.1 用户选项字节(000C0H~ 000C2H/010C0H ~010C2H)                                                                                                                                                                                                    | 634<br>634<br>635               |

| 23.1                                                                 | <b>选项字节的功能</b>                                                                                                                                                                                                                                                 | 634<br>634<br>635               |

| 23.1                                                                 | <b>选项字节的功能</b> 23.1.1 用户选项字节(000C0H~ 000C2H/010C0H ~010C2H)                                                                                                                                                                                                    |                                 |

| 23.1<br>23.2<br>23.3                                                 | 选项字节的功能                                                                                                                                                                                                                                                        |                                 |

| 23.1<br>23.2<br>23.3<br>23.4                                         | 选项字节的功能                                                                                                                                                                                                                                                        |                                 |

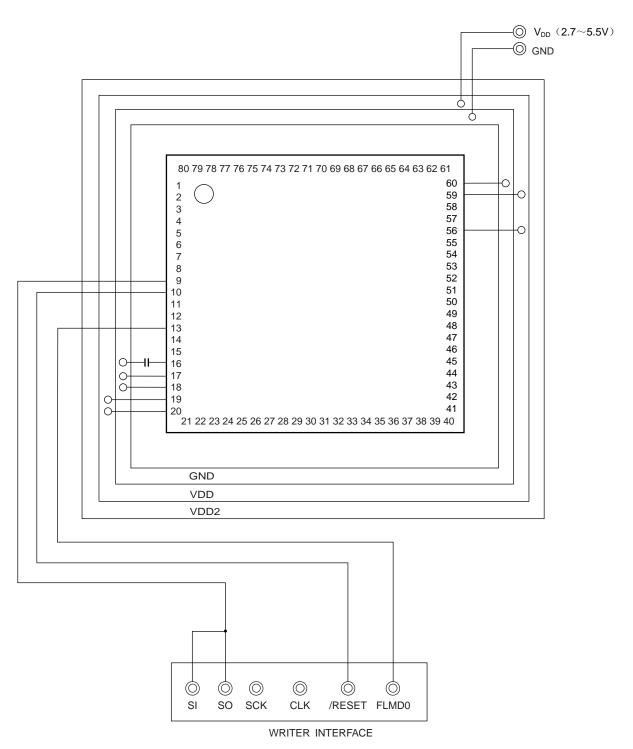

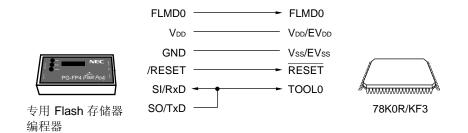

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四                                 | 选项字节的功能  23.1.1 用户选项字节(000C0H~000C2H/010C0H~010C2H)  23.1.2 片上调试选项字节(000C3H/010C3H)  用户选项字节的格式  片上调试选项字节的格式  选项字节的设置                                                                                                                                           | 634635635637637                 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1                         | 选项字节的功能 23.1.1 用户选项字节(000C0H~ 000C2H/010C0H ~010C2H) 23.1.2 片上调试选项字节(000C3H/ 010C3H) 用户选项字节的格式 片上调试选项字节的格式 选项字节的格式 选项字节的设置 FLASH 存储器                                                                                                                           | 634<br>635<br>635<br>637<br>638 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.1                 | 选项字节的功能                                                                                                                                                                                                                                                        | 634635637638638                 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.2<br>24.3         | 选项字节的功能                                                                                                                                                                                                                                                        |                                 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.2<br>24.3         | 选项字节的功能<br>23.1.1 用户选项字节(000C0H~ 000C2H/010C0H ~010C2H)<br>23.1.2 片上调试选项字节(000C3H/ 010C3H)<br>用户选项字节的格式<br>片上调试选项字节的格式<br>选项字节的设置<br>登 FLASH 存储器<br>用 Flash 存储器编程器写入<br>编程环境<br>通信模式                                                                           |                                 |

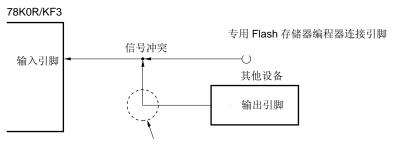

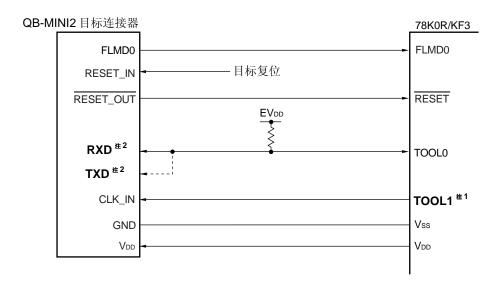

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.2<br>24.3         | 选项字节的功能  23.1.1 用户选项字节(000C0H~ 000C2H/010C0H ~010C2H)  23.1.2 片上调试选项字节(000C3H/ 010C3H)  用户选项字节的格式  片上调试选项字节的格式  选项字节的设置  章 FLASH 存储器  用 Flash 存储器编程器写入 编程环境  通信模式  On Board 方式的引脚连接                                                                            |                                 |

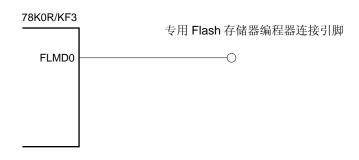

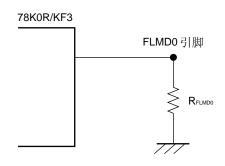

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.2<br>24.3         | 选项字节的功能  23.1.1 用户选项字节(000C0H~ 000C2H/010C0H ~010C2H)  23.1.2 片上调试选项字节(000C3H/ 010C3H)  用户选项字节的格式  片上调试选项字节的格式  选项字节的设置  章 FLASH 存储器  用 Flash 存储器编程器写入 编程环境  通信模式  On Board 方式的引脚连接  24.4.1 FLMD0 引脚                                                           |                                 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.2<br>24.3         | 选项字节的功能                                                                                                                                                                                                                                                        |                                 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.2<br>24.3         | 选项字节的功能  23.1.1 用户选项字节(000C0H~ 000C2H/010C0H~010C2H) 23.1.2 片上调试选项字节(000C3H/ 010C3H) 用户选项字节的格式  片上调试选项字节的格式  选项字节的设置  3章 FLASH 存储器  用 Flash 存储器编程器写入 编程环境 通信模式  On Board 方式的引脚连接  24.4.1 FLMD0 引脚 24.4.2 TOOL0 引脚 24.4.3 RESET 引脚 24.4.4 端口引脚                  |                                 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.2<br>24.3         | 选项字节的功能  23.1.1 用户选项字节(000C0H~ 000C2H/010C0H~ 010C2H) 23.1.2 片上调试选项字节(000C3H/ 010C3H) 用户选项字节的格式  片上调试选项字节的格式  选项字节的设置  3章 FLASH 存储器  用 Flash 存储器编程器写入 编程环境  通信模式  On Board 方式的引脚连接  24.4.1 FLMD0 引脚 24.4.2 TOOL0 引脚 24.4.3 RESET 引脚 24.4.4 端口引脚 24.4.5 REGC 引脚 |                                 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十四<br>24.1<br>24.2<br>24.3         | 选项字节的功能                                                                                                                                                                                                                                                        |                                 |

| 23.1<br>23.2<br>23.3<br>23.4<br>第二十月<br>24.1<br>24.2<br>24.3<br>24.4 | 选项字节的功能  23.1.1 用户选项字节(000C0H~ 000C2H/010C0H~ 010C2H) 23.1.2 片上调试选项字节(000C3H/ 010C3H) 用户选项字节的格式  片上调试选项字节的格式  选项字节的设置  3章 FLASH 存储器  用 Flash 存储器编程器写入 编程环境  通信模式  On Board 方式的引脚连接  24.4.1 FLMD0 引脚 24.4.2 TOOL0 引脚 24.4.3 RESET 引脚 24.4.4 端口引脚 24.4.5 REGC 引脚 |                                 |

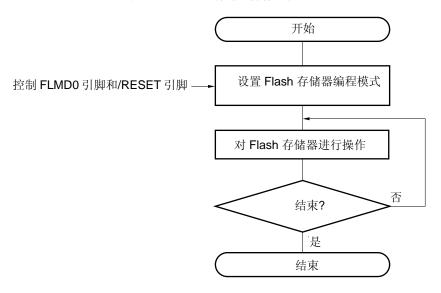

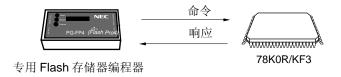

| 24.6                                  | <b>3</b> 编程方法                                        | 644  |

|---------------------------------------|------------------------------------------------------|------|

|                                       | 24.6.1 控制 flash 存储器                                  | 644  |

|                                       | 24.6.2 Flash 存储器编程模式                                 | 644  |

|                                       | 24.6.3 选择通信模式                                        | 645  |

|                                       | 24.6.4 通信命令                                          | 645  |

| 24.7                                  | 7 安全设置                                               | 647  |

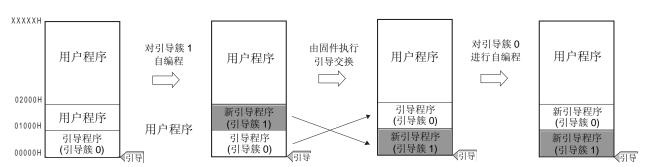

| 24.8                                  | 3  通过自编程进行 Flash 存储器编程                               | 649  |

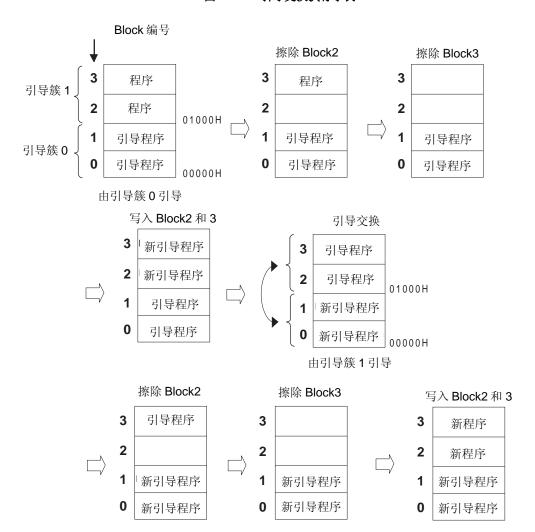

|                                       | 24.8.1 引导交换功能                                        | 651  |

|                                       | 24.8.2 Flash 防护窗口功能                                  | 653  |

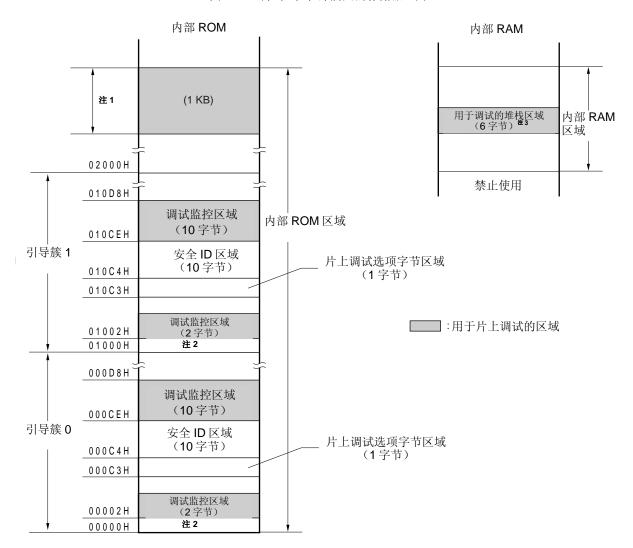

| <b>举一</b> 上·                          | 五章 片上调试功能                                            | CE A |

|                                       |                                                      |      |

| 25.1<br>25.2                          |                                                      |      |

| 25.2<br>25.3                          |                                                      |      |

| 25.0                                  | 9 用广页你的休日                                            |      |

| 第二十                                   | 六章 BCD 修正电路                                          | 657  |

| 26.1                                  |                                                      |      |

| 26.2                                  |                                                      |      |

| 26.3                                  |                                                      |      |

| 20.0                                  | 200 PT. GHWI-                                        |      |

| 第二十一                                  | 七章 指令集                                               | 660  |

| 27 1                                  | Ⅰ 操作列表使用规则                                           | 660  |

| 21.1                                  | <b>27.1.1</b> 操作数标识符和标识方法                            |      |

|                                       | 27.1.2 操作栏描述                                         |      |

|                                       | 27.1.3 标志操作栏的描述                                      |      |

|                                       | 27.1.4 前缀指令                                          | 662  |

| 27.2                                  | 2 操作列表                                               | 663  |

| <b>4</b> 2★ → 1.                      | 1. 本. 中 <i>与</i> 此处                                  | 000  |

| 弗—丁 <i>/</i>                          | 八章 电气特性                                              |      |

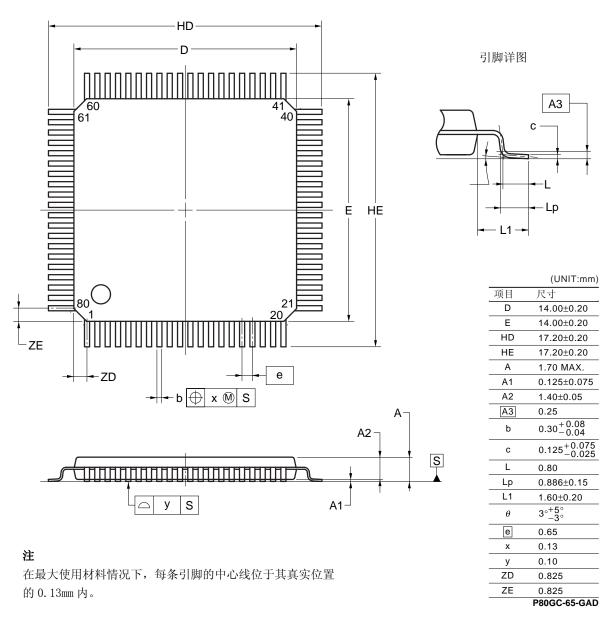

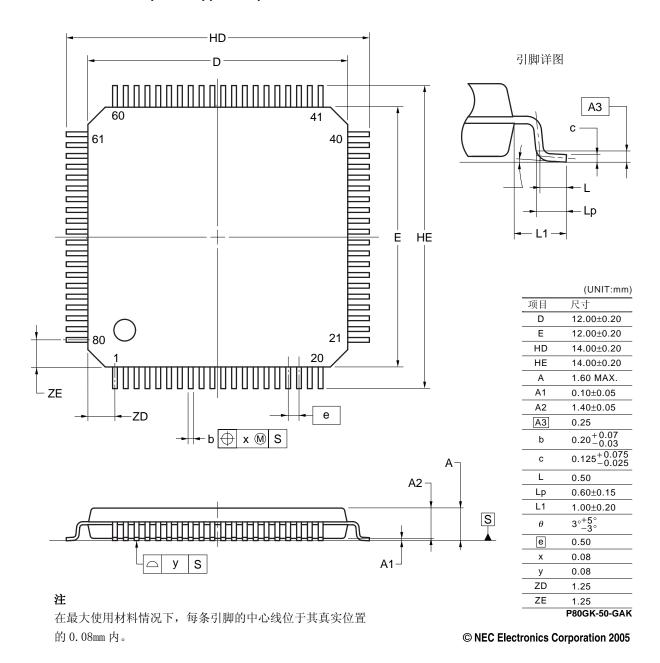

| 第二十                                   | 九章 封装图                                               | 726  |

| , , , , , , , , , , , , , , , , , , , |                                                      |      |

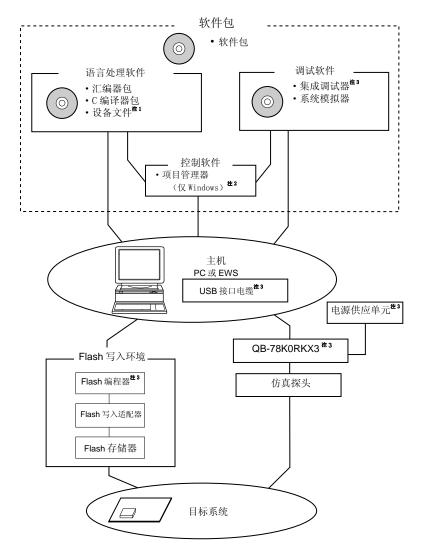

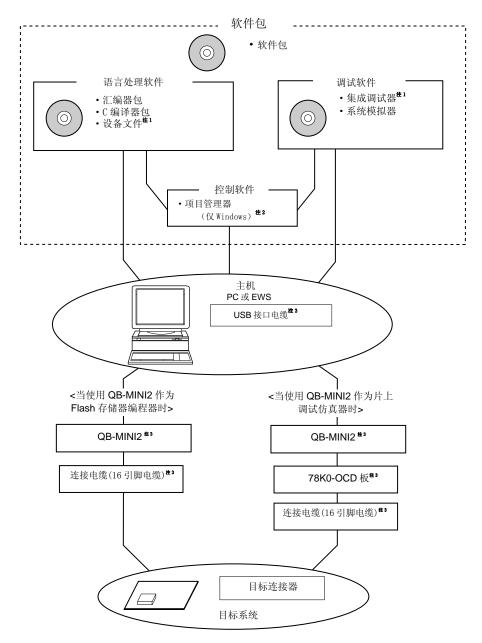

| 附录 A                                  | 开发工具                                                 | 728  |

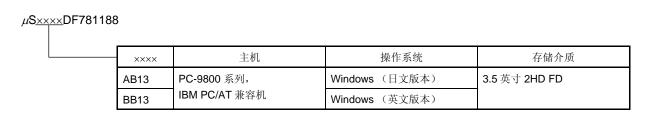

| A.1                                   | 软件包                                                  | 731  |

| A.2                                   | 语言处理软件                                               | 731  |

|                                       | 控制软件                                                 |      |

| A.4                                   | Flash 存储器编程工具                                        | 732  |

|                                       | A.4.1 当使用 flash 存储器编程器 FG-FP5,FL-PR5,FG-FP4 和 FL-PR4 |      |

|                                       | A.4.2 当使用具有编程功能的片上调试仿真器 QB-MINI2                     |      |

| A.5                                   | 调试工具 (硬件)                                            |      |

|                                       | A.5.1 当使用在线仿真器 QB-78K0RKX3                           |      |

| _                                     | A.5.2 当使用具有编程功能的片上调试仿真器 QB-MINI2 时                   |      |

| A.6                                   | 调试工具 (软件)                                            | 735  |

| 附录 B                                  | 修订历史                                                 | 736  |

| R 1                                   | 本版中的主要修订之处                                           | 736  |

|                                       | 以往版本的修订历史                                            | 740  |

#### 第一章 概述

#### 1.1 特性

- O 指令最短执行时间可以改变,范围在高速 (0.05 μs: @高速系统时钟的操作频率为 20 MHz) 和超低速 (61 μs: @子系统时钟的操作频率为 32.768 kHz) 之间

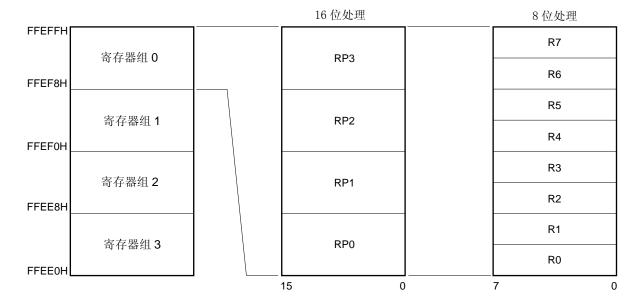

- O 通用寄存器: 8位×32寄存器(8位×8寄存器×4组)

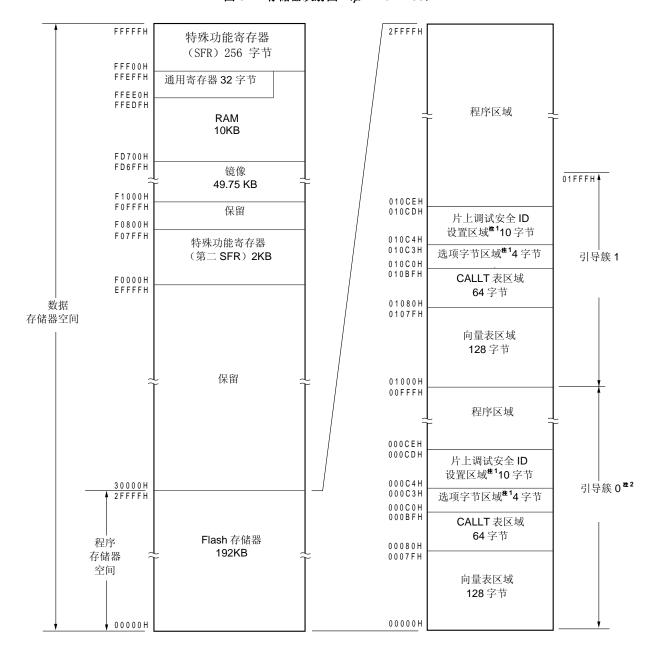

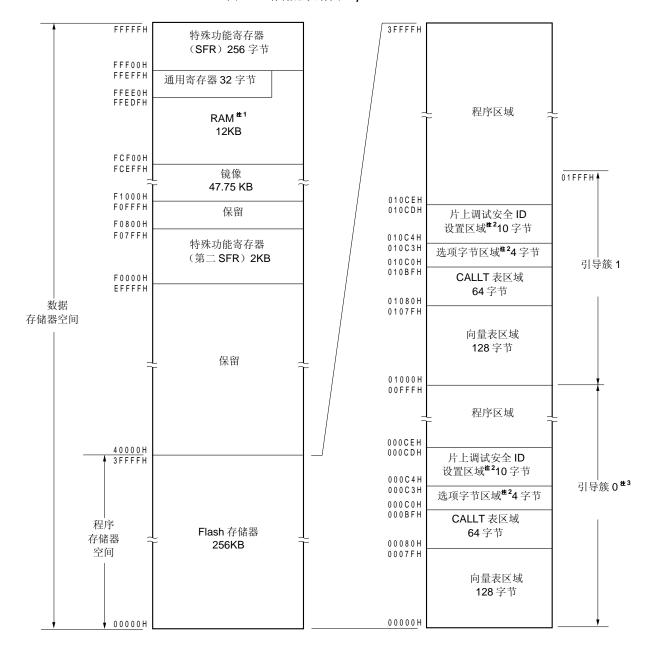

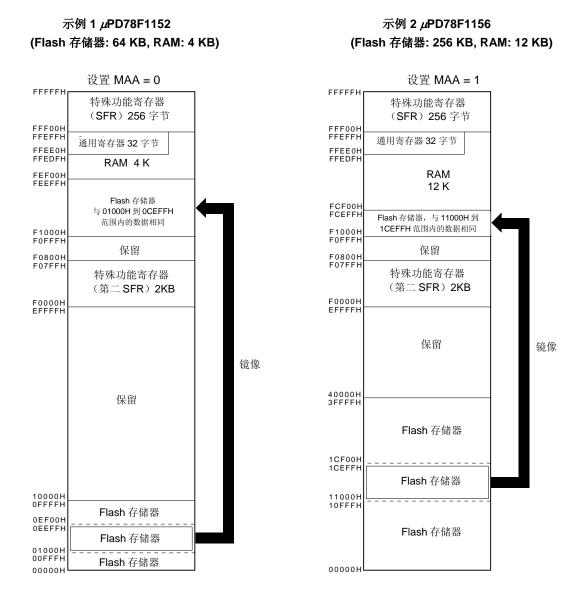

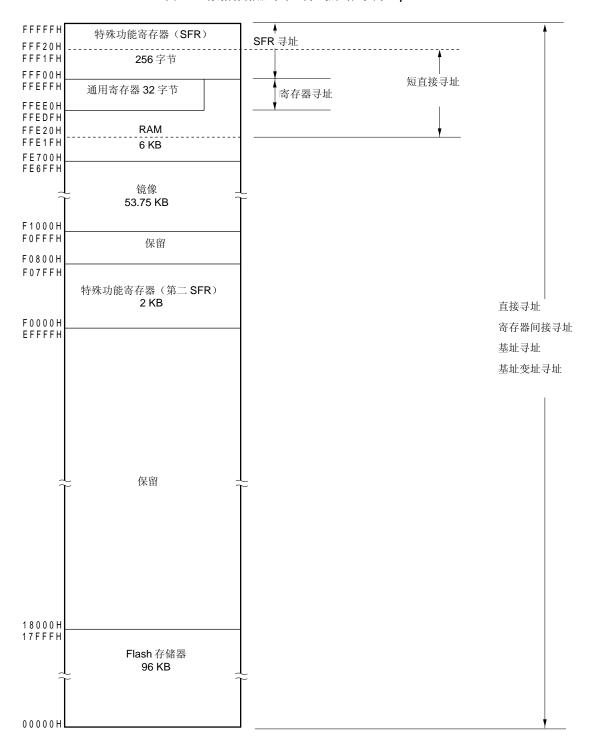

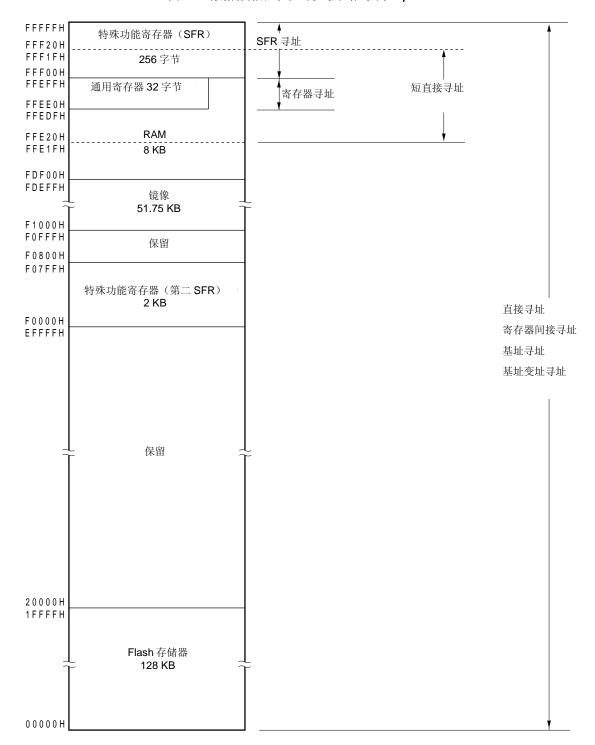

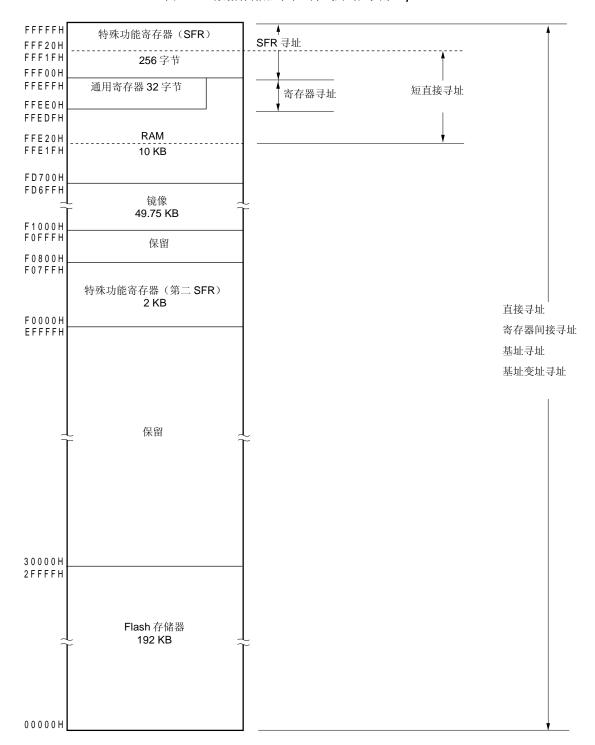

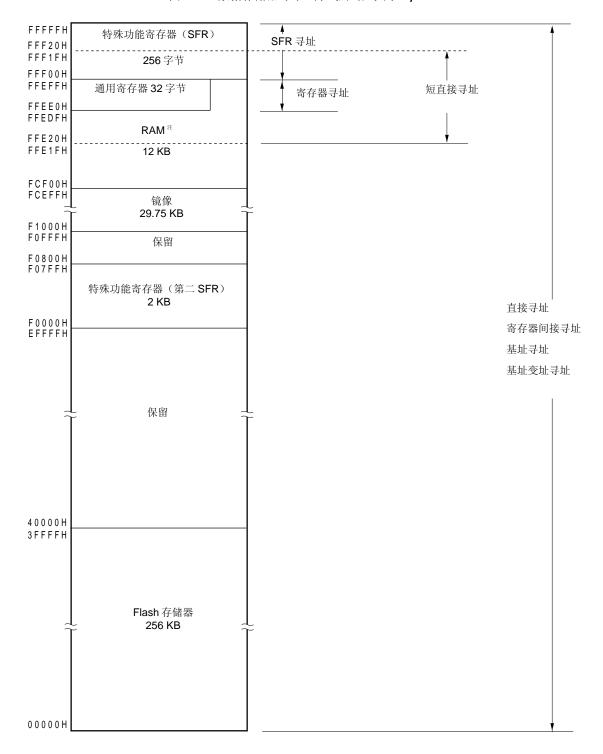

- O ROM, RAM 容量

| 项目<br>产品型号 | 程序存<br>(ROM |        | 数据存储器<br>(RAM) |

|------------|-------------|--------|----------------|

| μPD78F1152 | Flash 存储器   | 64 KB  | 4 KB           |

| μPD78F1153 |             | 96 KB  | 6 KB           |

| μPD78F1154 |             | 128 KB | 8 KB           |

| μPD78F1155 |             | 192 KB | 10 KB          |

| μPD78F1156 |             | 256 KB | 12 KB          |

- O 内置单电源 flash 存储器(芯片擦除/ 块擦除/禁止写入功能)

- O 自编程(具有引导交换功能/flash 屏蔽窗口功能)

- O 片上调试功能

- O 内置上电清零电路(POC)和低电压检测电路(LVI)

- O 内置看门狗定时器 (通过片上内部低速振荡时钟操作)

- O 内置乘法器(16位×16位)

- O 内置按键中断功能

- O 内置时钟输出/ 蜂鸣器输出控制器

- O 片上 BCD 调整

- O I/O 端口: 70 (N 沟道开漏: 4)

- O 定时器: 10 通道

- 16 位定时器: 8 通道看门狗定时器: 1 通道实时计数器: 1 通道

- 〇 串行接口

- CSI: 2 通道/UART: 1 通道

- CSI: 1 通道/UART: 1 通道/ 简易 I<sup>2</sup>C: 1 通道

- CSI: 1 通道/UART: 1 通道/ 简易 I<sup>2</sup>C: 1 通道

- UART (支持 LIN 总线): 1 通道

- I<sup>2</sup>C: 1 通道

- O 10 位分辨率 A/D 转换器 (AVREFO = 2.3~5.5 V): 8 通道

- O 8 位分辨率 D/A 转换器 (AVREF1 = 1.8~5.5 V): 2 通道

- O 供电电压: VDD = 1.8~5.5 V

- O 工作环境温度: Ta = -40~+85°C

## 1.2 应用

- 〇 家用电器

- 激光打印机马达

- 衣物清洗设备

- 空调设备

- 冰箱

- O 家庭音响系统

- O 数码相机,数码摄像机

## 1.3 订购信息

## • Flash 存储器版本

| 产品型号                | 封装                           |

|---------------------|------------------------------|

| μPD78F1152GC-GAD-AX | 80-引脚塑封 LQFP (14×14)         |

| μPD78F1153GC-GAD-AX | 80-引脚塑封 LQFP (14×14)         |

| μPD78F1154GC-GAD-AX | 80-引脚塑封 LQFP (14×14)         |

| μPD78F1155GC-GAD-AX | 80-引脚塑封 LQFP (14×14)         |

| μPD78F1156GC-GAD-AX | 80-引脚塑封 LQFP (14×14)         |

| μPD78F1152GK-GAK-AX | 80-引脚塑封 LQFP (密脚距) (12 × 12) |

| μPD78F1153GK-GAK-AX | 80-引脚塑封 LQFP (密脚距) (12 × 12) |

| μPD78F1154GK-GAK-AX | 80-引脚塑封 LQFP (密脚距) (12 × 12) |

| μPD78F1155GK-GAK-AX | 80-引脚塑封 LQFP (密脚距) (12 × 12) |

| μPD78F1156GK-GAK-AX | 80-引脚塑封 LQFP (密脚距) (12 × 12) |

注意事项 78K0R/KF3 具有片上调试功能。大规模生产时不要使用本产品,因为在使用片上调试功能后,从 flash 存储器可重写的次数受到限制这一点来看,它的可靠性不能保证。NEC Electronics 不接受对 于本产品使用片上调试功能后的任何投诉。

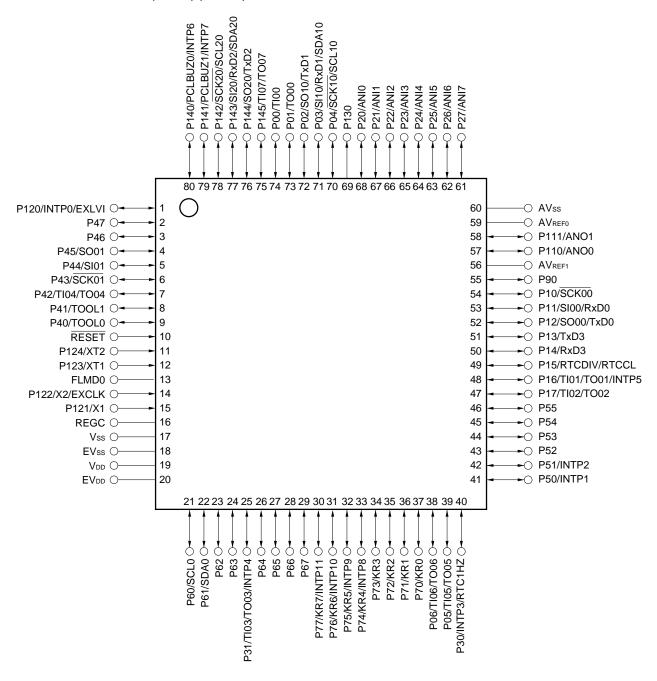

## 1.4 引脚配置 (俯视图)

- 80-引脚塑封 LQFP (14 × 14)

- 80-引脚塑封 LQFP (密脚距) (12 × 12)

注意事项 1. 使 AVss 的电压与 EVss 和 Vss 相同。

<R>

- 2. 使 EVDD 的电压与 VDD 相同。

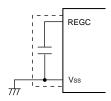

- 3. 通过一个电容(0.47 $\sim$ 1  $\mu$ F)将 REGC 引脚连接到 Vss。

**备注** 应用单片机时,必须减少其内部产生的噪声,推荐给两个 EVod 引脚提供独立的电源,并将两个 EVss 引脚分别连接到地线。

#### 引脚标识

ANIO~ANI7: 模拟 输入 REGC: 调节器电容 ANO0, ANO1: 模拟 输出 RESET: 复位 AVREFO, AVREF1: 模拟参考电压 RTC1HZ: 实时计数器修正时钟(1 Hz)输 AVss: 模拟 地 EV<sub>DD</sub>: 端口的供电电源 RTCCL: 实时计数器时钟 (32 kHz 原始振 EVss: 端口的地 荡)输出 **EXCLK:** 外部时钟输入 RTCDIV: 实时计数器时钟 (32 kHz 分频) (主系统时钟) 输出 为低电压检测电路提供的 EXLVI: RxD0~RxD3: 接收数据 外部电压输入 SCK00, SCK01, FLMD0: Flash 编程模式 SCK10, SCK20: 串行时钟输入/输出 INTP0~INTP11: 外部中断输入 SCL0, SCL10, SCL20: 串行时钟输入/输出 KR0~KR7: 按键返回 SDA0, SDA10, SDA20: 串行数据输入/输出 P00~P06: 端口 0 SI00, SI01, P10~P17: 端口 1 SI10, SI20: 串行数据输入 P20~P27: 端口2 SO00, SO01, P30, P31: 端口3 SO10, SO20: 串行数据输出 P40~P47: 端口4 TI00~TI07: 定时器 输入 P50~P55: TO00~TO07: 端口 5 定时器 输出 P60~P67: 端口6 TOOL0: 对工具的数据输入/输出 P70~P77: TOOL1: 端口7 对工具的时钟 输出 P90: 端口9 TxD0~TxD3: 发送数据 P110, P111: VDD: 端口 11 电源电压 P120~P124: Vss: 端口 12 地 X1, X2: P130: 端口 13 晶体振荡器(主系统时钟) P140~P145: 端口 14 XT1, XT2: 晶体振荡器 (子系统时钟) PCLBUZ0, PCLBUZ1: 可编程时钟输出/

蜂鸣器输出

## 1.5 78K0R 系列单片机列表

| ROM    | RAM   | 78K0R/KE3  | 78K0R/KF3  | 78K0R/KG3               | 78K0R/KH3               | 78K0R/KJ3               |

|--------|-------|------------|------------|-------------------------|-------------------------|-------------------------|

|        |       | 64 引脚      | 80 引脚      | 100 引脚                  | 128 引脚                  | 144 引脚                  |

| 512 KB | 30 KB | -          | -          | μPD78F1168 <sup>≇</sup> | μPD78F1178 <sup>推</sup> | μPD78F1188 <sup>±</sup> |

| 384 KB | 24 KB | -          | -          | μPD78F1167 <sup>±</sup> | μPD78F1177 <sup>推</sup> | μPD78F1187 <sup>±</sup> |

| 256 KB | 12 KB | μPD78F1146 | μPD78F1156 | μPD78F1166              | μPD78F1176 <sup>±</sup> | μPD78F1186 <sup>ំ</sup> |

| 192 KB | 10 KB | μPD78F1145 | μPD78F1155 | μPD78F1165              | μPD78F1175 <sup>±</sup> | μPD78F1185 <sup>ំ</sup> |

| 128 KB | 8 KB  | μPD78F1144 | μPD78F1154 | μPD78F1164              | μPD78F1174 <sup>½</sup> | μPD78F1184 <sup>ំ</sup> |

| 96 KB  | 6 KB  | μPD78F1143 | μPD78F1153 | μPD78F1163              | -                       | -                       |

| 64 KB  | 4 KB  | μPD78F1142 | μPD78F1152 | μPD78F1162              | _                       | _                       |

注 开发中

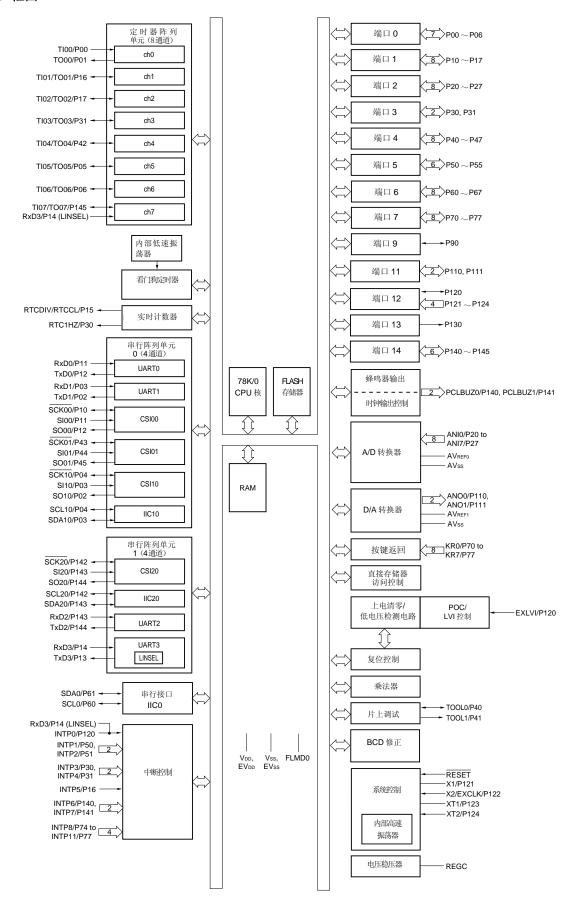

#### 1.6 框图

## 1.7 功能概述

(1/2)

|                 |                                             |                                                                                                            |                                      |               |            | (1/2)      |  |  |

|-----------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|------------|------------|--|--|

|                 | 项目                                          | μPD78F1152                                                                                                 | μPD78F1153                           | μPD78F1154    | μPD78F1155 | μPD78F1156 |  |  |

| 内部存储器           | Flash 存储器<br>(支持自编程)                        | 64 KB                                                                                                      | 96 KB                                | 128 KB        | 192 KB     | 256 KB     |  |  |

|                 | RAM                                         | 4 KB                                                                                                       | 6 KB                                 | 8 KB          | 10 KB      | 12 KB      |  |  |

| 存储器空间           |                                             | 1 MB                                                                                                       |                                      |               |            |            |  |  |

| 主系统时钟<br>(振荡频率) | 高速系统时钟                                      |                                                                                                            | 瓷)振荡,外部<br>Vdd = 2.7∼5.5 ′           |               |            | V          |  |  |

|                 | 内部高速振荡时钟 内部振荡 8 MHz (TYP.): Vpp = 1.8~5.5 V |                                                                                                            |                                      |               |            |            |  |  |

| 副系统时钟<br>(振荡频率) |                                             | XT1 (晶体)<br>32.768 kHz (                                                                                   | 振荡<br>TYP.): V <sub>DD</sub> =       | : 1.8∼5.5 V   |            |            |  |  |

| 内部低速振荡          | 时钟(WDT)                                     | 内部振荡<br>240 kHz (TY                                                                                        | P.) : V <sub>DD</sub> = 1.8          | 3∼5.5 V       |            |            |  |  |

| 通用寄存器           |                                             | 8位×32寄存                                                                                                    | 器 (8位×8寄                             | 存器 × 4 组)     |            |            |  |  |

| 最小指令执行          | 时间                                          | 0.05 μs (高速                                                                                                | 医系统时钟: fmx                           | = 20 MHz 操作   | )          |            |  |  |

|                 |                                             | 0.125 <i>μ</i> s (内                                                                                        | 部高速振荡时钟                              | : fін = 8 MHz | (TYP.) 操作) |            |  |  |

|                 |                                             | 61 μs (副系统                                                                                                 | 61 μs (副系统 时钟: fsuB = 32.768 kHz 操作) |               |            |            |  |  |

| 指令集             |                                             | <ul> <li>8 位操作, 16 位操作</li> <li>乘法 (16 位 x 16 位)</li> <li>位操作 (Set, reset, test, 和 Boolean 操作)等</li> </ul> |                                      |               |            |            |  |  |

| I/O 端口          |                                             | 总计:     70       CMOS I/O:     61       CMOS 输入:     4       CMOS 输出:     1       N沟道开搂 I/O(6 V 耐压):     4 |                                      |               |            |            |  |  |

| 定时器             |                                             | <ul> <li>16 位定时器:</li> <li>看门狗定时器:</li> <li>实时计数器:</li> <li>1 通道</li> <li>1 通道</li> </ul>                  |                                      |               |            |            |  |  |

|                 | 定时器 输出                                      | 8(PWM 输出                                                                                                   | d: 7)                                |               |            |            |  |  |

|                 | RTC 输出                                      | 2<br>• 1 Hz (副系统 时钟: fsuB = 32.768 kHz)<br>• 512 Hz 或 16.384 kHz 或 32.768 kHz (副系统 时钟: fsuB = 32.768 kHz)  |                                      |               |            |            |  |  |

| 时钟 输出/ 蜂        | 鸣器输出                                        | 2                                                                                                          |                                      |               |            |            |  |  |

| A/D 转换器         |                                             | 10 位分辨率 × 8 通道 (AVREFO = 2.3~5.5 V)                                                                        |                                      |               |            |            |  |  |

| D/A 转换器         |                                             | 8 位分辨率 × 2 通道 (AV <sub>REF1</sub> = 1.8~5.5 V)                                                             |                                      |               |            |            |  |  |

|                 |                                             |                                                                                                            |                                      |               |            |            |  |  |

(2/2)

| 申行接口       • UART 支持 LIN 总线: 1 通道         • CSI: 2 通道/UART: 1 通道       • CSI: 1 通道/GRT: 1 通道/GRT: 1 通道         • CSI: 1 通道/UART: 1 通道/GRT: 1 通道       • CSI: 1 通道/GRT: 1 通道         • CSI: 1 通道/UART: 1 通道/GRT: 1 通道       • I°C 总线: 1 通道         • I°C 总线: 1 通道       • I G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X 1 G M X                                                                                                                                                                                      |                                                                                                                                                      |    |                                                      |                                 |            |            | (2/2)      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------------------------------|---------------------------------|------------|------------|------------|

| CSI: 2 通道/UART: 1 通道         CSI: 1 通道/UART: 1 通道/简易 I²C: 1 通道         CSI: 1 通道/UART: 1 通道/简易 I²C: 1 通道         CSI: 1 通道/UART: 1 通道/简易 I²C: 1 通道         FC 总线: 1 通道         PC 总线: 1 通道         DMA 控制器       2 通道         内部       28         外部       13         按键中断       通过按键输入引脚(KR0~KR7)的下降沿检测发生的按键中断(INTKR)。         复位       由 RESET 引脚 引起的复位         由由看门狗定时器引起的内部复位       由由信事等引起的内部复位         由由作电压检测电路引起的内部复位       由非法指令执行引起的内部复位         自由非法指令执行引起的内部复位       日本:法指令执行引起的内部复位         大上调试功能       提供         大上调试功能       提供         大上调试功能       基件         工作环境温度       TA = -40~+85°C         封装       80 引脚塑封 LQFP(14×14)(0.65 mm 间距)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 项目                                                                                                                                                   |    | μPD78F1152                                           | μPD78F1153                      | μPD78F1154 | μPD78F1155 | μPD78F1156 |

| DMA 控制器       2 通道         向量中断源       内部       28         外部       13         复位       • 由 RESET 引脚 引起的复位<br>• 由看门狗定时器引起的内部复位<br>• 由上电清零引起的内部复位<br>• 由低电压检测电路引起的内部复位<br>• 由非法指令执行引起的内部复位<br>• 由非法指令执行引起的内部复位<br>• 由非不可能的内部复位<br>• 由非不可能的内部复位<br>• 由非不同的的方式。         片上调试功能       提供         供电电压       Vpd = 1.8~5.5 V         工作环境温度       Ta = -40~+85°C         封装       80 引脚塑封 LQFP(14×14)(0.65 mm 间距)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>CSI: 2 通道/UART: 1 通道</li> <li>CSI: 1 通道/UART: 1 通道/简易 I<sup>2</sup>C: 1 通道</li> <li>CSI: 1 通道/UART: 1 通道/简易 I<sup>2</sup>C: 1 通道</li> </ul> |    |                                                      |                                 |            |            |            |

| 向量中断源     内部     28       外部     13       复位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 乘法器                                                                                                                                                  |    | 16位×16位=                                             | = 32 位                          |            |            |            |

| 外部       13         按键中断       通过按键输入引脚(KR0~KR7)的下降沿检测发生的按键中断(INTKR)。         复位       • 由 RESET 引脚 引起的复位         • 由看门狗定时器引起的内部复位       • 由任电清零引起的内部复位         • 由低电压检测电路引起的内部复位       • 由非法指令执行引起的内部复位         • 由非法指令执行引起的内部复位       **         性电压       Vod = 1.8~5.5 V         工作环境温度       TA = -40~+85°C         封装       80 引脚塑封 LQFP(14×14)(0.65 mm 间距)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DMA 控制器                                                                                                                                              |    | 2 通道                                                 |                                 |            |            |            |

| 按键中断       通过按键输入引脚(KR0~KR7)的下降沿检测发生的按键中断(INTKR)。         复位       • 由 RESET 引脚 引起的复位<br>• 由看门狗定时器引起的内部复位<br>• 由上电清零引起的内部复位<br>• 由低电压检测电路引起的内部复位<br>• 由非法指令执行引起的内部复位<br>• 由非法指令执行引起的内部复位<br>**         片上调试功能       提供         供电电压       Vpp = 1.8~5.5 V         工作环境温度       TA = -40~+85°C         封装       80 引脚塑封 LQFP(14×14)(0.65 mm 间距)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 向量中断源                                                                                                                                                | 内部 | 28                                                   | 28                              |            |            |            |

| (INTKR)。  (INTKR)  (INTK |                                                                                                                                                      | 外部 | 13                                                   |                                 |            |            |            |

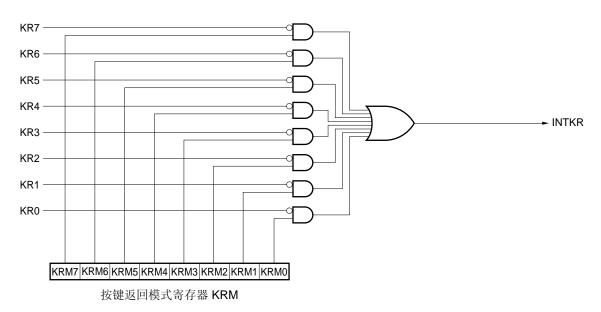

| <ul> <li>● 由看门狗定时器引起的内部复位</li> <li>● 由上电清零引起的内部复位</li> <li>● 由低电压检测电路引起的内部复位</li> <li>● 由非法指令执行引起的内部复位</li> <li>● 由非法指令执行引起的内部复位</li> <li>         世程</li> <li>         供电电压         Vpp = 1.8~5.5 V     </li> <li>         工作环境温度         TA = -40~+85°C     </li> <li>         封装         80 引脚塑封 LQFP(14×14)(0.65 mm间距)     </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 按键中断                                                                                                                                                 | •  |                                                      | 引脚 (KR0∼KF                      | R7)的下降沿检   | 测发生的按键中    | 断          |

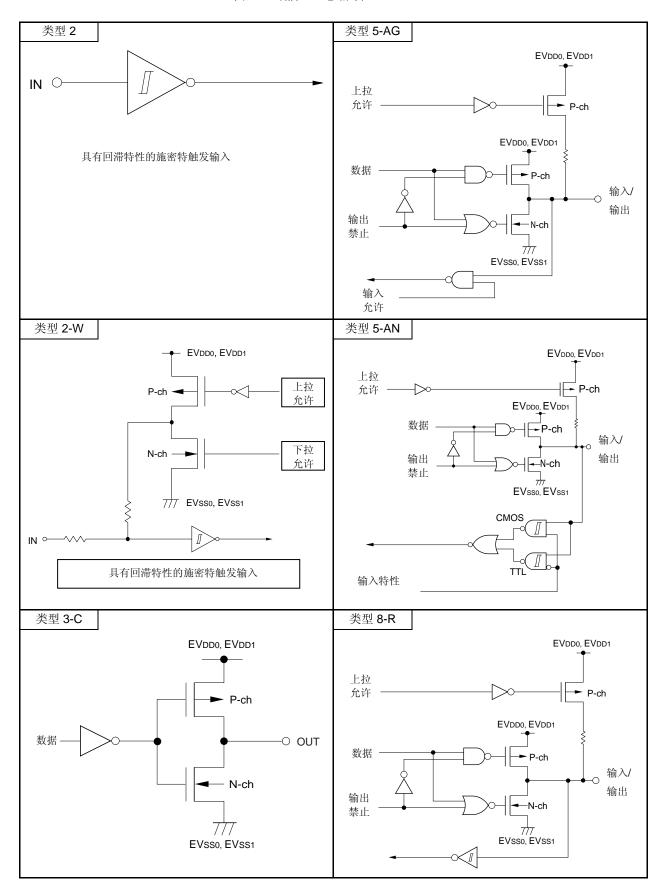

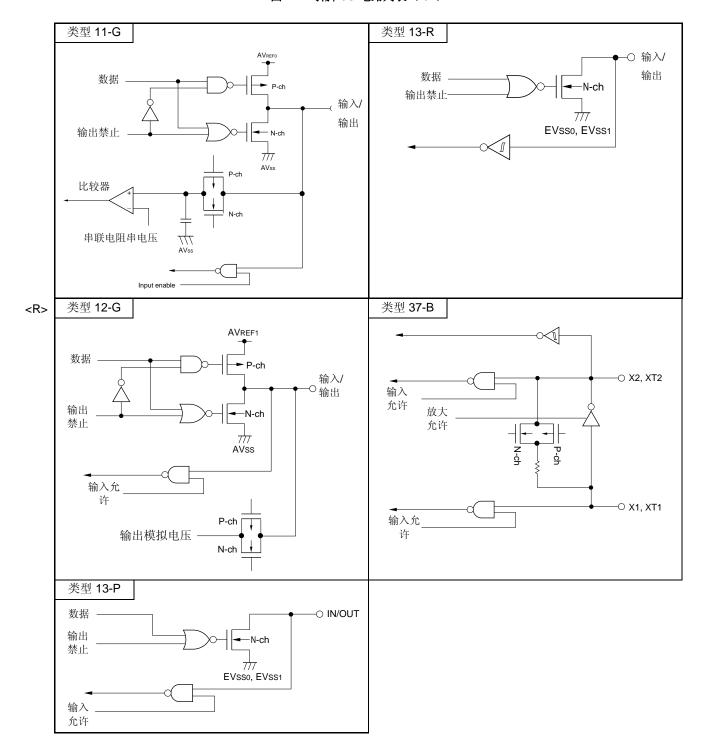

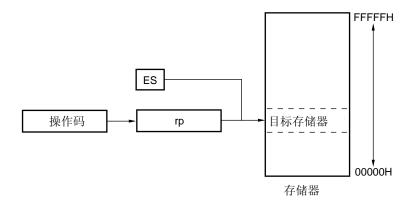

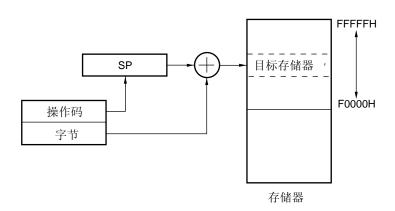

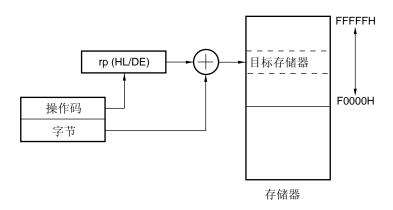

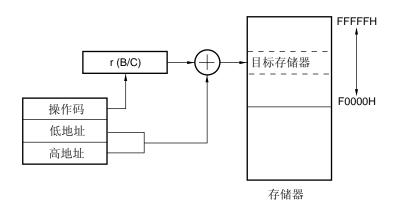

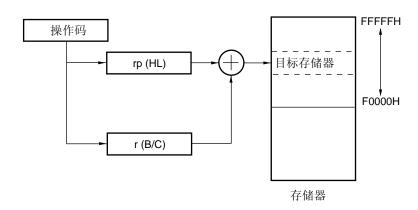

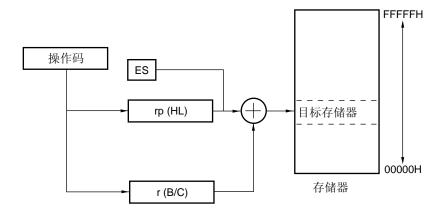

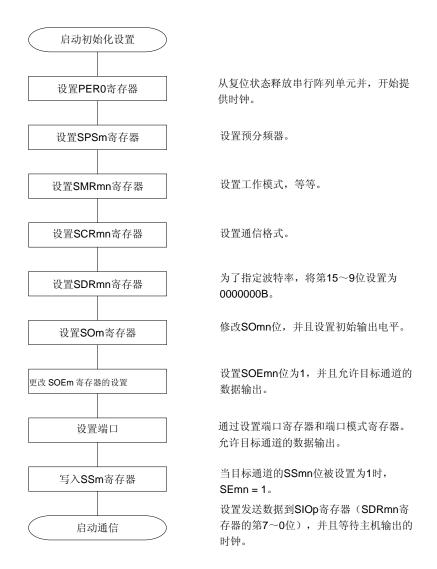

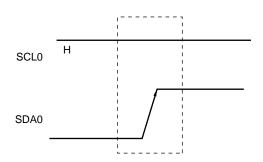

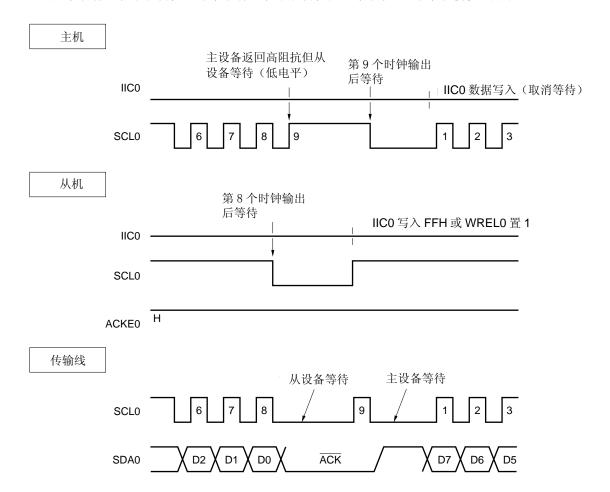

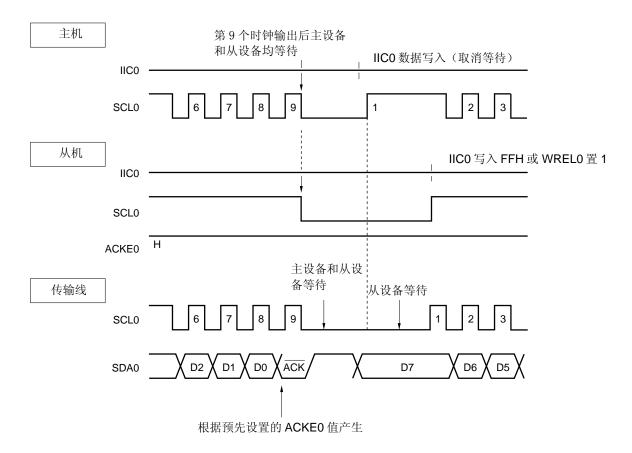

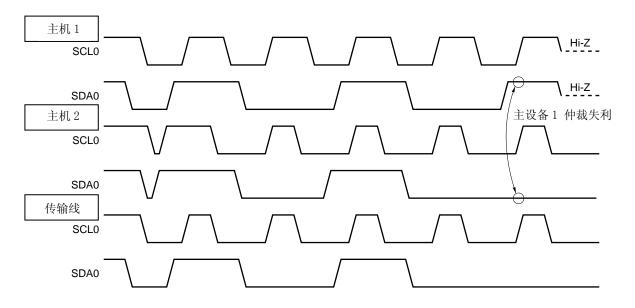

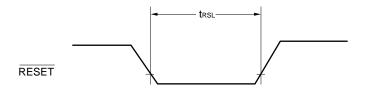

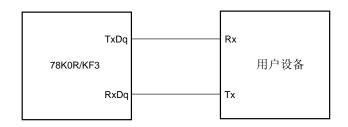

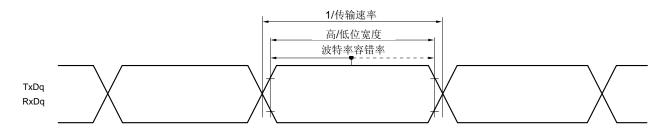

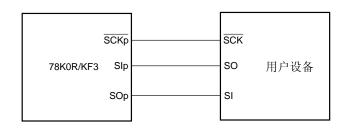

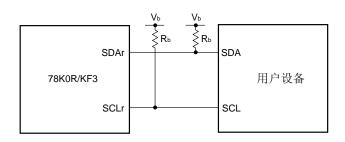

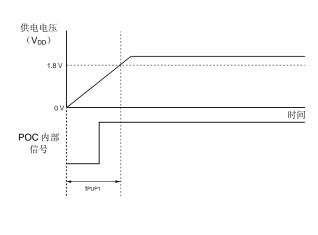

| 供电电压     V <sub>DD</sub> = 1.8~5.5 V       工作环境温度     T <sub>A</sub> = -40~+85°C       封装     80 引脚塑封 LQFP(14×14)(0.65 mm 间距)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 复位                                                                                                                                                   |    | <ul><li>由看门狗定</li><li>由上电清零</li><li>由低电压检测</li></ul> | 时器引起的内部。<br>引起的内部复位<br>则电路引起的内部 | 部复位        |            |            |