### RAA214023 Simetrix Model

This document discusses the Simetrix model for the RAA214023 LDO including the features supported and not supported by the model. To download the model, see the RAA214023 product page.

## Contents

| 1. | Model Features                                | 1 |  |

|----|-----------------------------------------------|---|--|

|    | 1.1 Device Performance Features Supported     | 1 |  |

|    | 1.2 Device Performance Features NOT Supported | 1 |  |

| 2. | Downloading and Running the Software          | 2 |  |

| 3. | License Statement                             |   |  |

| 4. | Revision History                              | 3 |  |

## 1. Model Features

This Simetrix Macromodel is intended to give typical DC and AC performance characteristics under a wide range of external circuit configurations using compatible simulation platforms such as iSim PE.

### 1.1 Device Performance Features Supported

The following are the device performance features that are supported by this model.

- · Device parameters are set to typical room temperature values

- Output voltage programmed using internal and external resistors

- Gain and phase

- Input noise terms including 1/f effects

- PSRR

- Transient V<sub>IN</sub>, V<sub>OUT</sub>, and Load. Reference the Excel spreadsheet that is included with the SPICE software (Figure 1), for test results (RAA214023 Simetrix Model Validations.xlsx).

- Output current limit

- Enable and Disable function using the Enable pin.

- Power-Good through the PG pin.

- UVLO <1V and 300Ω output impedance.

- $300\Omega$  output pull-down when part is disabled and V<sub>IN</sub> > 1V

- 300 $\Omega$  output pull-down when part is enabled and 1V < V<sub>IN</sub> > 2.5V

### 1.2 Device Performance Features NOT Supported

The following are the device performance features that are NOT supported by this model.

- Harmonic distortion effects

- Thermal effects and/or over-temperature

- Parameter variation

- · Part-to-part performance variation because of normal process parameter spread

- Any performance difference arising from different packaging

## 2. Downloading and Running the Software

The RAA214023 Simetrix model software can be down loaded from the RAA214023 product page.

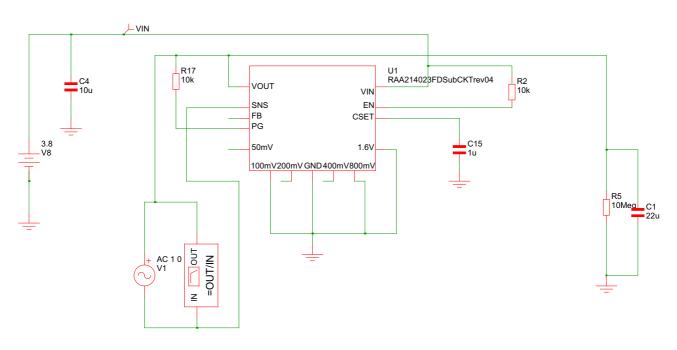

Save the file to a common directory for your Simetrix simulations. This application note assumes you have a basic knowledge of running Simetrix simulations. There are seven different files to run simulations (Figure 1). Each file is setup to evaluate a specific test (GainPhase, LoadSweep, Noise, NoiseExternalR, PSRR, VoutInternalR, and VsweepExternalR). An Excel spread sheet is also provided documenting the validation of the model. Figure 2 shows the Gain Phase simulation schematic. To run the test, click **Simulator** then **Run Schematic** in the tool bar. From here, you can copy and paste the sub-circuit into your design.

| Name                                          | Date modified     | Туре               | Size     |

|-----------------------------------------------|-------------------|--------------------|----------|

| 🚮 RAA214023 Simetrix Model Validations.xlsm   | 6/4/2021 10:21 AM | Microsoft Excel M  | 1,961 KB |

| RAA214023FDSubCKTrev04GainPhaseEmbedded.sxsch | 6/4/2021 10:22 AM | SIMetrix Schematic | 95 KB    |

| RAA214023SubCKTLoadSweepEmbedded.sxsch        | 6/3/2021 9:02 AM  | SIMetrix Schematic | 70 KB    |

| RAA214023SubCKTNoiseEmbedded.sxsch            | 6/3/2021 3:43 PM  | SIMetrix Schematic | 80 KB    |

| RAA214023SubCKTNoiseExternalRembedded.sxsch   | 6/3/2021 3:46 PM  | SIMetrix Schematic | 83 KB    |

| RAA214023SubCKTPSRRembedded.sxsch             | 6/3/2021 3:48 PM  | SIMetrix Schematic | 94 KB    |

| RAA214023SubCKTVoutInternalRembedded.sxsch    | 6/3/2021 3:50 PM  | SIMetrix Schematic | 69 KB    |

| RAA214023SubCKTVsweepExternalRembedded.sxsch  | 6/3/2021 3:53 PM  | SIMetrix Schematic | 72 KB    |

Figure 1. RAA214020 Simetrix Model Software

Figure 2. Gain Phase Test Setup with Sub-Circuit RAA214023FDSubCKTrev04

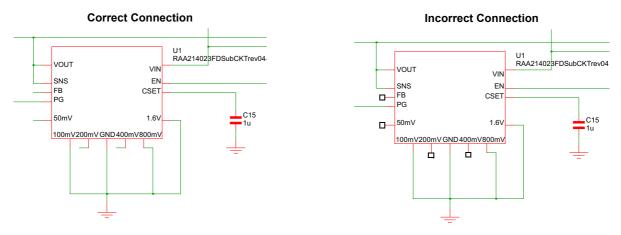

**Note:** All pins need to be connected on the SubCKT to avoid errors during net listing. Figure 3 shows the correct and incorrect connection of the RAA214023 output voltage programmed to 3.3V with the internal resistors. Pin 3, Pin 5, Pin 7, and Pin 9 are floating to achieve this. You must connect a wire to the floating pins.

Figure 3. Floating Pins Need to be Connected

# 3. License Statement

The information in this Simetrix model is protected under the United States copyright laws. Renesas Electronics Corporation hereby grants users of this macro-model hereto referred to as Licensee, a nonexclusive, nontransferable license to use this model as long as the Licensee abides by the terms of this agreement. Before using this macro-model, the Licensee should read this license. If the Licensee does not accept these terms, permission to use the model is not granted.

The Licensee may not sell, loan, rent, or license the macro-model, in whole, in part, or in modified form, to anyone outside the Licensee's company. The Licensee may modify the macro-model to suit his/her specific applications and the Licensee may make copies of this macro-model for use within their company only.

This macro-model is provided AS IS, WHERE IS AND WITH NO WARRANTY OF ANY KIND EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Renesas is not liable for special, collateral, incidental, or consequential damages in connection with or arising out of the use of this macro-model. Renesas reserves the right to make changes to the product and the macro-model without prior notice.

# 4. Revision History

| Revision | Date         | Description     |

|----------|--------------|-----------------|

| 1.0      | Jun 14, 2021 | Initial release |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/