## Introduction

Hardware design in high performance applications is rapidly becoming more complex. Designers typically use solutions they are familiar with and generally prefer the simplest solution available. At first glance a crystal oscillator (XO) seems like an easier solution than using a programmable clock. At first glance, programmable clocks may seem complicated, however, they offer a lot more flexibility and ultimately lead to a more elegant solution.

## 1 Main Advantages of Programmable Clocks

The VersaClock® family of programmable clocks has many advantages versus XO or crystal devices.

Flexibility is a main advantage of a programmable clock:

From the frequency generation (1 MHz to 350 MHz) to the outputs programming stand point, VersaClock 5, VersaClock 6 and VersaClock 3 can generate a lot of different combinations. The following output types, LVPECL, LVDS, HCSL, LP- HCSL, single ended and differential LVCMOS, are programmable via I2C. It can cover different voltage output levels from 1.8V to 3.3V. See [Section 2, "Output Logic Levels for Programmable Clocks"](#) for more details on the output logic levels.

Not to mention that the VersaClock family of products offers the advantage of having multiple configurations programmed in the OTP. Up to 4 configurations (5 for VersaClock 3) can be programmed and selected with SEL pins. That means 16 different frequencies can be generated from the same device.

The performance of VersaClock 5 (0.7 ps RMS phase jitter) and VersaClock 6 (0.5 ps RMS phase jitter) are perfect for Ethernet switch/router, 10G Ethernet and driving FPGA clock requirements (see [AN-905](#)).

Saving space and cost is another superiority of using programmable clocks. One single device can replace many crystals and XO devices and reduce board size. The number of outputs can go up to 9 outputs for VersaClock 3 (replacing up to 9 crystals or XO).

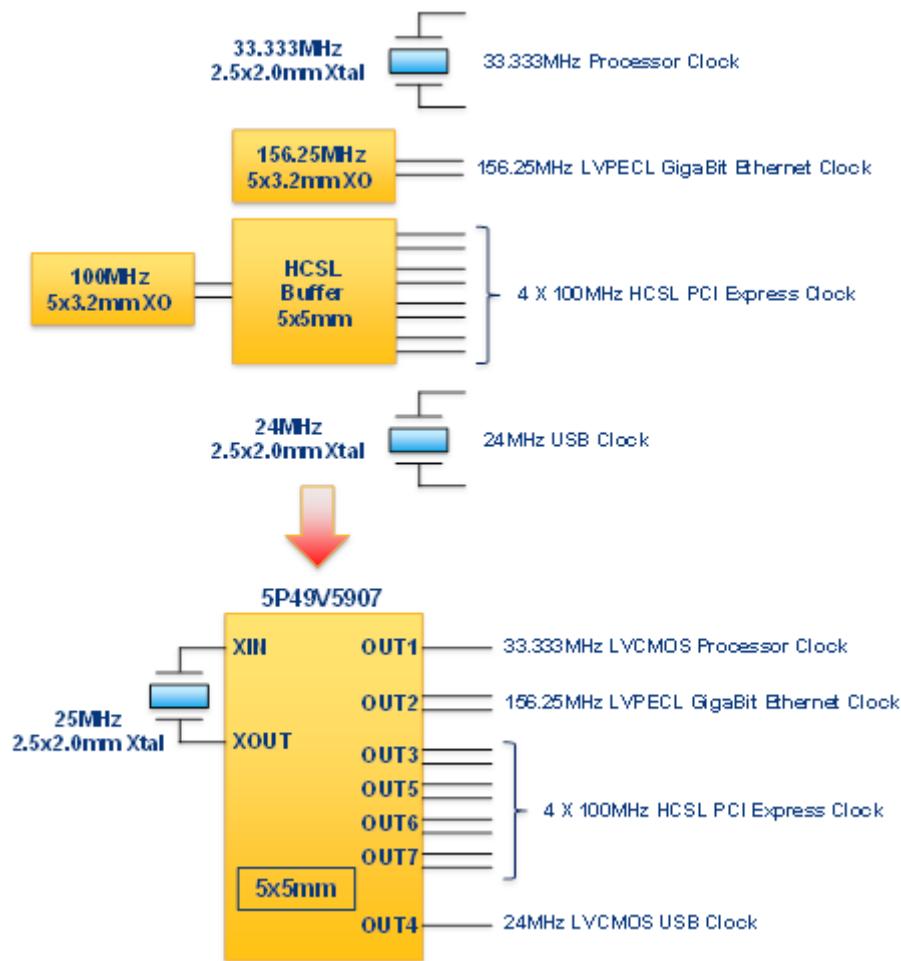

[Figure 1](#) below illustrates an example application that uses a processor clock, a GigaBit Ethernet clock, four PCI Express clocks and a USB clock.

The original application uses two crystals, each with 5mm<sup>2</sup> size. There are two XO modules with 16mm<sup>2</sup> size and one clock generator IC with 25mm<sup>2</sup>. This adds up to 67mm<sup>2</sup> total space. The VersaClock 5 replacement uses 5mm<sup>2</sup> + 25mm<sup>2</sup> = 30mm<sup>2</sup> total space, less than half.

Cost savings for this example are 30% ~ 50% depending upon volume and specifications. This is just an average example of what is possible.

Figure 1. Example Application where a 5P49V5907 Replaces Many Devices

The possibility to enable spread spectrum function with VersaClock 3, 5 and 6 or PCIe frequency generators to reduce EMI will be described in [Section 5, “Multiple Devices in One”](#)

## 2 Output Logic Levels for Programmable Clocks

VersaClock generators have individual output buffer power supply pins and the output levels for LVC MOS can be set by applying the desired power supply voltage. When driving a crystal pin from an LVC MOS output this is also useful for adjusting the driving amplitude.

Differential logic types LVDS and HCSL are not dependent upon the power supply value and the power supply level can be different at the driver side and receiver side without causing issues.

LVPECL uses VDD (or VCC) as its reference so it is important to choose the correct power supply value. VersaClock devices can work with both 2.5V and 3.3V power supply values.

PCIe clock generators or buffers can also be used to drive a variety of clock inputs. See application note [AN-891](#) for driving various input types from IDT's Low Power HCSL drivers.

### 3 Clock Frequency Accuracy

The clock outputs of a clock generator IC are as accurate as the reference clock supplied to the clock generator. When replacing a number of clock products and one of them is a very accurate clock like a TCXO, then it makes sense to preserve the TCXO and use it as a reference for the clock generator so all clocks from the clock generator get the same TCXO precision. In general one selects to use a reference that meets the requirement for the clock with the tightest frequency accuracy spec. All clocks will now meet this tightest spec.

VersaClock devices have capacitors for the crystal load capacitance on the chip and these capacitors are programmable. It is possible to fine-tune the load capacitance to correct for PCB parasitic for better frequency accuracy.

VersaClock generators 5P49V5935 and 5P49V5933 have the reference built in. This has two advantages:

1. It relieves the customer from acquiring the proper frequency reference, either a crystal or oscillator product.

2. Nominal accuracy is better than a plain crystal because the integrated reference is calibrated during production. It can be argued that the integrated reference is also better than the average clock oscillator precision. When the crystal in a clock oscillator is calibrated, there are more manufacturing steps to follow that can shift the final frequency. This results in additional frequency inaccuracy. The VersaClock calibration is done through programming without physical changes to the product after the calibration so the final frequency will remain where you set it.

The 5P49V5935 can be found at:

[www.idt.com/products/clocks-timing/clock-generators-frequency-synthesizers-pll-and-differential-clocks/programmable-clock-generators-low-power-programmable-oscillators/5p49v5935-versaclock-5-low-power-programmable-clock-generator-integrated-crystal](http://www.idt.com/products/clocks-timing/clock-generators-frequency-synthesizers-pll-and-differential-clocks/programmable-clock-generators-low-power-programmable-oscillators/5p49v5935-versaclock-5-low-power-programmable-clock-generator-integrated-crystal)

### 4 Frequency Margining

Using the pre-programmed configurations in the VersaClock generators it is possible to switch between fast, slow and nominal frequency sets for frequency margining purpose. Granted, the fast and slow frequency sets will only be used during the qualification phase of the application but nevertheless the frequency margining feature is very popular with the VersaClock generators.

Besides, using different configurations, frequency margining can also be achieved by applying changes through I2C programming.

### 5 Multiple Devices in One

Another benefit of multiple configurations in VersaClock generators is that the same device can be used in multiple locations with different configurations in each location. This greatly benefits inventory and logistics.

### 6 Layout Focus

It is important to layout clock traces as transmission lines. Theoretically a transmission line does not radiate and preserves the original waveform. Losses in a clock trace usually are insignificant at frequencies where crystals operate and at frequencies available from VersaClock products. The theoretical loss with a typical  $50\Omega$  trace on FR4 is 1dB or 10% in signal amplitude at 500 MHz and 35 cm (14 inches) of trace length. PCBs larger than 70 cm (placing the clock IC near the center) are unlikely.

Replacing XOs is the least complex because the clock generator output only needs to be set to the same logic type as the XO it is replacing. Replacing a crystal may need more care. It is still easy when the IC manufacturer simply states that the crystal oscillator input pin can also be driven with an external clock. See “[Appendix A](#)” for a recommended circuit when driving a crystal oscillator input pin.

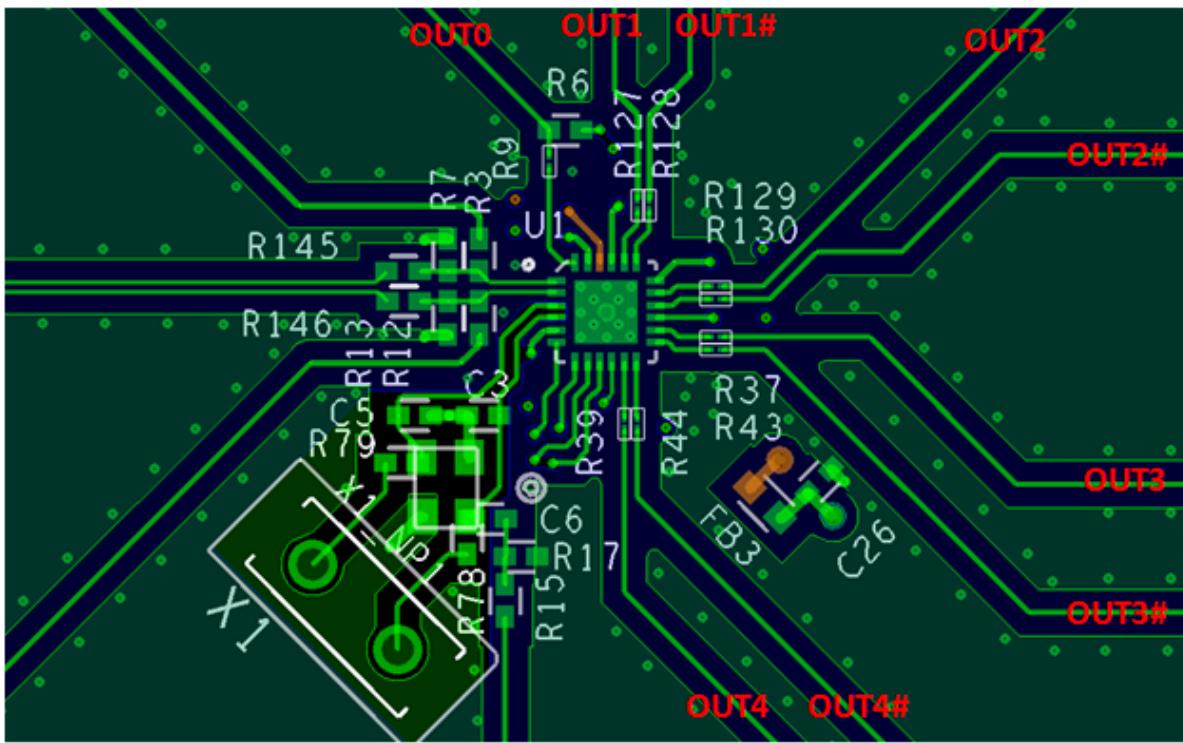

[Figure 2](#) is a snapshot of a VersaClock 6 Evaluation board layout (around VersaClock 6). All outputs are properly terminated with  $33\Omega$  series resistors, followed by  $50\Omega$  traces.

**Figure 2. Example VersaClock 6 Layout**

## 7 EMI

Whenever the subject is brought up of replacing XOs and crystals with a multiple output clock generator IC there is worry about EMI. The clock generator cannot be close to all target inputs so relatively long clock traces will be needed for some targets. Tests have shown that the clock generator IC is often a cleaner solution when IC bypassing is done properly and clock traces are laid out as transmission lines (stripline or micro strip). For more details about clock generator layout guidelines, please refer to: [www.idt.com/document/apn/909-pcb-layout-considerations-designing-idt-versaclock-5-clock-products](http://www.idt.com/document/apn/909-pcb-layout-considerations-designing-idt-versaclock-5-clock-products)

Crystal and XO devices can actually emit significant radiation. A few milliamps of RF current pass through the crystal and its traces. The crystal circuit is a resonating tank and damping of the tank should be avoided for reliable operation of the crystal oscillator. The traces to the crystal need to maintain high impedance to ground and therefore cannot be designed as transmission lines. As a result the crystal traces emit electromagnetic radiation.

With XOs the main source of radiation usually is not the clock output when the clock trace is designed properly. The main source of radiation is the power pins. Because of cost, most XOs do not have power supply bypassing inside the package and switching currents will flow in and out of the VDD and GND pins. EMI from power supply connections is proportional to the distance between the actual chip and the closest bypass capacitor. In general it is easier to place bypass capacitors closer to the actual chip with clock generator ICs than it is with an XO. As a result we often see less EMI from a clock generator solution.

VersaClock and PCIe generators have a spread spectrum feature that can help reduce EMI further by 'spreading' the clock. Spread spectrum can reduce cost even more when shielding efforts are no longer necessary to meet EMI requirements. Spread spectrum is a certain type of modulation that essentially causes a certain amount of jitter to spread the energy over a wider range of frequencies. While not suited for every application, more and more systems are designed to be able to handle a certain level of spread spectrum modulation. PCI Express is an example of such an application. With VersaClock generators we can choose the amount of spread spectrum modulation so it can be dialed in to the level the application can tolerate or what is needed to achieve certain EMI performance.

VersaClock 5 devices 5P49V5907 and 5P49V5908 combine PCI Express clock fanout with additional programmable clock outputs so the single device can provide almost all the clock needs of an application.

The 5P49V5907 can be found at:

[www.idt.com/products/clocks-timing/clock-generators-frequency-synthesizers-pll-and-differential-clocks/programmable-clock-generators-low-power-programmable-oscillators/5p49v5907-versaclock-5-low-power-programmable-clock-generator](http://www.idt.com/products/clocks-timing/clock-generators-frequency-synthesizers-pll-and-differential-clocks/programmable-clock-generators-low-power-programmable-oscillators/5p49v5907-versaclock-5-low-power-programmable-clock-generator)

## 8 Noise / Jitter Considerations

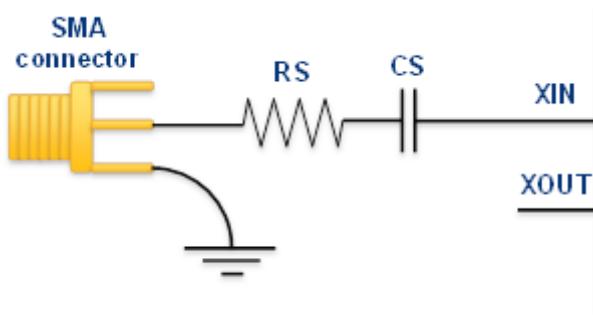

For a clock input there usually is a noise or jitter spec. So when replacing a XO that drives that clock input, the noise and/or jitter requirements usually are known. With a crystal oscillator it is very unlikely to see a noise spec in the IC datasheet unless the datasheet describes how to drive an external clock into the crystal oscillator input pin. Crystal oscillators are very low noise by nature and the noise properties are not very dependent upon the crystal manufacturer so there is no motivation for the IC manufacturer to publish the actual requirements. However, knowing the overall requirements for the system that the IC is a part of, a ballpark value for crystal oscillator noise can be predicted. When the ballpark noise requirement is in line with the clock generator noise performance, an actual test can be done using a sample of the clock generator on its evaluation board, wired into the target crystal pin. An SMA connector can be wired to the XIN pin and attached through a  $50\Omega$  coax cable to the evaluation board for the clock generator. See below example:

**Figure 3. Wiring an Evaluation Board Clock into a Crystal Pin**

Also see “Appendix A” for optional signal adjustments for optimum performance. When the evaluation board output is AC coupled, CS will not be needed. Connect the SMA connector ground as close as possible to the IC ground pin for the crystal oscillator to avoid adding in ground noise.

Differential clocks can be wired similarly, where  $50\Omega$  coax cables are replacing  $50\Omega$  traces. The original termination scheme can be preserved where possibly the evaluation board needs to be adjusted for the source side of the termination.

## Appendix A

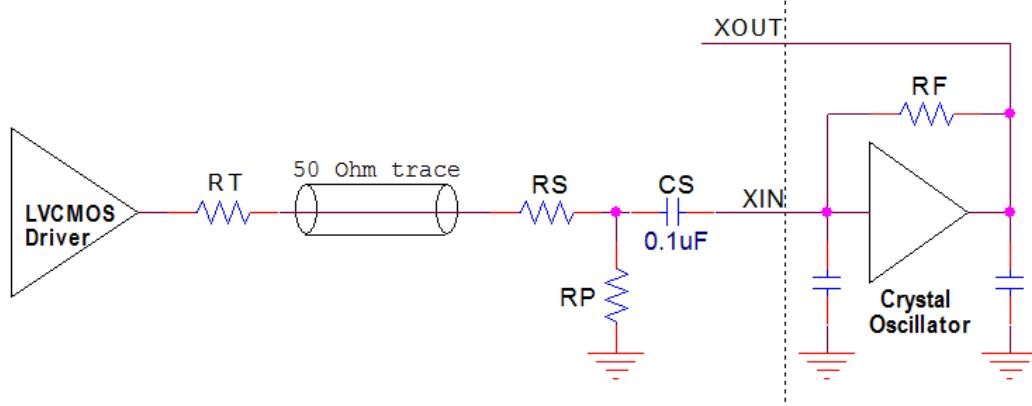

Figure 4 is a generic circuit for driving a crystal pin from a single ended LVCMOS clock output.

**Figure 4. Driving XIN from an LVCMOS Output**

On-chip crystal oscillators are commonly designed around an inverting amplifier. There are capacitors to match the load capacitance of the crystal and a feedback resistor RF for DC bias (see [Figure 1](#)). Instead of connecting a crystal between the XIN and XOUT pins, XIN can also be driven with a single ended clock signal. In that case XOUT will be left open. When using CS for AC coupling, the crystal oscillator's DC bias remains functional.

RS and RP are optional. RS on its own (no RP) can help slow down rise and fall times of the signal at XIN. The circuit is originally designed for use with a crystal where the waveform at XIN will be sinusoidal. There may be extra cross-talk into other circuits on the IC when applying fast clock edges to XIN and RS can help slow the edges down. Common values for RS are 100Ω to 1000Ω. RS is essentially in series with the 50Ω output impedance of the PCB trace. Without RS (RS=0) the rise/fall times at XIN will be dominated by the RC-time of 50Ω with the XIN input capacitance, for example  $50\Omega \times 24\text{pF} = 1.2\text{ns}$ . Adding RS=100Ω will triple the rise/fall times to 3.6ns.

A combination of RS and RP works as an attenuator in case the LVCMS clock amplitude is too large for XIN to handle. The easiest way to control the amplitude is with the LVCMS driver power supply voltage but when we have limited choice of power supply voltages or the amplitude needs to be smaller than the lowest available power supply voltage, RS and RP can be used to set certain attenuation. The attenuation can be calculated with  $V_{XIN} = V_{LVCMS} \times RP / (RP + RS + 50)$ . The output impedance of the RS & RP network controls the rise/fall times. The output impedance is RP parallel to (RS+50). For example when RS=50Ω and RP=100Ω, the amplitude at XIN will be  $V_{XIN} = V_{LVCMS} \times 100 / (50+100) = V_{LVCMS} \times 0.5$ . The output impedance of the network is  $RP // (RS+50) = 100 // (50+50) = 50\Omega$ . In case the XIN input capacitance is 24pF, the rise/fall times will be about 1.2ns.

The value of RT depends upon the output impedance of the LVCMS driver. In case the LVCMS driver output impedance is 17Ω, the value of RT needs to be 33Ω to add up to 50Ω for matching with 50Ω PCB trace impedance. RT needs to be placed near the LVCMS driver output pin. RS, RP and CS need to be placed near the XIN input pin.

## Notice

1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

(Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

(Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Disclaimer Rev.5.0-1)

## Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

## Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

[www.renesas.com/contact/](http://www.renesas.com/contact/)

## Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.