# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **Application Note**

# 78K0/Kx2-L

# Sample Program (Serial Interface IICA)

# **Slave Communication**

This document describes an operation overview of the sample program and how to use it, as well as how to set up and use serial interface IICA. In the sample program, 16 bytes of data are transmitted and received via the I<sup>2</sup>C bus in slave operation.

# Target devices

78K0/KY2-L microcontroller 78K0/KA2-L microcontroller 78K0/KB2-L microcontroller 78K0/KC2-L microcontroller

# **CONTENTS**

| CHAPTER 1 OVERVIEW                           | 3  |

|----------------------------------------------|----|

| 1.1 Primary Initial Settings                 | 4  |

| 1.2 Processing After Main Loop               | 4  |

| CHAPTER 2 CIRCUIT DIAGRAM                    | 5  |

| 2.1 Circuit Diagram                          | 5  |

| 2.2 Used Device Other than Microcontroller   | 6  |

| CHAPTER 3 SOFTWARE                           | 7  |

| 3.1 Included Files                           | 7  |

| 3.2 Internal Peripheral Functions to Be Used | 7  |

| 3.3 Initial Settings and Operation Overview  | 8  |

| 3.4 Flow Charts                              |    |

| CHAPTER 4 SETTING METHODS                    |    |

| 4.1 Setting up Serial Interface IICA         |    |

| 4.2 Software Coding Example                  | 25 |

| CHAPTER 5 RELATED DOCUMENTS                  |    |

| APPENDIX A PROGRAM LIST                      | 30 |

| APPENDIX B USING 78K0/KC2-L 44-PIN PRODUCTS  | 59 |

| APPENDIX C REVISION HISTORY                  | 60 |

Document No. U19691EJ1V0AN00 (1st edition)

Date Published September 2009 N

© NEC Electronics Corporation 2009 Printed in Japan

- The information in this document is current as of May, 2009. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets,

etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or

types are available in every country. Please check with an NEC Electronics sales representative for

availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. In addition, NEC Electronics products are not taken measures to prevent radioactive rays in the product design. When customers use NEC Electronics products with their products, customers shall, on their own responsibility, incorporate sufficient safety measures such as redundancy, fire-containment and anti-failure features to their products in order to avoid risks of the damages to property (including public or social property) or injury (including death) to persons, as the result of defects of NEC Electronics products.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and

"Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E0904E

# **CHAPTER 1 OVERVIEW**

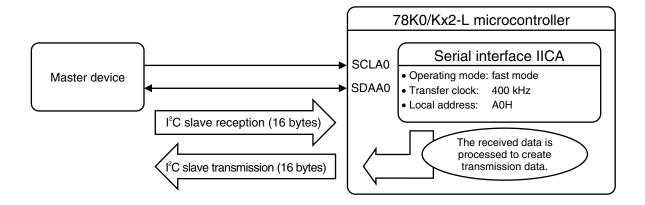

This sample program shows an example of using serial interface IICA. 16 bytes of data are transmitted and received via the I<sup>2</sup>C bus in slave operation.

#### [Operation overview]

Caution For a definition of the I<sup>2</sup>C bus, refer to the <u>78K0/Kx2-L User's Manual</u>.

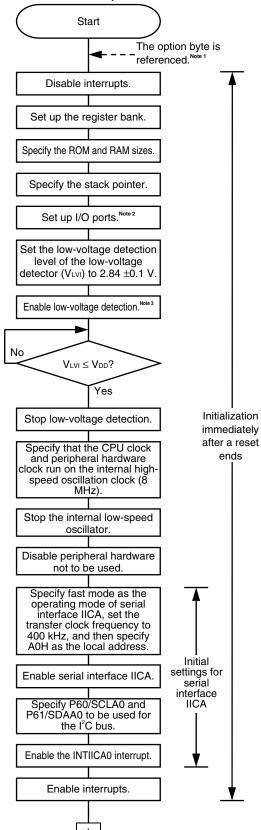

# 1.1 Primary Initial Settings

The primary initial settings are as follows:

- <Option byte settings>

- Allowing the internal low-speed oscillator to be programmed to stop

- Disabling the watchdog timer

- Setting the internal high-speed oscillation clock frequency to 8 MHz

- Disabling LVI from being started by default

- <Settings during initialization immediately after a reset ends>

- Specifying the ROM and RAM sizes

- Setting up I/O ports

- Checking whether VDD is 2.7 V or more by using the low-voltage detector<sup>Note 1</sup>

- Specifying that the CPU clock and peripheral hardware clock run on the internal high-speed oscillation clock (8 MHz)

- Stopping the internal low-speed oscillator

- Disabling peripheral hardware not to be used

- Setting up serial interface IICA

- Specifying fast mode as the operating mode and setting the transfer clock frequency to 400 kHz

- Specifying A0H as the local address

- Specifying that P60/SCLA0 and P61/SDAA0 are used for the I<sup>2</sup>C bus

- Enabling the INTIICA0 interrupt Note 2

- Enabling interrupts

- Notes 1. For details about the low-voltage detector, refer to the 78K0/Kx2-L User's Manual.

- 2. In this sample program, the HALT mode is entered while the system waits for data communication to end, and the HALT mode is exited when the INTIICA0 interrupt is generated at the end of data communication. When adding other interrupts to this sample program, make sure that these interrupts do not affect the HALT mode from being exited when the INTIICA0 interrupt occurs.

# 1.2 Processing After Main Loop

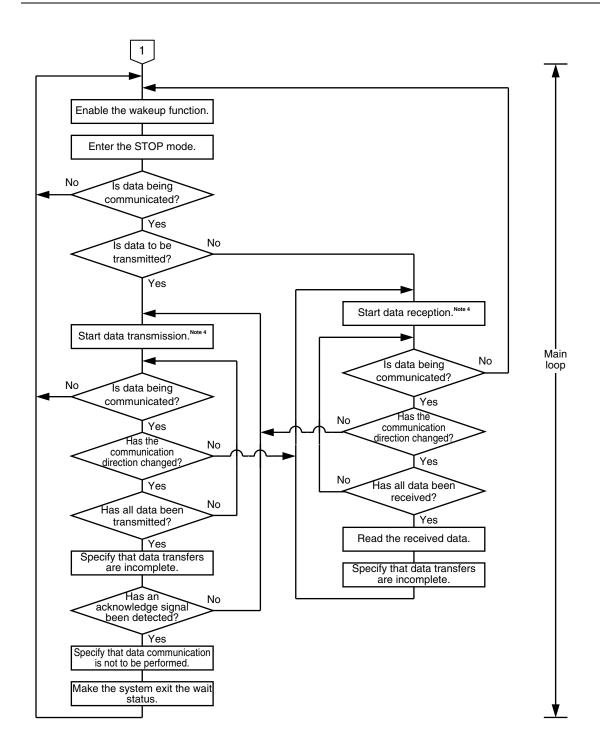

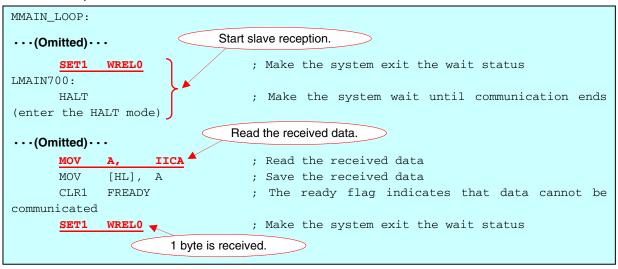

After the initial settings have been specified, the STOP mode is entered. If a local address is received, the STOP mode is exited, and then I<sup>2</sup>C communication starts. During reception, up to 16 bytes of data are received and then saved in the RAM area. During transmission, received data is processed and then transmitted.

#### **CHAPTER 2 CIRCUIT DIAGRAM**

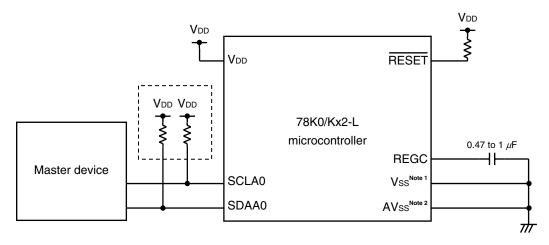

This chapter provides a circuit diagram used in this sample program.

#### 2.1 Circuit Diagram

A circuit diagram is shown below.

Notes 1. This is shared with AVss in the 78K0/KY2-L and 78K0/KA2-L.

- 2. This is provided only in the 78K0/KB2-L and 78K0/KC2-L.

- Cautions 1. Use the microcontroller at a voltage in the range of 2.94 V  $\leq$  VDD  $\leq$  5.5 V.

- 2. Connect REGC to Vss via a capacitor (0.47 to 1  $\mu$ F).

- 3. For the 78K0/KY2-L and 78K0/KA2-L, Vss is also used as the ground potential for the A/D converter. Be sure to connect Vss to a stable GND.

- 4. Make the AVss pin have the same potential as Vss and connect it directly to GND (only for the 78K0/KB2-L and 78K0/KC2-L microcontrollers).

- 5. Connect the AVREF pin directly to VDD.

- 6. Handle unused pins that are not shown in the circuit diagram as follows:

- I/O ports: Set them to output mode and leave them open (unconnected).

- Input ports: Connect them independently to VDD or Vss via a resistor.

- 7. Adjust the resistance of the pull-up resistors connected to the serial clock line and serial data bus line (enclosed in the dotted lines above) in accordance with the voltage and capacitance of the  $I^2C$  bus and the transfer clock. In this sample program, resistors with a resistance of 2 to 10  $k\Omega$  are used.

- 8. In this sample program, the P121/X1/TOOLC0 and P122/X2/EXCLK/TOOLD0 pins are used for onchip debugging.

# 2.2 Used Device Other than Microcontroller

The following device is used in addition to the microcontroller:

# (1) Master device

A device that performs master transmission and reception is used as the other party of I<sup>2</sup>C slave communication.

#### **CHAPTER 3 SOFTWARE**

This chapter describes the files included in the compressed file to be downloaded, internal peripheral functions of the microcontroller to be used, and initial settings and provides an operation overview of the sample program and the flow charts.

# 3.1 Included Files

The following table shows the files included in the compressed file to be downloaded.

| File Name                                                        | Description                                                                                                                                                                                                  | Compressed (*.2 | zip) File Included |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|

|                                                                  |                                                                                                                                                                                                              |                 | ₽M<br>0 32         |

| main.asm (Assembly language version) main.c (C language version) | Source file for hardware initialization processing and main processing of microcontroller                                                                                                                    | Note            | Note               |

| op.asm                                                           | Assembler source file for setting the option byte (This file is used for setting up the watchdog timer and internal low-speed oscillator and selecting the internal high-speed oscillation clock frequency.) | •               | •                  |

| Kx2-L_IICAS.prw                                                  | Work space file for integrated development environment PM+                                                                                                                                                   |                 | •                  |

| Kx2-L_IICAS.prj                                                  | Project file for integrated development environment PM+                                                                                                                                                      |                 | •                  |

Note "main.asm" is included with the assembly language version, and "main.c" with the C language version.

Remark

: Only the source file is included.

: The files to be used with integrated development environment PM+ are included.

#### 3.2 Internal Peripheral Functions to Be Used

The following internal peripheral functions of the microcontroller are used in this sample program.

# (1) Peripheral hardware

Serial interface IICA: Performs l<sup>2</sup>C slave communication.

Low-voltage detector: Checks whether VDD is 2.7 V or more.

### (2) Pin functions

SCLA0/P60: Used as the I<sup>2</sup>C serial clock pin.

SDAA0/P61: Used as the I<sup>2</sup>C serial data bus pin.

#### 3.3 Initial Settings and Operation Overview

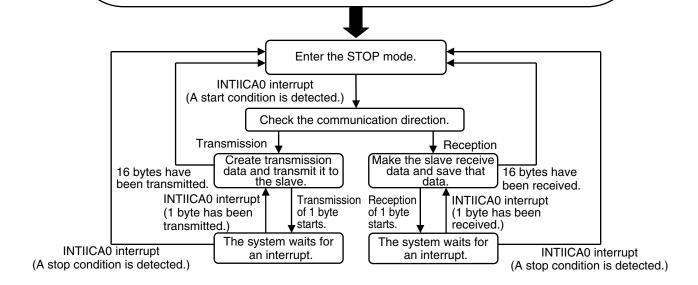

In this sample program, initial settings including the selection of the clock frequency, setting of the I/O ports, and setting of serial interface IICA are performed. After the initial settings have been specified, the STOP mode is entered. If a local address is received, the STOP mode is exited, and then I<sup>2</sup>C communication starts. During reception, up to 16 bytes of data are received and then saved in the RAM area. During transmission, received data is processed and then transmitted.

The details are described in the state transition diagram shown below.

#### Initial settings

- <Option byte settings>

- Allowing the internal low-speed oscillator to be programmed to stop

- Disabling the watchdog timer

- Setting the internal high-speed oscillation clock frequency to 8 MHz

- Disabling LVI from being started by default

<Settings during initialization immediately after a reset ends>

- Specifying the ROM and RAM sizes

- Setting up I/O ports

- Checking whether VDD is 2.7 V or more by using the low-voltage detector

- Specifying that the CPU clock and peripheral hardware clock run on the internal high-speed oscillation clock (8 MHz)

- Stopping the internal low-speed oscillator

- Disabling peripheral hardware not to be used

- Setting up serial interface IICA

- Specifying fast mode as the operating mode and setting the transfer clock frequency to 400 kHz

- Specifying A0H as the local address

- Specifying that P60/SCLA0 and P61/SDAA0 are used for the I2C bus

- Enabling the INTIICA0 interrupt

- Enabling interrupts

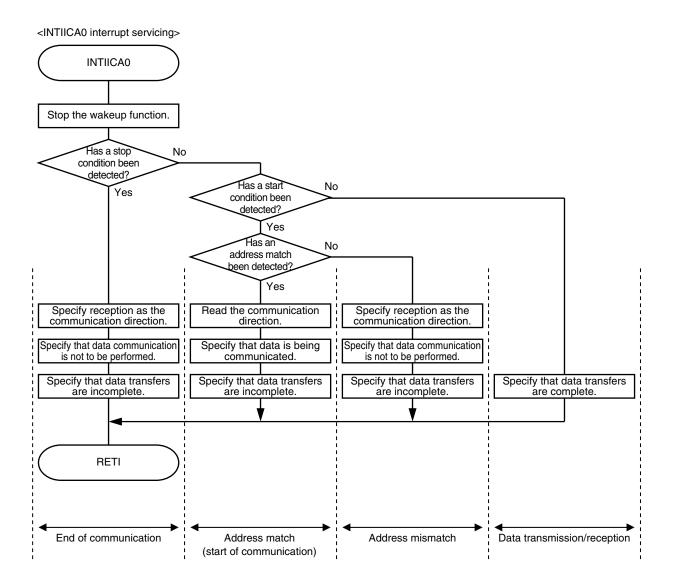

#### 3.4 Flow Charts

The flow charts for the sample program are shown below.

<Initialization immediately after a reset ends>

- **Notes 1.** The option byte is automatically referenced by the microcontroller immediately after a reset ends. In this sample program, the following settings are specified using the option byte:

- Allowing the internal low-speed oscillator to be programmed to stop

- Disabling the watchdog timer

- Setting the internal high-speed oscillation clock frequency to 8 MHz

- Disabling LVI from being started by default

- 2. P60/SCLA0 and P61/SDAA0 are specified as input ports so that port output does not affect the I<sup>2</sup>C bus.

- 3. The low-voltage detector is enabled, and then the system is made to wait at least 10  $\mu$ s until the low-voltage detector stabilizes.

- **4.** The HALT mode is entered during communication, and then exited when the INTIICA0 interrupt occurs at the end of communication.

# **CHAPTER 4 SETTING METHODS**

This chapter describes how to set up serial interface IICA and provides software coding examples.

For other initial settings, refer to the <u>78K0/Kx2-L Sample Program (Initial Settings) LED Lighting Switch Control Application Note.</u>

For how to set registers, refer to the <u>78K0/Kx2-L User's Manual</u>.

For assembler instructions, refer to the <u>78K/0 Series Instructions User's Manual</u>.

# 4.1 Setting up Serial Interface IICA

Serial interface IICA uses the following eight registers:

- IICA control register 0 (IICACTL0)

- IICA flag register 0 (IICAF0)

- IICA control register 1 (IICACTL1)

- IICA low-level width setting register (IICWL)

- IICA high-level width setting register (IICWH)

- Port output mode register 6 (POM6)

- Port mode register 6 (PM6)

- Port register 6 (P6)

# [Example of the setup procedure when using serial interface IICA for I<sup>2</sup>C slave communication]

(The same procedure is used in the sample program.)

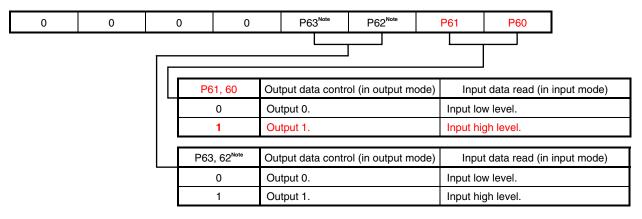

- <1> Set bits 0 and 1 (PM60 and PM61) of PM6 to 1 (input mode). Note

- <2> Set up the transfer clock by using IICWL and IICWH.

- <3> Specify the local address by using SVA0.

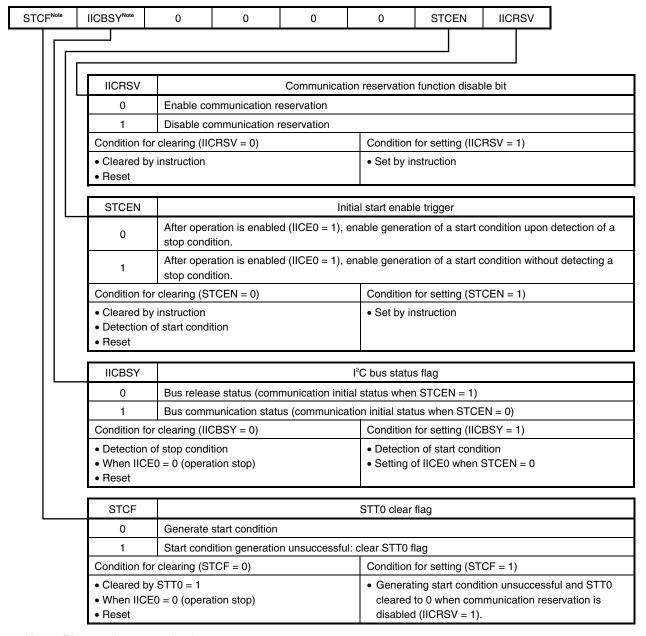

- <4> Specify the conditions for starting I<sup>2</sup>C communication by using bit 1 (STCEN) of IICAF0.

- <5> Set bit 2 (ACKE0) of IICACTL0 to 1 (to enable acknowledge signals).

- <6> Set bit 3 (WTIM0) of IICACTL0 to 1 (to generate an interrupt request at the falling edge of the ninth clock cycle).

- <7> Set bit 4 (SPIE0) of IICACTL0 to 1 (to enable an interrupt request to be generated when a stop condition is detected).

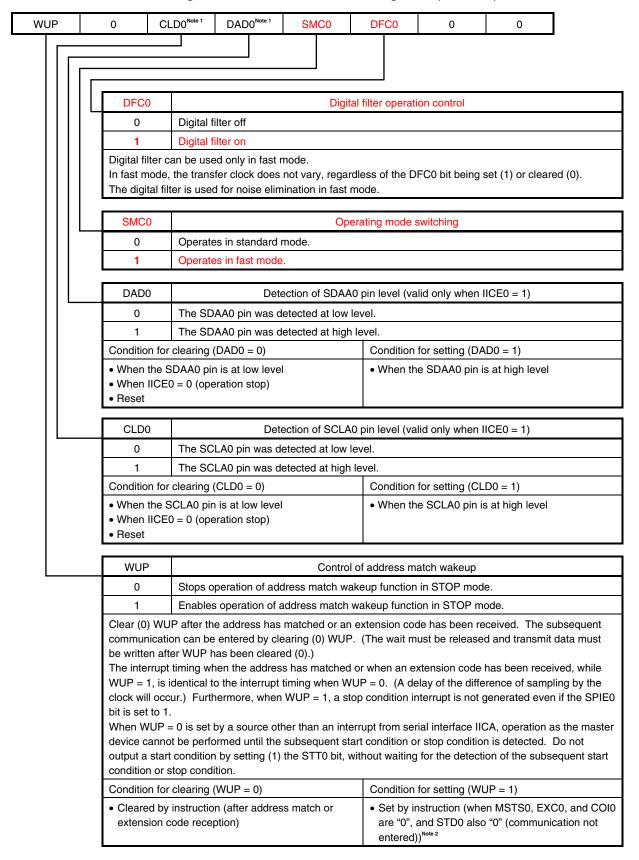

- <8> Specify the operating mode and operation of the digital filter by using bit 3 (SMC0) and bit 2 (DFC0) of IICACTL1, respectively.

- <9> Set bit 7 (IICE0) of IICACTL0 to 1 (to enable the I2C bus).

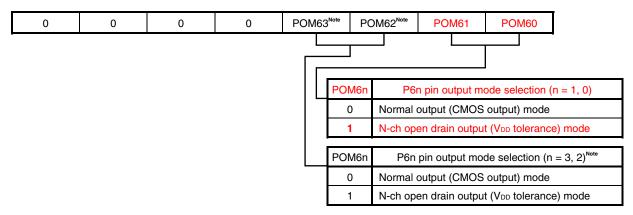

- <10> Set bits 0 and 1 (POM60 and POM61) of POM6 to 1 (N-ch open-drain output (VDD withstand voltage) mode).

- <11> Set bits 0 and 1 (P60 and P61) of P6 to 1 (to output 1).

- <12> Clear bits 0 and 1 (PM60 and PM61) of PM6 to 0 (output mode).

- <13> Clear the INTIICA0 interrupt request (clear IICAIF0 to 0).

- <14> Enable the INTIICA0 interrupt (clear IICAMK0 to 0).

- <15> Enable interrupts (EI).

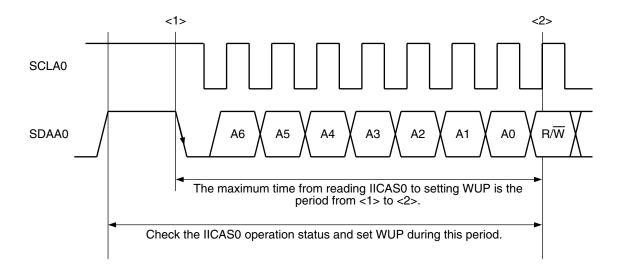

- <16> Set bit 7 (WUP) of IICACTL1 to 1 (to enable the wakeup function when an address match occurs in the STOP mode).

Note P60/SCLA0 and P61/SDAA0 are specified as input ports so that port output does not affect the I<sup>2</sup>C bus.

# (1) IICA control register 0 (IICACTL0)

This register is used to enable/stop I<sup>2</sup>C operations, set wait timing, and set other I<sup>2</sup>C operations.

Figure 4-1. Format of IICA Control Register 0 (IICACTL0) (1/4)

| IICE0 | LREL0                                                                                      | WREL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SPIE0                                                                       | WTIM0                                                                    | ACKE0                                                             | STT0                | SPT0                                                                  |

|-------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------|

|       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                          |                                                                   |                     |                                                                       |

|       | WREL0 <sup>Note</sup>                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                             |                                                                          | Wait cancellat                                                    | ion                 |                                                                       |

|       | 0                                                                                          | Do not car                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ncel wait                                                                   |                                                                          | vait caricellat                                                   | 1011                |                                                                       |

|       | 1                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | a is automatica                                                          | ally cleared afte                                                 | er wait is cance    | led.                                                                  |

|       |                                                                                            | L0 is set (wai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | it canceled) du                                                             | ring the wait p                                                          |                                                                   | th clock pulse      | in the transmission status                                            |

|       | , ,                                                                                        | or clearing (W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                             | <u> </u>                                                                 | 1                                                                 | r setting (WRE      | L0 = 1)                                                               |

|       | <ul><li>Automation</li><li>Reset</li></ul>                                                 | cally cleared a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | fter execution                                                              |                                                                          | Set by instr                                                      | ruction             |                                                                       |

|       | LREL0 <sup>Note 1</sup>                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | Exit                                                                     | from commun                                                       | ications            |                                                                       |

|       | 0 Normal operation                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                          |                                                                   |                     |                                                                       |

|       | 1                                                                                          | automaticality uses in The SCLAThe follow cleared to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ally cleared to<br>clude cases in<br>0 and SDAA0<br>ring flags of IIC<br>0. | 0 after being e<br>which a locall<br>lines are set to<br>A control regis | xecuted.<br>y irrelevant ext<br>o high impedar<br>ster 0 (IICACTI | ension code ha      | This setting is as been received. atus register 0 (IICAS0) are • STD0 |

|       | <ul><li>entry condi</li><li>After a sto</li><li>An address</li><li>Condition for</li></ul> | y mode following exit from communications remains in effect until the following communications are met.  pp condition is detected, restart is in master mode.  ss match or extension code reception occurs after the start condition.  pr clearing (LREL0 = 0)  Condition for setting (LREL0 = 1)  eally cleared after execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                             |                                                                          |                                                                   |                     |                                                                       |

|       |                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                             |                                                                          |                                                                   |                     |                                                                       |

|       | IICE0                                                                                      | The state of the s |                                                                             |                                                                          |                                                                   |                     |                                                                       |

|       | 0 Stop operation. Reset the IICA status                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | register 0 (IICA                                                         | AS0) <sup>Note 2</sup> . Stop                                     | internal operation. |                                                                       |

|       | 1 Enable operation.                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             | AO l'acce and at high level                                              |                                                                   |                     |                                                                       |

|       | Be sure to set this bit (1) while the SCLA0 and SDAA                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                          |                                                                   |                     |                                                                       |

|       |                                                                                            | or clearing (IIC<br>by instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SE0 = 0)                                                                    |                                                                          | Condition for setting (IICE0 = 1)  • Set by instruction           |                     |                                                                       |

- **Notes 1.** The signal of this bit is invalid while IICE0 is 0.

- 2. The IICAS0 register, the STCF and IICBSY bits of the IICAF0 register, and the CLD0 and DAD0 bits of the IICACTL1 register are reset.

Caution The start condition is detected immediately after I<sup>2</sup>C is enabled to operate (IICE0 = 1) while the SCLA0 line is at high level and the SDAA0 line is at low level. Immediately after enabling I<sup>2</sup>C to operate (IICE0 = 1), set LREL0 (1) by using a 1-bit memory manipulation instruction.

**Remark** The values written in red in the above figure are specified in this sample program.

Figure 4-1. Format of IICA Control Register 0 (IICACTL0) (2/4) IICE0 SPIE0 **WTIM0** ACKE0 LREL0 WREL0 STT0 SPT0 ACKFO<sup>Notes 1, 2</sup> Acknowledgment control Disable acknowledgment. 0 Enable acknowledgment. During the ninth clock period, the SDAA0 line is set to low level. Condition for clearing (ACKE0 = 0) Condition for setting (ACKE0 = 1) · Cleared by instruction · Set by instruction Reset WTIMO<sup>Note 1</sup> Control of wait and interrupt request generation Interrupt request is generated at the eighth clock's falling edge. Master mode: After output of eight clocks, clock output is set to low level and wait is set. 0 Slave mode: After input of eight clocks, the clock is set to low level and wait is set for master device. Interrupt request is generated at the ninth clock's falling edge. Master mode: After output of nine clocks, clock output is set to low level and wait is set. 1 Slave mode: After input of nine clocks, the clock is set to low level and wait is set for master device. An interrupt is generated at the falling edge of the ninth clock during address transfer independently of the setting of this bit. The setting of this bit is valid when the address transfer is completed. When in master mode, a wait is inserted at the falling edge of the ninth clock during address transfers. For a slave device that has received a local address, a wait is inserted at the falling edge of the ninth clock after an acknowledge (ACK) is issued. However, when the slave device has received an extension code, a wait is inserted at the falling edge of the eighth clock. Condition for clearing (WTIM0 = 0) Condition for setting (WTIM0 = 1) · Cleared by instruction · Set by instruction Reset SPIE0<sup>Note 1</sup> Enable/disable generation of interrupt request when stop condition is detected

|   | 0                         | Disable              |                                   |

|---|---------------------------|----------------------|-----------------------------------|

|   | 1                         | Enable               |                                   |

|   | Condition for             | clearing (SPIE0 = 0) | Condition for setting (SPIE0 = 1) |

| I | • Cleared by              | instruction          | Set by instruction                |

|   | <ul> <li>Reset</li> </ul> |                      |                                   |

| • | •                         |                      |                                   |

**Notes 1.** The signal of this bit is invalid while IICE0 is 0. Set this bit during that period.

2. The set value is invalid during address transfer and if the code is not an extension code.

When the device serves as a slave and the addresses match, an acknowledgment is generated regardless of the set value.

**Remark** The values written in red in the above figure are specified in this sample program.

Figure 4-1. Format of IICA Control Register 0 (IICACTL0) (3/4)

|  | IICE0 | LREL0 | WREL0 | SPIE0 | WTIMO | ACKE0 | STT0 | SPT0 |

|--|-------|-------|-------|-------|-------|-------|------|------|

|--|-------|-------|-------|-------|-------|-------|------|------|

| STT0 <sup>Note</sup>                                                           | Start                                                                                                                                                                                                                                                                                                      | condition trigger                                                                                                                                                    |  |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0                                                                              | Do not generate a start condition.                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |  |

| 1                                                                              | is changed from high level to low level and the amount of time has elapsed, SCLA0 is changed. When a third party is communicating:  • When communication reservation function Functions as the start condition reservation condition after the bus is released.  • When communication reservation function | is enabled (IICRSV = 0) In flag. When set to 1, automatically generates a start is disabled (IICRSV = 1) In (1) to STT0 is cleared. No start condition is generated. |  |

| <ul><li>For mas been cle</li><li>For mas during th</li><li>Cannot be</li></ul> | ared to 0 and slave has been notified of final rec                                                                                                                                                                                                                                                         | erated normally during the acknowledge period. Set to 1 k.                                                                                                           |  |

|                                                                                | clearing (STT0 = 0)                                                                                                                                                                                                                                                                                        | Condition for setting (STT0 = 1)                                                                                                                                     |  |

| reservation  Cleared by Cleared aff device Cleared by                          | setting STT0 to 1 while communication is prohibited. loss in arbitration er start condition is generated by master  LREL0 = 1 (exit from communications) 0 = 0 (operation stop)                                                                                                                            | Set by instruction                                                                                                                                                   |  |

Note The signal of this bit is invalid while IICE0 is 0.

Remarks 1. Bit 1 (STT0) becomes 0 when it is read after data setting.

2. IICRSV: Bit 0 of IICA flag register 0 (IICAF0)