-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

71V67603

circleアクティブサンプル入手可能3.3V 256K x 36 Synchronous 3.3V I/O PipeLined SRAM

ページセクションへ移動:

arrow_drop_down

概要

説明

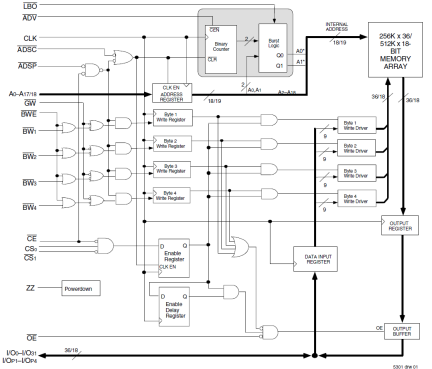

The 71V67603 3.3V CMOS SRAM is organized as 256K x 36. The 71V67603 SRAM contains write, data, address and control registers. The burst mode feature offers the highest level of performance to the system designer, as it can provide four cycles of data for a single address presented to the SRAM.The order of these three addresses are defined by the internal burst counter and the LBO input pin.

特長

- High system speed 166MHz (3.5ns clock access time)

- LBO input selects interleaved or linear burst mode

- Self-timed write cycle with global write control (GW), byte

- write enable (BWE), and byte writes (BWx)

- 3.3V core power supply

- Power down controlled by ZZ input

- 3.3V I/O supply (VDDQ)

- Available in 100-pin TQFP, 119-pin BGA and 165 fpBGA packages

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

購入するにはログインまたは登録してください

ログインしてカートに追加

Processing table

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product