-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

83940DI

circle廃止品Low Skew,1-to-18 LVPECL-to-LVCMOS/LVTTL Fanout Buffer

概要

説明

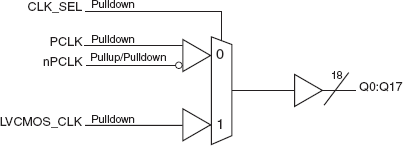

The 83940DI is a low skew, 1-to-18 LVPECL- to-LVCMOS/LVTTL Fanout Buffer. The 83940DI has two selectable clock inputs. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The LVCMOS_CLK can accept LVCMOS or LVTTL input levels. The low impedance LVCMOS/LVTTL outputs are designed to drive 50Ω series or parallel terminated transmission lines. The 83940DI is characterized at full 3.3V and 2.5V or mixed 3.3V core, 2.5V output operating supply modes. Guaranteed output and part-to-part skew characteristics make the 83940DI ideal for those clock distribution applications demanding well defined performance and repeatability.

特長

- Eighteen LVCMOS/LVTTL outputs

- Selectable LVCMOS_CLK or LVPECL clock inputs

- PCLK, nPCLK pair can accept the following differential input levels: LVPECL, CML, SSTL

- LVCMOS_CLK supports the following input types: LVCMOS or LVTTL

- Maximum output frequency: 250MHz

- Output skew: 150ps (maximum)

- Part-to-part skew: 750ps (maximum)

- Operating supply modes:

Core/Output

3.3V/3.3V

3.3V/2.5V

2.5V/2.5V - -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

ご購入 / サンプル |

|

|---|---|---|---|---|---|---|

| 型名 | ||||||

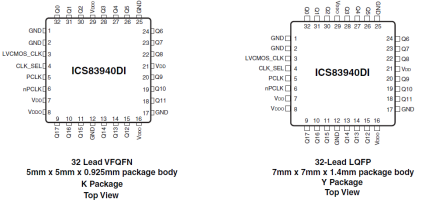

| VFQFPN | 32 | I | Yes | Tray | ||

| VFQFPN | 32 | I | Yes | Reel | ||

| TQFP | 32 | I | Yes | Tray | ||

| TQFP | 32 | I | Yes | Reel |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product