## Limiting IEEE 1588 Slave Clock Wander Caused by Packet Delay Variation

*Michael Rupert, Principle System Design Engineer, Data Center Business Division*

### Abstract

This white paper compares two IEEE 1588 slave clock implementations for effectiveness in limiting wander caused by packet delay variation (PDV). The implementations are:

- An IEEE 1588 slave clock that includes a PDV filter in the servo loop

- An IEEE 1588 slave clock that includes a low-pass filter in the servo loop

### Introduction

IEEE 1588 defines the Precision Time Protocol (PTP) that enables accurate synchronization over packet switched networks (PSN). For telecom frequency synchronization applications, PTP slave clocks must meet ITU-T G.8261 network limits for clock wander.

The PTP telecom profile for frequency synchronization (ITU-T G.8265.1) assumes that PTP masters and PTP slaves are used in PSNs that are not designed to support PTP. These PTP unaware networks can impose high packet delay variation (PDV) on PTP packets. Because PDV is a cause of wander on PTP slave clocks, PTP slave clock servos must be PDV tolerant if G.8261 wander limits are to be met.

This white paper compares two PTP slave clock implementations for effectiveness in limiting wander caused by PDV; the implementations are (1) a PTP slave clock that includes a PDV filter in the servo loop and (2) a PTP slave clock that includes a low-pass filter in the servo loop. The PTP slave clock with the PDV filter performs best with peak wander nearly 60 times lower than the PTP slave clock with a low-pass filter. Both implementations use the same local oscillator.

The Renesas PTP Clock Manager software includes a PTP clock servo with a PDV filter and other functionality that meets global ITU-T synchronization recommendations for telecom applications. The PTP Clock Manager is available under license from Renesas for use with Renesas timing products., and can be used with any IEEE 1588 protocol stack.

## Contents

|                                                                                                                       |   |

|-----------------------------------------------------------------------------------------------------------------------|---|

| <b>Abstract</b> .....                                                                                                 | 1 |

| <b>Introduction</b> .....                                                                                             | 1 |

| <b>Contents</b> .....                                                                                                 | 2 |

| <b>Definitions</b> .....                                                                                              | 3 |

| Clock .....                                                                                                           | 3 |

| Clock Signal .....                                                                                                    | 3 |

| Jitter .....                                                                                                          | 3 |

| Wander .....                                                                                                          | 3 |

| MTIE .....                                                                                                            | 3 |

| <b>Synchronization Standards</b> .....                                                                                | 3 |

| IEEE 1588 - Precision Time Protocol .....                                                                             | 3 |

| ITU-T G.8261 - Timing and Synchronization Aspects in Packet Networks .....                                            | 3 |

| ITU-T G.8265.1 - PTP Telecom Profile for Frequency Synchronization .....                                              | 3 |

| ITU-T G.8275.2 - PTP Telecom Profile for Phase/Time Synchronization with Partial Timing Support from the Network..... | 3 |

| <b>Basic Synchronization for a PTP Slave Clock</b> .....                                                              | 4 |

| <b>Packet Delay Variation</b> .....                                                                                   | 5 |

| <b>PDV Mitigation by the Network</b> .....                                                                            | 5 |

| <b>Limiting PTP Slave Clock Wander with a PDV Filter</b> .....                                                        | 5 |

| <b>Limiting PTP Slave Clock Wander with a Low-Pass Filter</b> .....                                                   | 6 |

| <b>Conclusion</b> .....                                                                                               | 9 |

| <b>Notes</b> .....                                                                                                    | 9 |

| <b>Revision History</b> .....                                                                                         | 9 |

## Definitions

### Clock

IEEE 1588 defines a clock as follows: A device that can provide a measurement of the passage of time since a defined epoch.

### Clock Signal

IEEE 1588 defines a clock signal as follows: A physical signal that has periodic events. The periodic events mark the significant instants at which a time counter is incremented. The clock signal is characterized by its frequency and phase.

### Jitter

For telecom applications, phase noise with frequencies of 10Hz and above is considered jitter.

### Wander

For telecom applications, phase noise with frequencies below 10Hz is considered wander.

### MTIE

Maximum time interval error (MTIE) charts display the largest phase change accumulated by a clock during any of a set of equal observation intervals within a measurement period. MTIE charts typically display MTIE on the vertical axis versus observation intervals on the horizontal axis. MTIE is often used to specify limits for wander and phase transients. ITU-T G.810<sup>0</sup> includes a formal definition of MTIE.

## Synchronization Standards

### IEEE 1588 - Precision Time Protocol

IEEE 1588<sup>0</sup> defines a protocol, the Precision Time Protocol (PTP), that enables accurate synchronization over packet switched networks (PSN). IEEE 1588 provides for profiles that fit the needs of specific industries or applications and support interoperability among devices using the same profile. IEEE 1588 does not specify synchronization performance requirements, and it does not specify PTP slave clock architectures.

### ITU-T G.8261 - Timing and Synchronization Aspects in Packet Networks

ITU-T G.8261<sup>0</sup> defines frequency synchronization aspects in packet networks including the network limits for wander at telecom synchronization interfaces. The network limits apply to synchronization interfaces whether they are derived from the physical layer (for example, from synchronous Ethernet) or from PTP over a PSN.

### ITU-T G.8265.1 - PTP Telecom Profile for Frequency Synchronization

ITU-T G.8265.1<sup>0</sup> defines the PTP telecom profile for frequency synchronization and specifies the required IEEE 1588 functions that ensure network element interoperability for the delivery of frequency. This profile addresses the case where the PTP masters and slaves will be used in networks where there is no PTP support in any intermediate node between the PTP master and the PTP slave.

### ITU-T G.8275.2 - PTP Telecom Profile for Phase/Time Synchronization with Partial Timing Support from the Network

ITU-T G.8275.2<sup>0</sup> defines the PTP telecom profile for phase/time synchronization with partial timing support from the network. This telecom profile is out of scope for this whitepaper, but it is mentioned because it covers applications that can benefit from packet delay variation (PDV) filtering. Networks intended for G.8275.2 should exhibit lower levels of PDV than networks intended for G.8265.1.

## Basic Synchronization for a PTP Slave Clock

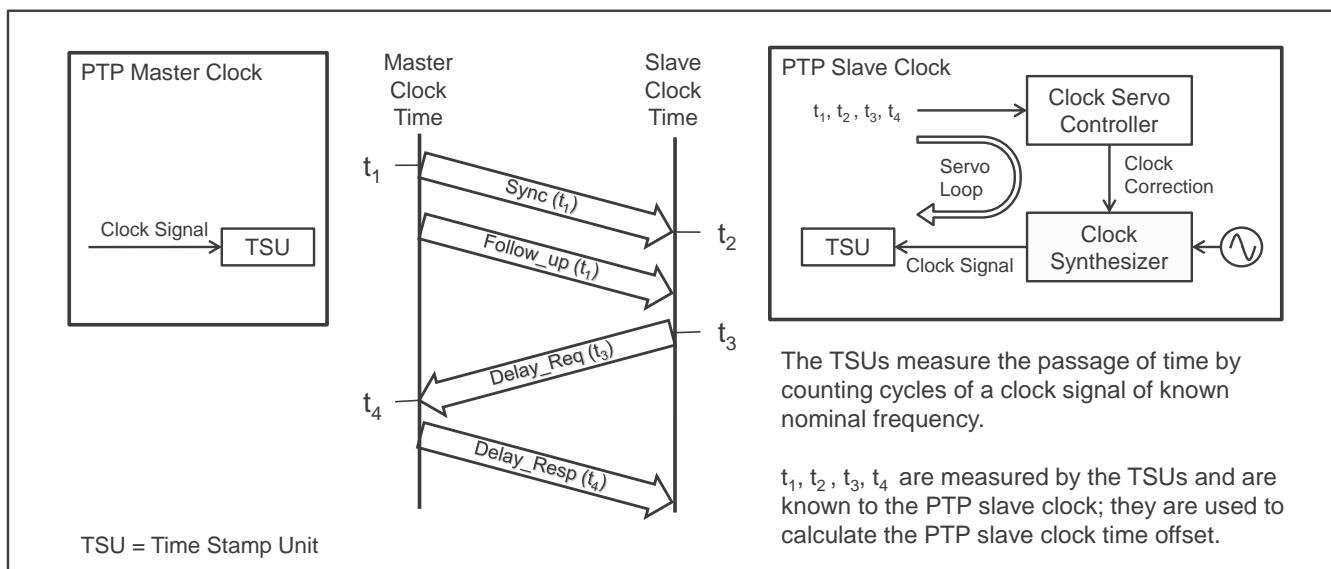

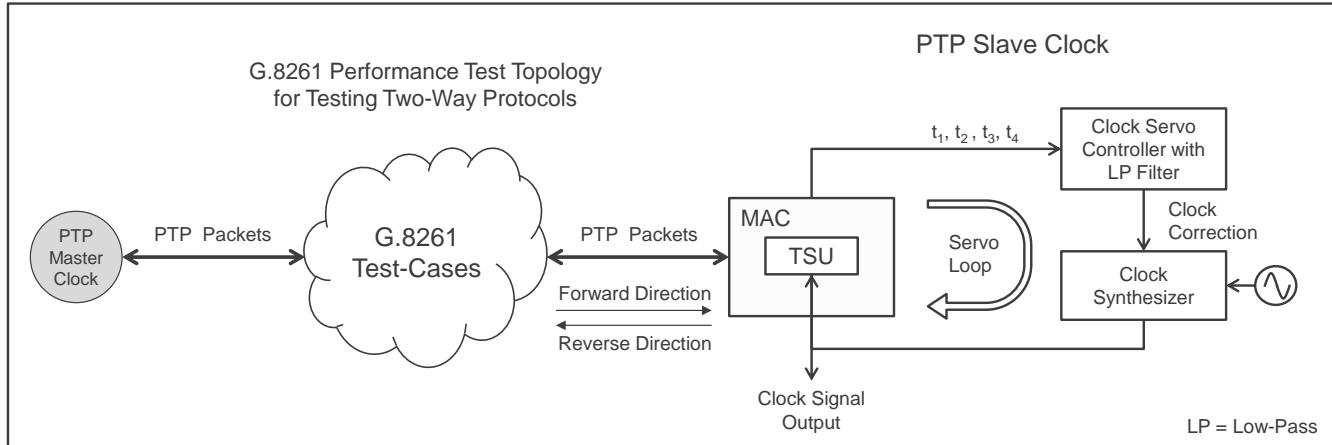

Figure 1 shows the basic PTP timing message exchange between a PTP master and a PTP slave; also shown is a PTP slave clock implemented as a servo loop with a clock servo controller (clock servo). Under ideal conditions, the clock servo can calculate the time offset of its local time stamp unit (TSU) versus the TSU of the master using Equation 1. The time offset is digitally compensated by the clock servo; afterwards, the frequency of the PTP slave clock signal is periodically adjusted to keep the time offset near zero. Therefore, the PTP slave clock is synchronized and locked to the PTP master clock.

**Equation 1. PTP Slave Clock Time Offset** =  $\frac{(t_2 - t_1) - (t_4 - t_3)}{2}$

PDV gives rise to phase noise, jitter/wander, on PTP slave clocks. Equation 1 is accurate if the packet delay (transmission time) of the Sync packet is equal to the packet delay of the associated Delay\_Req packet<sup>0</sup>. If the two packet delays differ, then the calculated time offset will include an error equal to half the difference. If the Sync packet and Delay\_Req packet delays change with respect to each other over time, then the PTP slave clock signal will exhibit jitter/wander in response.

Figure 1. Basic Precision Time Protocol Timing Packet Exchange

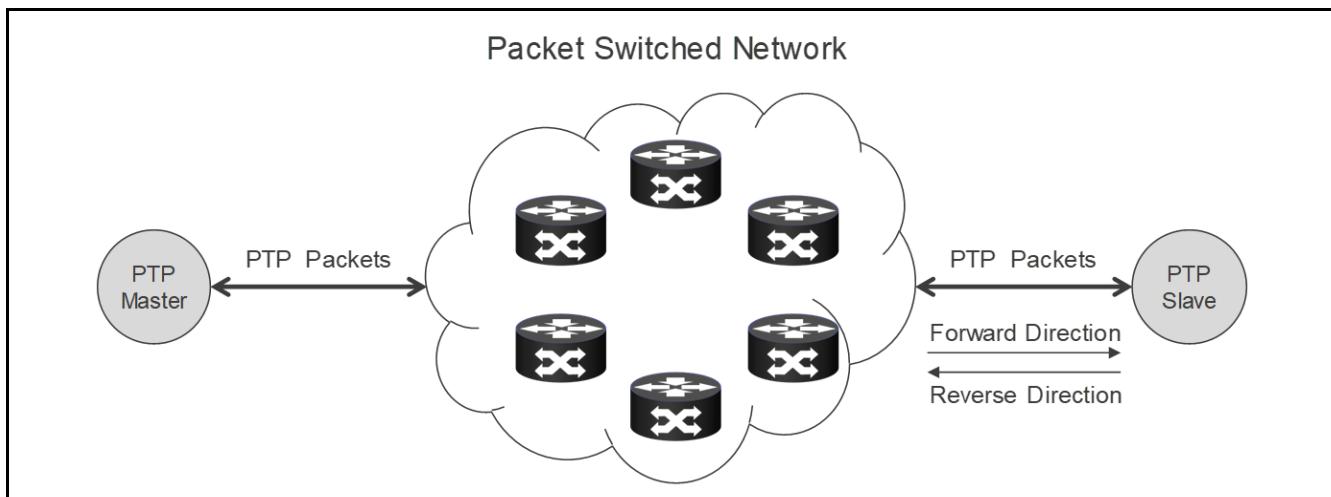

Figure 2. PTP over a Packet Switched Network

## Packet Delay Variation

Figure 2 illustrates a PSN with multiple switching nodes. PTP packets traversing such a network are subject to delays at each switching node; the total packet delay varies from packet to packet depending on the path taken through the network and on the direction of transmission (forward or reverse)<sup>0</sup>.

A sequence of PTP packets transmitted over a PSN exhibit PDV that depends on the conditions encountered by each packet in the switching nodes and in the overall network. A partial list of causes of PDV in a switching node includes processing, statistical multiplexing, buffering, port contention, and dropped packets. A partial list of causes of PDV for a network includes route diversity and misordered packets.

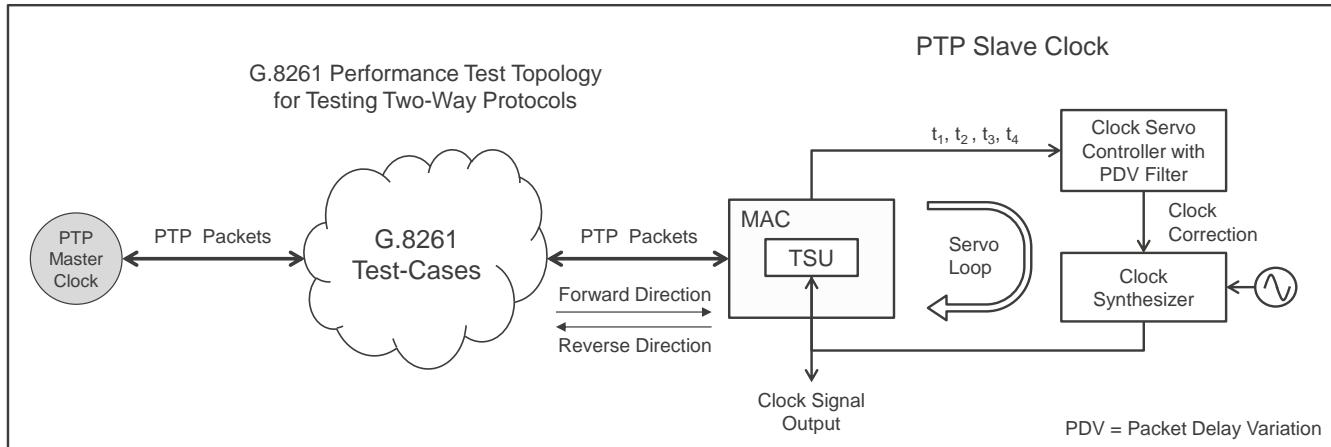

G.8261 defines seventeen test-cases that model PSN conditions and associated PDV. These test cases are intended to assist in the acquisition of performance characteristics used to establish benchmarking results. Test-cases 12 to 17 are intended for two-way protocols like IEEE 1588. The performance test topology for two-way protocols includes a chain of ten switching nodes between the PTP master clock and the PTP slave clock with traffic generators injecting interfering traffic in the forward and reverse directions.

**Table 1. G.8261 Test-Cases TC-12 to TC-17**

| Test-Case | Network Conditions Modeled by Test-Case                             |

|-----------|---------------------------------------------------------------------|

| TC-12     | "Static" packet load                                                |

| TC-13     | Sudden large, and persistent, changes in network load               |

| TC-14     | Slow change in network load over an extremely long (24 hour) period |

| TC-15     | Temporary network outages and restoration for varying periods       |

| TC-16     | Temporary network congestion and restoration for varying periods    |

| TC-17     | Routing changes caused by failures in the network                   |

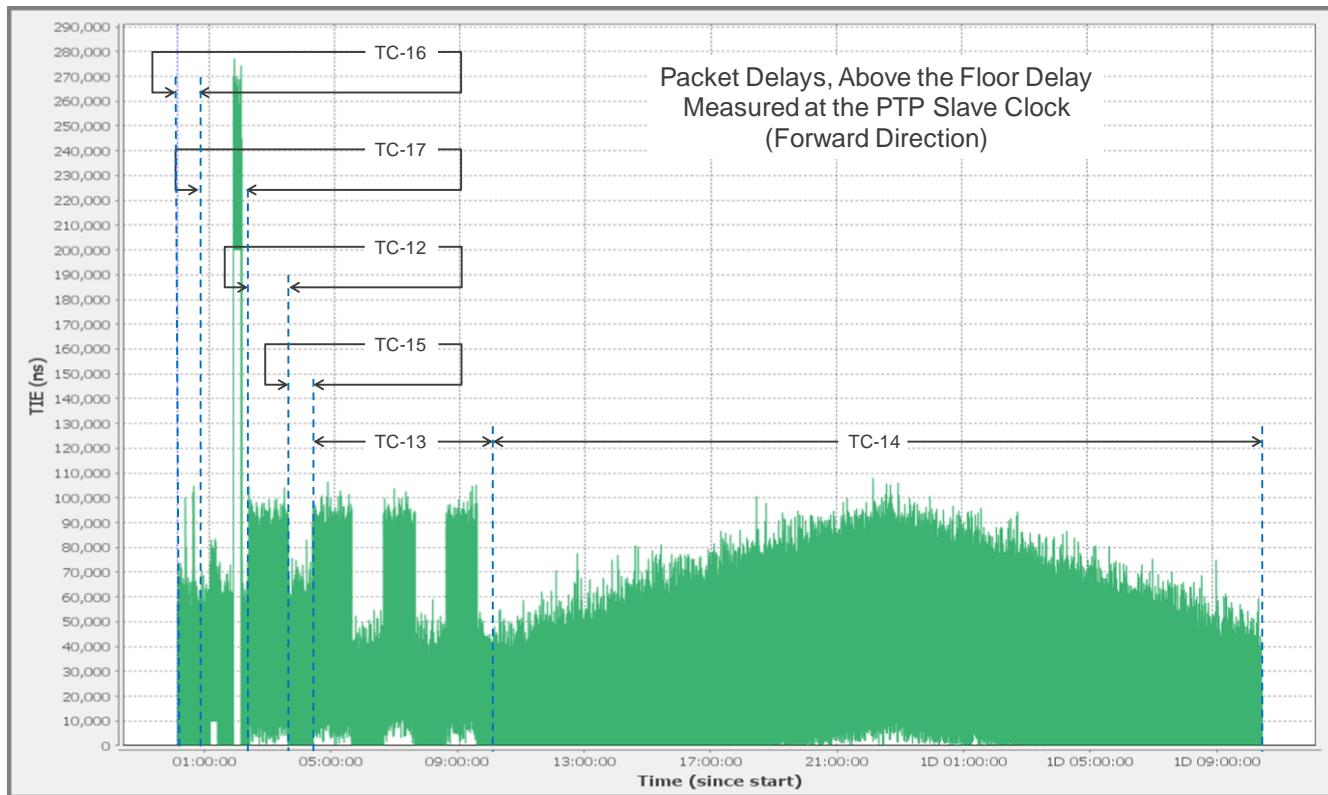

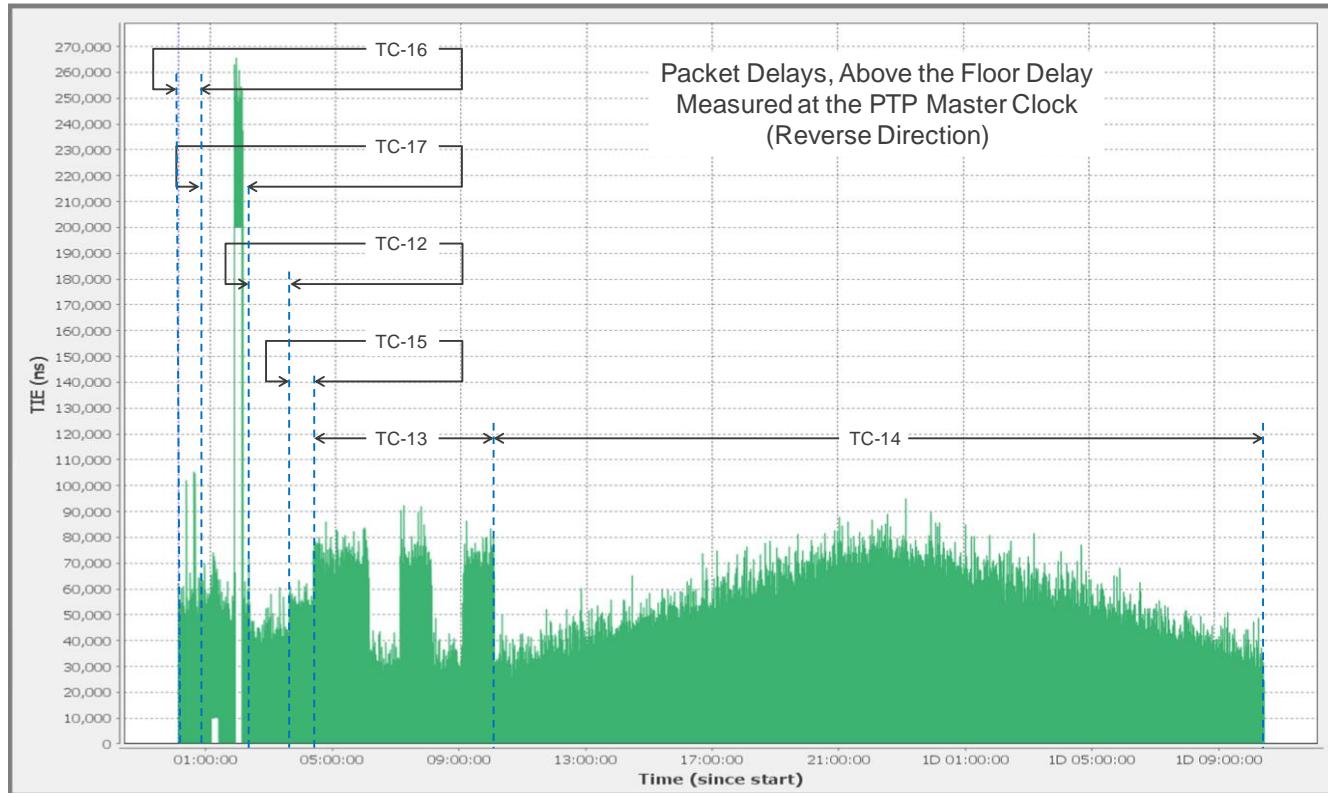

Figure 4 and Figure 5 show packet delay measurements taken at the inputs to a PTP slave clock and a PTP master clock, respectively, during a concatenated sequence of G.8261 test-cases. Traffic Model 2 and a packet rate of sixteen packets per second were used, and the test sequence required approximately 34.7 hours to complete.

The vertical axis shows the time interval error (TIE) in nanoseconds above the floor delay measured for each packet, and the horizontal axis shows the time since the start of the test in days and hours. The charts illustrate the delay conditions during each test-case and allow comparison of the simultaneous forward and reverse delays during the test sequence.

## PDV Mitigation by the Network

PDV can be mitigated in a PSN by deploying boundary clocks or transparent clocks at switching nodes; ideally, this is done at every switching node that PTP packets cross. However, boundary clocks and transparent clocks are out-of-scope for G.8265.1, and they are not used for the telecom profile for frequency synchronization.

## Limiting PTP Slave Clock Wander with a PDV Filter

PTP slave clock wander due to PDV can be limited by including a PDV filter in the servo loop. The PDV filter enables a PTP slave clock, using a low-cost temperature compensated crystal oscillator (TCXO), to generate clock signals that meet ITU-T network wander limits.

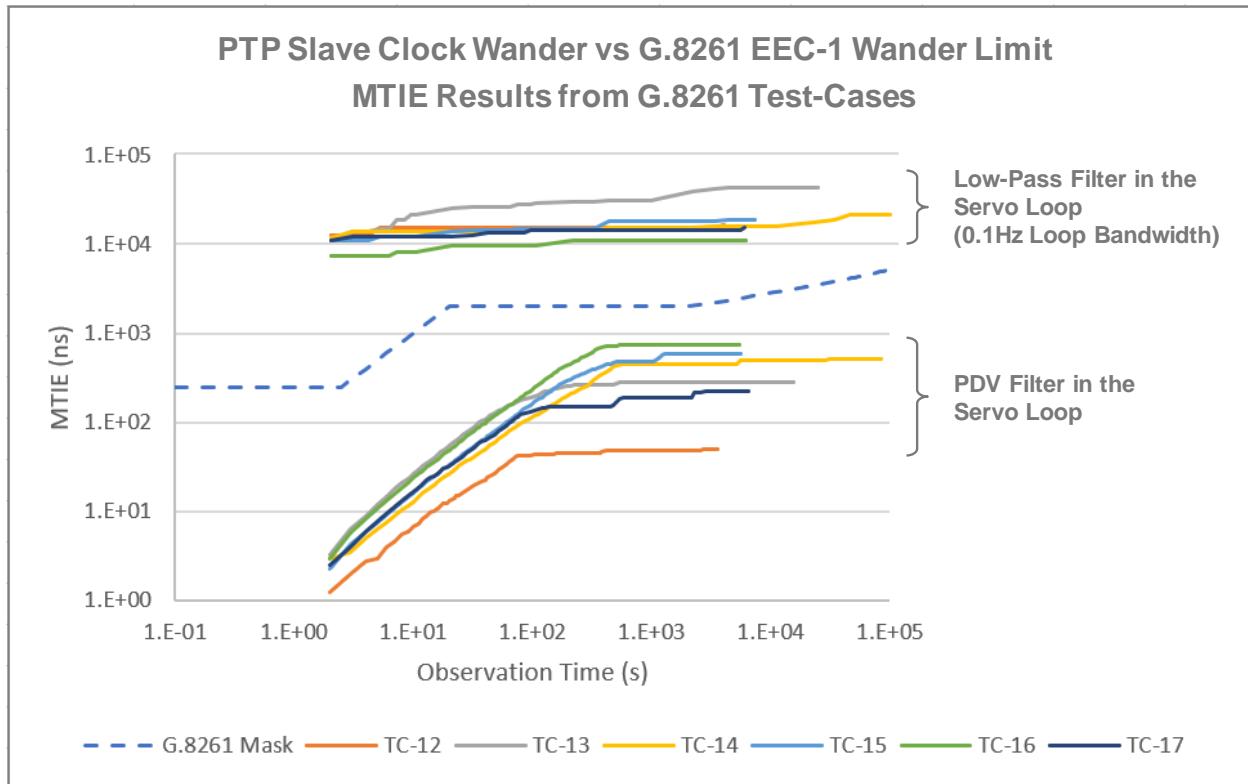

Figure 3 illustrates a PTP slave clock with a PDV filter in the servo loop. The PDV filter implements an array of algorithms that limit the effects of PDV on the frequency corrections that reach the clock synthesizer. The wander measured on this PTP slave clock during the G.8261 test-cases is shown in Figure 7. The PTP slave

clock with a PDV filter in the servo loop passes for every test case versus the G.8261 EEC-1 network wander limits.

**Figure 3. PTP Slave Clock with a PDV Filter in a G.8261 Test Environment**

## Limiting PTP Slave Clock Wander with a Low-Pass Filter

PTP slave clock wander due to PDV can be limited, to some extent, by including a low-pass filter in the servo loop. But the PDV processes that cause the wander have distributions and mean delays that change over long periods of time. For example, G.8261 test-case 13 models network phenomena that occur on a scale of hours and test-case 14 models network phenomena that occur over an entire day. Effectively attenuating such wander requires an extremely low bandwidth filter.

Low-pass filtering of timing signals requires a stable local time base. TCXOs are often used in network clocks with a bandwidth of 0.1Hz. For this reason, a TCXO and 0.1Hz PTP slave clock bandwidth were used for these tests. Lower bandwidths are possible, but they require more stable and presumably higher cost oscillators.

Figure 4. Packet Delay vs Time, Forward Direction, G.8261 Test Cases TC-12 to TC-17

Figure 5. Packet Delay vs Time, Reverse Direction, G.8261 Test-Cases TC-12 to TC-17

Figure 6 shows a PTP slave clock with a low-pass filter in the servo loop. Equation 1 is used to calculate time offset corrections. The time offset corrections are filtered by a low-pass filter that outputs frequency corrections for the clock synthesizer. The bandwidth of this servo loop is tuned to 0.1Hz. The wander measured on this PTP slave clock during the G.8261 test-cases is shown in Figure 7. The PTP slave clock with a low-pass filter in the servo loop fails for every test case versus the G.8261 EEC-1 network wander limits.

Figure 6. PTP Slave Clock with a Low-Pass Filter in a G.8261 Test Environment

Figure 7. PTP Slave Clock Wander vs G.8261 EEC-1 Wander Limit

## Conclusion

The PTP slave clock with a PDV filter in the servo loop complies with G.8261 EEC-1 network wander limits when tested versus ITU-T G.8261 test-cases 12 to 17. Whereas, the PTP slave with a low-pass filter in the servo loop does not comply with G.8261 EEC-1 network wander limits when tested versus ITU-T G.8261 test-cases 12 to 17. The highest wander measured for the PTP slave clock with a PDV filter had MTIE of 0.7 $\mu$ s from test-case 16. The highest wander measured for the PTP slave clock with a low-pass filter had MTIE of 41.9 $\mu$ s from test-case 13. Both PTP slave clock implementations used the same TCXO as the local oscillator.

For the low-pass filter implementation, a tighter bandwidth can be used at the cost of a more stable local oscillator. The tighter bandwidth would reduce the MTIE for shorter observation intervals. However, to reduce the MTIE for the 10000s and 100000s observation intervals would require a very stable and possibly cost prohibitive local oscillator.

A PTP slave clock with a PDV filter in the servo loop, together with a stable and low-cost TCXO, is effective for limiting wander due to PDV and is compliant with G.8261 network limits for wander at a telecom frequency synchronization interface.

The Renesas PTP Clock Manager software includes a PTP clock servo with a PDV filter and other functionality that meets global ITU-T synchronization recommendations for telecom applications. The PTP Clock Manager is available under license from Renesas for use with Renesas timing products, and can be used with any IEEE 1588 protocol stack.

## Notes

- 1 Recommendation ITU-T G.810 (1996), Definitions and Terminology for Synchronization Networks

- 2 IEEE Std 1588-2019, Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems

- 3 Recommendation ITU-T G.8261/Y.1361 (2019), Amendment 1 (03/2020), *Timing and Synchronization Aspects in Packet Networks*

- 4 Recommendation ITU-T G.8265.1/Y.1365.1 (2014), Amendment 1 (08/2019), *Precision Time Protocol Telecom Profile for Frequency Synchronization*

- 5 Recommendation ITU-T G.8275.2/Y.1369.2 (2020), Precision Time Protocol Telecom Profile for Phase/Time Synchronization with Partial Timing Support from the Network.

- 6 In addition, the frequency of the PTP slave clock must be stable from the arrival time of the Sync packet until the transmission time of the Delay\_Req packet.

- 7 Networks can be designed to ensure deterministic transmission times for PTP traffic; such networks are outside the scope of this whitepaper.

## Revision History

| Revision | Date      | Description                                                              |

|----------|-----------|--------------------------------------------------------------------------|

| 1.1      | Feb.1.21  | Updated diagrams and text to improve consistency with related documents. |

| 1.0      | Nov.25.20 | Initial release.                                                         |

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).