# RENESAS TECHNICAL UPDATE

〒135-0061 東京都江東区豊洲3-2-24 豊洲フォレシア

ルネサス エレクトロニクス株式会社

問合せ窓口 <http://japan.renesas.com/contact/>

E-mail: csc@renesas.com

| 製品分類 | MPU & MCU                                    | 発行番号   | TN-RX*-A158A/J | Rev.                                                                                                                      | 第1版 |

|------|----------------------------------------------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------|-----|

| 題名   | RX64M、RX71M グループ<br>POE3 ハイインピーダンス制御に関する誤記訂正 |        | 情報分類           | 技術情報                                                                                                                      |     |

| 適用製品 | RX71M グループ、RX64M グループ                        | 対象ロット等 | 関連資料           | RX71M グループ ユーザーズマニュアル ハードウェア編 Rev1.00、<br>(R01UH0493JJ0100)<br>RX64M グループ ユーザーズマニュアル ハードウェア編 Rev1.00<br>(R01UH0377JJ0100) |     |

|      |                                              | 全ロット   |                |                                                                                                                           |     |

「25.3 動作説明」 ハイインピーダンス制御に関する記載内容に誤記がありましたので、ご連絡いたします。

## 【修正前】

### 25.3 動作説明

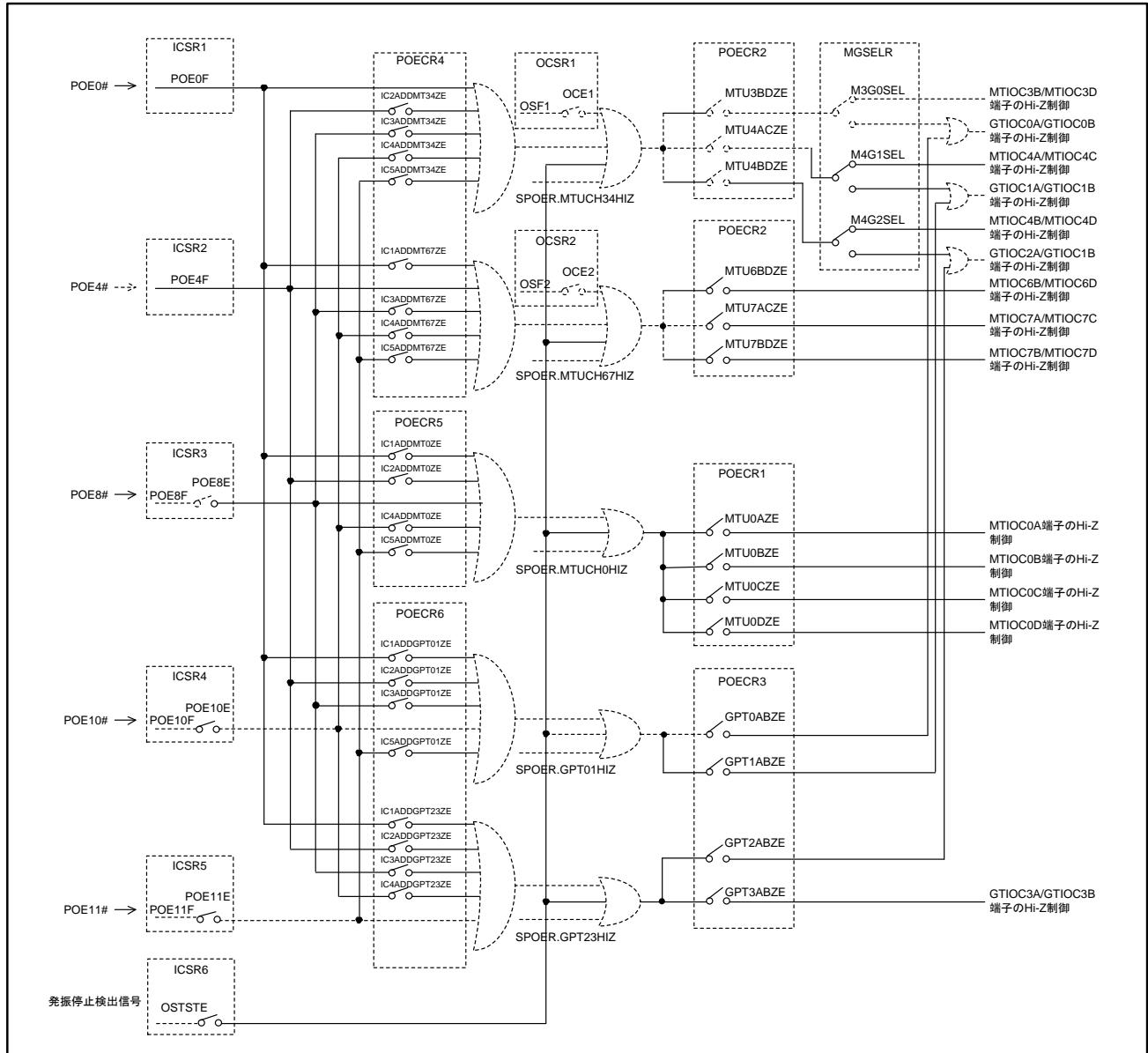

以下にハイインピーダンス制御の対象になる端子と条件を示します。

#### (1) MTU3 端子または GPT0 端子 (注 1) (MTIOC3B/GTIOC0A、MTIOC3D/GTIOC0B)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE0#端子の入力レベル検出動作

ICSR1.POEOF フラグと OCSR1.OSF1 フラグが“1”の状態で、OCSR1.OCE1 ビットが“1”になったとき

- MTIOC3B/GTIOC0A 端子と MTIOC3D/GTIOC0B 端子の出力レベル比較動作

POECR2.MTU3BDZE ビットが“1”の状態で、OCSR1.OSF1 フラグが“1”になったとき

- SPOER レジスタ設定

POECR2.MTU3BDZE ビットが“1”の状態で、SPOER.MTUCH34HIZ ビットが“1”になったとき

- POECR4 レジスタで追加された条件

POECR2.MTU3BDZE ビットと POECR4.IC2ADDMT34ZE ビットが“1”の状態で、ICSR2.POE4 フラグが“1”になったとき

POECR2.MTU3BDZE ビットと POECR4.IC3ADDMT34ZE ビットが“1”の状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POECR2.MTU3BDZE ビットと POECR4.IC4ADDMT34ZE ビットが“1”の状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

POECR2.MTU3BDZE ビットと POECR4.IC5ADDMT34ZE ビットが“1”の状態で、ICSR5.POE11F フラグと ICSR5.POE11E ビットが“1”になったとき

- 発振停止検出

POECR2.MTU3BDZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

注 1. MGSELR レジスタで MTU 端子または GPT 端子のどちらかを選択している端子のみ有効です。

#### (2) MTU4 端子または GPT1 端子 (注 1) (MTIOC4A/GTIOC1A、MTIOC4C/GTIOC1B)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE0#端子の入力レベル検出動作

ICSR1.POE0F フラグと OCSR1.OSF1 フラグが“1”の状態で、OCSR1.OCE1 ビットが“1”になったとき

- MTIOC4A/GTIOC1A 端子と MTIOC4C/GTIOC1B 端子の出力レベル比較動作

POECR2.MTU4ACZE ビットが“1”の状態で、OCSR1.OSF1 フラグが“1”になったとき

- SPOER レジスタ設定

POECR2.MTU4ACZE ビットが“1”の状態で、SPOER.MTUCH34HIZ ビットが“1”になったとき

- POECR4 レジスタで追加された条件

POECR2.MTU4ACZE ビットと POECR4.IC2ADDMMT34ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POECR2.MTU4ACZE ビットと POECR4.IC3ADDMMT34ZE ビットが“1”の状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POECR2.MTU4ACZE ビットと POECR4.IC4ADDMMT34ZE ビットが“1”の状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

POECR2.MTU4ACZE ビットと POECR4.IC5ADDMMT34ZE ビットが“1”の状態で、ICSR5.POE11F フラグと ICSR5.POE11E ビットが“1”になったとき

- 発振停止検出

POECR2.MTU4ACZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

注 1. MGSELR レジスタで MTU 端子または GPT 端子のどちらかを選択している端子のみ有効です。

### (3) MTU4 端子または GPT2 端子（注 1）(MTIOC4B/GTIOC2A、MTIOC4D/GTIOC2B)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE0#端子の入力レベル検出動作

ICSR1.POE0F フラグと OCSR1.OSF1 フラグが“1”の状態で、OCSR1.OCE1 ビットが“1”になったとき

- MTIOC4B/GTIOC2A 端子と MTIOC4D/GTIOC2B 端子の出力レベル比較動作

POECR2.MTU4BDZE ビットが“1”の状態で、OCSR1.OSF1 フラグが“1”になったとき

- SPOER レジスタ設定

POECR2.MTU4BDZE ビットが“1”の状態で、SPOER.MTUCH34HIZ ビットが“1”になったとき

- POECR4 レジスタで追加された条件

POECR2.MTU4BDZE ビットと POECR4.IC2ADDMMT34ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POECR2.MTU4BDZE ビットと POECR4.IC3ADDMMT34ZE ビットが“1”の状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POECR2.MTU4BDZE ビットと POECR4.IC4ADDMMT34ZE ビットが“1”の状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

POECR2.MTU4BDZE ビットと POECR4.IC5ADDMMT34ZE ビットが“1”の状態で、ICSR5.POE11F フラグと ICSR5.POE11E ビットが“1”になったとき

- 発振停止検出

POECR2.MTU4BDZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

注 1. MGSELR レジスタで MTU 端子または GPT 端子のどちらかを選択している端子のみ有効です。

#### (4) MTU6 端子 (MTIOC6B、MTIOC6D)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE4#端子の入力レベル検出動作

ICSR2.POE4F フラグと OCSR2.OSF2 フラグが“1”の状態で、OCSR2.OCE2 ビットが“1”になったとき

- MTIOC6B 端子と MTIOC6D 端子の出力レベル比較動作

POEGR2.MTU6BDZE ビットが“1”的状態で、OCSR2.OSF2 フラグが“1”になったとき

- SPOER レジスタ設定

POEGR2.MTU6BDZE ビットが“1”的状態で、SPOER.MTUCH67HIZ ビットが“1”になったとき

- POEGR4 レジスタで追加された条件

POEGR2.MTU6BDZE ビットと POEGR4.IC1ADDMT67ZE ビットが“1”的状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR2.MTU6BDZE ビットと POEGR4.IC3ADDMT67ZE ビットが“1”的状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POEGR2.MTU6BDZE ビットと POEGR4.IC4ADDMT67ZE ビットが“1”的状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

POEGR2.MTU6BDZE ビットと POEGR4.IC5ADDMT67ZE ビットが“1”的状態で、ICSR5.POE11F フラグと ICSR5.POE11E ビットが“1”になったとき

- 発振停止検出

POEGR2.MTU6BDZE ビットが“1”的状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (5) MTU7 端子 (MTIOC7A、MTIOC7C)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE4#端子の入力レベル検出動作

ICSR2.POE4F フラグと OCSR2.OSF2 フラグが“1”的状態で、OCSR2.OCE2 ビットが“1”になったとき

- MTIOC7A 端子と MTIOC7C 端子の出力レベル比較動作

POEGR2.MTU7ACZE ビットが“1”的状態で、OCSR2.OSF2 フラグが“1”になったとき

- SPOER レジスタ設定

POEGR2.MTU7ACZE ビットが“1”的状態で、SPOER.MTUCH67HIZ ビットが“1”になったとき

- POEGR4 レジスタで追加された条件

POEGR2.MTU7ACZE ビットと POEGR4.IC1ADDMT67ZE ビットが“1”的状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR2.MTU7ACZE ビットと POEGR4.IC3ADDMT67ZE ビットが“1”的状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POEGR2.MTU7ACZE ビットと POEGR4.IC4ADDMT67ZE ビットが“1”的状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

POEGR2.MTU7ACZE ビットと POEGR4.IC5ADDMT67ZE ビットが“1”的状態で、ICSR5.POE11F フラグと ICSR5.POE11E ビットが“1”になったとき

- 発振停止検出

POEGR2.MTU7ACZE ビットが“1”的状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”に

なったとき

#### (6) MTU7 端子 (MTIOC7B、MTIOC7D)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE4#端子の入力レベル検出動作

ICSR2.POE4F フラグと OCSR2.OSF2 フラグが“1”の状態で、OCSR2.OCE2 ビットが“1”になったとき

- MTIOC7B 端子と MTIOC7D 端子の出力レベル比較動作

POEGR2.MTU7BDZE ビットが“1”の状態で、OCSR2.OSF2 フラグが“1”になったとき

- SPOER レジスタ設定

POEGR2.MTU7BDZE ビットが“1”の状態で、SPOER.MTUCH67HIZ ビットが“1”になったとき

- POEGR4 レジスタで追加された条件

POEGR2.MTU7BDZE ビットと POEGR4.IC1ADDMT67ZE ビットが“1”の状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR2.MTU7BDZE ビットと POEGR4.IC3ADDMT67ZE ビットが“1”の状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POEGR2.MTU7BDZE ビットと POEGR4.IC4ADDMT67ZE ビットが“1”の状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

POEGR2.MTU7BDZE ビットと POEGR4.IC5ADDMT67ZE ビットが“1”の状態で、ICSR5.POE11F フラグと ICSR5.POE11E ビットが“1”になったとき

- 発振停止検出

POEGR2.MTU7BDZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (7) MTU0 端子 (MTIOC0A)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE8#端子の入力レベル検出動作

ICSR3.POE8F フラグが“1”の状態で、ICSR3.POE8E ビットが“1”になったとき

- SPOER レジスタ設定

POEGR1.MTU0AZE ビットが“1”の状態で、SPOER.MTUCH0HIZ ビットが“1”になったとき

- POEGR5 レジスタで追加された条件

POEGR1.MTU0AZE ビットと POEGR5.IC1ADDMT0ZE ビットが“1”の状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR1.MTU0AZE ビットと POEGR5.IC2ADDMT0ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR1.MTU0AZE ビットと POEGR5.IC4ADDMT0ZE ビットが“1”の状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

POEGR1.MTU0AZE ビットと POEGR5.IC5ADDMT0ZE ビットが“1”の状態で、ICSR5.POE11F フラグと ICSR5.POE11E ビットが“1”になったとき

- 発振停止検出

POEGR1.MTU0AZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (8) MTU0 端子 (MTIOC0B)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE8#端子の入力レベル検出動作

ICSR3.POEE8F フラグが“1”の状態で、ICSR3.POEE8E ビットが“1”になったとき

- SPOER レジスタ設定

POEGR1.MTU0BZE ビットが“1”の状態で、SPOER.MTUCH0HIZ ビットが“1”になったとき

- POEGR5 レジスタで追加された条件

POEGR1.MTU0BZE ビットと POEGR5.IC1ADDMT0ZE ビットが“1”の状態で、ICSR1.POEE0F フラグが“1”になったとき

POEGR1.MTU0BZE ビットと POEGR5.IC2ADDMT0ZE ビットが“1”の状態で、ICSR2.POEE4F フラグが“1”になったとき

POEGR1.MTU0BZE ビットと POEGR5.IC4ADDMT0ZE ビットが“1”の状態で、ICSR4.POEE10F フラグと ICSR4.POEE10E ビットが“1”になったとき

POEGR1.MTU0BZE ビットと POEGR5.IC5ADDMT0ZE ビットが“1”の状態で、ICSR5.POEE11F フラグと ICSR5.POEE11E ビットが“1”になったとき

- 発振停止検出

POEGR1.MTU0BDZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (9) MTU0 端子 (MTIOC0C)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE8#端子の入力レベル検出動作

ICSR3.POEE8F フラグが“1”の状態で、ICSR3.POEE8E ビットが“1”になったとき

- SPOER レジスタ設定

POEGR1.MTU0CZE ビットが“1”の状態で、SPOER.MTUCH0HIZ ビットが“1”になったとき

- POEGR5 レジスタで追加された条件

POEGR1.MTU0CZE ビットと POEGR5.IC1ADDMT0ZE ビットが“1”の状態で、ICSR1.POEE0F フラグが“1”になったとき

POEGR1.MTU0CZE ビットと POEGR5.IC2ADDMT0ZE ビットが“1”の状態で、ICSR2.POEE4F フラグが“1”になったとき

POEGR1.MTU0CZE ビットと POEGR5.IC4ADDMT0ZE ビットが“1”の状態で、ICSR4.POEE10F フラグと ICSR4.POEE10E ビットが“1”になったとき

POEGR1.MTU0CZE ビットと POEGR5.IC5ADDMT0ZE ビットが“1”の状態で、ICSR5.POEE11F フラグと ICSR5.POEE11E ビットが“1”になったとき

- 発振停止検出

POEGR1.MTU0CZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (10) MTU0 端子 (MTIOC0D)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE8#端子の入力レベル検出動作

ICSR3.POEE8F フラグが“1”的状態で、ICSR3.POEE8E ビットが“1”になったとき

- SPOER レジスタ設定

POECCR1.MTU0DZE ビットが“1”的状態で、SPOER.MTUCH0HIZ ビットが“1”になったとき

- POECCR5 レジスタで追加された条件

POECCR1.MTU0DZE ビットと POECCR5.IC1ADDMT0ZE ビットが“1”的状態で、ICSR1.POEE0F フラグが“1”になったとき

POECCR1.MTU0DZE ビットと POECCR5.IC2ADDMT0ZE ビットが“1”的状態で、ICSR2.POEE4F フラグが“1”になったとき

POECCR1.MTU0DZE ビットと POECCR5.IC4ADDMT0ZE ビットが“1”的状態で、ICSR4.POEE10F フラグと ICSR4.POEE10E ビットが“1”になったとき

POECCR1.MTU0DZE ビットと POECCR5.IC5ADDMT0ZE ビットが“1”的状態で、ICSR5.POEE11F フラグと ICSR5.POEE11E ビットが“1”になったとき

- 発振停止検出

POECCR1.MTU0DZE ビットが“1”的状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (11) GPT0 端子 (GTIOC0A、GTIOC0B)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE10#端子の入力レベル検出動作

ICSR4.POEE10F フラグが“1”的状態で、ICSR4.POEE10E ビットが“1”になったとき

- SPOER レジスタ設定

POECCR3.GPT0ABZE ビットが“1”的状態で、SPOER.GPT01HIZ ビットが“1”になったとき

- POECCR6 レジスタで追加された条件

POECCR3.GPT0ABZE ビットと POECCR6.IC1ADDGPT01ZE ビットが“1”的状態で、ICSR1.POEE0F フラグが“1”になったとき

POECCR3.GPT0ABZE ビットと POECCR6.IC2ADDGPT01ZE ビットが“1”的状態で、ICSR2.POEE4F フラグが“1”になったとき

POECCR3.GPT0ABZE ビットと POECCR6.IC3ADDGPT01ZE ビットが“1”的状態で、ICSR3.POEE8F フラグと ICSR3.POEE8E ビットが“1”になったとき

POECCR3.GPT0ABZE ビットと POECCR6.IC5ADDGPT01ZE ビットが“1”的状態で、ICSR5.POEE11F フラグと ICSR5.POEE11E ビットが“1”になったとき

- 発振停止検出

POECCR3.GPT0ABZE ビットが“1”的状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (12) GPT1 端子 (GTIOC1A、GTIOC1B)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE10#端子の入力レベル検出動作

ICSR4.POEE10F フラグが“1”的状態で、ICSR4.POEE10E ビットが“1”になったとき

- SPOER レジスタ設定

POEGR3.GPT1ABZE ビットが“1”の状態で、SPOER.GPT01HIZ ビットが“1”になったとき

- POEGR6 レジスタで追加された条件

POEGR3.GPT1ABZE ビットと POEGR6.IC1ADDGPT01ZE ビットが“1”の状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR3.GPT1ABZE ビットと POEGR6.IC2ADDGPT01ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR3.GPT1ABZE ビットと POEGR6.IC3ADDGPT01ZE ビットが“1”の状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POEGR3.GPT1ABZE ビットと POEGR6.IC5ADDGPT01ZE ビットが“1”の状態で、ICSR5.POE11F フラグと ICSR5.POE11E ビットが“1”になったとき

- 発振停止検出

POEGR3.GPT1ABZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (13) GPT2 端子 (GTIOC2A、GTIOC2B)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE11#端子の入力レベル検出動作

ICSR5.POE11F フラグが“1”の状態で、ICSR5.POE11E ビットが“1”になったとき

- SPOER レジスタ設定

POEGR3.GPT2ABZE ビットが“1”の状態で、SPOER.GPT23HIZ ビットが“1”になったとき

- POEGR6 レジスタで追加された条件

POEGR3.GPT2ABZE ビットと POEGR6.IC1ADDGPT23ZE ビットが“1”の状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR3.GPT2ABZE ビットと POEGR6.IC2ADDGPT23ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR3.GPT2ABZE ビットと POEGR6.IC3ADDGPT23ZE ビットが“1”の状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POEGR3.GPT2ABZE ビットと POEGR6.IC4ADDGPT23ZE ビットが“1”の状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

- 発振停止検出

POEGR3.GPT2ABZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

#### (14) GPT3 端子 (GTIOC3A、GTIOC3B)

以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE11#端子の入力レベル検出動作

ICSR5.POE11F フラグが“1”の状態で、ICSR5.POE11E ビットが“1”になったとき

- SPOER レジスタ設定

POEGR3.GPT3ABZE ビットが“1”の状態で、SPOER.GPT23HIZ ビットが“1”になったとき

- POEGR6 レジスタで追加された条件

POEGR3.GPT3ABZE ビットと POEGR6.IC1ADDGPT23ZE ビットが“1”の状態で、ICSR1.POE0F フラグ

が“1”になったとき

POECR3.GPT3ABZE ビットと POECR6.IC2ADDGPT23ZE ビットが“1”的状態で、ICSR2.POE4F フラグが“1”になったとき

POECR3.GPT3ABZE ビットと POECR6.IC3ADDGPT23ZE ビットが“1”的状態で、ICSR3.POE8F フラグと ICSR3.POE8E ビットが“1”になったとき

POECR3.GPT3ABZE ビットと POECR6.IC4ADDGPT23ZE ビットが“1”的状態で、ICSR4.POE10F フラグと ICSR4.POE10E ビットが“1”になったとき

・発振停止検出

POECR3.GPT3ABZE ビットが“1”の状態で、ICSR6.OSTSTF フラグと ICSR6.OSTSTE ビットが“1”になったとき

図 25.2 ハイインピーダンス制御の対象と条件

## 【修正後】

## 25.3 動作説明

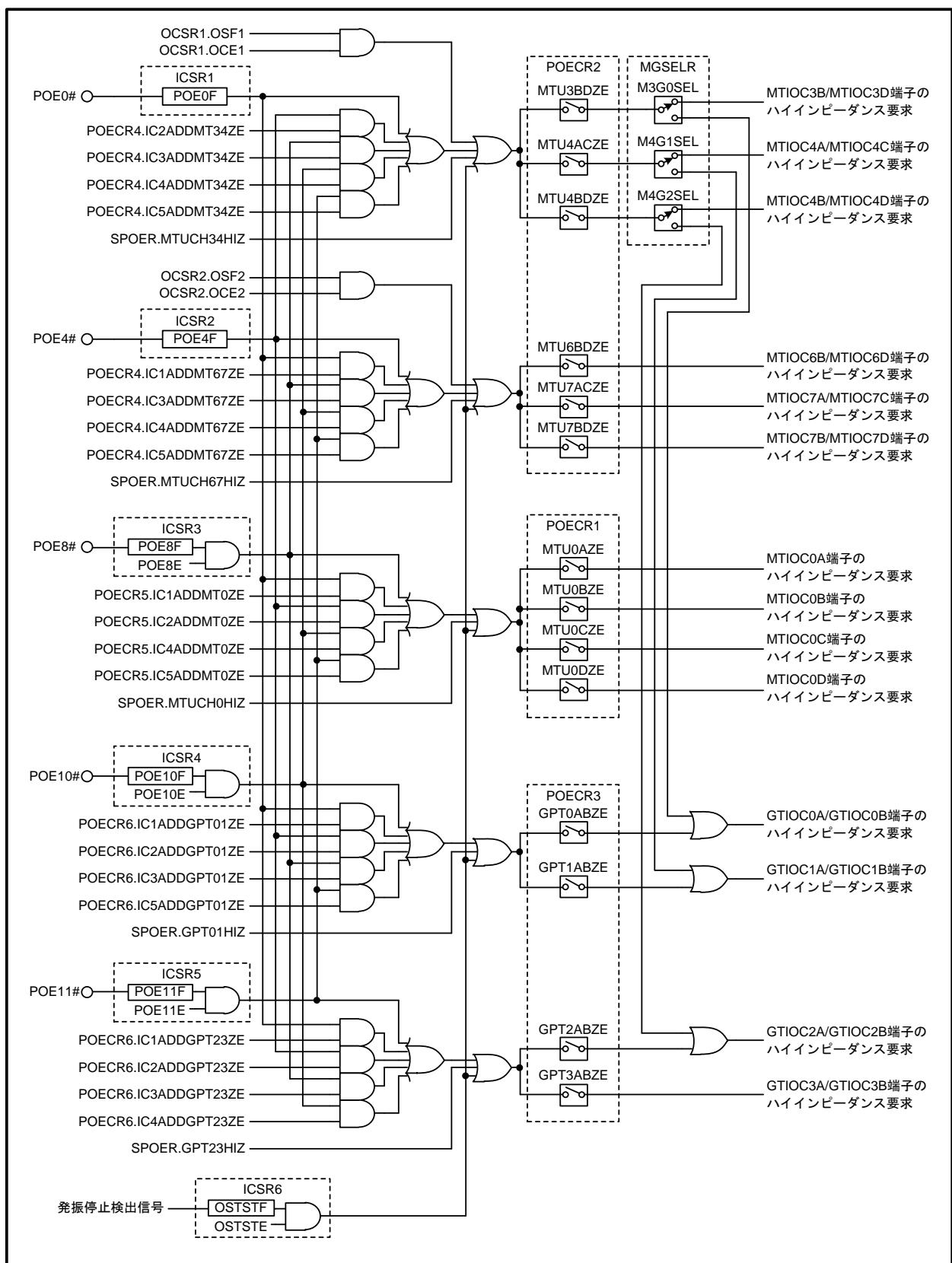

以下にハイインピーダンス制御の対象になる端子と条件を示します。

(1) MTU3 端子または GPT0 端子（注 1）（MTIOC3B/GTIOC0A, MTIOC3D/GTIOC0B）

POEGR2.MTU3BDZE ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE0#端子の入力レベル検出動作

ICSR1.POE0F フラグが“1”になったとき

- MTIOC3B/GTIOC0A 端子と MTIOC3D/GTIOC0B 端子の出力レベル比較動作

OCSR1.OCE1 ビットが“1”の状態で、OCSR1.OSF1 フラグが“1”になったとき

- SPOER レジスタ設定

SPOER.MTUCH34HIZ ビットを“1”にしたとき

- POEGR4 レジスタで追加された条件

POEGR4.IC2ADDMT34ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR4.IC3ADDMT34ZE ビットと ICSR3.POE8E ビットが“1”の状態で、ICSR3.POE8F フラグが“1”になったとき

POEGR4.IC4ADDMT34ZE ビットと ICSR4.POE10E ビットが“1”の状態で、ICSR4.POE10F フラグが“1”になったとき

POEGR4.IC5ADDMT34ZE ビットと ICSR5.POE11E ビットが“1”の状態で、ICSR5.POE11F フラグが“1”になったとき

- 発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

注 1. MGSELR.M3G0SEL ビットで選択されている端子のみ対象です。

(2) MTU4 端子または GPT1 端子（注 1）（MTIOC4A/GTIOC1A, MTIOC4C/GTIOC1B）

POEGR2.MTU4ACZE ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE0# 端子の入力レベル検出動作

ICSR1.POE0F フラグが“1”になったとき

- MTIOC4A/GTIOC1A 端子と MTIOC4C/GTIOC1B 端子の出力レベル比較動作

OCSR1.OCE1 ビットが“1”の状態で、OCSR1.OSF1 フラグが“1”になったとき

- SPOER レジスタ設定

SPOER.MTUCH34HIZ ビットを“1”にしたとき

- POEGR4 レジスタで追加された条件

POEGR4.IC2ADDMT34ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR4.IC3ADDMT34ZE ビットと ICSR3.POE8E ビットが“1”の状態で、ICSR3.POE8F フラグが“1”になったとき

POEGR4.IC4ADDMT34ZE ビットと ICSR4.POE10E ビットが“1”の状態で、ICSR4.POE10F フラグが“1”になったとき

POEGR4.IC5ADDMT34ZE ビットと ICSR5.POE11E ビットが“1”の状態で、ICSR5.POE11F フラグが“1”

になったとき

- ・発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

注 1. MGSELR.M4G1SEL ビットで選択されている端子のみ対象です。

(3) MTU4 端子または GPT2 端子（注 1）（MTIOC4B/GTIOC2A, MTIOC4D/GTIOC2B）

**POEGR2.MTU4BDZE** ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- ・POE0#端子の入力レベル検出動作

ICSR1.POE0F フラグが“1”になったとき

- ・MTIOC4B/GTIOC2A 端子と MTIOC4D/GTIOC2B 端子の出力レベル比較動作

OCSR1.OCE1 ビットが“1”の状態で、OCSR1.OSF1 フラグが“1”になったとき

- ・SPOER レジスタ設定

SPOER.MTUCH34HIZ ビットを“1”にしたとき

- ・POEGR4 レジスタで追加された条件

POEGR4.IC2ADDMT34ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR4.IC3ADDMT34ZE ビットと ICSR3.POE8E ビットが“1”の状態で、ICSR3.POE8F フラグが“1”になったとき

POEGR4.IC4ADDMT34ZE ビットと ICSR4.POE10E ビットが“1”の状態で、ICSR4.POE10F フラグが“1”になったとき

POEGR4.IC5ADDMT34ZE ビットと ICSR5.POE11E ビットが“1”の状態で、ICSR5.POE11F フラグが“1”になったとき

- ・発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

注 1. MGSELR.M4G2SEL ビットで選択されている端子のみ対象です。

(4) MTU6 端子（MTIOC6B, MTIOC6D）

**POEGR2.MTU6BDZE** ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- ・POE4#端子の入力レベル検出動作

ICSR2.POE4F フラグが“1”になったとき

- ・MTIOC6B 端子と MTIOC6D 端子の出力レベル比較動作

OCSR2.OCE2 ビットが“1”の状態で、OCSR2.OSF2 フラグが“1”になったとき

- ・SPOER レジスタ設定

SPOER.MTUCH67HIZ ビットを“1”にしたとき

- ・POEGR4 レジスタで追加された条件

POEGR4.IC1ADDMT67ZE ビットが“1”の状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR4.IC3ADDMT67ZE ビットと ICSR3.POE8E ビットが“1”の状態で、ICSR3.POE8F フラグが“1”になったとき

POEGR4.IC4ADDMT67ZE ビットと ICSR4.POE10E ビットが“1”の状態で、ICSR4.POE10F フラグが“1”になったとき

- POEGR4.IC5ADDMT67ZE ビットと ICSR5.POE11E ビットが“1”的状態で、ICSR5.POE11F フラグが“1”になったとき

- ・発振停止検出

- ICSR6.OSTSTE ビットが“1”的状態で、ICSR6.OSTSTF フラグが“1”になったとき

#### (5) MTU7 端子 (MTIOC7A, MTIOC7C)

- POEGR2.MTU7ACZE ビットが“1”的状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- ・POE4#端子の入力レベル検出動作

- ICSR2.POE4F フラグが“1”になったとき

- ・MTIOC7A 端子と MTIOC7C 端子の出力レベル比較動作

- OCSR2.OCE2 ビットが“1”的状態で、OCSR2.OSF2 フラグが“1”になったとき

- ・SPOER レジスタ設定

- SPOER.MTUCH67HIZ ビットを“1”にしたとき

- ・POEGR4 レジスタで追加された条件

- POEGR4.IC1ADDMT67ZE ビットが“1”的状態で、ICSR1.POE0F フラグが“1”になったとき

- POEGR4.IC3ADDMT67ZE ビットと ICSR3.POE8E ビットが“1”的状態で、ICSR3.POE8F フラグが“1”になったとき

- POEGR4.IC4ADDMT67ZE ビットと ICSR4.POE10E ビットが“1”的状態で、ICSR4.POE10F フラグが“1”になったとき

- POEGR4.IC5ADDMT67ZE ビットと ICSR5.POE11E ビットが“1”的状態で、ICSR5.POE11F フラグが“1”になったとき

- ・発振停止検出

- ICSR6.OSTSTE ビットが“1”的状態で、ICSR6.OSTSTF フラグが“1”になったとき

#### (6) MTU7 端子 (MTIOC7B, MTIOC7D)

- POEGR2.MTU7BDZE ビットが“1”的状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- ・POE4#端子の入力レベル検出動作

- ICSR2.POE4F フラグが“1”になったとき

- ・MTIOC7B 端子と MTIOC7D 端子の出力レベル比較動作

- OCSR2.OCE2 ビットが“1”的状態で、OCSR2.OSF2 フラグが“1”になったとき

- ・SPOER レジスタ設定

- SPOER.MTUCH67HIZ ビットを“1”にしたとき

- ・POEGR4 レジスタで追加された条件

- POEGR4.IC1ADDMT67ZE ビットが“1”的状態で、ICSR1.POE0F フラグが“1”になったとき

- POEGR4.IC3ADDMT67ZE ビットと ICSR3.POE8E ビットが“1”的状態で、ICSR3.POE8F フラグが“1”になったとき

- POEGR4.IC4ADDMT67ZE ビットと ICSR4.POE10E ビットが“1”的状態で、ICSR4.POE10F フラグが“1”になったとき

- POEGR4.IC5ADDMT67ZE ビットと ICSR5.POE11E ビットが“1”的状態で、ICSR5.POE11F フラグが“1”

になったとき

- ・発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

#### (7) MTU0 端子 (MTIOC0A)

POEGR1.MTU0AZE ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- ・POE8#端子の入力レベル検出動作

ICSR3.POE8E ビットが“1”の状態で、ICSR3.POE8F フラグが“1”になったとき

- ・SPOER レジスタ設定

SPOER.MTUCH0HIZ ビットを“1”にしたとき

- ・POEGR5 レジスタで追加された条件

POEGR5.IC1ADDMT0ZE ビットが“1”の状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR5.IC2ADDMT0ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR5.IC4ADDMT0ZE ビットと ICSR4.POE10E ビットが“1”の状態で、ICSR4.POE10F フラグが“1”になったとき

POEGR5.IC5ADDMT0ZE ビットと ICSR5.POE11E ビットが“1”の状態で、ICSR5.POE11F フラグが“1”になったとき

- ・発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

#### (8) MTU0 端子 (MTIOC0B)

POEGR1.MTU0BZE ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- ・POE8#端子の入力レベル検出動作

ICSR3.POE8E ビットが“1”の状態で、ICSR3.POE8F フラグが“1”になったとき

- ・SPOER レジスタ設定

SPOER.MTUCH0HIZ ビットを“1”にしたとき

- ・POEGR5 レジスタで追加された条件

POEGR5.IC1ADDMT0ZE ビットが“1”の状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR5.IC2ADDMT0ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR5.IC4ADDMT0ZE ビットと ICSR4.POE10E ビットが“1”の状態で、ICSR4.POE10F フラグが“1”になったとき

POEGR5.IC5ADDMT0ZE ビットと ICSR5.POE11E ビットが“1”の状態で、ICSR5.POE11F フラグが“1”になったとき

- ・発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

#### (9) MTU0 端子 (MTIOC0C)

POEGR1.MTU0CZE ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE8#端子の入力レベル検出動作

**ICSR3.POE8E** ビットが“1”の状態で、**ICSR3.POE8F** フラグが“1”になったとき

- SPOER レジスタ設定

SPOER.MTUCH0HIZ ビットを“1”にしたとき

- POECR5 レジスタで追加された条件

POECR5.IC1ADDMT0ZE ビットが“1”の状態で、**ICSR1.POE0F** フラグが“1”になったとき

POECR5.IC2ADDMT0ZE ビットが“1”の状態で、**ICSR2.POE4F** フラグが“1”になったとき

POECR5.IC4ADDMT0ZE ビットと **ICSR4.POE10E** ビットが“1”の状態で、**ICSR4.POE10F** フラグが“1”になったとき

POECR5.IC5ADDMT0ZE ビットと **ICSR5.POE11E** ビットが“1”の状態で、**ICSR5.POE11F** フラグが“1”になったとき

- 発振停止検出

**ICSR6.OSTSTE** ビットが“1”の状態で、**ICSR6.OSTSTF** フラグが“1”になったとき

#### (10) MTU0 端子 (MTIOC0D)

**POECR1.MTU0DZE** ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE8#端子の入力レベル検出動作

**ICSR3.POE8E** ビットが“1”の状態で、**ICSR3.POE8F** フラグが“1”になったとき

- SPOER レジスタ設定

SPOER.MTUCH0HIZ ビットを“1”にしたとき

- POECR5 レジスタで追加された条件

POECR5.IC1ADDMT0ZE ビットが“1”の状態で、**ICSR1.POE0F** フラグが“1”になったとき

POECR5.IC2ADDMT0ZE ビットが“1”の状態で、**ICSR2.POE4F** フラグが“1”になったとき

POECR5.IC4ADDMT0ZE ビットと **ICSR4.POE10E** ビットが“1”の状態で、**ICSR4.POE10F** フラグが“1”になったとき

POECR5.IC5ADDMT0ZE ビットと **ICSR5.POE11E** ビットが“1”の状態で、**ICSR5.POE11F** フラグが“1”になったとき

- 発振停止検出

**ICSR6.OSTSTE** ビットが“1”の状態で、**ICSR6.OSTSTF** フラグが“1”になったとき

#### (11) GPT0 端子 (GTIOC0A, GTIOC0B)

**POECR3.GPT0ABZE** ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE10#端子の入力レベル検出動作

**ICSR4.POE10E** ビットが“1”の状態で、**ICSR4.POE10F** フラグが“1”になったとき

- SPOER レジスタ設定

SPOER.GPT01HIZ ビットを“1”にしたとき

- POECR6 レジスタで追加された条件

POECR6.IC1ADDGPT01ZE ビットが“1”の状態で、**ICSR1.POE0F** フラグが“1”になったとき

POECR6.IC2ADDGPT01ZE ビットが“1”の状態で、**ICSR2.POE4F** フラグが“1”になったとき

POEGR6.IC3ADDGPT01ZE ビットと ICSR3.POE8E ビットが“1”の状態で、ICSR3.POE8F フラグが“1”になったとき

POEGR6.IC5ADDGPT01ZE ビットと ICSR5.POE11E ビットが“1”の状態で、ICSR5.POE11F フラグが“1”になったとき

・発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

#### (12) GPT1 端子 (GTIOC1A, GTIOC1B)

POEGR3.GPT1ABZE ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE10# 端子の入力レベル検出動作

ICSR4.POE10E ビットが“1”の状態で、ICSR4.POE10F フラグが“1”になったとき

- SPOER レジスタ設定

SPOER.GPT01HIZ ビットを“1”にしたとき

- POEGR6 レジスタで追加された条件

POEGR6.IC1ADDGPT01ZE ビットが“1”の状態で、ICSR1.POEOF フラグが“1”になったとき

POEGR6.IC2ADDGPT01ZE ビットが“1”の状態で、ICSR2.POEF フラグが“1”になったとき

POEGR6.IC3ADDGPT01ZE ビットと ICSR3.POE8E ビットが“1”の状態で、ICSR3.POEOF フラグが“1”になったとき

POEGR6.IC5ADDGPT01ZE ビットと ICSR5.POE11E ビットが“1”の状態で、ICSR5.POEOF フラグが“1”になったとき

・発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

#### (13) GPT2 端子 (GTIOC2A, GTIOC2B)

POEGR3.GPT2ABZE ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

- POE11# 端子の入力レベル検出動作

ICSR5.POE11E ビットが“1”の状態で、ICSR5.POEOF フラグが“1”になったとき

- SPOER レジスタ設定

SPOER.GPT23HIZ ビットが“1”になったとき

- POEGR6 レジスタで追加された条件

POEGR6.IC1ADDGPT23ZE ビットが“1”の状態で、ICSR1.POEOF フラグが“1”になったとき

POEGR6.IC2ADDGPT23ZE ビットが“1”の状態で、ICSR2.POEOF フラグが“1”になったとき

POEGR6.IC3ADDGPT23ZE ビットと ICSR3.POEOF ビットが“1”の状態で、ICSR3.POEOF フラグが“1”になったとき

POEGR6.IC4ADDGPT23ZE ビットと ICSR4.POEOF ビットが“1”の状態で、ICSR4.POEOF フラグが“1”になったとき

・発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

#### (14) GPT3 端子 (GTIOC3A, GTIOC3B)

POEGR3.GPT3ABZE ビットが“1”の状態で、以下のいずれかの条件が成立したとき、端子をハイインピーダンスにします。

ダンスにします。

- POE11#端子の入力レベル検出動作

ICSR5.POE11E ビットが“1”の状態で、ICSR5.POE11F フラグが“1”になったとき

- SPOER レジスタ設定

SPOER.GPT23HIZ ビットが“1”になったとき

- POEGR6 レジスタで追加された条件

POEGR6.IC1ADDGPT23ZE ビットが“1”の状態で、ICSR1.POE0F フラグが“1”になったとき

POEGR6.IC2ADDGPT23ZE ビットが“1”の状態で、ICSR2.POE4F フラグが“1”になったとき

POEGR6.IC3ADDGPT23ZE ビットと ICSR3.POE8E ビットが“1”の状態で、ICSR3.POE8F フラグが“1”になったとき

POEGR6.IC4ADDGPT23ZE ビットと ICSR4.POE10E ビットが“1”の状態で、ICSR4.POE10F フラグが“1”になったとき

- 発振停止検出

ICSR6.OSTSTE ビットが“1”の状態で、ICSR6.OSTSTF フラグが“1”になったとき

図 25.2 ハイインピーダンス制御の対象と条件

以上