# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                  | Document<br>No.         | TN-RL*-A0102A/E        | Rev.     | 1.00 |  |

|-----------------------|----------------------------------------------------------------------------------------------------------|-------------------------|------------------------|----------|------|--|

| Title                 | Correction for Incorrect Description Notice RI<br>Descriptions in the User's Manual: Hardware<br>Changed | Information<br>Category | Technical Notification |          |      |  |

|                       |                                                                                                          | Lot No.                 |                        |          |      |  |

| Applicable<br>Product | RL78/G23 Group                                                                                           | All lots                | Reference<br>Document  | Rev 1 10 |      |  |

This document describes misstatements found in the RL78/G23 User's Manual: Hardware Rev. 1.10 (R01UH0896EJ0110).

#### **Corrections**

| Applicable Item                                                                | Applicable<br>Page                    | Contents                       |

|--------------------------------------------------------------------------------|---------------------------------------|--------------------------------|

| Initial value of flash memory sequencer status registers H, L (FSASTH, FSASTL) | Page 146,<br>Page 1314                | Incorrect descriptions revised |

| 12.8.2 A/D conversion by inputting a hardware trigger                          | Page 578                              | Caution added                  |

| 17.2.9 UARTA clock select register 0 (UTA0CK)                                  | Page 899                              | Caution added                  |

| 17.2.10 UARTA clock select register 1 (UTA1CK)                                 | Page 900                              | Caution added                  |

| 23.2.2 Memory power reduction control register (PSMCR)                         | Page 1105                             | Caution added                  |

| 23.3.2 STOP mode                                                               | Page 1116                             | Incorrect descriptions revised |

| 23.3.3 SNOOZE mode                                                             | Page 1119,<br>Page 1120               | Incorrect descriptions revised |

| 27.3.8.1 Guard register of IAWCTL register (GIAWCTL)                           | Page 1172                             | Incorrect descriptions revised |

| 27.3.12.1 UART loopback select register (ULBS)                                 | Page 1181,<br>Page 1182               | Incorrect descriptions revised |

| 28.2.2 Setting of flash read protection                                        | Page 1188                             | Caution added                  |

| 29.6 Operation in Standby Modes                                                | Page 1233                             | Caution added                  |

| Access to the extra area                                                       | Page 1319,<br>Page 1322,<br>Page 1341 | Incorrect descriptions revised |

| 33.6.8.3 Example of executing the commands to rewrite the extra area           | Page 1340                             | Incorrect descriptions revised |

| 34.4 Allocation of Memory Spaces to User Resources                             | Page 1352                             | Caution added                  |

| Section 37 Electrical Characteristics                                          | Page 1378                             | Description added              |

| 37.1 Absolute Maximum Ratings                                                  | Page 1378,<br>Page 1379               | Incorrect descriptions revised |

| 37.2 Characteristics of the Oscillators                                        | Page 1380                             | Incorrect descriptions revised |

| 37.3.1 Pin characteristics                                                     | Page 1388,<br>Page 1390               | Incorrect descriptions revised |

| High-speed on-chip oscillator operating current                                | Page 1409                             | Incorrect descriptions revised |

| 37.4 AC Characteristics                                                        | Page 1412                             | Incorrect descriptions revised |

| 37.6.1 A/D converter characteristics                                           | Page 1453,<br>Page 1454               | Caution added                  |

## Document Improvement

The above corrections will be made for the next revision of the User's Manual: Hardware.

Corrections in the User's Manual: Hardware

|     |                                                                      |                                       | Corrections and Applicable Items |                                    | Pages in this               |

|-----|----------------------------------------------------------------------|---------------------------------------|----------------------------------|------------------------------------|-----------------------------|

| No. |                                                                      |                                       |                                  | R01UH0896EJ0110                    | document for<br>corrections |

| 1   |                                                                      | alue of flash memory s<br>TH, FSASTL) | sequencer status registers H, L  | Page 146, Page 1314                | Page 3, Page 4              |

| 2   | 12.8.2                                                               | VD conversion by inp                  | utting a hardware trigger        | Page 578                           | Page 5                      |

| 3   | 17.2.9 l                                                             | JARTA clock select re                 | gister 0 (UTA0CK)                | Page 899                           | Page 6                      |

| 4   | 17.2.10                                                              | UARTA clock select i                  | egister 1 (UTA1CK)               | Page 900                           | Page 7                      |

| 5   | 23.2.2                                                               | Memory power reducti                  | on control register (PSMCR)      | Page 1105                          | Page 8                      |

| 6   | 23.3.2 \$                                                            | STOP mode                             |                                  | Page 1116                          | Page 9                      |

| 7   | 23.3.3 \$                                                            | SNOOZE mode                           |                                  | Page 1119, Page 1120               | Page 10, Page 11            |

| 8   | 27.3.8.1 Guard register of IAWCTL register (GIAWCTL)                 |                                       |                                  | Page 1172                          | Page 12                     |

| 9   | 27.3.12.1 UART loopback select register (ULBS)                       |                                       |                                  | Page 1181, Page 1182               | Page 13, Page 14            |

| 10  | 28.2.2 Setting of flash read protection                              |                                       |                                  | Page 1188                          | Page 15                     |

| 11  | 29.6 Operation in Standby Modes                                      |                                       |                                  | Page 1233                          | Page 16                     |

| 12  | Access to the extra area                                             |                                       |                                  | Page 1319, Page 1322,<br>Page 1341 | Page 17, Page 18            |

| 13  | 33.6.8.3 Example of executing the commands to rewrite the extra area |                                       |                                  | Page 1340                          | Page 19                     |

| 14  | 34.4 All                                                             | ocation of Memory Sp                  | aces to User Resources           | Page 1352                          | Page 20, Page 21            |

| 15  | Section                                                              | 37 Electrical Charact                 | eristics                         | Page 1378                          | Page 22                     |

| 16  | 37.1 Absolute Maximum Ratings                                        |                                       | ngs                              | Page 1378, Page 1379               | Page 23, Page 24            |

| 17  | 37.2 Ch                                                              | aracteristics of the Os               | scillators                       | Page 1380                          | Page 25                     |

| 18  | 37.3.1                                                               | Pin characteristics                   |                                  | Page 1388, Page 1390               | Page 26, Page 27            |

| 19  | High-sp                                                              | eed on-chip oscillator                | operating current                | Page 1409                          | Page 28                     |

| 20  | 37.4 AC                                                              | Characteristics                       |                                  | Page 1412                          | Page 29                     |

| 21  | 37.6.1                                                               | VD converter characte                 | eristics                         | Page 1453, Page 1454               | Page 30, Page31             |

Incorrect: Bold with underline; Correct: Gray hatched

## **Revision History**

RL78/G23 Correction for incorrect description notice

| Document N | umber  | Issue Date   | Description                                       |

|------------|--------|--------------|---------------------------------------------------|

| TN-RL*-A0  | 102A/E | Oct. 3, 2022 | First edition issued                              |

|            |        |              | Corrections No.1 to No.21 revised (this document) |

## 1. <u>Initial value of flash memory sequencer status registers H, L</u> (FSASTH, FSASTL) (Page 146, Page 1314)

## Incorrect:

#### Table 3 - 6List of Extended Special Function Registers (2nd SFRs) (9/15)

| Address | Special Function Register (SFR) Name     | Symbol  | R/W   | Manipulable Bit Range |              |              | After Reset |

|---------|------------------------------------------|---------|-------|-----------------------|--------------|--------------|-------------|

| Address |                                          |         | 1-bit | 8-bit                 | 16-bit       | Alter Reset  |             |

| F02CAH  | Flash memory sequencer status register L | FSASTL  | R     | $\checkmark$          | V            | —            | QQH         |

| F02CBH  | Flash memory sequencer status register H | FSASTH  | R     | $\checkmark$          | $\checkmark$ | —            | <b>00H</b>  |

| F02CCH  | Flash write buffer register L            | FLWL    | R/W   | -                     | —            | $\checkmark$ | 0000H       |

| F02CEH  | Flash write buffer register H            | FLWH    | R/W   | _                     | _            | V            | 0000H       |

| F02E0H  | DTC base address register                | DTCBAR  | R/W   | _                     | V            | —            | FDH         |

| F02E8H  | DTC activation enable register 0         | DTCEN0  | R/W   | V                     | V            | —            | 00H         |

| F02E9H  | DTC activation enable register 1         | DTCEN1  | R/W   | V                     | V            | —            | 00H         |

| F02EAH  | DTC activation enable register 2         | DTCEN2  | R/W   | V                     | V            | —            | 00H         |

| F02EBH  | DTC activation enable register 3         | DTCEN3  | R/W   | V                     | V            | —            | 00H         |

| F02ECH  | DTC activation enable register 4         | DTCEN4  | R/W   | V                     | V            | —            | 00H         |

| F02F0H  | Flash memory CRC control register        | CRC0CTL | R/W   | V                     | V            | —            | 00H         |

## Correct:

| Table 3 - 6 | List of Extended Special Function Registers (2nd SFRs) (9/15) |

|-------------|---------------------------------------------------------------|

|-------------|---------------------------------------------------------------|

| Address | Special Function Register (SFR) Name     | Symbol  | R/W   | Manipulable Bit Range |         |        | After Reset |

|---------|------------------------------------------|---------|-------|-----------------------|---------|--------|-------------|

| Audress | Special Function Register (SFR) Name     | Symbol  | 10,00 | 1-bit                 | 8-bit   | 16-bit | Aller Reset |

| F02CAH  | Flash memory sequencer status register L | FSASTL  | R     | V                     | 1       | -      | 00H/80H     |

| F02CBH  | Flash memory sequencer status register H | FSASTH  | R     | V                     | ~       | —      | 00H/04H     |

| F02CCH  | Flash write buffer register L            | FLWL    | R/W   | —                     | —       | V      | 0000H       |

| F02CEH  | Flash write buffer register H            | FLWH    | R/W   | —                     | —       | V      | 0000H       |

| F02E0H  | DTC base address register                | DTCBAR  | R/W   | —                     | √ — FDH |        | FDH         |

| F02E8H  | DTC activation enable register 0         | DTCEN0  | R/W   | V                     | √ — 00H |        | 00H         |

| F02E9H  | DTC activation enable register 1         | DTCEN1  | R/W   | V                     | 1       | —      | 00H         |

| F02EAH  | DTC activation enable register 2         | DTCEN2  | R/W   | V                     | ~       | —      | 00H         |

| F02EBH  | DTC activation enable register 3         | DTCEN3  | R/W   | V                     | 1       | —      | 00H         |

| F02ECH  | DTC activation enable register 4         | DTCEN4  | R/W   | V                     | √ — 00Н |        | 00H         |

| F02F0H  | Flash memory CRC control register        | CRC0CTL | R/W   | V                     | √       | 00H    |             |

#### Date: Oct. 3, 2022

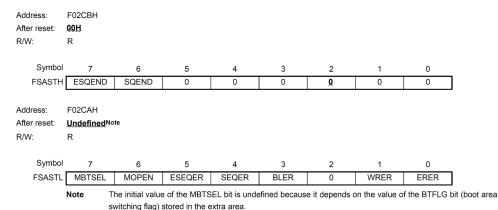

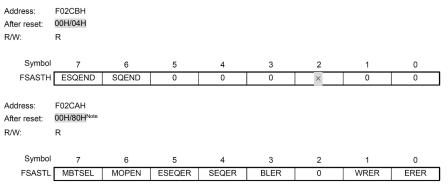

#### 33.6.2.12 Flash memory sequencer status registers H and L (FSASTH, FSASTL)

The FSASTH and FSASTL registers indicate the results of the respective operations of the flash memory sequencer when it has been used with the extra area or code/data flash memory areas.

The FSASTH and FSASTL registers can be read by a 1-bit or 8-bit memory manipulation instruction.

Figure 33 - 20 Format of Flash Memory Sequencer Status Registers H and L (FSASTH, FSASTL) (1/2)

#### 33.6.2.12 Flash memory sequencer status registers H and L (FSASTH, FSASTL)

The FSASTH and FSASTL registers indicate the results of the respective operations of the flash memory sequencer when it has been used with the extra area or code/data flash memory areas. The FSASTH and FSASTL registers can be read by a 1-bit or 8-bit memory manipulation instruction.

Figure 33 - 20 Format of Flash Memory Sequencer Status Registers H and L (FSASTH, FSASTL) (1/2)

Note The initial value of the MBTSEL bit is undefined because it depends on the value of the BTFLG bit (boot area switching flag) stored in the extra area.

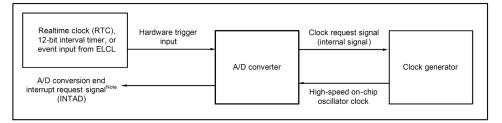

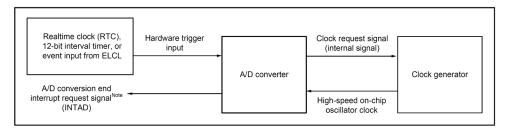

## 2. <u>12.8.2 A/D conversion by inputting a hardware trigger</u> (Page 578)

#### Incorrect:

Figure 12 - 42 Block Diagram When Using SNOOZE Mode Function (in Hardware Trigger Wait Mode)

When using the SNOOZE mode function, the initial setting of each register is specified before switching to the STOP mode (for details about these settings, see **Figure 12 - 45 Flowchart for Setting up SNOOZE Mode (Hardware Trigger)**). Just before moving to STOP mode, set bit 2 (AWC) of A/D converter mode register 2 (ADM2) to 1. After the initial settings are specified, set bit 0 (ADCE) of A/D converter mode register 0 (ADM0) to 1.

If a hardware trigger is input after switching to the STOP mode, the high-speed on-chip oscillator clock is supplied to the A/D converter. After supplying this clock, the A/D converter automatically counts up to the A/D power supply stabilization wait time, and then A/D conversion starts.

The SNOOZE mode operation after A/D conversion ends differs depending on whether an interrupt signal is generated Note.

- Note Depending on the setting of the A/D conversion result comparison function (ADRCK bit, ADUL/ADLL register), there is a possibility of no interrupt signal being generated.

- Caution Select the hardware trigger signal from among the realtime clock interrupt signal (INTRTC), 32-bit interval timer interrupt signal (INTITL), and event input from the ELCL.

Date: Oct. 3, 2022

#### Correct:

Figure 12 - 42 Block Diagram When Using SNOOZE Mode in Hardware Trigger Wait Mode

When using the SNOOZE mode, the initial setting of each register is specified before switching to the STOP mode (for details about these settings, see **Figure 12 - 45 Flowchart for Setting up SNOOZE Mode (Hardware Trigger)**). Just before moving to STOP mode, set bit 2 (AWC) of A/D converter mode register 2 (ADM2) to 1. After the initial settings are specified, set bit 0 (ADCE) of A/D converter mode register 0 (ADM0) to 1. If a hardware trigger is input after switching to the STOP mode, the high-speed on-chip oscillator clock is supplied to the A/D converter. After supplying this clock, the A/D converter automatically counts up to the A/D power supply stabilization wait time, and then A/D conversion starts. The SNOOZE mode operation after A/D conversion ends differs depending on whether an interrupt signal is generated<sup>Note</sup>.

Note

Depending on the setting of the A/D conversion result comparison function (ADRCK bit, ADUL/ADLL register), there is a possibility of no interrupt signal being generated.

When the 32-bit interval timer interrupt signal (INTITL) is selected as a hardware trigger, the detection flag in the ITLS0 register has to be cleared each time a 32-bit interval timer interrupt signal (INTITL) is generated.

the IILS0 register has to be cleared each time a 32-bit interval timer interrupt signal (INTITL) is generated. Therefore, clear the setting of the A/D conversion result comparison function (ADRCK bit and ADUL/ADLL register) to the initial value so that an A/D conversion end interrupt request signal (INTAD) is generated upon completion of A/D conversion.

Caution Select the hardware trigger signal from among the realtime clock interrupt signal (INTRTC), 32-bit interval timer interrupt signal (INTITL), and event input from the ELCL.

## 3. 17.2.9 UARTA clock select register 0 (UTA0CK) (Page 899)

## Incorrect:

Figure 17 - 10 Format of UARTA0 Clock Select Register (UTA0CK)

| Address:     | F0310H |

|--------------|--------|

| After reset: | 00H    |

|      | R/W |

|------|-----|

| R/W: | R/W |

| Symbol | 7       | 6 | 5       | 4       | 3       | 2       | 1       | 0       |

|--------|---------|---|---------|---------|---------|---------|---------|---------|

| UTA0CK | UTA0OEN | 0 | UTASEL1 | UTASEL0 | UTA0CK3 | UTA0CK2 | UTA0CK1 | UTA0CK0 |

| UTAQOEN | UARTA0 clock output function enable |

|---------|-------------------------------------|

| 0       | Disables CLKA0 output.              |

| 1       | Enables CLKA0 output.               |

| UTASEL1 | UTASEL0 | fseL clock select |

|---------|---------|-------------------|

| 0       | 0       | Stop              |

| 0       | 1       | fmxp              |

| 1       | 0       | fine              |

| 1       | 1       | fiMP              |

| UTA0CK3 | UTA0CK2          | UTA0CK1 | UTA0CK0 | UARTA0 operation clock select (futA0) |

|---------|------------------|---------|---------|---------------------------------------|

| 0       | 0                | 0       | 0       | fsel                                  |

| 0       | 0                | 0       | 1       | fsel/2                                |

| 0       | 0                | 1       | 0       | fsel/4                                |

| 0       | 0                | 1       | 1       | fsel/8                                |

| 0       | 1                | 0       | 0       | fsel/16                               |

| 0       | 1                | 0       | 1       | fsel/32                               |

| 0       | 1                | 1       | 0       | fsel/64                               |

| 1       | 0                | 0       | 0       | fsxp                                  |

| 1       | 0                | 0       | 1       | ELCL                                  |

|         | Other than above |         |         | Setting prohibited                    |

Caution This register should be read or written when the TXEAn and RXEAn bits are 0 (in the transmission/reception stopped state).

Date: Oct. 3, 2022

#### Correct:

Figure 17 - 10 Format of UARTA0 Clock Select Register (UTA0CK)

| Address:     | F0310H |  |

|--------------|--------|--|

| After reset: | 00H    |  |

| R/W:         | R/W    |  |

| Symbol | 7       | 6 | 5       | 4       | 3       | 2       | 1       | 0       |

|--------|---------|---|---------|---------|---------|---------|---------|---------|

| UTA0CK | UTA0OEN | 0 | UTASEL1 | UTASEL0 | UTA0CK3 | UTA0CK2 | UTA0CK1 | UTA0CK0 |

| UTA0OEN | UARTA0 clock output function enable |

|---------|-------------------------------------|

| 0       | Disables CLKA0 output.              |

| 1       | Enables CLKA0 output.               |

| UTASEL1 | UTASEL0 | fSEL clock select |

|---------|---------|-------------------|

| 0       | 0       | Stop              |

| 0       | 1       | fMXP              |

| 1       | 0       | fihp              |

| 1       | 1       | fIMP              |

| UTA0CK3 | UTA0CK2          | UTA0CK1 | UTA0CK0 | UARTA0 operation clock select (fUTA0) |

|---------|------------------|---------|---------|---------------------------------------|

| 0       | 0                | 0       | 0       | fsel                                  |

| 0       | 0                | 0       | 1       | fsel/2                                |

| 0       | 0                | 1       | 0       | fsel/4                                |

| 0       | 0                | 1       | 1       | fsel/8                                |

| 0       | 1                | 0       | 0       | fsel/16                               |

| 0       | 1                | 0       | 1       | fsel/32                               |

| 0       | 1                | 1       | 0       | fsel/64                               |

| 1       | 0                | 0       | 0       | fsxp                                  |

| 1       | 0                | 0       | 1       | ELCL                                  |

|         | Other than above |         |         | Setting prohibited                    |

Note Set this bit to 0 in the 36- to 52-pin products because the CLKA0 output pin is not present in the given products.

Caution This register should be read or written when the TXEAn and RXEAn bits are 0 (in the transmission/reception stopped state).

## 4. 17.2.10 UARTA clock select register 1 (UTA1CK) (Page 900)

#### Incorrect:

Figure 17 - 11 Format of UARTA1 Clock Select Register (UTA1CK)

| Address:    | F0311H |  |

|-------------|--------|--|

| After reach | 001    |  |

| After reset: | UUH |

|--------------|-----|

| R/W:         | R/W |

Symbol

7

UTA1CK UTA10EN

| R/W: | - F |

|------|-----|

|      |     |

6 5

4 3 2 1 0 0 UTA1CK3 UTA1CK2 UTA1CK1 UTA1CK0 0 0

| UTAQOEN | UARTA1 clock output function enable |

|---------|-------------------------------------|

| 0       | Disables CLKA1 output.              |

| 1       | Enables CLKA1 output.               |

|         |                                     |

| UTA1CK3 | UTA1CK2          | UTA1CK1 | UTA1CK0 | UARTA1 operation clock select (futA1) |

|---------|------------------|---------|---------|---------------------------------------|

| 0       | 0                | 0       | 0       | fsel                                  |

| 0       | 0                | 0       | 1       | fsel/2                                |

| 0       | 0                | 1       | 0       | fsel/4                                |

| 0       | 0                | 1       | 1       | fsel/8                                |

| 0       | 1                | 0       | 0       | fsel/16                               |

| 0       | 1                | 0       | 1       | fsel/32                               |

| 0       | 1                | 1       | 0       | fsel/64                               |

| 1       | 0                | 0       | 0       | fsxp                                  |

| 1       | 0                | 0       | 1       | ELCL                                  |

|         | Other than above |         |         | Setting prohibited                    |

Caution This register should be read or written when the TXEAn and RXEAn bits are 0 (in the transmission/reception stopped state).

Date: Oct. 3, 2022

#### Correct:

Figure 17 - 11 Format of UARTA1 Clock Select Register (UTA1CK)

| Address:     | F0311H |

|--------------|--------|

| After reset: | 00H    |

| R/W:         | R/W    |

| Symbol | 7       | 6 | 5 | 4 | 3       | 2       | 1       | 0       |   |

|--------|---------|---|---|---|---------|---------|---------|---------|---|

| UTA1CK | UTA10EN | 0 | 0 | 0 | UTA1CK3 | UTA1CK2 | UTA1CK1 | UTA1CK0 | l |

| UTA1OEN<br>Note | UARTA1 clock output function enable |  |

|-----------------|-------------------------------------|--|

| 0               | Disables CLKA1 output.              |  |

| 1               | Enables CLKA1 output.               |  |

| UTA1CK3          | UTA1CK2 | UTA1CK1 | UTA1CK0 | UARTA1 operation clock select (fUTA1) |

|------------------|---------|---------|---------|---------------------------------------|

| 0                | 0       | 0       | 0       | fsel                                  |

| 0                | 0       | 0       | 1       | fsel/2                                |

| 0                | 0       | 1       | 0       | fsel/4                                |

| 0                | 0       | 1       | 1       | fsel/8                                |

| 0                | 1       | 0       | 0       | fsel/16                               |

| 0                | 1       | 0       | 1       | fsel/32                               |

| 0                | 1       | 1       | 0       | fsel/64                               |

| 1                | 0       | 0       | 0       | fsxp                                  |

| 1                | 0       | 0       | 1       | ELCL                                  |

| Other than above |         |         |         | Setting prohibited                    |

Note Set this bit to 0 in the 44- to 52-pin products because the CLKA1 output pin is not present in the given products.

Caution This register should be read or written when the TXEAn and RXEAn bits are 0 (in the transmission/reception stopped state).

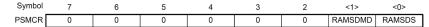

## 5. <u>23.2.2 Memory power reduction control register (PSMCR) (Page</u> <u>1105)</u>

#### Incorrect:

#### 23.2.2 Memory power reduction control register (PSMCR)

The PSMCR register is used to control the reduction of power consumption by the RAM. The leakage current can be reduced by placing the RAM in shutdown mode. The supply of power to the shut-down part of the RAM stops. Accordingly, that RAM does not retain data.

The PSMCR register can be set by a 1-bit or 8-bit memory manipulation instruction.

The value of this register is 00H following a reset.

Figure 23 - 2 Format of Memory Power Reduction Control Register (PSMCR)

Address: F0216H After reset: 00H R/W: R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | <1>     | <0>    |

|--------|---|---|---|---|---|---|---------|--------|

| PSMCR  | 0 | 0 | 0 | 0 | 0 | 0 | RAMSDMD | RAMSDS |

| RAMSDMD          | RAMSDS | Operating mode of the RAM          |

|------------------|--------|------------------------------------|

| 0                | 0      | Normal mode (continues to operate) |

| 1                | 0      | Standby mode                       |

| 1                | 1      | Shutdown mode                      |

| Other than above |        | Setting prohibited                 |

Caution 1. Shutdown mode applies to all RAM other than that in the range from FF000H to FFEFFH. The RAM that in the range from FF000H to FFEFFH continues to operate and retains data.

Caution 2. Do not access RAM while it is in the standby mode or shutdown mode.

Caution 3. When the RAM returns to normal mode from shutdown mode, the contents of the RAM other than in the range from FF000H to FFEFFH are undefined.

Date: Oct. 3, 2022

#### Correct:

#### 23.2.2 Memory power reduction control register (PSMCR)

The PSMCR register is used to control the reduction of power consumption by the RAM. The leakage current can be reduced by placing the RAM in shutdown mode. The supply of power to the shut-down part of the RAM stops. Accordingly, that RAM does not retain data. The PSMCR register can be set by a 1-bit or 8-bit memory manipulation instruction. The value of this register following a reset is 00H.

Figure 23 - 2 Format of Memory Power Reduction Control Register (PSMCR)

Address:F0216HAfter reset:00HR/W:R/W

| RAMSDMD          | RAMSDS | Operating mode of the RAM          |

|------------------|--------|------------------------------------|

| 0                | 0      | Normal mode (continues to operate) |

| 1                | 0      | Standby mode                       |

| 1                | 1      | Shutdown mode                      |

| Other than above |        | Setting prohibited                 |

Caution 1. Shutdown mode applies to all RAM other than that in the range from FF000H to FFEFFH. The RAM that in the range from FF000H to FFEFFH continues to operate and retains data.

- Caution 2. Do not access RAM while it is in the standby mode or shutdown mode.

- Caution 3. When the RAM returns to normal mode from shutdown mode, the contents of the RAM other than in the range from FF000H to FFEFFH are undefined.

- Caution 4. Access to the address ranges other than FF000H to FFEFFH in the RAM in the shutdown mode is still possible in on-chip debugging. When the RAM returns to normal mode from shutdown mode in on-chip debugging, the contents of the RAM other than in the range from FF000H to FFEFFH are not undefined.

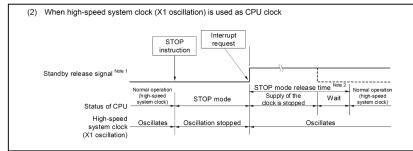

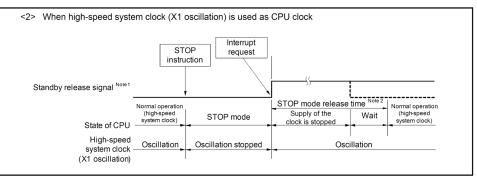

## 6. <u>23.3.2 STOP mode (Page 1116)</u>

#### Incorrect:

| Note 1. | For details of the standby release signal, see F | igure 21 - 1 Basic Configuration of Interrupt Function (1/2).                                   |

|---------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Note 2. | STOP mode release time                           |                                                                                                 |

|         | Supply of the clock is stopped:                  |                                                                                                 |

|         | When high-speed on-chip oscillator clock:        | 3.9 to 5.2 µs (FWKUP = 0: Starting of the high-speed on-chip oscillator is<br>at normal speed.) |

|         |                                                  | 0.6 to 0.8 µs (FWKUP = 1: Starting of the high-speed on-chip oscillator is                      |

|         |                                                  | at high speed.)                                                                                 |

|         |                                                  | The accuracy of the high-speed on-chip oscillator's frequency depends on                        |

|         |                                                  | whether starting of the high-speed on-chip oscillator is at normal speed or                     |

|         |                                                  | at high speed. See Section 37 Electrical Characteristics TA = -40 to                            |

|         |                                                  | +105°C.                                                                                         |

|         | When middle-speed on-chip oscillator clock:      | 1.5.to.2.5.µs                                                                                   |

|         | Wait:                                            |                                                                                                 |

|         | (common to the high-speed/middle-speed on        | -chip oscillator clock)                                                                         |

|         | When vectored interrupt servicing is carried     | out: 7 clock cycles                                                                             |

|         | When vectored interrupt servicing is not carr    | ried out: 1 clock cycle                                                                         |

- Caution To shorten oscillation stabilization time after the STOP mode is released when the CPU operates with the highspeed system clock (X1 oscillation), temporarily switch the CPU clock to the high-speed on-chip oscillator clock before the execution of the STOP instruction.

- Remark 1. The clock supply stop time varies depending on the temperature conditions and STOP mode period.

- Remark 2. The broken lines indicate the case when the interrupt request that has released the standby mode is acknowledged.

#### Figure 23 - 7 STOP Mode Release by Interrupt Request Generation (2/3)

- Note 1. For details of the standby release signal, see Figure 21 1 Basic Configuration of Interrupt Function (1/2).

- Note 2. STOP mode release time

Supply of the clock is stopped:

#### Oscillation stabilization time (set by OSTS)

Wait:

- When vectored interrupt servicing is carried out: 10.to.11.clock.cycles

- When vectored interrupt servicing is not carried out: 4 to 5 clock cycles

#### Correct:

|         | For details of the standby release signal, see Fig<br>STOP mode release time<br>Supply of the clock is stopped:                                       | gure 21 - 1 Basic Configuration                                         | of Interrupt Function.                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|         | For the high-speed on-chip oscillator clock                                                                                                           | 3.9 to 5.2 µs + 3 to 4 clock cycles on-chip oscillator is at normal spo | (FWKUP = 0: Starting of the high-speed eed.)                                             |

|         |                                                                                                                                                       | whether starting of the high-spee                                       | on-chip oscillator's frequency depends on<br>ad on-chip oscillator is at normal speed or |

|         | For the middle-speed on-chip oscillator clock                                                                                                         | at high speed. See Section 37 E                                         |                                                                                          |

|         | Wait:<br>(common to the high-speed/middle-speed on<br>• When vectored interrupt servicing is carried<br>• When vectored interrupt servicing is not ca | -chip oscillator clock)<br>d out: 7 clock cycles                        |                                                                                          |

| Caution | To shorten oscillation stabilization time af                                                                                                          | ter the STOP mode is released                                           | when the CPU operates with the high-                                                     |

- speed system clock (X1 oscillation), temporarily switch the CPU clock to the high-speed on-chip oscillator clock before the execution of the STOP instruction.

- Remark 1. The clock supply stop time varies depending on the temperature conditions and STOP mode period.Remark 2. The broken lines indicate the case when the interrupt request that has released the standby mode is acknowledged.

#### Figure 23 - 7 STOP Mode Release by Interrupt Request Generation (2/3)

Note 1. For details of the standby release signal, see Figure 21 - 1 Basic Configuration of Interrupt Function.

Note 2. STOP mode release time

Supply of the clock is stopped:

Oscillation stabilization time (set by OSTS) + 3 to 4 clock cycles

Wait:

- · When vectored interrupt servicing is carried out: 7 clock cycles

- When vectored interrupt servicing is not carried out: 1 clock cycles

## 7. 23.3.3 SNOOZE mode (Page 1119, Page 1120)

#### Incorrect:

#### 23.3.3 SNOOZE mode

SNOOZE mode setting and operating statuses The RL78/G23 can be placed in SNOOZE mode, in which operation of the following peripheral modules is selectable.

For details, see the sections on the individual modules.

- Section 12 A/D Converter (ADC)

- Section 15 Serial Array Unit (SAU)

- Section 18 Remote Control Signal Receiver (REMC)

- Section 19 Data Transfer Controller (DTC)

- Section 29 SNOOZE Mode Sequencer (SMS)

- Section 30 Capacitive Sensing Unit (CTSU2L)

Also, the RL78/G23 can be placed in SNOOZE mode if the CPU clock before entry to SNOOZE mode is the highspeed on-chip oscillator clock or middle-speed on-chip oscillator clock.

In SNOOZE mode transition, wait status to be only following time.

Transition time from STOP mode to SNOOZE mode:

When high-speed on-chip oscillator clock:

3.9 to 5.2  $\mu$ s (FWKUP = 0: Starting of the high-speed on-chip oscillator is at normal speed.)

**0. to 0.8 µs** (FWKUP = 1: Starting of the high-speed on-chip oscillator is at high speed.)

The accuracy of the high-speed on-chip oscillator's frequency depends on whether starting of the high-speed on-chip oscillator is at normal speed or at high speed. See Section 37 Electrical Characteristics TA = -40 to  $+105^{\circ}C$ .

When middle-speed on-chip oscillator clockNote: 1.3 to 2.5 µs

Remark Transition time from STOP mode to SNOOZE mode varies depending on the temperature conditions and the STOP mode period.

Date: Oct. 3, 2022

#### Correct:

#### 23.3.3 SNOOZE mode

- SNOOZE mode setting and operating states The RL78/G23 can be placed in SNOOZE mode, in which operation of the following peripheral modules is selectable. For details, see the sections on the individual modules.

- Section 12 A/D Converter (ADC)

- Section 15 Serial Array Unit (SAU)

- Section 18 Remote Control Signal Receiver (REMC)

- Section 19 Data Transfer Controller (DTC)

- Section 29 SNOOZE Mode Sequencer (SMS)

- Section 30 Capacitive Sensing Unit (CTSU2L)

Also, the RL78/G23 can be placed in SNOOZE mode if the CPU clock before entry to SNOOZE mode is the highspeed on-chip oscillator clock or middle-speed on-chip oscillator clock.

For transitions to SNOOZE mode, the following intervals of waiting are inserted.

Transition time from STOP mode to SNOOZE mode:

For the high-speed on-chip oscillator clock: 3.9 to 5.2 µs (FWKUP = 0: Starting of the high-speed on-chip

oscillator is at normal speed.)

0.6 to 0.8  $\mu$ s (FWKUP = 1: Starting of the high-speed on-chip oscillator is at high speed.)

The accuracy of the high-speed on-chip oscillator's frequency

depends on whether starting of the high-speed on-chip

oscillator is at normal speed or at high speed. See Section 37

#### Electrical Characteristics.

For the middle-speed on-chip oscillator clockNote: 1.3 to 2.5 µs

**Remark** The transition time from STOP mode to SNOOZE mode varies depending on the temperature conditions and the STOP mode period.

Transition time from SNOOZE mode to normal operation: When high-speed on-chip oscillator clock:

- When vectored interrupt servicing is carried out:

"0.3 to 0.4 µs" + 7 clock cycles

- When vectored interrupt servicing is not carried out:

##

- When middle-speed on-chip oscillator clockNote:

- When vectored interrupt servicing is carried out: **"0.6 to 1.2 us" + 7 clock cycles**

- When vectored interrupt servicing is not carried out: **"0.6 to 1.2 µs" + 1 clock cycles**

- Note This is selected when the setting of the MIOTRM register is its initial value.

The operating statuses in the SNOOZE mode are shown next.

#### Date: Oct. 3, 2022

Transition time from SNOOZE mode to normal operation:

- For the high-speed on-chip oscillator clock:

- When vectored interrupt servicing is carried out:

"0.3 to 0.4 μs" + 10 to 11 clock cycles

- When vectored interrupt servicing is not carried out:

"0.3 to 0.4 μs" + 4 to 5 clock cycles

- For the middle-speed on-chip oscillator clockNote:

- When vectored interrupt servicing is carried out:

"0.6 to 1.2 μs" + 10 to 11 clock cycles

- When vectored interrupt servicing is not carried out: "0.6 to 1.2 μs" + 4 to 5 clock cycles

- Note This is selected when the setting of the MIOTRM register is its initial value.

The operating states in the SNOOZE mode are shown on the following pages.

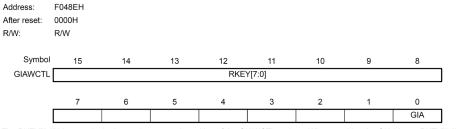

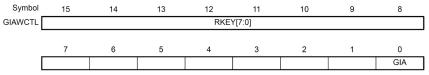

## 8. 27.3.8.1 Guard register of IAWCTL register (GIAWCTL) (Page 1172)

#### Incorrect:

#### 27.3.8.1 Guard register of IAWCTL register (GIAWCTL)

This register is used to protect the setting for enabling or disabling the illicit memory access detection. To allow rewriting of the invalid memory access detection control register (IAWCTL), set the GIAWCTL.GIA bit to 0 to disable protection of the IAWCTL register.

Figure 27 - 16 Format of Guard Register of IAWCTL Register (GIAWCTL)

The RKEY[7:0] bits contain the key code to control rewriting of the GIAWCTL register. When rewriting the GIA bit, set RKEY[7:0] to **C4H** and then write to all 16 bits of this register at once. The RKEY[7:0] bits return 00H when read.

| GIA | Control of rewriting the IAWCTL register                              |

|-----|-----------------------------------------------------------------------|

| 0   | Disables protection of the IAWCTL register (rewriting is allowed).    |

| 1   | Enables protection of the IAWCTL register (rewriting is not allowed). |

Date: Oct. 3, 2022

#### Correct:

#### 27.3.8.1 Guard register of IAWCTL register (GIAWCTL)

This register is used to protect the setting for enabling or disabling the illicit memory access detection. To allow rewriting of the invalid memory access detection control register (IAWCTL), set the GIAWCTL.GIA bit to 0 to disable protection of the IAWCTL register. The GIAWCTL register can be set by a 16-bit memory manipulation instruction. The value of this register following a reset is 0000H.

Figure 27 - 16 Format of Guard Register of IAWCTL Register (GIAWCTL)

Address: F048EH After reset: 0000H R/W: R/W

The RKEY[7:0] bits contain the key code to control rewriting of the GIAWCTL register. When rewriting the GIA bit, set RKEY[7:0] to A4H and then write to all 16 bits of this register at once. The RKEY[7:0] bits return 00H when read.

| ſ | GIA | Control of rewriting the IAWCTL register                              |

|---|-----|-----------------------------------------------------------------------|

| ſ | 0   | Disables protection of the IAWCTL register (rewriting is allowed).    |

|   | 1   | Enables protection of the IAWCTL register (rewriting is not allowed). |

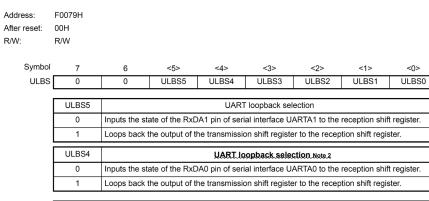

## 9. 27.3.12.1 UART loopback select register (ULBS) (Page 1181, Page 1182)

### Incorrect:

#### 27.3.12.1 UART loopback select register (ULBS)

The ULBS register is used to enable the UART loopback. This register has respective bits for independently controlling each UART channel. Setting the bit corresponding to each channel to 1 will select the UART loopback and loop back the output of the transmission shift register to the reception shift register.

The ULBS register can be set by a 1-bit or 8-bit memory manipulation instruction. The value of this register is 00H following a reset.

Figure 27 - 23 Format of UART Loopback Select Register (ULBS) (1/2)

|   | ULBS3 | UART Joopback selection Note 1                                                               |

|---|-------|----------------------------------------------------------------------------------------------|

| ſ | 0     | Inputs the state of the RxD3 pin of serial array unit UART3 to the reception shift register. |

|   | 1     | Loops back the output of the transmission shift register to the reception shift register.    |

| [ | ULBS2 | VART. loopback selection Note 1                                                              |

|---|-------|----------------------------------------------------------------------------------------------|

|   | 0     | Inputs the state of the RxD2 pin of serial array unit UART2 to the reception shift register. |

|   | 1     | Loops back the output of the transmission shift register to the reception shift register.    |

Date: Oct. 3. 2022

#### Correct:

#### 27.3.12.1 UART loopback select register (ULBS)

The ULBS register is used to enable the UART loopback. This register has respective bits for independently controlling each UART channel. Setting the bit corresponding to each channel to 1 will select the UART loopback and loop back the output of the transmission shift register to the reception shift register. The ULBS register can be set by a 1-bit or 8-bit memory manipulation instruction. The value of this register following a reset is 00H.

Figure 27 - 23 Format of UART Loopback Select Register (ULBS) (1/2)

F0079H Address: 00H After reset: R/W: R/W

| Symbol                                                                                      | 7     | 6                                                                                             | <5>   | <4>       | <3>   | <2>   | <1>   | <0>   |

|---------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------|-------|-----------|-------|-------|-------|-------|

| ULBS                                                                                        | 0     | 0                                                                                             | ULBS5 | ULBS4     | ULBS3 | ULBS2 | ULBS1 | ULBS0 |

|                                                                                             | ULBS5 | UART loopback selection                                                                       |       |           |       |       |       |       |

|                                                                                             | 0     | Inputs the state of the RxDA1 pin of serial interface UARTA1 to the reception shift register. |       |           |       |       |       |       |

|                                                                                             | 1     | Loops back the output of the transmission shift register to the reception shift register.     |       |           |       |       |       |       |

|                                                                                             |       |                                                                                               |       |           |       |       |       |       |

|                                                                                             | ULBS4 | UART loopback selection                                                                       |       |           |       |       |       |       |

| 0 Inpute the state of the PyDA0 pin of cariel interface LIAPTA0 to the recention shift regi |       |                                                                                               |       | tragiotor |       |       |       |       |

| 0 | inputs the state of the RXDAO pin of senal interface OARTAO to the reception sinit register. |

|---|----------------------------------------------------------------------------------------------|

| 1 | Loops back the output of the transmission shift register to the reception shift register.    |

| ULBS3 | UART loopback selection                                                                      |

|-------|----------------------------------------------------------------------------------------------|

| 0     | Inputs the state of the RxD3 pin of serial array unit UART3 to the reception shift register. |

| 1     | Loops back the output of the transmission shift register to the reception shift register.    |

| ULBS2 | UART loopback selection                                                                      |

|-------|----------------------------------------------------------------------------------------------|

| 0     | Inputs the state of the RxD2 pin of serial array unit UART2 to the reception shift register. |

| 1     | Loops back the output of the transmission shift register to the reception shift register.    |

<0>

#### Figure 27 - 23 Format of UART Loopback Select Register (ULBS) (2/2)

| ULBS1 | UART. loopback selection. Note 1                                                             |

|-------|----------------------------------------------------------------------------------------------|

| 0     | Inputs the state of the RxD1 pin of serial array unit UART1 to the reception shift register. |

| 1     | Loops back the output of the transmission shift register to the reception shift register.    |

| ULBS0 | UART. Loopback.selection.Note.1                                                              |

|-------|----------------------------------------------------------------------------------------------|

| 0     | Inputs the state of the RxD0 pin of serial array unit UART0 to the reception shift register. |

| 1     | Loops back the output of the transmission shift register to the reception shift register.    |

- Note 1....For UART0, set the PEQE10 bit of the port function output enable register 1 (PEQE1) to 1 when using the loopback.

- Note 2.....For UART0, set the PEOE14 bit of the port function output enable register 1 (PEOE1) to 1 when using the loopback.

Caution Be sure to clear bits 7 and 6 to 0.

#### Date: Oct. 3, 2022

Figure 27 - 23 Format of UART Loopback Select Register (ULBS) (2/2)

| ULBS1 | UART loopback selection                                                                      |

|-------|----------------------------------------------------------------------------------------------|

| 0     | Inputs the state of the RxD1 pin of serial array unit UART1 to the reception shift register. |

| 1     | Loops back the output of the transmission shift register to the reception shift register.    |

|       |                                                                                              |

| ULBS0 | LIART loopback selection                                                                     |

| ULBS0 | UART loopback selection                                                                      |

|-------|----------------------------------------------------------------------------------------------|

| 0     | Inputs the state of the RxD0 pin of serial array unit UART0 to the reception shift register. |

| 1     | Loops back the output of the transmission shift register to the reception shift register.    |

Caution Be sure to clear bits 7 and 6 to 0.

## 10. <u>28.2.2 Setting of flash read protection (Page 1188)</u>

#### Incorrect:

#### Table 28 - 2 Method of Setting Flash Read Protection

| Item to Be Set                                              | Method of Setting                                       | Method of Changing                                                                                                                                                                            |

|-------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block where flash read<br>protection starts                 | Using a flash memory programmer<br>or self-programming. | Using a flash memory programmer or self-programming. Note that the block where protection starts is not adjustable while changing of the flash read protection settings is disabled.          |

| Block where flash read<br>protection ends                   | Using a flash memory programmer<br>or self-programming. | Using a flash memory programmer or self-programming. Note that the block where protection ends is not adjustable while changing of the flash read protection settings is disabled.            |

| Disabling changing of the flash<br>read protection settings | Using a flash memory programmer<br>or self-programming. | Fixing of the flash read protection settings can be released by<br>using a flash memory programmer. <sup>Note</sup> If you do so, the values<br>for the start and end blocks are initialized. |

Note Release from the fixed setting is only possible when erasure of blocks is not prohibited, rewriting of boot area is not prohibited, and the code and data flash memory areas are blank.

- Caution 1. The settings for flash read protection in the extra area are not readable. To confirm that the settings for flash read protection are in place, read from the read-access disabled area and confirm that FFH is returned.

- Caution 2. To specify the read-access disabled area for flash read protection, be sure to specify the numbers of both the block where protection starts and the block where it ends.

- Caution 3. Reading from the read-access disabled area by using an on-chip debugger is also impossible. This means that program code allocated to the read access-disabled area cannot be debugged by using the on-chip debugger. Therefore, only make the settings for flash read protection after having debugged the program code in the protected areas.

- Caution 4. When a part of boot cluster 0 or boot cluster 1 is to be set as a part of the read-access disabled area, boot swapping may cause data in the read-access disabled area to be swapped with data in the read access-enabled area. To prevent this, when setting a part of boot cluster 0 or boot cluster 1 as part of the read-access disabled area, make the setting for prohibiting the rewriting of boot area so as to prohibit boot swapping itself.

#### Correct:

#### Table 28 - 2 Method of Setting Flash Read Protection

| Item to Be Set                                              | Method of Setting                                       | Method of Changing                                                                                                                                                                            |

|-------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block where flash read<br>protection starts                 | Using a flash memory programmer<br>or self-programming. | Using a flash memory programmer or self-programming. Note<br>that the block where protection starts is not adjustable while<br>changing of the flash read protection settings is disabled.    |

| Block where flash read<br>protection ends                   | Using a flash memory programmer<br>or self-programming. | Using a flash memory programmer or self-programming. Note<br>that the block where protection ends is not adjustable while<br>changing of the flash read protection settings is disabled.      |

| Disabling changing of the flash<br>read protection settings | Using a flash memory programmer<br>or self-programming. | Fixing of the flash read protection settings can be released by<br>using a flash memory programmer. <sup>Note</sup> If you do so, the values<br>for the start and end blocks are initialized. |

Note Release from the fixed setting is only possible when erasure of blocks is not prohibited, rewriting of boot area is not prohibited, and the code and data flash memory areas are blank.

- Caution 1. The settings for flash read protection in the extra area are not readable. To confirm that the settings for flash read protection are in place, read from the read-access disabled area and confirm that FFH is returned.

- Caution 2. To specify the read-access disabled area for flash read protection, be sure to specify the numbers of both the block where protection starts and the block where it ends.

- Caution 3. Reading from the read-access disabled area by using an on-chip debugger is also impossible. This means that program code allocated to the read access-disabled area cannot be debugged by using the on-chip debugger. Therefore, only make the settings for flash read protection after having debugged the program code in the protected areas.

- Caution 4. When a part of boot cluster 0 or boot cluster 1 is to be set as a part of the read-access disabled area, boot swapping may cause data in the read-access disabled area to be swapped with data in the read access-enabled area. To prevent this, when setting a part of boot cluster 0 or boot cluster 1 as part of the read-access disabled area, make the setting for prohibiting the rewriting of boot area so as to prohibit boot swapping itself.

- Caution 5. When settings for flash read protection have been made through self-programming, the settings become enabled after the MCU is reset and then released from the reset state.

## 11. 29.6 Operation in Standby Modes (Page 1233)

#### Incorrect:

#### 29.6 Operation in Standby Modes

| State       | Operation of the SNOOZE Mode Sequencer                                      |

|-------------|-----------------------------------------------------------------------------|

| HALT mode   | Operation continues.Note 1                                                  |

| STOP mode   | The activating trigger for the SNOOZE mode sequencer can be accepted.Note 3 |

| SNOOZE mode | Operation continues.Notes 2, 4, 5, 6                                        |

Note 1. When the subsystem clock is selected as fCLK, operation is disabled if the RTCLPC bit of the OSMC register is 1.

- Note 2. The SNOOZE mode can only be set when the high-speed on-chip oscillator clock or middle-speed on-chip oscillator clock is selected as fcLK.

- Note 3. Detection of an SMS activating trigger in STOP mode places the chip in SNOOZE mode, making the SNOOZE mode sequencer capable of operation. The state of the chip returns to the STOP mode after the operations of the SMS are completed. Note that the sequencer does not have access to certain memory areas in SNOOZE mode. For details, see 29.4.2 Memory space allocated to the sequencer.

- Note 4. When a transfer end interrupt from the CSIp in SNOOZE mode is being used as the activating trigger for the SNOOZE mode sequencer, use the interrupt plus termination command to release the chip from the SNOOZE mode and start processing by the CPU, or make the settings for reception by the CSIp (writing 1 to the STm0 bit, writing 0 to the SWCm bit, setting the SSCm register, and writing 1 to the SSm0 bit) again before the processing for termination.

- Note 5. When a transfer end interrupt from the UARTq in SNOOZE mode is being used as the activating trigger for the SNOOZE mode sequencer, use the interrupt plus termination command to release the chip from the SNOOZE mode and start processing by the CPU, or make the settings for reception by the UARTq (writing 1 to the STm1 bit, writing 0 to the SWCm bit, setting the SSCm register, and writing 1 to the SSm1 bit) again before the processing for termination.

- Note 6. When an A/D conversion end interrupt from the A/D converter in SNOOZE mode is being used as the activating trigger for the SNOOZE mode sequencer, use the interrupt plus termination command to release the chip from the SNOOZE mode and start processing by the CPU, or make the settings for the SNOOZE mode function of the A/D converter (writing 1 to the AWC bit after having written 0 to it) again before the processing for termination.

#### Correct:

#### 29.6 Operation in Standby Modes

| State       | Operation of the SNOOZE Mode Sequencer                                               |

|-------------|--------------------------------------------------------------------------------------|

| HALT mode   | Operation continues.Note 1                                                           |

| STOP mode   | The activating trigger for the SNOOZE mode sequencer can be accepted. Note ${\bf 3}$ |

| SNOOZE mode | Operation continues.Notes 2, 4, 5, 6                                                 |

Note 1. When the subsystem clock is selected as fCLK, operation is disabled if the RTCLPC bit of the OSMC register is 1.

- Note 2. The SNOOZE mode can only be set when the high-speed on-chip oscillator clock or middle-speed on-chip oscillator clock is selected as fcLk.

- Note 3. Detection of an SMS activating trigger in STOP mode places the chip in SNOOZE mode, making the SNOOZE mode sequencer capable of operation. The state of the chip returns to the STOP mode after the operations of the SMS are completed. Note that the sequencer does not have access to certain memory areas in SNOOZE mode. For details, see 29.4.2 Memory space allocated to the sequencer.

- Note 4. When a transfer end interrupt from the CSIp in SNOOZE mode is being used as the activating trigger for the SNOOZE mode sequencer, use the interrupt plus termination command to release the chip from the SNOOZE mode and start processing by the CPU, or make the settings for reception by the CSIp (writing 1 to the STm0 bit, writing 0 to the SWCm bit, setting the SSCm register, and writing 1 to the SSm0 bit) again before the processing for termination.

- Note 5. When a transfer end interrupt from the UARTq in SNOOZE mode is being used as the activating trigger for the SNOOZE mode sequencer, use the interrupt plus termination command to release the chip from the SNOOZE mode and start processing by the CPU, or make the settings for reception by the UARTq (writing 1 to the STm1 bit, writing 0 to the SWCm bit, setting the SSCm register, and writing 1 to the SSm1 bit) again before the processing for termination.

- Note 6. When an A/D conversion end interrupt from the A/D converter in SNOOZE mode is being used as the activating trigger for the SNOOZE mode sequencer, use the interrupt plus termination command to release the chip from the SNOOZE mode and start processing by the CPU, or make the settings for the SNOOZE mode function of the A/D converter (writing 1 to the AWC

- Caution Access to the following realtime clock registers through the SNOOZE mode sequencer is not possible in the standby mode.

• RTCC0, RTCC1, SEC, MIN, HOUR, DAY, WEEK, MONTH, YEAR, SUBCUD, ALARMWM, ALARMWH, and ALARMWW

## 12. Access to the extra area (Page 1319, Page 1322, Page 1341)

## Incorrect:

33.6.2.16 Data flash control register (DFLCTL)

The DFLCTL register enables or disables access to the data flash memory area**and\_extra area** The DFLCTL register can be set by a 1-bit or 8-bit memory manipulation instruction. The value of this register following a reset is 00H.

Figure 33 - 24 Format of Data Flash Control Register (DFLCTL)

Address: F0090H After reset: 00H R/W: R/W

| Symbol | 7 | 6 | 5 | 4 | 3 | 2 | 1 | <0>   |

|--------|---|---|---|---|---|---|---|-------|

| DFLCTL | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DFLEN |

| DFLEN | Data flash memory area lextra area access control                |

|-------|------------------------------------------------------------------|

| 0     | Access to the data flash memory area and extra area is disabled. |

| 1     | Access to the data flash memory area and extra area is enabled.  |

Date: Oct. 3, 2022

#### Correct:

#### 33.6.2.16 Data flash control register (DFLCTL)

The DFLCTL register enables or disables access to the data flash memory area. The DFLCTL register can be set by a 1-bit or 8-bit memory manipulation instruction. The value of this register following a reset is 00H.

Figure 33 - 24 Format of Data Flash Control Register (DFLCTL)

Address: F0090H After reset: 00H R/W: R/W

| Symbol | 7     | 6             | 5                                                | 4 | 3 | 2 | 1 | <0>   |  |  |  |  |

|--------|-------|---------------|--------------------------------------------------|---|---|---|---|-------|--|--|--|--|

| DFLCTL | 0     | 0             | 0                                                | 0 | 0 | 0 | 0 | DFLEN |  |  |  |  |

|        |       |               |                                                  |   |   |   |   |       |  |  |  |  |

|        | DFLEN |               | Data flash memory area access control            |   |   |   |   |       |  |  |  |  |

|        | 0     | Access to the | ccess to the data flash memory area is disabled. |   |   |   |   |       |  |  |  |  |

|        | 1     | Access to the | ccess to the data flash memory area is enabled.  |   |   |   |   |       |  |  |  |  |

#### 33.6.3 Setting the flash memory control mode

The flash memory has the following flash memory control modes.

Code flash memory programming mode

The code flash memory area and the extra area can be rewritten.

- Data flash memory programming mode

- The data flash memory area and the extra area can be rewritten.

- Non-programmable mode

The flash memory (code flash memory area, data flash memory area, and extra area) cannot be rewritten.

To rewrite the flash memory, set the flash memory control mode to code flash memory programming mode or data flash memory programming mode. Setting each of the flash memory control modes requires executing the specific sequence for setting the flash protect command register (PFCMD) and flash programming mode control register (FLPMC).

Caution For handling of the extra area or data flash memory area, follow the procedure while access to the data flash memory is enabled (the value of the DFLEN bit of the DFLCTL register is 1).

#### 33.6.9 Notes on self-programming

- Rewriting the code flash memory or extra area To rewrite the code flash memory or extra area, place the code or values in the RAM

- (2) Precondition for manipulating the data flash memory area and extra area Before manipulating the data flash memory area and extra area set the DFLEN bit of the data flash control register (DFLCTL) to 1 (enabling access to the data flash memory).

## Date: Oct. 3, 2022

## 33.6.3 Setting the flash memory control mode

#### The flash memory has the following flash memory control modes.

- Code flash memory programming mode

- The code flash memory area and the extra area can be rewritten.

- Data flash memory programming mode

- The data flash memory area can be rewritten.

- Non-programmable mode

- The flash memory (code flash memory area, data flash memory area, and extra area) cannot be rewritten.

To rewrite the flash memory, set the flash memory control mode to code flash memory programming mode or data flash memory programming mode. Setting each of the flash memory control modes requires executing the specific sequence for setting the flash protect command register (PFCMD) and flash programming mode control register (FLPMC).

## Caution For handling of the data flash memory area, follow the procedure while access to the data flash memory is enabled (the value of the DFLEN bit of the DFLCTL register is 1).

## 33.6.9 Notes on self-programming

- Rewriting the code flash memory or extra area To rewrite the code flash memory or extra area, place the code or values in the RAM.

- Precondition for manipulating the data flash memory area Before manipulating the data flash memory area, set the DFLEN bit of the data flash control register (DFLCTL) to 1 (enabling access to the data flash memory).

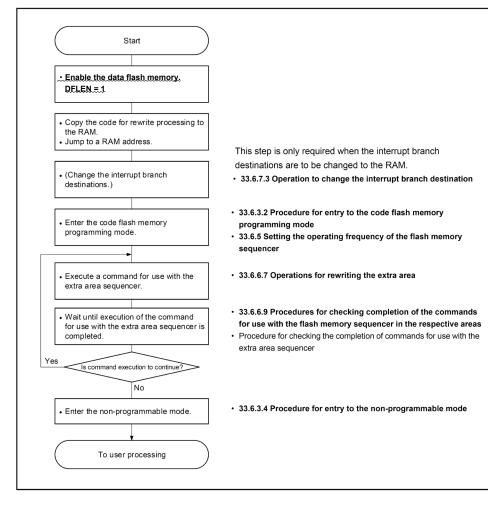

## 13. <u>33.6.8.3 Example of executing the commands to rewrite the extra</u> area (Page 1340)

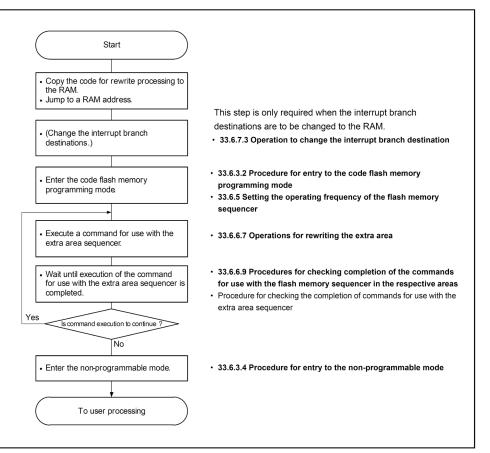

Incorrect:

33.6.8.3 Example of executing the commands to rewrite the extra area

Figure 33 - 29 shows the flow of executing the commands to rewrite the extra area.

Figure 33 - 29 Flow of Executing the Commands to Rewrite the Extra Area

Date: Oct. 3, 2022

#### Correct:

33.6.8.3 Example of executing the commands to rewrite the extra area

Figure 33 - 29 shows the flow of executing the commands to rewrite the extra area.

© 2022 Renesas Electronics Corporation. All rights reserved.

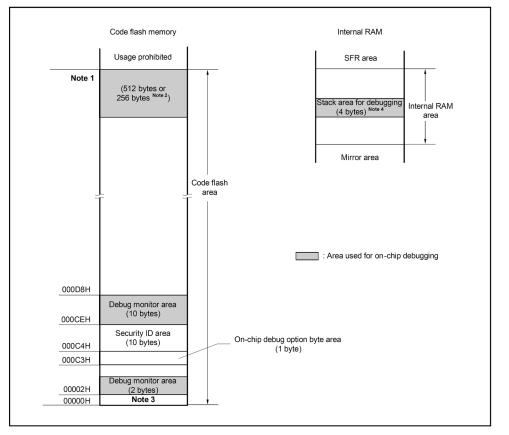

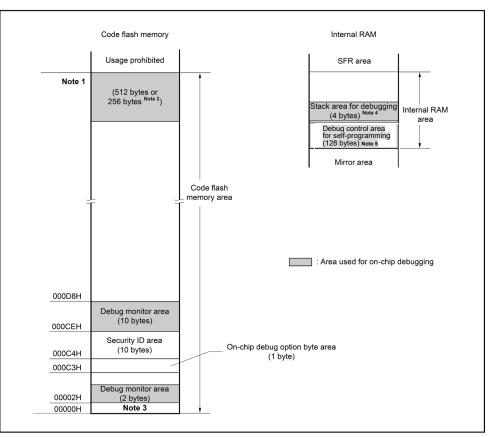

## 14. 34.4 Allocation of Memory Spaces to User Resources (Page 1352)

#### Incorrect:

Figure 34 - 2 Memory Spaces Allocated for Use by the Monitor Program for Debugging

Date: Oct. 3, 2022

#### Correct:

Figure 34 - 2 Memory Spaces Allocated for Use by the Monitor Program for Debugging

#### Note 1. The address depends on the products as shown below.

| Products                                      | Address of Note 1 |

|-----------------------------------------------|-------------------|

| R7F100GxF (x = A to C, E to G, J, L)          | 17FFFH            |

| R7F100GxG (x = A to C, E to G, J, L, M, P)    | 1FFFFH            |

| R7F100GxH (x = A to C, E to G, J, L, M, P)    | 2FFFFH            |

| R7F100GxJ (x = A to C, E to G, J, L, M, P, S) | 3FFFFH            |

| R7F100GxK (x = F, G, J, L, M, P, S)           | 5FFFFH            |

| R7F100GxL (x = F, G, J, L, M, P, S)           | 7FFFH             |

| R7F100GxN (x = F, G, J, L, M, P, S)           | BFFFFH            |

Note 2. When the realtime RAM monitor (RRM) and dynamic memory modification (DMM) are not to be used, the size of this area is 256 bytes.

Note 3. During debugging, the reset vector is relocated to the address of the monitor program.

Note 4. Since this area is allocated immediately below the portion of the main stack area that is currently in use, the address range of this area depends on the amount of the stack in use other than for debugging. Accordingly, four additional bytes are required for the entire stack area. In the case of self-programming, this is a 12-byte area, so 12 additional bytes are required.

#### Date: Oct. 3, 2022

Note 1. The address depends on the products as shown below.

| Products                                      | Address of Note 1 |

|-----------------------------------------------|-------------------|

| R7F100GxF (x = A to C, E to G, J, L)          | 17FFFH            |

| R7F100GxG (x = A to C, E to G, J, L, M, P)    | 1FFFFH            |

| R7F100GxH (x = A to C, E to G, J, L, M, P)    | 2FFFFH            |

| R7F100GxJ (x = A to C, E to G, J, L, M, P, S) | 3FFFFH            |

| R7F100GxK (x = F, G, J, L, M, P, S)           | 5FFFFH            |

| R7F100GxL (x = F, G, J, L, M, P, S)           | 7FFFH             |

| R7F100GxN (x = F, G, J, L, M, P, S)           | BFFFFH            |

- Note 2. When the realtime RAM monitor (RRM) and dynamic memory modification (DMM) are not to be used, the size of this area is 256 bytes.

- Note 3. During debugging, the reset vector is relocated to the address of the monitor program.

- Note 4. Since this area is allocated immediately below the portion of the main stack area that is currently in use, the address range of this area depends on the amount of the stack in use other than for debugging. Accordingly, four additional bytes are required for the entire stack area. In the case of self-programming, this is a 12-byte area, so 12 additional bytes are required.

- Note 5. The on-chip debugger uses the 128-byte RAM areas of the products listed in the table below for breaks in self-programming. The correspondences between target products and RAM areas are given in the table.

| Products                                  | RAM Area to be Used (128 bytes) |

|-------------------------------------------|---------------------------------|

| R7F100GxG (x = A, B, C, E, F, G, J, L)    | FBF00H to FBF7FH                |

| R7F100GxJ (x = A, B, C, E, F, G, J, L, M) | F9F00H to F9F7FH                |

| R7F100GxL (x = F, G, J, L, M, P, S)       | F3F00H to F3F7FH                |

| R7F100GxN (x = F, G, J, L, M, P, S)       | F3F00H to F3F7FH                |

If the setting to disable debugging by the on-chip debugger during self-programming has been made, the RAM areas stated above are not used.

For details on the settings for debugging during self-programming, see the user's manual for the integrated development environment in use.

15. Section 37 Electrical Characteristics (Page 1378)

Incorrect:

## Section 37 Electrical Characteristics TA = -40 to +105°C

Date: Oct. 3, 2022

Correct:

## Section 37 Electrical Characteristics

This section describes the electrical characteristics of the following products.

2D: Consumer applications, T<sub>A</sub> = -40 to +85°C

R7F100Gxx2Dxx

3C: Industrial applications, T<sub>A</sub> = -40 to +105°C

R7F100Gxx3Cxx

Caution 1. RL78 microcontrollers have on-chip debugging functionality for use in the development and evaluation of user systems. Do not use on-chip debugging with products designated as part of mass production, because using this function may cause the guaranteed number of times the flash memory is rewritten to be exceeded, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when on-chip debugging is used with products designated as part of mass production.

Caution 2. For the consumer application products, the ambient operating temperature of T<sub>A</sub> = -40°C to +85°C applies.

Caution 3. For products that do not have an EVDD0, EVDD1, EVSS0, or EVSS1 pin, read EVDD0 and EVDD1 as VDD, and EVSS0 and EVSS1 as VSS.

Caution 4. The present pins differ depending on the products. For details, see section 2.1 Functions of Port Pins through section 2.2.1 Functions for each product.

© 2022 Renesas Electronics Corporation. All rights reserved.

## 16. <u>37.1 Absolute Maximum Ratings (Page 1378, Page 1379)</u>

## Incorrect:

| Item                   | Symbols      | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ratings                                                             | Unit |