Date: Jan. FH, 2016

# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation.

| Product<br>Category   | MPU & MCU                                                                                                                                |                         | Document<br>No.        | TN-ÜÝ*-ŒFIIA/EÆÆÆev. 1.00              |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|----------------------------------------|--|

| Title                 | Revision of the RX23T Group User's Manual changes in the section of Electrical Character additional functions and correction of descript | Information<br>Category | Technical Notification |                                        |  |

|                       |                                                                                                                                          | Lot No.                 |                        | RX23T Group User's Manual:             |  |

| Applicable<br>Product | RX23T Group                                                                                                                              | All                     | Reference<br>Document  | Hardware Rev.1.00<br>(R01UH0520EJ0100) |  |

This is to inform you of erroneous description in the section of Electrical Characteristics in the RX23T Group, and of the following additional functions.

- (1) High-speed on-chip oscillation function and general-purpose port added to the clock pins

- (2) Expansion of the RAM capacity from 10 Kbytes to 12 Kbytes

Therefore, we revise the RX23T Group User's Manual: Hardware Rev.1.00 according the addition and correction of the functions mentioned above.

In addition, we also inform you of the corrections in other sections of the manual.

## <Changes in the Section of Electrical Characteristics>

•Page 1051, Table 35.3 DC Characteristics (1) is corrected as follows: Before correction

|                               | Item                                                                                                                                                 | Symbol          | Min.        | Тур. | Max.        | Unit | Test<br>Conditions |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|------|-------------|------|--------------------|

| Schmitt trigger input voltage | RIIC input pin (except for SMBus, 5 V tolerant)                                                                                                      | $V_{IH}$        | VCC × 0.7   | _    | 5.8         | V    |                    |

|                               | Ports B1 and B2<br>(5 V tolerant)                                                                                                                    |                 | VCC × 0.8   | _    | 5.8         |      |                    |

|                               | Ports 00 to 02, 10,11 Ports 22 to 24 Ports 30 to 33 Ports 70 to 76 Ports 91 to 94 Ports A2 to A5 Ports B0, B3 to B7 Ports D3 to D7 Port E2 Port RES# |                 | VCC × 0.8   | _    | VCC + 0.3   |      |                    |

|                               | Ports 40 to 47                                                                                                                                       |                 | AVCC0 × 0.8 | _    | AVCC0 + 0.3 |      |                    |

|                               | RIIC input pin (except for SMBus)                                                                                                                    | V <sub>IL</sub> | -0.3        | _    | VCC × 0.3   |      |                    |

|                               | Other than RIIC input pin                                                                                                                            |                 | -0.3        | _    | VCC × 0.2   |      |                    |

|                               | RIIC input pin (except for SMBus)                                                                                                                    | $\Delta V_{T}$  | VCC × 0.05  | _    | _           |      |                    |

|                               | Other than RIIC input pin                                                                                                                            |                 | VCC × 0.1   | _    | _           |      |                    |

| Input level                   | MD                                                                                                                                                   | V <sub>IH</sub> | VCC × 0.9   | _    | VCC + 0.3   | V    |                    |

| voltage (except for Schmitt   | EXTAL (external clock input)                                                                                                                         |                 | VCC × 0.8   | _    | VCC + 0.3   |      |                    |

| trigger input                 | RIIC input pin (SMBus)                                                                                                                               |                 | 2.1         | _    | VCC + 0.3   |      |                    |

| pins)                         | MD                                                                                                                                                   | V <sub>IL</sub> | -0.3        | _    | VCC × 0.1   |      |                    |

| -                             | EXTAL (external clock input)                                                                                                                         |                 | -0.3        | _    | VCC × 0.2   |      |                    |

|                               | RIIC input pin (SMBus)                                                                                                                               |                 | -0.3        | _    | 0.8         |      |                    |

#### Corrections Test Unit Item Symbol Min. Тур. Max. Conditions RIIC input pin VCC × 0.7 Schmitt trigger $V_{IH}$ 5.8 (except for SMBus, 5 V tolerant) input voltage Ports B1 and B2 VCC × 0.8 5.8 (5 V tolerant) Ports 00 to 02, 10, 11 VCC × 0.8 VCC + 0.3 Ports 22 to 24 Ports 30 to 33, 36, 37 Ports 70 to 76 Ports 91 to 94 Ports A2 to A5 Ports B0, B3 to B7 Ports D3 to D7 Port E2 Port RES# Ports 40 to 47 AVCC0 × 0.8 AVCC0 + 0.3 RIIC input pin (except for SMBus) -0.3VCC × 0.3 $V_{IL}$ Ports 40 to 47 -0.3 AVCC0 × 0.2 Other than RIIC input pin or ports -0.3VCC × 0.2 40 to 47 RIIC input pin (except for SMBus) $\Delta V_{\mathsf{T}}$ VCC × 0.05 Ports 40 to 47 AVCC0 × 0.1 Other than RIIC input pin or ports VCC × 0.1 40 to 47 Input level MD $V_{\text{IH}}$ **VCC × 0.9** VCC + 0.3 V voltage (except VCC × 0.8 VCC + 0.3 EXTAL (external clock input) for Schmitt 2.1 RIIC input pin (SMBus) VCC + 0.3 trigger input pins) $\mathsf{V}_{\mathsf{IL}}$ -0.3 MD VCC × 0.1 EXTAL (external clock input) -0.3 VCC × 0.2 RIIC input pin (SMBus) -0.3 8.0

•Page 1066, Table 35.14 Operating Frequency Value (High-Speed Operating Mode) is corrected as follows:

## **Before correction**

|                   | Item                            | Symbol           | min. | typ. | max. | Unit |

|-------------------|---------------------------------|------------------|------|------|------|------|

| Maximum operating | System clock (ICLK)             | f <sub>max</sub> | 1    | _    | 40   | MHz  |

| frequency         | FlashIF clock (FCLK)*1, *2      |                  | 1    | _    | 32   | _    |

|                   | Peripheral module clock (PCLKA) |                  | 1    | _    | 40   | _    |

|                   | Peripheral module clock (PCLKB) |                  | 1    | _    | 40   | _    |

|                   | Peripheral module clock (PCLKD) | _                | 1    | _    | 40   | _    |

## Corrections

|                   | Item                            | Symbol           | min. | typ. | max. | Unit |

|-------------------|---------------------------------|------------------|------|------|------|------|

| Maximum operating | System clock (ICLK)             | f <sub>max</sub> | _    | _    | 40   | MHz  |

| frequency         | FlashIF clock (FCLK)*1, *2      |                  | _    | _    | 32   | _    |

|                   | Peripheral module clock (PCLKA) | <u> </u>         | _    | _    | 40   | _    |

|                   | Peripheral module clock (PCLKB) |                  | _    | _    | 40   | _    |

|                   | Peripheral module clock (PCLKD) |                  | _    | _    | 40   | _    |

•Page 1066, Table 35.15 Operating Frequency Value (Middle-Speed Operating Mode) is corrected as follows:

## **Before correction**

|                   | Item                            | Symbol           | min. | typ. | max. | Unit        |

|-------------------|---------------------------------|------------------|------|------|------|-------------|

| Maximum operating | System clock (ICLK)             | f <sub>max</sub> | 1    | _    | 12   | MHz         |

| frequency         | FlashIF clock (FCLK)*1, *2      |                  | 1    | _    | 12   | <del></del> |

|                   | Peripheral module clock (PCLKA) |                  | 1    | _    | 12   | <del></del> |

|                   | Peripheral module clock (PCLKB) |                  | 1    | _    | 12   | <del></del> |

|                   | Peripheral module clock (PCLKD) |                  | 1    | _    | 12   | <del></del> |

|                   | Item                            | Symbol           | min. | typ. | max. | Unit         |

|-------------------|---------------------------------|------------------|------|------|------|--------------|

| Maximum operating | System clock (ICLK)             | f <sub>max</sub> | _    | _    | 12   | MHz          |

| frequency         | FlashIF clock (FCLK)*1, *2      |                  | _    | _    | 12   | <del>_</del> |

|                   | Peripheral module clock (PCLKA) |                  | _    | _    | 12   | <del>_</del> |

|                   | Peripheral module clock (PCLKB) |                  | _    | _    | 12   | <del>_</del> |

|                   | Peripheral module clock (PCLKD) | _                | _    | _    | 12   | _            |

# •Page 1067, Table 35.16 Clock Timing is corrected as follows: Before correction

| Item                                                            | Symbol               | Min.  | Тур. | Max.  | Unit | Test Conditions |

|-----------------------------------------------------------------|----------------------|-------|------|-------|------|-----------------|

| EXTAL external clock input cycle time                           | t <sub>Xcyc</sub>    | 50    | _    | _     | ns   | Figure 35.20    |

| EXTAL external clock input high pulse width                     | t <sub>XH</sub>      | 20    | _    | _     | ns   | _               |

| EXTAL external clock input low pulse width                      | t <sub>XL</sub>      | 20    | _    | _     | ns   | _               |

| EXTAL external clock rise time                                  | t <sub>Xr</sub>      | _     | _    | 5     | ns   | _               |

| EXTAL external clock fall time                                  | t <sub>Xf</sub>      | _     | _    | 5     | ns   | _               |

| EXTAL external clock input wait time*1                          | t <sub>EXWT</sub>    | 0.5   | _    | _     | μs   |                 |

| Main clock oscillator oscillation frequency*2                   | f <sub>MAIN</sub>    | 1     | _    | 20    | MHz  | _               |

| Main clock oscillation stabilization time (crystal)*2           | t <sub>MAINOSC</sub> | _     | 3    | _     | ms   | Figure 35.21    |

| Main clock oscillation stabilization time (ceramic resonator)*2 | t <sub>MAINOSC</sub> | _     | 50   | _     | μs   | _               |

| LOCO clock oscillation frequency                                | f <sub>LOCO</sub>    | 3.44  | 4.0  | 4.56  | MHz  |                 |

| LOCO clock oscillation stabilization time                       | t <sub>LOCO</sub>    | _     | _    | 0.5   | μs   | Figure 35.22    |

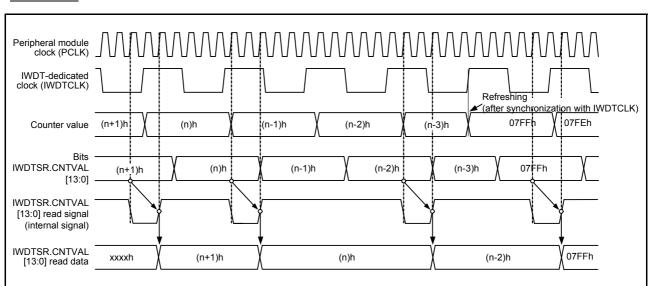

| IWDT-dedicated clock oscillation frequency                      | f <sub>ILOCO</sub>   | 12.75 | 15   | 17.25 | kHz  |                 |

| IWDT-dedicated clock oscillation stabilization time             | t <sub>ILOCO</sub>   | _     | _    | 50    | μs   | Figure 35.23    |

| PLL circuit oscillation frequency                               | f <sub>PLL</sub>     | 24    | _    | 40    | MHz  |                 |

| PLL clock oscillation stabilization time                        | t <sub>PLL</sub>     | _     | _    | 50    | μs   | Figure 35.24    |

| PLL free-running oscillation frequency                          | f <sub>PLLFR</sub>   | _     | 8    | _     | MHz  |                 |

| Item                                                            | Symbol               | Min.  | Тур. | Max.  | Unit | Test Conditions                              |

|-----------------------------------------------------------------|----------------------|-------|------|-------|------|----------------------------------------------|

| EXTAL external clock input cycle time                           | t <sub>Xcyc</sub>    | 50    | _    | _     | ns   | Figure 35.20                                 |

| EXTAL external clock input high pulse width                     | t <sub>XH</sub>      | 20    | _    | _     | ns   | _                                            |

| EXTAL external clock input low pulse width                      | t <sub>XL</sub>      | 20    | _    | _     | ns   | _                                            |

| EXTAL external clock rise time                                  | t <sub>Xr</sub>      | _     | _    | 5     | ns   | _                                            |

| EXTAL external clock fall time                                  | t <sub>Xf</sub>      | _     | _    | 5     | ns   | <del>-</del>                                 |

| EXTAL external clock input wait time*1                          | t <sub>EXWT</sub>    | 0.5   | _    | _     | μs   |                                              |

| Main clock oscillator oscillation frequency*2                   | f <sub>MAIN</sub>    | 1     | _    | 20    | MHz  | _                                            |

| Main clock oscillation stabilization time (crystal)*2           | t <sub>MAINOSC</sub> | _     | 3    | _     | ms   | Figure 35.21                                 |

| Main clock oscillation stabilization time (ceramic resonator)*2 | t <sub>MAINOSC</sub> | _     | 50   | _     | μs   | _                                            |

| LOCO clock oscillation frequency                                | f <sub>LOCO</sub>    | 3.44  | 4.0  | 4.56  | MHz  |                                              |

| LOCO clock oscillation stabilization time                       | t <sub>LOCO</sub>    | _     | _    | 0.5   | μs   | Figure 35.22                                 |

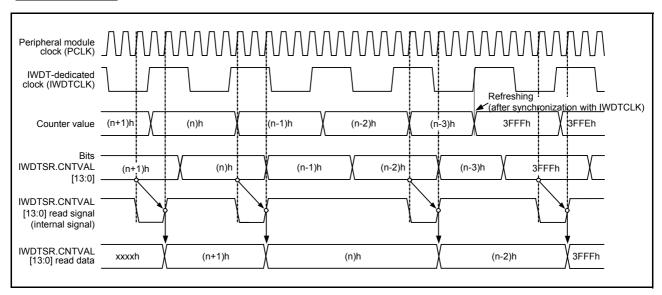

| IWDT-dedicated clock oscillation frequency                      | f <sub>ILOCO</sub>   | 12.75 | 15   | 17.25 | kHz  |                                              |

| IWDT-dedicated clock oscillation stabilization time             | t <sub>ILOCO</sub>   | _     | _    | 50    | μs   | Figure 35.23                                 |

| HOCO clock oscillation frequency                                | f <sub>HOCO</sub>    | 31.52 | 32   | 32.48 | MHz  | $T_a = -40 \text{ to } +85^{\circ}\text{C}$  |

|                                                                 | _                    | 31.68 | 32   | 32.32 |      | $T_a = -20 \text{ to } +85^{\circ}\text{C}$  |

|                                                                 | _                    | 31.36 | 32   | 32.64 |      | $T_a = -40 \text{ to } +105^{\circ}\text{C}$ |

| HOCO clock oscillation stabilization time                       | t <sub>HOCO</sub>    | _     | _    | 30    | μs   | Figure 35.25                                 |

| PLL circuit oscillation frequency                               | f <sub>PLL</sub>     | 24    | _    | 40    | MHz  |                                              |

| PLL clock oscillation stabilization time                        | t <sub>PLL</sub>     | _     | _    | 50    | μs   | Figure 35.26                                 |

| PLL free-running oscillation frequency                          | f <sub>PLLFR</sub>   | _     | 8    | _     | MHz  |                                              |

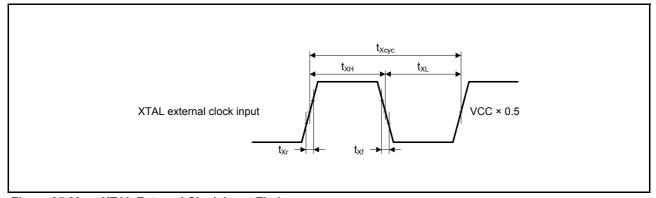

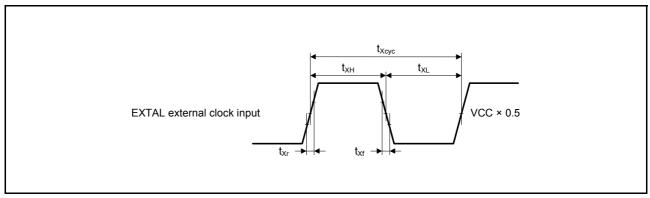

•Page 1067, Figure 35.20 XTAL External Clock Input Timing is corrected as follows: Before correction

Figure 35.20 XTAL External Clock Input Timing

#### Corrections

Figure 35.20 EXTAL External Clock Input Timing

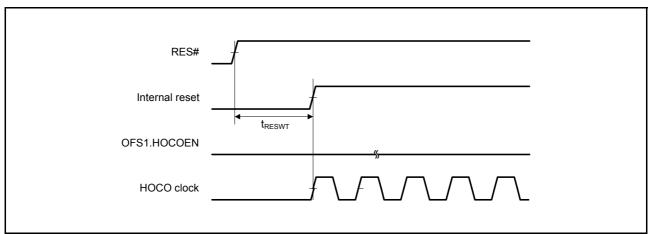

•Page 1068, Figure 35.24 HOCO Clock Oscillation Start Timing (After Reset is Canceled by Setting OFS1.HOCOEN Bit to 0) is added as follows:

Figure 35.24 HOCO Clock Oscillation Start Timing (After Reset is Canceled by Setting OFS1.HOCOEN Bit to 0)

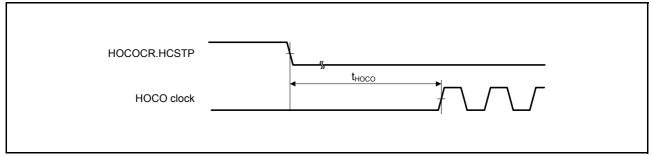

•Page 1068, Figure 35.25 HOCO Clock Oscillation Start Timing (Oscillation is Started by Setting HOCOCR.HCSTP Bit) is added as follows:

Figure 35.25 **HOCO Clock Oscillation Start Timing (Oscillation is Started by Setting HOCOCR.HCSTP Bit)**

•Page 1087, Table 35.32 Comparator Characteristics is corrected as follows: Before correction

| Item          | Symbol          | Min. | Тур. | Max. | Unit | Test Conditions                |

|---------------|-----------------|------|------|------|------|--------------------------------|

| Response time | t <sub>cr</sub> | _    | -    | 200  | ns   | VOD = 100 mV<br>PCLKB = 40 MHz |

|               | t <sub>cf</sub> | _    | _    | 200  | ns   | CMPCTL.ODFS = 0                |

#### Corrections

| Item          | Symbol          | Min. | Тур. | Max. | Unit | Test Conditions                 |

|---------------|-----------------|------|------|------|------|---------------------------------|

| Response time | t <sub>cr</sub> | _    | _    | 200  | ns   | VOD = 100 mV<br>CMPCTL.CDFS = 0 |

|               | t <sub>cf</sub> | _    | _    | 200  | ns   | _                               |

•Page 1088, Table 35.33 D/A Conversion Characteristics is corrected as follows: **Before correction**

| Item              | Min. | Тур. | Max. | Unit | Test Conditions |

|-------------------|------|------|------|------|-----------------|

| Resolution        | _    | _    | 8    | Bit  |                 |

| Conversion time   | _    | _    | 3.0  | μs   |                 |

| Absolute accuracy | _    | ±1.0 | ±3.0 | LSB  |                 |

| Item              | Symbol             | Min. | Тур. | Max. | Unit | Test Conditions |

|-------------------|--------------------|------|------|------|------|-----------------|

| Resolution        | _                  | _    | _    | 8    | Bit  |                 |

| Conversion time   | t <sub>DCONV</sub> | _    | _    | 3.0  | μs   |                 |

| Absolute accuracy | _                  | _    | ±1.0 | ±3.0 | LSB  |                 |

•Page 1090, Table 35.35 Power-On Reset Circuit and Voltage Detection Circuit Characteristics (2) is corrected as follows:

## Before correction

| Item                                                    | Symbol              | Min. | Тур. | Max. | Unit | Test Conditions                    |

|---------------------------------------------------------|---------------------|------|------|------|------|------------------------------------|

| Wait time after power-on reset cancellation             | t <sub>POR</sub>    | _    | 28.4 | _    | ms   | Figure 35.49                       |

| Wait time after voltage monitoring 1 reset cancellation | t <sub>LVD1</sub>   | _    | 568  | _    | μs   | Figure 35.51                       |

| Wait time after voltage monitoring 2 reset cancellation | t <sub>LVD2</sub>   | _    | 100  | _    | μs   | Figure 35.52                       |

| Response delay time                                     | t <sub>det</sub>    | _    | _    | 350  | μs   | Figure 35.48                       |

| Minimum VCC down time*1                                 | t <sub>VOFF</sub>   | 350  | _    | _    | μs   | Figure 35.48, VCC = 1.0 V or above |

| Power-on reset enable time                              | t <sub>W(POR)</sub> | 1    | _    | _    | ms   | Figure 35.49, VCC = below 1.0 V    |

| LVD operation stabilization time (after LVD is enabled) | $Td_{(E-A)}$        | _    | _    | 300  | μs   | Figure 35.51, Figure 35.52         |

| Hysteresis width (LVD1 and LVD2)                        | $V_{LVH}$           | _    | 70   | _    | mV   | Vdet1_0 to 4 selected              |

|                                                         |                     | _    | 60   | _    |      | Vdet1_5 to 8, LVD2 selected        |

| Item                                                    | Symbol              | Min. | Тур. | Max. | Unit | Test Conditions                    |

|---------------------------------------------------------|---------------------|------|------|------|------|------------------------------------|

| Wait time after power-on reset cancellation             | t <sub>POR</sub>    | _    | 28.4 | _    | ms   | Figure 35.51                       |

| Wait time after voltage monitoring 0 reset cancellation | t <sub>LVD0</sub>   | _    | 568  | _    | μs   | Figure 35.52                       |

| Wait time after voltage monitoring 1 reset cancellation | t <sub>LVD1</sub>   | _    | 100  | _    | μs   | Figure 35.53                       |

| Wait time after voltage monitoring 2 reset cancellation | t <sub>LVD2</sub>   | _    | 100  | _    | μs   | Figure 35.54                       |

| Response delay time                                     | t <sub>det</sub>    | _    | _    | 350  | μs   | Figure 35.50                       |

| Minimum VCC down time*1                                 | t <sub>VOFF</sub>   | 350  | _    | _    | μs   | Figure 35.50, VCC = 1.0 V or above |

| Power-on reset enable time                              | t <sub>W(POR)</sub> | 1    | _    | _    | ms   | Figure 35.51, VCC = below 1.0 V    |

| LVD operation stabilization time (after LVD is enabled) | $Td_{(E-A)}$        | _    | _    | 300  | μs   | Figure 35.53, Figure 35.54         |

| Hysteresis width (LVD1 and LVD2)                        | $V_{LVH}$           | _    | 70   | _    | mV   | Vdet1_0 to 4 selected              |

|                                                         |                     | _    | 60   | _    |      | Vdet1_5 to 8, LVD2 selected        |

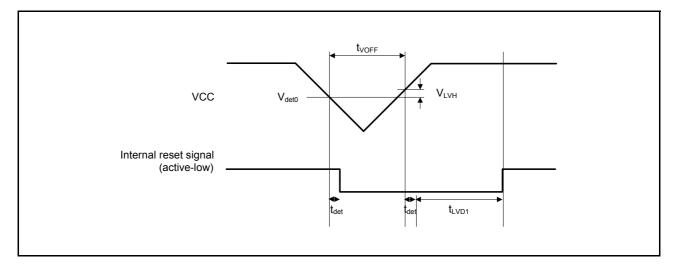

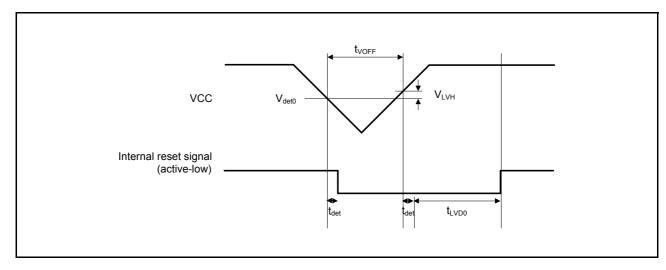

# •Page 1091, Figure 35.50 Voltage Detection Circuit Timing (Vdet0) is corrected as follows: Before correction

## <Description of the Additional Functions and Relevant Corrections>

•Page 34, the description in "Features" is corrected as follows:

#### Before correction

■ Up to 48 pins for general I/O ports

#### **Corrections**

- Up to 50 pins for general I/O ports

- •Page 34, the description of "On-chip SRAM, no wait states" in "Features" is corrected as follows: Before correction

- 10 Kbytes of SRAM

#### Corrections

- 12 Kbytes of SRAM

- •Page 34, the description of "Clock functions" in "Features" is corrected as follows:

#### **Before correction**

· On-chip low-speed oscillators, dedicated on-chip oscillator for the IWDT

## Corrections

- On-chip low-speed oscillator, on-chip high-speed oscillator, dedicated on-chip oscillator for the IWDT

- •Page 35, Table 1.1 Outline of Specifications (1/3) is corrected as follows:

Description

#### **Before correction**

|   | Classification | Module/Function          | Description                                                                                                             |

|---|----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| N | Memory         | RAM                      | · Capacity: 10 Kbytes                                                                                                   |

| ( | Clock          | Clock generation circuit | · Main clock oscillator, low-speed on-chip oscillator, PLL frequency synthesizer, and IWDT-dedicated on-chip oscillator |

## Corrections

Classification

Module/Function

| Memory | RAM                      | Capacity: 12 Kbytes                                                                                                                  |

|--------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Clock  | Clock generation circuit | Main clock oscillator, low-speed and high-speed on-chip oscillator, PLL frequency synthesizer, and IWDT-dedicated on-chip oscillator |

RENESAS TECHNICAL UPDATE TN-FL\*-5% (A/E Date: Jan. FH, 2016

## •Page 36, Table 1.1 Outline of Specifications (2/3) is corrected as follows:

## Before correction

ClassificationModule/FunctionDescriptionI/O portsGeneral I/O ports· I/O: 48/38/35

Pull-up resistors: 48/38/35Open-drain outputs: 40/30/27

#### Corrections

Classification

Module/Function

Description

I/O ports

General I/O ports

· I/O: 50/40/37

Pull-up resistors: 50/40/37Open-drain outputs: 42/32/29

# •Page 39, Table 1.3 List of Products: D Version ( $T_a = -40 \text{ to } +85^{\circ}\text{C}$ ) is corrected as follows: Before correction

| Group | Part No.     | Package      | ROM Capacity | RAM Capacity | Operating<br>Frequency | Operating<br>Temperature |

|-------|--------------|--------------|--------------|--------------|------------------------|--------------------------|

| RX23T | R5F523T5ADFL | PLQP0048KB-A | 128 Kbytes   | 10 Kbytes    | 40MHz                  | -40 to + 85°C            |

|       | R5F523T5ADFD | PLQP0052JA-A |              |              |                        |                          |

|       | R5F523T5ADFM | PLQP0064KB-A |              |              |                        |                          |

|       | R5F523T3ADFL | PLQP0048KB-A | 64 Kbytes    | 7            |                        |                          |

|       | R5F523T3ADFD | PLQP0052JA-A |              |              |                        |                          |

|       | R5F523T3ADFM | PLQP0064KB-A |              |              |                        |                          |

#### Corrections

| Group | Part No.     | Package      | ROM Capacity | RAM Capacity | Operating<br>Frequency | Operating<br>Temperature |

|-------|--------------|--------------|--------------|--------------|------------------------|--------------------------|

| RX23T | R5F523T5ADFL | PLQP0048KB-B | 128 Kbytes   | 12 Kbytes    | 40MHz                  | -40 to + 85°C            |

|       | R5F523T5ADFD | PLQP0052JA-B |              |              |                        |                          |

|       | R5F523T5ADFM | PLQP0064KB-C |              |              |                        |                          |

|       | R5F523T3ADFL | PLQP0048KB-B | 64 Kbytes    |              |                        |                          |

|       | R5F523T3ADFD | PLQP0052JA-B |              |              |                        |                          |

|       | R5F523T3ADFM | PLQP0064KB-C |              |              |                        |                          |

# •Page 39, Table 1.4 List of Products: G Version ( $T_a = -40 \text{ to } +105^{\circ}\text{C}$ ) is corrected as follows: Before correction

| Group | Part No.     | Package      | ROM Capacity | RAM Capacity | Operating<br>Frequency | Operating<br>Temperature |

|-------|--------------|--------------|--------------|--------------|------------------------|--------------------------|

| RX23T | R5F523T5AGFL | PLQP0048KB-A | 128 Kbytes   | 10 Kbytes    | 40MHz                  | -40 to +105°C            |

|       | R5F523T5AGFD | PLQP0052JA-A |              |              |                        |                          |

|       | R5F523T5AGFM | PLQP0064KB-A |              |              |                        |                          |

|       | R5F523T3AGFL | PLQP0048KB-A | 64 Kbytes    | ]            |                        |                          |

|       | R5F523T3AGFD | PLQP0052JA-A |              |              |                        |                          |

|       | R5F523T3AGFM | PLQP0064KB-A |              |              |                        |                          |

RENESAS TECHNICAL UPDATE TN-FL\*-5% (A/E Date: Jan. FH, 2016

## Corrections

| Part No.     | Package                                                                      | ROM Capacity                                                                                                                      | RAM Capacity                                                                                                                                                                                                                                           | Operating<br>Frequency                                                                                                                                                                                                                                                                                                          | Operating<br>Temperature                                                                                                                                                                                                                                                                                                                                                    |

|--------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R5F523T5AGFL | PLQP0048KB-B                                                                 | 128 Kbytes                                                                                                                        | 12 Kbytes                                                                                                                                                                                                                                              | 40MHz                                                                                                                                                                                                                                                                                                                           | -40 to +105°C                                                                                                                                                                                                                                                                                                                                                               |

| R5F523T5AGFD | PLQP0052JA-B                                                                 |                                                                                                                                   |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                             |

| R5F523T5AGFM | PLQP0064KB-C                                                                 |                                                                                                                                   |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                             |

| R5F523T3AGFL | PLQP0048KB-B                                                                 | 64 Kbytes                                                                                                                         | 7                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                             |

| R5F523T3AGFD | PLQP0052JA-B                                                                 |                                                                                                                                   |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                             |

| R5F523T3AGFM | PLQP0064KB-C                                                                 |                                                                                                                                   |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                             |

|              | R5F523T5AGFL<br>R5F523T5AGFD<br>R5F523T5AGFM<br>R5F523T3AGFL<br>R5F523T3AGFD | R5F523T5AGFL PLQP0048KB-B R5F523T5AGFD PLQP0052JA-B R5F523T5AGFM PLQP0064KB-C R5F523T3AGFL PLQP0048KB-B R5F523T3AGFD PLQP0052JA-B | R5F523T5AGFL         PLQP0048KB-B         128 Kbytes           R5F523T5AGFD         PLQP0052JA-B           R5F523T5AGFM         PLQP0064KB-C           R5F523T3AGFL         PLQP0048KB-B         64 Kbytes           R5F523T3AGFD         PLQP0052JA-B | R5F523T5AGFL         PLQP0048KB-B         128 Kbytes         12 Kbytes           R5F523T5AGFD         PLQP0052JA-B         128 Kbytes         12 Kbytes           R5F523T5AGFM         PLQP0064KB-C         64 Kbytes           R5F523T3AGFL         PLQP0048KB-B         64 Kbytes           R5F523T3AGFD         PLQP0052JA-B | Part No.         Package         ROM Capacity         RAM Capacity         Frequency           R5F523T5AGFL         PLQP0048KB-B         128 Kbytes         12 Kbytes         40MHz           R5F523T5AGFD         PLQP0052JA-B         R5F523T5AGFM         PLQP0064KB-C         64 Kbytes           R5F523T3AGFL         PLQP0048KB-B         64 Kbytes         64 Kbytes |

•Page 40, Figure 1.1 How to Read the Product Part Number is corrected as follows:

#### Before correction

ROM/RAM capacity

5: 128 Kbytes/10 Kbytes

3: 64 Kbytes/10 Kbytes

#### Corrections

ROM/RAM capacity

5: 128 Kbytes/12 Kbytes

3: 64 Kbytes/12 Kbytes

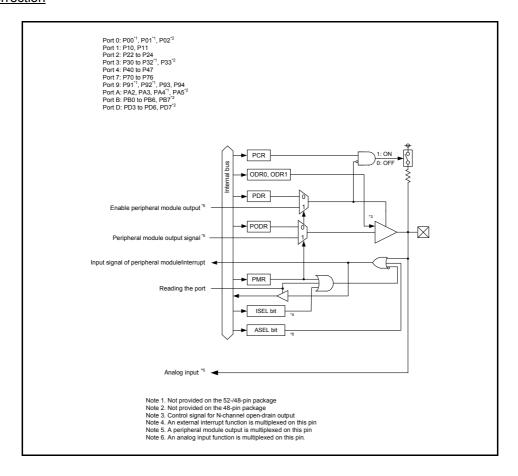

•Page 43, Table 1.5 Pin Functions (2/2) is corrected as follows:

#### Before correction

| Classifications | Pin Name   | I/O | Description              |

|-----------------|------------|-----|--------------------------|

| I/O ports       | P30 to P33 | I/O | 4-bit input/output pins. |

#### Corrections

ClassificationsPin NameI/ODescriptionI/O portsP30 to P33, P36, P37I/O6-bit input/output pins.

•Page 44, 45, and 46, Figure 1.3 Pin Assignments of the 64-Pin LFQFP, Figure 1.4 Pin Assignments of the 52-Pin LQFP, and Figure 1.5 Pin Assignments of the 48-Pin LFQFP are corrected as follows:

## Before correction

**XTAL**

**EXTAL**

## Corrections

P37/XTAL

P36/EXTAL

## •Page 47, Table 1.6 List of Pins and Pin Functions (64-Pin LFQFP) (1/2) is corrected as follows: **Before correction**

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, TMR, POE, CAC) | Communications<br>(SCIg, RSPI, RIIC) | Others  |

|------------|-------------------------------------------|----------|--------------------------------|--------------------------------------|---------|

| 7          | XTAL                                      | (blank)  | (blank)                        | (blank)                              | (blank) |

| 9          | EXTAL                                     | (blank)  | (blank)                        | (blank)                              | (blank) |

## Corrections

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, TMR, POE, CAC) | Communications<br>(SCIg, RSPI, RIIC) | Others  |

|------------|-------------------------------------------|----------|--------------------------------|--------------------------------------|---------|

| 7          | XTAL                                      | P37      | (blank)                        | (blank)                              | (blank) |

| 9          | EXTAL                                     | P36      | (blank)                        | (blank)                              | (blank) |

•Page 49, Table 1.7 List of Pins and Pin Functions (52-Pin LQFP) is corrected as follows:

## Before correction

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, TMR, POE, CAC) | Communications<br>(SCIg, RSPI, RIIC) | Others  |

|------------|-------------------------------------------|----------|--------------------------------|--------------------------------------|---------|

| 5          | XTAL                                      | (blank)  | (blank)                        | (blank)                              | (blank) |

| 7          | EXTAL                                     | (blank)  | (blank)                        | (blank)                              | (blank) |

## Corrections

|   | Pin<br>No. | Clock, System Control | I/O Port | Timers<br>(MTU, TMR, POE, CAC) | Communications<br>(SCIg, RSPI, RIIC) | Others  |

|---|------------|-----------------------|----------|--------------------------------|--------------------------------------|---------|

| ; | 5          | XTAL                  | P37      | (blank)                        | (blank)                              | (blank) |

| - | 7          | EXTAL                 | P36      | (blank)                        | (blank)                              | (blank) |

•Page 50, Table 1.8 List of Pins and Pin Functions (48-Pin LFQFP) is corrected as follows: Before correction

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, TMR, POE, CAC) | Communications<br>(SCIg, RSPI, RIIC) | Others  |

|------------|-------------------------------------------|----------|--------------------------------|--------------------------------------|---------|

| 4          | XTAL                                      | (blank)  | (blank)                        | (blank)                              | (blank) |

| 6          | EXTAL                                     | (blank)  | (blank)                        | (blank)                              | (blank) |

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | Timers<br>(MTU, TMR, POE, CAC) | Communications<br>(SCIg, RSPI, RIIC) | Others  |

|------------|-------------------------------------------|----------|--------------------------------|--------------------------------------|---------|

| 4          | XTAL                                      | P37      | (blank)                        | (blank)                              | (blank) |

| 6          | EXTAL                                     | P36      | (blank)                        | (blank)                              | (blank) |

•Page 84, Figure 4.1 Memory Map in Each Operating Mode is corrected as follows:

**Before correction**

RAM (bytes)

Capacity Address

10 Kbytes 0000 0000h to 0000 27FFh

Corrections

RAM (bytes)

Capacity Address

12 Kbytes 0000 0000h to 0000 27FFh

0000 4000h to 0000 4A7Fh

•Page 87, the following registers are added to Table 5.1 List of I/O Registers (Address Order) (1/16):

|            | Module |                                                     | Register | Number of |             | Number of<br>Access Cycles | - Reference |  |

|------------|--------|-----------------------------------------------------|----------|-----------|-------------|----------------------------|-------------|--|

| Address    | Symbol | Register Name                                       | Symbol   | Bits      | Access Size | ICLK ≥PCLK                 | Section     |  |

| 0008 0036h | SYSTEM | High-Speed On-Chip Oscillator Control Register      | HOCOCR   | 8         | 8           | 3ICLK                      | section 9.  |  |

| 0008 00A5h | SYSTEM | High-Speed On-Chip Oscillator Wait Control Register | HOCOWTCR | 8         | 8           | 3ICLK                      | section 9.  |  |

•Page 97, the following registers are added to Table 5.1 List of I/O Registers (Address Order) (11/16):

| Address    | Module<br>Symbol | Register Name                 | Register<br>Symbol | Number of Bits |       | Number of<br>Access Cycles<br>ICLK ≥PCLK | Reference<br>Section |

|------------|------------------|-------------------------------|--------------------|----------------|-------|------------------------------------------|----------------------|

| 0008 C087h | PORT3            | Open Drain Control Register 1 | ODR1               | 8              | 8, 16 | 2 or 3 PCLKB                             | section 18           |

•Page 118, "Option Function Select Register 1 (OFS1)" is corrected as follows: The HOCOEN bit is added in b8.

## **Before correction**

Address(es): FFFF FF88h

| _                  | b31 | b30                         | b29 | b28 | b27 | b26 | b25 | b24 | b23 | b22 | b21 | b20 | b19 | b18       | b17   | b16     |

|--------------------|-----|-----------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------|-------|---------|

|                    | _   | _                           | _   | _   |     |     | _   | _   | _   | _   |     |     | _   | _         | _     | _       |

| Value after reset: |     | The value set by the user*1 |     |     |     |     |     |     |     |     |     |     |     |           |       |         |

|                    | b15 | b14                         | b13 | b12 | b11 | b10 | b9  | b8  | b7  | b6  | b5  | b4  | b3  | b2        | b1    | b0      |

|                    |     |                             |     |     |     |     |     |     |     |     |     |     |     | L) (D A O | \/D0E | 1.54.01 |

Value after reset.

The value set by the user\*1

| Bit       | Symbol     | Bit Name                             | Description                                                                                                                                  | R/W |

|-----------|------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b1, b0    | VDSEL[1:0] | Voltage Detection 0 Level<br>Select  | b1 b0 0 0: 3.84 V is selected 1 0: 2.51 V is selected Settings other than above are prohibited when the voltage detection 0 circuit is used. | R   |

| b2        | LVDAS      | Voltage Detection 0 Circuit<br>Start | Voltage monitoring 0 reset is enabled after a reset     Voltage monitoring 0 reset is disabled after a reset                                 | R   |

| b31 to b3 | _          | Reserved                             | When reading, these bits return the value written by the user. The write value should be 1.                                                  | R   |

## Corrections

Address(es): FFFF FF88h

|                                                | b31 | b30 | b29 | b28 | b27 | b26 | b25 | b24  | b23 | b22 | b21 | b20 | b19 | b18   | b17  | b16     |

|------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|-------|------|---------|

|                                                | _   | _   | _   | _   | _   | -   | _   | -    | _   | _   | _   | _   | _   | -     | _    | _       |

| Value after reset: The value set by the user*1 |     |     |     |     |     |     |     |      |     |     |     |     |     |       |      |         |

|                                                | b15 | b14 | b13 | b12 | b11 | b10 | b9  | b8   | b7  | b6  | b5  | b4  | b3  | b2    | b1   | b0      |

|                                                |     |     |     |     |     |     |     | носо |     |     |     |     |     | LVDAC | VDCE | 1 [4.0] |

Value after reset

The value set by the user\*1

| Bit       | Symbol     | Bit Name                             | Description                                                                                                                                  | R/W |

|-----------|------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b1, b0    | VDSEL[1:0] | Voltage Detection 0 Level<br>Select  | b1 b0 0 0: 3.84 V is selected 1 0: 2.51 V is selected Settings other than above are prohibited when the voltage detection 0 circuit is used. | R   |

| b2        | LVDAS      | Voltage Detection 0 Circuit<br>Start | Voltage monitoring 0 reset is enabled after a reset     Voltage monitoring 0 reset is disabled after a reset                                 | R   |

| b7 to b3  | _          | Reserved                             | When reading, these bits return the value written by the user. The write value should be 1.                                                  | R   |

| b8        | HOCOEN     | HOCO Oscillation Enable              | HOCO oscillation is enabled after a reset     HOCO oscillation is disabled after a reset                                                     | R   |

| b31 to b9 | _          | Reserved                             | When reading, these bits return the value written by the user. The write value should be 1.                                                  | R   |

(Additional description)

#### **HOCOEN Bit (HOCO Oscillation Enable)**

This bit selects whether the HOCO oscillation is effective or not after a reset.

Setting the HOCOEN bit to 0 allows the HOCO oscillation to be started before the CPU starts operation, and therefore reduces the wait time for oscillation stabilization.

Note that even if the HOCOEN bit is set to 0, the system clock source is not switched to HOCO. The system clock source is switched to HOCO only by modifying the clock source select bits (SCKCR3.CKSEL[2:0]) from the CPU.

Also, when the HOCOEN bit is set to 0, the HOCO oscillation stabilization time (tHOCO) is secured by hardware, so the clock with the accuracy of the HOCO oscillation frequency (fHOCO) shown in Electrical Characteristics is supplied after release from the CPU reset state.

## •Page 137, the following item is added to Table 9.1 Specifications of Clock Generation Circuit:

| Item                                 | Specification                 |

|--------------------------------------|-------------------------------|

| High-speed on-chip oscillator (HOCO) | Oscillation frequency: 32 MHz |

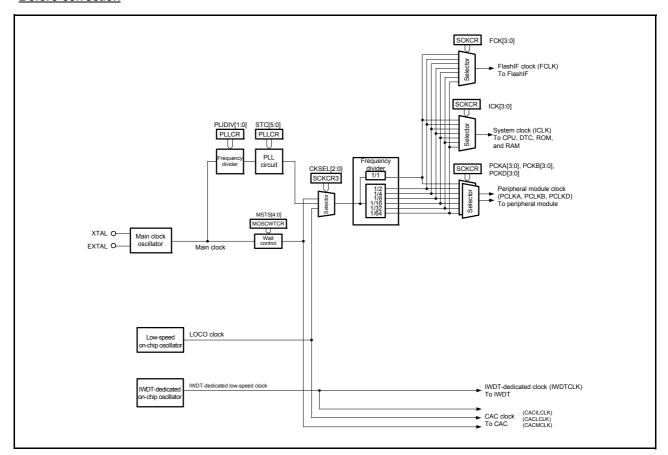

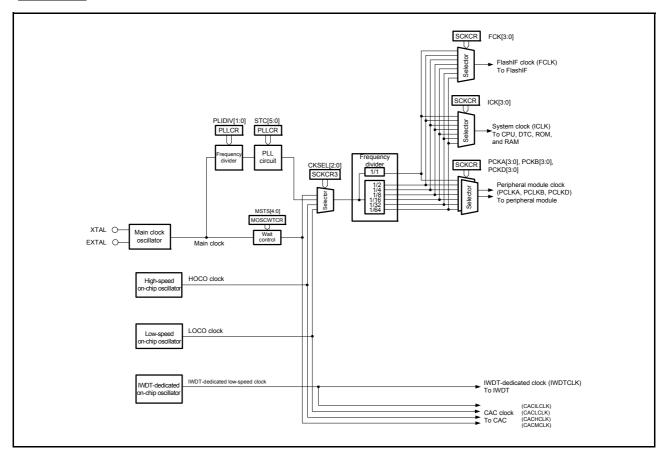

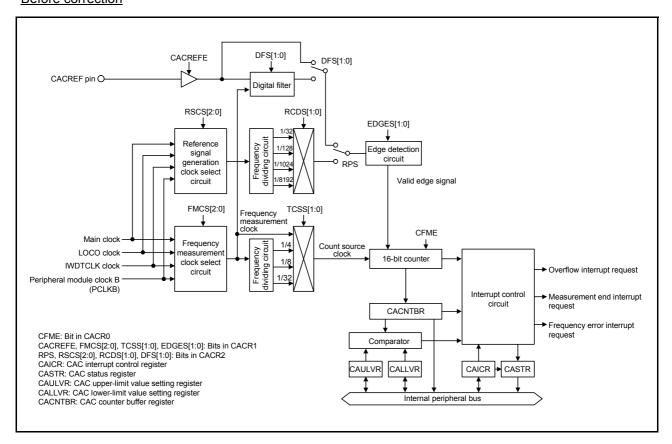

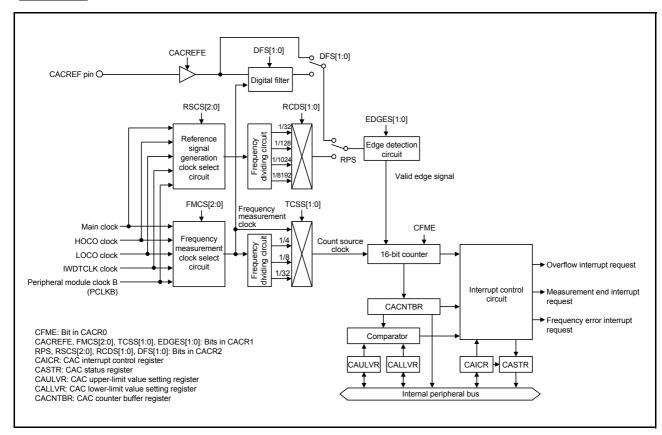

# •Page 138, Figure 9.1 Block Diagram of Clock Generation Circuit is corrected as follows: Before correction

"Date: Jan. FH, 2016

## Corrections

## •Page 142, "System Clock Control Register 3 (SCKCR3)" is corrected as follows: Before correction

| Bit        | Symbol           | Bit Name            | Description                                                                                                  | R/W |

|------------|------------------|---------------------|--------------------------------------------------------------------------------------------------------------|-----|

| b7 to b0   | _                | Reserved            | These bits are read as 0. The write value should be 0.                                                       | R/W |

| b10 to b8  | CKSEL[2:0]<br>*1 | Clock Source Select | b10 b8 0 0 0: LOCO 0 1 0: Main clock oscillator 1 0 0: PLL circuit Settings other than above are prohibited. | R/W |

| b15 to b11 | _                | Reserved            | These bits are read as 0. The write value should be 0.                                                       | R/W |

| Bit        | Symbol           | Bit Name            | Description                                                                                                              | R/W |

|------------|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------|-----|

| b7 to b0   | _                | Reserved            | These bits are read as 0. The write value should be 0.                                                                   | R/W |

| b10 to b8  | CKSEL[2:0]<br>*1 | Clock Source Select | b10 b8 0 0 0: LOCO 0 0 1: HOCO 0 1 0: Main clock oscillator 1 0 0: PLL circuit Settings other than above are prohibited. | R/W |

| b15 to b11 | _                | Reserved            | These bits are read as 0. The write value should be 0.                                                                   | R/W |

- •Page 147, the following register description is added after the description of the IWDT-Dedicated On-Chip Oscillator Control Register (ILOCOCR):

- 9.2.8 High-Speed On-Chip Oscillator Control Register (HOCOCR)

- 9.2.9 High-Speed On-Chip Oscillator Wait Control Register (HOCOWTCR)

The number of the following sections are changed according to the additional description above.

#### Before correction

- 9.2.8 Oscillation Stabilization Flag Register (OSCOVFSR)

- 9.2.9 Oscillation Stop Detection Control Register (OSTDCR)

- 9.2.10 Oscillation Stop Detection Status Register (OSTDSR)

- 9.2.11 Main Clock Oscillator Wait Control Register (MOSCWTCR)

- 9.2.12 Main Clock Oscillator Forced Oscillation Control Register (MOFCR)

- 9.2.13 Memory Wait Cycle Setting Register (MEMWAIT)

#### Corrections

- 9.2.10 Oscillation Stabilization Flag Register (OSCOVFSR)

- 9.2.11 Oscillation Stop Detection Control Register (OSTDCR)

- 9.2.12 Oscillation Stop Detection Status Register (OSTDSR)

- 9.2.13 Main Clock Oscillator Wait Control Register (MOSCWTCR)

- 9.2.14 Main Clock Oscillator Forced Oscillation Control Register (MOFCR)

- 9.2.15 Memory Wait Cycle Setting Register (MEMWAIT)

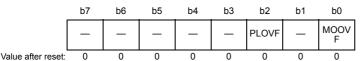

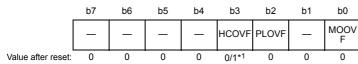

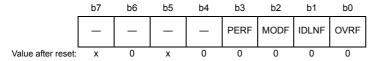

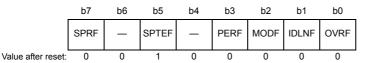

- •Page 148, "Oscillation Stabilization Flag Register (OSCOVFSR)" is corrected as follows: The HCOVF bit is added in b3.

## Before correction

Address(es): 0008 003Ch

| Bit      | Symbol | Bit Name                                     | Description                                                                                                | R/W |

|----------|--------|----------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|

| b0       | MOOVF  | Main Clock Oscillation<br>Stabilization Flag | 0: Main clock is stopped 1: Oscillation is stable and the clock can be used as the system clock*1          | R   |

| b1       | _      | Reserved                                     | This bit is read as 0. The write value should be 0.                                                        | R/W |

| b2       | PLOVF  | PLL Clock Oscillation<br>Stabilization Flag  | O: PLL is stopped or not stabilized     Scillation is stable and the clock can be used as the system clock | R   |

| b3       | _      | Reserved                                     | This bit is read as 0 and cannot be modified.                                                              | R   |

| b7 to b4 | _      | Reserved                                     | These bits are read as 0. The write value should be 0.                                                     | R/W |

#### Corrections

Address(es): 0008 003Ch

Note 1. The HCOVF value after a reset is 1 when the HOCO oscillation enable bit in option function selection register 1 (OFS1.HOCOEN) is 0. The HCOVF value after a reset is 0 when the OFS1.HOCOEN bit is 1.

| Bit | Symbol | Bit Name                                     | Description                                                                                                   | R/W |

|-----|--------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|

| b0  | MOOVF  | Main Clock Oscillation<br>Stabilization Flag | Main clock is stopped     Coscillation is stable and the clock can be used as the system clock*1              | R   |

| b1  | _      | Reserved                                     | This bit is read as 0. The write value should be 0.                                                           | R/W |

| b2  | PLOVF  | PLL Clock Oscillation<br>Stabilization Flag  | D: PLL is stopped or not stabilized     Scillation is stable and the clock can be used as the system clock    | R   |

| b3  | HCOVF  | HOCO Clock Oscillation<br>Stabilization Flag | 0: HOCO is stopped or not stabilized 1: Oscillation is stable and the clock can be used as the system clock*1 | R   |

These bits are read as 0. The write value should be 0.

(Additional description)

#### **HCOVF Flag (HOCO Clock Oscillation Stabilization Flag)**

Reserved

This flag indicates whether oscillation of the HOCO clock is stable.

#### [Setting condition]

b7 to b4

- After the HOCOCR.HCSTP bit is set to 0 (HOCO is operating) when the HCSTP bit is 1 (HOCO is stopped), supply of the HOCO clock is started to the MCU internally. [Clearing condition]

- After the HOCOCR.HCSTP bit is set to 1, the processing to stop the oscillation of the HOCO is completed.

- •Page 158, the following description is added to "Oscillation Stop Detection Interrupts".

When the PLL detects an oscillation stop and is running at its own oscillation frequency, this indicates the occurrence of some system failure. An emergency measure should be taken to handle the failure.

## Page 159, "Internal Clock" is corrected as follows:

#### Before correction

Clock sources of internal clock signals are the main clock, LOCO clock, PLL clock, and dedicated low-speed clock for the IWDT. The internal clocks listed below are produced from these sources.

#### Corrections

Clock sources of internal clock signals are the main clock, HOCO clock, LOCO clock, PLL clock, and dedicated low-speed clock for the IWDT. The internal clocks listed below are produced from these sources.

## Page 159, "CAC Clock" is corrected as follows:

#### **Before correction**

The CACCLK clocks include CACMCLK which is generated by the main clock oscillator, CACLCLK which is generated by the low-speed on-chip oscillator, and CACILCLK which is generated by the IWDT-dedicated on-chip oscillator.

#### Corrections

The CACCLK clocks include CACMCLK which is generated by the main clock oscillator, CACHCLK which is generated by the high-speed on-chip oscillator, CACLCLK which is generated by the low-speed on-chip oscillator, and CACILCLK which is generated by the IWDT-dedicated on-chip oscillator.

Date: Jan. FH, 2016

R/W

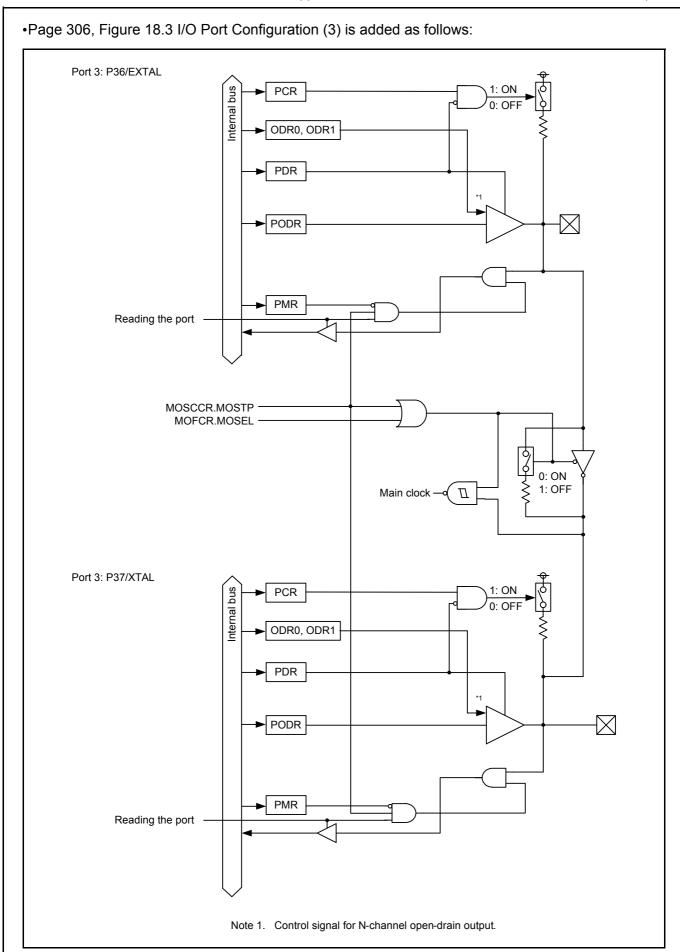

•Page 160, "Notes on Resonator Connection Pins" is added as follows:

## 9.7.4 Notes on Resonator Connection Pins

When the main clock is not used, the EXTAL and XTAL pins can be used as general ports P36 and P37. When using these pins as general ports, be sure to stop the main clock (MOSCCR.MOSTP = 1). However, do not use the EXTAL and XTAL pins as general ports P36 and P37 in a system that uses the main clock.

When the main clock is used, do not set P36 and P37 to output.

## •Page 161, Table 10.1 CAC Specifications is corrected as follows:

#### Before correction

| Item                         | Description                                                                                                                              |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Measurement target clocks    | The frequency of the following clocks can be measured.  • Main clock  • LOCO clock  • IWDTCLK clock  • Peripheral module clock B (PCLKB) |

| Measurement reference clocks | External clock input to the CACREF pin Main clock LOCO clock IWDTCLK clock Peripheral module clock B (PCLKB)                             |

| Item                         | Description                                                                                                                                            |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Measurement target clocks    | The frequency of the following clocks can be measured.  • Main clock  • HOCO clock  • LOCO clock  • IWDTCLK clock  • Peripheral module clock B (PCLKB) |

| Measurement reference clocks | External clock input to the CACREF pin Main clock HOCO clock LOCO clock IWDTCLK clock Peripheral module clock B (PCLKB)                                |

## •Page 161, Figure 10.1 CAC Block Diagram is corrected as follows: Before correction

# •Page 163, "CAC Control Register 1 (CACR1)" is corrected as follows:

## Before correction

| Bit      | Symbol    | Bit Name                        | Description                                                                                                                                       | R/W |

|----------|-----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b3 to b1 | FMCS[2:0] | Measurement Target Clock Select | b3 b1 0 0 0: Main clock 0 1 1: LOCO clock 1 0 0: IWDTCLK clock 1 0 1: Peripheral module clock B (PCLKB) Settings other than above are prohibited. | R/W |

## Corrections

| Bit      | Symbol    | Bit Name                        | Description                                                                                                                                                         | R/W |

|----------|-----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b3 to b1 | FMCS[2:0] | Measurement Target Clock Select | b3 b1 0 0 0: Main clock 0 1 0: HOCO clock 0 1 1: LOCO clock 1 0 0: IWDTCLK clock 1 0 1: Peripheral module clock B (PCLKB) Settings other than above are prohibited. | R/W |

# •Page 172, Table 11.2 Operating Conditions of Each Power Consumption Mode is corrected as follows:

## **Before correction**

|                                                 | Sleep Mode                     | Deep Sleep Mode                | Software Standby Mode          |

|-------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Entry trigger                                   | Control register + instruction | Control register + instruction | Control register + instruction |

| Exit trigger                                    | Interrupt                      | Interrupt                      | Interrupt*1                    |

| After exiting from each mode, CPU begins from*2 | Interrupt handling             | Interrupt handling             | Interrupt handling             |

| Main clock oscillator                           | Operating possible             | Operating possible             | Stopped                        |

| Low-speed on-chip oscillator                    | Operating possible             | Operating possible             | Stopped                        |

| IWDT-dedicated on-chip oscillator               | Operating possible*3           | Operating possible*3           | Operating possible*3           |

| PLL                                             | Operating possible             | Operating possible             | Stopped                        |

| CPU                                             | Stopped (Retained)             | Stopped (Retained)             | Stopped (Retained)             |

| RAM0 (0000 0000h to 0000 27FFh)                 | Operating possible (Retained)  | Stopped (Retained)             | Stopped (Retained)             |

| DTC                                             | Operating possible*5           | Stopped (Retained)             | Stopped (Retained)             |

| Flash memory                                    | Operating                      | Stopped (Retained)             | Stopped (Retained)             |

| Independent watchdog timer (IWDT)               | Operating possible*3           | Operating possible*3           | Operating possible*3           |

| Voltage detection circuit (LVD)                 | Operating possible             | Operating possible             | Operating possible             |

| Power-on reset circuit                          | Operating                      | Operating                      | Operating                      |

| Peripheral modules                              | Operating possible             | Operating possible             | Stopped (Retained)*4           |

| I/O ports                                       | Operating                      | Operating                      | Retained                       |

| Comparator C                                    | Operating possible             | Operating possible             | Operating possible*6           |

## Corrections

|                                                           | Sleep Mode                     | Deep Sleep Mode                | Software Standby Mode          |

|-----------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Entry trigger                                             | Control register + instruction | Control register + instruction | Control register + instruction |

| Exit trigger                                              | Interrupt                      | Interrupt                      | Interrupt*1                    |

| After exiting from each mode, CPU begins from*2           | Interrupt handling             | Interrupt handling             | Interrupt handling             |

| Main clock oscillator                                     | Operating possible             | Operating possible             | Stopped                        |

| High-speed on-chip oscillator                             | Operating possible             | Operating possible             | Stopped                        |

| Low-speed on-chip oscillator                              | Operating possible             | Operating possible             | Stopped                        |

| IWDT-dedicated on-chip oscillator                         | Operating possible*3           | Operating possible*3           | Operating possible*3           |

| PLL                                                       | Operating possible             | Operating possible             | Stopped                        |

| CPU                                                       | Stopped (Retained)             | Stopped (Retained)             | Stopped (Retained)             |

| RAM0 (0000 0000h to 0000 27FFh, 0000 4000h to 0000 4A7Fh) | Operating possible (Retained)  | Stopped (Retained)             | Stopped (Retained)             |

| DTC                                                       | Operating possible*5           | Stopped (Retained)             | Stopped (Retained)             |

| Flash memory                                              | Operating                      | Stopped (Retained)             | Stopped (Retained)             |

| Independent watchdog timer (IWDT)                         | Operating possible*3           | Operating possible*3           | Operating possible*3           |

| Voltage detection circuit (LVD)                           | Operating possible             | Operating possible             | Operating possible             |

| Power-on reset circuit                                    | Operating                      | Operating                      | Operating                      |

| Peripheral modules                                        | Operating possible             | Operating possible             | Stopped (Retained)*4           |

| I/O ports                                                 | Operating                      | Operating                      | Retained                       |

| Comparator C                                              | Operating possible             | Operating possible             | Operating possible*6           |

# •Page 178, "Module Stop Control Register C (MSTPCRC)" is corrected as follows: Before correction

| Bit | Symbol | Bit Name           | Description                                                                      | R/W |

|-----|--------|--------------------|----------------------------------------------------------------------------------|-----|

| b0  | MSTPC0 | RAM0 Module Stop*1 | Target module: RAM0 (0000 0000h to 0000 27FFh) 0: RAM0 operating 1: RAM0 stopped | R/W |

| Bit | Symbol | Bit Name           | Description                                                                                                | R/W |

|-----|--------|--------------------|------------------------------------------------------------------------------------------------------------|-----|

| b0  | MSTPC0 | RAM0 Module Stop*1 | Target module: RAM0 (0000 0000h to 0000 27FFh, 0000 4000h to 0000 4A7Fh) 0: RAM0 operating 1: RAM0 stopped | R/W |

•Page 192, Table 12.1 Association between PRCR Bits and Registers to be Protected is corrected as follows:

## **Before correction**

| PRCR Bit | Register to be Protected                                                                                                                                                                                                                                                                                      |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRC0     | <ul> <li>Registers related to the clock generation circuit:</li> <li>SCKCR, SCKCR3, PLLCR, PLLCR2, MOSCCR, LOCOCR, ILOCOCR, OSTDCR, OSTDSR, MEMWAITLOCOTRR, ILOCOTRR, HOCOTRR0, HOCOTRR3</li> </ul>                                                                                                           |

| PRC1     | <ul> <li>Register related to the operating modes:     SYSCR1</li> <li>Registers related to low power consumption functions:     SBYCR, MSTPCRA, MSTPCRB, MSTPCRC, OPCCR</li> <li>Registers related to the clock generation circuit:     MOFCR, MOSCWTCR</li> <li>Software reset register:     SWRR</li> </ul> |

| PRC3     | · Registers related to the LVD: LVCMPCR, LVD1CR0, LVD1CR1, LVD1SR, LVD2CR0, LVD2CR1, LVD2SR                                                                                                                                                                                                                   |

## Corrections

| PRCR Bit | Register to be Protected                                                                                                                                                                                                                                                                                      |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRC0     | Registers related to the clock generation circuit: SCKCR, SCKCR3, PLLCR, PLLCR2, MOSCCR, LOCOCR, ILOCOCR, HOCOCR, OSTDCR, OSTDSR, MEMWAIT                                                                                                                                                                     |

| PRC1     | <ul> <li>Register related to the operating modes:     SYSCR1</li> <li>Registers related to low power consumption functions:     SBYCR, MSTPCRA, MSTPCRB, MSTPCRC, OPCCR</li> <li>Registers related to the clock generation circuit:     MOFCR, MOSCWTCR</li> <li>Software reset register:     SWRR</li> </ul> |

| PRC2     | Register related to the clock generation circuit: HOCOWTCR                                                                                                                                                                                                                                                    |

| PRC3     | · Registers related to the LVD:<br>LVCMPCR, LVDLVLR, LVD1CR0, LVD1CR1, LVD1SR, LVD2CR0, LVD2CR1, LVD2SR                                                                                                                                                                                                       |

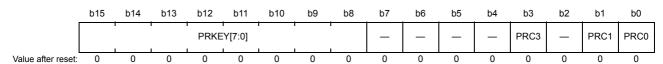

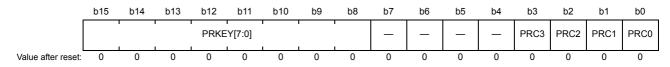

•Page 193, "Protect Register (PRCR)" is corrected as follows:

## **Before correction**

Address(es): 0008 03FEh

| Bit       | Symbol     | Bit Name      | Function                                                                                                                                                                                                            | R/W   |

|-----------|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| b0        | PRC0       | Protect Bit 0 | Enables writing to the registers related to the clock generation circuit and the flash memory.  0: Write disabled  1: Write enabled                                                                                 | R/W   |

| b1        | PRC1       | Protect Bit 1 | Enables writing to the registers related to operating modes, low power consumption functions, the clock generation circuit, and software reset.  0: Write disabled  1: Write enabled                                | R/W   |

| b2        | _          | Reserved      | This bit is read as 0. The write value should be 0.                                                                                                                                                                 | R/W   |

| b3        | PRC3       | Protect Bit 3 | Enables writing to the registers related to the LVD. 0: Write disabled 1: Write enabled                                                                                                                             | R/W   |

| b7 to b4  | _          | Reserved      | These bits are read as 0. The write value should be 0.                                                                                                                                                              | R/W   |

| b15 to b8 | PRKEY[7:0] | PRC Key Code  | These bits control permission and prohibition of writing to the PRCR register.  To modify the PRCR register, write A5h to the 8 higher-order bits and the desired value to the 8 lower-order bits as a 16-bit unit. | R/W*1 |

.....Date: Jan. FH, 2016

Note 1. Write data is not retained.

#### PRCi Bits (Protect Bit i) (i = 0, 1, 3)

These bits enable or disable writing to the corresponding registers to be protected.

Setting the PRCi bits to 1 and 0 enable and disable writing to the corresponding registers to be protected, respectively.

#### Corrections

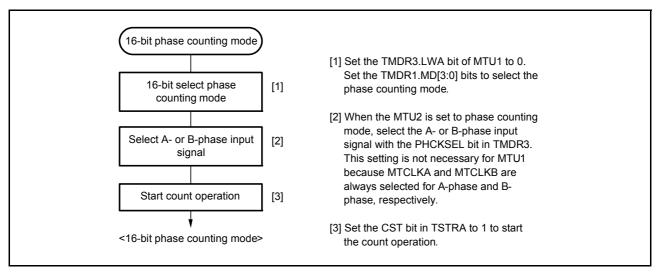

Address(es): 0008 03FEh