発行日:2020年8月20日

# **RENESAS TECHNICAL UPDATE**

〒135-0061 東京都江東区豊洲 3-2-24 豊洲フォレシア ルネサス エレクトロニクス株式会社

問合せ窓口 https://www.renesas.com/jp/ja/support/contact/

| 製   | 品分類                     | システムLSI   | 発行番号   | TN-RZ*-A0067A/J                      |      | Rev. | 第1版 |

|-----|-------------------------|-----------|--------|--------------------------------------|------|------|-----|

| 題名  | QSPI =                  | ントローラの不具合 |        | 情報分類                                 | 技術情報 |      |     |

| 適   |                         |           | 対象ロット等 |                                      |      |      |     |

| 用製品 | RZ/N1 シリーズ<br>(詳細は下記参照) | 全ロット      | 関連資料   | RZ/N1 シリーズ<br>ユーザーズマニュア<br>(詳細は下記参照) | プル   |      |     |

QSPI コントローラの不具合が判明いたしましたので報告いたします。お手数をおかけしますが、本内容をご配慮の上、ご使用くださいますようお願いいたします。

# 1. 適用製品

| 製品分類   | 製品型名          | パッケージタイプ | 機能構成                          |

|--------|---------------|----------|-------------------------------|

| RZ/N1D | R9A06G032NGBG | 400BGA   | デュアル Cortex-A7、PRP/HSR        |

|        | R9A06G032VGBG | 400BGA   | デュアル Cortex-A7                |

|        | R9A06G032PGBG | 400BGA   | デュアル Cortex-A7、PRP/HSR、セキュリティ |

|        | R9A06G032EGBG | 400BGA   | デュアル Cortex-A7、セキュリティ         |

|        | R9A06G032VGBA | 324BGA   | デュアル Cortex-A7                |

|        | R9A06G032EGBA | 324BGA   | デュアル Cortex-A7、セキュリティ         |

| RZ/N1S | R9A06G033NGBG | 324BGA   | シングル Cortex-A7、PRP            |

|        | R9A06G033PGBG | 324BGA   | シングル Cortex-A7、PRP、セキュリティ     |

|        | R9A06G033VGBA | 196BGA   | シングル Cortex-A7                |

|        | R9A06G033EGBA | 196BGA   | シングル Cortex-A7、セキュリティ         |

| RZ/N1L | R9A06G034VGBA | 196BGA   | Cortex-M3                     |

### 2. 関連資料

| 関連資料名                                 | 文書番号            | 改訂前版数 | 改訂後版数 |

|---------------------------------------|-----------------|-------|-------|

| RZ/N1D グループ、RZ/N1S グループ、RZ/N1L グループ ユ | R01UH0751JJ**** | V1.00 | V1.10 |

| ーザーズマニュアル:システム・周辺機能1編                 |                 |       |       |

3. 不具合内容および発生条件

QSPI コントローラの AHB スレーブコントローラは、ベースアドレスが 0番地ベースのアドレスが入力されることを想定しています。一方で、NoC(Network-on-Chip) から QSPI コントローラへは 32bit 幅のメモリマップアドレスが、オフセットアドレス含めてそのまま接続されているため、以下の動作に不具合が発生します。

① AHB デコード機能動作不具合

NoC から入力されたアドレスをデコードし、ハードウェアで外部チップセレクト(CS)を切り替える機能(AHB デコード機能)が正しく動作しません。 QSPI1 において、各 CS サイズを 64MB 設定し、AHB デコード機能を使用した場合の動作を以下に示します。

| 期待する動作       |            |            |            |            |

|--------------|------------|------------|------------|------------|

| MMap Address | 0x10000000 | 0x14000000 | 0x18000000 | 0x1c000000 |

| CS0#         | п          |            |            | <u> </u>   |

| CS1#         | +          | !<br>1     |            |            |

|              | 4          |            |            |            |

| CS2#         | Ц          | <br>       |            |            |

| CS3#         |            | 1          |            |            |

|              |            | :          |            | i          |

| 実際の動作 (不具合動作) |                   |            |            |            |  |  |

|---------------|-------------------|------------|------------|------------|--|--|

| MMap Address  | 0x10000000 0      | 0x14000000 | 0x18000000 | 0x1c000000 |  |  |

| CS0#          |                   |            |            |            |  |  |

| CS1#          |                   |            |            |            |  |  |

| CS2#          |                   |            |            |            |  |  |

| CS3#          | 該当しないと<br>CS3#がアサ |            | 1          |            |  |  |

発行日:2020年8月20日

※MMap Address = Memory Mapped Address

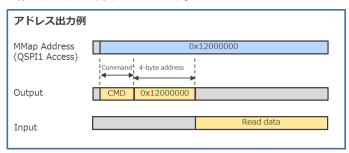

② 4-byte アドレス出力時の不正アドレス出力

16MB より大きい QSPI デバイスを接続する場合、4-byte のアドレス出力が必要となります。RZ/N1 シリーズでサポート する QSPI デバイスは最大 256MB のため、最上位 4bit は本来 4'b0 固定ですが、メモリマップアドレス[31:28]の値が反映 されます。最上位 4-bit を無視する QSPI デバイスであれば問題ありませんが、QSPI デバイスの仕様によっては正常な動作とならない可能性があります。

最上位 4bit に反映されるアドレス

QSPI1 領域アクセス時: 0x1

QSPI2 領域アクセス時: 0xA (RZ/N1S 324pin のみ)

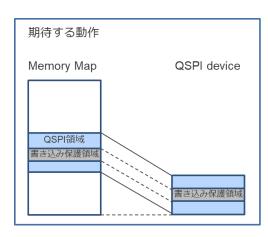

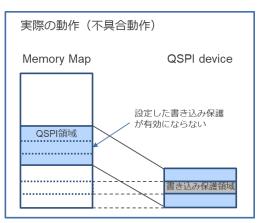

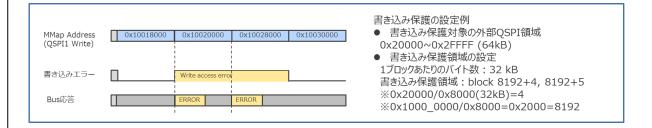

#### ③ 書き込み保護機能動作不具合

QSPI コントローラの書き込み保護機能が、オフセットが含まれた QSPI 領域へのメモリマップアドレスを対象として動作します。 QSPI コントローラは、オフセットを考慮せずにアドレスを比較するため、 QSPI デバイスを基準にして保護領域設定した場合、期待した領域が書き込み保護されません。

発行日:2020年8月20日

4. 不具合の回避策

以下に①~③の回避策を示します。

① AHB デコード機能動作不具合

AHB デコード機能を使用せず、ソフトウェアにより CS を制御することで、RZ/N1 に接続している任意の外部 QSPI デバイスにアクセスすることができます。

**QSPI** コントローラのレジスタにより、 AHB デコード機能を無効にし、CS を選択します。

- AHB デコードイネーブルビット(config\_reg.enable\_ahb\_decoder\_fld) = 0 に設定

- ペリフェラルチップセレクトライン(config\_reg.periph\_cs\_lines\_fld)で CS 選択

- ペリフェラル選択デコード(config\_reg.periph\_sel\_dec\_fld) = 0 の場合

periph\_cs\_lines\_fld に応じて、1 つの CS を選択

$xxx0b : QUAD_CS_N[3:0] = 1110b$

$xx01b: QUAD\_CS\_N[3:0] \!=\! 1101b$

x011b : QUAD\_CS\_N[3:0]=1011b

0111b : QUAD\_CS\_N[3:0]=0111b

1111b:QUAD\_CS\_N[3:0]=1111b(ペリフェラルの選択なし)

• ペリフェラル選択デコード(config\_reg.periph\_sel\_dec\_fld) = 1 の場合:

periph\_cs\_lines\_fld 値がそのまま QUAD\_CS\_N[3:0] に反映

② 4-byte アドレス出力時の不正アドレス出力

メモリマップアドレスをリマップさせることにより、オフセット無しの 4-byte アドレスを出力させることが可能です。

• アドレスリマッピングレジスタ(remap\_addr\_reg) にアドレスに加算する値を設定

QSPI1 領域アクセス時: 0xF0000000

※0x100000000【ベースアドレス】+0xF0000000【加算オフセット値】=0x00000000

QSPI2 領域アクセス時: 0x60000000

%0xA00000000【ベースアドレス】 + 0x60000000【加算オフセット値】 = 0x00000000

• QSPI 設定レジスタ(config\_reg. enb\_ahb\_addr\_remap\_fld) = 1 に設定し、アドレスリマップ機能を有効

発行日:2020年8月20日

③ 書き込み保護機能動作不具合

書き込み保護領域設定は、QSPI コントローラへ入力されるメモリマップアドレスを使用して制御されるため、アドレスオフセット値を考慮した設定を行ってください。もしくは、アドレスリマップ機能を利用してオフセット値の無効化を行ってください。

#### 対策1 オフセット値を考慮して設定する場合

書き込み保護レジスタ(xxx wr prot reg)にオフセット値に対するブロック数を加算する。

例)QSPI1 のオフセット値: 0x100000000、1 ブロックのバイト数を 32 Kbyte(0x8000)とすると、オフセット値/ブロックのバイト数 = 8192 ブロックを書き込み保護する領域に対して加算して、書き込み保護レジスタに設定

対策2 アドレスリマップ機能で、オフセット値を無効にする場合

• アドレスリマッピングレジスタ(remap\_addr\_reg) にアドレスに加算する値を設定

QSPI1 領域アクセス時: 0xF0000000

※0x100000000【ベースアドレス】+0xF0000000【加算オフセット値】=0x00000000

QSPI2 領域アクセス時: 0x60000000

%0xA00000000【ベースアドレス】 + 0x60000000【加算オフセット値】 = 0x00000000

• QSPI 設定レジスタ(config reg. enb ahb addr remap fld) = 1 に設定し、アドレスリマップ機能を有効

## 5. サンプルドライバ

当社より提供の QSPI ドライバは該当機能をサポートしていないため、改訂の予定はありません。

発行日:2020年8月20日