# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | System LSI                                                                                                              | Document<br>No. | TN-RIN-A011                                    | B/E                                                                            | Rev. | 2.00 |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------|--------------------------------------------------------------------------------|------|------|--|

| Title                 | Notification of R-IN32M3 Series User's Ma<br>Modules (Rev.8.00 to Rev.9.00)<br>Revised contents: Corrections and new fu |                 | Information<br>Category Technical Notification |                                                                                |      |      |  |

|                       |                                                                                                                         | Lot No.         |                                                | R-IN32M3 Series User's Manual:                                                 |      |      |  |

| Applicable<br>Product | See following                                                                                                           | All lots        | Reference<br>Document                          | Peripheral Modules<br>R-IN32M3-EC, R-IN32M3-CL<br>Rev9.00<br>(R18UZ0007EJ0900) |      |      |  |

R-IN32M3 Series User's Manual Peripheral Modules Rev. 9.00 (R18UZ0007EJ0900) has been released on Renesas website. This technical update follows revision 1.00 and includes the entirety of revised items. For details, refer to "2. Documentation Updates" given below. Please take note that items marked with "caution needed" may have severe impact on the operation of corresponding devices.

#### 1 Applicable Product

| Product Type  | Model Marking | Product Code         |

|---------------|---------------|----------------------|

|               | MC-10287F1    | MC-10287F1-HN4-A     |

| R-IN32M3-EC   | MC-10287F1    | MC-10287F1-HN4-M1-A  |

| R-INSZIVIS-EC | MC-10287BF1   | MC-10287BF1-HN4-A    |

|               | MIC-10207 BF1 | MC-10287BF1-HN4-M1-A |

|               | D60510F1      | UPD60510F1-HN4-A     |

| R-IN32M3-CL   | D00510F1      | UPD60510F1-HN4-M1-A  |

| R-IN32WI3-CL  | D60510BF1     | UPD60510BF1-HN4-A    |

|               | DOUSTUBET     | UPD60510BF1-HN4-M1-A |

#### 2 Documentation Updates

|    |                                                  | Applicable       | (                    | (1/5)        |

|----|--------------------------------------------------|------------------|----------------------|--------------|

| No | Applicable Item (Rev. 9.00 Section)              | Page (Rev. 9.00) | Contents             | Revised      |

| 1  | 2. Clocks and Resets                             | 2-1              | Complement           | $\checkmark$ |

| 2  | 2.1.1 Description of Internal Clocks             | 2-1              | Complement           | $\checkmark$ |

| 3  | 2.1.1 Description of Internal Clocks             | 2-1              | Complement           | $\checkmark$ |

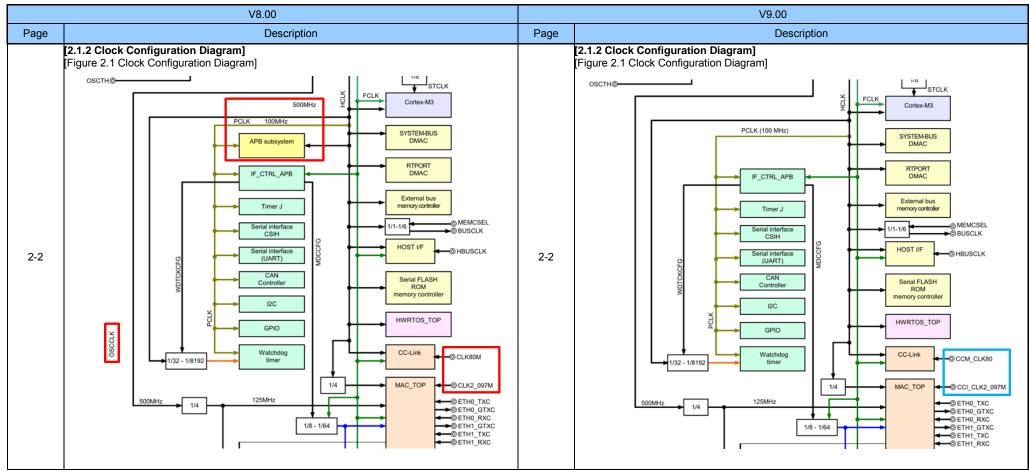

| 4  | 2.1.2 Clock Configuration Diagram                | 2-2              | Error correction     | $\checkmark$ |

| 5  | 2.2.2 Clock Control Registers (CLKGTD0, CLKGTD1) | 2-4              | Error correction     | $\checkmark$ |

| 6  | 2.3.2 (5) Reset output (RSTOUTZ output)          | 2-7              | Error correction     | $\checkmark$ |

| 7  | 2.3.4 (1) Software Reset Register (SFTRES1)      | 2-10             | Expression alignment | $\checkmark$ |

| 8  | 3. CPU and Internal RAMs                         | 3-1              | Complement           | $\checkmark$ |

| 9  | 3.4.2 Read Buffer                                | 3-3              | Error correction     | $\checkmark$ |

| 10 | 3.5 Internal Data RAM                            | 3-4              | Expression alignment | $\checkmark$ |

| 11 | 3.6 Buffer RAM                                   | 3-5              | Error correction     | $\checkmark$ |

| 12 | 4. Bus Architecture                              | 4-1              | Error correction     |              |

| 13 | 6.2 Semaphores                                   | 6-1              | Error correction     | $\checkmark$ |

| 14 | Deleted from Rev. 8.00: 6.6 Service Calls        | —                | Expression alignment | $\checkmark$ |

| 15 | 7. Gigabit Ethernet MAC                          | 7-1              | Expression alignment | $\checkmark$ |

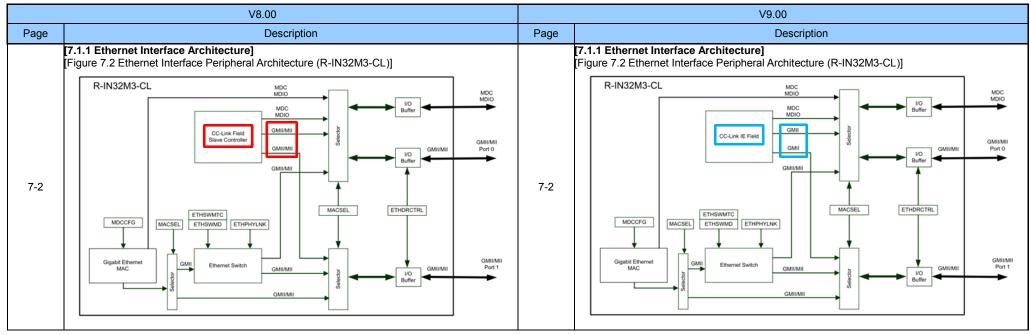

| 16 | 7.1.1 Ethernet Interface Architecture            | 7-2              | Expression alignment | $\checkmark$ |

| 17 | 7.3.1 (3) Gigabit Ethernet MAC control register  | 7-4 ~ 7-5        | Error correction     | $\checkmark$ |

| 18 | 7.3.1 (3) Gigabit Ethernet MAC control register  | 7-5              | Expression alignment | $\checkmark$ |

| 19 | 7.3.1 (4) Hardware function call register        | 7-5              | Expression alignment |              |

| 20 | 7.3.2.1 MAC Select Register (MACSEL)             | 7-6              | Error correction     |              |

| 21 | 7.3.3.1 MDC Clock Select Register (MDCCFG)       | 7-7              | Error correction     | $\checkmark$ |

| 22 | 7.3.4.1 MIIM Register (GMAC_MIIM)                | 7-9              | Expression alignment | $\checkmark$ |

| 23 | 7.3.4.1 MIIM Register (GMAC_MIIM)                | 7-9              | Expression alignment | $\checkmark$ |

| 24 | 7.3.4.1 MIIM Register (GMAC_MIIM)                | 7-9              | Expression alignment | $\checkmark$ |

| 25 | 7.3.4.1 MIIM Register (GMAC_MIIM)                | 7-9              | Expression alignment | $\checkmark$ |

| 26 | 7.3.4.2 TX ID Register (GMAC_TXID)               | 7-10             | Complement           | $\checkmark$ |

| 27 | 7.3.4.3 TX Result Register (GMAC_TXRESULT)       | 7-10             | Expression alignment | $\checkmark$ |

| 28 | 7.3.4.3 TX Result Register (GMAC_TXRESULT)       | 7-10             | Expression alignment | $\checkmark$ |

| 29 | 7.3.4.4 Mode Register (GMAC_MODE)                | 7-11             | Complement           | $\checkmark$ |

| 30 | 7.3.4.4 Mode Register (GMAC_MODE)                | 7-11             | Complement           | $\checkmark$ |

(1/5)

| No               | Applicable Item (Rev. 9.00 Section)                               | Applicable<br>Page (Rev. 9.00) | Contents             | 2/5)<br>Revis |

|------------------|-------------------------------------------------------------------|--------------------------------|----------------------|---------------|

| 31               | 7.3.4.4 Mode Register (GMAC_MODE)                                 | 7-11                           | Complement           | $\checkmark$  |

| 32               | 7.3.4.5 RX Mode Register (GMAC_RXMODE)                            | 7-11                           | Complement           | $\checkmark$  |

| 33               | 7.3.4.5 RX Mode Register (GMAC_RXMODE)                            | 7-11                           | Expression alignment | $\checkmark$  |

| 34               | 7.3.4.6 TX Mode Register (GMAC_TXMODE)                            | 7-13                           | Complement           |               |

| 35               | 7.3.4.6 TX Mode Register (GMAC_TXMODE)                            | 7-13                           | Error correction     |               |

| 36               | 7.3.4.6 TX Mode Register (GMAC_TXMODE)                            | 7-13                           | Complement           |               |

| 37               | 7.3.4.6 TX Mode Register (GMAC_TXMODE)                            | 7-13                           | Complement           |               |

| 38               | 7.3.4.6 TX Mode Register (GMAC_TXMODE)                            | 7-14                           | Expression alignment |               |

| 39               | 7.3.4.7 Reset Register (GMAC_RESET)                               | 7-15                           | Complement           | $\checkmark$  |

| 40               | 7.3.4.7 Reset Register (GMAC_RESET)                               | 7-15                           | Expression alignment | $\checkmark$  |

| 41               | 7.3.4.7 Reset Register (GMAC_RESET)                               | 7-15                           | Expression alignment | $\checkmark$  |

| 42               | 7.3.4.7 Reset Register (GMAC_RESET)                               | 7-15                           | Expression alignment | √             |

| 43               | 7.3.4.8 Pause Packet Data Register (GMAC_PAUSEn)                  | 7-16                           | Complement           | ~             |

| 44               | 7.3.4.9 RX Flow Control Register (GMAC_FLWCTL)                    | 7-17                           | Complement           | ~             |

| 45               | 7.3.4.10 Pause Packet Register (GMAC_PAUSPKT)                     | 7-18                           | Complement           | √             |

| 46               | 7.3.4.10 Pause Packet Register (GMAC_PAUSPKT)                     | 7-18                           | Expression alignment | ~             |

| 47               | 7.3.4.11 MAC Address Registers (GMAC_ADRnA, GMAC_ADRnB)           | 7-19                           | Error correction     | √             |

| 48               | 7.3.4.11 MAC Address Registers (GMAC ADRnA, GMAC ADRnB)           | 7-19                           | Expression alignment | √             |

| 49               | 7.3.4.12 RX FIFO Status Register (GMAC_RXFIFO)                    | 7-20                           | Complement           | ~             |

| 50               | 7.3.4.12 RX FIFO Status Register (GMAC_RXFIFO)                    | 7-20                           | Expression alignment | · ·           |

| 51               | 7.3.4.12 RX FIFO Status Register (GMAC_RXFIFO)                    | 7-20                           | Expression alignment | · ·           |

| 52               | 7.3.4.12 RX FIFO Status Register (GMAC_RXFIFO)                    | 7-20                           | Expression alignment | v<br>√        |

| 52<br>53         |                                                                   |                                | · · ·                | <br>✓         |

|                  | 7.3.4.13 TX FIFO Status Register (GMAC_TXFIFO)                    | 7-21                           | Complement           | ✓<br>✓        |

| 54               | 7.3.4.13 TX FIFO Status Register (GMAC_TXFIFO)                    | 7-21                           | Error correction     |               |

| 55               | 7.3.4.14 TCPIPACC Register (GMAC_ACC)                             | 7-22                           | Complement           | ~             |

| 56               | 7.3.4.14 TCPIPACC Register (GMAC_ACC)                             | 7-22                           | Complement           | ~             |

| 57               | 7.3.4.15 RX MAC Enable Register (GMAC_RXMAC_ENA)                  | 7-22                           | Complement           | ~             |

| 58               | 7.3.4.16 LPI mode control register (GMAC_LPI_MODE)                | 7-23                           | Complement           | ~             |

| 59               | 7.3.4.17 LPI Client Timing Control Register (GMAC_LPI_TIMING)     | 7-23                           | Complement           | ~             |

| 60               | 7.3.4.17 LPI Client Timing Control Register (GMAC_LPI_TIMING)     | 7-23                           | Error correction     | ~             |

| 61               | 7.3.4.18 Receive Buffer Information Register (BUFID)              | 7-24                           | Error correction     | ~             |

| 62               | 7.3.4.18 Receive Buffer Information Register (BUFID)              | 7-24                           | Complement           | ~             |

| 63               | 7.3.5 Hardware Function Call Register                             | 7-25                           | Expression alignment |               |

| 64               | 7.3.5.1 Hardware Function Command Register (SYSC)                 | 7-25                           | New function         |               |

| 65               | 7.3.5.2 Hardware Function Argument Registers (R4-7)               | 7-26                           | Complement           |               |

| 66               | 7.3.5.3 Hardware Function Operating Mode Control Register (CMD)   | 7-27                           | New function         |               |

| 67               | 7.3.5.4 Hardware Function Return Value Registers (R0, R1)         | 7-28                           | Complement           |               |

| 68               | 7.3.5.5 Hardware Function Type Register (CNTX TYPE0)              | 7-28                           | New function         |               |

| 69               | 7.3.5.6 Hardware Function State Register (CNTX_STAT0)             | 7-29                           | New function         |               |

| 70               | 7.4.1 Hardware Functions                                          | 7-30                           | New function         |               |

| 71               | 7.4.1.1 Initial Settings                                          | 7-31                           | New function         | ~             |

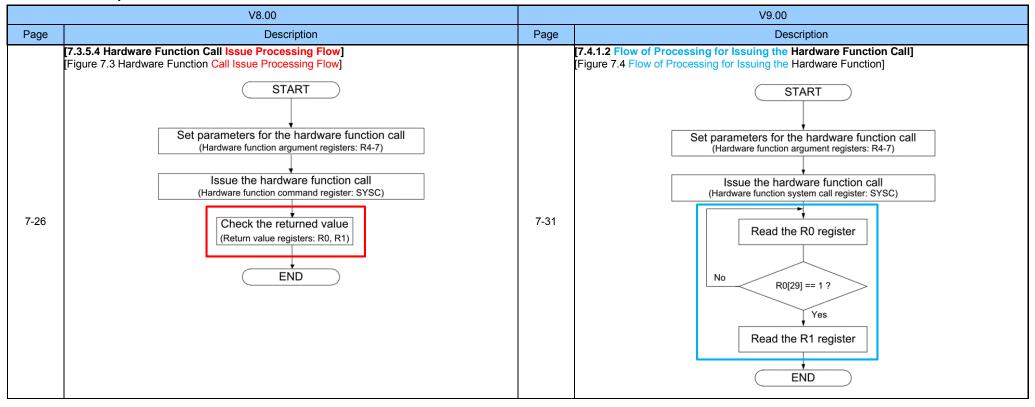

| 72               | 7.4.1.2 Flow of Processing for Issuing the Hardware Function Call | 7-31                           | Error correction     | ~             |

| 73               | 7.4.1.3 Buffer Allocator                                          | 7-32                           | New function         |               |

|                  |                                                                   | 7-32                           |                      |               |

| 74               | 7.4.1.4 MAC DMA Controller                                        |                                | New function         | - v           |

| 75<br>76         | 7.4.1.5 Buffer RAM DMA Controller                                 | 7-50                           | New function         | -             |

|                  | 7.4.2 Interrupts                                                  | 7-55                           | New function         | +             |

| 77               | Deleted from Rev. 8.00: 7.4.1.1 Initial Settings                  | -                              | Expression alignment | v             |

| 78               | 7.4.3.1 Acquiring a Transmit Buffer                               | 7-58                           | Error correction     | v             |

| 79               | 7.4.3.2 Creating TX Data                                          | 7-59                           | Expression alignment | v             |

| 30               | Deleted from Rev. 8.00: 7.4.2.1 Initial Settings                  | -                              | Error correction     | v             |

| 31               | 7.4.4.5 Rx Data Format *caution needed                            | 7-64                           | Error correction     |               |

| 32               | 7.4.4.5 Rx Data Format                                            | 7-64                           | Error correction     |               |

| 33               | 7.4.4.5 Rx Data Format *caution needed                            | 7-65                           | New function         |               |

| 34               | 8.3.1 (2) Switch Configuration Registers                          | 8-3                            | Error correction     | v             |

| 35               | 8.3.2.1 Ethernet PHY LINK Mode Register (ETHPHYLNK)               | 8-6                            | Complement           | v             |

| 86               | 8.3.2.1 Ethernet PHY LINK Mode Register (ETHPHYLNK)               | 8-6                            | Complement           | `             |

| 37               | 8.3.2.1 Ethernet PHY LINK Mode Register (ETHPHYLNK)               | 8-6                            | Expression alignment | `             |

| 38               | 8.3.2.1 Ethernet PHY LINK Mode Register (ETHPHYLNK)               | 8-6                            | Expression alignment | v             |

| 39               | 8.3.2.1 Ethernet PHY LINK Mode Register (ETHPHYLNK)               | 8-6                            | Expression alignment | v             |

| 90               | 8.3.2.1 Ethernet PHY LINK Mode Register (ETHPHYLNK)               | 8-6                            | Expression alignment | v             |

| ) <u>)</u><br>)1 | 8.3.3.5 Input Learning Blocking Register (INPUT_LEARN_BLOCK)      | 8-14                           | Error correction     | v             |

| 92               | 8.5.2 Switch Initialization                                       | 8-96                           | Expression alignment | v             |

| )2               | 8.5.2 Switch Initialization                                       | 8-97                           | Expression alignment |               |

| 93<br>94         |                                                                   | 9-1                            |                      | v             |

|                  | 9. Asynchronous SRAM Memory Controller (ROM/SRAM)                 |                                | Complement           | · ·           |

| 95               | 9.2 (1) (a) SRAM and external I/O connection                      | 9-2                            | Error correction     | -             |

| 96               | 9.2 (1) (b) Page ROM connection                                   | 9-2                            | Error correction     | +             |

| 97               | 9.3.3 Static Memory Control Registers 0 to 3 (SMC0 to SMC3)       | 9-6                            | Error correction     | v             |

| 98               | 9.3.3 Static Memory Control Registers 0 to 3 (SMC0 to SMC3)       | 9-6                            | Error correction     | v             |

| 99               | 9.3.5 Write Enable Switching Register (WREN)                      | 9-11                           | Expression alignment | v             |

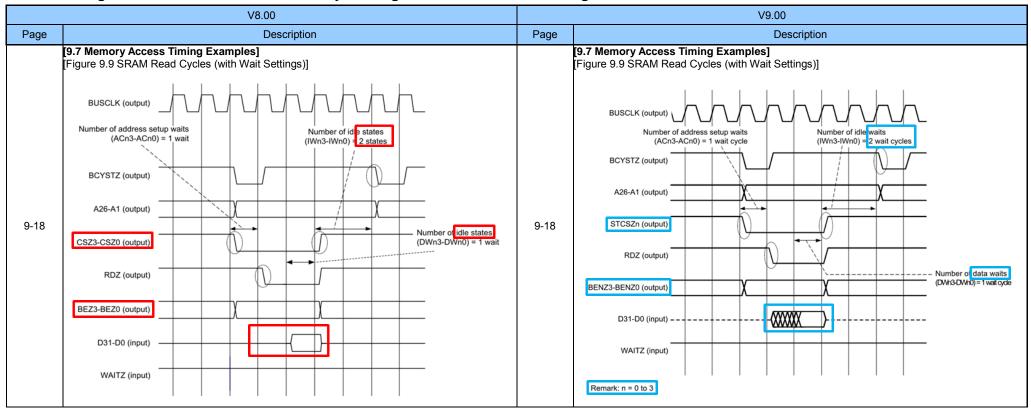

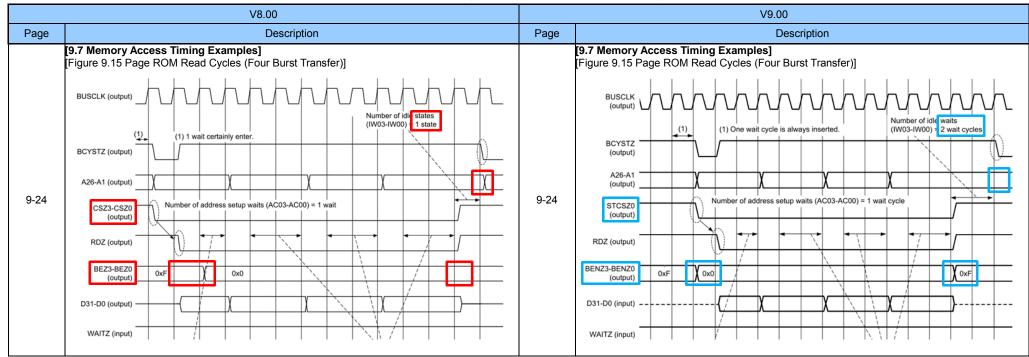

| 00               | 9.7 Memory Access Timing Examples                                 | 9-17 ~ 9-24                    | Error correction     | ,             |

|                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |                                                                                                                                          | (3/5)                 |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| No                                                                                      | Applicable Item (Rev. 9.00 Section)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Applicable<br>Page (Rev. 9.00)                                                                           | Contents                                                                                                                                 | Revised               |

| 101                                                                                     | 9.7 Memory Access Timing Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9-18                                                                                                     | Error correction                                                                                                                         | √                     |

| 102                                                                                     | 9.7 Memory Access Timing Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9-24                                                                                                     | Error correction                                                                                                                         | ~                     |

| 103                                                                                     | 10. Synchronous Burst Access Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-1                                                                                                     | Complement                                                                                                                               | ✓<br>✓                |

| 104<br>105                                                                              | 10.1 Features<br>10.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-1<br>10-2                                                                                             | Error correction<br>Error correction                                                                                                     | ✓<br>✓                |

| 105                                                                                     | 10.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10-2                                                                                                     | Error correction                                                                                                                         | ·<br>✓                |

| 100                                                                                     | 10.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10-2                                                                                                     | Error correction                                                                                                                         | · √                   |

| 108                                                                                     | 10.2 Control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10-3                                                                                                     | Error correction                                                                                                                         | $\checkmark$          |

| 109                                                                                     | 10.2.1 WAITZ Selection Register (WAITZSEL)                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10-4                                                                                                     | Error correction                                                                                                                         | $\checkmark$          |

| 110                                                                                     | 10.2.1 WAITZ Selection Register (WAITZSEL)                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10-4 ~ 10-5                                                                                              | Complement                                                                                                                               | $\checkmark$          |

| 111                                                                                     | 10.2.2 Synchronous Burst Access Memory Controller Area Select Registers<br>(SMADSEL0 to SMADSEL3)                                                                                                                                                                                                                                                                                                                                                                                                        | 10-7                                                                                                     | Error correction                                                                                                                         | ~                     |

| 112                                                                                     | 10.2.2 Synchronous Burst Access Memory Controller Area Select Registers<br>(SMADSEL0 to SMADSEL3)                                                                                                                                                                                                                                                                                                                                                                                                        | 10-7                                                                                                     | Error correction                                                                                                                         | ~                     |

| 113                                                                                     | 10.2.4 Synchronous Burst Access Memory Controller Operation Setting<br>Register (SMC352MD)                                                                                                                                                                                                                                                                                                                                                                                                               | 10-9                                                                                                     | Error correction                                                                                                                         | $\checkmark$          |

| 114                                                                                     | 10.2.4 Synchronous Burst Access Memory Controller Operation Setting<br>Register (SMC352MD) *caution needed                                                                                                                                                                                                                                                                                                                                                                                               | 10-9                                                                                                     | Error correction                                                                                                                         | $\checkmark$          |

| 115                                                                                     | 10.2.4 Synchronous Burst Access Memory Controller Operation Setting<br>Register (SMC352MD)                                                                                                                                                                                                                                                                                                                                                                                                               | 10-9                                                                                                     | Error correction                                                                                                                         | ~                     |

| 116                                                                                     | 10.2.6 Cycle Setting Register (SET_CYCLE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10-11                                                                                                    | Error correction                                                                                                                         | ✓                     |

| 117                                                                                     | 10.2.8 Synchronous Burst Access Memory Controller Refresh Setting<br>Register (REF_PERIOD0) *caution needed                                                                                                                                                                                                                                                                                                                                                                                              | 10-15                                                                                                    | Error correction                                                                                                                         | ~                     |

| 118                                                                                     | 10.2.10 Synchronous Burst Access Memory Controller CSn Mode Registers (OPMODE0_n)                                                                                                                                                                                                                                                                                                                                                                                                                        | 10-16                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

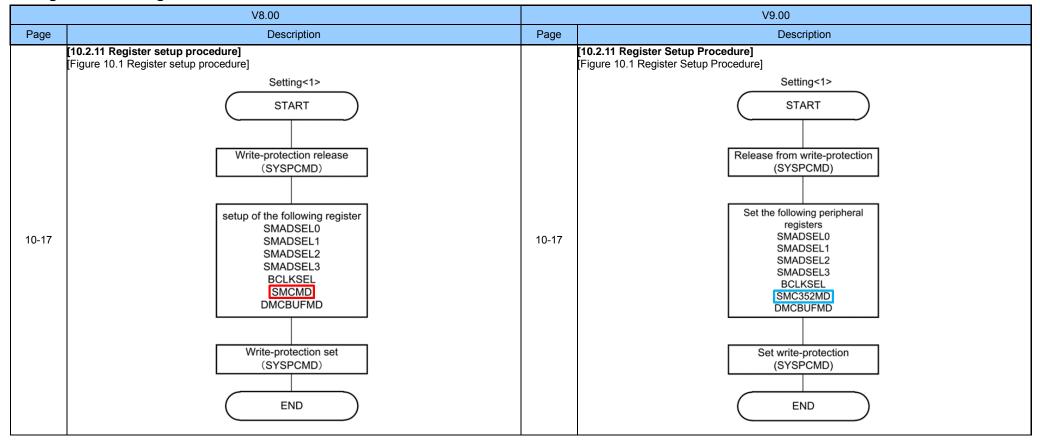

| 119                                                                                     | 10.2.11 Register Setup Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-17                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

| 120                                                                                     | 10.3.1 Bus Clock Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10-18                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

| 121                                                                                     | 10.3.3 Address/Data Multiplexing Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10-19                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

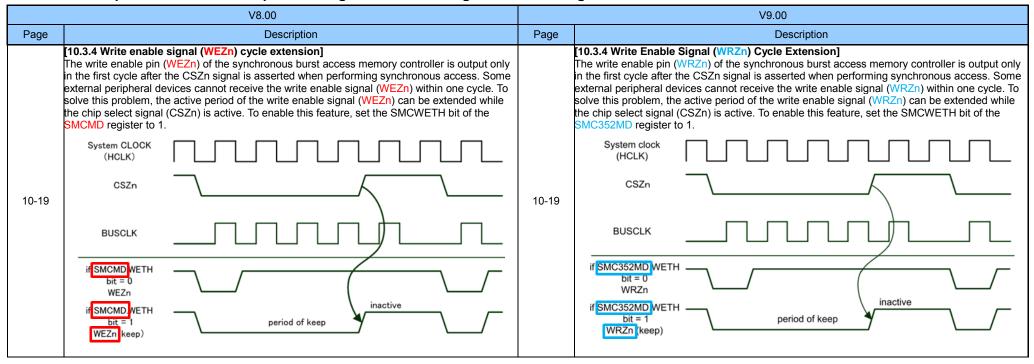

| 122                                                                                     | 10.3.4 Write Enable Signal (WRZn) Cycle Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10-19                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

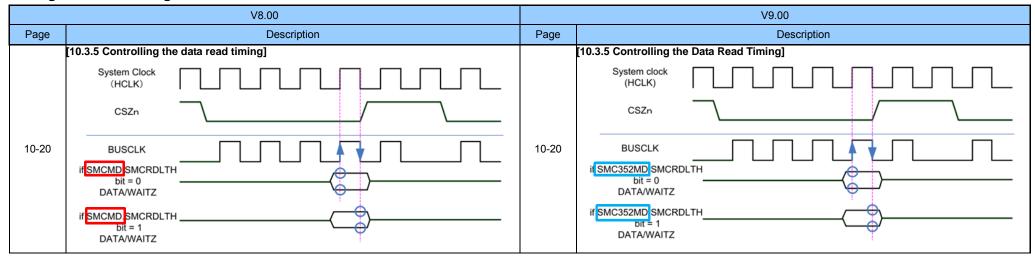

| 123                                                                                     | 10.3.5 Controlling the Data Read Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10-20                                                                                                    | Error correction                                                                                                                         | ~                     |

| 124                                                                                     | 10.3.6 (1) Connection example 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10-21                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

| 125                                                                                     | 10.3.6 (2) Connection example 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10-22                                                                                                    | Error correction                                                                                                                         | √                     |

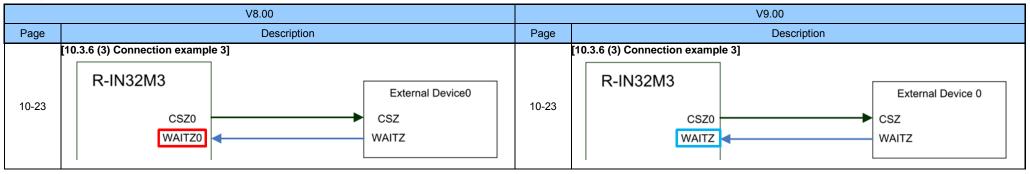

| 126                                                                                     | 10.3.6 (3) Connection example 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10-23                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

| 127                                                                                     | 10.4.2 Synchronous Access Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-42                                                                                                    | Complement                                                                                                                               |                       |

| 128                                                                                     | 11. External MCU Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11-1                                                                                                     | Complement                                                                                                                               |                       |

| 129                                                                                     | 11.2.5 (2) HOSTIF bus control register (HIFBCC)                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11-18                                                                                                    | Expression alignment                                                                                                                     | $\checkmark$          |

| 130                                                                                     | 11.3.2 Selection of Operational Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11-27                                                                                                    | Complement                                                                                                                               | v                     |

| 131<br>132                                                                              | 11.3.4 (2) HOSTIF synchronous SRAM control register 0 (HIFEXT0)<br>11.3.4 (3) HOSTIF synchronous SRAM control register 1 (HIFEXT1)                                                                                                                                                                                                                                                                                                                                                                       | 11-29<br>11-30                                                                                           | Complement                                                                                                                               |                       |

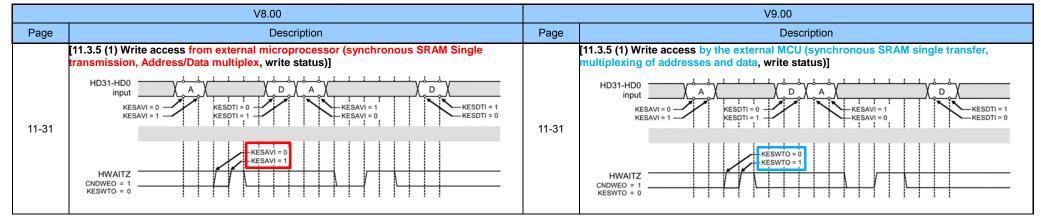

| 132                                                                                     | 11.3.5 (1) Write access by the external MCU (synchronous SRAM single                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11-30                                                                                                    | Complement                                                                                                                               | ~                     |

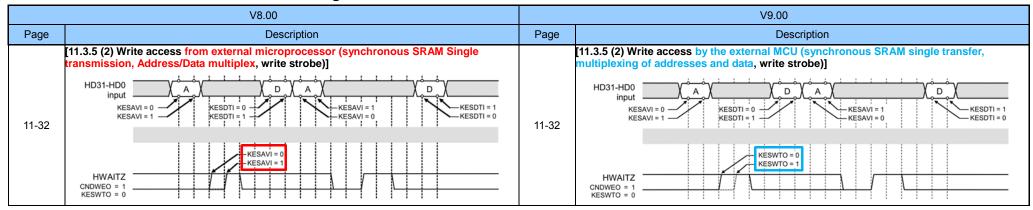

| 133                                                                                     | transfer, multiplexing of addresses and data, write status)<br>1.3.5 (2) Write access by the external MCU (synchronous SRAM single                                                                                                                                                                                                                                                                                                                                                                       | 11-31                                                                                                    | Error correction                                                                                                                         | · ·                   |

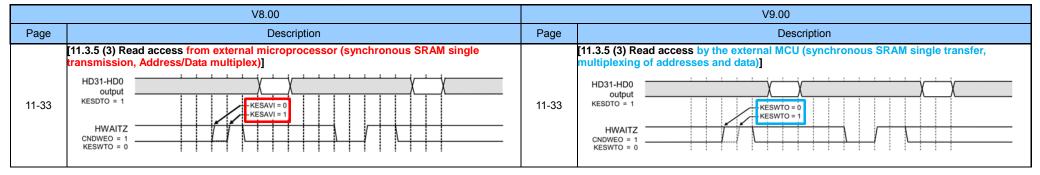

| 134                                                                                     | transfer, multiplexing of addresses and data, write strobe)<br>11.3.5 (3) Read access by the external MCU (synchronous SRAM single                                                                                                                                                                                                                                                                                                                                                                       | 11-32                                                                                                    | Error correction                                                                                                                         | · ·                   |

| 135<br>136                                                                              | transfer, multiplexing of addresses and data)                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11-33<br>12-1 ~ 12-25                                                                                    | Error correction                                                                                                                         | · ·                   |

| 136                                                                                     | 12.2.1 Transfer Mode Control Register (SFMSMD)                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12-1~12-25                                                                                               | Error correction                                                                                                                         | ·<br>✓                |

| 137                                                                                     | 12.4.4 (1) ROM Reading by Individual Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12-3                                                                                                     | Complement                                                                                                                               | ·<br>~                |

| 139                                                                                     | 12.4.4 (2) ROM Reading by Using Prefetching                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12-21                                                                                                    | Complement                                                                                                                               | · ·                   |

| 140                                                                                     | 12.4.4 (4) ROM Reading by Using SPI Bus Cycle Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12-22                                                                                                    | Complement                                                                                                                               | $\checkmark$          |

| 141                                                                                     | 12.4.5 Automatic Release from the Deep Power-Down State                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12-24                                                                                                    | Complement                                                                                                                               | ~                     |

| 142                                                                                     | 12.4.6 (3) SPI Bus Cycle Generation in Direct Communications Mode                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12-25                                                                                                    | Complement                                                                                                                               | 1                     |

| 143                                                                                     | 13.1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13-4                                                                                                     | Complement                                                                                                                               |                       |

| 144                                                                                     | 13.4.3.2 (4) (a) Channel status register (CHSTATn) (3/6)                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13-21                                                                                                    | Complement                                                                                                                               | $\checkmark$          |

| 145                                                                                     | 13.4.3.2 (4) (b) Channel control register (CHCTRLn) (1/3)                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13-25                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

| 146                                                                                     | 13.4.3.2 (4) (c) Channel configuration register (CHCFGn) (5/7)                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13-32                                                                                                    | Complement                                                                                                                               | ~                     |

|                                                                                         | 13.4.4.2 (4) (b) Channel control register (RTCHCTRL) (1/3)                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13-58                                                                                                    | Error correction                                                                                                                         | $\checkmark$          |

| 147                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          | Europe composition                                                                                                                       | $\checkmark$          |

| 148                                                                                     | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13-84                                                                                                    | Error correction                                                                                                                         |                       |

| 148<br>149                                                                              | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)<br>13.4.6 DMA Trigger Factor Selection Register (DTFRn, RTDTFR)                                                                                                                                                                                                                                                                                                                                                                            | 13-87                                                                                                    | Error correction                                                                                                                         | ✓                     |

| 148                                                                                     | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)         13.4.6 DMA Trigger Factor Selection Register (DTFRn, RTDTFR)         13.7.2 (1) Register Mode Operation Flow         13.7.2 (2) (c) Terminal count output (DMATCZp) mask setting                                                                                                                                                                                                                                                   |                                                                                                          |                                                                                                                                          | ✓<br>✓<br>✓           |

| 148<br>149<br>150<br>151                                                                | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)         13.4.6 DMA Trigger Factor Selection Register (DTFRn, RTDTFR)         13.7.2 (1) Register Mode Operation Flow         13.7.2 (2) (c) Terminal count output (DMATCZp) mask setting         (CHCFGn.TCM)                                                                                                                                                                                                                              | 13-87<br>13-93<br>13-94                                                                                  | Error correction<br>Error correction<br>Error correction                                                                                 | ✓<br>✓                |

| 148<br>149<br>150<br>151<br>152                                                         | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)         13.4.6 DMA Trigger Factor Selection Register (DTFRn, RTDTFR)         13.7.2 (1) Register Mode Operation Flow         13.7.2 (2) (c) Terminal count output (DMATCZp) mask setting<br>(CHCFGn.TCM)         13.7.2 (3) (b) When two register sets are used for continuous execution                                                                                                                                                   | 13-87<br>13-93<br>13-94<br>13-97                                                                         | Error correction<br>Error correction<br>Error correction<br>Error correction                                                             | ✓<br>✓<br>✓           |

| 148<br>149<br>150<br>151<br>152<br>153                                                  | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)         13.4.6 DMA Trigger Factor Selection Register (DTFRn, RTDTFR)         13.7.2 (1) Register Mode Operation Flow         13.7.2 (2) (c) Terminal count output (DMATCZp) mask setting<br>(CHCFGn.TCM)         13.7.2 (3) (b) When two register sets are used for continuous execution         13.8.3 (2) Edge detection                                                                                                                 | 13-87<br>13-93<br>13-94<br>13-97<br>13-118                                                               | Error correction<br>Error correction<br>Error correction<br>Error correction<br>Error correction                                         | ✓<br>✓<br>✓<br>✓      |

| 148         149         150         151         152         153         154             | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)         13.4.6 DMA Trigger Factor Selection Register (DTFRn, RTDTFR)         13.7.2 (1) Register Mode Operation Flow         13.7.2 (2) (c) Terminal count output (DMATCZp) mask setting<br>(CHCFGn.TCM)         13.7.2 (3) (b) When two register sets are used for continuous execution         13.8.3 (2) Edge detection         13.8.3 (3) Level detection                                                                              | 13-87<br>13-93<br>13-94<br>13-97<br>13-118<br>13-119                                                     | Error correction<br>Error correction<br>Error correction<br>Error correction<br>Error correction<br>Error correction                     | ✓<br>✓<br>✓           |

| 148         149         150         151         152         153         154         155 | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)         13.4.6 DMA Trigger Factor Selection Register (DTFRn, RTDTFR)         13.7.2 (1) Register Mode Operation Flow         13.7.2 (2) (c) Terminal count output (DMATCZp) mask setting<br>(CHCFGn.TCM)         13.7.2 (3) (b) When two register sets are used for continuous execution         13.8.3 (2) Edge detection         13.8.4 (1) Specification of the acknowledge signal mode for each DMA<br>transfer request source         | 13-87           13-93           13-94           13-97           13-118           13-119           13-121 | Error correction<br>Error correction<br>Error correction<br>Error correction<br>Error correction<br>Error correction<br>Error correction |                       |

| 148<br>149<br>150<br>151<br>152<br>153<br>154                                           | 13.4.6 DMA Trigger Source Selection Registers (DTFRn, RTDTFR)         13.4.6 DMA Trigger Factor Selection Register (DTFRn, RTDTFR)         13.7.2 (1) Register Mode Operation Flow         13.7.2 (2) (c) Terminal count output (DMATCZp) mask setting<br>(CHCFGn.TCM)         13.7.2 (3) (b) When two register sets are used for continuous execution         13.8.3 (2) Edge detection         13.8.3 (3) Level detection         13.8.4 (1) Specification of the acknowledge signal mode for each DMA | 13-87<br>13-93<br>13-94<br>13-97<br>13-118<br>13-119                                                     | Error correction<br>Error correction<br>Error correction<br>Error correction<br>Error correction<br>Error correction                     | ✓<br>✓<br>✓<br>✓<br>✓ |

| No                | Applicable Item (Rev. 9.00 Section)                                                                                                                                                                           | Applicable<br>Page (Rev. 9.00) | Contents                                     | Revise       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------|--------------|

| 159               | 13.9.1 Setting Example 1 (Register Mode, Single Transfer Mode, and Hardware Trigger)                                                                                                                          | 13-136                         | Error correction                             | $\checkmark$ |

| 160               | 13.9.2 Setting Example 2 (Register Mode, Block Transfer Mode, and Software Trigger)                                                                                                                           | 13-139                         | Error correction                             | ~            |

| 161               | 13.9.2 Setting Example 2 (Register Mode, Block Transfer Mode, and Software Trigger)                                                                                                                           | 13-140                         | Error correction                             | ~            |

| 162               | 13.9.3 Setting Example 3 (Register Mode: Continuous Execution, Block<br>Transfer Mode, and Software Trigger)                                                                                                  | 13-142                         | Error correction                             | ~            |

| 163               | 14.1 Features of TAUJ2                                                                                                                                                                                        | 14-1                           | Expression alignment                         | $\checkmark$ |

| 164               | 14.1 Features of TAUJ2                                                                                                                                                                                        | 14-1                           | Expression alignment                         | √            |

| 165               | 14.1 Features of TAUJ2                                                                                                                                                                                        | 14-1                           | Expression alignment                         | $\checkmark$ |

| 166<br>167        | 14.1 Features of TAUJ2<br>14.1 Features of TAUJ2                                                                                                                                                              | 14-2<br>14-2                   | Complement<br>Error correction               | ✓<br>✓       |

| 168               | 14.1 Features of TAUJ2                                                                                                                                                                                        | 14-2                           | Error correction                             | ·<br>~       |

| 169               | 14.1 Features of TAUJ2                                                                                                                                                                                        | 14-2                           | Error correction                             | $\checkmark$ |

| 170               | 14.1 Features of TAUJ2                                                                                                                                                                                        | 14-2                           | Error correction                             | $\checkmark$ |

| 171               | 14.1 Features of TAUJ2                                                                                                                                                                                        | 14-2                           | Complement                                   | $\checkmark$ |

| 172               | 14.3.2 (1) TAUJ2 Prescaler Clock Select Register (TAUJ2TPS)                                                                                                                                                   | 14-12                          | Expression alignment                         | $\checkmark$ |

| 173               | 14.3.3 (2) TAUJ2 Channel Counter Register (TAUJ2CNTm)                                                                                                                                                         | 14-15                          | Expression alignment                         | $\checkmark$ |

| 174               | 14.3.3 (3) TAUJ2 Channel Mode OS Register (TAUJ2CMORm)                                                                                                                                                        | 14-19                          | Complement                                   | ✓            |

| 175               | 14.5.1 Basic Rules of Synchronous Channel Operation                                                                                                                                                           | 14-31                          | Expression alignment                         | ✓<br>✓       |

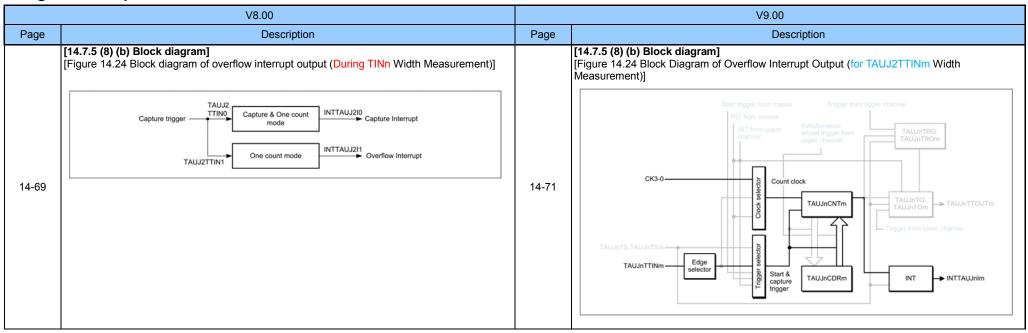

| 176<br>177        | 14.7.5 (8) (b) Block diagram<br>15. Window Watchdog Timer A (WDTA)                                                                                                                                            | <u>14-71</u><br>15-1           | Expression alignment<br>Expression alignment | <br>✓        |

| 178               | 15.1 Features of WDTA                                                                                                                                                                                         | 15-1                           | Expression alignment                         | · √          |

| 179               | 15.2 Functional Overview                                                                                                                                                                                      | 15-2                           | Expression alignment                         | ~            |

| 180               | 16. Asynchronous Serial Interface J (UARTJ)                                                                                                                                                                   | 16-1                           | Expression alignment                         | ~            |

| 181               | 16.1 Features of UARTJn                                                                                                                                                                                       | 16-1                           | Expression alignment                         | √            |

| 182               | 16.1 Features of UARTJn                                                                                                                                                                                       | 16-1                           | Expression alignment                         | $\checkmark$ |

| 183               | 16.1 Features of UARTJn                                                                                                                                                                                       | 16-2                           | Complement                                   | $\checkmark$ |

| 184               | 16.1 Features of UARTJn                                                                                                                                                                                       | 16-2                           | Error correction                             | $\checkmark$ |

| 185               | 16.4 (2) UARTJn control register 1 (URTJnCTL1)                                                                                                                                                                | 16-9                           | Error correction                             |              |

| <u>186</u><br>187 | 16.4 (5) UARTJn status register 0 (URTJnSTR0)<br>16.4 (6) UARTJn status register 1 (URTJnSTR1)                                                                                                                | <u>16-15</u><br>16-16          | Complement<br>Complement                     |              |

| 188               | 16.4 (6) UARTJI status register 1 (URTJIISTRT)                                                                                                                                                                | 16-17                          | Complement                                   |              |

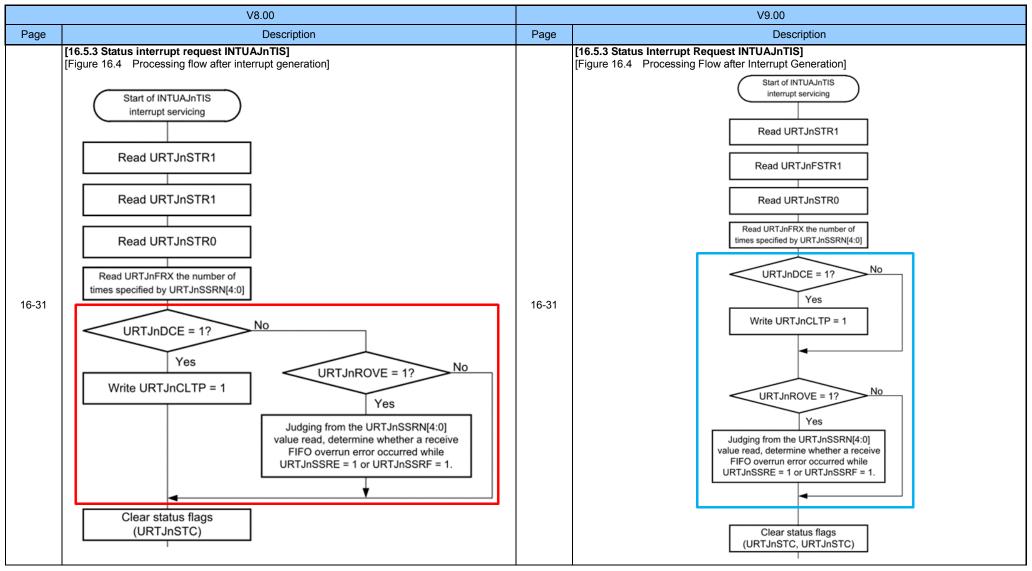

| 189               | 16.5.3 Status Interrupt Request INTUAJnTIS *caution needed                                                                                                                                                    | 16-31                          | Error correction                             |              |

| 190               | 16.6.6 (2) Reception start and stop                                                                                                                                                                           | 16-46                          | Complement                                   |              |

| 191               | 16.7 Bit-Rate Generator                                                                                                                                                                                       | 16-54                          | Complement                                   |              |

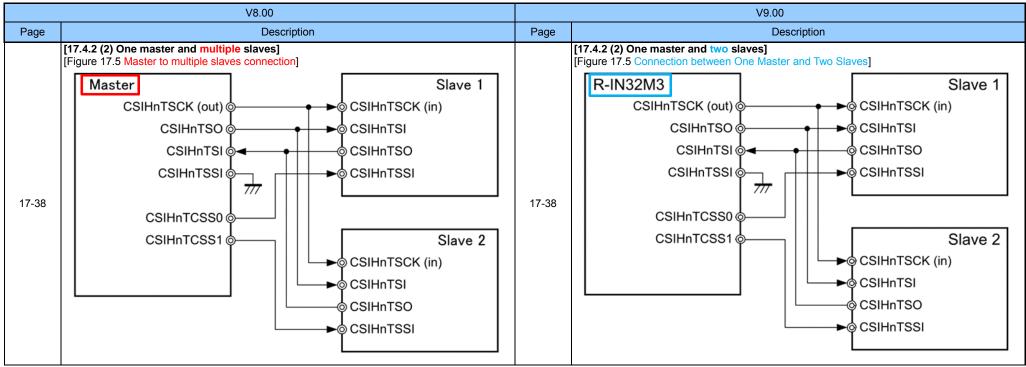

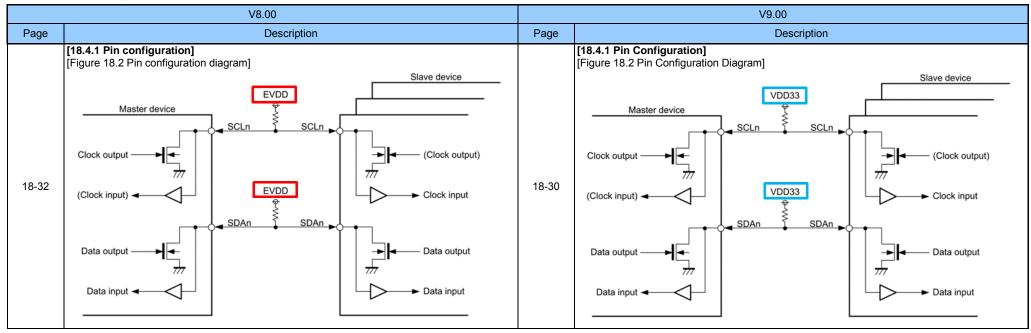

| 192               | 17. Clocked Serial Interface H (CSIH)                                                                                                                                                                         | 17-1                           | Expression alignment                         | $\checkmark$ |