# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | System LSI                                                     |         | Document<br>No.         | TN-RIN-A015A/E                                                                 | Rev. | 1.00 |

|-----------------------|----------------------------------------------------------------|---------|-------------------------|--------------------------------------------------------------------------------|------|------|

| Title                 | Ethernet MAC reception issue in case TCPIP accelerator enabled |         | Information<br>Category | Technical Notification                                                         |      |      |

| Applicable<br>Product | Please refer to [1. Applicable Product] described below.       | Lot No. |                         | R-IN32M3 Series User's Manual:                                                 |      |      |

|                       |                                                                | All lot | Reference<br>Document   | Peripheral Modules<br>R-IN32M3-EC, R-IN32M3-CL<br>Rev9.00<br>(R18UZ0007EJ0900) |      |      |

This document describes information about issues of Ethernet MAC in case TCPIP accelerator is used. Please use the

Ethernet MAC considering those issues.

#### 1. Applicable Product

| Product Type | Model Marking | Product Code         |  |

|--------------|---------------|----------------------|--|

| R-IN32M3-EC  | MC-10287F1    | MC-10287F1-HN4-A     |  |

|              |               | MC-10287F1-HN4-M1-A  |  |

|              | MC-10287BF1   | MC-10287BF1-HN4-A    |  |

|              |               | MC-10287BF1-HN4-M1-A |  |

| R-IN32M3-CL  | D60510F1      | UPD60510F1-HN4-A     |  |

|              |               | UPD60510F1-HN4-M1-A  |  |

|              | D60510BF1     | UPD60510BF1-HN4-A    |  |

|              |               | UPD60510BF1-HN4-M1-A |  |

#### [R-IN32M3 sample software download site]

https://www.renesas.com/products/factory-automation/multi-protocol-communication.html

➔ download

[Sample software related to this issues]

| Target               | Issue Date       |  |  |

|----------------------|------------------|--|--|

| TCP/IP, UDP/IP       | November 7, 2016 |  |  |

| Modbus TCP/RTU/ASCII | March 11, 2016   |  |  |

#### 2. Issue

- 2.1 Reception issue in case Rx FIFO overflow is occurred

- 2.1.1 Content

- It is possible that error information which is related to the previous error frame is included in frame information of normal reception frame.

- It is possible that abnormal frame which caused Rx FIFO overflow is regarded as normal frame because of illegal value is included in frame information

- 2.1.2 Condition

In case Rx FIFO overflow is occurred when Rx TCPIP accelerator is enabled.

2.1.3 Workaround

Any of the following methods should be applied.

- (A) Disable Rx TCPIP accelerator without padding insertion to MAC header. Specifically, clear bit0 of GMAC\_ACC register.

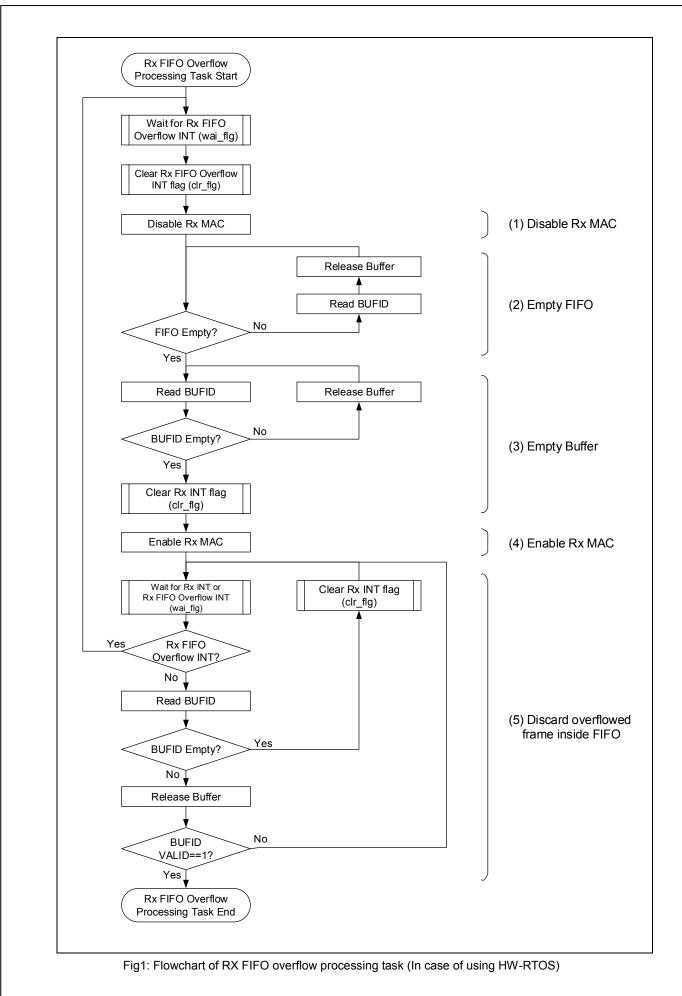

- (B) When Rx FIFO is overflowed, discard all frames left in Rx FIFO and Buffer RAM. Specifically, apply the following procedure;

- (1) Disable Rx MAC.

- (2) Discard all frames inside Rx FIFO.

- (3) Discard all frames inside Buffer RAM.

- (4) Enable Rx MAC.

- (5) Discard at least one frame with BUFID VALID bit = 1. This is because FIFO empty state can be read even if the frame which caused FIFO overflow remains in the FIFO. Receive normal frame once and discard remained abnormal frame with it.

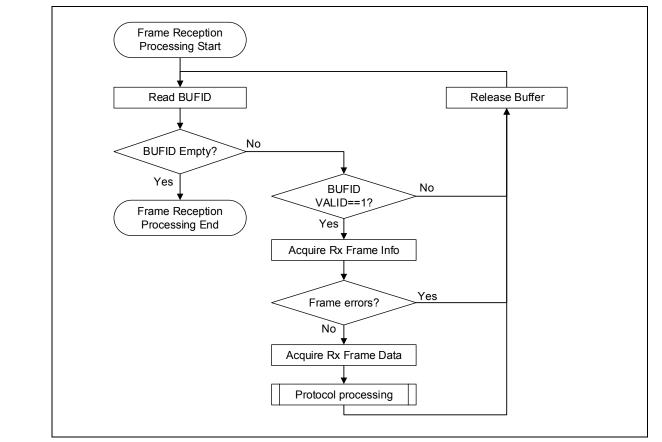

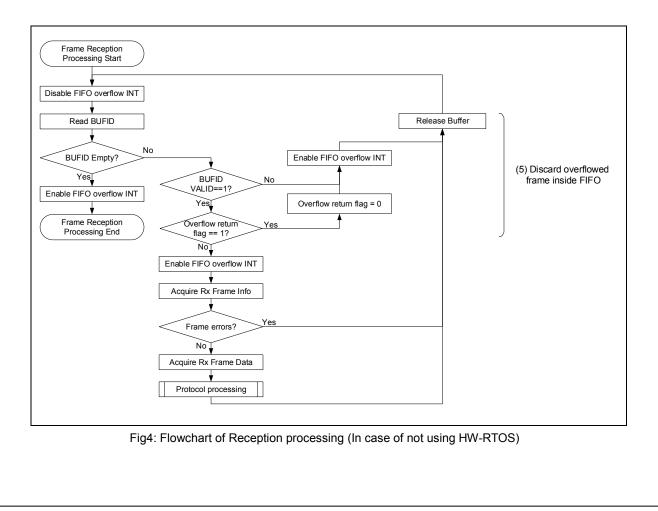

Fig1~4 are the flowcharts of workaround described above.

• In case of using HW-RTOS

Fig1: Flowchart of RX FIFO overflow processing task

Fig2: Flowchart of Reception processing task

- ✓ Create overflow processing task with higher priority than one of reception processing task

- ✓ Start overflow task by HWISR combined with FIFO overflow interrupt

- ✓ Discard the abnormal frame remained in the FIFO by HWISR combined with reception interrupt

In case of not using HW-RTOS

Fig3: Flowchart of RX FIFO overflow processing

Fig4: Flowchart of Reception processing

- ✓ The abnormal frame remained in the FIFO is discarded in reception processing. Discard valid data once when overflow return flag is set.

- Overflow interrupt is disabled from reading BUFID till checking overflow return flag

# RENESAS TECHNICAL UPDATE TN-RIN-A015A/E

Fig2: Flowchart of Reception processing task (In case of using HW-RTOS)

## Fig3: Flowchart of RX FIFO overflow processing (In case of not using HW-RTOS)

#### 2.2 Reception issue of frame more than 64 bytes with padding

2.2.1 Content

It is possible that reception word size (RX\_WORD[12:0]) in the frame information increases by 1 word (4 bytes) or decreases by 1 word compared with correct size. In case of decrease by 1 word, it is possible that RX\_WORD indicates the size which causes lack of IP packet. IP packet itself is NOT lacked.

#### 2.2.2 Condition

In case all the following conditions are met,

- (A) RX TCPIP accelerator enabled

- (B) Reception frame meets all the following conditions;

- (1) Frame size including FCS is more than 64 bytes.

- (2) TCP/IP or UDP/IP packet is included.

- (3) Padding (Trailer) is included between IP packet and FCS.

## 2.2.3 Workaround

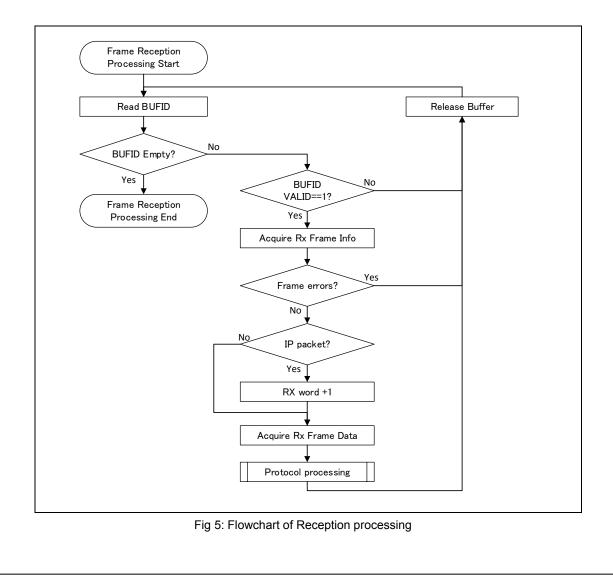

Any of the following methods should be applied.

- (A) Disable Rx TCPIP accelerator. Specifically, clear bit0 or set bit2 of GMAC\_ACC register.

- (B) In order to avoid lack of the IP packet, increase reception word size by 1 and transfer the size to protocol stack. In the protocol stack, payload data should be extracted based on size of Total Length field in IP header and the rest data should be discarded. Fig 5 is the flowchart of this workaround.

#### 3. Update Plan

Renesas will update User's Manual (Peripheral modules edition) and Ethernet MAC driver and releases the update in Feb, 2017 on Renesas Web site.

# [R-IN32M3 sample software download site]

https://www.renesas.com/products/factory-automation/multi-protocol-communication.html

➔ download

[Sample software related to this issues]

| Target               | Issue Date     |

|----------------------|----------------|

| TCP/IP, UDP/IP       | February, 2017 |

| Modbus TCP/RTU/ASCII | February, 2017 |