# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                              |                         | Document<br>No.        | TN-SH7-A895A/E                            | Rev. | 1.00 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|-------------------------------------------|------|------|

| Title                 | Addition of the description about the minimur<br>of idle cycles on the internal bus of the bus s<br>controller (BSC) | Information<br>Category | Technical Notification |                                           |      |      |

|                       |                                                                                                                      | Lot No.                 |                        |                                           |      |      |

| Applicable<br>Product | SH7231 Series                                                                                                        | All lots                | Reference<br>Document  | SH7231 Group User's<br>Hardware (R01UH007 |      |      |

We would like to inform you of the corrections in the minimum number of idle cycles on the internal bus of the bus state controller (BSC) in the above applicable products.

[Correction of Errors in the User's Manual]

10.5.10 Wait between Access Cycles

[Before correction (p.411)]

## Table 10.20 Minimum Number of Idle Cycles on Internal Bus (CPU Operation)

| CPU Operation             | Clock Ratio (lø:Bø) |     |     |     |  |  |  |

|---------------------------|---------------------|-----|-----|-----|--|--|--|

|                           | 8:1                 | 4:1 | 2:1 | 1:1 |  |  |  |

| Write $\rightarrow$ write | 1                   | 2   | 2   | 3   |  |  |  |

| Write $\rightarrow$ read  | 0                   | 0   | 0   | 1   |  |  |  |

| Read $\rightarrow$ write  | 1                   | 2   | 2   | 3   |  |  |  |

| $Read \to read$           | 0                   | 0   | 0   | 1   |  |  |  |

[After correction]

# Table 10.20 Minimum Number of Idle Cycles on Internal Bus (CPU Operation)

| CPU Operation                         | Clock Ratio (lø:Bø)  |                      |                      |                      |  |  |  |  |

|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|--|

|                                       | 8:1                  | 4:1                  | 2:1                  | 1:1                  |  |  |  |  |

| Write $\rightarrow$ write             | 0                    | 0                    | 0                    | 0                    |  |  |  |  |

| Write $\rightarrow$ read              | 0                    | 0                    | 0                    | 0                    |  |  |  |  |

| Read $\rightarrow$ write              | 1 or 0* <sup>1</sup> | 1 or 0* <sup>1</sup> | 2 or 0* <sup>1</sup> | 3 or 0* <sup>1</sup> |  |  |  |  |

| $\text{Read} \rightarrow \text{read}$ | 0                    | 0                    | 0                    | 0                    |  |  |  |  |

#### Operating conditions:

1. The bits for setting the idle cycles between access cycles in CS1BCR and CS2BCR are all set to 0.

2. In CS1WCR and CS2WCR, the WM bit is set to 1 (external WAIT pin disabled), the SW[1:0] bits are set to 00 (CS assertion is not extended), and the HW[1:0] bits are set to 00 (CS negation is not extended).

3. For both the CS1 and CS2 spaces, SRAM devices are connected, the bit width is 16 bits.

4. The unit of access by the CPU data transfer instructions is 16 bits (MOV.W).

Note: 1. This is the case where fetching of an instruction from the external bus (through the F bus) is followed by a data transfer instruction writing to the external bus (through the M bus).

[Before correction (p.411)]

#### Table 10.21 Minimum Number of Idle Cycles on Internal Bus (DMAC Operation)

| DMAC Operation                        | Transfer Mode |                |  |  |  |  |

|---------------------------------------|---------------|----------------|--|--|--|--|

|                                       | Dual Address  | Single Address |  |  |  |  |

| Write $\rightarrow$ write             | 0             | 2              |  |  |  |  |

| Write $\rightarrow$ read              | 0 or 2        | 0              |  |  |  |  |

| Read $\rightarrow$ write              | 0             | 0              |  |  |  |  |

| $\text{Read} \rightarrow \text{read}$ | 0             | 2              |  |  |  |  |

Notes: 1. The write  $\rightarrow$  write and read  $\rightarrow$  read columns in dual address transfer indicate the cycles in the divided access cycles.

2. For the write → read cycles in dual address transfer, 0 is applicable when different channels are activated successively and 2 is applicable when the same channel is activated successively. When a DMAC activation request is issued from an on-chip peripheral module and the activation is made successively in burst mode, the number of cycle is 0 even when the same channel is activated successively.

3. The write → read and read → write columns in single address transfer indicate the case when different channels are activated successively. The "write" means transfer from a device with DACK to external memory and the "read" means transfer from external memory to a device with DACK.

#### [After correction]

#### Table 10.21 Minimum Number of Idle Cycles on Internal Bus (DMAC Operation)

| DMAC Operation                                     | Transfer Mode |                                                                                                            |                                    |                                                   |                                    |  |  |  |  |  |  |  |

|----------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------|------------------------------------|--|--|--|--|--|--|--|

|                                                    |               | Dual Address                                                                                               |                                    |                                                   |                                    |  |  |  |  |  |  |  |

|                                                    | Auto Request  | Auto Request         Peripheral         External Request         External Request         External Request |                                    |                                                   |                                    |  |  |  |  |  |  |  |

|                                                    |               | Module                                                                                                     | (Level, AM = 0)                    | (Level, AM = 1)                                   | (Edge)                             |  |  |  |  |  |  |  |

| Write $\rightarrow$ write <sup>*<sup>3</sup></sup> | 2             | 2                                                                                                          | 4* <sup>1</sup> or 2* <sup>2</sup> | 9* <sup>1</sup> * <sup>4</sup> or 2* <sup>2</sup> | 4* <sup>1</sup> or 2* <sup>2</sup> |  |  |  |  |  |  |  |

| Write $\rightarrow$ read <sup>*3</sup>             | 0             | 0                                                                                                          | 2* <sup>1</sup> or 0* <sup>2</sup> | 6* <sup>1</sup> * <sup>4</sup> or 0* <sup>2</sup> | 1* <sup>1</sup> or 0* <sup>2</sup> |  |  |  |  |  |  |  |

| $\text{Read} \rightarrow \text{write}$             | 0             | 0                                                                                                          | 0                                  | 0                                                 | 0                                  |  |  |  |  |  |  |  |

| $\text{Read} \rightarrow \text{read}$              | 2             | 2                                                                                                          | 5* <sup>1</sup> or 2* <sup>2</sup> | 4* <sup>1</sup> or 2* <sup>2</sup>                | 4* <sup>1</sup> or 2* <sup>2</sup> |  |  |  |  |  |  |  |

| DMAC Operation                          | Transfer Mode                                     |                                    |  |  |  |  |

|-----------------------------------------|---------------------------------------------------|------------------------------------|--|--|--|--|

|                                         | Single Address                                    |                                    |  |  |  |  |

|                                         | External Request External Request                 |                                    |  |  |  |  |

|                                         | (Level)                                           | (Edge)                             |  |  |  |  |

| Write $\rightarrow$ write <sup>*3</sup> | 7* <sup>1</sup> * <sup>4</sup> or 0* <sup>2</sup> | 2* <sup>1</sup> or 0* <sup>2</sup> |  |  |  |  |

| Write $\rightarrow$ read <sup>*3</sup>  | 0* <sup>2</sup>                                   | 0* <sup>2</sup>                    |  |  |  |  |

| $\text{Read} \rightarrow \text{write}$  | 0* <sup>2</sup>                                   | 0* <sup>2</sup>                    |  |  |  |  |

| $\text{Read} \rightarrow \text{read}$   | 5* <sup>1</sup> or 0* <sup>2</sup>                | 2* <sup>1</sup> or 0* <sup>2</sup> |  |  |  |  |

#### Operating conditions:

1. The bits for setting the idle cycles between access cycles in CS1BCR and CS2BCR are all set to 0.

2. In CS1WCR and CS2WCR, the WM bit is set to 1 (external WAIT pin disabled), the SW[1:0] bits are set to 00 (CS assertion is not extended), and the HW[1:0] bits are set to 00 (CS negation is not extended).

3. For both the CS1 and CS2 spaces, SRAM devices are connected, the bit width is 16 bits.

4. The DMA transfer size is 16 bits. The operating mode of the DMAC is burst mode.

- 5. Numbers of cycles given for write → write sequences in dual address transfer are for data transfer between the on-chip memory and external memory, those given for read → read sequences are for data transfer between external memory and the on-chip memory, and those given for write → read and read → write sequences are for data transfer between locations in external memory.

- 6. In single address transfer, "write" means transfer from a device that has DACK to external memory and "read" means transfer from external memory to a device that has DACK.

Notes: 1. The minimum number of idle cycles in continuous DMA transfer on the same channel.

2. The minimum number of idle cycles in continuous DMA transfer between different channels.

3. When CS assertion extension (Th), access wait cycles (Tw), and CS negation extension (Tf) have been inserted for the previous access, the minimum numbers of idle cycles are reduced from the values in the table by Th+Tw+Tf due to the effect of the write buffer.

4. The effect of the write buffer does not reduce the minimum number of idle cycles.

# [Before correction (p.412)]

|                               | Next Cycle |                             |             |                           |                           |       |                                  |                            |  |  |  |

|-------------------------------|------------|-----------------------------|-------------|---------------------------|---------------------------|-------|----------------------------------|----------------------------|--|--|--|

| Previous Cycle                | SRAM       | Burst ROM<br>(Asynchronous) | MPX-<br>I/O | Byte<br>SRAM<br>(BAS = 0) | Byte<br>SRAM<br>(BAS = 1) | SDRAM | SDRAM<br>(Low-Frequency<br>Mode) | Burst ROM<br>(Synchronous) |  |  |  |

| SRAM                          | 0          | 0                           | 1           | 0                         | 1                         | 1     | 1.5                              | 0                          |  |  |  |

| Burst ROM<br>(asynchronous)   | 0          | 0                           | 1           | 0                         | 1                         | 1     | 1.5                              | 0                          |  |  |  |

| MPX-I/O                       | 1          | 1                           | 0           | 1                         | 1                         | 1     | 1.5                              | 1                          |  |  |  |

| Byte SRAM<br>(BAS = 0)        | 0          | 0                           | 1           | 0                         | 1                         | 1     | 1.5                              | 0                          |  |  |  |

| Byte SRAM<br>(BAS = 1)        | 1          | 1                           | 2           | 1                         | 0                         | 0     | 1.5                              | 1                          |  |  |  |

| SDRAM                         | 1          | 1                           | 2           | 1                         | 0                         | 0     | -                                | 1                          |  |  |  |

| SDRAM<br>(low-frequency mode) | 1.5        | 1.5                         | 2.5         | 1.5                       | 0.5                       | -     | 1                                | 1.5                        |  |  |  |

| Burst ROM<br>(synchronous)    | 0          | 0                           | 1           | 0                         | 1                         | 1     | 1.5                              | 0                          |  |  |  |

# [After correction]

Table 10.22

Number of Idle Cycles Inserted between Access Cycles to Different Memory Types

|                               |      |                             |             | ľ                         | lext Access               |       |                                  |                            |

|-------------------------------|------|-----------------------------|-------------|---------------------------|---------------------------|-------|----------------------------------|----------------------------|

| Previous Access               | SRAM | Burst ROM<br>(Asynchronous) | MPX-<br>I/O | Byte<br>SRAM<br>(BAS = 0) | Byte<br>SRAM<br>(BAS = 1) | SDRAM | SDRAM<br>(Low-Frequency<br>Mode) | Burst ROM<br>(Synchronous) |

| SRAM                          | 0    | 0                           | 1           | 0                         | 1                         | 1     | 1.5                              | 0                          |

| Burst ROM<br>(asynchronous)   | 0    | 0                           | 1           | 0                         | 1                         | 1     | 1.5                              | 0                          |

| MPX-I/O                       | 1    | 1                           | 0           | 1                         | 1                         | 1     | 1.5                              | 1                          |

| Byte SRAM<br>(BAS = 0)        | 0    | 0                           | 1           | 0                         | 1                         | 1     | 1.5                              | 0                          |

| Byte SRAM<br>(BAS = 1)        | 1    | 1                           | 2           | 1                         | 0                         | 0     | 1.5                              | 1                          |

| SDRAM                         | 1    | 1                           | 2           | 1                         | 0                         | 0     | -                                | 1                          |

| SDRAM<br>(low-frequency mode) | 1.5  | 1.5                         | 2.5         | 1.5                       | 0.5                       | -     | 1                                | 1.5                        |

| Burst ROM<br>(synchronous)    | 0    | 0                           | 1           | 0                         | 1                         | 1     | 1.5                              | 0                          |

#### [Before correction (p.413)]

Sample Estimation of Idle Cycles between Access Cycles

This example estimates the idle cycles for data transfer from the CS1 space to CS2 space by CPU access. Transfer is repeated in the following order: CS1 read ° CS1 read ° CS2 write ° CS2 write ° CS1 read ° ...

· Conditions

The bits for setting the idle cycles between access cycles in CS1BCR and CS2BCR are all set to 0.

In CS1WCR and CS2WCR, the WM bit is set to 1 (external WAIT pin disabled) and the HW[1:0] bits are set to 00 (CS negation is not extended).

If:Bf is set to 4:1, and no other processing is done during transfer.

For both the CS1 and CS2 spaces, normal SRAM devices are connected, the bus width is 32 bits, and access size is also 32 bits.

The idle cycles generated under each condition are estimated for each pair of access cycles. In the following table, R indicates a read cycle and W indicates a write cycle.

| Condition             | R ® R | R ® W | W ° W | W ® R | Note                                                                                                                                                                                                                                                                            |

|-----------------------|-------|-------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1] or [2]            | 0     | 0     | 0     | 0     | CSnBCR is set to 0.                                                                                                                                                                                                                                                             |

| [3] or [4]            | 0     | 0     | 0     | 0     | The WM bit is set to 1.                                                                                                                                                                                                                                                         |

| [5]                   | 1     | 1     | 0     | 0     | Generated after a read cycle.                                                                                                                                                                                                                                                   |

| [6]                   | 0     | 2     | 2     | 0     | See the $lf:Bf = 4:1$ column in table 10.20.                                                                                                                                                                                                                                    |

| [7]                   | 0     | 1     | 0     | 0     | No idle cycle is generated for the second time due to the write buffer effect.                                                                                                                                                                                                  |

| [5] + [6] + [7]       | 1     | 4     | 2     | 0     |                                                                                                                                                                                                                                                                                 |

| [8]                   | 0     | 0     | 0     | 0     | Value for SRAM <sup>®</sup> SRAM access                                                                                                                                                                                                                                         |

| Estimated idle cycles | 1     | 4     | 2     | 0     | Maximum value among conditions [1] or [2], [3] or [4],<br>[5] + [6] + [7], and [8]                                                                                                                                                                                              |

| Actual idle<br>cycles | 1     | 4     | 2     | 1     | The estimated value does not match the actual value in<br>the W <sup>®</sup> R cycles because the internal idle cycles due to<br>condition [6] is estimated as 0 but actually an internal idle<br>cycle is generated due to execution of a loop condition<br>check instruction. |

Figure 10.43 Comparison between Estimated Idle Cycles and Actual Value

#### [After correction]

Sample Estimation of Idle Cycles between Access Cycles

This example estimates the idle cycles for data transfer from the CS1 space to CS2 space by CPU access. Transfer is repeated in the following order: CS1 read  $^{\circ}$  CS1 read  $^{\circ}$  CS2 write  $^{\circ}$  CS2 write  $^{\circ}$  CS1 read  $^{\circ}$  ...

Conditions

The bits for setting the idle cycles between access cycles in CS1BCR and CS2BCR are all set to 0.

In CS1WCR and CS2WCR, the WM bit is set to 1 (external WAIT pin disabled) and the HW[1:0] bits are set to 00

(CS negation is not extended).

If:Bf is set to 4:1, and no other processing is done during transfer.

For both the CS1 and CS2 spaces, SRAM devices are connected, the bus width is 16 bits, and access size is

also 16 bits.

The idle cycles generated under each condition are estimated for each pair of access cycles. In the following table, R indicates a read cycle and W indicates a write cycle.

| Condition                | R ® R | R ® W | W ° W | W ® R | Note                                                                                                                                                                                                                                                                 |

|--------------------------|-------|-------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1] or [2]               | 0     | 0     | 0     | 0     | CSnBCR is set to 0.                                                                                                                                                                                                                                                  |

| [3] or [4]               | 0     | 0     | 0     | 0     | The WM bit is set to 1.                                                                                                                                                                                                                                              |

| [5]                      | 1     | 1     | 0     | 0     | Generated after a read cycle.                                                                                                                                                                                                                                        |

| [6]                      | 0     | 1     | 0     | 0     | See the $lf:Bf = 4:1$ column in table 10.20.                                                                                                                                                                                                                         |

| [7]                      | 0     | 1     | 0     | 0     | No idle cycle is generated for the second time due to the write buffer effect.                                                                                                                                                                                       |

| [5] + [6] + [7]          | 1     | 3     | 0     | 0     |                                                                                                                                                                                                                                                                      |

| [8]                      | 0     | 0     | 0     | 0     | Value for SRAM <sup>®</sup> SRAM access                                                                                                                                                                                                                              |

| Estimated idle<br>cycles | 1     | 3     | 0     | 0     | Maximum value among conditions [1] or [2], [3] or [4],<br>[5] + [6] + [7], and [8]                                                                                                                                                                                   |

| Actual idle<br>cycles    | 1     | 3     | 0     | 1     | The estimated value does not match the actual value in<br>the W * R cycles because the internal idle cycles due to<br>condition [6] is estimated as 0 but actually an internal idle<br>cycle is generated due to execution of a loop condition<br>check instruction. |

Figure 10.43 Comparison between Estimated Idle Cycles and Actual Value

## 10.5.11 Bus Arbitration

#### (4) Number of Access Cycles

Tables 10.23 Number of Access Cycles (1), (2), and (3) have been modified as shown below. For table number n, read numerals from 1 to 3.

[Before correction (p.419 to 424)]

### Table 10.23 Number of Access Cycles (n)

|       |     |    |            | Ιφ Ι       | Вф         |            |

|-------|-----|----|------------|------------|------------|------------|

|       |     |    | 1:1        | 2:1        | 4:1        | 8:1        |

| Βφ Ρφ | 1:1 | m1 | 2Iø        | 2lø to 3lø | 2lø to 5lø | 2lø to 9lø |

|       |     | m2 | 1Bø        | 1Bø        | 1Bø        | 1B¢        |

|       |     | m3 | 2Iø        | 3Iø        | 4lø        | 4Iφ        |

|       | 2:1 | m1 | 2lø        | 2lø to 3lø | 2lø to 5lø | 2lø to 9lø |

|       |     | m2 | 1B¢ to 2B¢ | 1Bø to 2Bø | 1Bø to 2Bø | 1Bø to 2Bø |

|       |     | m3 | 2Iø        | 3Iφ        | 4lø        | 4Iφ        |

|       | 4:1 | m1 | 2Iø        | 2lø to 3lø | 2lø to 5lø | 2lø to 9lø |

|       |     | m2 | 1Bø to 4Bø | 1Bø to 4Bø | 1Bø to 4Bø | 1Bø to 4Bø |

|       |     | m3 | 2lø        | 3Iφ        | 4lø        | 4Iφ        |

|       | 8:1 | m1 | 2Iø        | 2lø to 3lø | 2lø to 5lø | 2lø to 9lø |

|       |     | m2 | 1B¢ to 8B¢ | 1B¢ to 8B¢ | 1B¢ to 8B¢ | 1B¢ to 8B¢ |

|       |     | m3 | 2lø        | 3Iφ        | 4lø        | 4Iφ        |

#### [After correction]

Table 10.23

Number of Access Cycles (n)

|         |     |    |            | lφ <mark>:</mark> | Вф         |            |

|---------|-----|----|------------|-------------------|------------|------------|

|         |     |    | 1:1        | 2:1               | 4:1        | 8:1        |

| B¢ : P¢ | 1:1 | m1 | 2Iø        | 2lø to 3lø        | 2lø to 5lø | 2lø to 9lø |

|         |     | m2 | 1Bø        | 1Bø               | 1Bø        | 1Bø        |

|         |     | m3 | 2Iø        | 2lø               | 2lø to 3lø | ЗІф        |

|         | 2:1 | m1 | 2Iø        | 2lø to 3lø        | 2lø to 5lø | 2lø to 9lø |

|         |     | m2 | 1Bø to 2Bø | 1B¢ to 2B¢        | 1Bø to 2Bø | 1Bø to 2Bø |

|         |     | m3 | 2Iø        | <b>2</b> Iφ       | 2lø to 3lø | 3Iø        |

|         | 4:1 | m1 | 2Iø        | 2lø to 3lø        | 2lø to 5lø | 2lø to 9lø |

|         |     | m2 | 1Bø to 4Bø | 1Bø to 4Bø        | 1B¢ to 4B¢ | 1Bø to 4Bø |

|         |     | m3 | 2Iø        | 2lø               | 2lø to 3lø | ЗІф        |

|         | 8:1 | m1 | 2Iø        | 2lø to 3lø        | 2lø to 5lø | 2lø to 9lø |

|         |     | m2 | 1B¢ to 8B¢ | 1B¢ to 8B¢        | 1Bộ to 8Bộ | 1B¢ to 8B¢ |

|         |     | m3 | 2Iø        | 2lφ               | 2lø to 3lø | ЗIф        |

#### [Before correction (p.425)]

**Figure 10.45** shows an example of the timing of write access to the peripheral bus when  $I\phi:B\phi:P\phi = 4:4:1$ . Data are output to the CPU bus, which is connected to the CPU, in synchronization with  $I\phi$ . When  $I\phi:B\phi = 1:1$ , transfer of data from the CPU bus to the internal bus takes  $2 \times I\phi + 1 \times B\phi$ .

#### [After correction]

**Figure 10.45** shows an example of the timing of write access to the peripheral bus when  $I\phi:B\phi:P\phi = 4:4:1$ . Data are output to the CPU bus, which is connected to the CPU, in synchronization with  $I\phi$ . When  $I\phi:B\phi = 1:1$ , transfer of data from the CPU bus to the internal bus takes  $2 \times I\phi$ .

#### [Before correction (p.426)]

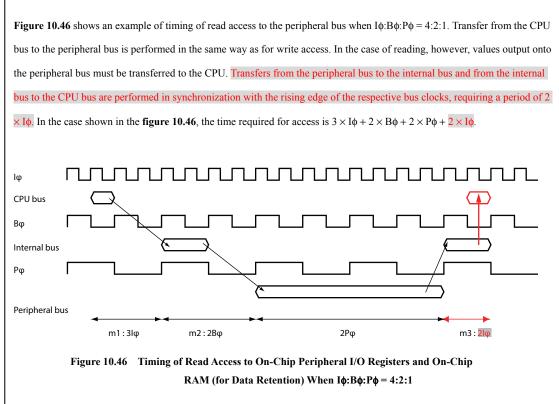

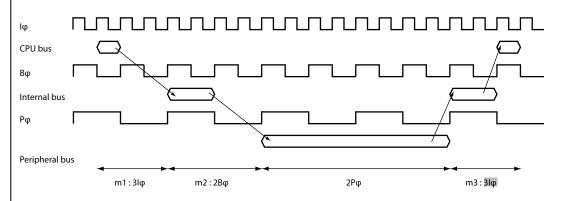

**Figure 10.46** shows an example of timing of read access to the peripheral bus when  $I\phi:B\phi:P\phi = 4:2:1$ . Transfer from the CPU bus to the peripheral bus is performed in the same way as for write access. In the case of reading, however, values output onto the peripheral bus must be transferred to the CPU. Although transfers from the peripheral bus to the internal bus and from the internal bus to the CPU bus are performed in synchronization with the rising edge of the respective bus clocks, a period of  $3 \times I\phi$  is actually required because  $I\phi \ge B\phi \ge P\phi$ . In the case shown in the **figure 10.46**, the time required for access is  $3 \times I\phi + 2 \times B\phi + 2 \times P\phi + 3 \times I\phi$ .

Figure 10.46 Timing of Read Access to On-Chip Peripheral I/O Registers and On-Chip RAM (for Data Retention) When I\\$B\$P\$=4:2:1

#### [After correction]