## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## 一 日立半導体技術情報 一

〒 100-0004 東京都千代田区大手町2丁目6番2号 (日本ビル) TEL (03)5201-5271 (ダイヤルイン)

REL (03)5201-5271 (タイヤルイン) 株式会社 日立製作所 半導体グループ

|      |                                                |        |      |                                                                                         | MOVAL PLANTIN     | 1 /111 \ |     |

|------|------------------------------------------------|--------|------|-----------------------------------------------------------------------------------------|-------------------|----------|-----|

| 製品分類 | マイコン                                           |        | 発行番号 |                                                                                         | TN-H8*-233A       | Rev.     | 第1版 |

| 題名   | H8/3672 シリーズハードウェアマニュアル<br>第2版発行時の修正、削除および追加箇所 |        |      | 情報     1. 仕様変更       (2) ドキュメント訂正追加等       (3) 使用上の注意事項       (4) マスク変更       (5) ライン変更 |                   |          |     |

| 適    |                                                | 対象ロット等 | 関連   | H8/3679                                                                                 | 2 シリーズハードウェアマニュアル | 有        | 効期限 |

| 用製品  | H8/3672 シリーズ                                   | ズ 全ロット |      |                                                                                         | 02-267A           |          | 永年  |

日立シングルチップマイクロコンピュータ H8/3672 シリーズ(H8/3672、H8/3670)ハードウェアマニュアル第 2 版におきまして、第 1 版の誤記を修正、削除、および追加した箇所がありますので、ご連絡させて頂きます。

| 項目                                | ページ | 修正箇所                                                                                                                   |

|-----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------|

| 製品に関する一般的注意事項                     |     | 追加                                                                                                                     |

| 本書の構成                             |     | 追加                                                                                                                     |

| はじめに                              |     | ご注意追加                                                                                                                  |

|                                   |     | オンチップエミュレータ(E10T)を使用して H8/3672 のプログラム開発、デバッグを行う場合の制限事項<br>(1~5)                                                        |

| 1.1 特長                            | 1-1 | パッケージ LQFP-48 ( FP-48B ) 追加                                                                                            |

| 1.2 内部プロック図                       | 1-2 | ←→ E10T_0                                                                                                              |

| 図 1.1 内部プロック図                     |     | → E10T_1<br>→ E10T_2                                                                                                   |

| 1.3 ビン配置図<br>図 1.2 ビン配置図 (FP-64E) | 1-3 | P20/SCK3  P20/SCK3  P3/FILOD  P8/FILOD  P8/FILOD  P8/FILOD  P8/FILOD  P8/FILOD  P8/FILOD  P8/FILOD  P8/FILOD  P8/FILOD |

|                                   |     | 【注】 NC には何も接続しないでください(内部は接続されていません)。                                                                                   |

| 図 1.3 ピン配置図 (FP-48F、FP-48B)       | 1-4 | (                                                                                                                      |

| 項目                                        | ページ        | 修正箇所                                                           |  |  |  |  |  |

|-------------------------------------------|------------|----------------------------------------------------------------|--|--|--|--|--|

| 1.4 端子機能                                  | 1-5        |                                                                |  |  |  |  |  |

| 表 1.1 端子機能                                |            | シリアルコミュ   TXD   46   36   出力                                   |  |  |  |  |  |

|                                           |            | ニケーションイ                                                        |  |  |  |  |  |

|                                           |            | ンタフェース   SCK3   44   34   入出力                                  |  |  |  |  |  |

|                                           | 1-6        | E10T E10T_0、 41、42、 31、32、 E10Tエミュレータ用                         |  |  |  |  |  |

|                                           |            | E10T_1、 43 33 インタフェース端子                                        |  |  |  |  |  |

|                                           |            | E10T_2 です。                                                     |  |  |  |  |  |

| 2.1 アドレス空間とメモリマップ                         | 2-2        | HD64F3672 HD64F3670                                            |  |  |  |  |  |

| 図 2.1 メモリマップ                              |            |                                                                |  |  |  |  |  |

|                                           |            | H'3FFF                                                         |  |  |  |  |  |

|                                           |            | H'4000 E10T制御プログラム H'4000 E10T制御プログラム エリア (4Kパイト) エリア (4Kパイト)  |  |  |  |  |  |

|                                           |            | H'4FFF T37 (HOVIT)                                             |  |  |  |  |  |

|                                           |            |                                                                |  |  |  |  |  |

|                                           |            | H'F780                                                         |  |  |  |  |  |

|                                           |            | (フラッシュメモリ   (フラッシュメモリ  <br>  書き換え用&E10T   書き換え用&E10T           |  |  |  |  |  |

|                                           |            | ワークエリア ワークエリア<br>1Kパイト) 1Kパイト)                                 |  |  |  |  |  |

|                                           |            | H'FB7F 内蔵RAM                                                   |  |  |  |  |  |

|                                           |            |                                                                |  |  |  |  |  |

| 4.1.1 アドレスプレークコントロールレジ                    | 4-2        | ビット ビット名 説 明                                                   |  |  |  |  |  |

| スタ ( ABRKCR )                             |            | 4 ACMP2 アドレスコンペア2~0                                            |  |  |  |  |  |

|                                           |            | 3 ACMP1 BAR と内部アドレスパスの比較条件を設定します。                              |  |  |  |  |  |

|                                           |            | 2 ACMPO 000:16 ピット比較します。                                       |  |  |  |  |  |

|                                           |            | 001:上位 12 ビット比較します。                                            |  |  |  |  |  |

|                                           |            | 010:上位 8 ビット比較します。                                             |  |  |  |  |  |

|                                           |            | 011:上位 4 ピット比較します。                                             |  |  |  |  |  |

|                                           |            | 1XX:予約(設定しないでください。)                                            |  |  |  |  |  |

| 4. アドレスプレーク                               | 4-4        | 説明修正                                                           |  |  |  |  |  |

| 4.2 動作説明                                  |            | アドレスブレーク機能は、ABRKSR の ABIF が 1 にセットされ、ABRKSR の ABIE が 1 にセットされて |  |  |  |  |  |

|                                           |            | るとき、CPU に対して割り込み要求を発生します。ここで ABRKSR の ABIF は、BAR に設定されたアド      |  |  |  |  |  |

|                                           |            | レス、BDR に設定されたデータ、および ABRKCR に設定された条件の組み合わせで、1 にセットされま          |  |  |  |  |  |

| 図 4.2 アドレスブレーク割り込み動作例 3 )<br>4.3 使用上の注意事項 | 4-5<br>4-5 | 追加                                                             |  |  |  |  |  |

| 4.3 使用上の注意事項<br>5.1 システムクロック発振器           | 5-2        | 追加                                                             |  |  |  |  |  |

| 8.1 システムグロック光振器<br>図 5.2 システムクロック発振器のブロック | J-2        |                                                                |  |  |  |  |  |

| 図 5.2 システムクロック光振器のフロック                    |            | OSC2 O                                                         |  |  |  |  |  |

| -                                         |            | * ^                                                            |  |  |  |  |  |

|                                           |            | LPM                                                            |  |  |  |  |  |

|                                           |            | OSC1 Crw                                                       |  |  |  |  |  |

|                                           |            | (注】 LPM:低消費電力モード(スタンパイモード、サブスリーブモード)                           |  |  |  |  |  |

| 5.2.1 プリスケーラ S                            | 5-3        | 説明修正                                                           |  |  |  |  |  |

|                                           |            | なお、アクティブモードおよびスリーブモードではブリスケーラ S のクロック入力は SYSCR2 の MA2          |  |  |  |  |  |

|                                           |            | MAO で設定した分周比のシステムクロックとなります。                                    |  |  |  |  |  |

| 項目                                          | ページ | 修正箇所                                                                                                                                                                                                                                                                                           |

|---------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3.1 発振子に関する注意事項                           | 5-4 | 説明修正<br>発振回路の回路定数は発振子、実装回路の浮遊容量などにより異なるため、発振子メーカと充分ご相談の<br>上決定してください。                                                                                                                                                                                                                          |

| 6.1.1 システムコントロールレジスタ 1<br>(SYSCR1)          | 6-2 | ビット     ビット名     説 明       6     STS2     スタンパイタイマセレクト 2~0       5     STS1     スタンパイモードからアクティブモード、スリーブモードに 遷移する際、システムクロック発振器が発振を開始してから クロックを供給するまでの待機ステート数を設定します。動作周波数に応じて待機時間が 6.5ms 以上となるように設定してください。設定値と待機ステート数の関係は表 6.1 のとお リです。       ・ 外部クロックを使用する場合は最小値(STS2 = STS1 = STS0 = 1)を推奨します。 |

| 6.1.4 モジュールスタンバイコントロール<br>レジスタ 2 ( MSTCR2 ) | 6-4 | 削除                                                                                                                                                                                                                                                                                             |

| 7. ROM                                      | 7-1 | 修正 EIOT E10T ・書き換え回数 1000 回まで書き換え可能です。 ・低消費電力モード 削除                                                                                                                                                                                                                                            |

| 7.2.4 フラッシュメモリイネーブルレジス<br>タ(FENR)           | 7-4 | 説明修正<br>FENR のピット 7(FLSHE)は、CPU からフラッシュメモリの制御レジスタ FLMCR1、FLMCR2、EBR1<br>をアクセスする場合のアクセス許可 / 禁止を設定します。                                                                                                                                                                                           |

| 7.3 オンボードプログラミング<br>表 7.1 プログラミングモード選択方法    | 7-5 | 修正<br>EIOT_0 E10T_0                                                                                                                                                                                                                                                                            |

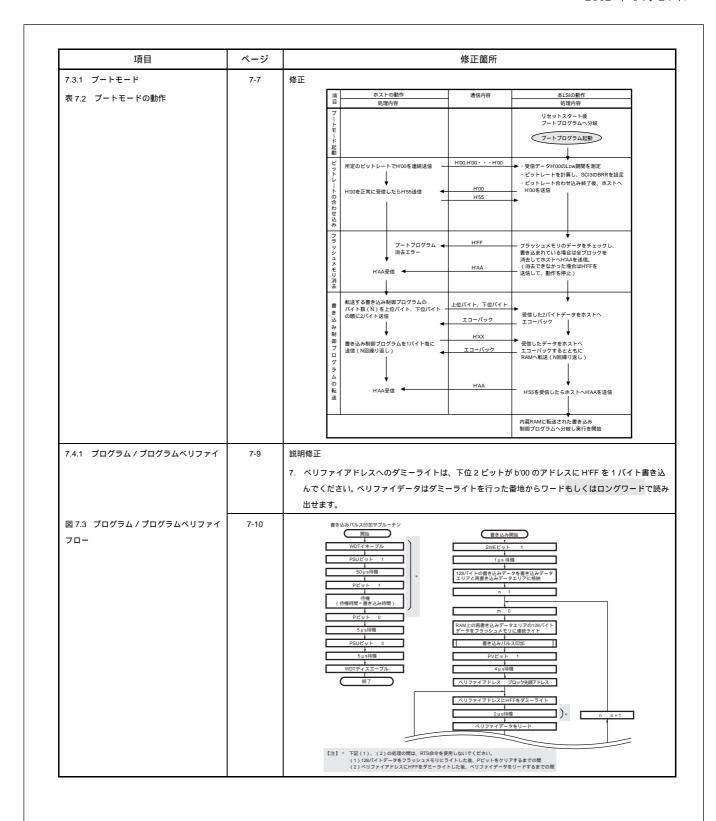

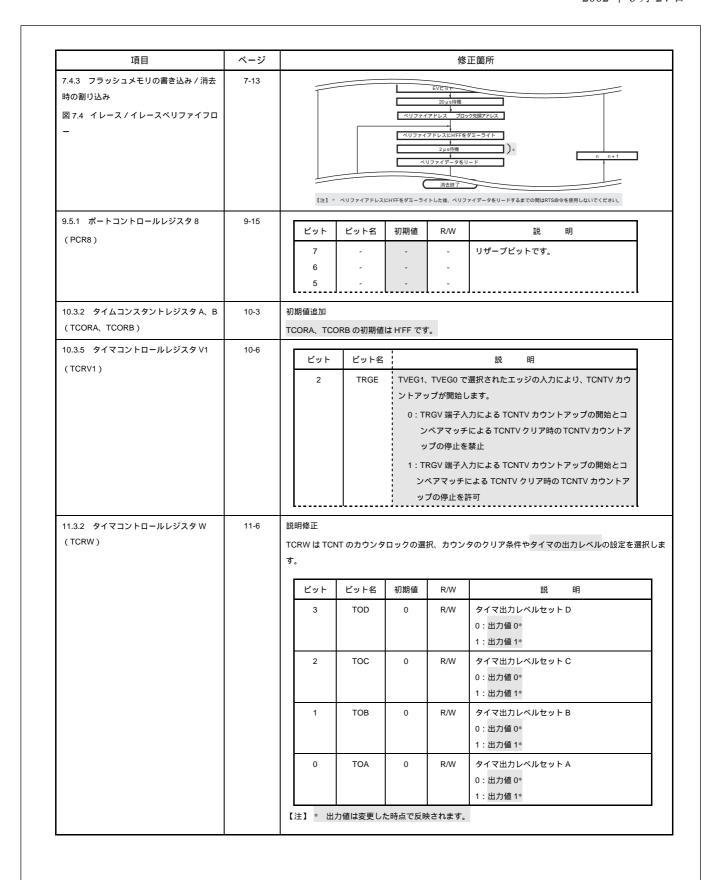

| 項目                                                                                      | ページ          | 修正箇所                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.4.1 通常動作<br>図 11.6 トグル出力の動作例( TOA = 0、TOB<br>= 1 の場合 )                               | 11-14        | TCNTの値<br>H'FFFF<br>GRA<br>GRB<br>H'0000                                                                                                                                |

| 12.1 特長                                                                                 | 12-1         | 説明修正     ・9 種類の内部クロックを選択可能     タイマのカウントクロックとして 8 種類の内部クロック( /64、 /128、 /256、 /512、 /1024、 /2048 /4096、 /8192)または内部発振器を選択可能です。内部発振器を選択した場合はすべての動作モートでウォッチドッグタイマとして動作します。 |

| 12.2.1 タイマコントロール / ステータスレ<br>ジスタ WD ( TCSRWD )                                          | 12-2         | TCSRWD は TCSRWD 自身と TCWD の書き込み制御を行うレジスタです。また、ウォッチドッグタイマの動作制御と動作状態を示す機能も持っています。本レジスタの書き換えは MOV 命令で行ってくださいビット操作命令では設定値の変更ができません。                                          |

| 13.3.4 トランスミットデータレジスタ<br>(TDR)                                                          | 13-3         | 初期値追加<br>TDR の初期値は H'FF です。                                                                                                                                             |

| 13.3.7 シリアルステータスレジスタ ( SSR )                                                            | 13-7         | ビット ビット名 初期値 R/W                                                                                                                                                        |

|                                                                                         |              | 2 TEND 1 R                                                                                                                                                              |

| 15.1 内部電源降圧回路を使用する場合                                                                    | 15-1         | 2 TEND 1 R                                                                                                                                                              |

|                                                                                         | 15-1<br>15-1 | L!                                                                                                                                                                      |

| 15.1 内部電源降圧回路を使用する場合<br>15.2 内部電源降圧回路を使用しない場合<br>17.2.6 フラッシュメモリ特性<br>表 17.7 フラッシュメモリ特性 |              | L!<br>図 15.1 のように、Vcc 端子に外部電源を接続し、VcL と Vss 間に約 0.1 μ F の容量を接続してください。                                                                                                   |