# RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                                                  |         | Document<br>No.         | TN-R8C-A036A/E                                  | Rev. | 1.00 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|-------------------------------------------------|------|------|

| Title                 | User's Manuals Regarding CAN Module                                                                                                                      |         | Information<br>Category | Technical Notification                          |      |      |

| Applicable<br>Product | R8C/34E, R8C/34F Group<br>R8C/36E, R8C/36F Group<br>R8C/38E, R8C/38F Group<br>R8C/34W, R8C/34X Group<br>R8C/36W, R8C/36X Group<br>R8C/38W, R8C/38X Group | Lot No. | Reference<br>Document   | User's Manuals: Hardware of Applicable Products |      |      |

This document describes corrections to the chapter "CAN module" in the User's Manuals: Hardware of the above groups.

The corrections are indicated in red in the list below.

Page and chapter numbers are based on the R8C/34W Group, R8C/34X Group User's Manual:Hardware.

Refer to the User's Manual of each product for the corresponding pages and chapters in other groups.

# •Page 577 of 727

The description in 26.2.19 BLIF Bit is corrected as follows:

### **Before correction**

The BLIF bit becomes 1 if 32 consecutive dominant bits are detected on the CAN bus while the CAN module is in CAN operation mode.

After the BLIF bit becomes 1, 32 consecutive dominant bits are detected again under either of the following conditions:

- After this bit is set to 0 from 1, recessive bits are detected.

- After this bit is set to 0 from 1, the CAN module enters CAN reset mode or CAN halt mode and then enters CAN operation mode again.

#### **Corrections**

The BLIF bit becomes 1 if 32 consecutive dominant bits are detected on the CAN bus while the CAN module is in CAN operation mode.

After the BLIF bit becomes 1, bus lock can be detected again after either of the following conditions is satisfied:

- After this bit is set to 0 from 1, recessive bits are detected (bus lock is resolved).

- After this bit is set to 0 from 1, the CAN module enters CAN reset mode and then enters CAN operation mode again (internal reset).

### •Page 584 of 727

Note 3 is added to Figure 26.9 as follows:

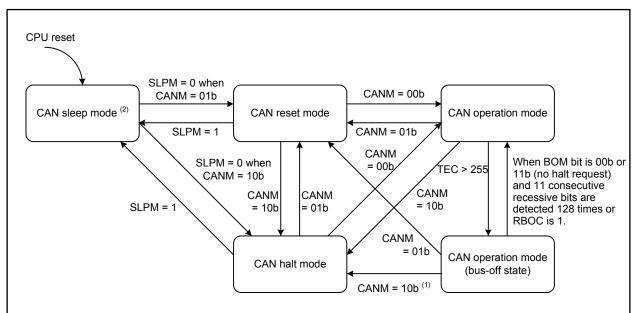

# **Before correction**

CANM, SLPM, BOM, RBOC: Bits in the COCTLR register

#### Notes:

- 1. The transition timing from the bus-off state to CAN halt mode depends on the setting of the BOM bit.

- When the BOM bit is 01b, the state transition timing is immediately after entering the bus-off state.

- When the BOM bit is 10b, the state transition timing is at the end of the bus-off state.

- When the BOM bit is 11b, the state transition timing is at the setting of the CANM bit to 10b (CAN halt mode).

- 2. Write only to the SLPM bit to exit/set CAN sleep mode.

Figure 26.9 Transition between CAN Operating Modes

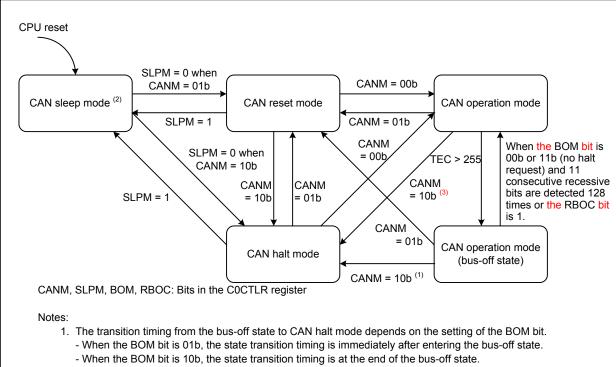

# **Corrections**

- When the BOM bit is 11b, the state transition timing is at the setting of the CANM bit to 10b (CAN halt mode).

- 2. Write only to the SLPM bit to exit/set CAN sleep mode.

- 3. The CAN module does not enter CAN Halt mode while the CAN bus is locked in dominant state. Enter CAN reset mode instead.

Figure 26.9 Transition between CAN Operating Modes

### •Page 586 of 727

Table 26.9 is corrected as follows:

Table 26.9 Operation in CAN Reset Mode and CAN Halt Mode

BOM bit: Bit in the C0CTLR register

#### Notes:

- 1. If several messages are requested to be transmitted, mode transition occurs after the completion of the first transmission. In a case that the CAN reset mode is being requested during suspend transmission, mode transition occurs when the bus is idle, the next transmission ends, or the CAN module becomes a receiver.

- 2. If the CAN bus is locked at the dominant level, the program can detect this state by monitoring the BLIF bit in the C0EIFR register.

- 3. If a CAN bus error occurs during reception after CAN halt mode is requested, the CAN mode transits to CAN halt mode.

- 4. If a CAN bus error or arbitration lost occurs during transmission after CAN reset mode or CAN halt mode is requested, the CAN mode transits to the requested CAN mode.

## **Corrections**

Table 26.9 Operation in CAN Reset Mode and CAN Halt Mode

| Mode      | Receiver                     | Transmitter                       | Bus-off                          |

|-----------|------------------------------|-----------------------------------|----------------------------------|

| CAN reset | CAN module enters CAN reset  | CAN module enters CAN reset       | CAN module enters CAN reset      |

| mode      | mode without waiting for the | mode after waiting for the end of | mode without waiting for the end |

|           | end of message reception     | message transmission (1, 4)       | of bus-off recovery              |

| CAN halt  | CAN module enters CAN        | CAN module enters CAN             | [When the BOM bit is 00b]        |

| mode      | halt mode after waiting for  | halt mode after waiting for       | A halt request from a            |

|           | the end of message           | the end of message                | program will be                  |

|           | reception. (2, 3)            | transmission. (1, 2, 4)           | acknowledged only after          |

|           |                              |                                   | bus-off recovery.                |

|           |                              |                                   | [When the BOM bit is 01b]        |

|           |                              |                                   | CAN module enters                |

|           |                              |                                   | automatically to CAN halt        |

|           |                              |                                   | mode without waiting for         |

|           |                              |                                   | the end of bus-off recovery      |

|           |                              |                                   | (regardless of a halt            |

|           |                              |                                   | request from a program).         |

|           |                              |                                   | [When the BOM bit is 10b]        |

|           |                              |                                   | CAN module enters                |

|           |                              |                                   | automatically to CAN halt        |

|           |                              |                                   | mode after waiting for the       |

|           |                              |                                   | end of bus-off recovery          |

|           |                              |                                   | (regardless of a halt            |

|           |                              |                                   | request from a program).         |

|           |                              |                                   | [When the BOM bit is 11b]        |

|           |                              |                                   | CAN module enters CAN            |

|           |                              |                                   | halt mode (without waiting       |

|           |                              |                                   | for the end of bus-off           |

|           |                              |                                   | recovery) if a halt is           |

|           |                              |                                   | requested by a program           |

|           |                              |                                   | during bus-off.                  |

BOM bit: Bit in the COCTLR register

#### Notes:

- If several messages are requested to be transmitted, mode transition occurs after the completion of the first message transmission. When CAN reset mode is being requested during suspend transmission, mode transition occurs when the bus is idle, the next transmission ends, or the CAN module becomes a receiver.

- 2. If the CAN bus is locked in dominant state, the program can detect this state by monitoring the BLIF bit in the C0EIFR register. The CAN module does not enter CAN Halt mode while the CAN bus is locked in dominant state. Enter CAN reset mode instead.

- 3. If a CAN bus error occurs during reception after CAN halt mode is requested, the CAN module enters CAN halt mode. However, the CAN module does not enter CAN Halt mode when the CAN bus is locked in dominant state.

- 4. If a CAN bus error or arbitration lost occurs during transmission after CAN reset mode or CAN halt mode is requested, the CAN module enters the requested operating mode. However, the CAN module does not enter CAN Halt mode when the CAN bus is locked in dominant state