## ZMID4200

One Wire Interface (OWI)

## **Contents**

| 1.  | 1. Introduction |                    |                                         |    |  |  |  |  |  |  |

|-----|-----------------|--------------------|-----------------------------------------|----|--|--|--|--|--|--|

| 2.  | One             | One Wire Interface |                                         |    |  |  |  |  |  |  |

|     | 2.1             | OWI O              | verview                                 | 2  |  |  |  |  |  |  |

|     | 2.2             | OWI G              | eneral Data Transfer                    | 3  |  |  |  |  |  |  |

|     | 2.3             | OWI Pr             | rotocol Details                         | 3  |  |  |  |  |  |  |

|     |                 | 2.3.1.             | Bit Transfer                            | 3  |  |  |  |  |  |  |

|     |                 | 2.3.2.             | ZMID4200 Protocol Element               | 4  |  |  |  |  |  |  |

|     |                 | 2.3.3.             | Standard Protocol Flow                  | 5  |  |  |  |  |  |  |

|     |                 | 2.3.4.             | Protocol Error Handling                 | 6  |  |  |  |  |  |  |

|     |                 | 2.3.5.             | Fail-Safe Communication                 | 7  |  |  |  |  |  |  |

|     |                 | 2.3.6.             | Command Protocol                        | 7  |  |  |  |  |  |  |

|     | 2.4             | Comma              | and Description                         | 7  |  |  |  |  |  |  |

| 3.  | OWI             | Electrica          | al Characteristics                      | 9  |  |  |  |  |  |  |

| 4.  | Glos            | sary               |                                         | 9  |  |  |  |  |  |  |

| 5.  | Revi            | sion His           | story                                   | 10 |  |  |  |  |  |  |

|     |                 |                    |                                         |    |  |  |  |  |  |  |

| Fi  | gure            | es                 |                                         |    |  |  |  |  |  |  |

| Fig | ure 1.          | OWI Ove            | erview                                  | 2  |  |  |  |  |  |  |

| Fig | ure 2.          | OWI Bit F          | Representation                          | 4  |  |  |  |  |  |  |

| Fig | ure 3.          | OWI Bit T          | Timing Parameters                       | 4  |  |  |  |  |  |  |

| Fig | ure 4.          | OWI ZMI            | ID4200 Protocol Elements                | 5  |  |  |  |  |  |  |

| Fig | ure 5.          | OWI Deta           | ailed Data Transfer                     | 5  |  |  |  |  |  |  |

| Fig | ure 6.          | OWI Re-            | synchronization from an Undefined State | 6  |  |  |  |  |  |  |

| _   |                 |                    | eout as a Protocol Element              |    |  |  |  |  |  |  |

| Fig | ure 8.          | OWI Com            | mmand Structure                         | 7  |  |  |  |  |  |  |

| Та  | ble             | S                  |                                         |    |  |  |  |  |  |  |

| Tab | ole 1. C        | OWI Gene           | eral Data Transfer                      | 3  |  |  |  |  |  |  |

| Tab | le 2. C         | OWI Com            | nmand and Data Format                   | 6  |  |  |  |  |  |  |

| Tab | le 3. C         | OWI Com            | nmand Field                             | 8  |  |  |  |  |  |  |

| Tab | le 4. C         | OWI Com            | nmand Code Definition                   | 8  |  |  |  |  |  |  |

| Tab | le 5. C         | DWI Elect          | etrical Characteristics                 | 9  |  |  |  |  |  |  |

|     |                 |                    |                                         |    |  |  |  |  |  |  |

## 1. Introduction

This document describes the One Wire Interface (OWI) implemented in the ZMID4200 product.

## 2. One Wire Interface

The OWI is used for programming purposes. It is a bidirectional, serial point-to-point interface, which provides access to all calibration, configuration, and identification EEPROM words and also to user, test, and evaluation registers. ZMID4200 functions can also be triggered via the OWI; e.g., the start/stop for position calculation or enabling certain test modes.

## 2.1 OWI Overview

The ZMID4200 OWI has the following main properties:

- Single signal wire connection

- Push-pull output driver

- Point-to-point connection; single-master, single-slave system configuration

- Bidirectional serial communication with most significant bit (MSB) first

- Pulse-width encoding of digital symbols (0, 1)

- Self-synchronizing (no clock transfer from master to slave)

- Flexible bit rate; automatic adaption to the master at the slave side

- 16-bit-word oriented data transfer

- Even parity bit for each transferred byte in both directions

- START, STOP, and handover conditions for data flow control

- Timeout to recover protocol errors

- Glitch suppression circuit on input path

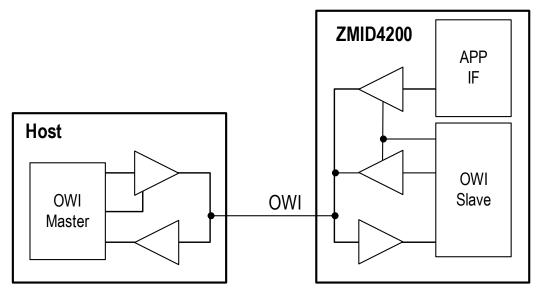

Figure 1 shows the system connection with the OWI. The host system, e.g. a laboratory computer, contains an OWI master, and the ZMID4200 has an OWI slave. Both are connected by bidirectional bus drivers to the common OWI wire. On the ZMID4200 side, the OWI input is a CMOS Schmitt trigger and the output is a CMOS buffer.

Figure 1. OWI Overview

## 2.2 OWI General Data Transfer

The general OWI protocol uses the following sequence:

- The ZMID4200 is always the slave.

- The master sends the START condition.

- The master sends a command byte (MSB first). The next parameter is determined by the operation:

- For a WRITE access, the master sends a word as the parameter (MSB first).

- · For a READ access, the slave returns a word (MSB first).

- For an action, the master continues with the next step (no parameter required).

- The master sends the STOP condition.

- The master enters the idle condition.

| START | Command | Data Word 1 | Data Word 0 | STOP | Idle |

|-------|---------|-------------|-------------|------|------|

|       |         |             |             |      |      |

**Table 1. OWI General Data Transfer**

The command determines whether the access is a READ or WRITE access or an action:

- WRITE: The master sends the write data followed by a STOP condition.

- READ: The master disables its output after a 3/4 bit period (handover). The slave waits for the falling edge on the bus and immediately drives a 0 (takeover). If the takeover bit time is finished, the slave transfers the requested word. The slave sends a 0 at the end but must disable its output after a 3/4 bit period (handover). The master waits for the falling edge on the bus and immediately drives a 0 (takeover). If the takeover bit time is finished, the master finishes the read transfer with a STOP condition.

- Action: The master immediately sends the stop condition since an action trigger does not need a parameter.

- Timeout: If no rising edge is found for a time longer than the maximum towi\_bit specification \* 2 (see Table 5), the slave goes into the idle state and waits for a rising edge as a START condition. This can be used to set the interface to a defined state.

### 2.3 OWI Protocol Details

#### 2.3.1. Bit Transfer

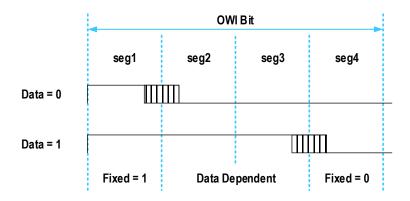

As no clock is transferred between master and slave, the protocol must be self-synchronizing. This is realized by a pulse-width modulation of the bits. Each bit time is split into four segments (seg1, seg2, seg3, seg4). During the first segment, the OWI signal is unconditionally driven high; during the last segment, it is unconditionally driven low. The two intermediate segments are set to the respective data bit; i.e., for a 0 data bit, they are both driven low and for a 1 data bit, they are both driven high. Therefore, any bit contains a rising and a falling edge. The rising edges are equally spaced and are used by the slave to determine the bit period and consequently as clock regeneration. The falling edges carry the actual data information. Figure 2 shows the encoding of a single 0 or 1 data bit (note: the timing is not to scale).

Figure 2. OWI Bit Representation

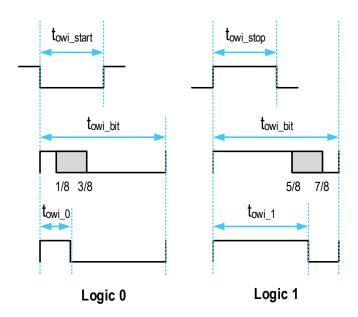

Figure 3 shows the timing parameters of the OWI protocol. The values are specified in section 3.

Figure 3. OWI Bit Timing Parameters

## 2.3.2. ZMID4200 Protocol Element

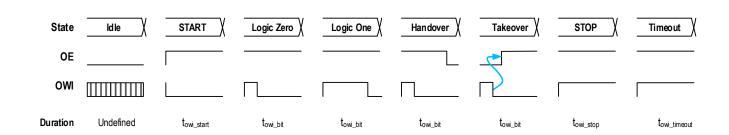

Apart from the bit representations, the OWI protocol requires several other protocol elements primarily for the correct handshaking between master and slave. These include the following:

- Idle: Master and slave are both in idle state, no transaction is ongoing

- START: Start condition sent by the master to setup a new transaction

- Handover: The driving side disables its output and releases the OWI to the other side

- Takeover: The listening side enables its output and takes over the OWI to become the driving side

- STOP: The STOP condition is sent by the master to finalize the ongoing transaction

- Timeout: No rising master edge during an ongoing transaction for the duration of towi\_timeout (see section 3).

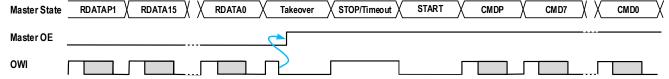

Figure 4 illustrates these ZMID4200 OWI elements with the associated output enable (OE) and OWI signals. Note that Figure 4 is not to scale. The actual timings are specified in section 3.

Figure 4. OWI ZMID4200 Protocol Elements

### 2.3.3. Standard Protocol Flow

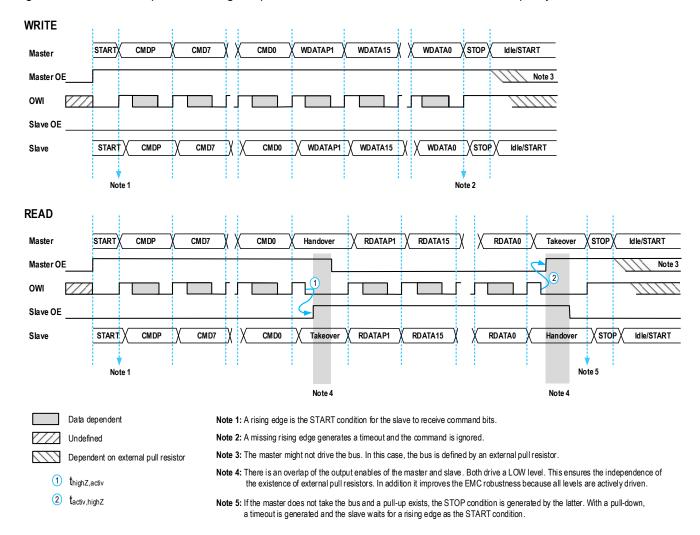

Figure 5 shows the timing for full WRITE and READ access. Each command consists of an associated parity bit followed by 8 command bits (CMDP, CMD7 to CMD0). Each data word consists of the parity bit associated with the 8 most significant bits (MSBs) followed by the 8 MSBs and then the parity bit associated with the 8 least significant bits (LSBs) followed by the 8 LSBs (DATAP1, DATA15 to DATA8, DATAP0, DATA7 to DATA0). The parity bit is always transferred first followed by the data starting with the MSB.

Figure 5 illustrates this protocol using the prefix R or W to indicate the direction of the parity and data bits.

Figure 5. OWI Detailed Data Transfer

Table 2. shows the bit positions within the serial data stream. Each byte begins with its own parity bit.

#### **Table 2. OWI Command and Data Format**

| Р  | CMD7 | <br>CDM0 |             | Р  | DATA | 15 | DATA8 | Р | DATA | ۸7 | DATA0 |

|----|------|----------|-------------|----|------|----|-------|---|------|----|-------|

| 26 | 25   | <br>18   | <del></del> | 17 | 16   |    | 9     | 8 | 7    |    | 0     |

## 2.3.4. Protocol Error Handling

Typically, access is terminated when the master sends a STOP condition, which sets the slave to the idle state. In a disturbed environment, it is possible that the data bits and/or other protocol elements are not detected correctly. This could lead to a loss of synchronism between the master and the slave, in which case the slave will not able to follow the master transactions.

This type of out-of-sync condition can be resolved by a timeout initiated by the master. The timeout resets the slave to the idle state regardless of preceding events. Therefore the next transaction starts from a clean state.

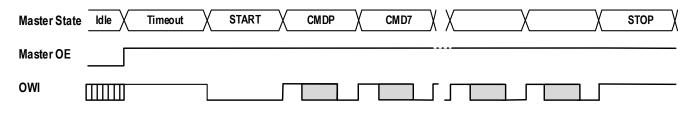

### Resynchronization from an Undefined State (Timeout HIGH):

## Resynchronization from an Undefined State (Timeout LOW):

Figure 6. OWI Re-synchronization from an Undefined State

When the synchronism is lost, only the timeout can reset the communication to a stable state. The STOP condition alone is not sufficient, as it functions only within a proper, complete transaction.

In addition, each command and data word is protected with its own parity bit. In the event of a parity error, the ZMID4200 ignores the command.

#### 2.3.5. Fail-Safe Communication

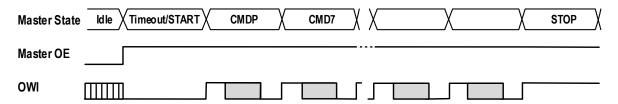

#### WRITE - STOP/Timeout - WRITE

Figure 7. The Timeout as a Protocol Element

The timeout protocol element can be added to the protocol flow by default. When used in a distributed environment, this approach provides an additional level of security, as each access is completely independent of the previous state of the involved interfaces.

The trade-off in using the timeout as a default protocol element is reduced bandwidth. In an undisturbed environment when there is only a low probability that the master and slave controllers are not synchronized, then not using the timeout protocol is a good option because it will increase the throughput.

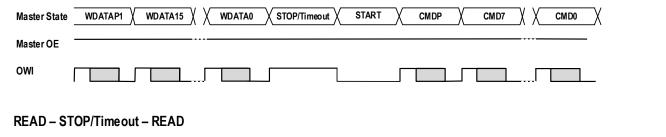

#### 2.3.6. Command Protocol

Full access consists of the transfer of a command byte to the ZMID4200 plus a WRITE data word (16 bits) to the ZMID4200 or a READ data word (16 bits) from the ZMID4200. After completion of a full access, the ZMID4200 is ready for the next command.

In the case of a WRITE access to the EEPROM, the ZMID4200 internal charge pump must be activated and the addressed memory field must be erased before the WRITE. This procedure is controlled by the ZMID4200 logic, which extends the WRITE access.

Therefore after sending the command *ee\_write* <00<sub>HEX</sub> to 1F<sub>HEX</sub>> to the ZMID4200, the host system must pause a specific execution time t<sub>cmd\_exe</sub> to allow the ZMID4200 to process the command. The execution time t<sub>cmd\_exe</sub> is specified for each command individually.

In the case of a WRITE command, the next command can be sent if the execution time has passed.

The READ command is served immediately after the takeover phase.

## 2.4 Command Description

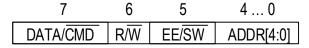

The length of the OWI command is 1 byte. The first 3 bits (MSBs) represent the instruction type, and the remaining 5 LSBs represent the address to be accessed.

Figure 8. OWI Command Structure

Page 7

**Table 3. OWI Command Field**

| Bit Number | Name                   | Description                                                      |

|------------|------------------------|------------------------------------------------------------------|

| 7          | DATA/not Command       | 0: The instruction is one of the following commands:             |

|            | (DATA/CMD in Figure 8) | ee_download, start_dpu, stop_dpu, set_security_access, ee_write  |

|            |                        | 1: The instruction is of the type "data access"                  |

|            |                        | EEPROM or shadow register R/W access                             |

| 6          | Read /not Write        | 1: Memory READ access                                            |

|            | $(R/\overline{W})$     | 0: Memory WRITE access                                           |

| 5          | BLSEL (EE/SW)          | This block-select bit determines the memory type to be accessed: |

|            |                        | 0: Shadow registers access                                       |

|            |                        | 1: EEPROM memory access                                          |

| [4:0]      | Address                | Address field in the case of a DATA instruction.                 |

|            | (ADDR[4:0])            |                                                                  |

Table 4 lists the available commands. It shows the following items:

- Command Code: the 8-bit code for the command in hex format.

- Access: The type of command; i.e., WRITE, READ or action.

- t<sub>cmd\_exec</sub>: The execution time required to complete the command, which starts after the STOP element.

- Note: The ZMID4200 oscillator must first be calibrated for the t<sub>cmd\_exec</sub> specification to be valid.

- Register: If applicable, the register related to the command.

- Description: The name and description of the command or the description of the register/field

**Table 4. OWI Command Code Definition**

| Command Code                           | Access | t <sub>cmd_exec</sub> | Register             | Description                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------|--------|-----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01 <sub>HEX</sub>                      | Action | 120µs                 | -                    | Command: EE_DOWNLOAD Copy EEPROM to shadow registers <sup>1</sup>                                                                                                                                                                                                                                                                |

| 02 <sub>HEX</sub>                      | Action | -                     | -                    | Command: OWI_SIGNATURE Signature = 83AE <sub>HEX</sub> = Manufacturer Mode. Enable the WRITE and READ access to the complete address range of EEPROM and shadow register cells. Signature = xxxx <sub>HEX</sub> = Command Mode. Enable the WRITE and READ access to a limited address range of EEPROM and shadow register cells. |

| 03 <sub>HEX</sub>                      | Action | _                     | -                    | Command: DPU_RUN Starts the digital processing unit (DPU).                                                                                                                                                                                                                                                                       |

| 04 <sub>HEX</sub>                      | Action | _                     | -                    | Command: DPU_HOLD Stop/freeze DPU.                                                                                                                                                                                                                                                                                               |

| 05 <sub>HEX</sub> to 7F <sub>HEX</sub> | _      | _                     | -                    | Unused                                                                                                                                                                                                                                                                                                                           |

| 80 <sub>HEX</sub> to 9F <sub>HEX</sub> | WRITE  | -                     | shadow_word_ <n></n> | Command: SW_WRITE <01F> WRITE data to shadow word <n></n>                                                                                                                                                                                                                                                                        |

| C0 <sub>HEX</sub> to DF <sub>HEX</sub> | READ   | _                     | shadow_word_ <n></n> | Command: SW_READ <01F> READ data from shadow word <n></n>                                                                                                                                                                                                                                                                        |

| A0 <sub>HEX</sub> to BF <sub>HEX</sub> | WRITE  | 10.5ms                | eeprom_word_ <n></n> | Command: EE_WRITE <01F> WRITE data to EEPROM word <n></n>                                                                                                                                                                                                                                                                        |

| E0 <sub>HEX</sub> to FF <sub>HEX</sub> | READ   | _                     | eeprom_word_ <n></n> | Command: EE_READ <01F> READ data from EEPROM word <n></n>                                                                                                                                                                                                                                                                        |

<sup>1.</sup> Parameter out\_pro = 00<sub>BIN</sub> (Output register 0A<sub>HEX</sub>); otherwise the access mode will be terminated!

## 3. OWI Electrical Characteristics

## **Table 5. OWI Electrical Characteristics**

Note: No external pull-up resistor nor external pull-down resistor should be used.

| OWI (CMOS)                                                                      |                           |                                                                                         |       |      |       |                      |

|---------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------|-------|------|-------|----------------------|

| Parameter                                                                       | Symbol                    | Condition                                                                               | Min   | Тур  | Max   | Unit                 |

| Input voltage LOW                                                               | $V_{owi\_in\_low}$        |                                                                                         |       |      | 1.5   | V                    |

| Input voltage HIGH                                                              | $V_{owi\_in\_high}$       |                                                                                         | 3.5   |      |       | V                    |

| Output voltage LOW                                                              | $V_{owi\_out\_low}$       |                                                                                         | 0     |      | 1.0   | V                    |

| Output voltage HIGH                                                             | $V_{owi\_out\_high}$      |                                                                                         | 4.0   |      | 5.0   | V                    |

| Output capacitive load                                                          | C <sub>owi_out</sub>      |                                                                                         |       |      | 100   | nF                   |

| Duration of START condition <sup>1</sup>                                        | t <sub>owi_start</sub>    |                                                                                         | 5     |      |       | μs                   |

| Duration of STOP condition <sup>1</sup>                                         | t <sub>owi_stop</sub>     |                                                                                         | 5     |      |       | μs                   |

| Bit period <sup>1</sup>                                                         | t <sub>owi_bit</sub>      |                                                                                         | 10    |      | 100   | μs                   |

| Bit period deviation                                                            | $\Delta t_{owi\_bit}$     |                                                                                         | 0.8   | 1    | 1.2   | t <sub>owi_bit</sub> |

| High time for a logic 01                                                        | t <sub>owi_0</sub>        |                                                                                         | 0.175 | 0.25 | 0.375 | t <sub>owi_bit</sub> |

| High time for a logic 1 <sup>1</sup>                                            | t <sub>owi_1</sub>        |                                                                                         | 0.625 | 0.75 | 0.825 | t <sub>owi_bit</sub> |

| Duration of timeout condition <sup>2</sup>                                      | t <sub>owi_timeout</sub>  |                                                                                         | 150   |      |       | μs                   |

| Duration of slave takeover <sup>3</sup>                                         | thighZ,active             | Falling edge on the SOUT pin to slave output enable Calibrated oscillator required      | 2.0   |      | 5.0   | μs                   |

| Duration of master takeover <sup>3</sup>                                        | t <sub>active,highZ</sub> | Falling edge on S <sub>OUT</sub> to master output enable Calibrated oscillator required | 0.0   |      | 2.0   | μs                   |

| EEPROM programming time for a single WRITE access                               | t <sub>PROG</sub>         |                                                                                         | 10.5  |      |       | ms                   |

| Time to enter into Manufacturer<br>Mode or Command Mode after<br>power-on reset | tauthorization            |                                                                                         | 0.0   |      | 4.5   | ms                   |

- 1. See section 2.3.1 and Figure 3 for further information.

- 2. See section 2.3.2, section 2.3.4, and Figure 6 for further information.

- 3. See section 2.3.2, section 2.3.3, and Figure 5 for further information.

## 4. Glossary

| Term | Definition                                          |

|------|-----------------------------------------------------|

| ATE  | Automatic Test Equipment                            |

| ATPG | Automatic Test Pattern Generation                   |

| DPU  | Digital Processing Unit                             |

| PPU  | Position Processing Unit                            |

| E2P  | Electrically Erasable Programmable Read Only Memory |

| ECU  | Electronic Control Unit                             |

| ECC  | Error Correction Code                               |

| FEC  | Forward Error Correction                            |

| LSB  | Least Significant Bit                               |

| MSB  | Most Significant Bit                                |

| OWI  | One Wire Interface                                  |

# 5. Revision History

| Revision | Date         | Description                                                                                                          |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------|

| 1.1      | Apr 24, 2024 | <ul> <li>Description for 02<sub>HEX</sub> updated</li> <li>Electrical characteristics conditions updated.</li> </ul> |

| 1.0      | Jul 21, 2021 | Initial release.                                                                                                     |

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Disclaimer Rev.5.0-1)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

## **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>