## HS-201HSEH

Low Dose Rate Total Dose Results of the HS9-201HSEH Quad SPST Analog Switch

#### Introduction

This document reports the results of a low dose rate (LDR) total dose test of the HS-201HSEH quad SPST analog switch. The tests were conducted to provide an assessment of the LDR hardness of the part. Parts were irradiated to a maximum level of 100krad(Si) under bias and with all pins grounded.

The HS-201HSEH is acceptance tested on a wafer-by-wafer basis to 300krad(Si) at high dose rate (HDR) (50-300rad(Si)/s) and to 50krad(Si) at LDR (0.01rad(Si)/s), insuring product hardness to the specified level for both dose rates.

The part was well within the SMD post-radiation specification limits at both downpoints for all monitored parameters. No significant differences in total dose response were noted between biased and grounded irradiation for any parameters or between the four channels.

#### **Product Description**

The HS-201HSEH is a monolithic CMOS analog switch featuring power-off high input impedance, very fast switching speeds and low ON-resistance. Fabrication on the Renesas DI RSG process assures SEL immunity and good LDR performance. These Class V devices are acceptance tested to 300krad(Si) at HDR and to 50krad(Si) at LDR. Power-off high input impedance enables the use of this device in redundant circuits without causing data bus signal degradation. ESD protection, overvoltage protection, fast switching times, low ON-resistance and guaranteed radiation hardness make the HS-201HSRH ideal for any space application where improved switching performance is required.

Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA).

- QML qualified per MIL-PRF-38535

- Radiation performance:

- HDR (50-300rad(Si)/s): 300krad(Si)

- LDR (0.01rad(SI)/s): 50krad(Si)

- SEL immune: DI RSG process

- Overvoltage protection (power on, switch off): ±30V

- Power off high impedance: ±17V

- Fast switching times

- t<sub>ON</sub>: 110ns (maximum)

- t<sub>OFF</sub>: 80ns (maximum)

- Low ON-resistance: 50Ω (maximum)

- · Pin compatible with industry standard 201 switches

- Operating supply range: ±10V to ±15V

- Wide analog voltage range (±15V supplies): ±15V

# Contents

| 1. | Test Description          |                                           |    |  |  |

|----|---------------------------|-------------------------------------------|----|--|--|

|    | 1.1                       | Irradiation Facilities                    |    |  |  |

|    | 1.2                       | Test Fixturing                            | 3  |  |  |

|    | 1.3                       | Characterization Equipment and Procedures | 3  |  |  |

|    | 1.4                       | Experimental Matrix                       | 3  |  |  |

|    | 1.5                       | Downpoints                                | 3  |  |  |

| 2. | Results                   |                                           |    |  |  |

|    | 2.1                       | Test results                              | 3  |  |  |

|    | 2.2                       | Variables Data                            | 4  |  |  |

| 3. | Discussion and Conclusion |                                           |    |  |  |

| 4. | Revision History          |                                           |    |  |  |

| Α. | Арре                      | əndix                                     | 13 |  |  |

## 1. Test Description

### 1.1 Irradiation Facilities

LDR irradiation at 0.01rad(Si)/s was performed using the Renesas Palm Bay N40 panoramic gamma ray irradiator.

## 1.2 Test Fixturing

Biased irradiation was performed in accordance with the production irradiation diagram. Grounded irradiation was performed with all pins hardwired to ground.

### **1.3 Characterization Equipment and Procedures**

All electrical testing was performed outside the irradiator using the production automated test equipment (ATE) with data logging at each downpoint. Downpoint electrical testing was performed at room temperature. Three control units were used to improve repeatability.

### **1.4 Experimental Matrix**

The experimental matrix consisted of 30 samples irradiated at LDR under bias and 30 samples irradiated at LDR with all pins grounded. Samples of the HS-201HSEH were drawn from preproduction lot E0P8WEH and were packaged in the hermetic 16-pin solder-sealed ceramic flatpack (K16.C) package. Samples were processed through the standard burn-in cycle before irradiation, as required by MIL-STD-883, and were screened to the ATE limits at room temperature prior to the test.

### 1.5 Downpoints

Downpoints were 0, 50, and 100krad(Si).

## 2. Results

### 2.1 Test results

LDR testing of the HS-201HSEH is complete through 100krad(Si). Table 1 shows the attributes data for the test.

| Dose Rate     | Bias     | Sample Size | Downpoint   | Bin 1 <sup>[1]</sup> | Rejects |

|---------------|----------|-------------|-------------|----------------------|---------|

|               |          |             | 0           | 30                   | 0       |

| 0.01rad(Si)/s | Biased   | 30          | 50krad(Si)  | 30                   | 0       |

|               |          |             | 100krad(Si) | 30                   | 0       |

|               |          |             | 0           | 30                   | 0       |

| 0.01rad(Si)/s | Grounded | 30          | 50krad(Si)  | 30                   | 0       |

|               |          |             | 100krad(Si) | 30                   | 0       |

Table 1. Total Dose Test Attributes Data

1. Bin 1 indicates a device that passes all pre-irradiation specification limits.

#### 2.2 Variables Data

The plots in Figure 1 to Figure 15 show data at all downpoints for key parameters. The plots show the response to total dose irradiation at LDR for the biased and unbiased (all pins grounded) cases. We chose to plot the average for these parameters due to the relatively large sample sizes. Discussion and Conclusion provides individual discussion of the figures. No differences in total dose response were noted between biased and grounded irradiation for any parameters. Additionally, no channel to channel differences were noted, either in the pre-irradiation data or in the total dose response of the parts.

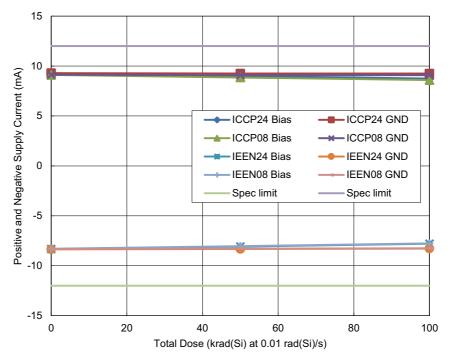

Figure 1. HS-201HSEH positive and negative power supply current, sum of all four channels, at ±8.0V and ±24V supplies as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limits are +12.0mA maximum (positive supply) and -12.0mA maximum (negative supply).

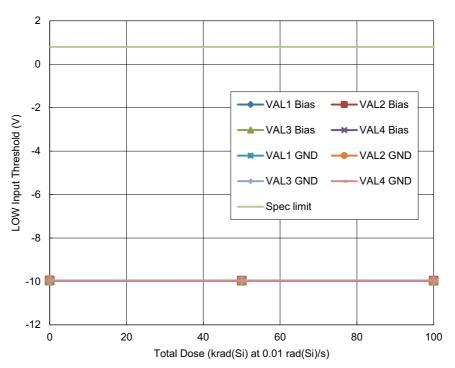

Figure 2. HS-201HSEH LOW input threshold voltage, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limit is 0.8V maximum.

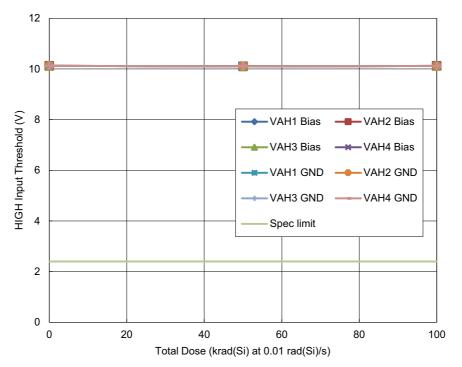

Figure 3. HS-201HSEH HIGH input threshold voltage, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limit is 2.4V minimum.

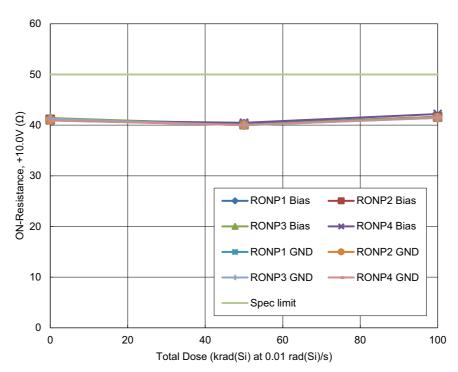

Figure 4. HS-201HSEH ON resistance at +10.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limit is  $50\Omega$  maximum.

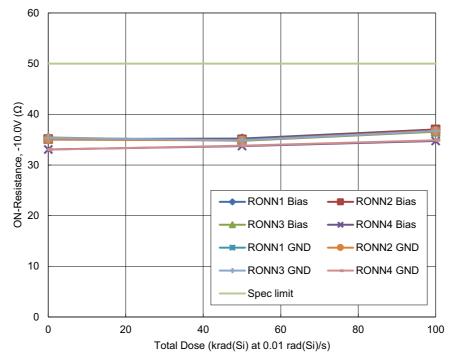

Figure 5. HS-201HSEH ON resistance at -10.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limit is  $50\Omega$  maximum.

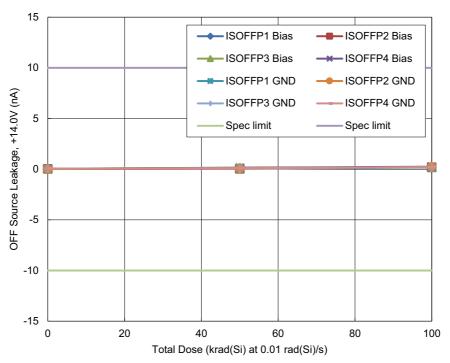

Figure 6. HS-201HSEH OFF source leakage at +14.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limits are -10.0nA to +10.0nA.

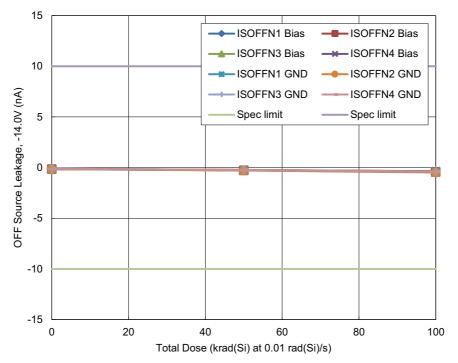

Figure 7. HS-201HSEH OFF source leakage at -14.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limits are -10.0nA to +10.0nA.

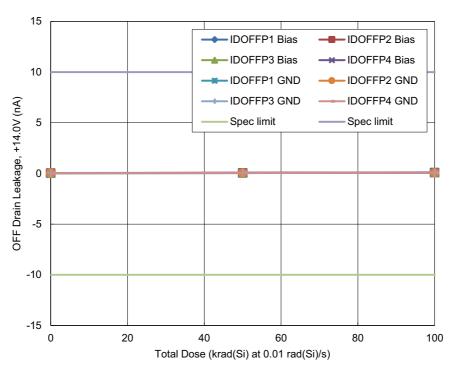

Figure 8. HS-201HSEH OFF drain leakage at +14.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limits are -10.0nA to +10.0nA.

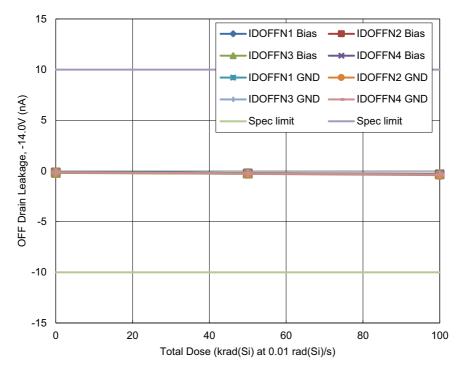

Figure 9. HS-201HSEH OFF drain leakage at -14.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limits are -10.0nA to +10.0nA.

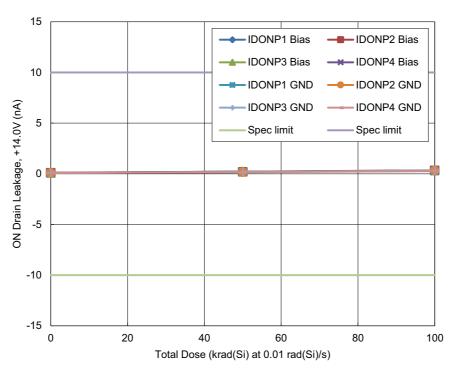

Figure 10. HS-201HSEH ON drain leakage at +14.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limits are -10.0nA to +10.0nA.

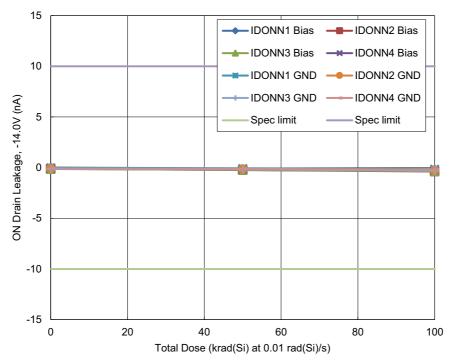

Figure 11. HS-201HSEH ON drain leakage at -14.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limits are -10.0nA to +10.0nA.

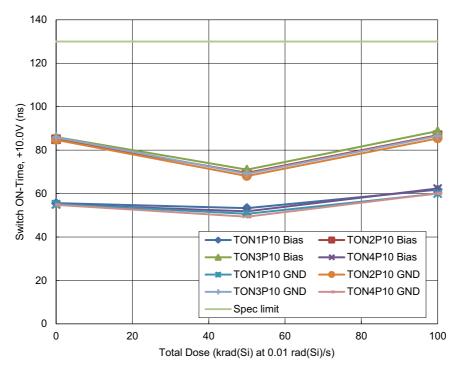

Figure 12. HS-201HSEH switch turn-on time at +10.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limit is 130ns maximum.

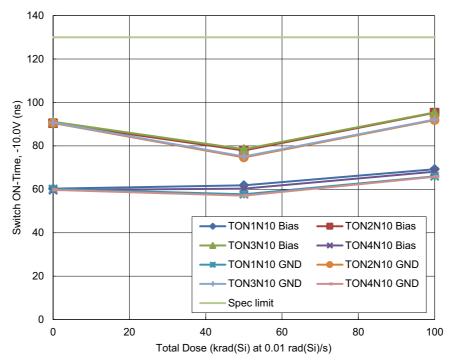

Figure 13. HS-201HSEH switch turn-on time at -10.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limit is 130ns maximum.

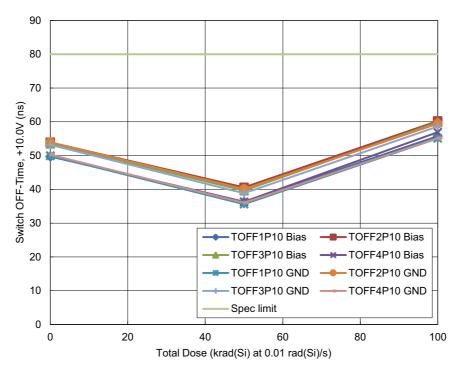

Figure 14. HS-201HSEH switch turn-off time at +10.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limit is 80ns maximum.

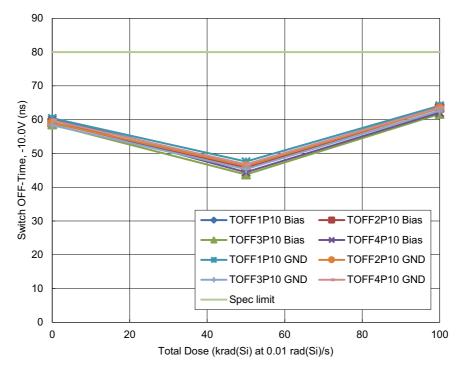

Figure 15. HS-201HSEH switch turn-off time at -10.0V, each channel, as a function of LDR total dose irradiation for the biased and unbiased (all pins grounded) cases. The dose rate was 0.01rad(Si)/s. The sample sizes for the two LDR cells were 30 for each cell. The specification limit is 80ns maximum.

## 3. Discussion and Conclusion

This document reports the results of LDR testing of the HS-201HSEH quad SPST analog switch. Parts were irradiated at 0.01rad(Si)/s under bias and with all pins grounded per MIL-STD-883 Test Method 1019. The test was run to a maximum level of 100krad(Si). All parameters remained within the SMD and data sheet pre-irradiation limits at all downpoints. We have summarized the results in a table of attributes data (Test results) followed by a limited number of curves of interest (Variables Data). We will discuss each of the figures separately.

Figure 1, power supply current: This plot shows both the positive and negative power supply current and plots the aggregate supply current for all four switch channels, which is hard to avoid since all four channels have common VCC and VEE pins. Both parameters showed excellent stability, with the average supply current per amplifier about 9.5mA.

Figure 2 and Figure 3, LOW and HIGH input threshold voltage: These parameters were very stable over irradiation and anneal, with no discernible bias sensitivity.

Figure 4 and Figure 5, ON-resistance at +10.0V and -10.0V: These parameters were stable over irradiation and anneal, with no discernible bias sensitivity.

Figure 6 and Figure 7, OFF source leakage at +14.0V and -14.0V: These parameters were stable over irradiation and anneal, with no discernible bias sensitivity.

Figure 8 and Figure 9, OFF drain leakage at +14.0V and -14.0V: These parameters were stable over irradiation and anneal, with no discernible bias sensitivity.

Figure 10 and Figure 11, ON drain leakage at +14.0V and -14.0V: These parameters were stable over irradiation and anneal, with no discernible bias sensitivity.

Figure 12 and Figure 13, switch turn-on time at +10.0V and -10.0V: These parameters were stable over irradiation and anneal, with no discernible bias sensitivity.

Figure 14 and Figure 15, switch turn-off time at +10.0V and -10.0V: These parameters were stable over irradiation and anneal, with no discernible bias sensitivity.

The part is acceptance tested on a wafer-by-wafer basis to 300krad(Si) at HDR (50-300rad(Si)/s) and to 50krad(Si) at LDR (0.01rad(Si)/s), ensuring hardness to the specified level for both dose rates. No significant differences in LDR response were noted between biased and grounded irradiation for any parameters. Additionally, no channel to channel differences were noted, either in the pre-irradiation data or in the total dose response of the parts.

## 4. Revision History

|   | Revision | Date        | Description      |

|---|----------|-------------|------------------|

| ſ | 1.00     | May 8, 2024 | Initial release. |

## A. Appendix

| Figure | Parameter                      | Low Limit | High<br>Limit | Units | Notes                 |

|--------|--------------------------------|-----------|---------------|-------|-----------------------|

| 1      | Power Supply Current           | -         | 12.0          | mA    | Sum of all 4 channels |

| 2      | LOW Input Threshold Voltage    | -         | +0.8          | V     | Channels 1 through 4  |

| 3      | HIGH Input Threshold Voltage   | 2.4       | -             | V     | Channels 1 through 4  |

| 4      | ON-Resistance, +10V            | -         | 50.0          | Ω     | Channels 1 through 4  |

| 5      | ON-Resistance, -10V            | -         | 50.0          | Ω     | Channels 1 through 4  |

| 6      | Source OFF Leakage, +14.0V     | -10.0     | +10.0         | nA    | Channels 1 through 4  |

| 7      | Source OFF Leakage, -14.0V     | -10.0     | +10.0         | nA    | Channels 1 through 4  |

| 8      | Drain OFF Leakage, +14.0V      | -10.0     | +10.0         | nA    | Channels 1 through 4  |

| 9      | Drain OFF Leakage, -14.0V      | -10.0     | +10.0         | nA    | Channels 1 through 4  |

| 10     | Drain ON Leakage, +14.0V       | -10.0     | +10.0         | nA    | Channels 1 through 4  |

| 11     | Drain ON Leakage, +14.0V       | -10.0     | +10.0         | nA    | Channels 1 through 4  |

| 12     | Switch Turn-On Time at +10.0V  | 130.0     | -             | ns    | Channels 1 through 4  |

| 13     | Switch Turn-On Time at -10.0V  | 130.0     | -             | ns    | Channels 1 through 4  |

| 14     | Switch Turn-Off Time at +10.0V | 80.0      | -             | ns    | Channels 1 through 4  |

| 15     | Switch Turn-Off Time at -10.0V | 80.0      | -             | ns    | Channels 1 through 4  |

#### Table 2. Reported Parameters and Post-Irradiation Limits

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.