# **Supercapacitor Charging Reference Design**

### 1.0 Description

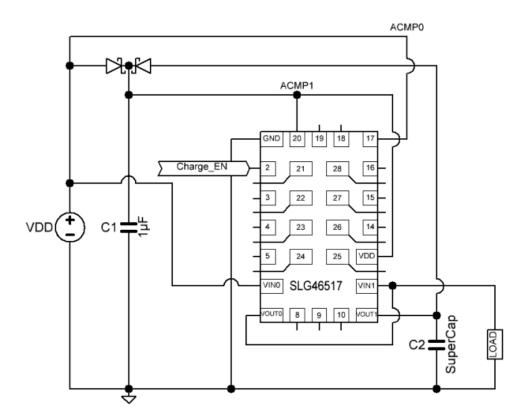

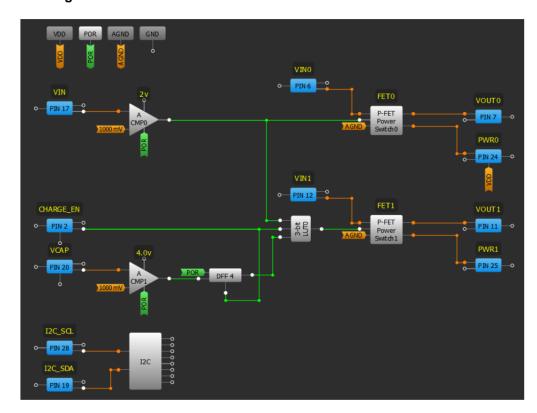

We propose to charge and discharge a single supercapacitor with a Silego GreenPAK SLG46517 device. This GreenPAK is a configurable mixed-signal matrix chip that includes several GPIOs, Look Up Tables, ACMPs, and counters, as well as a pair of integrated power switches. The design will charge the supercapacitor up to a voltage determined by an Analog Comparator inside the GreenPAK, and then discharge the supercapacitor when VIN drops below a set voltage. If desired, the GreenPAK can also receive a Charge\_EN signal which would allow a host controller to determine when it wants to begin charging the supercapacitor.

### 2.0 Modes of Operation

Bypass mode: As soon as VDD is connected to the circuit, FET0 will be turned on so that the load will be powered off of VDD. FET1 will be turned off so that the supercapacitor does not begin charging prematurely. Charging mode: If Charge\_EN goes HIGH, FET0 will stay on and FET1 will be turned on until until Charge\_EN goes LOW or VC1 = VACMP1\_THRESHOLD, at which point the GreenPAK will disable FET1 to avoid overcharging the supercapacitor. Discharging mode: When VDD drops below VACMP0\_THRESHOLD, switch FET0 will be turned off and switch FET1 will be turned on, so that the circuit is powered off of the supercapacitor.

#### 3.0 Schematic

# 4.0 GreenPAK Design

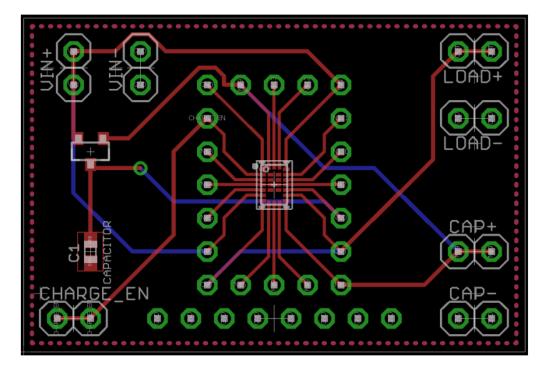

# 5.0 PCB Schematic

# 6.0 PCB Schematic

# BOM per module:

- Supercapacitor (x1)

- GreenPAK SLG46517 (x1)

- 0.1µF Hold up capacitor (x1)

- BAT54C Schottky Diode (x1)

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.