# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

# μPD789489サプシリーズ

8ビット・シングルチップ・マイクロコンピュータ

μPD789488 μPD789489 μPD78F9488 μPD78F9489

資料番号 U15331JJ4V1UD00 (第4版) 発行年月 June 2005 NS CP(K) [メ モ]

# 目次要約

第1章 概 説 ... 25 **第2章 端子機能** ... 36 第3章 CPUアーキテクチャ ... 47 第4章 ポート機能 ... 74 第5章 クロック発生回路 ... 94 **第6章 16ピット・タイマ**20 ... 107 第7章 8**ビット・タイマ**50, 60, 61 ... 119 第8章 時計用タイマ ... 159 **第9章 ウォッチドッグ・タイマ** ... 165 第10章 10**ビット**A/Dコンパータ ... 171 第11章 シリアル・インタフェース20 ... 184 第12章 **シリアル・インタフェース**1A0 ... 214 第13章 LCDコントローラ / ドライバ ... 248 第14章 乗算器 ... 265 第15章 リモコン受信回路(μPD789489, 78F9489のみ) ... 269 第16章 割り込み機能 ... 288 第17章 スタンバイ機能 ... 305 第18章 リセット機能 ... 313 第19章 フラッシュ・メモリ製品 ... 317 第20章 マスク・オプション ... 329 第21章 命令セットの概要 ... 330 第22章 **電気的特性(**μ PD789488, 78F9488, 789489, 78F9489**)** ... 341 **第23章 LCDコントローラ/ドライバ特性曲線(参考値)** … 360 第24章 外形図 ... 362 第25章 半田付け推奨条件 ... 364 付録A 開発ツール ... 367 付録B ターゲット・システム設計上の注意 ... 373 付録C レジスタ索引 ... 377 **付録D 改版履歴** ... 383

### CMOSデバイスの一般的注意事項

### 入力端子の印加波形

#### 入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

CMOSデバイスの入力がノイズなどに起因して、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、 $V_L$ (MAX.)から $V_H$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

#### 未使用入力の処理

#### CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVpoまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 静電気対策

#### MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 初期化以前の状態

### 電源投入時, MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

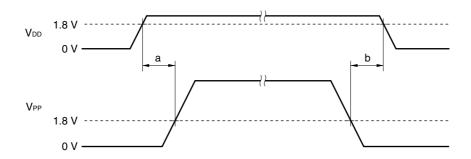

#### 電源投入切断順序

内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には,原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により,内部素子に過電圧が印加され,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源投入切断シーケンス」についての記載のある製品については,その内容を守ってください。

#### 電源OFF時における入力信号

当該デバイスの電源がOFF状態の時に,入力信号や入出力プルアップ電源を入れないでください。 入力信号や入出力プルアップ電源からの電流注入により,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

FIP, EEPROMは, NECエレクトロニクス株式会社の登録商標です。

Windows , Windows NTおよびWindows XPは , 米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。

PC/ATは,米国IBM社の商標です。

HP9000シリーズ700, HP-UXは,米国ヒューレット・パッカード社の商標です。

SPARCstationは、米国SPARC International, Inc.の商標です。

Solaris, SunOSは,米国サン・マイクロシステムズ社の商標です。

本製品のうち,外国為替及び外国貿易法の規定により規制貨物等(または役務)に該当するものについては,日本国外に輸出する際に,同法に基づき日本国政府の輸出許可が必要です。

非該当品 : μ PD78F9488, 78F9489 ユーザ判定品: μ PD789488, 789489

- ・本資料に記載されている内容は2005年6月現在のもので,今後,予告なく変更することがあります。量 産設計の際には最新の個別データ・シート等をご参照ください。

- ・文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は,本資料の誤りに関し,一切 その責を負いません。

- ・当社は,本資料に記載された当社製品の使用に関連し発生した第三者の特許権,著作権その他の知的財産権の侵害等に関し,一切その責を負いません。当社は,本資料に基づき当社または第三者の特許権,著作権その他の知的財産権を何ら許諾するものではありません。

- ・本資料に記載された回路,ソフトウエアおよびこれらに関する情報は,半導体製品の動作例,応用例を 説明するものです。お客様の機器の設計において,回路,ソフトウエアおよびこれらに関する情報を使 用する場合には,お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し,当社は,一切その責を負いません。

- ・当社は,当社製品の品質,信頼性の向上に努めておりますが,当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命,身体および財産に対する損害の危険を最小限度にするために,冗長設計,延焼対策設計,誤動作防止設計等安全設計を行ってください。

- ・当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定していただく「特定水準」に分類しております。また,各品質水準は,以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認ください。

標準水準:コンピュータ, OA機器, 通信機器, 計測機器, AV機器, 家電, 工作機械, パーソナル機器, 産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート,データ・ブック等の資料で特に品質水準の表示がない場合は,標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には,事前に当社販売窓口までお問い合わせください。

#### (注)

- (1)本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2)本事項において使用されている「当社製品」とは,(1)において定義された当社の開発,製造製品をいう。

M8E 02.11

# 本版で改訂された主な箇所

| 箇 所        | 内 容                                                                       |

|------------|---------------------------------------------------------------------------|

| 全般         | μ PD789489, 78F9489の開発完了による表記変更                                           |

|            | ・開発中の表記削除                                                                 |

|            | ・サブシリーズ名を「μ PD789489サブシリーズ 」に変更                                           |

| p.30-32    | 1.5 78K/0S <b>シリーズの展開</b> を最新の内容に変更                                       |

| p.122      | <b>図</b> 7 - 2 <b>タイマ</b> 50 <b>のプロック図</b> を修正                            |

| p.123      | <b>図</b> 7 - 3 <b>タイマ</b> 60 <b>のブロック図</b> を修正                            |

| p.125      | <b>図</b> 7-5 <b>出力制御回路(タイマ</b> 60 <b>)のブロック図</b> を修正                      |

| p.125      | 7.2 (2) 8 <b>ピット・コンペア・レジスタ</b> 60 (CR60)に,説明文を追加                          |

| p.126      | 7.2 (4) 8 <b>ビット</b> H <b>幅コンペア・レジスタ</b> 60, 61 ( CRH60, CRH61 ) に,説明文を追加 |

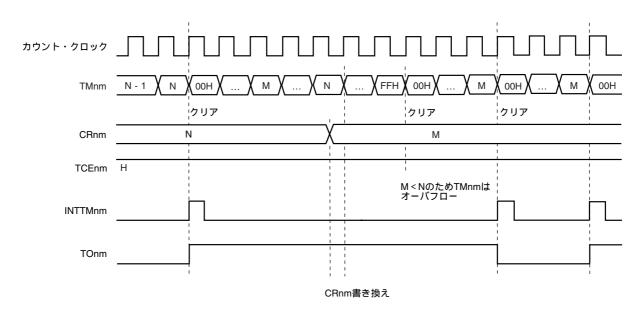

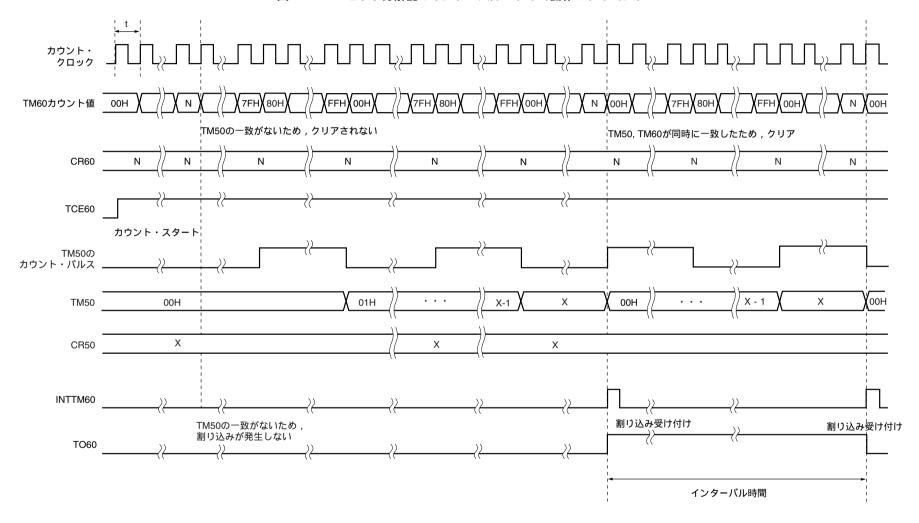

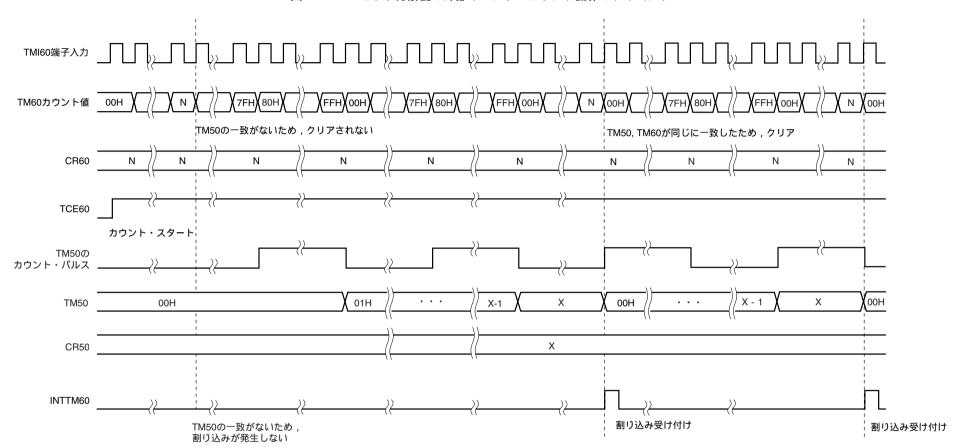

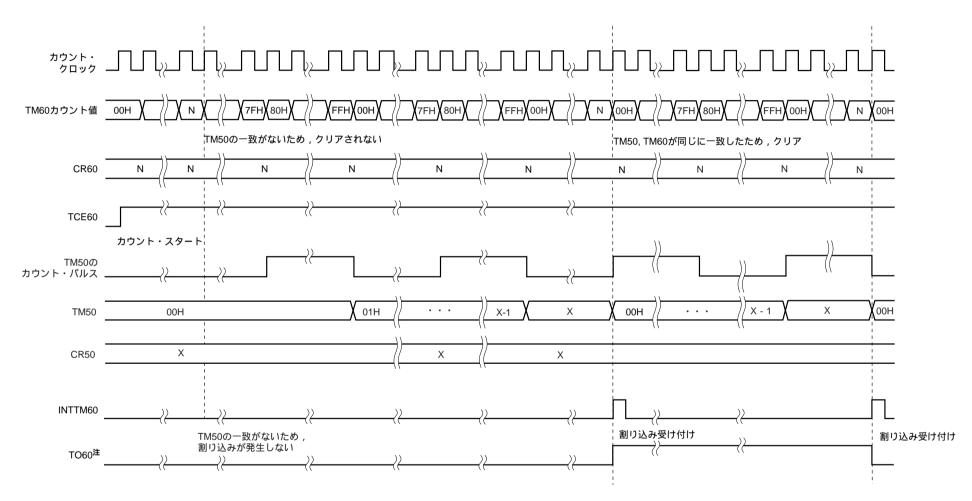

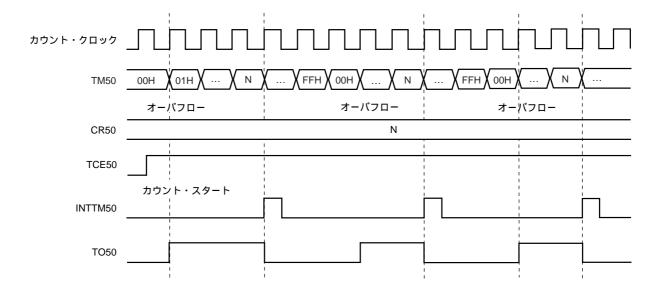

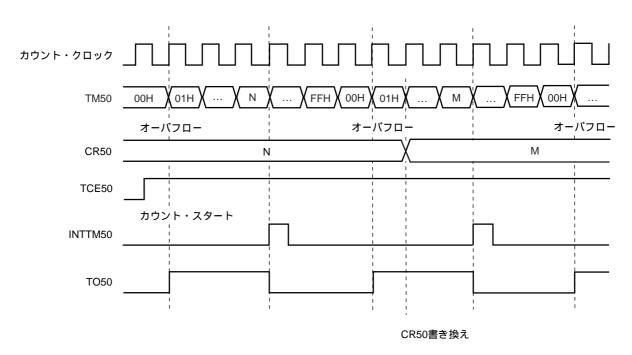

| p.135      | 図7 - 11 8ビット分解能のインターバル・タイマ動作のタイミング(基本動作)を修正                               |

| p.136      | 図7 - 13 8ビット分解能のインターバル・タイマ動作のタイミング(CRnm = FFH設定時)を修                       |

|            | 正                                                                         |

| p.138      | 図7 - 17 16 <b>ビット分解能の外部イベント・カウンタ動作のタイミング</b> を修正                          |

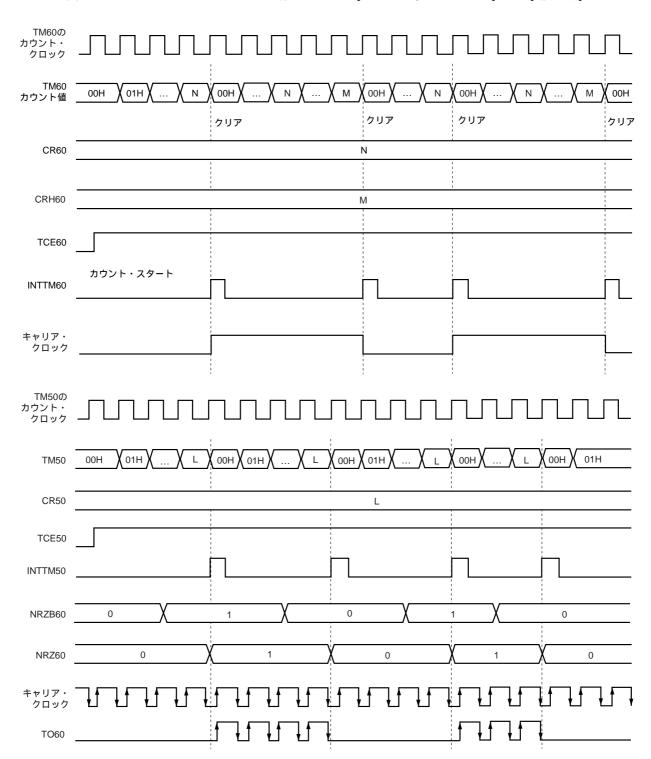

| p.148      | 7.4.3 <b>キャリア・ジェネレータとしての動作</b> の設定手順の記述を追加                                |

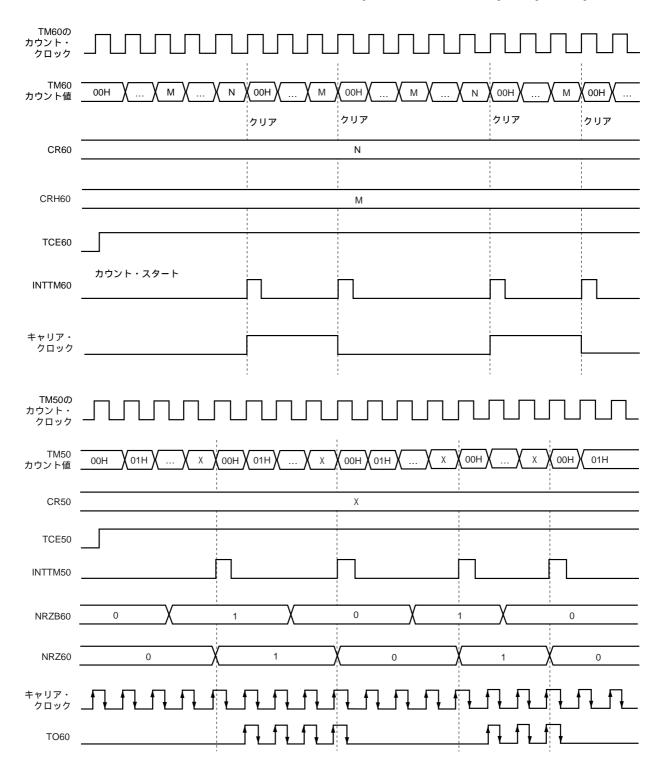

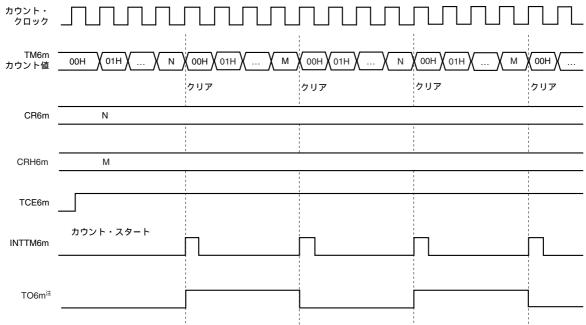

| p.149      | 図7 - 22 キャリア・ジェネレータの動作タイミング(CR60 = N, CRH60 = M (M > N) 設定時)              |

|            | を修正                                                                       |

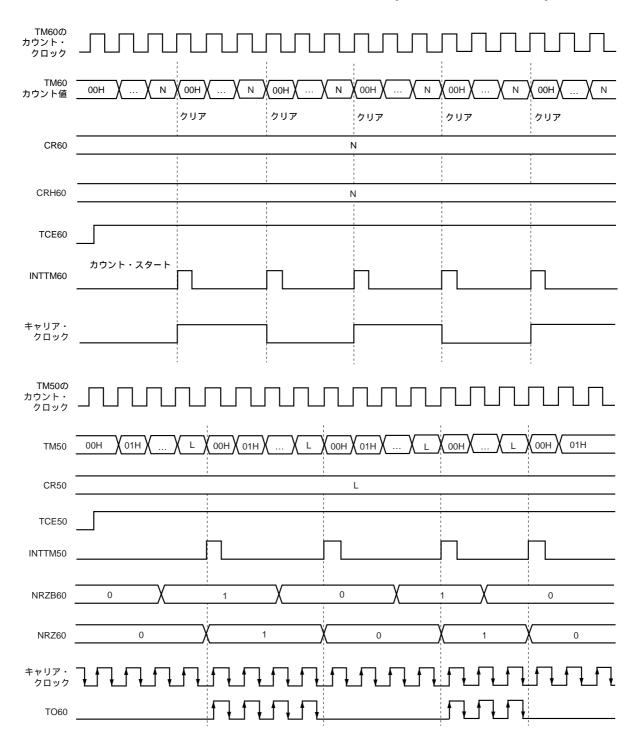

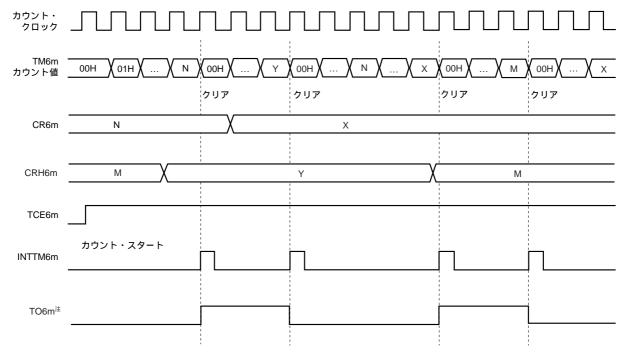

| p.150      | 図7 - 23 キャリア・ジェネレータの動作タイミング(CR60 = N, CRH60 = M (M < N) 設定時)              |

|            | を修正                                                                       |

| p.151      | 図7 - 24 キャリア・ジェネレータの動作タイミング (CR60 = CRH60 = N設定時)を修正                      |

| p.152-155  | 7.4.4 PWM <b>出力モードとしての動作(タイマ</b> 50 <b>)</b> のモード名称を修正                    |

| p.156, 157 | 7.4.5 PPG <b>出力モードとしての動作(タイマ</b> 60, 61 <b>)</b> のモード名称を修正                |

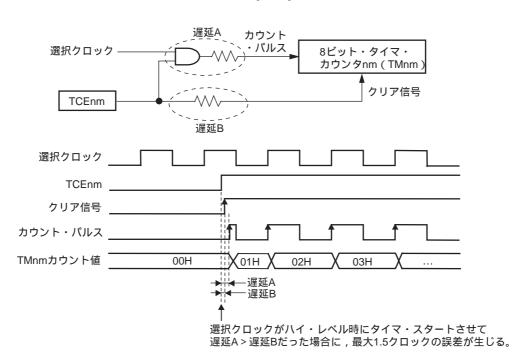

| p.158      | 7.5 8 <b>ピット・タイマ</b> 50,60,61 <b>の注意事項の(1)タイマ・スタート時の誤差</b> を内容改訂          |

| p.172      | <b>図</b> 10 - 1 10 <b>ピット</b> A/D <b>コンバータのブロック図</b> を修正                  |

| p.180      | 10.5 10ピットA/Dコンバータの注意事項の(1)スタンバイ・モードの消費電流についてを修正                          |

| p.185      | 図11 - 1 シリアル・インタフェース20 <b>のプロック図</b> を修正                                  |

| p.188      | 図11 - 3 シリアル動作モード・レジスタ20のフォーマットに注意文を追加                                    |

| p.192      | 図11 - 6 ボー・レート・ジェネレータ・コントロール・レジスタ20のフォーマットの注意文を                           |

|            | 修正                                                                        |

| p.193, 201 | 表11 - 3 , 表11 - 5 システム・クロックとボー・レートの関係例の注意文を修正                             |

| p.220      | 図12 - 4 <b>自動データ送受信転送間隔指定レジスタ0のフォーマット</b> の記述を修正                          |

| p.341-359  | 第22章 <b>電気的特性(</b> μ PD789488, 78F9489, 78F9489 <b>)</b>                  |

|            | ・μ PD789489, 78F9489の正式スペックを追加                                            |

| p.364, 365 | <b>第</b> 25 <b>章 半田付け推奨条件</b> にμ PD789489, 78F9489の半田付け条件を追加              |

|            | 修正版(U15331JJ4V1UD00)で改訂された主な箇所                                            |

| 全般         | 鉛フリー製品を追加                                                                 |

| p.252, 255 | <b>第</b> 13 <b>章</b> LCD <b>コントローラ / ドライバ</b> の昇圧ウエイト時間の記述を変更             |

| p.326      | 図19 - 9 3線式シリアルI/〇方式(ハンドシェークあり)でのフラッシュ書き込み用アダプタ配線                         |

|            | 例を修正                                                                      |

本文欄外の★印は,本版で改訂された主な箇所を示しています。

## はじめに

**対象者** このマニュアルはμ PD789489サブシリーズの機能を理解し,その応用システムや応用プログラムを設計,開発するユーザのエンジニアを対象としています。

対象製品は,次に示すサブシリーズの各製品です。

・ $\mu$  PD789489サブシリーズ :  $\mu$  PD789488, 789489, 78F9488, 78F9489

**目 的** このマニュアルは,次の構成に示す機能をユーザに理解していただくことを目的としています。

構 成  $\mu$  PD789489サブシリーズのマニュアルは,このマニュアルと命令編(78K/0Sシリーズ共通)の2冊に分かれています。

μPD789489サブシリーズ ユーザーズ・マニュアル 78K/0Sシリーズ ユーザーズ・マニュアル 命令編

端子機能 内部ブロック機能

割り込み

その他の内蔵周辺機能

電気的特性

CPU機能 命令セット 命令の説明

読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコンピュータの一般知識を必要とします。

一通りの機能を理解しようとするとき

目次に従って読んでください。

レジスタ・フォーマットの見方

ビット番号を で囲んでいるものは、そのビット名称がアセンブラでは予約語に、Cコンパイラでは#pragma sfr指令で、sfr変数として定義されているものです。

レジスタ名が分かっていてレジスタの詳細を確認するとき

付録C レジスタ索引を利用してください。

78K/0Sシリーズの命令機能の詳細を知りたいとき

別冊の78K/0S**シリーズ ユーザーズ・マニュアル 命令編 (**U11047J**)** を参照してください。 *u* PD789489サブシリーズの電気的特性を知りたいとき

第22章 電気的特性 (μ PD789488, 78F9488, 789489, 78F9489) を参照してください。

**凡** 例 データ表記の重み:左が上位桁,右が下位桁

アクティブ・ロウの表記 :  $\overline{\times \times \times}$  (端子, 信号名称に上線)

注:本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数…××××または××××B

10進数...×××× 16進数...××××H

# **関連資料** 関連資料は暫定版の場合がありますが、この資料では「暫定」の表示をしておりません。あらかじめ ご了承ください。

### デバイスの関連資料

| 資 料 名                                      |   | 資料番号 |   |   |

|--------------------------------------------|---|------|---|---|

|                                            | 和 | 文    | 英 | 文 |

| μPD789489サブシリーズ ユーザーズ・マニュアル このマニュアル U1533  |   | 1E   |   |   |

| 78K/0Sシリーズ ユーザーズ・マニュアル 命令編 U11047J U11047E |   | 7E   |   |   |

### ★ 開発ツール (ソフトウエア) の資料 (ユーザーズ・マニュアル)

| 資 料 名                          |               | 資料      | 番号      |

|--------------------------------|---------------|---------|---------|

|                                |               | 和 文     | 英 文     |

| RA78KOS アセンブラ・パッケージ            | 操作編           | U17391J | U17391E |

|                                | 言語編           | U17390J | U17390E |

|                                | 構造化アセンブリ言語編   | U17389J | U17389E |

| CC78K0S Cコンパイラ                 | 操作編           | U16654J | U16654E |

|                                | 言語編           | U16655J | U16655E |

| SM+ システム・シミュレータ                | 操作編           | U17246J | U17246E |

|                                | ユーザ・オープン・     | U17247J | U17247E |

|                                | インタフェース編      |         |         |

| SM78Kシリーズ Ver.2.52 システム・シミュレータ | 操作編           | U16768J | U16768E |

|                                | 外部部品ユーザ・オープン・ | U15802J | U15802E |

|                                | インタフェース仕様編    |         |         |

| ID78K0S-NS Ver.2.52 統合ディバッガ    | 操作編           | U16584J | U16584E |

| PM plus Ver.5.20               |               | U16934J | U16934E |

### 開発ツール (ハードウエア)の資料 (ユーザーズ・マニュアル)

| 資 料 名                         |         | 資料番号    |  |  |

|-------------------------------|---------|---------|--|--|

|                               | 和文      | 英 文     |  |  |

| IE-78KOS-NS インサーキット・エミュレータ    | U13549J | U13549E |  |  |

| IE-78KOS-NS-A インサーキット・エミュレータ  | U15207J | U15207E |  |  |

| IE-789488-NS-EM1 エミュレーション・ボード | U16492J | U16492E |  |  |

#### フラッシュ・メモリ書き込み用の資料

| 資料名                                | 資料番号    |         |  |

|------------------------------------|---------|---------|--|

|                                    | 和文      | 英 文     |  |

| PG-FP3 フラッシュ・メモリ・プログラマ ユーザーズ・マニュアル | U13502J | U13502E |  |

| PG-FP4 フラッシュ・メモリ・プログラマ ユーザーズ・マニュアル | U15260J | U15260E |  |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

### その他の資料

|   | COIDORA                                                 |         |         |

|---|---------------------------------------------------------|---------|---------|

|   | 資料名                                                     | 資料番号    |         |

|   |                                                         | 和文      | 英 文     |

| * | SEMICONDUCTOR SELECTION GUIDE - Products and Packages - | X13769X |         |

| * | 半導体デバイス 実装マニュアル                                         | 注       |         |

|   | NEC半導体デバイスの品質水準                                         | C11531J | C11531E |

|   | NEC半導体デバイスの信頼性品質管理                                      | C10983J | C10983E |

|   | 静電気放電(ESD)破壊対策ガイド                                       | C11892J | C11892E |

|   | 半導体 品質 / 信頼性ハンドブック                                      | C12769J | -       |

|   | マイクロコンピュータ関連製品ガイド 社外メーカ編                                | U11416J | -       |

注 「半導体デバイス実装マニュアル」のホーム・ページ参照

和文:http://www.necel.com/pkg/ja/jissou/index.html 英文:http://www.necel.com/pkg/en/mount/index.html

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

# 目 次

| <b>万   早</b> | <b>版 就</b> 25                                           |

|--------------|---------------------------------------------------------|

| 4.4          | A± Oth OF                                               |

|              | 特 徵 25<br>                                              |

|              | 応用分野 25<br>オーダ情報 26                                     |

|              | <b>端子接続図 (</b> Top View) 27                             |

|              | 78K/OS <b>シリーズの展開</b> 30                                |

|              | プロック図 33                                                |

|              | 機能概要 34                                                 |

|              |                                                         |

| 第2章          | <b>端子機能</b> 36                                          |

| -1           |                                                         |

| 2. 1         | <b>端子機能一覧</b> 36                                        |

| 2. 2         | 端子機能の説明 39                                              |

|              | 2. 2. 1 P00-P07 ( Port 0 ) 39                           |

|              | 2. 2. 2 P10, P11 ( Port 1 ) 39                          |

|              | 2. 2. 3 P20-P25 ( Port 2 ) 39                           |

|              | 2. 2. 4 P30-P34 (Port 3) 40                             |

|              | 2. 2. 5 P50-P53 ( Port 5 ) 40                           |

|              | 2. 2. 6 P60-P67 ( Port 6 ) 41                           |

|              | 2. 2. 7 P70-P73 ( Port 7 ) 41                           |

|              | 2. 2. 8 P80-P87 ( Port 8 ) 41                           |

|              | 2. 2. 9 S0-S27 41                                       |

|              | 2. 2. 10 COM0-COM3 41                                   |

|              | 2. 2. 11 VLC0-VLC2 41                                   |

|              | 2. 2. 12 CAPH, CAPL 41                                  |

|              | 2. 2. 13 RESET 42                                       |

|              | 2. 2. 14 X1, X2 42                                      |

|              | 2. 2. 15 XT1, XT2 42                                    |

|              | 2. 2. 16 AVDD 42                                        |

|              | 2. 2. 17 AVss 42                                        |

|              | 2. 2. 18 VDD 42                                         |

|              | 2. 2. 19 Vss 42                                         |

|              | 2. 2. 20 Vpp (フラッシュ・メモリ製品のみ) 42                         |

| 2.2          | 2. 2. 21 ICO(マスクROM製品のみ) 43<br>端子の入出力回路と未使用端子の処理 44     |

| 2. 3         | - MTの人山万国府と不使用MTの処理 44                                  |

| 筆3音          | CPU <b>アーキテクチャ</b> 47                                   |

| わり子          | OI OJ 7 J J J F 47                                      |

| 3. 1         | メモリ空間 47                                                |

| · ·          | 3. 1. 1 内部プログラム・メモリ空間 51                                |

|              | 3. 1. 2 内部データ・メモリ空間 52                                  |

|              | 3. 1. 3 特殊機能レジスタ (SFR: Special Function Register) 領域 52 |

|              | 3. 1. 4 データ・メモリ・アドレシング 53                               |

|              |                                                         |

| 3. 2             | プロセッサ・レジスタ 57                  |

|------------------|--------------------------------|

|                  | 3. 2. 1 制御レジスタ 57              |

|                  | 3. 2. 2 汎用レジスタ 60              |

|                  | 3.2.3 特殊機能レジスタ(SFR) 61         |

| 3. 3             | 命令アドレスのアドレシング 65               |

|                  | 3. 3. 1 レラティブ・アドレシング 65        |

|                  | 3.3.2 イミーディエト・アドレシング 66        |

|                  | 3.3.3 テーブル・インダイレクト・アドレシング 67   |

|                  | 3. 3. 4 レジスタ・アドレシング 67         |

| 3. 4             | オペランド・アドレスのアドレシング 68           |

|                  | 3. 4. 1 ダイレクト・アドレシング 68        |

|                  | 3.4.2 ショート・ダイレクト・アドレシング 69     |

|                  | 3.4.3 特殊機能レジスタ (SFR) アドレシング 70 |

|                  | 3. 4. 4 レジスタ・アドレシング 71         |

|                  | 3.4.5 レジスタ・インダイレクト・アドレシング 72   |

|                  | 3.4.6 ベースト・アドレシング 73           |

|                  | 3.4.7 スタック・アドレシング 73           |

|                  |                                |

| 第4章              | <b>ポート機能</b> 74                |

|                  |                                |

| 4. 1             | ポートの機能 74                      |

| 4. 2             | <b>ポートの構成</b> 75               |

|                  | 4. 2. 1 ポート0 76                |

|                  | 4. 2. 2 ポート1 77                |

|                  | 4. 2. 3 ポート2 78                |

|                  | 4.2.4 ポート3 83                  |

|                  | 4. 2. 5 ポート5 85                |

|                  | 4.2.6 ポート6 86                  |

|                  | 4. 2. 7 ポート7 88                |

|                  | 4.2.8 ポート8 89                  |

| 4. 3             | <b>ポート機能を制御するレジスタ</b> 90       |

| 4. 4             | <b>ポート機能の動作</b> 93             |

|                  | 4. 4. 1 入出力ポートへの書き込み 93        |

|                  | 4.4.2 入出力ポートからの読み出し 93         |

|                  | 4.4.3 入出力ポートでの演算 93            |

| ~~ - <del></del> |                                |

| <b>第5草</b>       | <b>クロック発生回路</b> 94             |

| 5 1              | <b>クロック発生回路の機能</b> 94          |

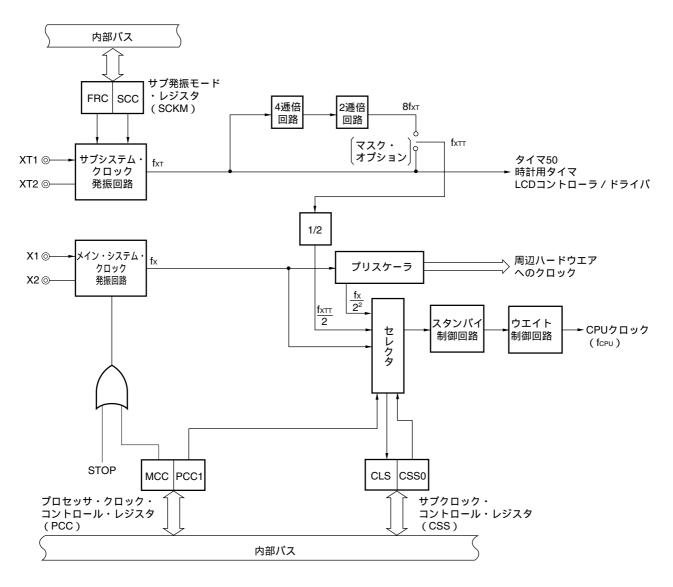

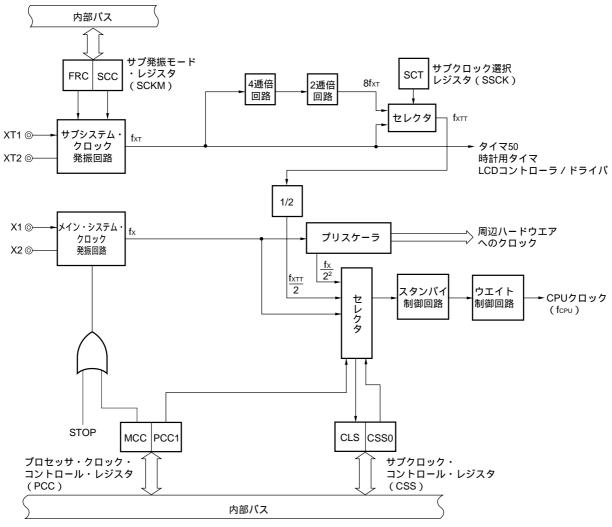

|                  | クロック発生回路の構成 94                 |

|                  | クロック発生回路を制御するレジスタ 97           |

|                  | システム・クロック発振回路 100              |

| О. Т             | 5. 4. 1 メイン・システム・クロック発振回路 100  |

|                  | 5. 4. 2 サプシステム・クロック発振回路 101    |

|                  | 5.4.3 発振子の接続の悪い例 102           |

|                  | 5.4.4 分周回路 103                 |

|                  | 5.4.5 サプシステム・クロックを使用しない場合 103  |

|                  | 5.4.6 サプシステム・クロック4逓倍回路 103     |

| E                |                                |

| ວ. ວ             | <b>クロック発生回路の動作</b> 104         |

|                      | 5. 6. 1 システム・クロックとCPUクロックの切り替えに要する時間<br>5. 6. 2 システム・クロックとCPUクロックの切り替え手順 106                                                                                                                                                                                                                                                                                                                                                                                   | 105 |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>第</b> 6章          | 16 <b>ビット・タイマ</b> 20 107                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

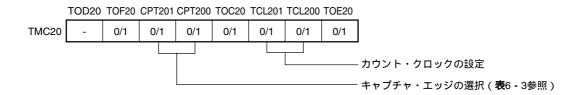

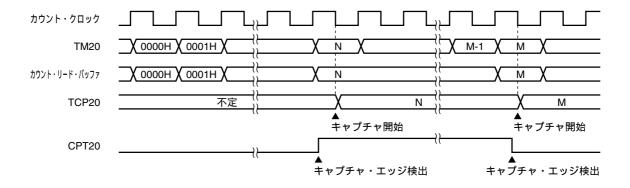

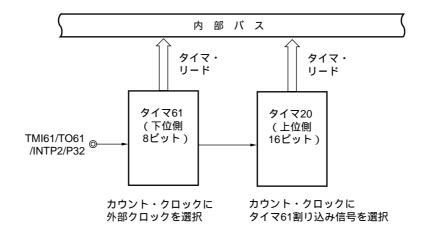

| 6. 2<br>6. 3<br>6. 4 | 16 <b>ビット・タイマ20の機能</b> … 107<br>16 <b>ビット・タイマ20の構成</b> … 107<br>16 <b>ビット・タイマ20を制御するレジスタ</b> … 109<br>16 <b>ビット・タイマ20の動作</b> … 112<br>6.4.1 タイマ割り込みとしての動作 … 112<br>6.4.2 タイマ出力としての動作 … 114<br>6.4.3 キャプチャ動作 … 115<br>6.4.4 16ビット・タイマ・カウンタ20の読み出し … 116<br>16 <b>ビット・タイマ20の注意事項</b> … 117<br>6.5.1 16ビット・コンペア・レジスタ20を書き換える際の制限事項 …                                                                                                                              | 117 |

| 第7章                  | 8 <b>ピット・タイマ</b> 50, 60, 61 119                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 7. 2<br>7. 3<br>7. 4 | 8 <b>ビット・タイマ</b> 50, 60, 61 <b>の機能</b> … 119<br>8 <b>ビット・タイマ</b> 50, 60, 61 <b>の構成</b> … 121<br>8 <b>ビット・タイマ</b> 50, 60, 61 <b>を制御するレジスタ</b> … 127<br>8 <b>ビット・タイマ</b> 50, 60, 61 <b>の動作</b> … 133<br>7. 4. 1 8ビット・タイマ・カウンタ・モードとしての動作 … 133<br>7. 4. 2 16ビット・タイマ・カウンタ・モードとしての動作 … 141<br>7. 4. 3 キャリア・ジェネレータとしての動作 … 148<br>7. 4. 4 PWM出力モードとしての動作 (タイマ50) … 152<br>7. 4. 5 PPG出力モードとしての動作 (タイマ60, 61) … 156<br>8 <b>ビット・タイマ</b> 50, 60, 61 <b>の注意事項</b> … 158 |     |

| 第8章                  | <b>時計用タイマ</b> 159                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 8. 2<br>8. 3         | 時計用タイマの機能 159<br>時計用タイマの構成 160<br>時計用タイマを制御するレジスタ 161<br>時計用タイマの動作 163<br>8.4.1 時計用タイマとしての動作 163<br>8.4.2 インターバル・タイマとしての動作 163                                                                                                                                                                                                                                                                                                                                 |     |

| <b>第</b> 9章          | ウォッチドッグ・タイマ 165                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 9. 2<br>9. 3         | ウォッチドッグ・タイマの機能 165<br>ウォッチドッグ・タイマの構成 166<br>ウォッチドッグ・タイマを制御するレジスタ 167<br>ウォッチドッグ・タイマの動作 169<br>9.4.1 ウォッチドッグ・タイマとしての動作 169<br>9.4.2 インターバル・タイマとしての動作 170                                                                                                                                                                                                                                                                                                        |     |

5.6 システム・クロックとCPUクロックの設定の変更 ... 105

| 第1         | 0章                                                 | 10 <b>ビット</b> A/D <b>コンバータ</b> 171                                                                                                                                                                                                                                                                            |

|------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 10. 2<br>10. 3<br>10. 4                            | 10 <b>ビット</b> A/D <b>コンバータの機能</b> 171<br>10 <b>ビット</b> A/D <b>コンバータの構成</b> 171<br>10 <b>ビット</b> A/D <b>コンバータを制御するレジスタ</b> 174<br>10 <b>ビット</b> A/D <b>コンバータの動作</b> 176<br>10.4.1 10ビットA/Dコンバータの基本動作 176<br>10.4.2 入力電圧と変換結果 178<br>10.4.3 10ビットA/Dコンバータの動作モード 179<br>10 <b>ビット</b> A/D <b>コンバータの</b> 注意事項 180 |

| 第1         | 1章                                                 | シリアル・インタフェース20 184                                                                                                                                                                                                                                                                                            |

|            | 11. 2<br>11. 3<br>11. 4                            | シリアル・インタフェース20の機能 184<br>シリアル・インタフェース20の構成 184<br>シリアル・インタフェース20を制御するレジスタ 188<br>シリアル・インタフェース20の動作 195<br>11.4.1 動作停止モード 195<br>11.4.2 アシンクロナス・シリアル・インタフェース(UART)モード 197<br>11.4.3 3線式シリアルI/Oモード 209                                                                                                          |

| <b>第</b> 1 | 2章                                                 | シリアル・インタフェース1A0 214                                                                                                                                                                                                                                                                                           |

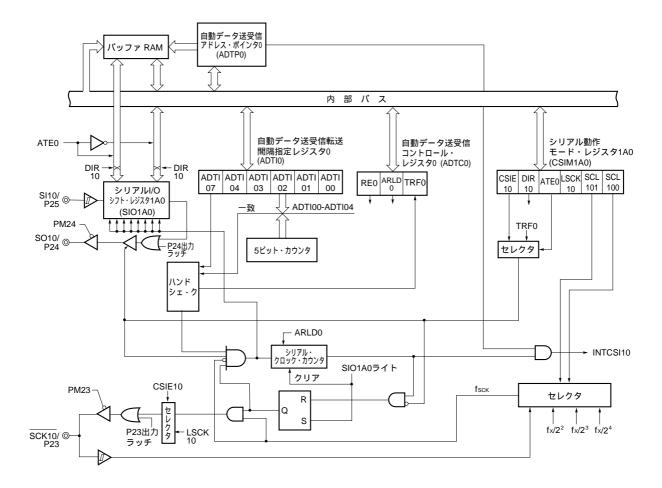

|            | 12. 2<br>12. 3<br>12. 4                            | シリアル・インタフェース1A0の機能214シリアル・インタフェース1A0の構成215シリアル・インタフェース1A0を制御するレジスタ217シリアル・インタフェース1A0の動作22212. 4. 1動作停止モード22212. 4. 23線式シリアルI/Oモード22312. 4. 3自動送受信機能付き3線式シリアルI/Oモード228                                                                                                                                         |

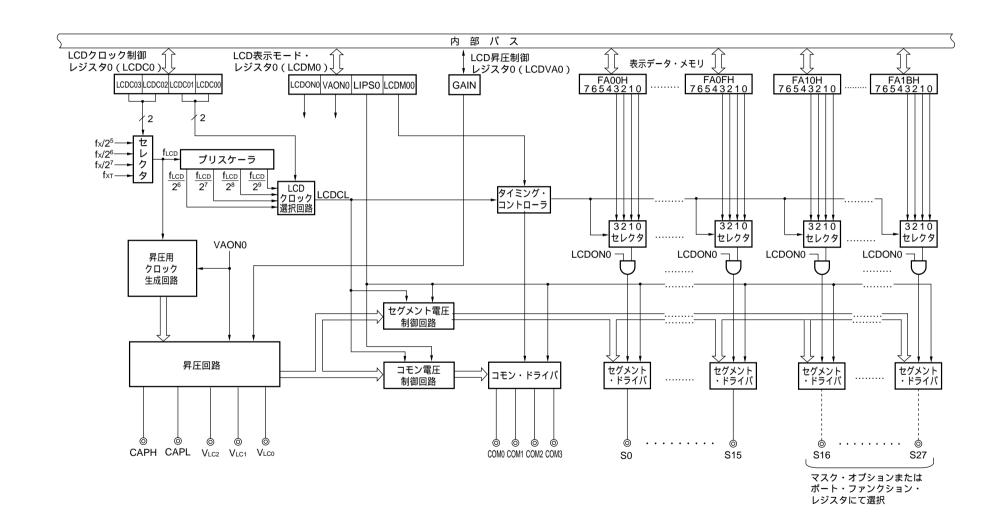

| 第1         | 3章                                                 | LCD <b>コントローラ / ドライバ</b> 248                                                                                                                                                                                                                                                                                  |

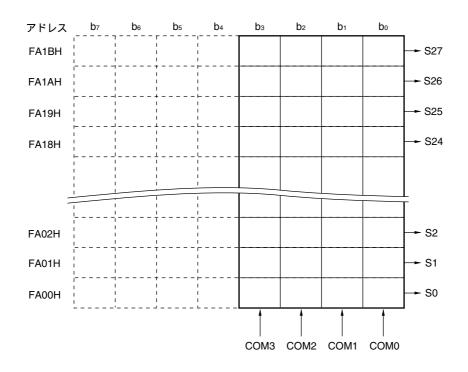

|            | 13. 2<br>13. 3<br>13. 4<br>13. 5<br>13. 6<br>13. 7 | LCDコントローラ/ドライバの機能 … 248<br>LCDコントローラ/ドライバの構成 … 248<br>LCDコントローラ/ドライバを制御するレジスタ … 251<br>LCDコントローラ/ドライバの設定 … 255<br>LCD表示データ・メモリ … 255<br>コモン信号とセグメント信号 … 256<br>表示モード … 258<br>13. 7. 1 3時分割表示例 … 258<br>13. 7. 2 4時分割表示例 … 261<br>LCD駆動電圧VLCO, VLC1, VLC2の供給 … 264                                            |

| 第1         | 4章                                                 | 乗 算 器 265                                                                                                                                                                                                                                                                                                     |

|            |                                                    | 乗算器の機能 265<br>乗算器の構成 265                                                                                                                                                                                                                                                                                      |

14.3 乗算器を制御するレジスタ ... 267

### 14.4 乗算器の動作 ... 268

| 第15章                 | <b>リモコン受信回路(</b> μ PD789489, 78F9489 <b>のみ)</b> 269 |

|----------------------|-----------------------------------------------------|

| 15. 1                | <b>リモコン受信回路の機能</b> 269                              |

|                      | <b>リモコン受信回路の構成</b> 269                              |

|                      | <b>リモコン受信回路を制御するレジスタ</b> 275                        |

|                      | リモコン受信回路の動作 277                                     |

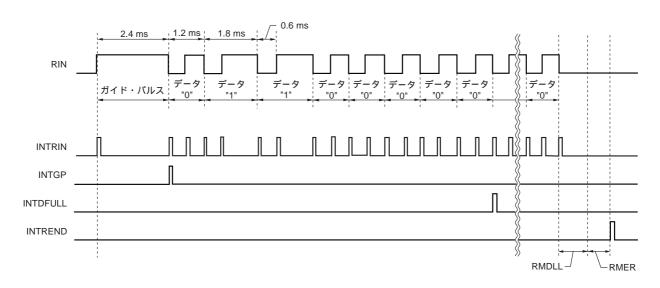

|                      | 15. 4. 1 A方式受信モードのフォーマット 277                        |

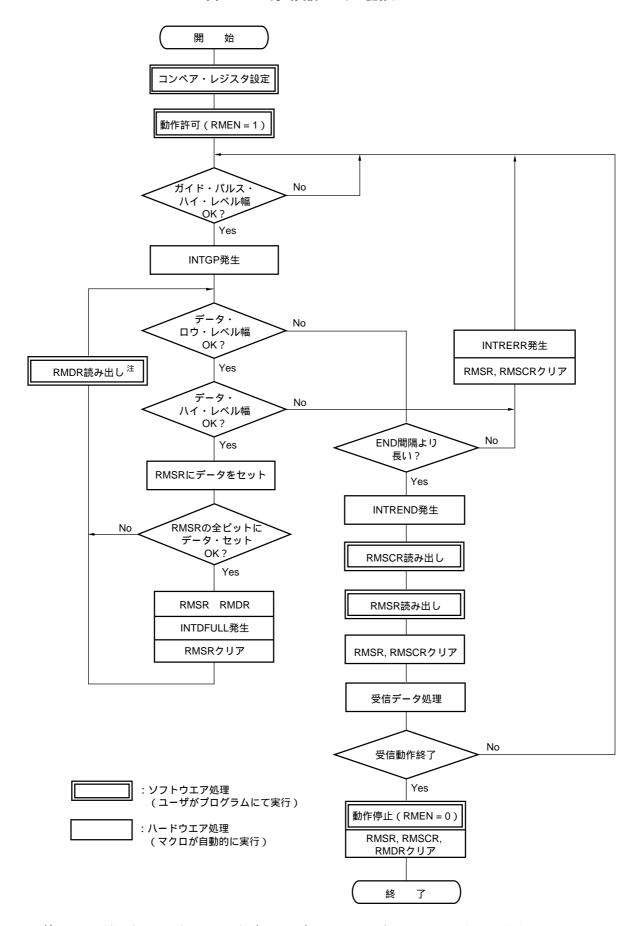

|                      | 15. 4. 2 A方式受信モードの動作フロー 277                         |

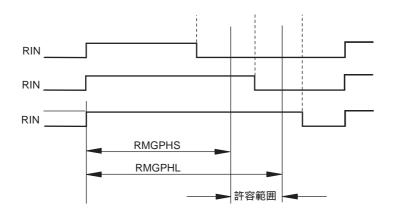

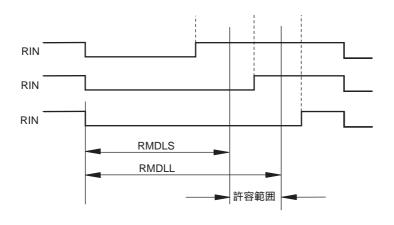

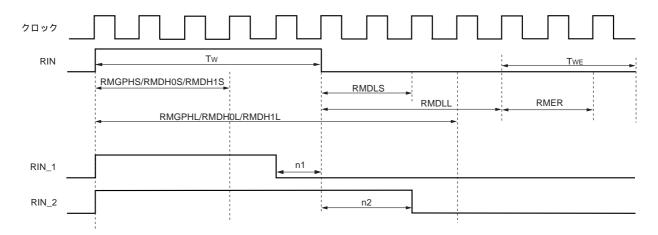

|                      | 15.4.3 タイミング説明 279                                  |

|                      | 15. 4. 4 コンペア・レジスタ設定 281                            |

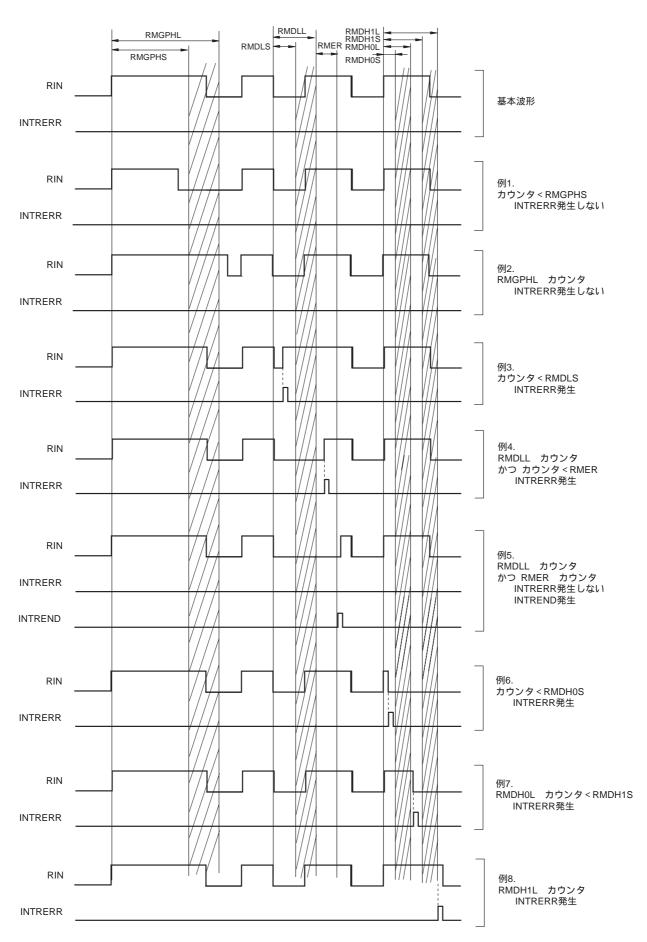

|                      | 15.4.5 エラー割り込み発生タイミング 283                           |

|                      | 15.4.6 ノイズ・キャンセル 285                                |

| <b>第</b> 16 <b>章</b> | 割り込み機能 288                                          |

| 16. 1                | 割り込み機能の種類 288                                       |

| 16. 2                | 割り込み要因と構成 288                                       |

| 16. 3                | <b>割り込み機能を制御するレジスタ</b> 292                          |

| 16. 4                | 割り込み処理動作 299                                        |

|                      | 16. 4. 1 ノンマスカブル割り込み要求の受け付け動作 299                   |

|                      | 16.4.2 マスカブル割り込み要求の受け付け動作 301                       |

|                      | 16.4.3 多重割り込み処理 303                                 |

| •                    | 16.4.4 割り込み要求の保留 304                                |

| <b>第</b> 17 <b>章</b> | ス <b>タンパイ機能</b> 305                                 |

| 17. 1                | スタンパイ機能と構成 305                                      |

|                      | 17. 1. 1 スタンバイ機能 305                                |

|                      | 17. 1. 2 スタンバイ機能を制御するレジスタ 306                       |

| 17. 2                | スタンパイ機能の動作 307                                      |

|                      | 17.2.1 HALTモード 307                                  |

|                      | 17.2.2 STOPモード 310                                  |

| <b>第</b> 18 <b>章</b> | <b>リセット機能</b> 313                                   |

| <b>第</b> 19 <b>章</b> | フラッシュ・メモリ製品 317                                     |

| 19. 1                | フラッシュ・メモリ <b>の特徴</b> 318                            |

|                      | <br>19. 1. 1 プログラミング環境 318                          |

|                      | 19. 1. 2 通信方式 319                                   |

|                      | 19. 1. 3 オンボード上の端子処理 322                            |

|                      | 19.1.4 フラッシュ書き込み用アダプタ上の接続 325                       |

| 19. 2                | μ PD78F9488, 78F9489 <b>の注意事項</b> 328               |

| 第20章                 | マスク・オプション 329                                       |

### 第21章 命令セットの概要 ... 330

- 21.1 オペレーション ... 330

- 21.1.1 オペランドの表現形式と記述方法 ... 330

- 21.1.2 オペレーション欄の説明 ... 331

- 21.1.3 フラグ動作欄の説明 ... 331

- 21.2 **オペレーション一覧** ... 332

- 21.3 アドレシング別命令一覧 ... 338

- **第22章 電気的特性(**μ PD789488, 78F9488, 789489, 78F9489**)** ... 341

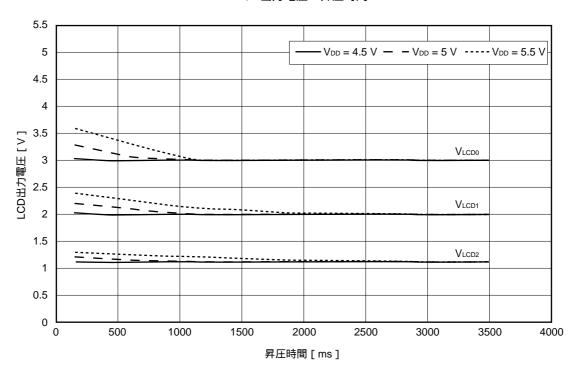

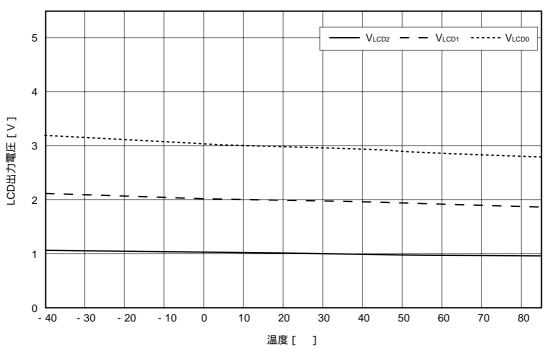

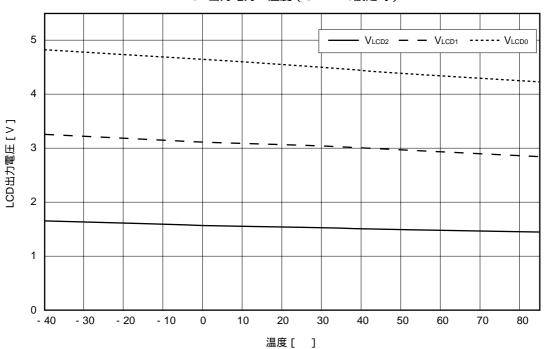

- **第23章 LCDコントローラ/ドライバ特性曲線(参考値)** … 360

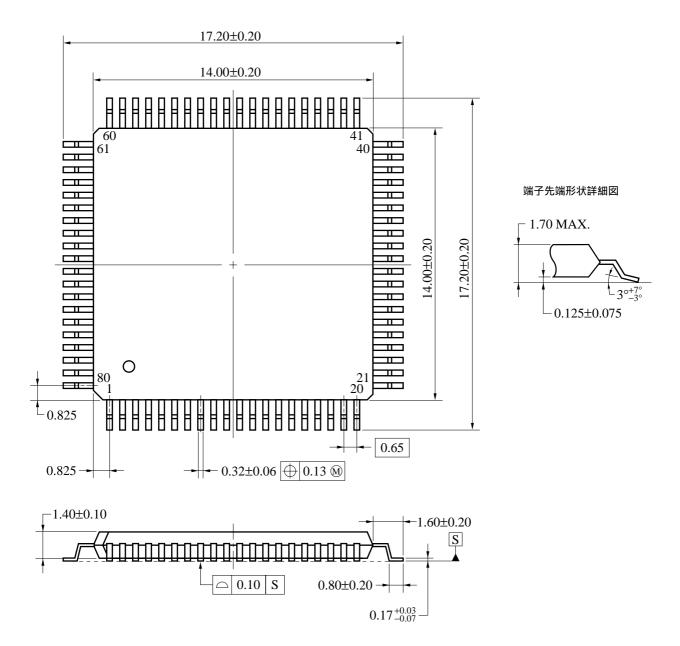

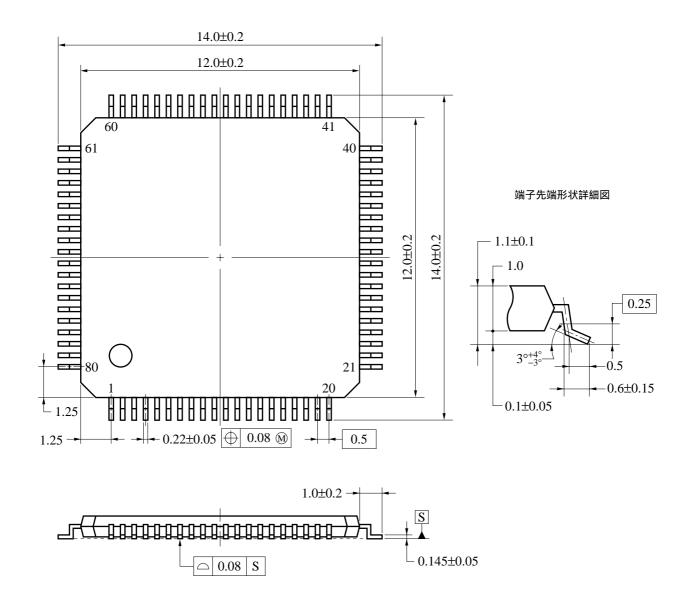

- 第24章 外形図 ... 362

- 第25章 半田付け推奨条件 ... 364

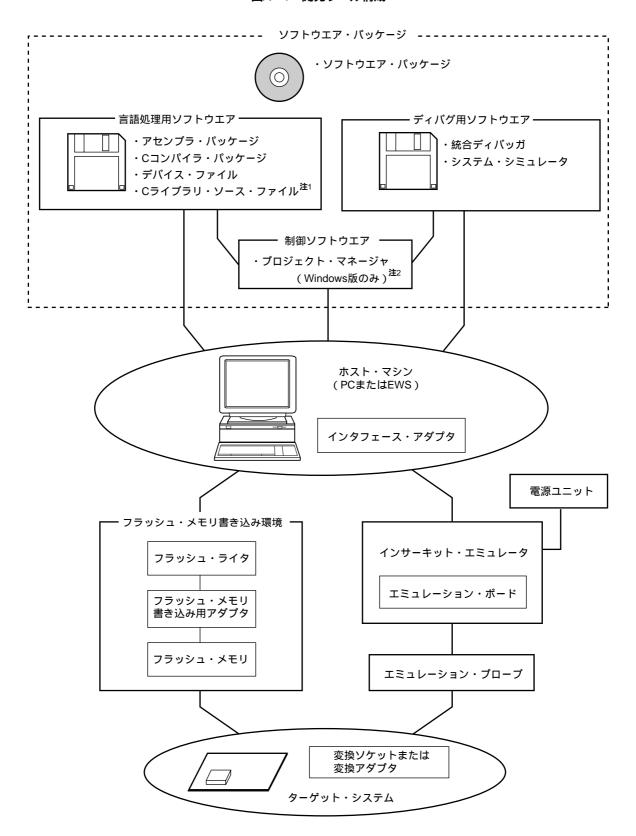

- 付録A 開発ツール ... 367

- A. 1 ソフトウエア・パッケージ ... 369

- A. 2 言語処理用ソフトウエア ... 369

- A. 3 **制御ソフトウエア** ... 370

- A. 4 フラッシュ・メモリ書き込み用ツール ... 370

- A.5 ディバグ用ツール (ハードウエア) ... 371

- A. 6 ディバグ用ツール (ソフトウエア) ... 372

- 付録B ターゲット・システム設計上の注意 ... 373

- 付録C レジスタ索引 ... 377

- C.1 **レジスタ索引 (50音順)** ... 377

- C. 2 レジスタ索引 (アルファベット順) ... 380

- **付録D 改版履歴** ... 383

# 図の目次 (1/6)

| 図番号    | タイトル , ページ                              |

|--------|-----------------------------------------|

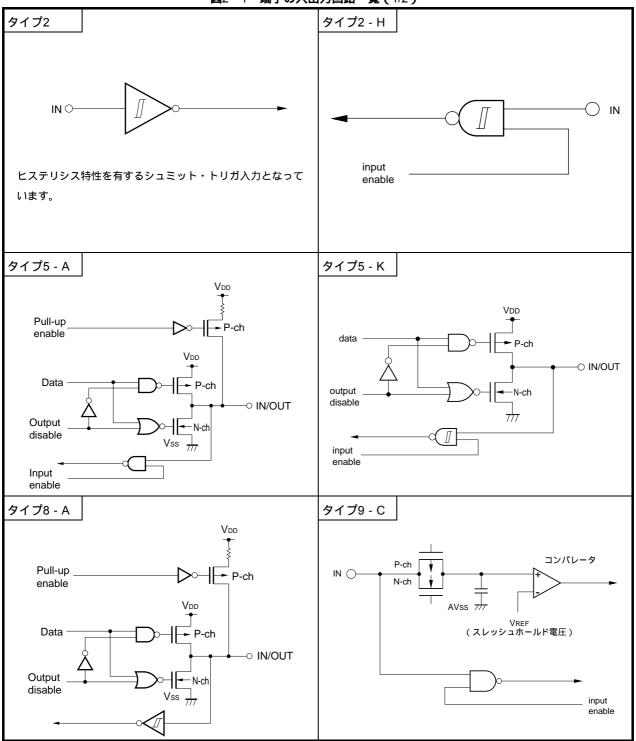

| 2 - 1  | 端子の入出力回路一覧 45                           |

|        |                                         |

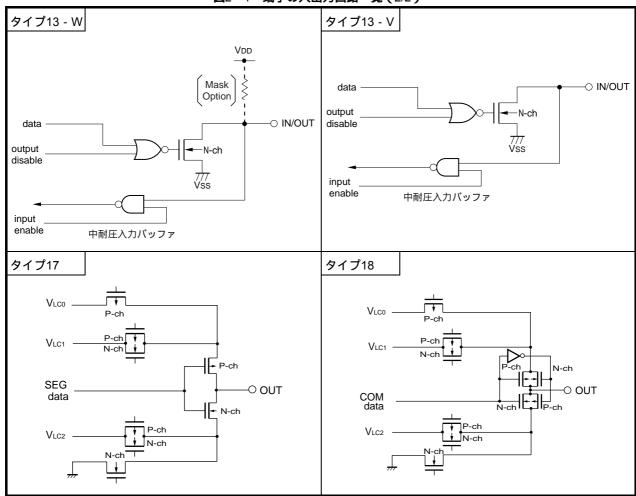

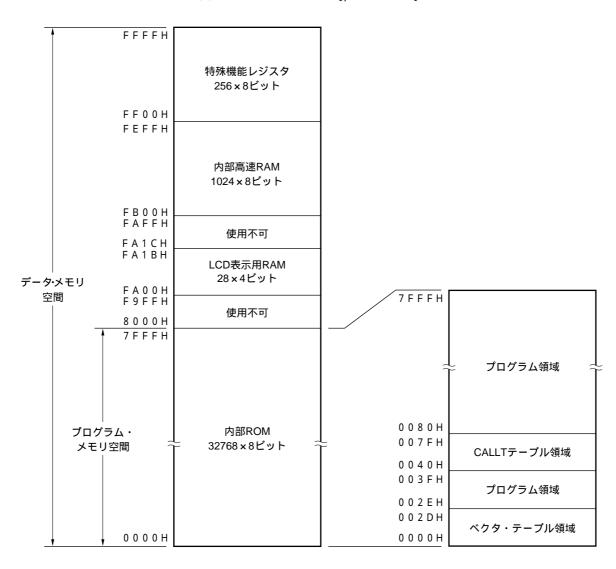

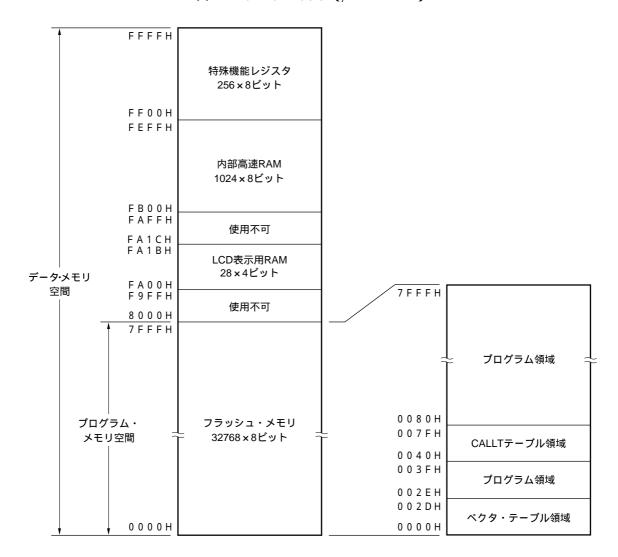

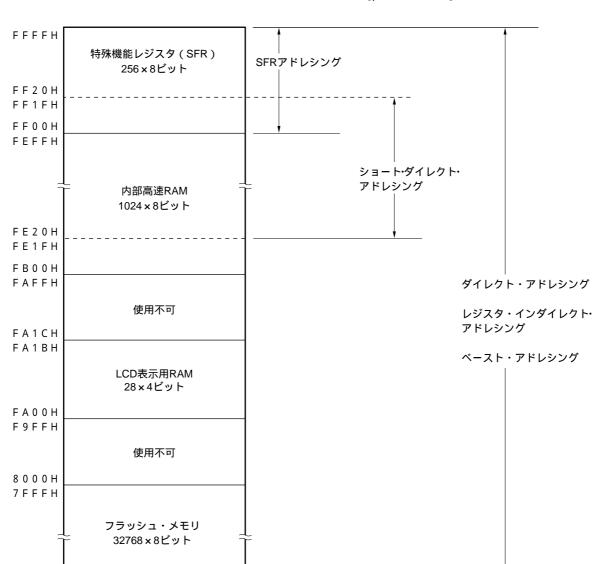

| 3 - 1  | メモリ・マップ (μPD789488) 47                  |

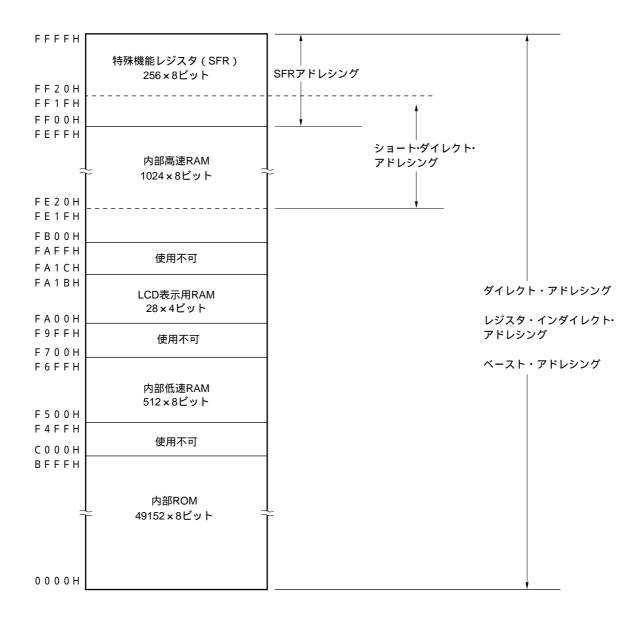

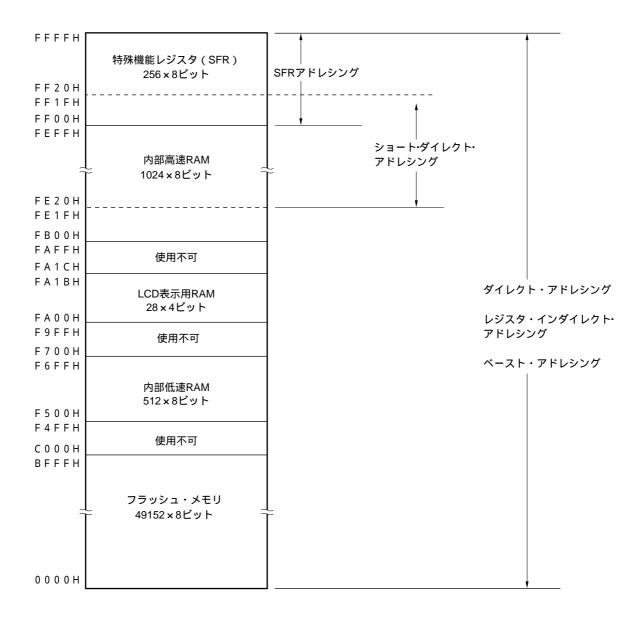

| 3 - 2  | メモリ・マップ (μPD78F9488) 48                 |

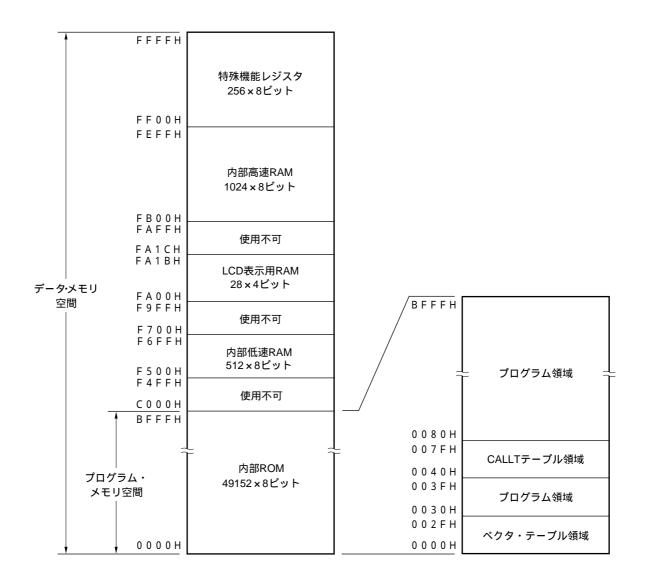

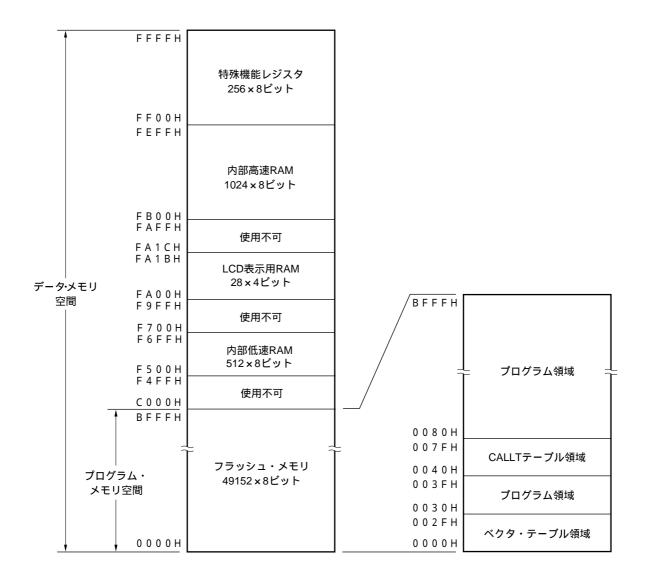

| 3 - 3  | メモリ・マップ (μPD789489) 49                  |

| 3 - 4  | メモリ・マップ(μPD78F9489) 50                  |

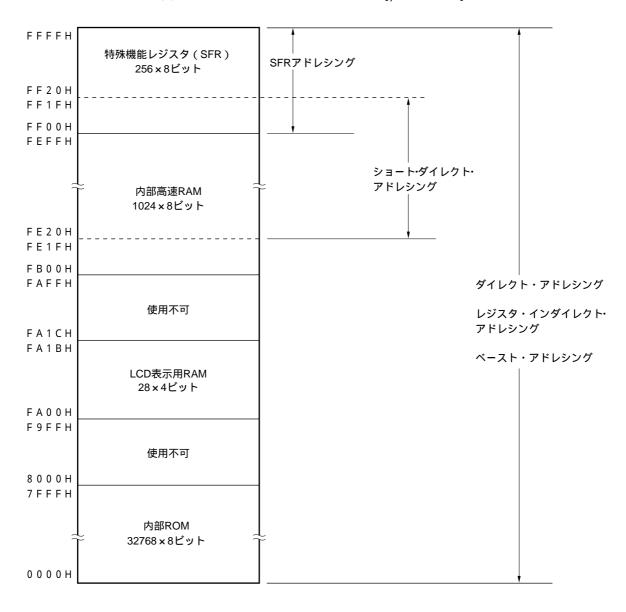

| 3 - 5  | データ・メモリのアドレシング( $\mu$ PD789488) 53      |

| 3 - 6  | データ・メモリのアドレシング( $\mu$ PD78F9488) 54     |

| 3 - 7  | データ・メモリのアドレシング( $\mu$ PD789489) 55      |

| 3 - 8  | データ・メモリのアドレシング( $\mu$ PD78F9489) 56     |

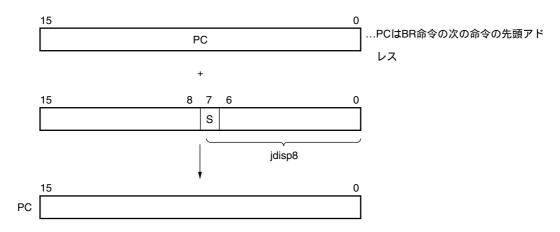

| 3 - 9  | プログラム・カウンタの構成 57                        |

| 3 - 10 | プログラム・ステータス・ワードの構成 57                   |

| 3 - 11 | スタック・ポインタの構成 59                         |

| 3 - 12 | スタック・メモリへ退避されるデータ 59                    |

| 3 - 13 | スタック・メモリから復帰されるデータ 59                   |

| 3 - 14 | 汎用レジスタの構成 60                            |

|        |                                         |

| 4 - 1  | ポートの種類 74                               |

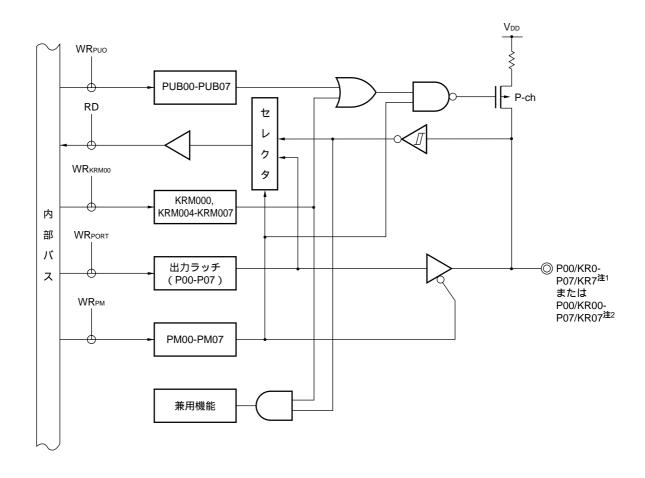

| 4 - 2  | P00-P07のブロック図 76                        |

| 4 - 3  | P10, P11のブロック図 77                       |

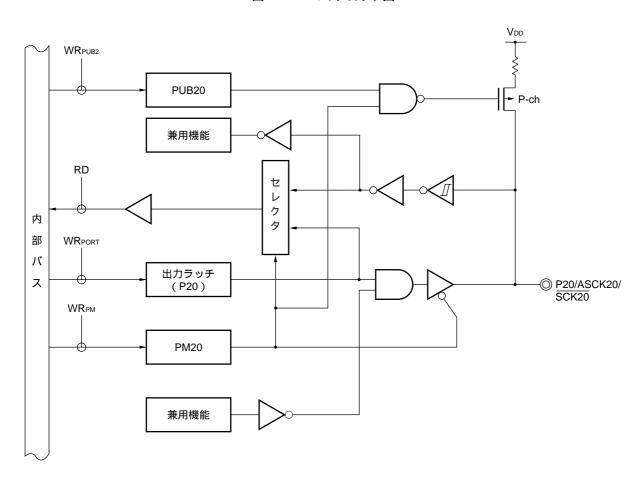

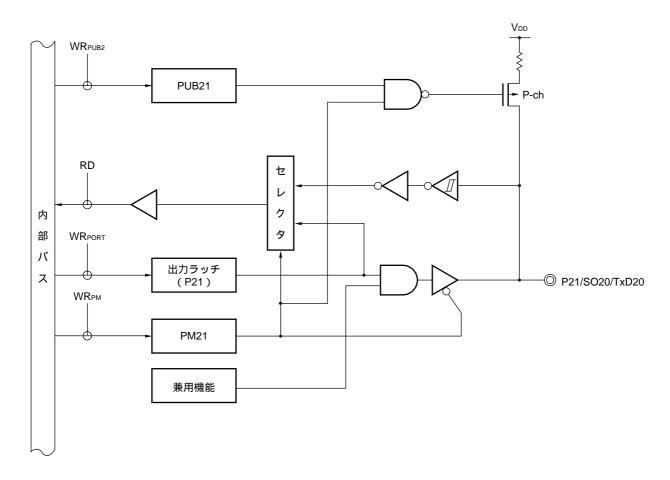

| 4 - 4  | P20のブロック図 78                            |

| 4 - 5  | P21のブロック図 79                            |

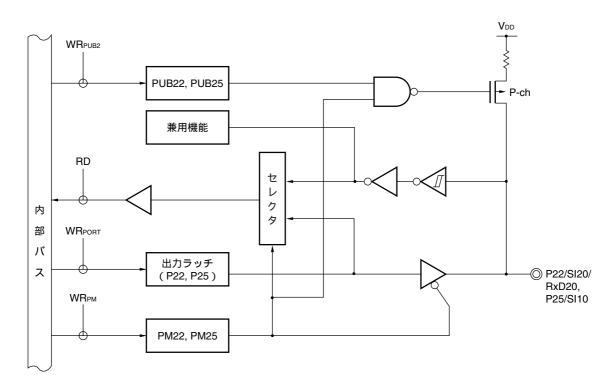

| 4 - 6  | P22, P25のブロック図 80                       |

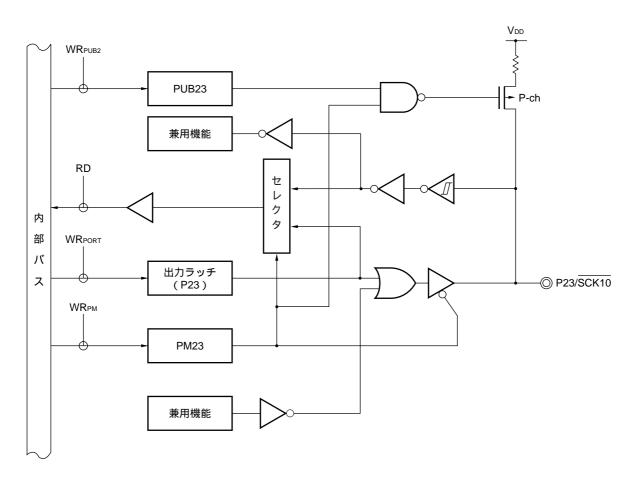

| 4 - 7  | P23のブロック図 81                            |

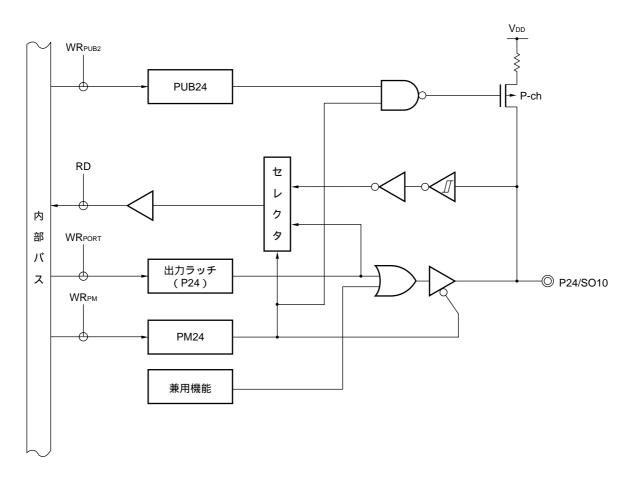

| 4 - 8  | P24のブロック図 82                            |

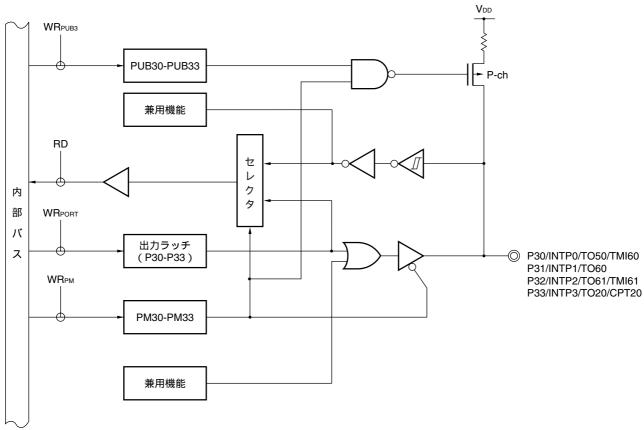

| 4 - 9  | P30-P33のブロック図 83                        |

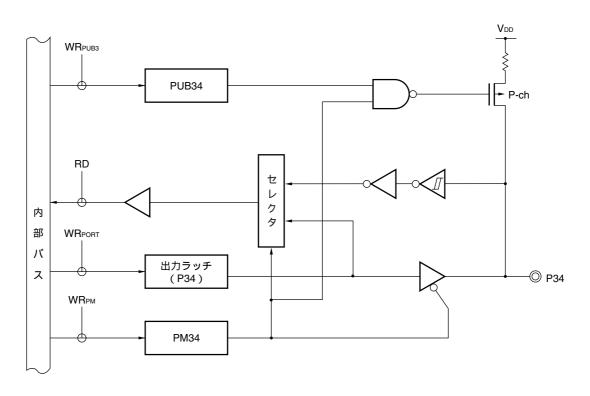

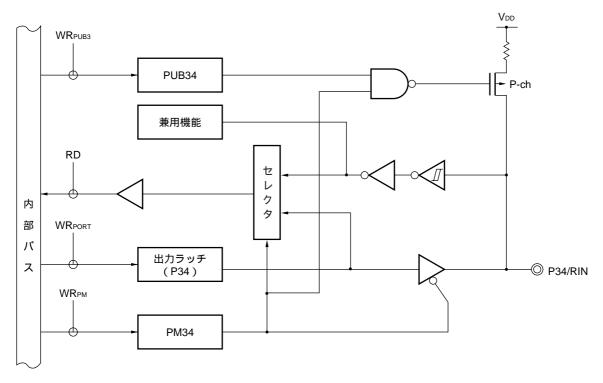

| 4 - 10 | P34のブロック図 84                            |

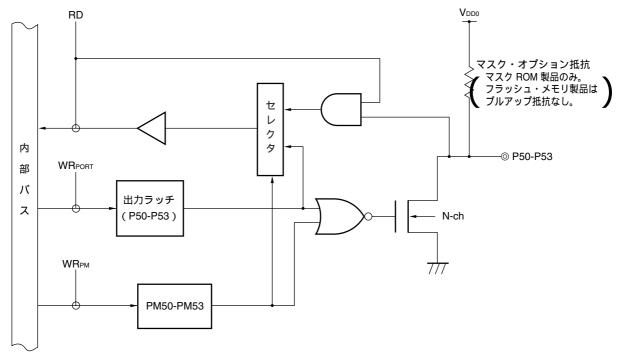

| 4 - 11 | P50-P53のブロック図 85                        |

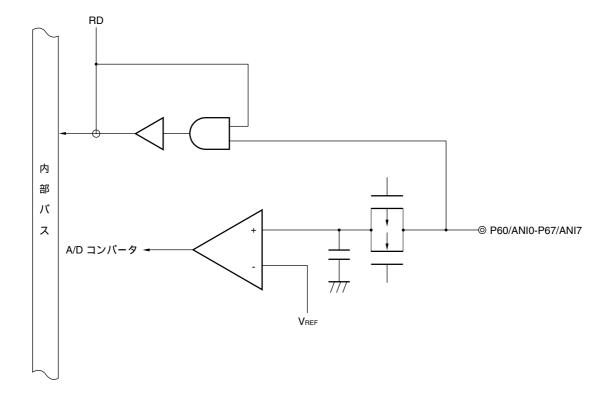

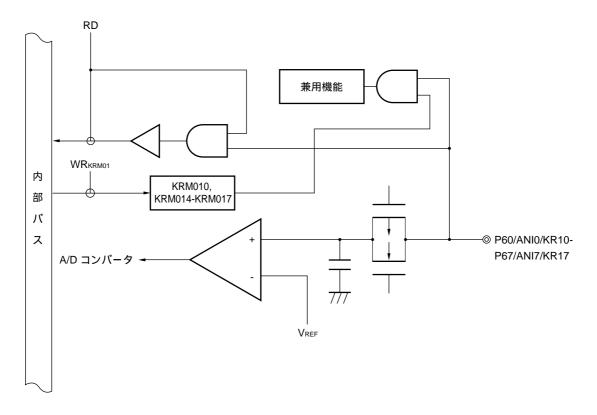

| 4 - 12 | P60-P67のブロック図 86                        |

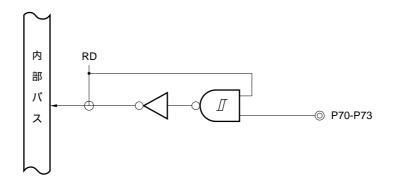

| 4 - 13 | P70-P73のブロック図 88                        |

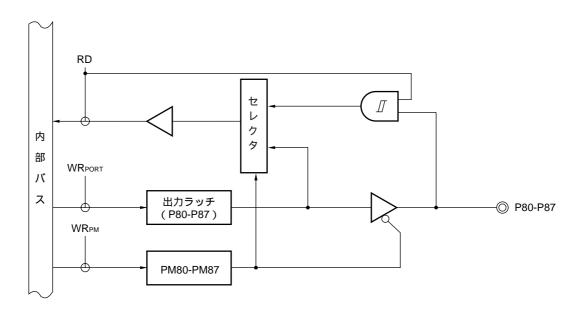

| 4 - 14 | P80-P87のブロック図 89                        |

| 4 - 15 | ポート・モード・レジスタのフォーマット 90                  |

| 4 - 16 | プルアップ抵抗オプション・レジスタのフォーマット 92             |

| 4 - 17 | ポート・ファンクション・レジスタのフォーマット 92              |

|        |                                         |

| 5 - 1  | クロック発生回路のブロック図(μ PD789488, 789489) 95   |

| 5 - 2  | クロック発生回路のブロック図(μ PD78F9488, 78F9489) 96 |

| 5 - 3  | プロセッサ・クロック・コントロール・レジスタのフォーマット 97        |

| 5 - 4  | サプ発振モード・レジスタのフォーマット 98                  |

# 図の目次 (2/6)

| 図番号    | タイトル , ページ                                           |

|--------|------------------------------------------------------|

| 5 - 5  | サブクロック・コントロール・レジスタのフォーマット 98                         |

| 5 - 6  | サブクロック選択レジスタのフォーマット 99                               |

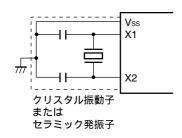

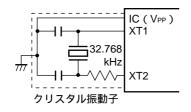

| 5 - 7  | メイン・システム・クロック発振回路の外付け回路 100                          |

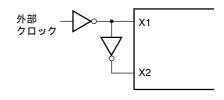

| 5 - 8  | サプシステム・クロック発振回路の外付け回路 101                            |

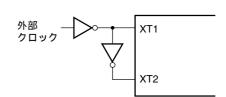

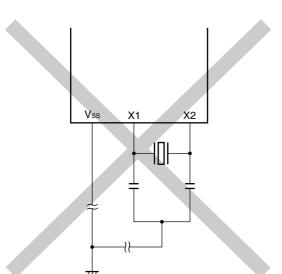

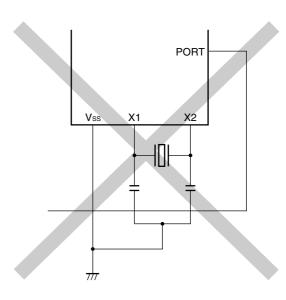

| 5 - 9  | 発振子の接続の悪い例 102                                       |

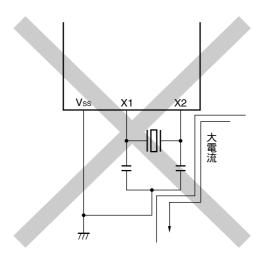

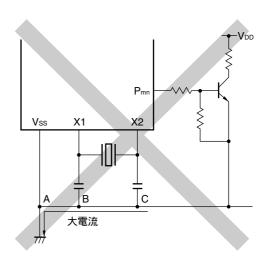

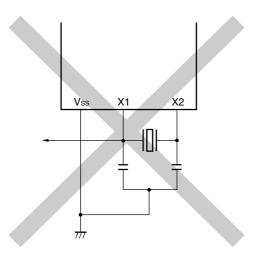

| 5 - 10 | システム・クロックとCPUクロックの切り替え 106                           |

|        |                                                      |

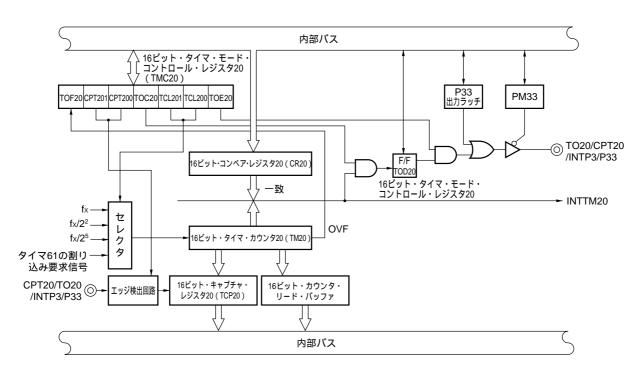

| 6 - 1  | 16ビット・タイマ20のブロック図 108                                |

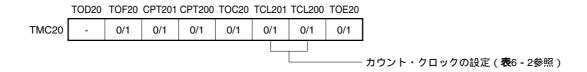

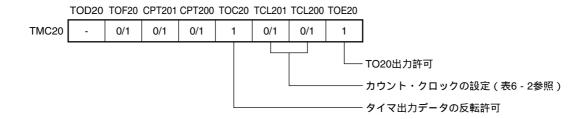

| 6 - 2  | 16ビット・タイマ・モード・コントロール・レジスタ20のフォーマット 110               |

| 6 - 3  | ポート・モード・レジスタ3のフォーマット 111                             |

| 6 - 4  | タイマ割り込み動作時の16ビット・タイマ・モード・コントロール・レジスタ20の設定内容          |

|        | 112                                                  |

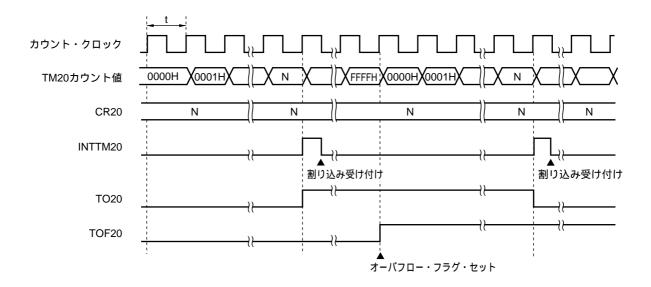

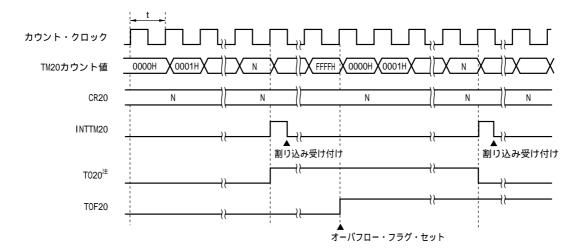

| 6 - 5  | タイマ割り込み動作のタイミング 113                                  |

| 6 - 6  | タイマ出力動作時の16ビット・タイマ・モード・コントロール・レジスタ20の設定内容            |

|        | 114                                                  |

| 6 - 7  | タイマ出力のタイミング 114                                      |

| 6 - 8  | キャプチャ動作時の16ビット・タイマ・モード・コントロール・レジスタ20の設定内容            |

|        | 115                                                  |

| 6 - 9  | キャプチャ動作のタイミング(CPT20端子の両エッジ指定時) 115                   |

| 6 - 10 | 16ビット・タイマ・カウンタ20の読み出しのタイミング 116                      |

|        |                                                      |

| 7 - 1  | 24ビット・イベント・カウンタのブロック図 120                            |

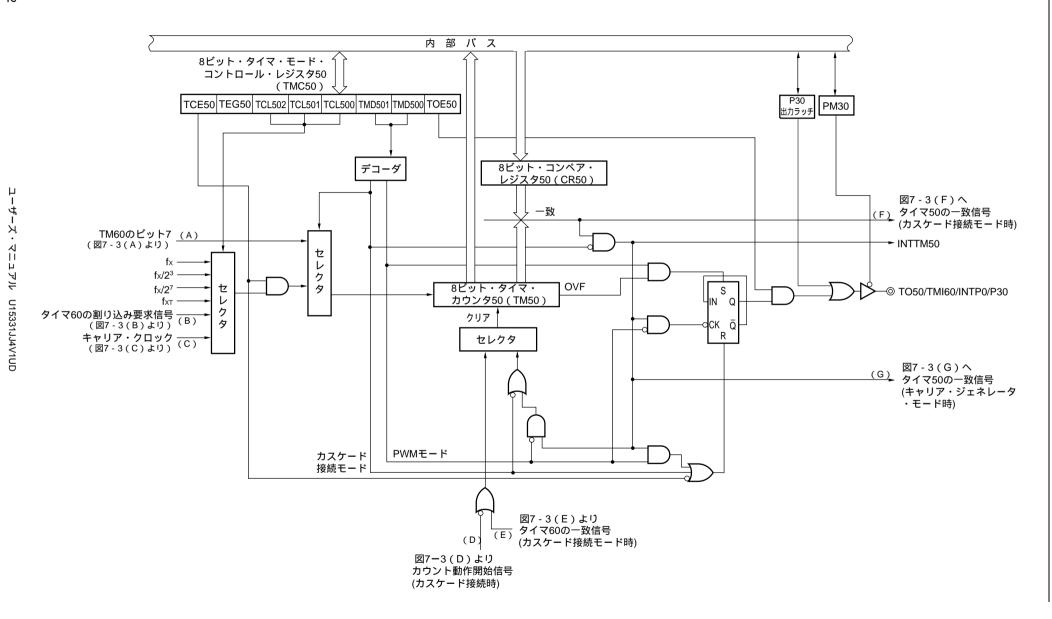

| 7 - 2  | タイマ50のブロック図 122                                      |

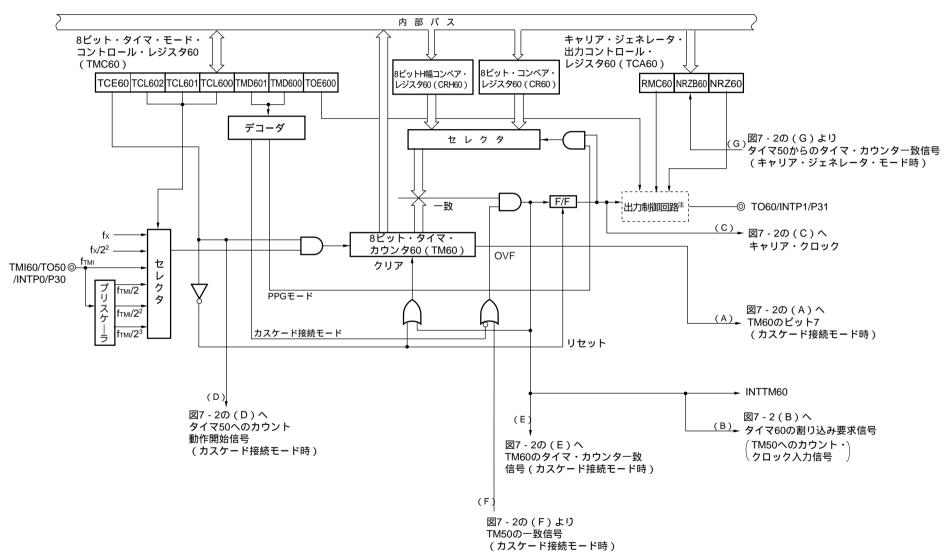

| 7 - 3  | タイマ60のブロック図 123                                      |

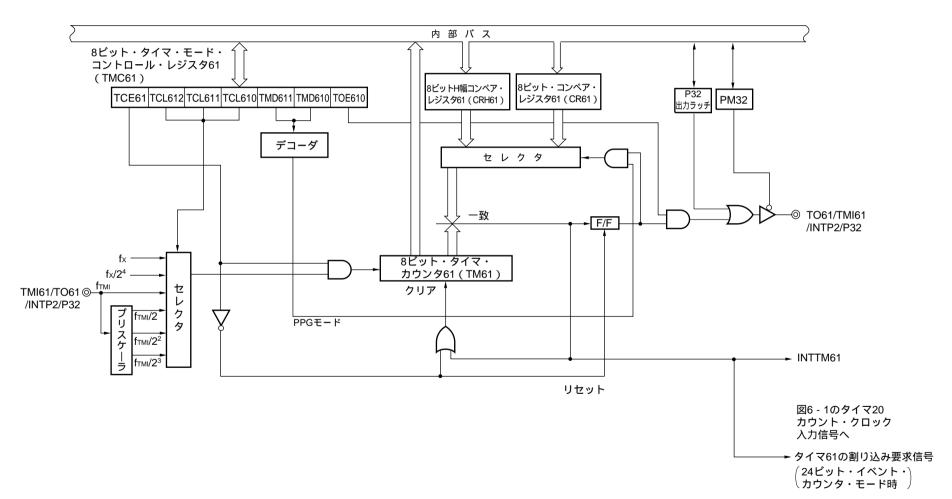

| 7 - 4  | タイマ61のブロック図 124                                      |

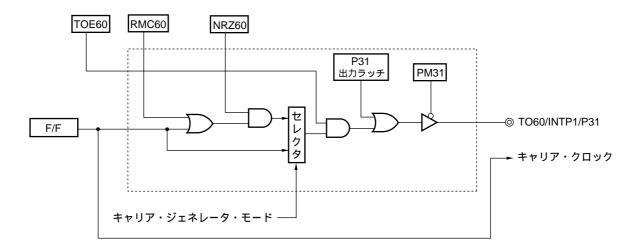

| 7 - 5  | 出力制御回路(タイマ60)のブロック図 125                              |

| 7 - 6  | 8ビット・タイマ・モード・コントロール・レジスタ50のフォーマット 127                |

| 7 - 7  | 8ビット・タイマ・モード・コントロール・レジスタ60のフォーマット 129                |

| 7 - 8  | キャリア・ジェネレータ出力コントロール・レジスタ60のフォーマット 130                |

| 7 - 9  | 8ビット・タイマ・モード・コントロール・レジスタ61のフォーマット 131                |

| 7 - 10 | ポート・モード・レジスタ3のフォーマット 132                             |

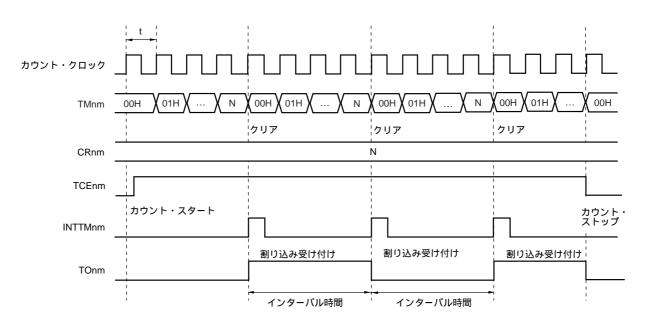

| 7 - 11 | 8ビット分解能のインターバル・タイマ動作のタイミング(基本動作) 135                 |

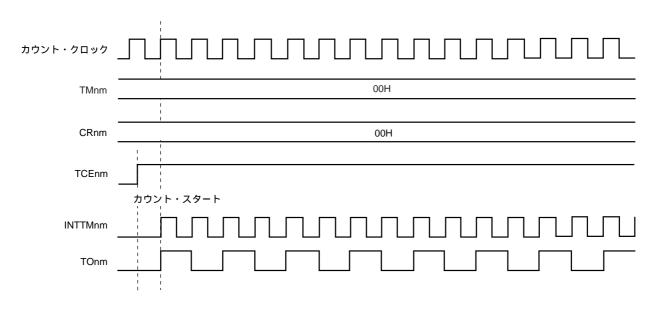

| 7 - 12 | 8ビット分解能のインターバル・タイマ動作のタイミング(CRnm = 00H設定時) 135        |

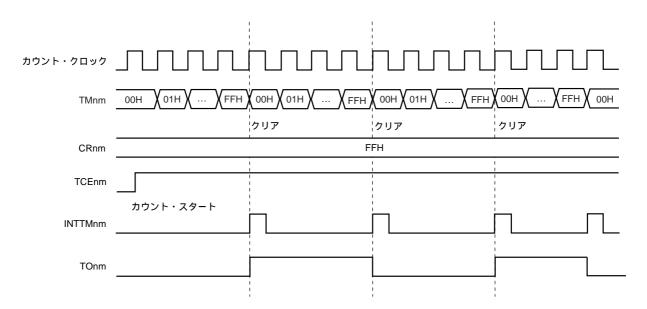

| 7 - 13 | 8ビット分解能のインターバル・タイマ動作のタイミング(CRnm = FFH設定時) 136        |

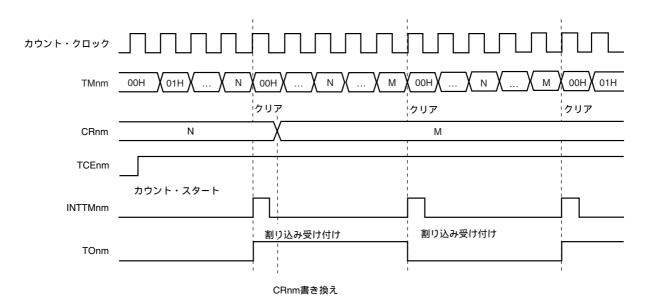

| 7 - 14 | 8ビット分解能のインターバル・タイマ動作のタイミング( $CRnm = N M(N < M)$ 変更時) |

|        | 136                                                  |

| 7 - 15 | 8ビット分解能のインターバル・タイマ動作のタイミング(CRnm = N M(N>M)変更時)       |

|        | 137                                                  |

# 図の目次(3/6)

| 図番号    | タイトル , ページ                                                       |

|--------|------------------------------------------------------------------|

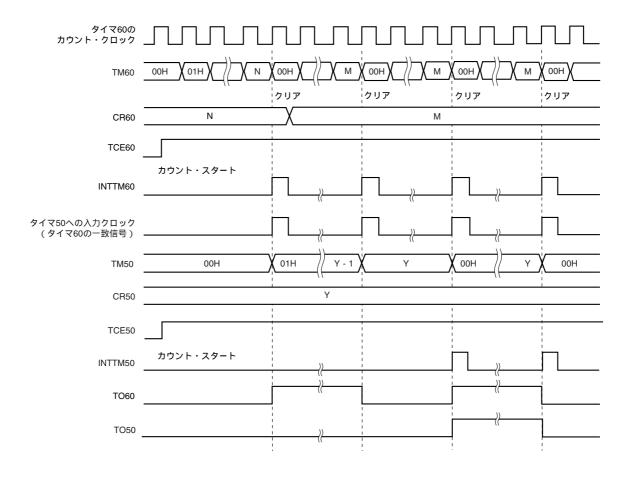

| 7 - 16 | 8ビット分解能のインターバル・タイマ動作のタイミング                                       |

|        | (タイマ50のカウント・クロックにタイマ60一致信号選択時) 137                               |

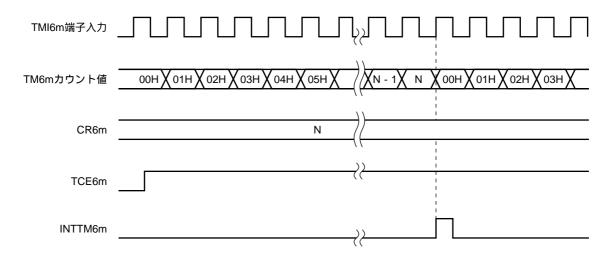

| 7 - 17 | 8ビット分解能の外部イベント・カウンタ動作のタイミング 138                                  |

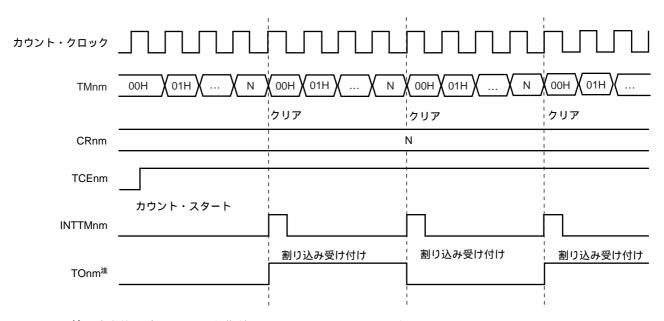

| 7 - 18 | 8ビット分解能の方形波出力のタイミング 140                                          |

| 7 - 19 | 16ビット分解能のインターバル・タイマ動作のタイミング 143                                  |

| 7 - 20 | 16ビット分解能の外部イベント・カウンタ動作のタイミング 145                                 |

| 7 - 21 | 16ビット分解能の方形波出力のタイミング 147                                         |

| 7 - 22 | キャリア・ジェネレータの動作タイミング( CR60 = N, CRH60 = M( M > N )設定時) 149        |

| 7 - 23 | キャリア・ジェネレータの動作タイミング( CR60 = N, CRH60 = M( M < N )設定時) 150        |

| 7 - 24 | キャリア・ジェネレータの動作タイミング(CR60 = CRH60 = N設定時) 151                     |

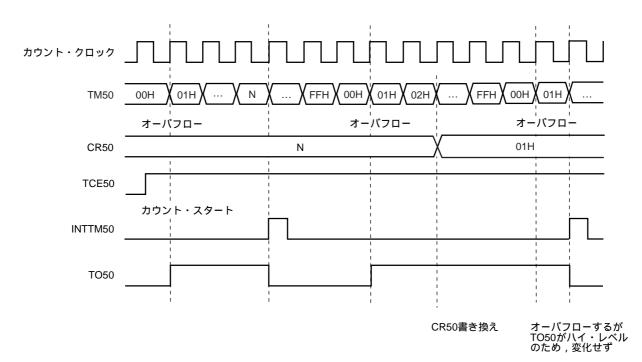

| 7 - 25 | PWM出力モード動作時の動作タイミング(立ち上がりエッジ選択時) 152                             |

| 7 - 26 | CR50書き換え時の動作タイミング(立ち上がりエッジ選択時) 153                               |

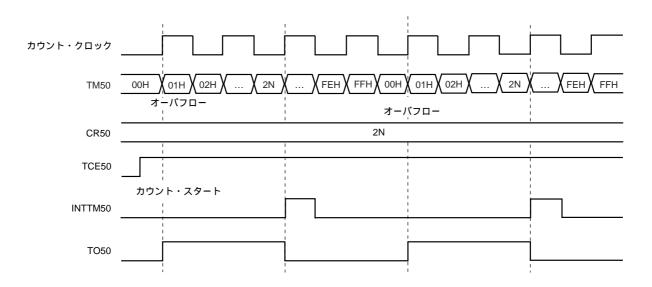

| 7 - 27 | PWM出力モード動作時の動作タイミング(両エッジ選択時) 154                                 |

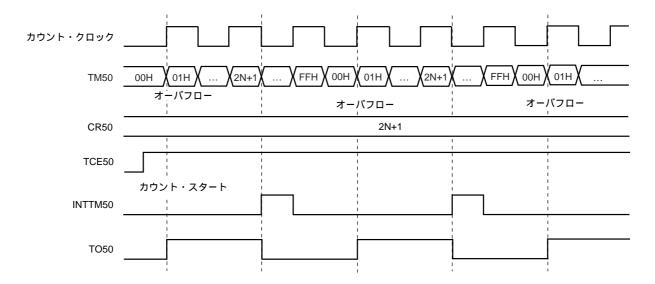

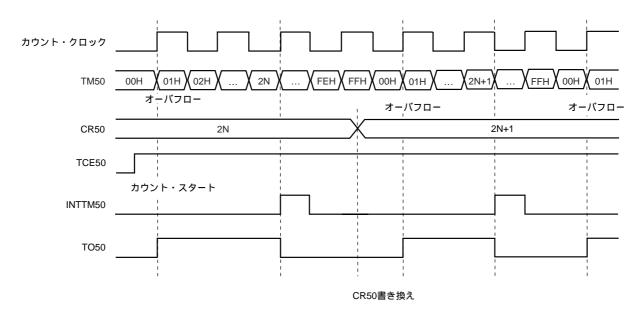

| 7 - 28 | PWM出力モード動作時の動作タイミング(両エッジ選択時)(CR50を書き換えた場合)<br>155                |

| 7 - 29 | 155<br>PPG出力モードのタイミング(基本動作) 157                                  |

| 7 - 29 | PPG出力モードのタイミング(基本動作) 157 PPG出力モードのタイミング(CR6m, CRH6mを書き換えた場合) 157 |

| 7 - 31 | 1.5クロック (最大) の誤差が出るケース 158                                       |

| 7 - 32 | 外部イベント・カウンタとしての動作時のタイミング(8ビット分解能時) 158                           |

| 7 02   |                                                                  |

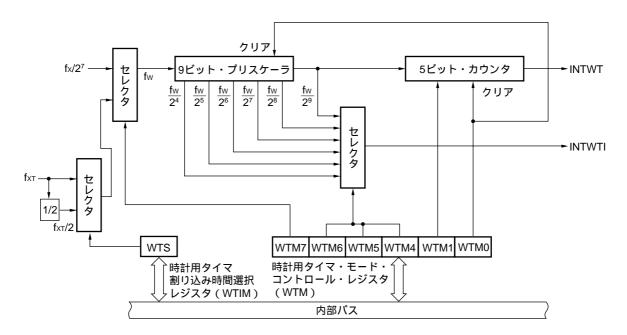

| 8 - 1  | 時計用タイマのブロック図 159                                                 |

| 8 - 2  | 時計用タイマ・モード・コントロール・レジスタのフォーマット 161                                |

| 8 - 3  | 時計用タイマ割り込み時間選択レジスタのフォーマット 162                                    |

| 8 - 4  | 時計用タイマ / インターバル・タイマの動作タイミング 164                                  |

|        |                                                                  |

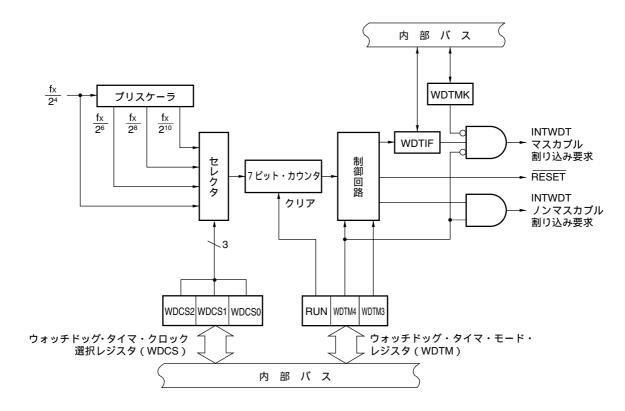

| 9 - 1  | ウォッチドッグ・タイマのブロック図 166                                            |

| 9 - 2  | ウォッチドッグ・タイマ・クロック選択レジスタのフォーマット 167                                |

| 9 - 3  | ウォッチドッグ・タイマ・モード・レジスタのフォーマット 168                                  |

|        |                                                                  |

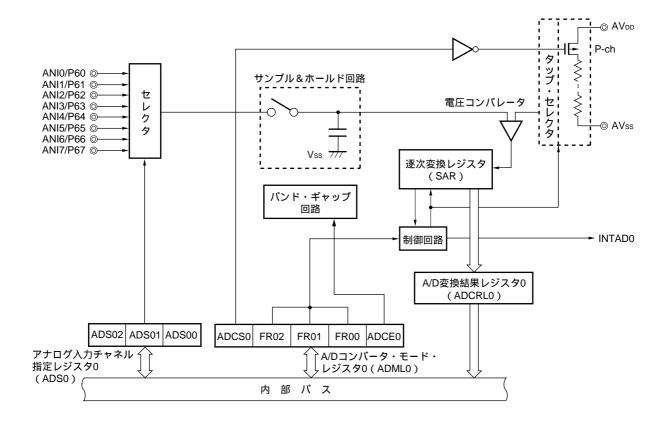

| 10 - 1 | 10ビットA/Dコンバータのブロック図 172                                          |

| 10 - 2 | A/Dコンバータ・モード・レジスタ0のフォーマット 174                                    |

| 10 - 3 | アナログ入力チャネル指定レジスタ0のフォーマット 175                                     |

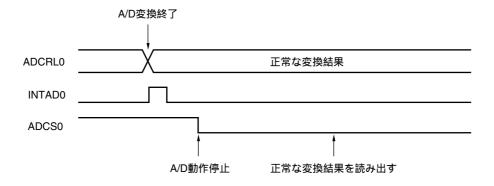

| 10 - 4 | 10ビットA/Dコンバータの基本動作 177                                           |

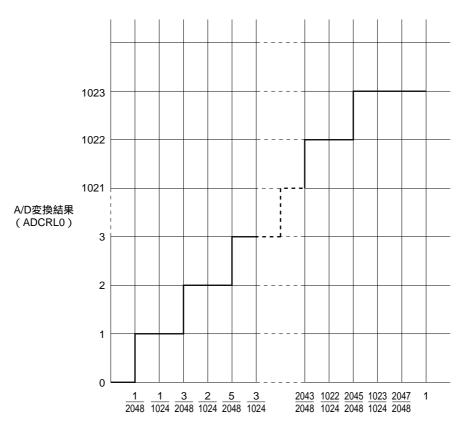

| 10 - 5 | アナログ入力電圧とA/D変換結果の関係 178                                          |

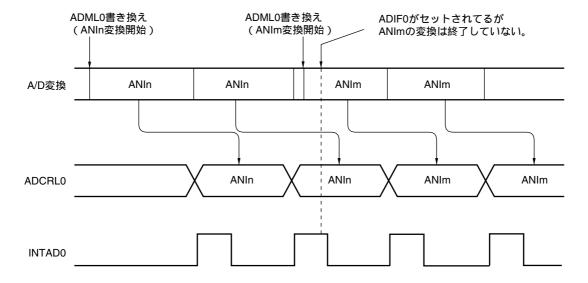

| 10 - 6 | ソフトウエア・スタートによるA/D変換動作 179                                        |

| 10 - 7 | スタンバイ・モード時の消費電流を低減させる方法例 180                                     |

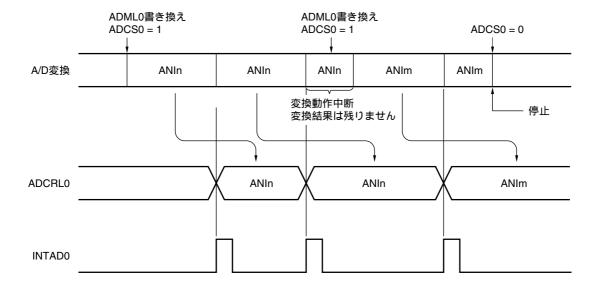

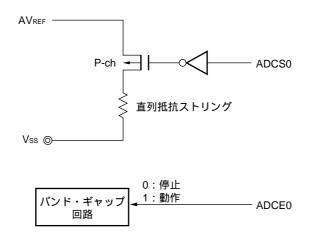

| 10 - 8 | 変換結果を読み出すタイミング(変換結果が不定値の場合) 181                                  |

# 図の目次 (4/6)

|   | <b>.</b> | <b>5 7 1 11 20 2 2 2</b>                 |     |

|---|----------|------------------------------------------|-----|

| - | 図番号      | タイトル,ページ                                 |     |

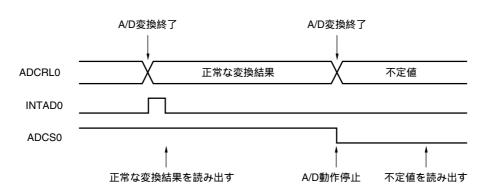

|   |          | 変換結果を読み出すタイミング(変換結果が正常値の場合) 181          |     |

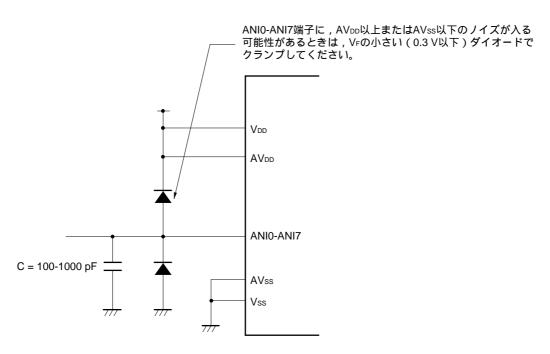

|   |          | アナログ入力端子の処理 182                          |     |

|   |          | A/D変換終了割り込み要求発生タイミング 183                 |     |

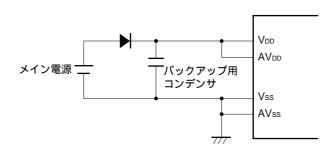

|   | 10 - 12  | AVDD端子の処理 183                            |     |

|   |          |                                          |     |

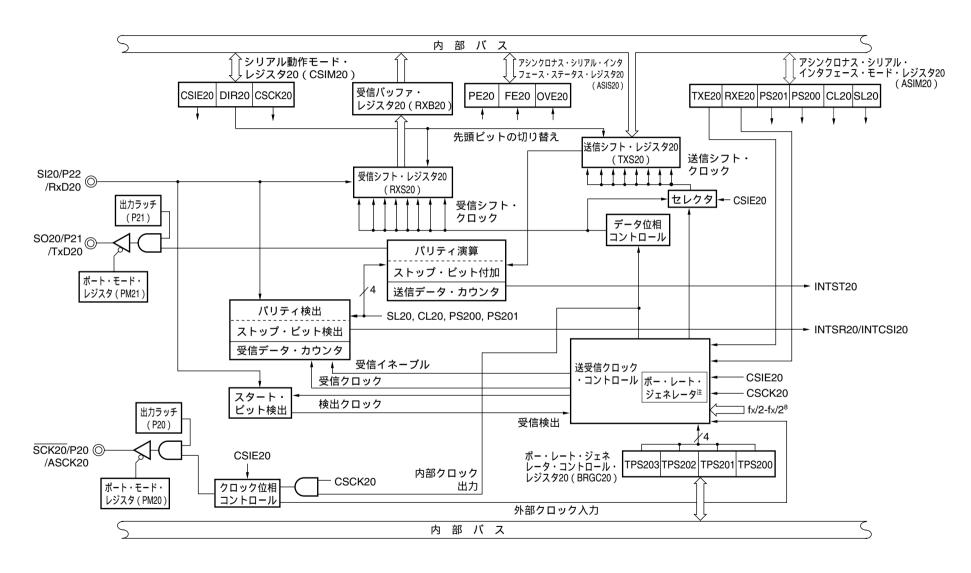

|   | 11 - 1   | シリアル・インタフェース20のブロック図 185                 |     |

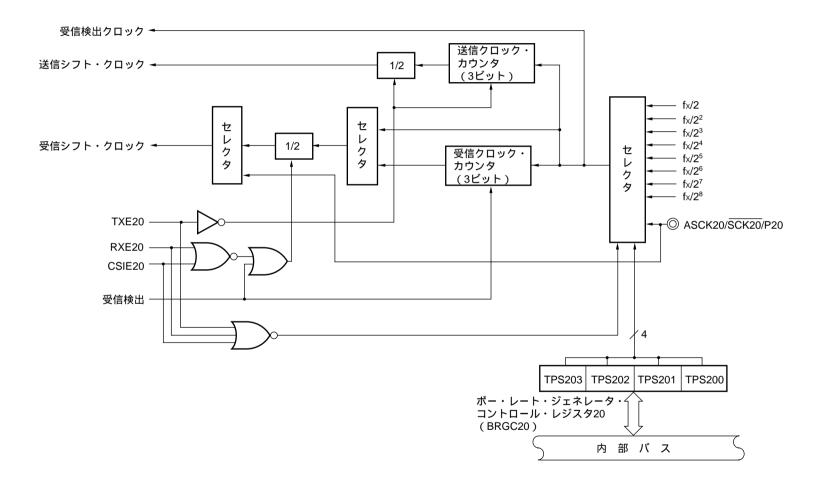

|   | 11 - 2   | ボー・レート・ジェネレータ20のブロック図 186                |     |

|   | 11 - 3   | シリアル動作モード・レジスタ20のフォーマット 188              |     |

|   | 11 - 4   | アシンクロナス・シリアル・インタフェース・モード・レジスタ20のフォーマット   | 189 |

|   | 11 - 5   | アシンクロナス・シリアル・インタフェース・ステータス・レジスタ20のフォーマット |     |

|   |          | 191                                      |     |

|   | 11 - 6   | ボー・レート・ジェネレータ・コントロール・レジスタ20のフォーマット 192   |     |

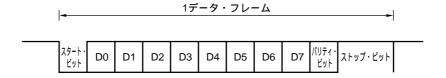

|   | 11 - 7   | アシンクロナス・シリアル・インタフェースの送受信データのフォーマット 202   |     |

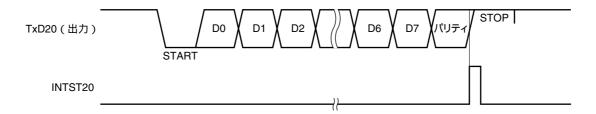

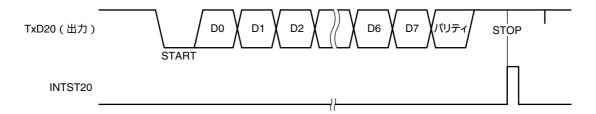

|   | 11 - 8   | アシンクロナス・シリアル・インタフェース送信完了割り込みタイミング 204    |     |

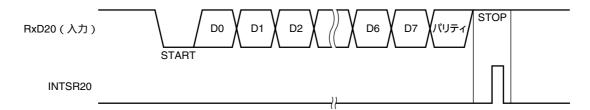

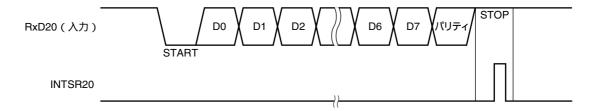

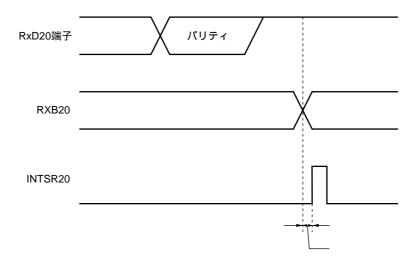

|   | 11 - 9   | アシンクロナス・シリアル・インタフェース受信完了割り込みタイミング 205    |     |

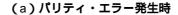

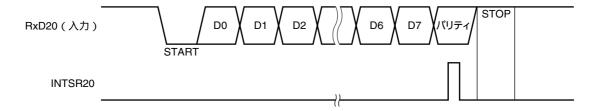

|   | 11 - 10  | 受信エラー・タイミング 206                          |     |

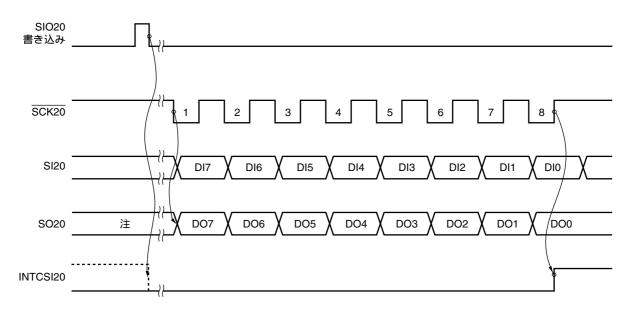

|   | 11 - 11  | 3線式シリアルI/Oモードのタイミング 212                  |     |

|   |          |                                          |     |

|   | 12 - 1   | シリアル・インタフェース1A0のブロック図 215                |     |

|   | 12 - 2   | シリアル動作モード・レジスタ1A0のフォーマット 218             |     |

|   | 12 - 3   | 自動データ送受信コントロール・レジスタ0のフォーマット 219          |     |

|   | 12 - 4   | 自動データ送受信転送間隔指定レジスタ0のフォーマット 220           |     |

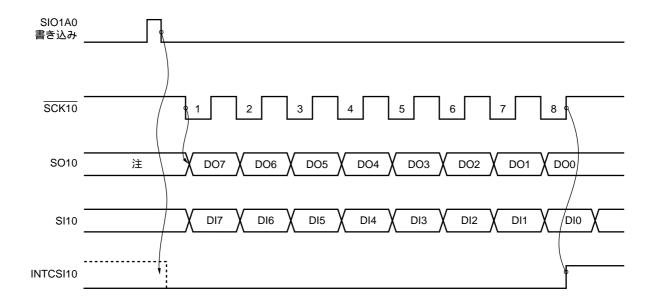

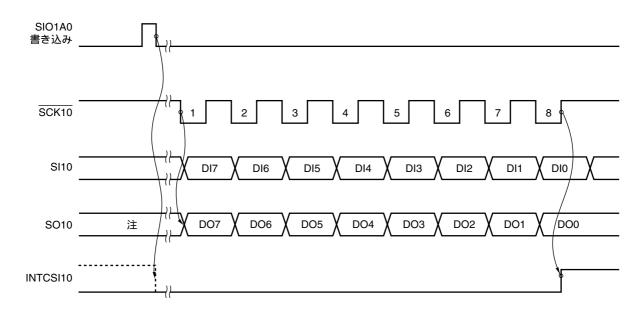

|   | 12 - 5   | 3線式シリアルI/Oモードのタイミング 225                  |     |

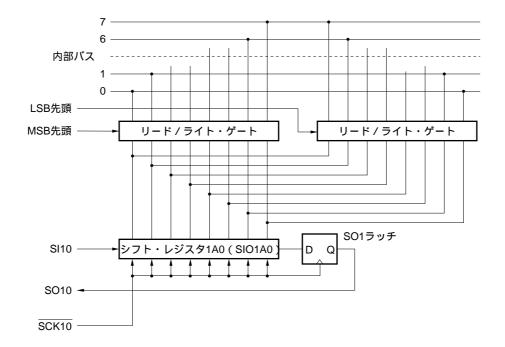

|   | 12 - 6   | 転送ビット順切り替え回路 227                         |     |

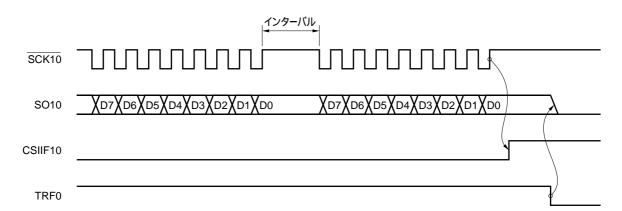

|   | 12 - 7   | 基本送受信モードの動作タイミング 234                     |     |

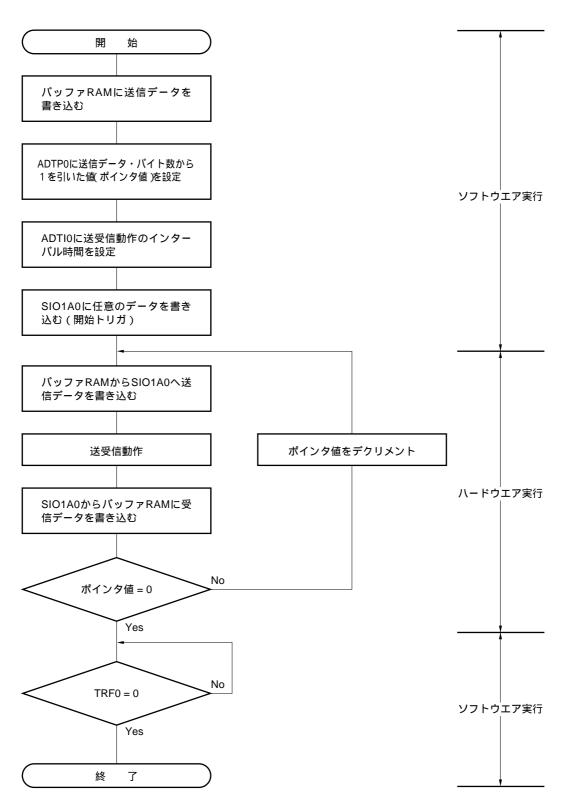

|   | 12 - 8   | 基本送受信モードのフロー・チャート 235                    |     |

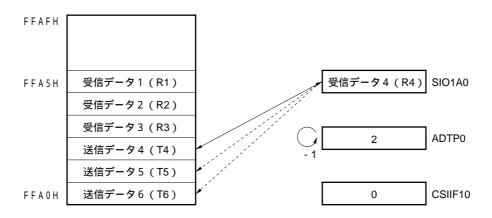

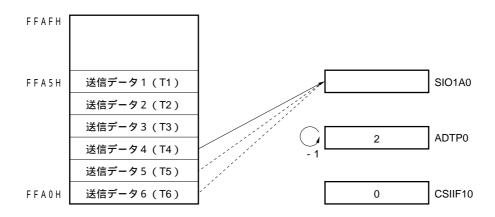

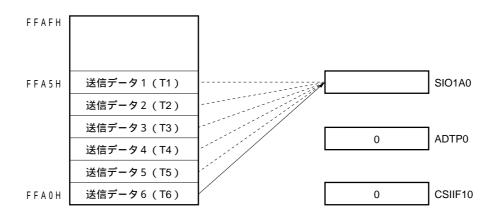

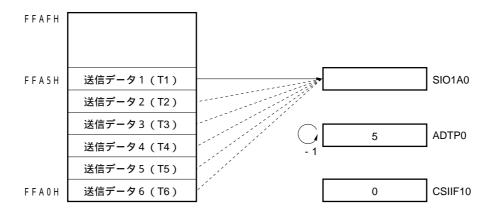

|   | 12 - 9   | 6バイト分送受信するときのバッファRAMの動作(基本送受信モード時) 236   |     |

|   | 12 - 10  | 基本送信モードの動作タイミング 238                      |     |

|   | 12 - 11  | 基本送信モードのフロー・チャート 239                     |     |

|   | 12 - 12  | 6バイト分送信するときのバッファRAMの動作(基本送信モード時) 240     |     |

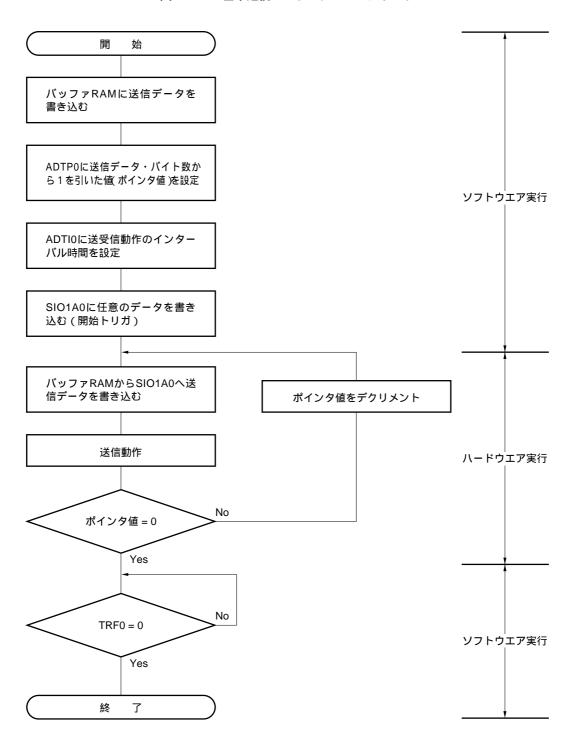

|   | 12 - 13  | 繰り返し送信モードの動作タイミング 242                    |     |

|   | 12 - 14  | 繰り返し送信モードのフロー・チャート 243                   |     |

|   | 12 - 15  | 6バイト分送信するときのバッファRAMの動作(繰り返し送信モード時) 244   |     |

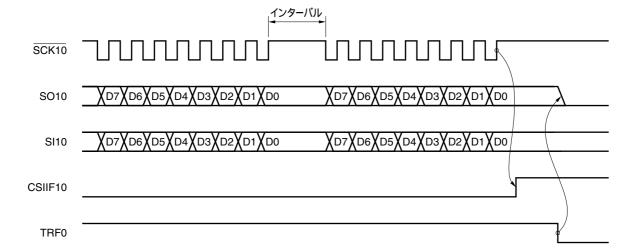

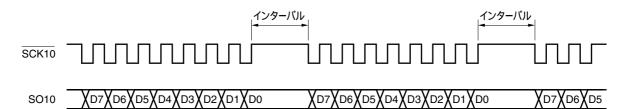

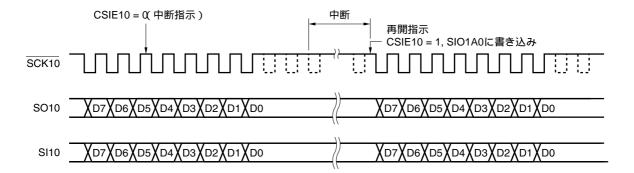

|   | 12 - 16  | 自動送受信の中断と再開 246                          |     |

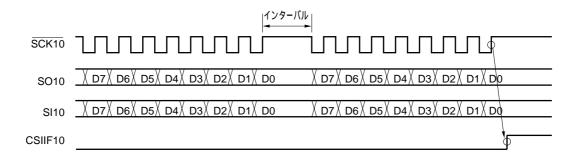

|   | 12 - 17  | 自動送受信のインターバル時間 247                       |     |

|   |          |                                          |     |

|   | 13 - 1   | LCD表示用RAMとの対応 249                        |     |

|   | 13 - 2   | LCDコントローラ / ドライバのブロック図 250               |     |

|   | 13 - 3   | LCD表示モード・レジスタ0のフォーマット 252                |     |

|   |          |                                          |     |

# 図の目次 (5/6)

| 図番号     | タイトル , ページ                                                    |

|---------|---------------------------------------------------------------|

| 13 - 4  | LCDクロック制御レジスタ0のフォーマット 253                                     |

| 13 - 5  | LCD昇圧制御レジスタ0のフォーマット 254                                       |

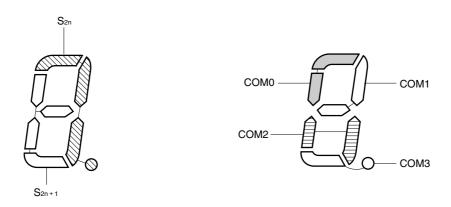

| 13 - 6  | LCD表示データ・メモリの内容とセグメント出力 / コモン出力の関係 (S16-S27を使用した場             |

|         | 合) 255                                                        |

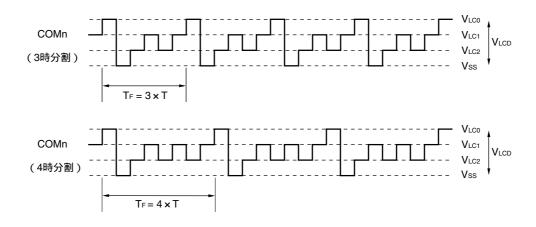

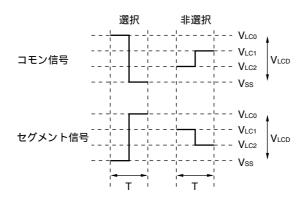

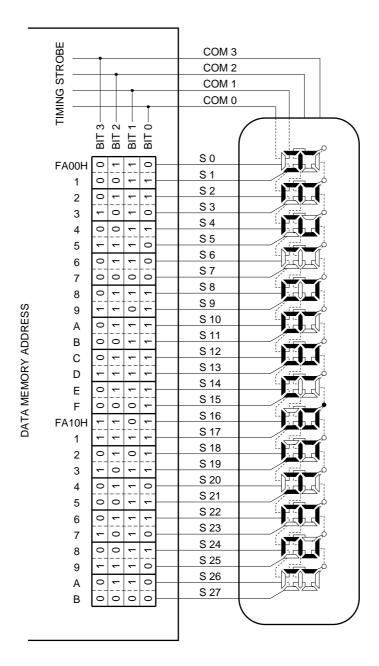

| 13 - 7  | コモン信号波形 257                                                   |

| 13 - 8  | コモン信号とセグメント信号の電圧と位相 257                                       |

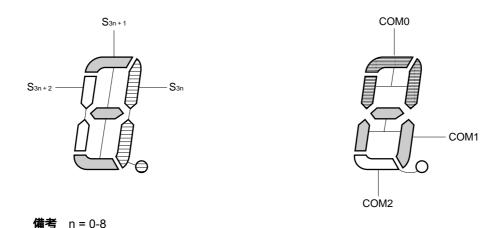

| 13 - 9  | 3時分割LCD表示パターンと電極結線 258                                        |

| 13 - 10 | 3時分割LCDパネルの結線例 259                                            |

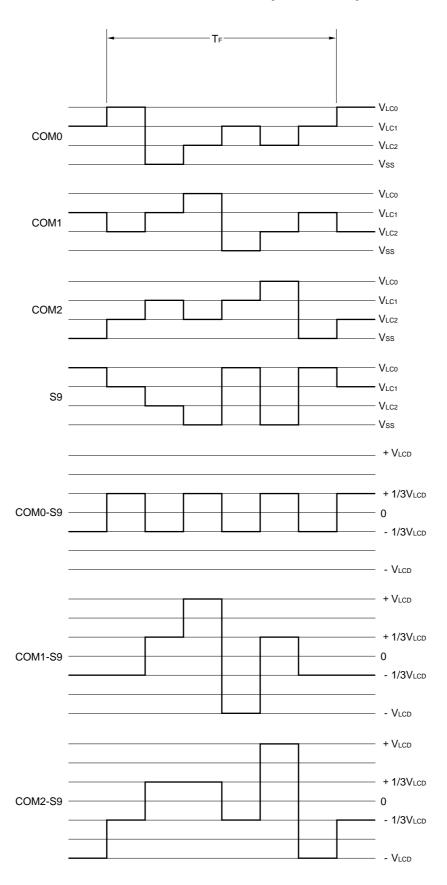

| 13 - 11 | 3時分割LCD駆動波形例(1/3バイアス法) 260                                    |

| 13 - 12 | 4時分割LCD表示パターンと電極結線 261                                        |

| 13 - 13 | 4時分割LCDパネルの結線例 262                                            |

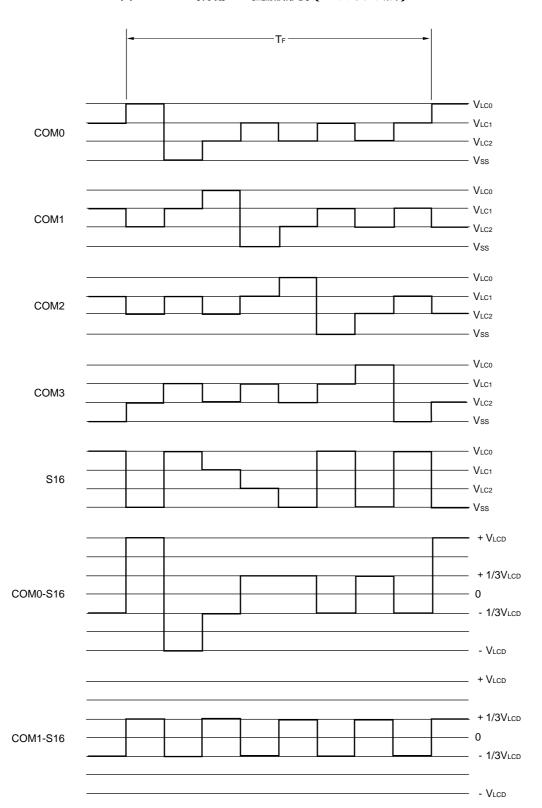

| 13 - 14 | 4時分割LCD駆動波形例(1/3バイアス法) 263                                    |

| 13 - 15 | LCDドライバ用端子接続例 264                                             |

|         |                                                               |

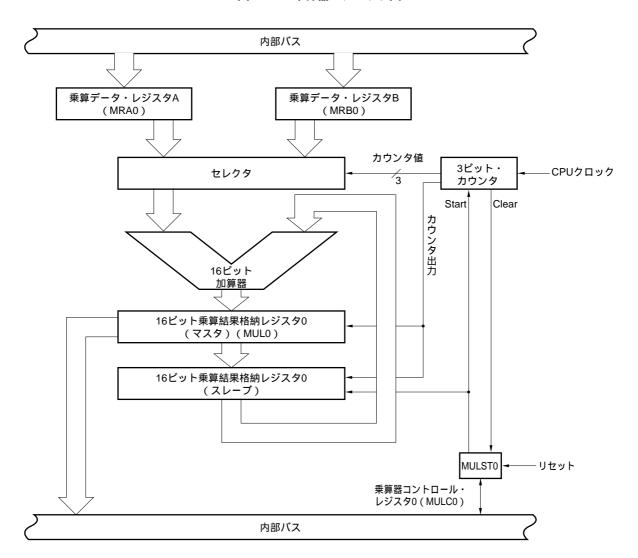

| 14 - 1  | 乗算器のブロック図 266                                                 |

| 14 - 2  | 乗算器コントロール・レジスタ0のフォーマット 267                                    |

| 14 - 3  | 乗算器の動作タイミング(AAH×D3Hの例) 268                                    |

| 45 4    |                                                               |

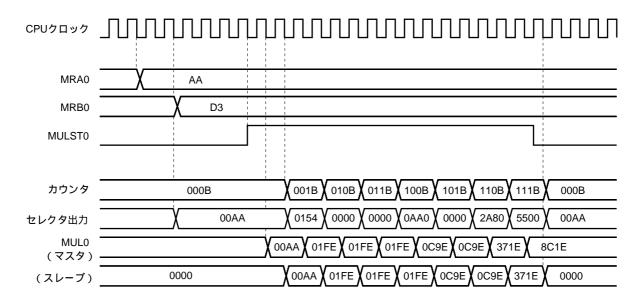

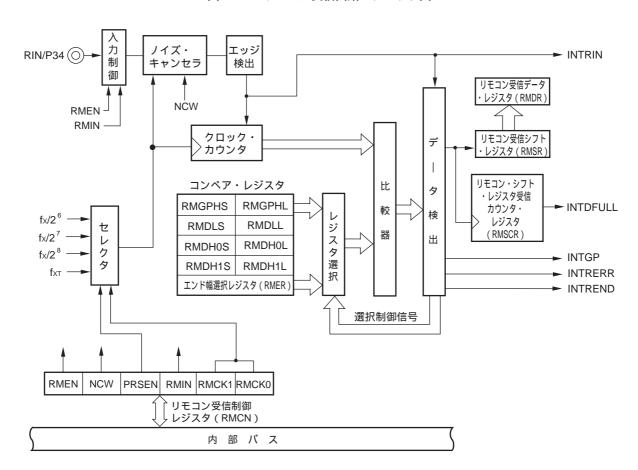

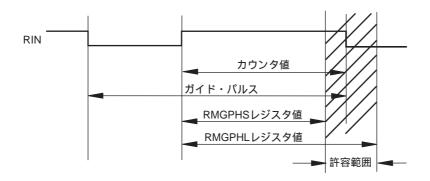

|         | リモコン受信回路のプロック図 270                                            |

| 15 - 2  | 1010101011111111B(16ビット)を受信する場合のRMSR, RMSCR, RMDRレジスタの動作例 271 |

| 15 - 3  | リモコン受信制御レジスタのフォーマット 275                                       |

|         | A方式データ・フォーマット例 277                                            |

|         | A方式受信モードの動作フロー 278                                            |

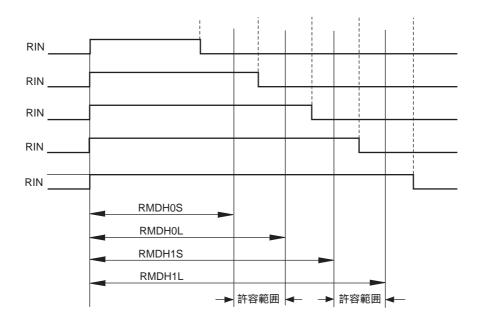

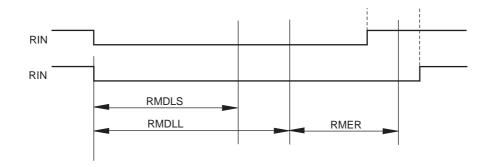

|         | 設定例 (n1 = 1, n2 = 2のとき) 282                                   |

| 15 - 7  | INTRERR信号の発生タイミング 284                                         |

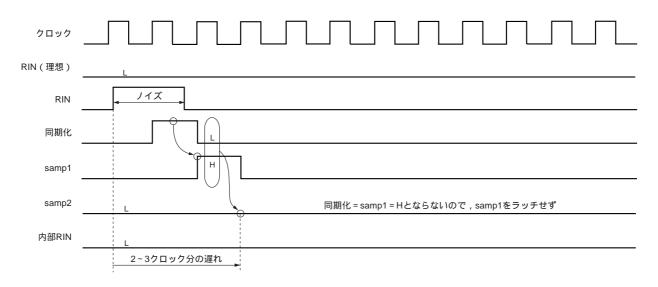

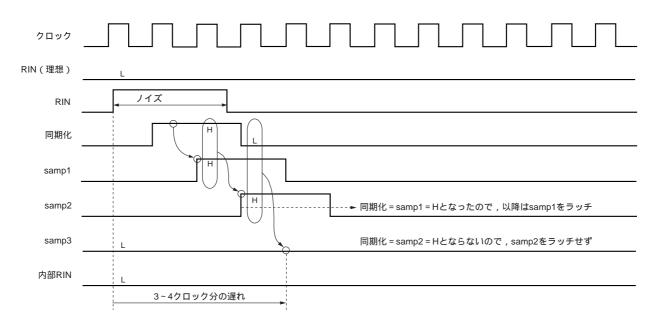

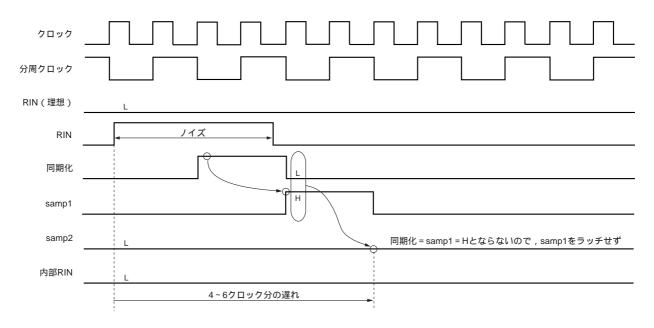

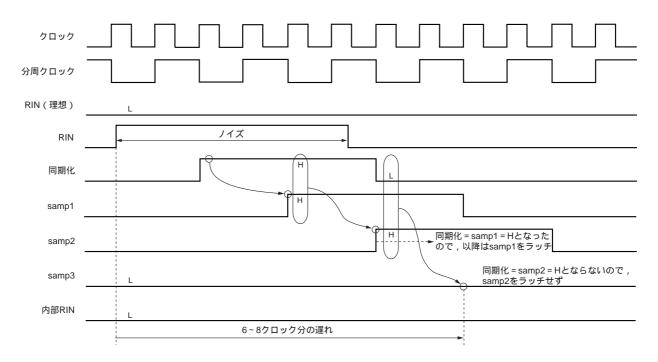

|         | ノイズ・キャンセル動作例 286                                              |

|         |                                                               |

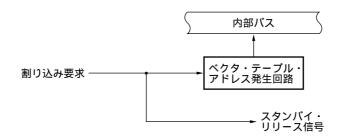

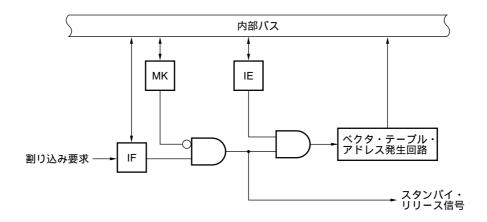

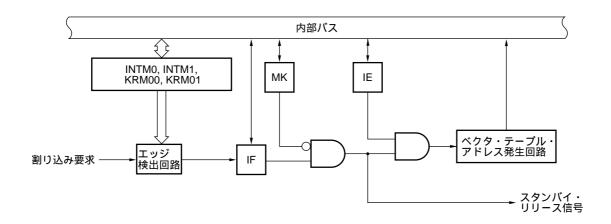

| 16 - 1  | 割り込み機能の基本構成 291                                               |

| 16 - 2  | 割り込み要求フラグ・レジスタのフォーマット 293                                     |

| 16 - 3  | 割り込みマスク・フラグ・レジスタのフォーマット 294                                   |

| 16 - 4  | 外部割り込みモード・レジスタのフォーマット 295                                     |

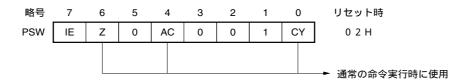

| 16 - 5  | プログラム・ステータス・ワードの構成 296                                        |

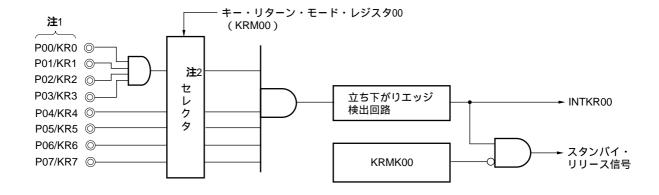

| 16 - 6  | キー・リターン・モード・レジスタ00のフォーマット 297                                 |

| 16 - 7  | 立ち下がりエッジの検出回路のブロック図 297                                       |

| 16 - 8  | キー・リターン・モード・レジスタ01のフォーマット 298                                 |

| 16 - 9  | 立ち下がりエッジの検出回路のブロック図 298                                       |

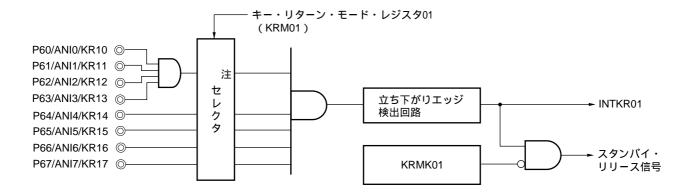

| 16 - 10 | ノンマスカブル割り込み要求発生から受け付けまでのフロー・チャート 300                          |

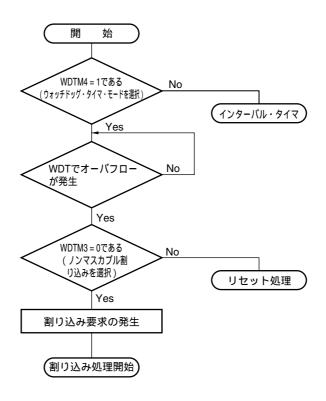

| 16 - 11 | ノンマスカブル割り込み要求の受け付けタイミング 300                                   |

# 図の目次 (6/6)

| 図番号     | タイトル , ページ                                 |

|---------|--------------------------------------------|

|         |                                            |

|         | 割り込み要求受け付け処理アルゴリズム 301                     |

|         | 割り込み要求の受け付けタイミング(MOV A, rの例) 302           |

|         | 割り込み要求の受け付けタイミング(命令実行中の最終クロックで割り込み要求フラグが発生 |

|         | したとき) 302                                  |

| 16 - 16 | 多重割り込みの例 303                               |

|         | 2 Lii 7 20 000                             |

| 17 - 1  | 発振安定時間選択レジスタのフォーマット 306                    |

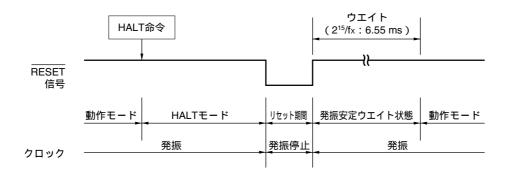

| 17 - 2  | HALTモードの割り込み発生による解除 308                    |

| 17 - 3  | HALTモードのRESET入力による解除 309                   |

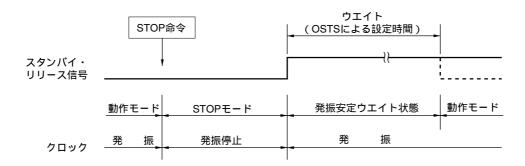

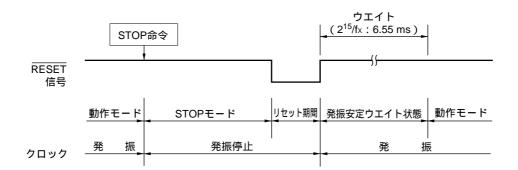

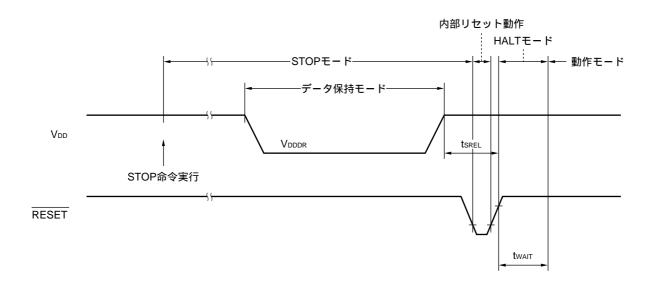

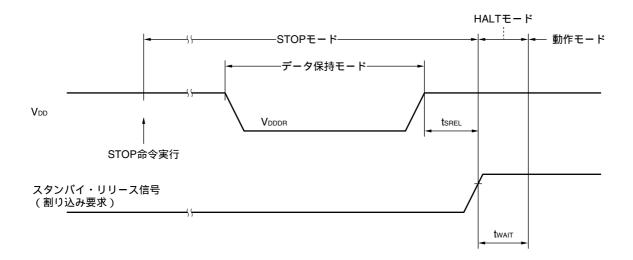

| 17 - 4  | STOPモードの割り込み発生による解除 311                    |

|         | STOPモードのRESET入力による解除 312                   |

| •       |                                            |

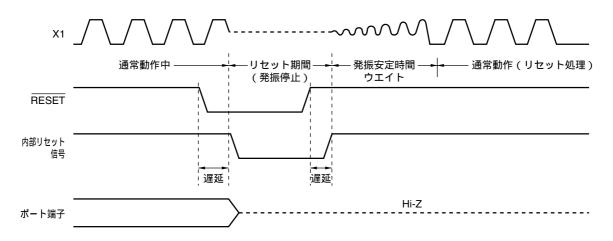

| 18 - 1  | リセット機能のブロック図 313                           |

| 18 - 2  | RESET入力によるリセット・タイミング 314                   |

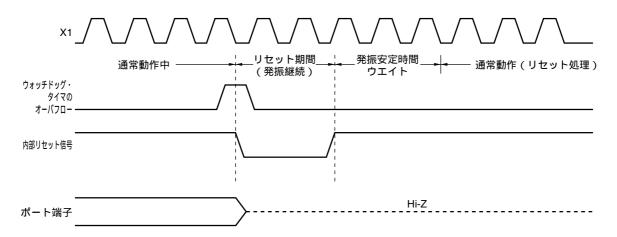

| 18 - 3  | ウォッチドッグ・タイマのオーバフローによるリセット・タイミング 314        |

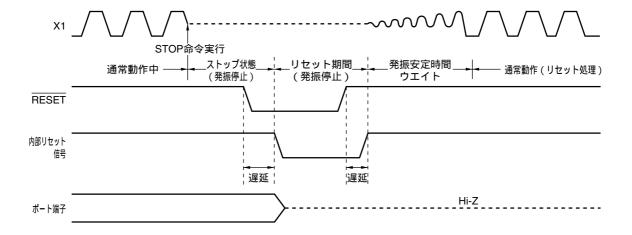

|         | STOPモード中のRESET入力によるリセット・タイミング 314          |

|         |                                            |

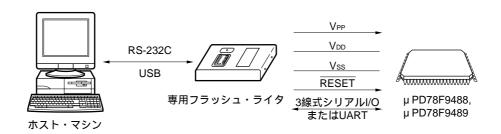

| 19 - 1  | フラッシュ・メモリにプログラムを書き込むための環境 318              |

| 19 - 2  | 通信方式選択フォーマット 319                           |

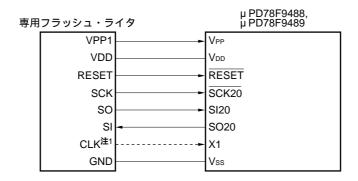

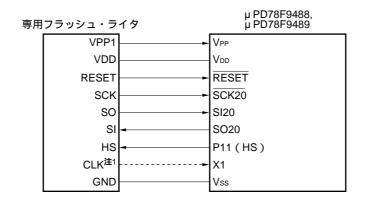

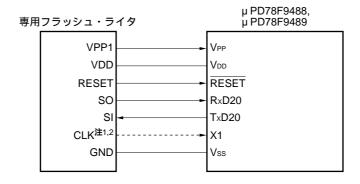

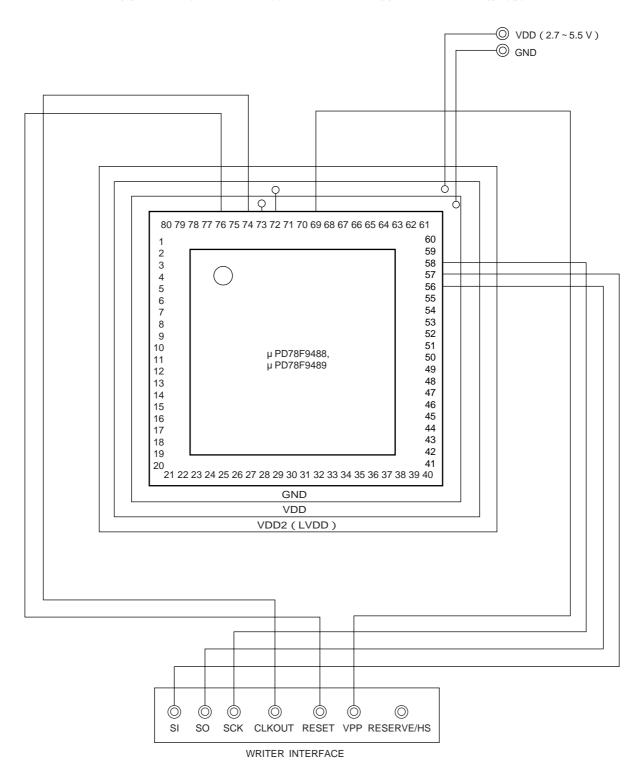

| 19 - 3  | 専用フラッシュ・ライタとの接続例 320                       |

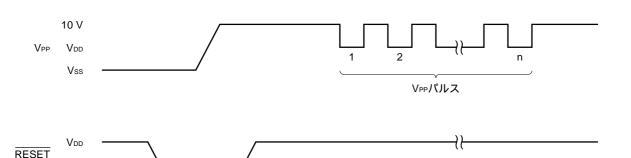

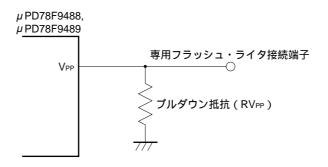

| 19 - 4  | V <sub>PP</sub> 端子の接続例 322                 |

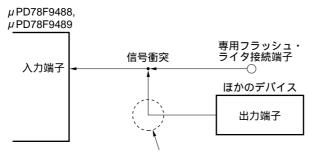

| 19 - 5  | 信号の衝突(シリアル・インタフェースの入力端子) 323               |

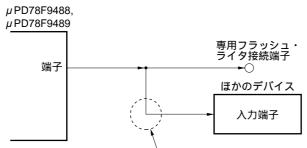

| 19 - 6  | ほかのデバイスの異常動作 323                           |

| 19 - 7  | 信号の衝突(RESET端子) 324                         |

| 19 - 8  | 3線式シリアルI/O方式でのフラッシュ書き込み用アダプタ配線例 325        |

| 19 - 9  | 3線式シリアルI/O方式(ハンドシェークあり)でのフラッシュ書き込み用アダプタ配線例 |

|         | 326                                        |

| 19 - 10 | UART方式でのフラッシュ書き込み用アダプタ配線例 327              |

|         |                                            |

| A - 1   | 開発ツール構成 368                                |

|         |                                            |

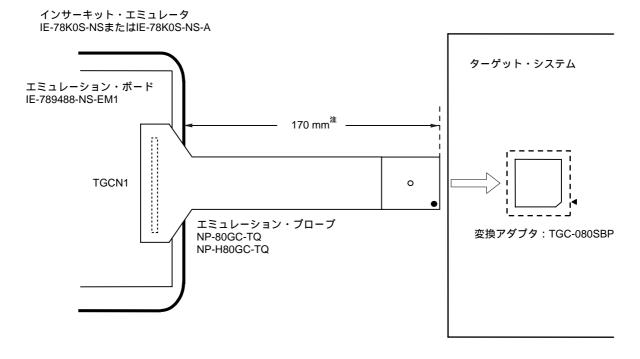

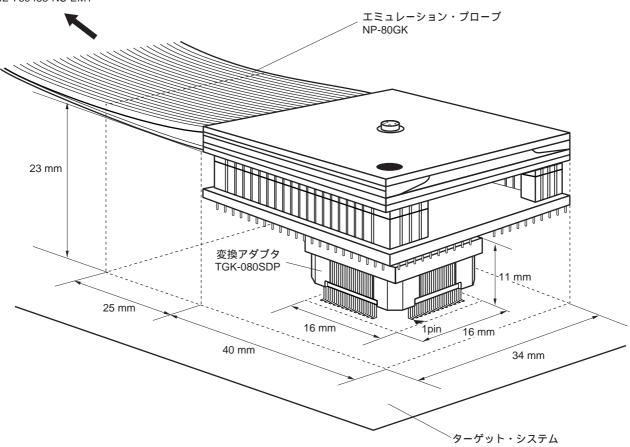

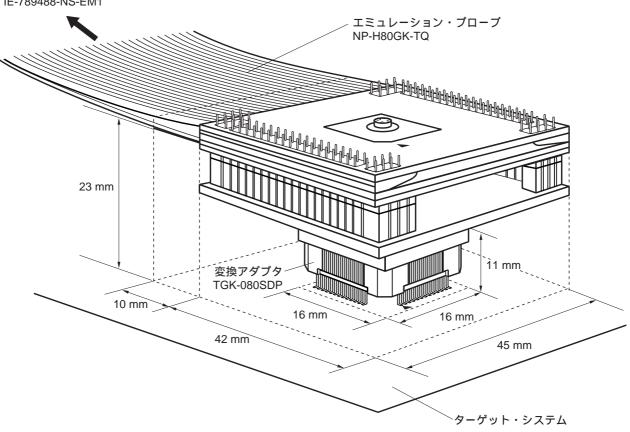

| B - 1   | インサーキット・エミュレータから変換ソケットまでの距離(80GCの場合) 373   |

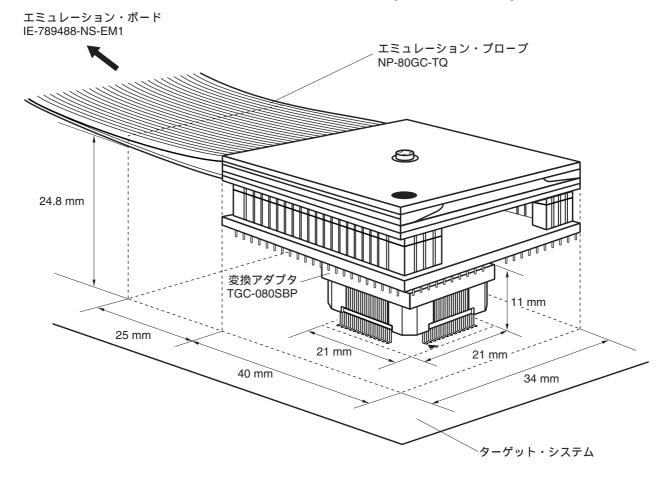

| B - 2   | ターゲット・システムの接続条件(NP-80GC-TQの場合) 374         |

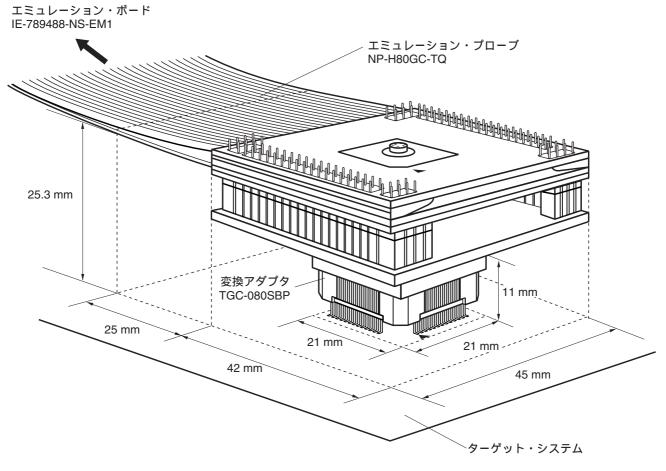

| B - 3   | ターゲット・システムの接続条件(NP-H80GC-TQの場合) 374        |

| B - 4   | インサーキット・エミュレータから変換アダプタまでの距離(80GKの場合) 375   |

| B - 5   | ターゲット・システムの接続条件(NP-80GKの場合) 376            |

| B - 6   | ターゲット・システムの接続条件(NP-H80GK-TQの場合) 376        |

# 表の目次 (1/3)

| 表番号        | タイトル , ページ                       |

|------------|----------------------------------|

| 2 - 1      | 各端子の入出力回路タイプと未使用端子の処理 44         |

|            |                                  |

| 3 - 1      | 内部ROM容量 51                       |

| 3 - 2      | ベクタ・テーブル 51                      |

| 3 - 3      | 内部高速RAM,内部低速RAM容量 52             |

| 3 - 4      | 特殊機能レジスター覧 62                    |

|            |                                  |

| 4 - 1      | ポートの機能 75                        |

| 4 - 2      | ポートの構成 75                        |

| 4 - 3      | 兼用機能使用時のポート・モード・レジスタ,出力ラッチの設定 91 |

|            |                                  |

|            | クロック発生回路の構成 94                   |

| 5 - 2      | CPUクロックの切り替えに要する最大時間 105         |

|            |                                  |

|            | 16ビット・タイマ20の構成 107               |

| _          | 16ビット・タイマ20のインターバル時間 112         |

| 6 - 3      | キャプチャ・エッジの設定内容 115               |

|            |                                  |

|            | モード一覧 119                        |

| 7 - 2      | 8ビット・タイマ50, 60, 61の構成 121        |

| 7 - 3      | タイマ50のインターバル時間 134               |

| 7 - 4      | タイマ60のインターバル時間 134               |

|            | タイマ61のインターバル時間 134               |

|            | タイマ50の方形波出力範囲 139                |

|            | タイマ60の方形波出力範囲 140                |

| 7 - 8      | タイマ61の方形波出力範囲 140                |

|            | 16ビット分解能でのインターバル時間 142           |

| 7 - 10     | 16ビット分解能の方形波出力範囲 146             |

| Q 1        | インターバル・タイマのインターバル時間 160          |

|            | サ計用タイマの構成 160                    |

|            | インターバル・タイマのインターバル時間 163          |

| υ <b>-</b> | コンフーバル・フォミのコンターバル時間 103          |

| 9 - 1      | ウォッチドッグ・タイマの暴走検出時間 165           |

|            | インターバル時間 165                     |

|            | ウォッチドッグ・タイマの構成 166               |

|            | ウォッチドッグ・タイマの暴走検出時間 169           |

|            | インターバル・タイマのインターバル時間 170          |

# 表の目次 (2/3)

| 表番号              | タイトル , ページ                                      |

|------------------|-------------------------------------------------|

| 10 - 1           | 10ビットA/Dコンバータの構成 171                            |

|                  |                                                 |

| 11 - 1           | シリアル・インタフェース20の構成 184                           |

| 11 - 2           | シリアル・インタフェース20の動作モードの設定一覧 190                   |

| 11 - 3           | システム・クロックとボー・レートの関係例 193                        |

| 11 - 4           | ASCK20端子入力周波数とボー・レートの関係(BRGC20 = 80H設定時) 194    |

| 11 - 5           | システム・クロックとボー・レートの関係例 201                        |

| 11 - 6           | ASCK20端子入力周波数とボー・レートの関係(BRGC20 = 80H設定時) 201    |

| 11 - 7           | 受信エラーの要因 206                                    |

|                  |                                                 |

|                  | シリアル・インタフェース1A0の構成 215                          |

| 12 - 2           | 割り込み要求信号の発生タイミング 247                            |

| 40 4             |                                                 |

| 13 - 1           |                                                 |

|                  | LCDコントローラ / ドライバの構成 248                         |

|                  | フレーム周波数 (Hz ) 253                               |

| 13 - 4<br>13 - 5 |                                                 |

| 13 - 5           | 選択,非選択電圧(COMO-COM2) 258                         |

|                  | 選択,非選択電圧(COM0-COM3) 261<br>VLco-VLc2端子の出力電圧 264 |

| 13 - 1           | VLC0-VLC2姍 」 <b>0</b> 7 田/万电圧 <b>20</b> 4       |

| 15 - 1           | リモコン受信回路の構成 269                                 |

|                  | ノイズ・キャンセル幅 285                                  |

|                  |                                                 |

| 16 - 1           | 割り込み要因一覧(µ PD789488, 78F9488) 289               |

| 16 - 2           | 割り込み要因一覧(μ PD789489, 78F9489) 290               |

| 16 - 3           | 割り込み要求信号名に対する各種フラグ 292                          |

| 16 - 4           | マスカブル割り込み要求発生から処理までの時間 301                      |

|                  |                                                 |

| 17 - 1           | HALTモード時の動作状態 307                               |

| 17 - 2           | HALTモードの解除後の動作 309                              |

| 17 - 3           | STOPモード時の動作状態 310                               |

| 17 - 4           | STOPモードの解除後の動作 312                              |

|                  |                                                 |

| 18 - 1           | 各ハードウエアのリセット後の状態 315                            |

|                  |                                                 |

| 19 - 1           | μPD78F9488, 78F9489とマスクROM製品の違い 317             |

| 19 - 2           | 通信方式一覧 319                                      |

| 19 - 3           | 端子接続一覧 321                                      |

# 表の目次(3/3)

表番号

タイトル , ページ

- 21 1 オペランドの表現形式と記述方法 ... 330

- 25 1 表面実装タイプの半田付け条件 ... 364

# 第1章 概 説

### 1.1 特 徵

ROM, RAM容量

| 項目                   | プログ       | ラム・メモリ  | データ・メモリ |           |  |  |

|----------------------|-----------|---------|---------|-----------|--|--|

| 品名                   | (         | ROM)    | 内部RAM   | LCD表示用RAM |  |  |

| μPD789488            | マスクROM    | 32 Kバイト | 1024バイト | 28×4ビット   |  |  |

| μ PD78F9488 フラッシュ・メモ |           |         |         |           |  |  |

| μPD789489 マスクROM     |           | 48 Kバイト | 1536バイト |           |  |  |

| $\mu$ PD78F9489      | フラッシュ・メモリ |         |         |           |  |  |

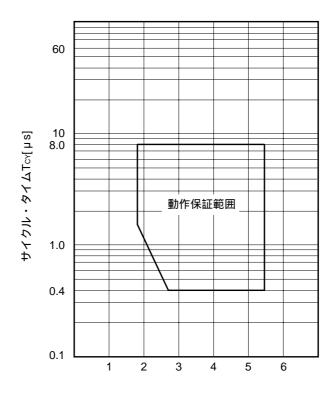

高速( $0.4~\mu$  s:メイン・システム・クロック5.0~MHz動作時)と低速( $1.6~\mu$  s:メイン・システム・クロック5.0~MHz動作時)と超低速( $122~\mu$  s:サプシステム・クロック32.768~kHz動作時)に最小命令実行時間を変更可能

サブシステム・クロック4逓倍回路の使用を選択可能

(15.26 μs: サブシステム・クロック32.768 kHzの4逓倍クロック131 kHz動作時)

I/Oポート:45本(N-chオープン・ドレーン:4本)

タイマ:6チャネル

シリアル・インタフェース:2チャネル

10ビット分解能A/Dコンバータ:8チャネル

LCDコントローラ / ドライバ (昇圧回路内蔵)

セグメント信号:28本,コモン信号:4本

乗算器内蔵:8ビット×8ビット = 16ビット

赤外線リモコン受信回路内蔵 ( μ PD789489, 78F9489のみ )

キー・リターン信号検出回路内蔵

電源電圧: VDD = 1.8~5.5 V

# 1.2 応用分野

CDラジカセ,ポータブル・オーディオ,コンパクト・カメラ,健康機器など

# 1.3 オーダ情報

|   | オーダ名称                          | パッケージ                           | 内部ROM     |

|---|--------------------------------|---------------------------------|-----------|

|   | $\mu$ PD789488GC- × × × -8BT   | 80ピン・プラスチックQFP(14×14)           | マスクROM    |

|   | $\mu$ PD789488GK- × × × -9EU   | 80ピン・プラスチックTQFP(ファインピッチ)(12×12) | <i>II</i> |

|   | $\mu$ PD78F9488GC-8BT          | 80ピン・プラスチックQFP(14×14)           | フラッシュ・メモリ |

|   | $\mu$ PD78F9488GK-9EU          | 80ピン・プラスチックTQFP(ファインピッチ)(12×12) | <i>II</i> |

| * | $\mu$ PD789489GC- × × × -8BT   | 80ピン・プラスチックQFP(14×14)           | マスクROM    |

| * | $\mu$ PD789489GK- × × × -9EU   | 80ピン・プラスチックTQFP(ファインピッチ)(12×12) | <i>II</i> |

| * | $\mu$ PD78F9489GC-8BT          | 80ピン・プラスチックQFP(14×14)           | フラッシュ・メモリ |

| * | $\mu$ PD78F9489GK-9EU          | 80ピン・プラスチックTQFP(ファインピッチ)(12×12) | "         |

| * | $\mu$ PD789488GC- × × × -8BT-A | 80ピン・プラスチックQFP(14×14)           | マスクROM    |

| * | $\mu$ PD789488GK- × × × -9EU-A | 80ピン・プラスチックTQFP(ファインピッチ)(12×12) | "         |

| * | $\mu$ PD78F9488GC-8BT-A        | 80ピン・プラスチックQFP(14×14)           | フラッシュ・メモリ |

| * | $\mu$ PD78F9488GK-9EU-A        | 80ピン・プラスチックTQFP(ファインピッチ)(12×12) | "         |

| * | $\mu$ PD789489GC- × × × -8BT-A | 80ピン・プラスチックQFP(14×14)           | マスクROM    |

| * | $\mu$ PD789489GK- × × × -9EU-A | 80ピン・プラスチックTQFP(ファインピッチ)(12×12) | "         |

| * | $\mu$ PD78F9489GC-8BT-A        | 80ピン・プラスチックQFP(14×14)           | フラッシュ・メモリ |

| * | $\mu$ PD78F9489GK-9EU-A        | 80ピン・プラスチックTQFP(ファインピッチ)(12×12) | <i>''</i> |

**備考**1.×××はROMコード番号です。

★ 2. オーダ名称末尾「-A」の製品は,鉛フリー製品です。

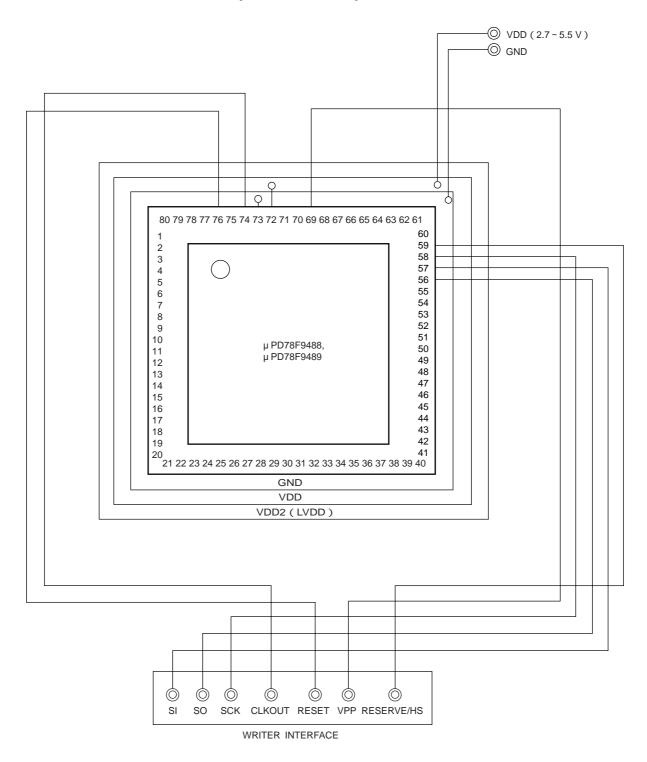

### 1. 4 **端子接続図(**Top View**)**

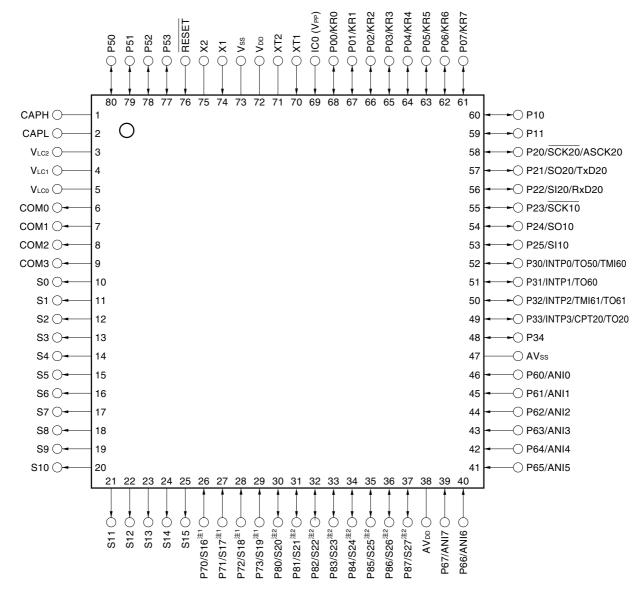

(1) μ PD789488, 78F9488

80ピン・プラスチックQFP(14×14)

μ PD789488GC-×××-8BT μ PD78F9488GC-8BT

μ PD789488GC-×××-8BT-A μ PD78F9488GC-8BT-A

80ピン・プラスチックTQFP(ファインピッチ)(12×12)

μ PD789488GK-×××-9EU μ PD78F9488GK-9EU

μ PD789488GK-×××-9EU-A μ PD78F9488GK-9EU-A

- **注**1. マスク・オプションまたはポート・ファンクション・レジスタにより,入力ポート(P70-P73)として使うか,セグメント出力(S16-S19)として使うかをビット単位で選択できます(4.3(3)ポート・ファンクション・レジスタ,第20章 マスク・オプション参照)。

- 2. マスク・オプションまたはポート・ファンクション・レジスタにより,入出力ポート(P80-P87)として使うか,セグメント出力(S20-S27)として使うかをビット単位で選択できます(4.3(3)ポート・ファンクション・レジスタ,第20章 マスク・オプション参照)。

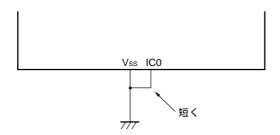

注意1. IC (Internally Connected) 端子はVssに直接接続してください。

- 2. AVDD端子はVDDに接続してください。

- 3. AVss端子はVssに接続してください。

**備考** ( )内は, μ PD78F9488のとき

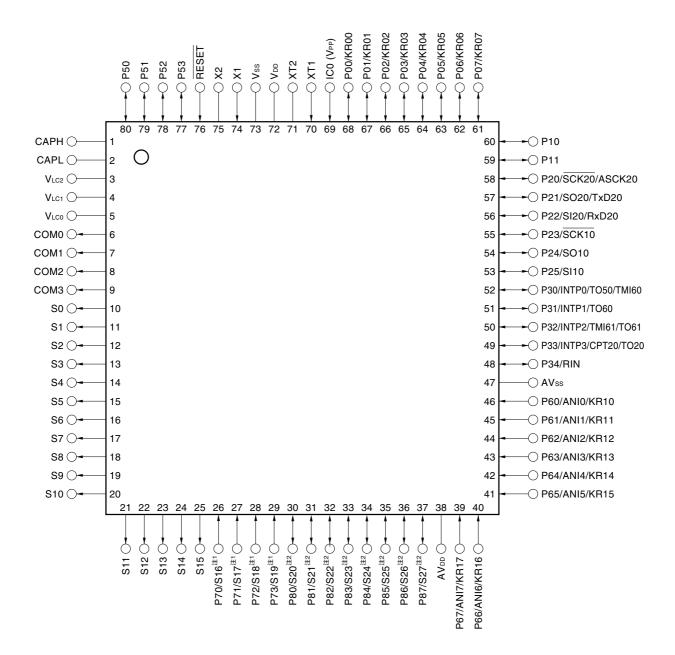

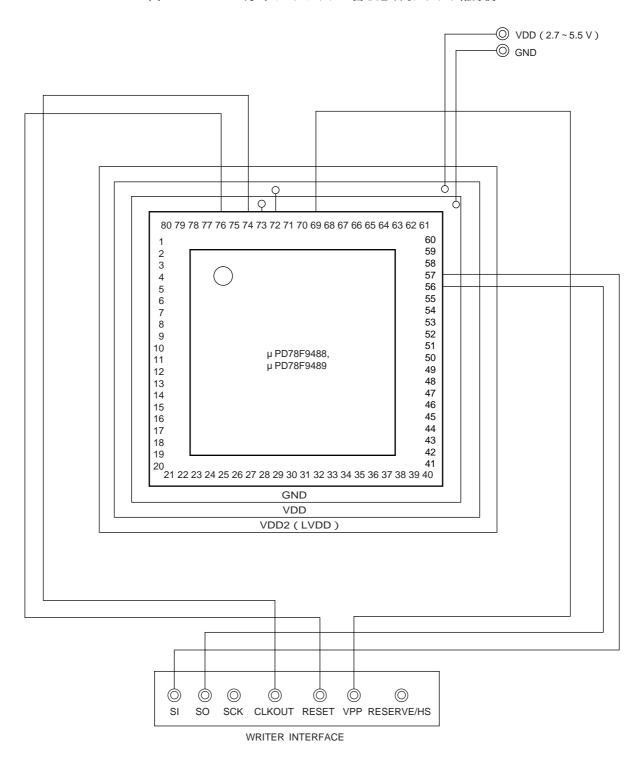

★ (2) μ PD789489, 78F9489

80ピン・プラスチックQFP(14×14) μ PD789489GC-×××-8BT μ PD78F9489GC-8BT μ PD789489GC-×××-8BT-A μ PD78F9489GC-8BT-A

80ピン・プラスチックTQFP (ファインピッチ) (12×12)

$\mu$  PD789489GK- × × × -9EU  $\mu$  PD78F9489GK-9EU  $\mu$  PD78F9489GK- × × × -9EU-A  $\mu$  PD78F9489GK-9EU-A

- **注**1. マスク・オプションまたはポート・ファンクション・レジスタにより,入力ポート(P70-P73)として使うか,セグメント出力(S16-S19)として使うかをビット単位で選択できます(4.3(3)ポート・ファンクション・レジスタ,第20章 マスク・オプション参照)。

- 2. マスク・オプションまたはポート・ファンクション・レジスタにより,入出力ポート(P80-P87)として使うか,セグメント出力(S20-S27)として使うかをビット単位で選択できます(4.3(3)ポート・ファンクション・レジスタ,第20章 マスク・オプション参照)。

注意1. IC (Internally Connected) 端子はVssに直接接続してください。

- 2. AVDD端子はVDDに接続してください。

- 3. AVss端子はVssに接続してください。

**備考** ( )内は, μ PD78F9489のとき

#### 端子名称

| ANI0-ANI7   | : Analog Input                         | RESET         | : Reset                       |

|-------------|----------------------------------------|---------------|-------------------------------|

| ASCK20      | : Asynchronus Serial Input             | RIN           | : Remote Control Input        |

| AVDD        | : Analog Power Supply                  | RxD0          | : Receive Data                |

| AVss        | : Analog Ground                        | S0-S27        | : Segment Output              |

| CAPH, CAPL  | : LCD Power Supply Capacitance Control | SCK10         | : Serial Clock Input/Output   |

| COM0-COM3   | : Common Output                        | SI10          | : Serial Data Input           |

| CPT20       | : Capture Trigger Input                | SO10          | : Serial Data Output          |

| IC0         | : Internally connected                 | SCK20         | : Serial Clock Input/Output   |

| INTP0-INTP3 | : External Interrupt Input             | SI20          | : Serial Data Input           |

| KR0-KR7     | : Key Return                           | SO20          | : Serial Data Output          |

| KR00-KR07   | : Key Return                           | TMI60,61      | : Timer Input                 |

| KR10-KR17   | : Key Return                           | TO20,50,60,61 | : Timer Output                |

| P00-P07     | : Port 0                               | TxD0          | : Transmit Data               |

| P10, P11    | : Port 1                               | $V_{DD}$      | : Power Supply                |

| P20-P25     | : Port 2                               | VLC0-VLC2     | : Power Supply for LCD        |

| P30-P34     | : Port 3                               | VPP           | : Programming Power Supply    |

| P60-P67     | : Port 6                               | Vss           | : Ground                      |

| P70-P73     | : Port 7                               | X1, X2        | : Crystal (Main system clock) |

| P80-P87     | : Port 8                               | XT1, XT2      | : Crystal (Subsystem clock)   |

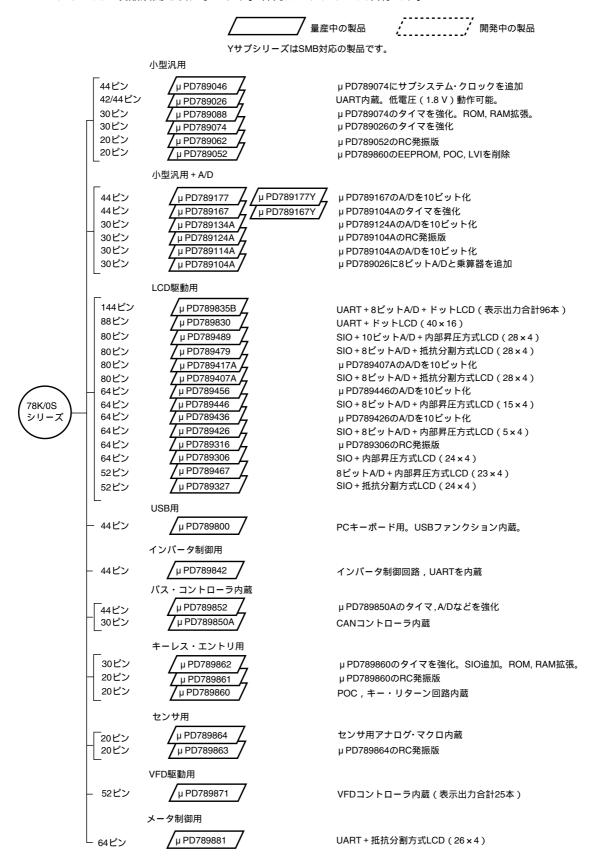

### ★ 1.5 78K/0Sシリーズの展開

78K/OSシリーズの製品展開を次に示します。枠内はサブシリーズ名称です。

**備考** 蛍光表示管の一般的な英語名称はVFD ( Vacuum Fluorescent Display ) ですが , ドキュメントによってはFIP<sup>®</sup> (Fluorescent Indicator Panel ) と記述しているものがあります。VFDとFIPは同等の機能です。

各サブシリーズ間の主な機能の違いを次に示します。

汎用,LCD駆動用シリーズ

| 機 能 ROM容量 |                |           |       | タイ     | イマ   |      | 8-bit | 10-bit | シリアル・               | I/O | V <sub>DD</sub>    | 備考     |

|-----------|----------------|-----------|-------|--------|------|------|-------|--------|---------------------|-----|--------------------|--------|

| サブシリ-     | -ズ名            | (バイト)     | 8-bit | 16-bit | 時計   | WDT  | A/D   | A/D    | インタフェース             |     | 最小値                |        |

| 小型        | μPD789046      | 16 K      | 1 ch  | 1 ch   | 1 ch | 1 ch | -     | -      | 1 ch ( UART : 1ch ) | 34本 | 1.8 V              | -      |

| 汎用        | μPD789026      | 4 K-16 K  |       |        | -    |      |       |        |                     |     |                    |        |

|           | μPD789088      | 16 K-32 K | 3 ch  |        |      |      |       |        |                     | 24本 |                    |        |

|           | μPD789074      | 2 K-8 K   | 1 ch  |        |      |      |       |        |                     |     |                    |        |

|           | μPD789062      | 4 K       | 2 ch  | -      |      |      |       |        | -                   | 14本 |                    | RC発振版  |

|           | μPD789052      |           |       |        |      |      |       |        |                     |     |                    | -      |

| 小型        | μPD789177      | 16 K-24 K | 3 ch  | 1 ch   | 1 ch | 1ch  | 1     | 8 ch   | 1 ch ( UART : 1ch ) | 31本 | 1.8 V              | -      |

| 汎用        | μPD789167      |           |       |        |      |      | 8 ch  | 1      |                     |     |                    |        |

| + A/D     | μPD789134A     | 2 K-8 K   | 1 ch  |        | -    |      | -     | 4 ch   |                     | 20本 |                    | RC発振版  |

|           | μPD789124A     |           |       |        |      |      | 4 ch  | -      |                     |     |                    |        |

|           | μPD789114A     |           |       |        |      |      | -     | 4 ch   |                     |     |                    | -      |

|           | μPD789104A     |           |       |        |      |      | 4 ch  | -      |                     |     |                    |        |

| LCD       | μPD789835B     | 24 K-60 K | 6 ch  | -      | 1 ch | 1 ch | 3 ch  | -      | 1 ch ( UART : 1ch ) | 37本 | 1.8 V <sup>注</sup> | ドットLCD |

| 駆動用       | μPD789830      | 24 K      | 1 ch  | 1 ch   |      |      | -     |        |                     | 30本 | 2.7 V              | 対応     |

|           | μPD789489      | 32 K-48 K | 3 ch  |        |      |      |       | 8 ch   | 2 ch ( UART : 1ch ) | 45本 | 1.8 V              | -      |

|           | μPD789479      | 24 K-48 K |       |        |      |      | 8 ch  | -      |                     |     |                    |        |

|           | μPD789417A     | 12 K-24 K |       |        |      |      | -     | 7 ch   | 1 ch ( UART : 1ch ) | 43本 |                    |        |

|           | μPD789407A     |           |       |        |      |      | 7 ch  | -      |                     |     |                    |        |

|           | μPD789456      | 12 K-16 K | 2 ch  |        |      |      | -     | 6 ch   |                     | 30本 |                    |        |

|           | μPD789446      |           |       |        |      |      | 6 ch  | -      |                     |     |                    |        |

|           | μPD789436      |           |       |        |      |      | -     | 6 ch   |                     | 40本 |                    |        |

|           | μPD789426      |           |       |        |      |      | 6 ch  | -      |                     |     |                    |        |

|           | μPD789316      | 8 K-16 K  |       |        |      |      | -     |        | 2 ch ( UART : 1ch ) | 23本 |                    | RC発振版  |

|           | μPD789306      |           |       |        |      |      |       |        |                     |     |                    | -      |

|           | μPD789467      | 4 K-24 K  |       | -      |      |      | 1 ch  |        | -                   | 18本 |                    |        |

|           | $\mu$ PD789327 |           |       |        |      |      | -     |        | 1 ch                | 21本 |                    |        |

注 フラッシュ・メモリ版:3.0 V

### ASSP用シリーズ

|              | 機能                                     | ROM容量     |       | タイ         | イマ   |      | 8-bit | 10-bit | シリアル・               | I/O | V <sub>DD</sub>     | 備考                             |

|--------------|----------------------------------------|-----------|-------|------------|------|------|-------|--------|---------------------|-----|---------------------|--------------------------------|

| サブシリ-        | -ズ名                                    | (バイト)     | 8-bit | 16-bit     | 時計   | WDT  | A/D   | A/D    | インタフェース             |     | 最小値                 |                                |

| USB用         | μPD789800                              | 8K        | 2 ch  | -          | -    | 1 ch | -     | -      | 2 ch ( USB : 1 ch ) | 31本 | 4.0 V               | -                              |

| インバータ制御用     | μPD789842                              | 8 K-16 K  | 3 ch  | 注1         | 1 ch | 1 ch | 8 ch  | -      | 1 ch ( UART : 1ch ) | 30本 | 4.0 V               | -                              |

| バス・コント       | μPD789852                              | 24 K-32 K | 3 ch  | 1 ch       | -    | 1 ch | -     | 8ch    | 3 ch ( UART : 2ch ) | 31本 | 4.0 V               | -                              |

| ローラ内蔵        | μPD789850A                             | 16 K      | 1 ch  |            |      |      | 4 ch  | -      | 2 ch ( UART : 1ch ) | 18本 |                     |                                |

| キーレス<br>・エント | μPD789861                              | 4 K       | 2 ch  | -          | -    | 1 ch | -     | -      | -                   | 14本 | 1.8 V               | RC発振版,<br>EEPROM内蔵             |

| リ用           | μPD789860                              | 16 K      | 1 ch  | 2 ch       |      |      |       |        | 1 ch ( UART : 1ch ) | 22本 |                     | EEPROM内蔵                       |

| センサ<br>用     | μ PD789862<br>μ PD789864<br>μ PD789863 | 4 K       | 1 ch  | <b>注</b> 2 | -    | 1 ch | -     | 4 ch   | -                   | 5本  | 1.9 V               | EEPROM内蔵<br>RC発振版,<br>EEPROM内蔵 |

| VFD<br>駆動用   | μPD789871                              | 4 K-8 K   | 3 ch  | -          | 1 ch | 1 ch | -     | 1      | 1 ch                | 33本 | 2.7 V               | -                              |

| メータ 制御用      | μPD789881                              | 16 K      | 2 ch  | 1 ch       | -    | 1 ch | -     | -      | 1 ch ( UART : 1ch ) | 28本 | 2.7 V <sup>注3</sup> | -                              |

注1. 10ビット・タイマ:1チャネル 2. 12ビット・タイマ:1チャネル

3. フラッシュ・メモリ版:3.0 V

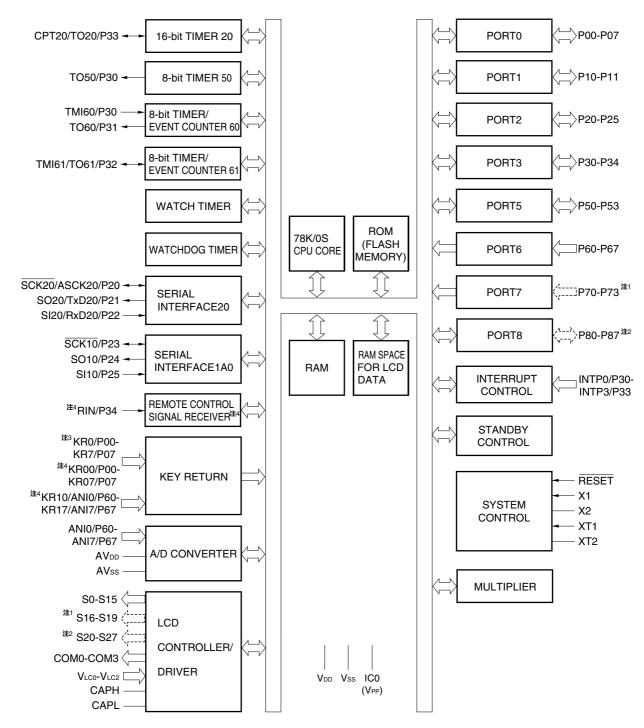

### 1.6 プロック図

- 注1.  $\mu$  PD789488, 789489はマスク・オプション , $\mu$  PD78F9488, 78F9489はポート・モード・レジスタにより , 入力ポート (P70-P73) として使うか , セグメント出力 (S16-S19) として使うかをビット単位で選択できます (4.3 (3) ポート・ファンクション・レジスタ ,第20章 マスク・オプション参照 )。

- 2. μPD789488, 789489はマスク・オプション,μPD78F9488, 78F9489はポート・モード・レジスタにより, 入出力ポート(P80-P87)として使うか,セグメント出力(S20-S27)として使うかをビット単位で選択できます(4.3(3)ポート・ファンクション・レジスタ,第20章 マスク・オプション参照)。

- 3. μPD789488, 78F9488のとき

- 4. μPD789489, 78F9489のとき

#### 備考 ( )内は,フラッシュ・メモリ製品のとき

# 1.7 機能概要

(1/2)

| 項目               |         | μ PD789488                                               | μ PD78F9488      | μ PD789489   | μ PD78F9489  |

|------------------|---------|----------------------------------------------------------|------------------|--------------|--------------|

| 内部メモリ            | ROM     | 32 Kバイト                                                  | 32 Kバイト( フラッ     | 48Kバイト       | 48 Kバイト( フラッ |

|                  |         |                                                          | シュ・メモリ)          |              | シュ・メモリ )     |

| 高速RAM            |         | 1024バイト                                                  |                  |              |              |

| 低速RAM            |         | - 512バイト                                                 |                  |              |              |

| LCD表示用RAM        |         | 28バイト                                                    |                  |              |              |

| メイン・システム・クロック    |         | セラミック / クリスタル発振                                          |                  |              |              |

| (発振周波数)          |         | (1.0~5.0 MHz)                                            |                  |              |              |

| サブシステム・クロック      |         | クリスタル発振(32.768 kHz)                                      |                  |              |              |

| (発振周波数)          |         |                                                          |                  |              |              |

| 最小命令実行時間         |         | 0.4 μ s/1.6 μ s(メイン・システム・クロック:5.0 MHz動作時)                |                  |              |              |

|                  |         | 122 μ s(サブシステム・クロック:32.768 kHz動作時)                       |                  |              |              |

|                  |         | 15.26 μs(サブシステム・クロックの4逓倍クロック:131 kHz動作時)                 |                  |              |              |

| サブシステム・クロック逓倍機能  |         | 4逓倍回路(動作電源電圧:Vpp = 2.7~5.5 V) <sup>注1</sup>              |                  |              |              |

| 汎用レジスタ           |         | 8ビット×8レジスタ                                               |                  |              |              |

| 命令セット            |         | ・16ビット演算                                                 |                  |              |              |

|                  |         | ・ビット操作(セット,リセット,テスト)など                                   |                  |              |              |

| 乗算器              |         | 8ビット×8ビット = 16ビット                                        |                  |              |              |

| I/Oポート           |         | <u>合計 : 45本<sup>注2</sup></u>                             |                  |              |              |

|                  |         | CMOS入出力                                                  | : 29本            |              |              |

|                  |         | CMOS入力 : 12本                                             |                  |              |              |

|                  |         | N-chオープン・ドレーン入出力 : 4本                                    |                  |              |              |

| タイマ              |         | ・16ビット・タイマ : 1チャネル                                       |                  |              |              |

|                  |         | ・8ビット・タイマ : 3チャネル                                        |                  |              |              |

|                  |         | ・時計用タイマ : 1チャネル                                          |                  |              |              |

| 5 ( = 1) ±       |         | ・ウォッチドッグ・タイマ : 1チャネル                                     |                  |              |              |

| タイマ出力            |         | 4本<br>HADT (2倍ポンリフリ)のエード・4 チャカリ                          |                  |              |              |

| シリアル・インタフェース     |         | UART / 3線式シリアルI/Oモード:1チャネル 3線式シリアルI/Oモード(白動転送機能付き):1チャネル |                  |              |              |

| A/Dコンバータ         |         | 3線式シリアルI/Oモード(自動転送機能付き):1チャネル 10ビット分解能×8チャネル             |                  |              |              |

|                  |         | ・セグメント信号出力: 28本 <sup>注3</sup>                            |                  |              |              |

| LCDコントローラ / ドライバ |         | ・セクメント信号田川: 28本<br>・コモン信号出力 : 4本                         |                  |              |              |

| <br>LCD駆動用電源供給方式 |         | ・コモン信号四月 : 4本<br>内部昇圧方式                                  |                  |              |              |

| 赤外線リモコン受信機能      |         | *************************************                    |                  | 内蔵           |              |

| サー・リターン信号検出機能    |         | 8本                                                       |                  | 16本          |              |

| ベクタ割り込み マスカブル    |         | <sup>6年</sup><br>  内部:11,外部:5                            |                  | 内部:16,外部:6   |              |

| 要因               | ノンマスカブル | 内部:11,外部:3                                               |                  | 10, 9Pap. 10 |              |

|                  |         |                                                          | <br>ロセット         |              |              |

|                  |         | ・RESET端子によるリセット<br>・ウォッチドッグ・タイマによる内部リセット                 |                  |              |              |

|                  |         | 2022127.2                                                | · · · にのるrinuソビソ | t .          |              |

- 注1. 4逓倍回路の使用可否を,マスク・オプションまたはサブクロック選択レジスタで決定します。

- 2. うち12本は,ポート機能かLCDセグメント出力のどちらかを,マスク・オプションまたはポート・ファンクション・レジスタで選択する端子です。

(2/2)

| 項目                                 | $\mu$ PD789488 $\mu$ PD78F9488 $\mu$ PD789489 $\mu$ PD78F9489 |  |  |  |  |  |  |  |  |  |

|------------------------------------|---------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 電源電圧 V <sub>DD</sub> = 1.8 ~ 5.5 V |                                                               |  |  |  |  |  |  |  |  |  |

| 動作周囲温度                             | T <sub>A</sub> = -40~+85                                      |  |  |  |  |  |  |  |  |  |

| パッケージ                              | ・80ピン・プラスチックQFP(14 × 14)                                      |  |  |  |  |  |  |  |  |  |

|                                    | ・80ピン・プラスチックTQFP(ファインピッチ)(12×12)                              |  |  |  |  |  |  |  |  |  |

## 次にタイマの概要を示します。

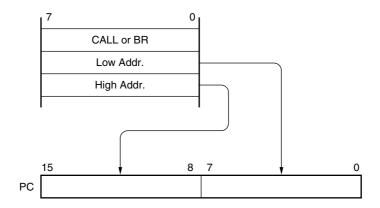

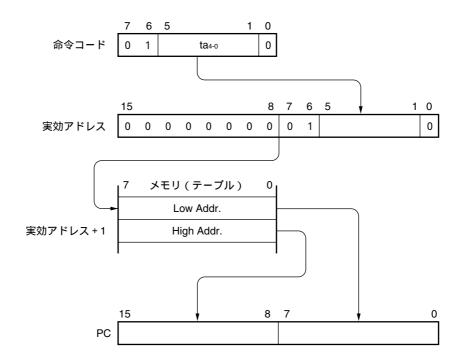

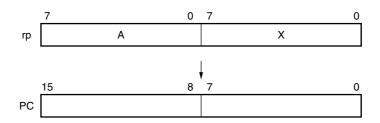

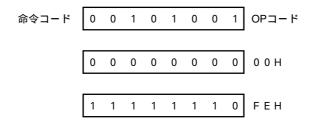

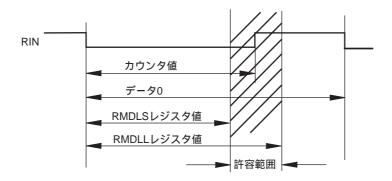

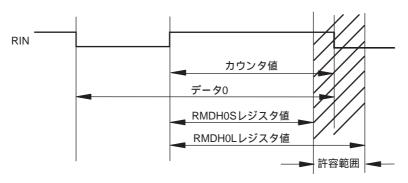

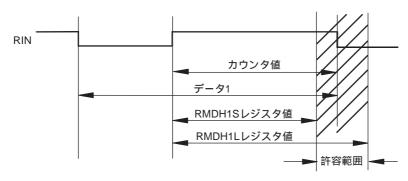

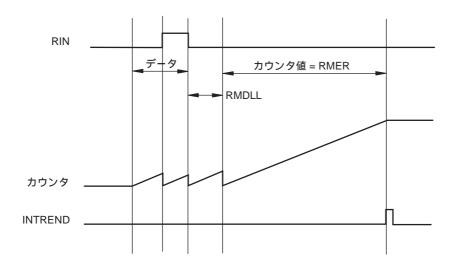

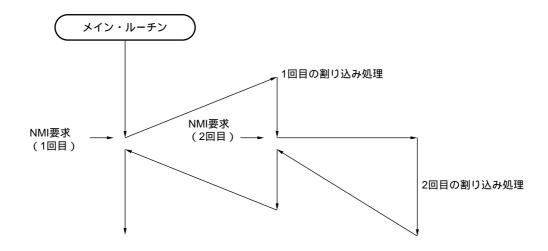

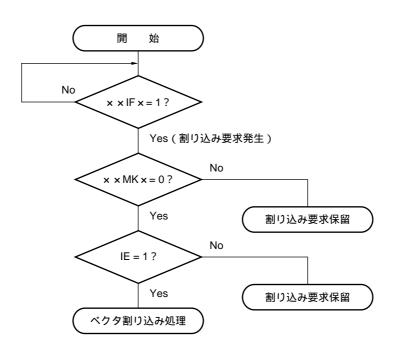

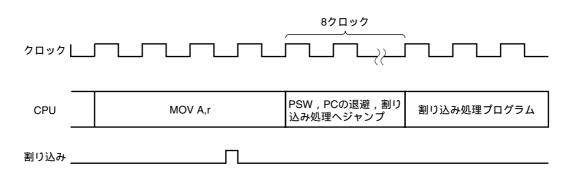

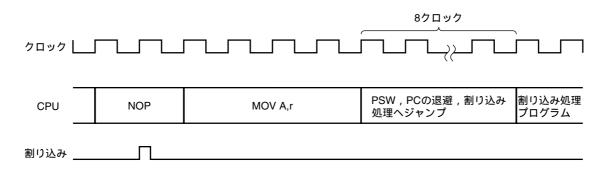

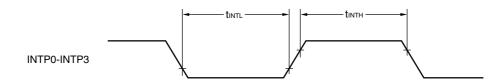

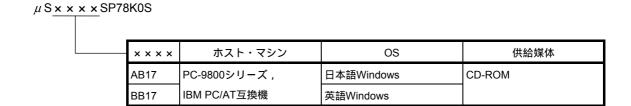

|       |                 | 16ビット・ | 8ビット・ | 8ビット・ | 8ビット・ | 時計用タイマ              | ウォッチドッ              |