## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

## ユーザーズ・マニュアル

# μPD780024AS, 780034ASサブシリーズ

8ビット・シングルチップ・マイクロコンピュータ

$\mu$ PD780021AS  $\mu$ PD780021AS(A)

$\mu$ PD780022AS  $\mu$ PD780022AS(A)

$\mu$ PD780023AS  $\mu$ PD780023AS(A)

$\mu$ PD780024AS  $\mu$ PD780024AS(A)

$\mu$ PD780031AS  $\mu$ PD780031AS(A)

$\mu$ PD780032AS  $\mu$ PD780032AS(A)

$\mu$ PD780033AS  $\mu$ PD780033AS(A)

$\mu$ PD780034AS  $\mu$ PD780034AS(A)

$\mu$ PD78F0034BS  $\mu$ PD78F0034BS(A)

資料番号 U16035JJ4V1UD00 (第 4 版) 発行年月 January 2005 N CP(K) (メ モ)

## 目次要約

第1章 概 説 … 16 第 2 章 端子機能 … 27 第3章 CPUアーキテクチャ … 37 第4章 ポート機能 … 70 第5章 クロック発生回路 … 91 第6章 16ビット・タイマ/イベント・カウンタ0 … 106 第7章 8ビット・タイマ/イベント・カウンタ50,51 … 142 第8章 時計用タイマ … 166 第9章 ウォッチドッグ・タイマ … 171 第10章 クロック出力/ブザー出力制御回路 … 176 第11章 8ビットA/Dコンバータ(μPD780024ASサブシリーズ) ··· 181 第12章 10ビットA/Dコンバータ(μPD780034ASサブシリーズ) ··· 203 第13章 シリアル・インタフェースUARTO … 225 第14章 シリアル・インタフェースSIO30, SIO31 ··· 253 第15章 割り込み機能 … 264 第16章 スタンバイ機能 … 286 第17章 リセット機能 … 294 第**18**章 μ PD78F0034BS ··· 298 第19章 命令セットの概要 … 312 第20章 電気的特性 … 327 第21章 外形図 … 349 第22章 半田付け推奨条件 … 350 付録 A μ PD780024A, 780024AS, 780034A, 780034ASサブシリーズ間の違い ... 352 付録B 開発ツール … 354 付録C ターゲット・システム設計上の注意 … 361

付録D レジスタ索引 … 363

付録 E 改版履歴 … 369

## CMOSデバイスの一般的注意事項・

#### ① 入力端子の印加波形

入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

CMOSデバイスの入力がノイズなどに起因して、 $V_{\text{IL}}$ (MAX.)から $V_{\text{IH}}$ (MIN.)までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、 $V_{\text{IL}}$ (MAX.)から $V_{\text{IH}}$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

## ② 未使用入力の処理

CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVoDまたはGNDに接続することが有効です。

資料中に「未使用端子の処理 | について記載のある製品については、その内容を守ってください。

#### ③ 静電気対策

MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また、MOSデバイスを実装したボードについても同様の扱いをしてください。

## ④ 初期化以前の状態

電源投入時, MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定、レジスタ内容などは保証しておりません。ただし、リセット動作やモード設定で定義している項目については、これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

#### ⑤ 電源投入切断順序

内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には、原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により、内部素子に過電圧が印加され、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源投入切断シーケンス」についての記載のある製品については、その内容を守ってください。

## ⑥ 電源OFF時における入力信号

当該デバイスの電源がOFF状態の時に、入力信号や入出力プルアップ電源を入れないでください。 入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

FIP, IEBusは, NECエレクトロニクス株式会社の登録商標です。

WindowsおよびWindowsNTは、米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。

PC/ATは、米国IBM社の商標です。

HP9000シリーズ700, HP-UXは, 米国ヒューレット・パッカード社の商標です。

SPARCstationは、米国SPARC International, Inc.の商標です。

Solaris, SunOSは、米国サン・マイクロシステムズ社の商標です。

TRONは、The Realtime Operating system Nucleusの略称です。

ITRONは、Industrial TRONの略称です。

本製品のうち、外国為替及び外国貿易法の規定により規制貨物等(または役務)に該当するものについては、日本国外に輸出する際に、同法に基づき日本国政府の輸出許可が必要です。

非 該 当 品: μPD78F0034BSGB-8ET, 78F0034BSGB(A)-8ET

ユーザ判定品:  $\mu$  PD780021ASGB- $\times$  $\times$  $\times$ -8ET, 780022ASGB- $\times$  $\times$  $\times$ -8ET, 780023ASGB- $\times$  $\times$  $\times$ -8ET,  $\mu$  PD780024ASGB- $\times$  $\times$  $\times$ -8ET, 780031ASGB- $\times$  $\times$  $\times$ -8ET, 780032ASGB- $\times$  $\times$  $\times$ -8ET,  $\mu$  PD780033ASGB- $\times$  $\times$  $\times$ -8ET, 780034ASGB- $\times$  $\times$  $\times$ -8ET,  $\mu$  PD780021ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780022ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780032ASGB(A)- $\times$  $\times$  $\times$ -8ET,  $\mu$  PD780024ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780031ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780033ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780034ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780033ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780034ASGB(A)- $\times$  $\times$  $\times$ -8ET

- ◆本資料に記載されている内容は2004年11月現在のもので、今後、予告なく変更することがあります。量産設計の際には最新の個別データ・シート等をご参照ください。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は、本資料の誤りに関し、一切 その責を負いません。

- 当社は、本資料に記載された当社製品の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、一切その責を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- ◆本資料に記載された回路、ソフトウェアおよびこれらに関する情報は、半導体製品の動作例、応用例を 説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関する情報を使 用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し、当社は、一切その責を負いません。

- 当社は、当社製品の品質、信頼性の向上に努めておりますが、当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命、身体および財産に対する損害の危険を最小限度にするために、冗長設計、延焼対策設計、誤動作防止設計等安全設計を行ってください。

- 当社は、当社製品の品質水準を「標準水準」、「特別水準」およびお客様に品質保証プログラムを指定 していただく「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われ ることを意図しておりますので、当社製品の品質水準をご確認ください。

標準水準:コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には、事前に当社販売窓口までお問い合わせください。

(注)

- (1) 本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2) 本事項において使用されている「当社製品」とは、(1) において定義された当社の開発、製造製品をいう。

M8E 02.11

## はじめに

対象者 このマニュアルは、 $\mu$ PD780024AS, 780034ASサブシリーズの機能を理解し、その応用システムや応用プログラムを設計、開発するユーザのエンジニアを対象としています。

対象製品は、次に示すサブシリーズの各製品です。

・ $\mu$ PD780024ASサブシリーズ :  $\mu$ PD780021AS, 780022AS, 780023AS, 780024AS,

780021AS(A), 780022AS(A), 780023AS(A), 780024AS(A)

・ $\mu$ PD780034ASサブシリーズ :  $\mu$ PD780031AS, 780032AS, 780033AS, 780034AS, 78F0034BS,

780031AS(A), 780032AS(A), 780033AS(A), 780034AS(A),

78F0034BS(A)

- 目 的 このマニュアルは、次の構成に示す機能をユーザに理解していただくことを目的としています。

- 構 成  $\mu$  PD780024AS, 780034ASサブシリーズのマニュアルは、このマニュアルと命令編(78K/0シリーズ 共通)の 2 冊に分かれています。

μ PD780024AS, 780034ASサブシリーズ ユーザーズ・マニュアル (このマニュアル) 78K/0シリーズ ユーザーズ・マニュアル 命令編

- ●端子機能

- ●内部ブロック機能

- ●割り込み

- ●その他の内蔵周辺機能

- ●電気的特性

- ●CPU機能

- ●命令セット

- ●命令の説明

- 読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコンピュータの一般知識を必要とします。

- □ (A) 製品のマニュアルとしてお使いになる方へ

- →標準製品と(A)製品は、品質水準のみが異なります。(A)製品については、品名を次のように読み替えてください。

$\mu$  PD780021AS  $\rightarrow \mu$  PD780021AS(A)

$\mu$  PD780032AS  $\rightarrow \mu$  PD780032AS(A)

$\mu PD780022AS \rightarrow \mu PD780022AS(A)$

$\mu PD780033AS \rightarrow \mu PD780033AS(A)$

$\mu$  PD780023AS  $\rightarrow \mu$  PD780023AS(A)

$\mu PD780034AS \rightarrow \mu PD780034AS(A)$

$\mu$  PD780024AS  $\rightarrow \mu$  PD780024AS(A)

$\mu$  PD78F0034BS  $\rightarrow \mu$  PD78F0034BS(A)

$\mu$  PD780031AS  $\rightarrow \mu$  PD780031AS(A)

- □一通りの機能を理解しようとするとき

- →目次に従って読んでください。本文欄外の★印は、本版で改訂された主な箇所を示しています。

- □レジスタ・フォーマットの見方

- →ビット番号を $\square$ で囲んでいるものは、そのビット名称がRA78K0では予約語に、CC78K0では #pragma sfr指令で、sfr変数として定義されているものです。

- □レジスタ名が分かっていて、レジスタの詳細を確認するとき

- →付録D レジスタ索引を利用してください。

## μPD780024AS, 780034ASサブシリーズ間の違い

$\mu$ PD780024AS, 780034ASサブシリーズ間では、A/Dコンバータの分解能が異なります。

| サブシリーズ名  | μPD780024AS | μPD780034AS |

|----------|-------------|-------------|

| 項目       |             |             |

| A/Dコンバータ | 8ビット分解能     | 10ビット分解能    |

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記: $\overline{XXX}$ (端子,信号名称に上線)

注 :本文中につけた注の説明

注意 :気をつけて読んでいただきたい内容

備考 : 本文の補足説明

数の表記 :2進数···×××stcは×××xB

> 10進数···××× 16進数···××××H

関連資料 関連資料は暫定版の場合がありますが、この資料では「暫定」の表示をしておりません。あらかじめご 了承ください。

## デバイスの関連資料

| 資 料 名                                   | 資料番号    |         |  |

|-----------------------------------------|---------|---------|--|

|                                         | 和文      | 英 文     |  |

| μPD780024AS, 780034ASサブシリーズ ユーザーズ・マニュアル | このマニュアル | U16035E |  |

| 78K/0シリーズ ユーザーズ・マニュアル 命令編               | U12326J | U12326E |  |

| 78K/0シリーズ アプリケーション・ノート 基礎編( I )         | U12704J | U12704E |  |

## 開発ツール(ソフトウエア)の資料(ユーザーズ・マニュアル)

| 資 料 名                          | 資 料 名         |         |         |  |  |  |

|--------------------------------|---------------|---------|---------|--|--|--|

|                                |               | 和文      | 英 文     |  |  |  |

| RA78K0 アセンブラ・パッケージ             | 操作編           | U16629J | U16629E |  |  |  |

|                                | 言語編           | U14446J | U14446E |  |  |  |

|                                | 構造化アセンブリ言語編   | U11789J | U11789E |  |  |  |

| CC78K0 Cコンパイラ                  | 操作編           | U16613J | U16613E |  |  |  |

|                                | 言語編           | U14298J | U14298E |  |  |  |

| SM78Kシリーズ Ver.2.52 システム・シミュレータ | 操作編           | U16768J | U16768E |  |  |  |

|                                | 外部部品ユーザ・オープン・ | U15802J | U15802E |  |  |  |

|                                | インタフェース仕様編    |         |         |  |  |  |

| ID78K0-NS Ver.2.52 統合ディバッガ     | 操作編           | U16488J | U16488E |  |  |  |

| ID78K0 統合ディバッガ EWSベース          | レファレンス編       | U11151J |         |  |  |  |

| PM plus Ver.5.20               |               | U16934J | U16934E |  |  |  |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

## 開発ツール(ハードウエア)の資料(ユーザーズ・マニュアル)

| 資料 名                          | 資料番号    |         |  |  |

|-------------------------------|---------|---------|--|--|

|                               | 和文      | 英 文     |  |  |

| IE-78K0-NS インサーキット・エミュレータ     | U13731J | U13731E |  |  |

| IE-78K0-NS-A インサーキット・エミュレータ   | U14889J | U14889E |  |  |

| IE-78K0-NS-PA パフォーマンス・ボード     | U16109J | 作成予定    |  |  |

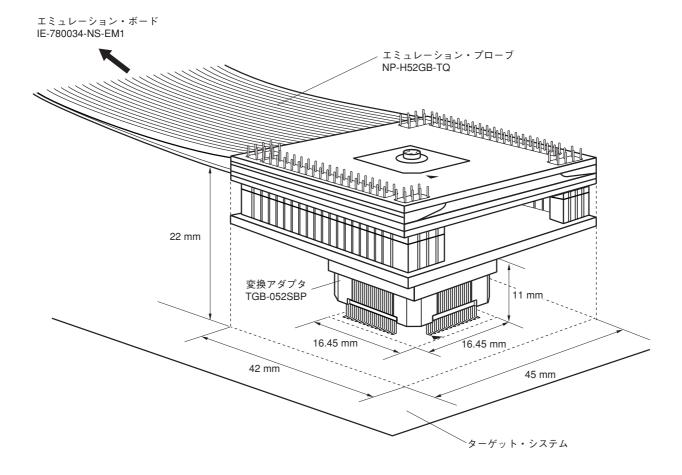

| IE-780034-NS-EM1 エミュレーション・ボード | U14642J | U14642E |  |  |

## フラッシュ・メモリ書き込み用の資料

| 資 料 名                              | 資料番号    |         |  |

|------------------------------------|---------|---------|--|

|                                    | 和文      | 英 文     |  |

| PG-FP3 フラッシュ・メモリ・プログラマ ユーザーズ・マニュアル | U13502J | U13502E |  |

| PG-FP4 フラッシュ・メモリ・プログラマ ユーザーズ・マニュアル | U15260J | U15260E |  |

## その他の資料

| 資 料 名                                                 | 資料番号    |         |  |  |

|-------------------------------------------------------|---------|---------|--|--|

|                                                       | 和文      | 英 文     |  |  |

| SEMICONDUCTOR SELECTION GUIDE -Products and Packages- | X13769X |         |  |  |

| 半導体デバイス 実装マニュアル                                       | 注       |         |  |  |

| NEC半導体デバイスの品質水準                                       | C11531J | C11531E |  |  |

| NEC半導体デバイスの信頼性品質管理                                    | C10983J | C10983E |  |  |

| 静電気放電(ESD)破壊対策ガイド                                     | C11892J | C11892E |  |  |

| 半導体 品質/信頼性ハンドブック                                      | C12769J | _       |  |  |

| マイクロコンピュータ関連製品ガイド 社外メーカ編                              | U11416J | _       |  |  |

注 「半導体デバイス実装マニュアル」のホーム・ページ参照

和文:http://www.necel.com/pkg/ja/jissou/index.html 英文:http://www.necel.com/pkg/en/mount/index.html

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

## 目 次

第1章 概 説 … 16

|     | 1.2<br>1.3<br>1.4<br>1.5<br>1.6 | 特 徴 … 16<br>応用分野 … 17<br>オーダ情報 … 17<br>品質水準 … 18<br>端子接続図(Top View) … 19<br>78K/0シリーズの展開 … 21<br>ブロック図 … 24<br>機能概要 … 25<br>標準水準品と特別水準品との違いについて … 26 |

|-----|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 第 2 | 章                               | <b>端子機能</b> … 27                                                                                                                                     |

|     | 2.1                             | 端子機能一覧 … 27                                                                                                                                          |

|     |                                 | 端子機能の説明 … 29                                                                                                                                         |

|     |                                 | 2.2.1 P00-P03 (Port0) ··· 29                                                                                                                         |

|     |                                 | 2.2.2 P10-P13 (Port1) ··· 29                                                                                                                         |

|     |                                 | 2.2.3 P20-P25 (Port2) ··· 30                                                                                                                         |

|     |                                 | 2.2.4 P34-P36 (Port3) ··· 30                                                                                                                         |

|     |                                 | 2.2.5 P40-P47 (Port4) ··· 31                                                                                                                         |

|     |                                 | 2.2.6 P50-P57 (Port5) ··· 31                                                                                                                         |

|     |                                 | 2.2.7 P70-P75 (Port7) ··· 32                                                                                                                         |

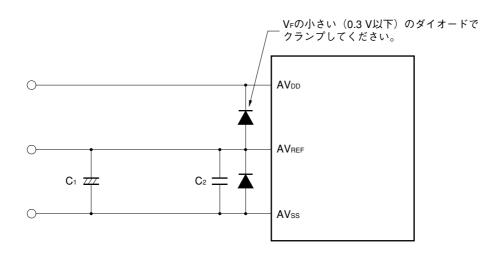

|     |                                 | 2.2.8 AVREF 32                                                                                                                                       |

|     |                                 | 2.2.9 AV <sub>DD</sub> ··· 32                                                                                                                        |

|     |                                 | 2.2.10 AVss ··· 33                                                                                                                                   |

|     |                                 | 2.2.11 RESET ··· 33                                                                                                                                  |

|     |                                 | 2.2.12 X1, X2 ··· 33                                                                                                                                 |

|     |                                 | 2.2.13 XT1, XT2 ··· 33                                                                                                                               |

|     |                                 | 2.2.14 VDD0, VDD1 ··· 33                                                                                                                             |

|     |                                 | 2.2.15 Vsso, Vss1 ··· 33                                                                                                                             |

|     |                                 | 2.2.16 Vpp(フラッシュ・メモリ製品のみ) … 33                                                                                                                       |

|     |                                 | 2.2.17 IC(マスクROM製品のみ) ··· 34                                                                                                                         |

|     | 2.3                             |                                                                                                                                                      |

| 第3  | 章                               | CPUアーキテクチャ … 37                                                                                                                                      |

|     | 3.1                             | メモリ空間 … 37                                                                                                                                           |

|     |                                 | 3.1.1 内部プログラム・メモリ空間 … 43                                                                                                                             |

|     |                                 | 3.1.2 内部データ・メモリ空間 … 44                                                                                                                               |

|     |                                 | 3.1.3 特殊機能レジスタ(SFR:Special Function Register)領域 ··· 44                                                                                               |

|     |                                 | 3.1.4 外部メモリ空間 … 44                                                                                                                                   |

|     |                                 | 3.1.5 データ・メモリ・アドレシング … 45                                                                                                                            |

|     | 2 2                             | プロセッサ・レジスタ … 50                                                                                                                                      |

|     | J . Z                           |                                                                                                                                                      |

|     | J. Z                            | 3.2.1 制御レジスタ … 50                                                                                                                                    |

|     | J. Z                            | 3.2.1 制御レジスタ … 50                                                                                                                                    |

|     | J. Z                            |                                                                                                                                                      |

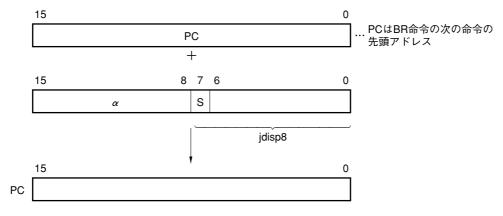

- 3.3.1 レラティブ・アドレシング … 58

- 3.3.2 イミーディエト・アドレシング … 59

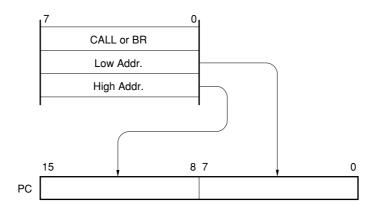

- 3.3.3 テーブル・インダイレクト・アドレシング … 60

- 3.3.4 レジスタ・アドレシング … 60

- 3.4 オペランド・アドレスのアドレシング … 61

- 3.4.1 インプライド・アドレシング … 61

- 3.4.2 レジスタ・アドレシング … 62

- 3.4.3 ダイレクト・アドレシング … 63

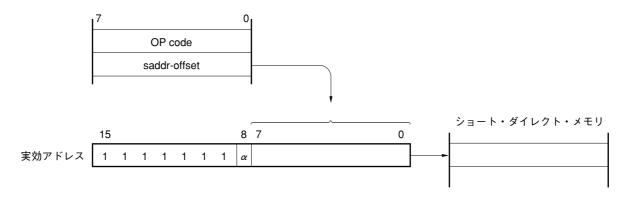

- 3.4.4 ショート・ダイレクト・アドレシング … 64

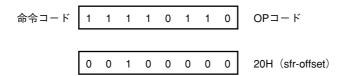

- 3.4.5 特殊機能レジスタ (SFR) アドレシング … 65

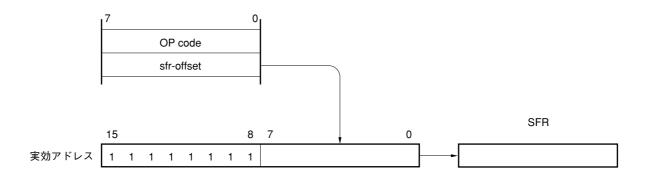

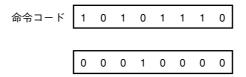

- 3.4.6 レジスタ・インダイレクト・アドレシング … 66

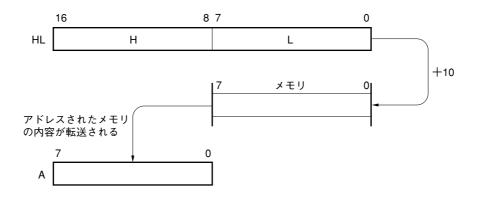

- 3.4.7 ベースト・アドレシング … 67

- 3.4.8 ベースト・インデクスト・アドレシング … 68

- 3.4.9 スタック・アドレシング … 69

## 第4章 ポート機能 … 70

- 4.1 ポートの機能 … 70

- 4.2 ポートの構成 … 72

- 4.2.1 ポート0 … 72

- 4.2.2 ポート1 … 74

- 4.2.3 ポート2 … 75

- 4.2.4 ポート3 … 78

- 4.2.5 ポート4 … 81

- 4.2.6 ポート5 … 82

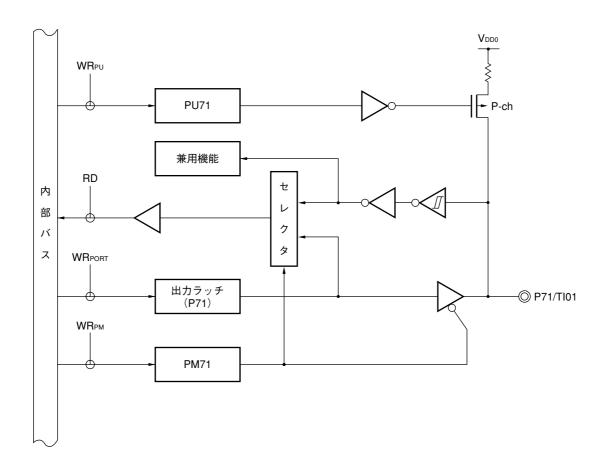

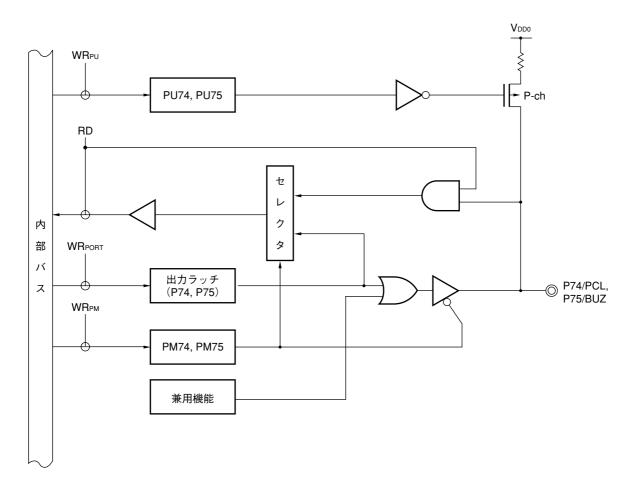

- 4.2.7 ポート7 … 83

- 4.3 ポート機能を制御するレジスタ … 86

- 4.4 ポート機能の動作 … 90

- 4.4.1 入出力ポートへの書き込み … 90

- 4.4.2 入出力ポートからの読み出し … 90

- 4.4.3 入出力ポートでの演算 … 90

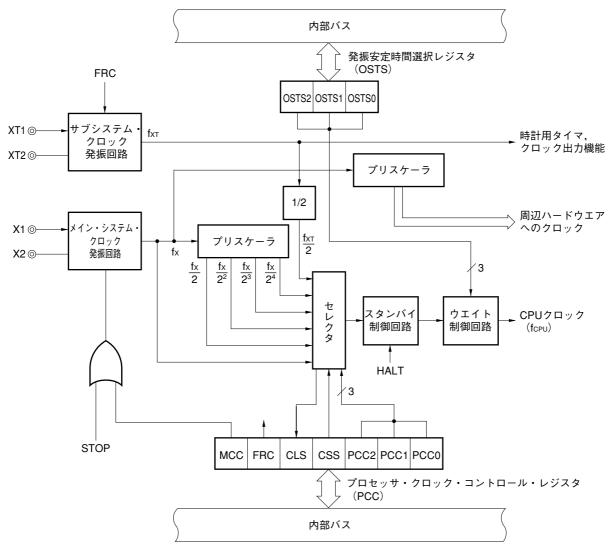

## 第5章 クロック発生回路 … 91

- 5.1 クロック発生回路の機能 … 91

- 5.2 クロック発生回路の構成 … 91

- 5.3 クロック発生回路を制御するレジスタ … 93

- 5.4 システム・クロック発振回路 … 96

- 5.4.1 メイン・システム・クロック発振回路 … 96

- 5.4.2 サブシステム・クロック発振回路 … 97

- 5.4.3 サブシステム・クロックを使用しない場合 … 100

- 5.5 クロック発生回路の動作 … 101

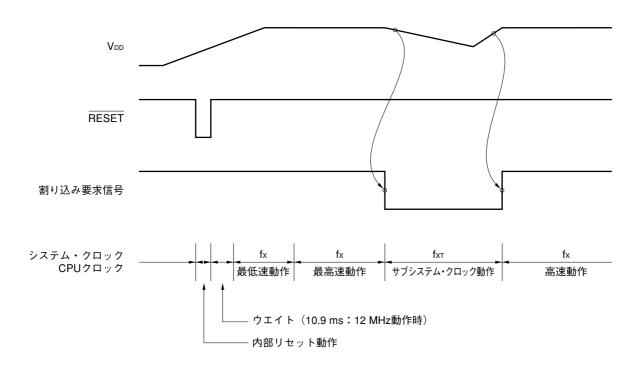

- 5.5.1 メイン・システム・クロックの動作 … 102

- 5.5.2 サブシステム・クロックの動作 … 103

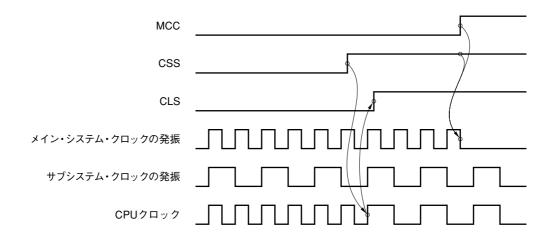

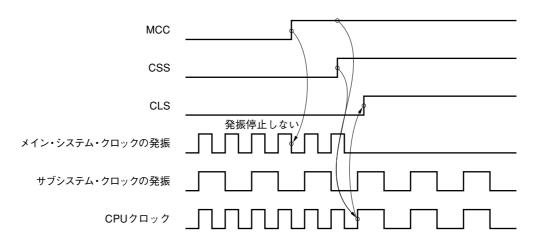

- 5.6 システム・クロックとCPUクロックの設定の変更 … 103

- 5.6.1 システム・クロックとCPUクロックの切り替えに要する時間 … 103

- 5.6.2 システム・クロックとCPUクロックの切り替え手順 … 105

## 第6章 16ビット・タイマ/イベント・カウンタ0 … 106

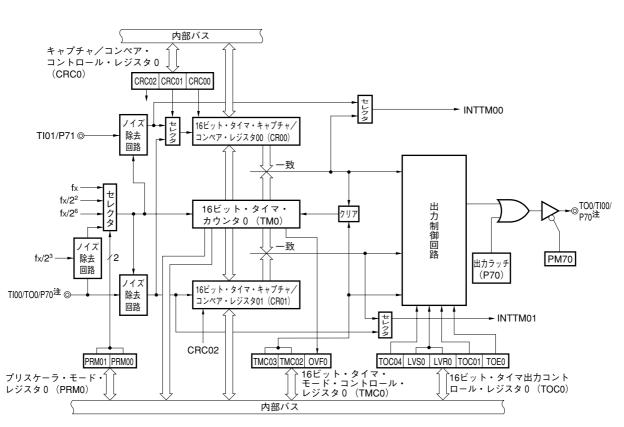

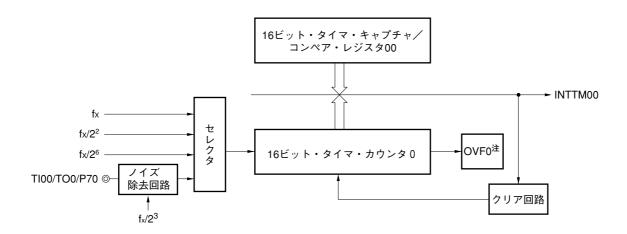

- 6.1 16ビット・タイマ/イベント・カウンタ 0 の機能 … 106

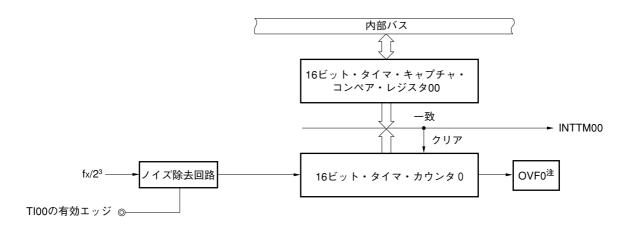

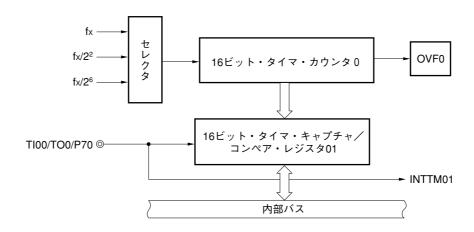

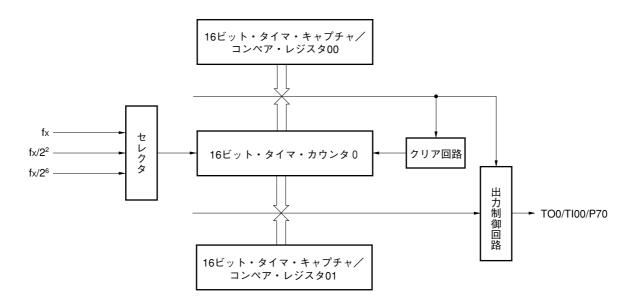

- 6.2 16ビット・タイマ/イベント・カウンタ 0 の構成 … 107

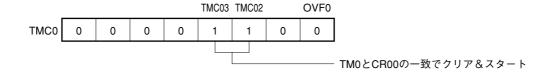

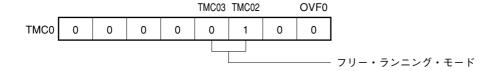

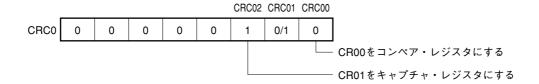

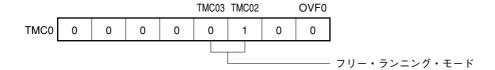

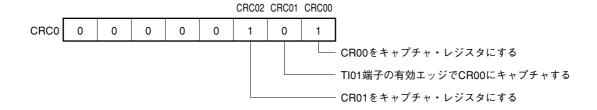

- 6.3 16ビット・タイマ/イベント・カウンタ0を制御するレジスタ … 110

- 6.4 16ビット・タイマ/イベント・カウンタ 0 の動作 … 116

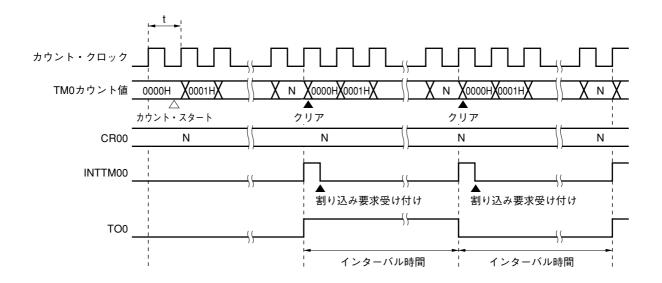

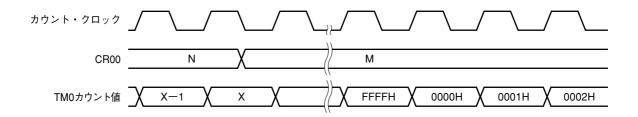

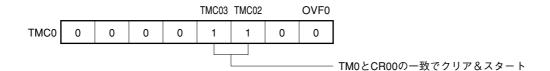

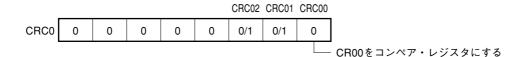

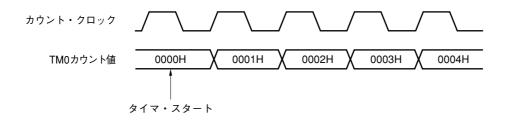

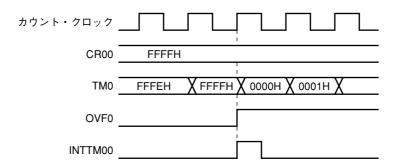

- 6.4.1 インターバル・タイマとしての動作 … 116

- 6.4.2 外部イベント・カウンタとしての動作 … 119

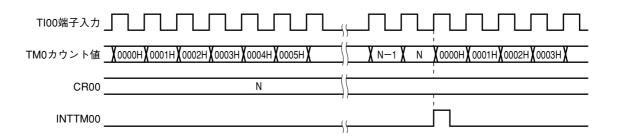

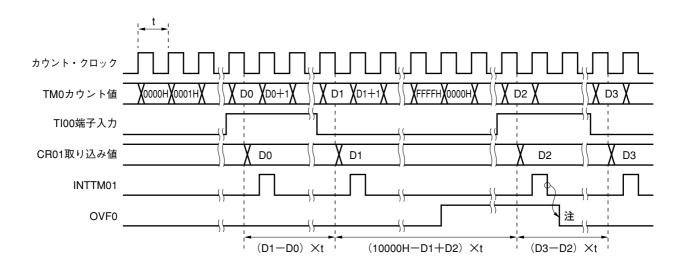

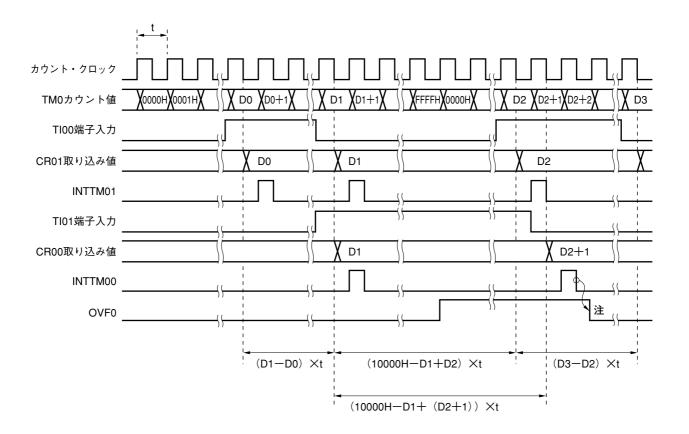

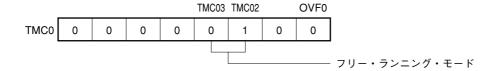

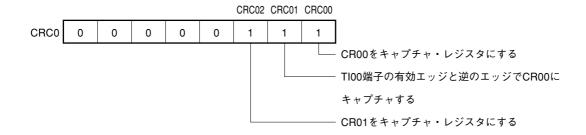

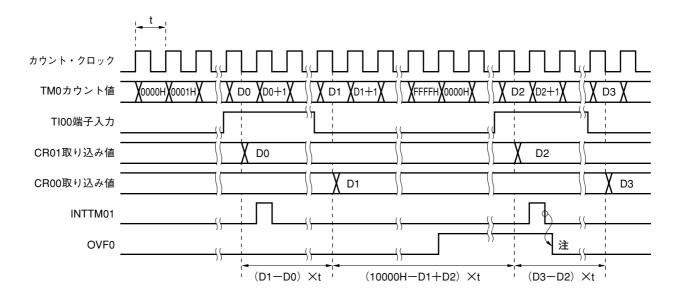

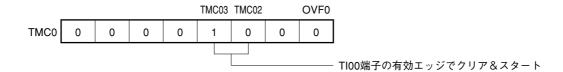

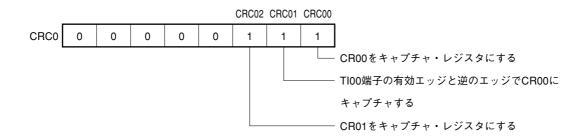

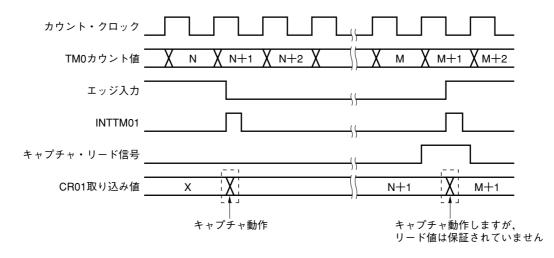

- 6.4.3 パルス幅測定としての動作 … 121

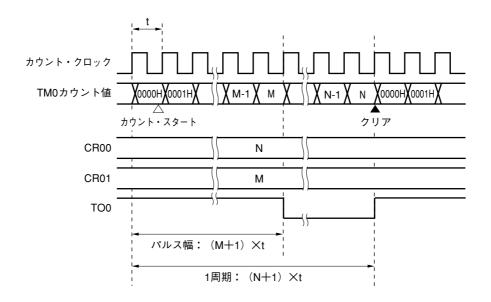

- 6.4.4 方形波出力としての動作 … 128

- 6.4.5 PPG出力としての動作 … 129

- 6.5 プログラム・リスト … 131

- 6.5.1 インターバル・タイマ … 132

- 6.5.2 フリー・ランニング・カウンタとキャプチャ・レジスタ 1 本によるパルス幅測定 … 133

- 6.5.3 フリー・ランニング・カウンタによる2つのパルス幅測定 … 134

- 6.5.4 リスタートによるパルス幅測定 … 136

- 6.5.5 PPG出力 ··· 137

- 6.6 16ビット・タイマ/イベント・カウンタ 0 の注意事項 … 138

## 第7章 8ビット・タイマ/イベント・カウンタ50,51 ··· 142

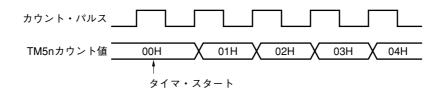

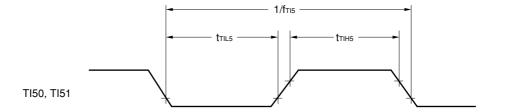

- 7.1 8ビット・タイマ/イベント・カウンタ50.51の機能 … 142

- 7.2 8ビット・タイマ/イベント・カウンタ50,51の構成 … 144

- 7.3 8ビット・タイマ/イベント・カウンタ50,51を制御するレジスタ … 146

- 7.4 8ビット・タイマ/イベント・カウンタ50,51の動作 … 151

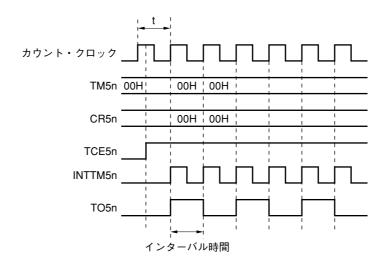

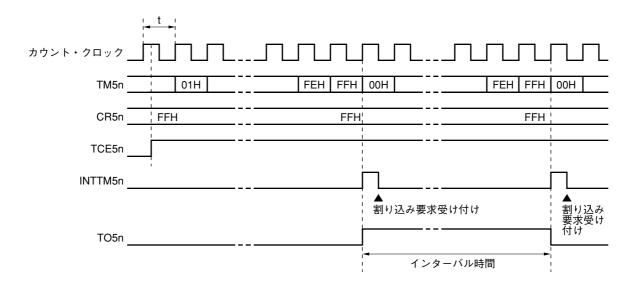

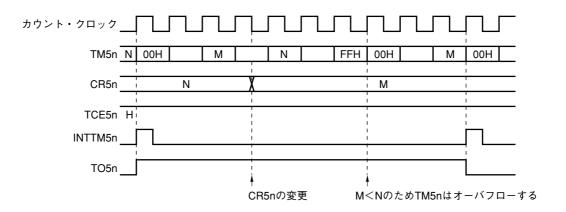

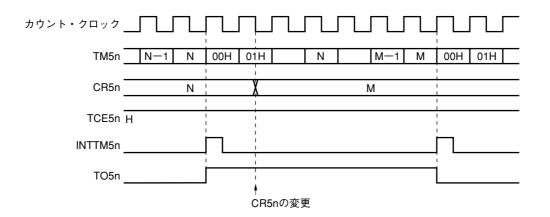

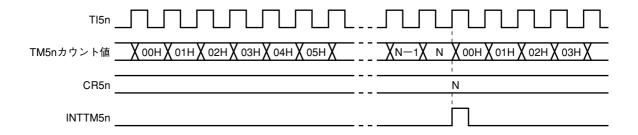

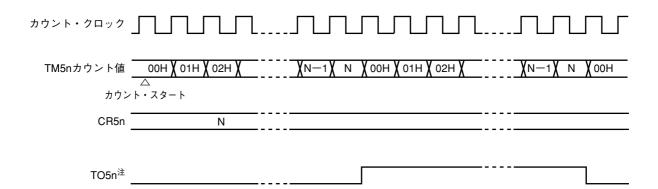

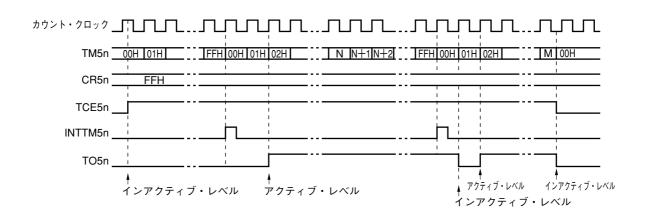

- 7.4.1 インターバル・タイマ(8ビット)としての動作 … 151

- 7.4.2 外部イベント・カウンタとしての動作 … 155

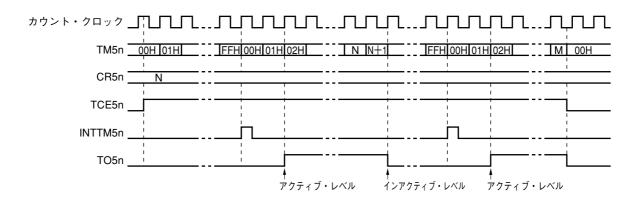

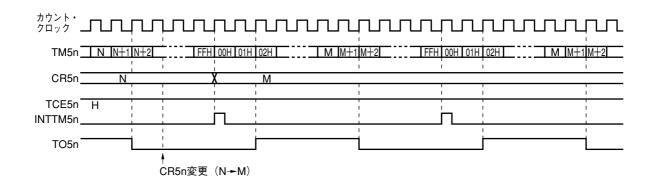

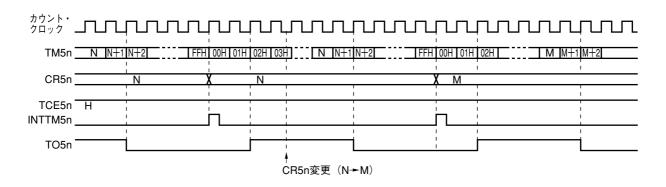

- 7.4.3 方形波出力(8ビット分解能)としての動作 … 156

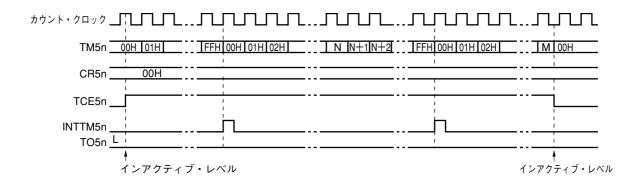

- 7.4.4 8ビットPWM出力としての動作 … 157

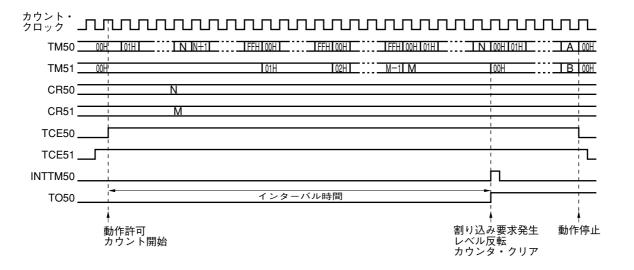

- 7.4.5 インターバル・タイマ(16ビット)としての動作 … 161

- 7.5 プログラム・リスト … 162

- 7.5.1 インターバル・タイマ(8ビット) … 162

- 7.5.2 外部イベント・カウンタ … 163

- 7.5.3 インターバル・タイマ(16ビット) … 164

- 7.6 8ビット・タイマ/イベント・カウンタ50,51の注意事項 … 165

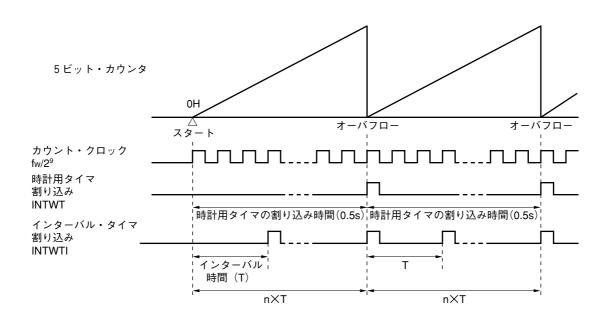

## 第8章 時計用タイマ … 166

- 8.1 時計用タイマの機能 … 166

- 8.2 時計用タイマの構成 … 167

- 8.3 時計用タイマを制御するレジスタ … 168

- 8.4 時計用タイマの動作 … 169

- 8.4.1 時計用タイマとしての動作 … 169

- 8.4.2 インターバル・タイマとしての動作 … 169

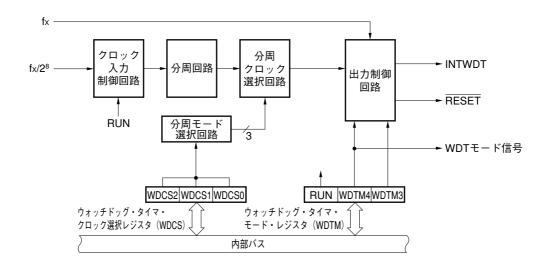

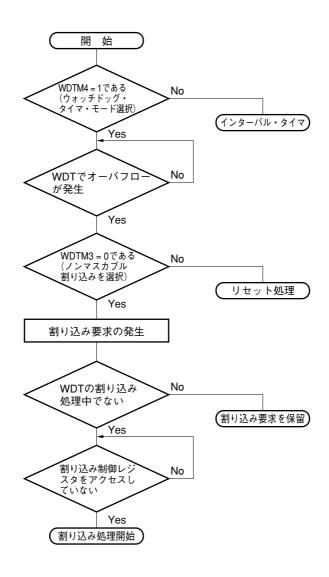

## 第9章 ウォッチドッグ・タイマ … 171

- 9.1 ウォッチドッグ・タイマの機能 … 171

- 9.2 ウォッチドッグ・タイマの構成 … 172

- 9.3 ウォッチドッグ・タイマを制御するレジスタ … 172

- 9.4 ウォッチドッグ・タイマの動作 … 174

- 9.4.1 ウォッチドッグ・タイマとしての動作 … 174

- 9.4.2 インターバル・タイマとしての動作 … 175

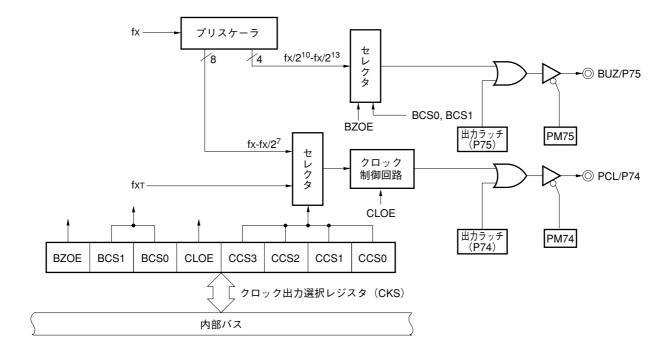

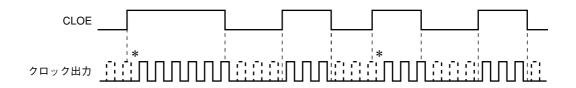

| 第10章                    | クロック出力/ブザー出力制御回路 … 176                                                                                                                                                                                                        |     |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10. 2<br>10. 3          | クロック出力/ブザー出力制御回路の機能 … 176<br>クロック出力/ブザー出力制御回路の構成 … 177<br>クロック出力/ブザー出力制御回路を制御するレジスタ … 177<br>クロック出力/ブザー出力制御回路の動作 … 180<br>10.4.1 クロック出力としての動作 … 180<br>10.4.2 ブザー出力としての動作 … 180                                               |     |

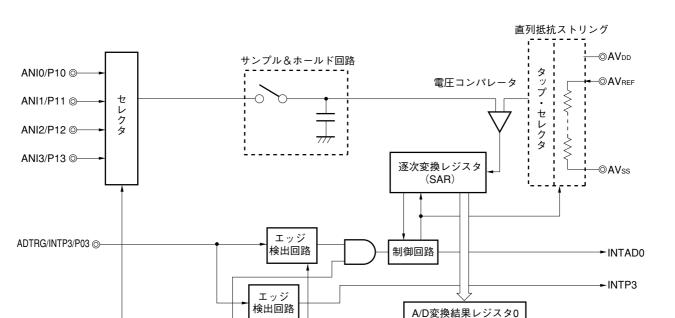

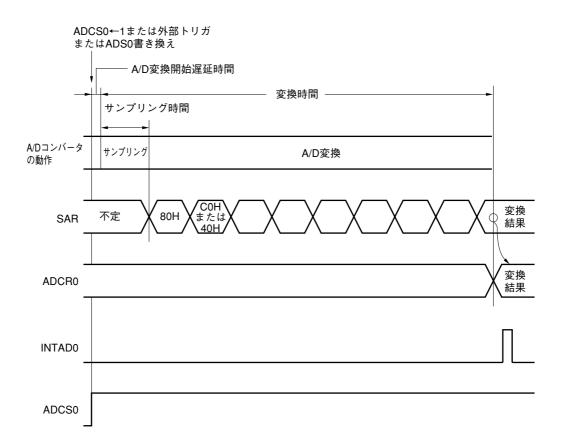

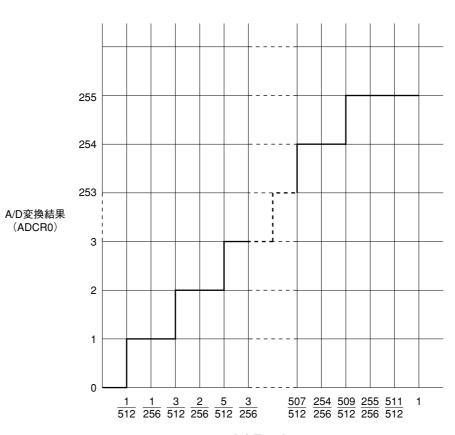

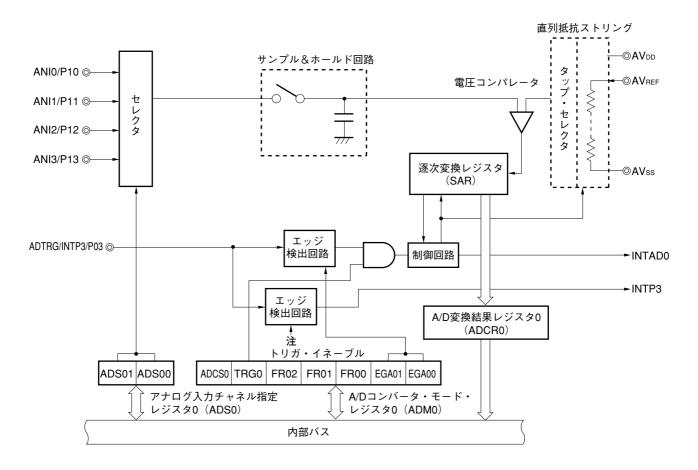

| 第11章                    | 8 ビットA/Dコンバータ( μ PD780024ASサブシリーズ) …                                                                                                                                                                                          | 181 |

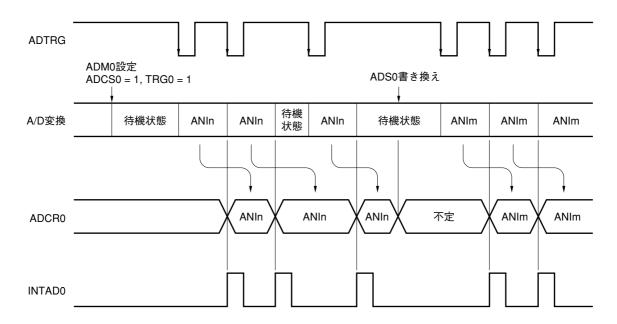

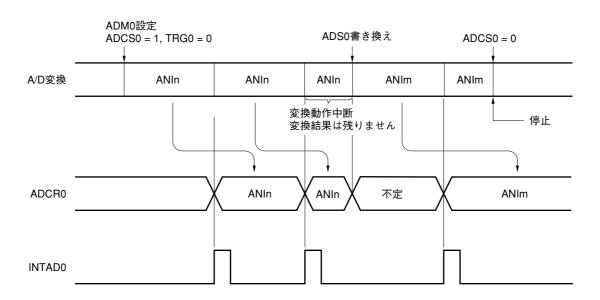

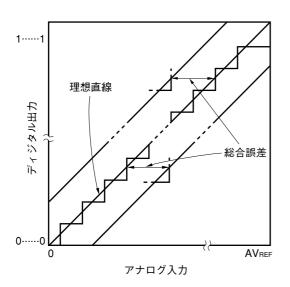

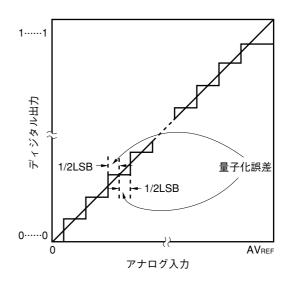

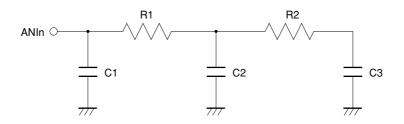

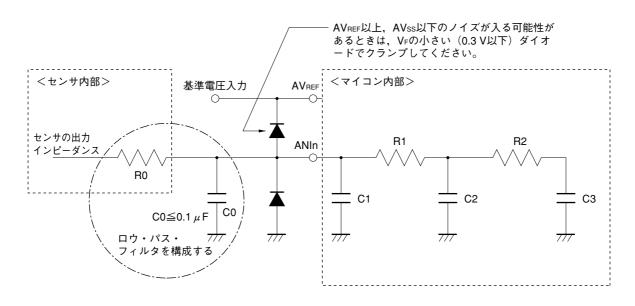

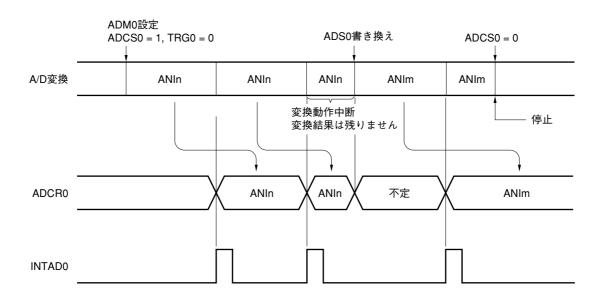

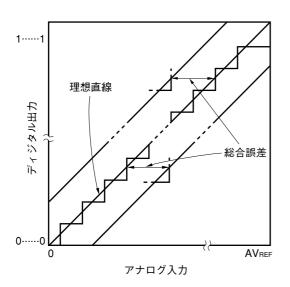

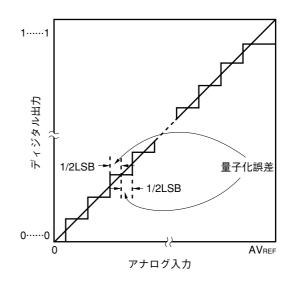

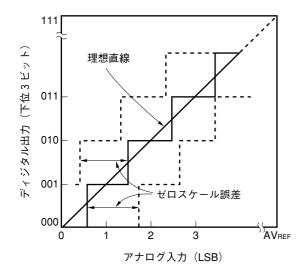

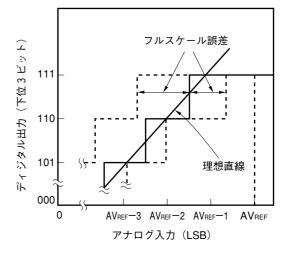

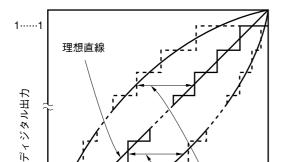

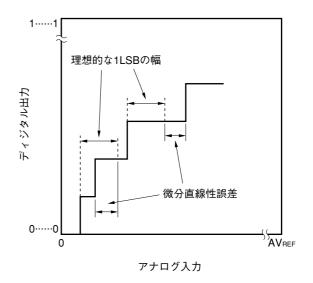

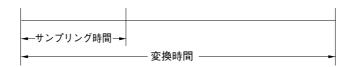

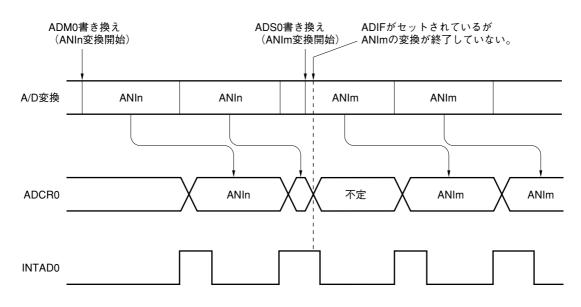

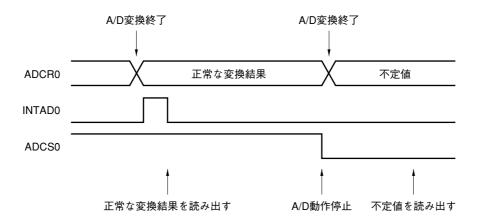

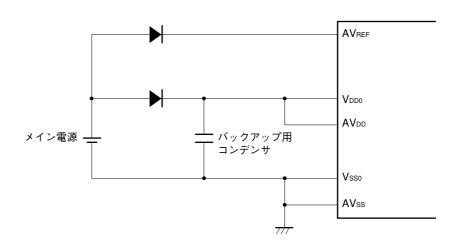

| 11. 2<br>11. 3<br>11. 4 | A/Dコンバータの機能 … 181<br>A/Dコンバータの構成 … 183<br>A/Dコンバータを制御するレジスタ … 185<br>A/Dコンバータの動作 … 188<br>11.4.1 A/Dコンバータの基本動作 … 188<br>11.4.2 入力電圧と変換結果 … 190<br>11.4.3 A/Dコンバータの動作モード … 191                                                 |     |

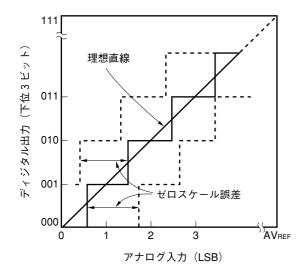

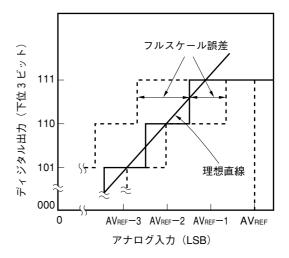

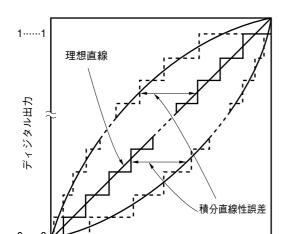

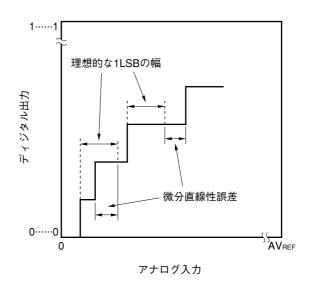

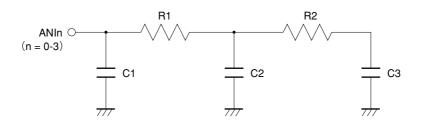

|                         | A/Dコンバータ特性表の読み方 ··· 194<br>A/Dコンバータの注意事項 ··· 197                                                                                                                                                                              |     |

| 第12章                    | 10ビットA/Dコンバータ( μ PD780034ASサブシリーズ) ··· 2                                                                                                                                                                                      | 203 |

| 12. 2<br>12. 3<br>12. 4 | A/Dコンバータの機能 … 203<br>A/Dコンバータの構成 … 205<br>A/Dコンバータを制御するレジスタ … 207<br>A/Dコンバータの動作 … 210<br>12.4.1 A/Dコンバータの基本動作 … 210<br>12.4.2 入力電圧と変換結果 … 212<br>12.4.3 A/Dコンバータの動作モード … 213<br>A/Dコンバータ特性表の読み方 … 216<br>A/Dコンバータの注意事項 … 219 |     |

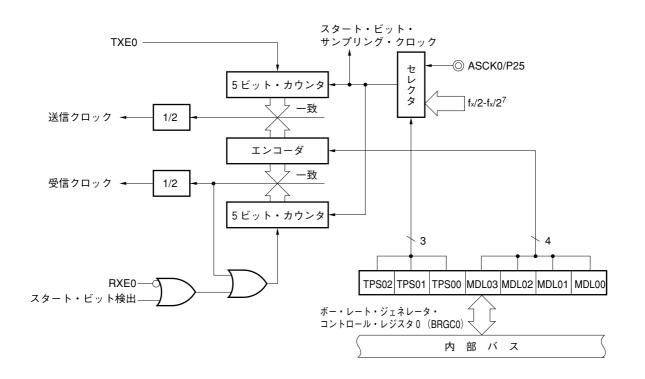

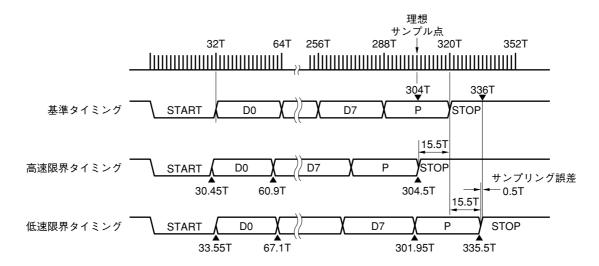

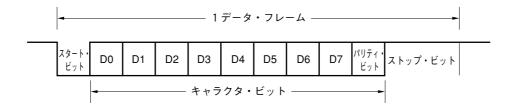

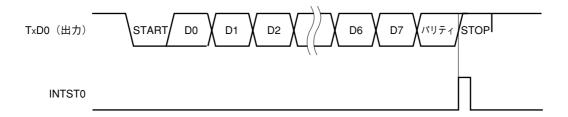

| 第13章                    | シリアル・インタフェース <b>UARTO</b> … 225                                                                                                                                                                                               |     |

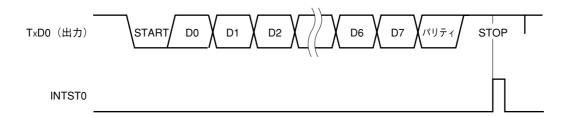

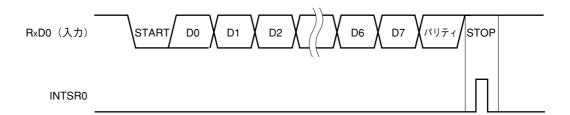

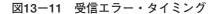

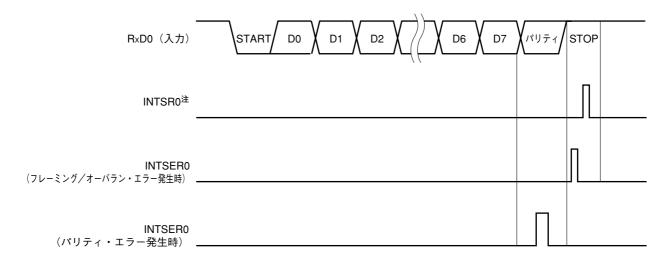

| 13. 2<br>13. 3          | シリアル・インタフェースUARTOの機能 … 225<br>シリアル・インタフェースUARTOの構成 … 227<br>シリアル・インタフェースUARTOを制御するレジスタ … 229<br>シリアル・インタフェースUARTOの動作 … 233<br>13.4.1 動作停止モード … 233<br>13.4.2 アシンクロナス・シリアル・インタフェース(UART)モード … 13.4.3 赤外線データ転送モード … 245         | 234 |

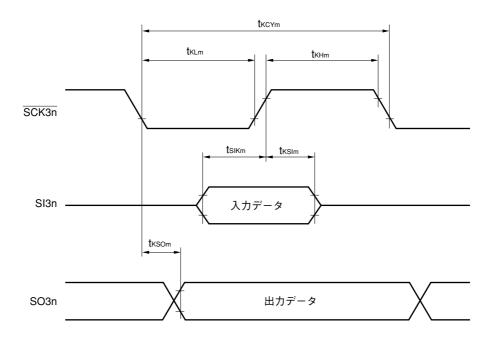

| 第14章                    | シリアル・インタフェースSIO30, SIO31 ··· 253                                                                                                                                                                                              |     |

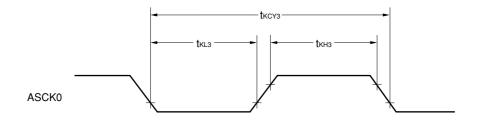

| 14. 2<br>14. 3          | シリアル・インタフェースSIO30, SIO31の機能 … 253<br>シリアル・インタフェースSIO30, SIO31の構成 … 254<br>シリアル・インタフェースSIO30, SIO31を制御するレジスタ … 254<br>シリアル・インタフェースSIO30, SIO31の動作 … 258<br>14.4.1 動作停止モード … 258<br>14.4.2 3線式シリアルI/Oモード … 259                  |     |

## 第15章 割り込み機能 … 264

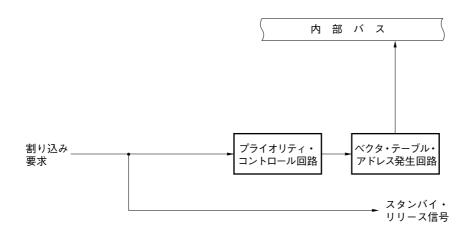

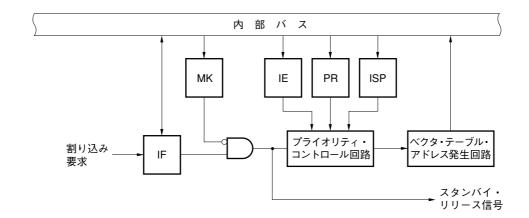

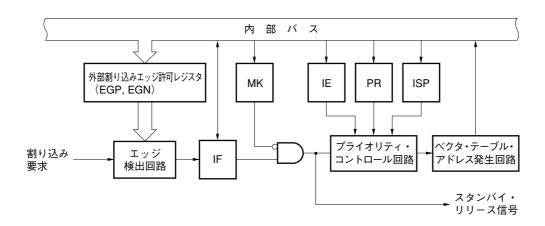

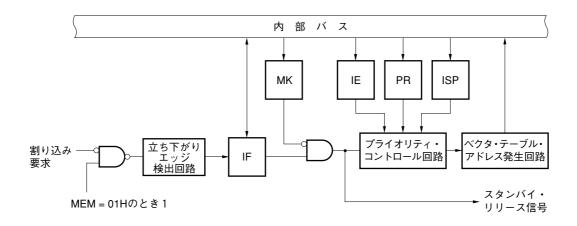

- 15.1 割り込み機能の種類 … 264

- 15.2 割り込み要因と構成 … 264

- 15.3 割り込み機能を制御するレジスタ … 268

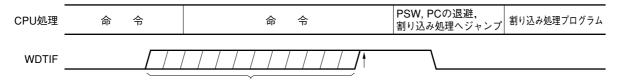

- 15.4 割り込み処理動作 … 275

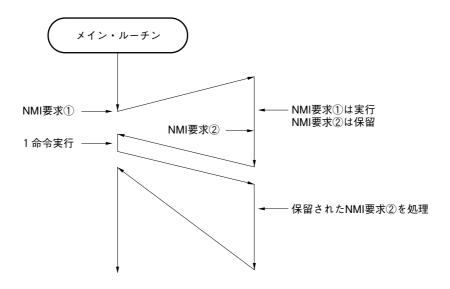

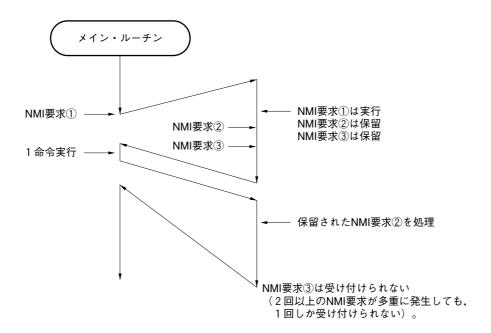

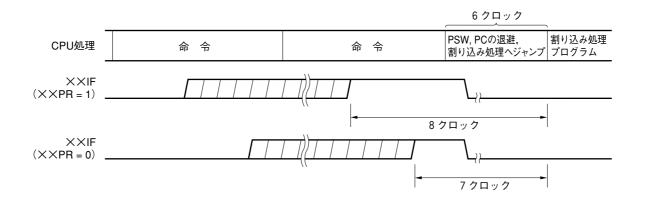

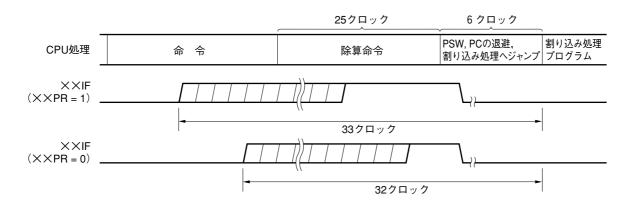

- 15.4.1 ノンマスカブル割り込み要求の受け付け動作 … 275

- 15.4.2 マスカブル割り込み要求の受け付け動作 … 278

- 15.4.3 ソフトウエア割り込み要求の受け付け動作 … 281

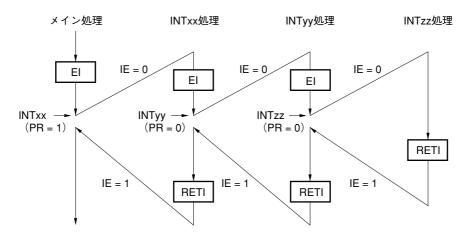

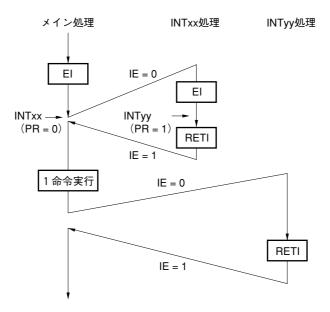

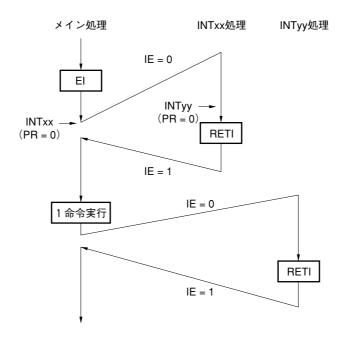

- 15.4.4 多重割り込み処理 … 281

- 15.4.5 割り込み要求の保留 … 285

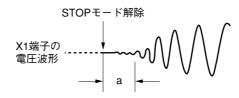

## 第16章 スタンバイ機能 … 286

- 16.1 スタンバイ機能と構成 … 286

- 16.1.1 スタンバイ機能 … 286

- 16.1.2 スタンバイ機能を制御するレジスタ … 287

- 16.2 スタンバイ機能の動作 … 288

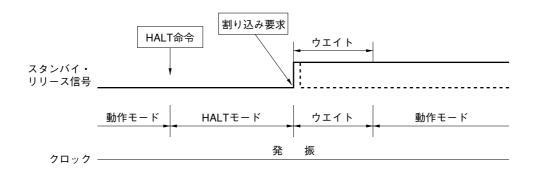

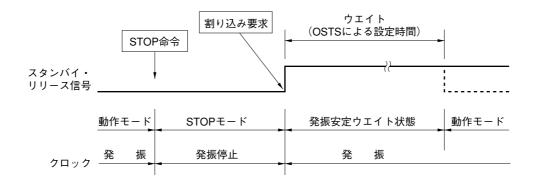

- 16.2.1 HALTモード … 288

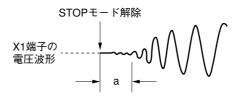

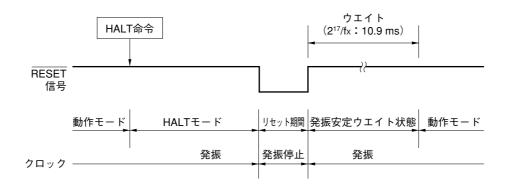

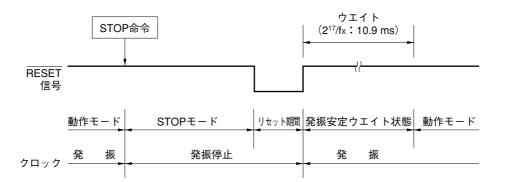

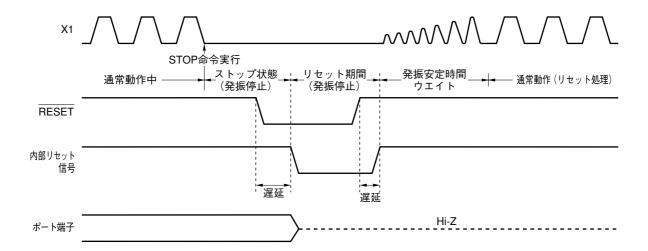

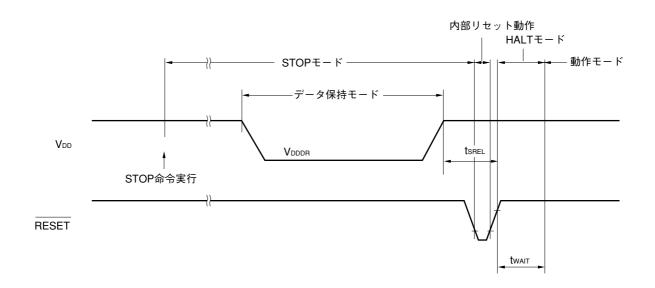

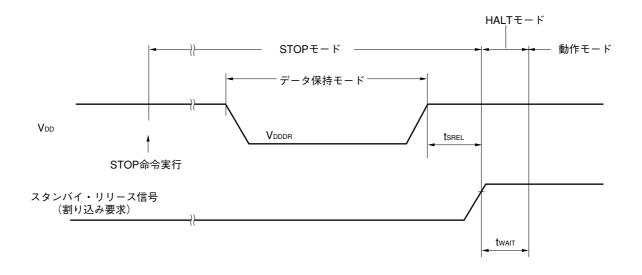

- 16.2.2 STOPモード … 291

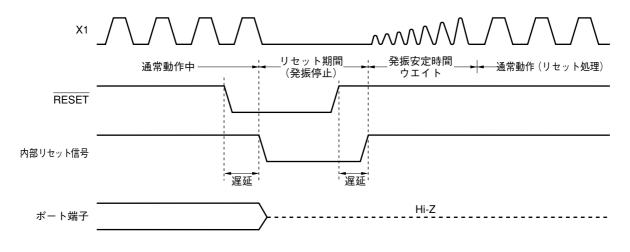

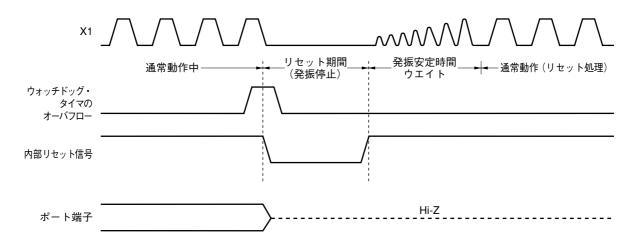

## 第17章 リセット機能 … 294

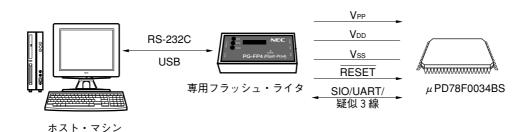

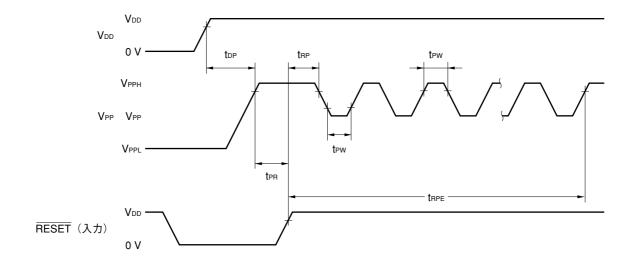

## 第**18**章 μ PD78F0034BS ··· 298

- 18.1 メモリ・サイズ切り替えレジスタ … 299

- 18.2 フラッシュ・メモリの特徴 … 300

- 18.2.1 プログラミング環境 ··· 300

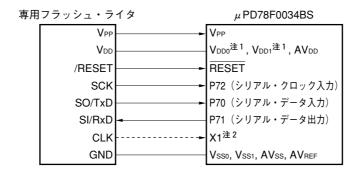

- 18.2.2 通信方式 … 301

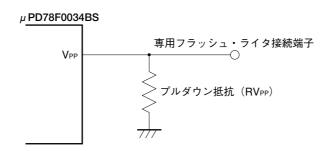

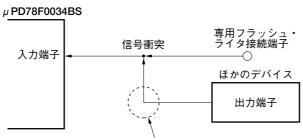

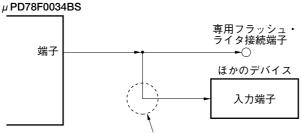

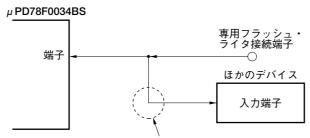

- 18.2.3 オンボード上の端子処理 … 304

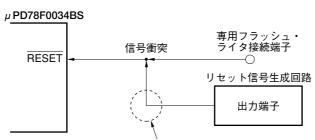

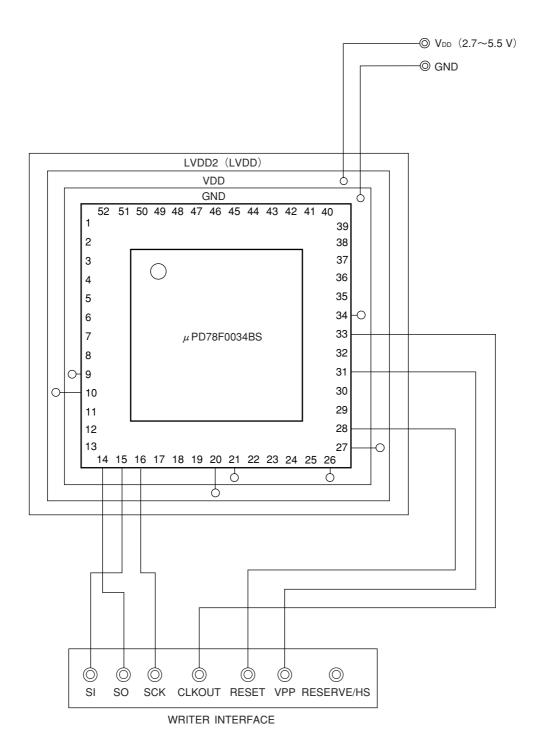

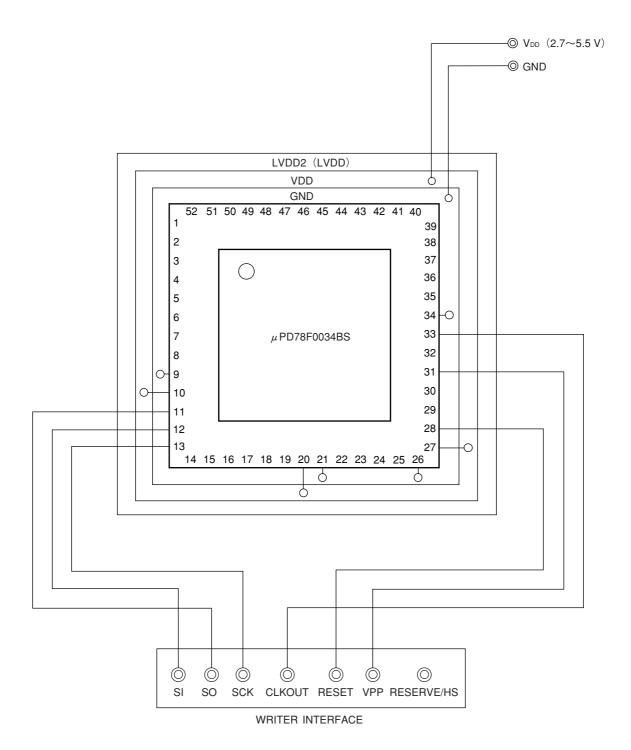

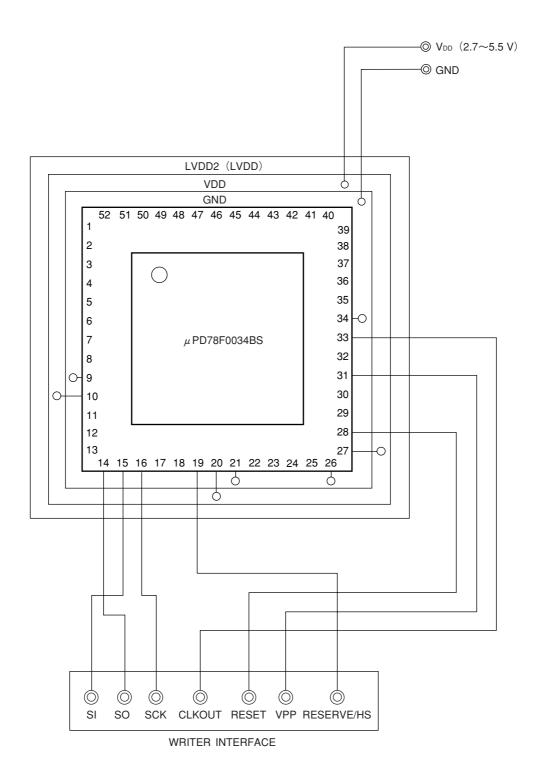

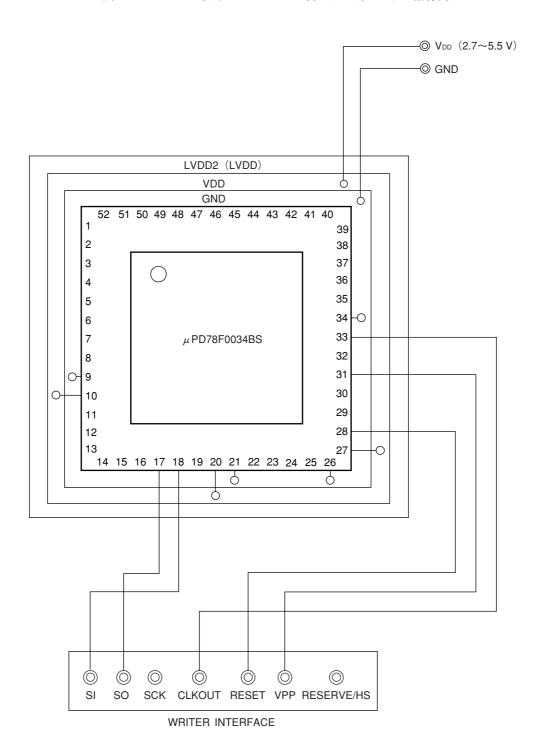

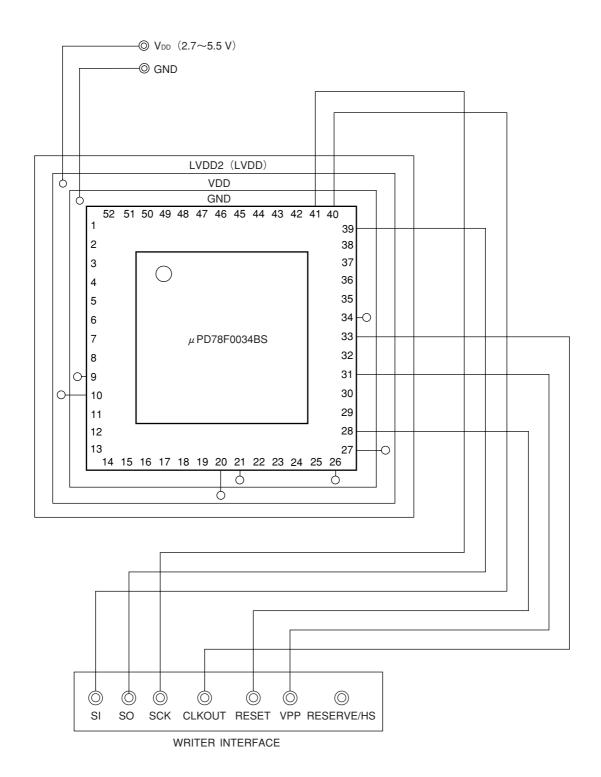

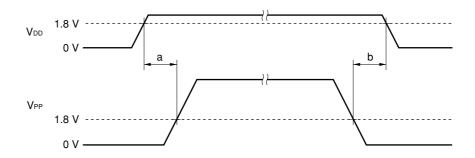

- 18.2.4 フラッシュ書き込み用アダプタの接続 … 307

## 第19章 命令セットの概要 … 312

- 19.1 凡 例 … 313

- 19.1.1 オペランドの表現形式と記述方法 … 313

- 19.1.2 オペレーション欄の説明 … 314

- 19.1.3 フラグ動作欄の説明 … 314

- 19.2 オペレーション一覧 … 315

- 19.3 アドレシング別命令一覧 … 323

## **第20章 電気的特性 … 327**

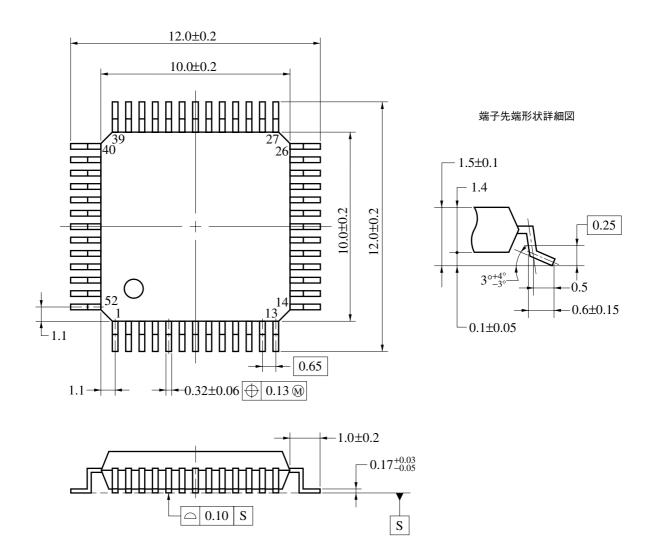

第21章 外形図 … 349

第22章 半田付け推奨条件 … 350

付録 A μ PD780024A, 780024AS, 780034A, 780034ASサブシリーズ間の違い … 352

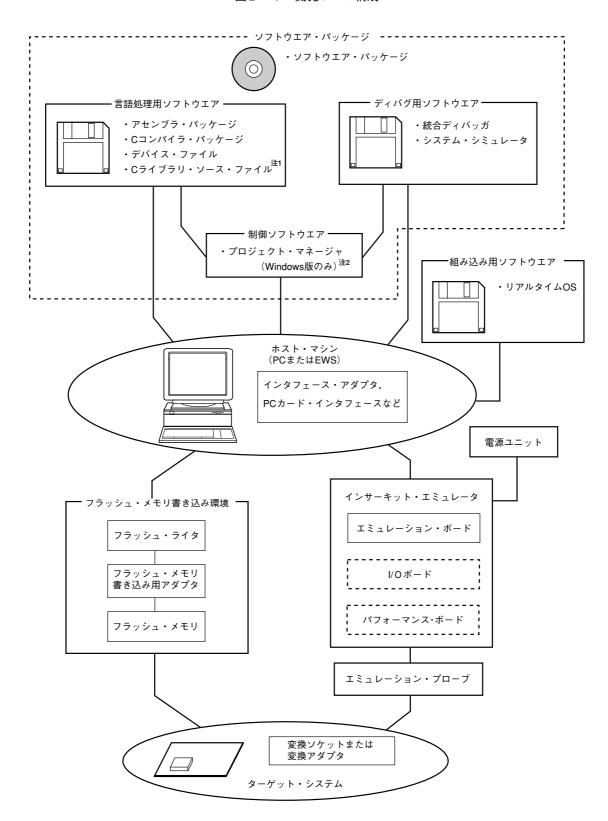

付録B 開発ツール … 354

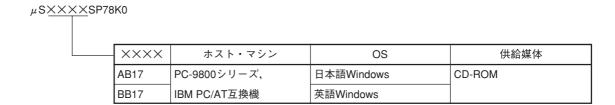

B.1 ソフトウエア・パッケージ … 356

- B.2 言語処理用ソフトウエア … 356

- B.3 制御ソフトウエア ··· 357

- B.4 フラッシュ・メモリ書き込み用ツール … 357

- B.5 ディバグ用ツール (ハードウエア) … 358

- B.6 ディバグ用ツール (ソフトウエア) ··· 359

- B.7 組み込み用ソフトウエア … 360

## 付録C ターゲット・システム設計上の注意 … 361

## 付録D レジスタ索引 … 363

- D.1 レジスタ索引(50音順) … 363

- D.2 レジスタ索引 (アルファベット順) … 366

## 付録E 改版履歴 … 369

- E.1 本版で改訂された主な箇所 … 369

- E.2 前版までの改版履歴 … 370

## 第1章 概 説

## 1.1 特 徵

## ○内部メモリ

|                       | 項 | 目 プログラム・メモリ          | データ・メモリ              |

|-----------------------|---|----------------------|----------------------|

| 品名                    |   | (ROM/フラッシュ・メヨ        | Eリ) (高速RAM)          |

| μPD780021AS, 780031AS |   | 8 Kバイト               | 512バイト               |

| μPD780022AS, 780032AS |   | 16 Kバイト              |                      |

| μPD780023AS, 780033AS |   | 24 Kバイト              | 1024バイト              |

| μPD780024AS, 780034AS |   | 32 Kバイト              |                      |

| μPD78F0034BS          |   | 32 Kバイト <sup>注</sup> | 1024バイト <sup>注</sup> |

- 注 メモリ・サイズ切り替えレジスタ(IMS)により、内部フラッシュ・メモリ、内部高速RAM容量の変更可能。

- ○外部メモリ拡張空間:64 Kバイト

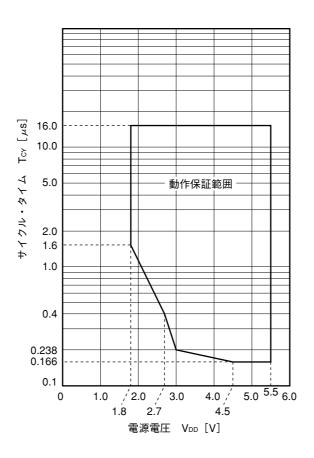

- ○高速( $0.166 \, \mu s$ :メイン・システム・クロック12 MHz,  $V_{DD} = 4.5 \sim 5.5 \, V$ 動作時)から超低速( $122 \, \mu s$ :サブシステム・クロック $32.768 \, k$ Hz動作時)まで最小命令実行時間変更可能

- ○システム制御に適した命令セット

- ・全アドレス空間でビット処理可能

- · 乗除算命令内蔵

- ○I/Oポート:39本

- $\bigcirc$  8 ビット分解能A/Dコンバータ : 4 チャネル(  $\mu$  PD780024ASサブシリーズのみ)

- ○10ビット分解能A/Dコンバータ : 4 チャネル (μPD780034ASサブシリーズのみ)

- ○シリアル・インタフェース : 3チャネル・3線式シリアルI/Oモード : 2チャネル・UARTモード : 1チャネル

- ○タイマ:5チャネル

- ・16ビット・タイマ/イベント・カウンタ:1 チャネル

- ・8ビット・タイマ/イベント・カウンタ:2チャネル

- ・時計用タイマ : 1 チャネル・ウォッチドッグ・タイマ : 1 チャネル

- ○ベクタ割り込み要因:20

- 2 種類のクロック発振回路内蔵(メイン・システム・クロックとサブシステム・クロック)

- ○電源電圧: V<sub>DD</sub> = 1.8~5.5 V

## 1.2 応用分野

μPD780021AS, 780022AS, 780023AS, 780024AS μPD780031AS, 780032AS, 780033AS, 780034AS, 78F0034BSの場合 家電製品, ページャ, AV機器, カー・オーディオ, OA機器など

$\mu$ PD780021AS(A), 780022AS(A), 780023AS(A), 780024AS(A)  $\mu$ PD780031AS(A), 780032AS(A), 780033AS(A), 780034AS(A), 78F0034BS(A)の場合

★ 輸送機器の制御装置、ガス検知遮断機、各種安全装置、自動車電装など

## 1.3 オーダ情報

| オーダ名称                                         | パッケージ                  | 内部ROM     |

|-----------------------------------------------|------------------------|-----------|

| μPD780021ASGB-XXX-8ET                         | 52ピン・プラスチックLQFP(10x10) | マスクROM    |

| $\mu$ PD780022ASGB- $\times$ $\times$ -8ET    | "                      | "         |

| $\mu$ PD780023ASGB- $\times$ $\times$ -8ET    | "                      | "         |

| $\mu$ PD780024ASGB- $\times$ $\times$ -8ET    | "                      | "         |

| $\mu$ PD780031ASGB- $\times$ $\times$ -8ET    | //                     | "         |

| $\mu$ PD780032ASGB- $\times$ $\times$ -8ET    | "                      | "         |

| $\mu$ PD780033ASGB- $\times$ $\times$ -8ET    | //                     | "         |

| $\mu$ PD780034ASGB- $\times$ $\times$ -8ET    | //                     | "         |

| $\mu$ PD780021ASGB(A)- $\times$ $\times$ -8ET | //                     | "         |

| $\mu$ PD780022ASGB(A)- $\times$ $\times$ -8ET | //                     | "         |

| $\mu$ PD780023ASGB(A)- $\times$ $\times$ -8ET | //                     | "         |

| $\mu$ PD780024ASGB(A)- $\times$ $\times$ -8ET | //                     | "         |

| $\mu$ PD780031ASGB(A)- $\times$ $\times$ -8ET | //                     | "         |

| $\mu$ PD780032ASGB(A)- $\times$ $\times$ -8ET | //                     | "         |

| $\mu$ PD780033ASGB(A)- $\times$ $\times$ -8ET | //                     | "         |

| $\mu$ PD780034ASGB(A)- $\times$ $\times$ -8ET | //                     | "         |

| $\mu$ PD78F0034BSGB-8ET                       | "                      | フラッシュ・メモリ |

| $\mu$ PD78F0034BSGB(A)-8ET                    | //                     | "         |

備考 ×××はROMコード番号です。

## 1.4 品質水準

| オーダ名称                                         | パッケージ                  | 品質水準          |

|-----------------------------------------------|------------------------|---------------|

| μPD780021ASGB-XXX-8ET                         | 52ピン・プラスチックLQFP(10x10) | 標準(一般電子機器用)   |

| $\mu$ PD780022ASGB- $\times$ $\times$ -8ET    | ,                      | "             |

| $\mu$ PD780023ASGB- $\times$ $\times$ -8ET    | ,                      | "             |

| $\mu$ PD780024ASGB- $\times$ $\times$ -8ET    | "                      | "             |

| $\mu$ PD780031ASGB- $\times$ $\times$ -8ET    | ,                      | "             |

| $\mu$ PD780032ASGB- $\times$ $\times$ -8ET    | ,                      | "             |

| $\mu$ PD780033ASGB- $\times$ $\times$ -8ET    | "                      | "             |

| $\mu$ PD780034ASGB- $\times$ $\times$ -8ET    | ,                      | "             |

| $\mu$ PD78F0034BSGB-8ET                       | ,                      | "             |

| $\mu$ PD780021ASGB(A)- $\times$ $\times$ -8ET | "                      | 特別(高信頼度電子機器用) |

| $\mu$ PD780022ASGB(A)- $\times$ $\times$ -8ET | ,                      | "             |

| $\mu$ PD780023ASGB(A)- $\times$ $\times$ -8ET | "                      | "             |

| $\mu$ PD780024ASGB(A)- $\times$ $\times$ -8ET | "                      | "             |

| $\mu$ PD780031ASGB(A)- $\times$ $\times$ -8ET | "                      | "             |

| $\mu$ PD780032ASGB(A)- $\times$ $\times$ -8ET | "                      | "             |

| $\mu$ PD780033ASGB(A)- $\times$ $\times$ -8ET | "                      | "             |

| $\mu$ PD780034ASGB(A)- $\times$ $\times$ -8ET | "                      | "             |

| $\mu$ PD78F0034BSGB(A)-8ET                    | "                      | "             |

備考 ×××はROMコード番号です。

品質水準とその応用分野の詳細については当社発行の資料  $\lceil NEC +$  半導体デバイスの品質水準  $\rfloor$  (C11531J) をご覧ください。

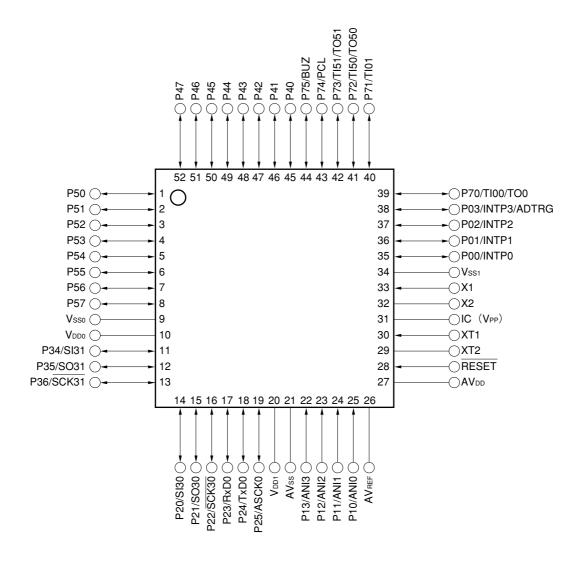

## 1.5 端子接続図(Top View)

・52ピン・プラスチックLQFP(10x10)

$\mu$ PD780021ASGB- $\times$  $\times$  $\times$ -8ET, 780022ASGB- $\times$  $\times$  $\times$ -8ET, 780023ASGB- $\times$  $\times$  $\times$ -8ET, 780024ASGB- $\times$  $\times$  $\times$ -8ET, 780031ASGB- $\times$  $\times$  $\times$ -8ET, 780032ASGB- $\times$  $\times$  $\times$ -8ET, 780033ASGB- $\times$  $\times$  $\times$ -8ET, 780034ASGB- $\times$  $\times$  $\times$ -8ET, 780034ASGB-8ET, 780021ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780022ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780032ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780034ASGB(A)- $\times$  $\times$  $\times$ -8ET, 780034BSGB(A)-8ET

- 注意 1. IC(Internally Connected)端子はVssoまたはVssoに直接接続してください。

- 2. AVssはVssoに接続してください。

- **備考1.** マイコン内部から発生するノイズを低減する必要がある応用分野で使用する場合、VDDOとVDD1に個別の電源を供給し、VSSOとVSS1を別々のグランド・ラインに接続するなどのノイズ対策を行うことを推奨します。

- 2. ( )内は $\mu$ PD78F0034BS, 78F0034BS(A)のとき。

ADTRG : AD Trigger Input P70-P75 : Port7

ANI0-ANI3 : Analog Input PCL : Programmable Clock

ASCK0 : Asynchronous Serial Clock RESET : Reset

$AV_{DD}$ : Analog Power Supply RxD0 : Receive Data AVREF SCK30, SCK31 : Serial Clock : Analog Reference Voltage AVss SI30, SI31 : Analog Ground : Serial Input BUZ : Buzzer Clock SO30,SO31 : Serial Output IC : Internally Connected TI00, TI01, TI50, TI51: Timer Input INTP0-INTP3 : External Interrupt Input TO0, TO50, TO51 : Timer Output

P00-P03 : Port0 TxD0 : Transmit Data

P10-P13 : Port1 VDD0, VDD1 : Power Supply

P20-P25 : Port2 VPP : Programming Power Supply

P34-P36 : Port3 Vsso, Vss1 : Ground

P40-P47 : Port4 X1, X2 : Crystal (Main System Clock)

P50-P57 : Port5 XT1, XT2 : Crystal (Subsystem Clock)

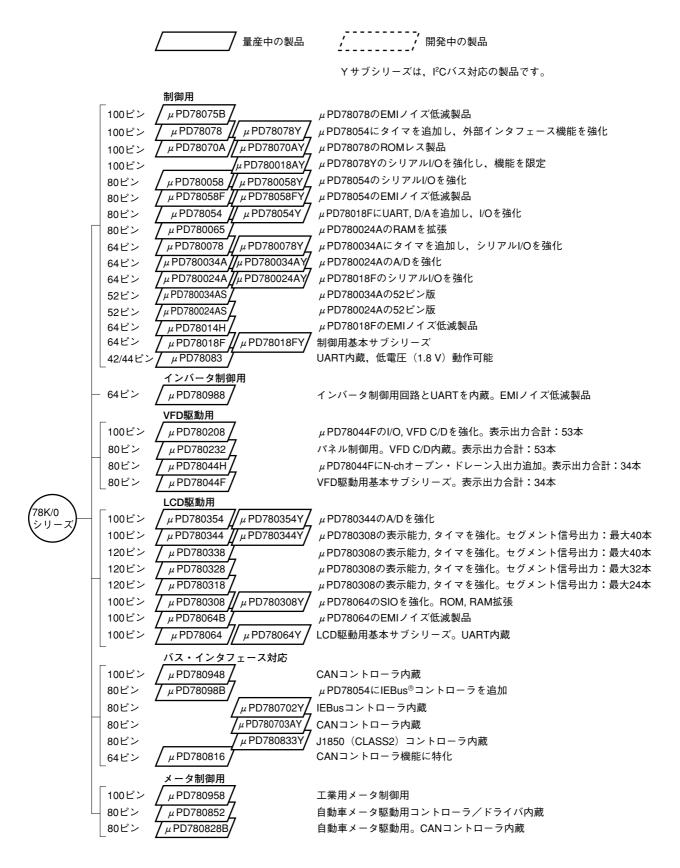

## 1.6 78K/0シリーズの展開

78K/0シリーズの製品展開を次に示します。枠内はサブシリーズ名称です。

備考 蛍光表示管の一般的な英語名称はVFD(Vacuum Fluorescent Display)ですが、ドキュメントによってはFIP®(Fluorescent Indicator Panel)と記述しているものがあります。VFDとFIPは同等の機能です。

各サブシリーズ間の主な機能の違いを次に示します。

## ・Yなしサブシリーズ

|        | 機能          | ROM容量     |       | タイ     | (マ  |     | 8-bit | 10-bit | 8-bit | シリアル・            | I/O | V <sub>DD</sub> | 外部 |

|--------|-------------|-----------|-------|--------|-----|-----|-------|--------|-------|------------------|-----|-----------------|----|

| サブシリ-  | -ズ名         | (バイト)     | 8-bit | 16-bit | 時計  | WDT | A/D   | A/D    | D/A   | インタフェース          |     | MIN.值           | 拡張 |

| 制御用    | μPD78075B   | 32 K-40 K | 4ch   | 1ch    | 1ch | 1ch | 8ch   | _      | 2ch   | 3ch(UART:1ch)    | 88本 | 1.8 V           | 0  |

|        | μPD78078    | 48 K-60 K |       |        |     |     |       |        |       |                  |     |                 |    |

|        | μPD78070A   | _         |       |        |     |     |       |        |       |                  | 61本 | 2.7 V           |    |

|        | μPD780058   | 24 K-60 K | 2ch   |        |     |     |       |        |       | 3ch(時分割UART:1ch) | 68本 | 1.8 V           | -  |

|        | μPD78058F   | 48 K-60 K |       |        |     |     |       |        |       | 3ch(UART:1ch)    | 69本 | 2.7 V           |    |

|        | μPD78054    | 16 K-60 K |       |        |     |     |       |        |       |                  |     | 2.0 V           |    |

|        | μPD780065   | 40 K-48 K |       |        |     |     |       |        | _     | 4ch(UART:1ch)    | 60本 | 2.7 V           |    |

|        | μPD780078   | 48 K-60K  |       | 2ch    |     |     | -     | 8ch    |       | 3ch(UART:2ch)    | 52本 | 1.8 V           |    |

|        | μPD780034A  | 8 K-32 K  |       | 1ch    |     |     |       |        |       | 3ch(UART:1ch)    | 51本 | 1               |    |

|        | μPD780024A  |           |       |        |     |     | 8ch   | _      |       |                  |     |                 |    |

|        | μPD780034AS |           |       |        |     |     | _     | 4ch    |       |                  | 39本 | 1               | _  |

|        | μPD780024AS |           |       |        |     |     | 4ch   | _      |       |                  |     |                 |    |

|        | μPD78014H   |           |       |        |     |     | 8ch   |        |       | 2ch              | 53本 |                 | 0  |

|        | μPD78018F   | 8 K-60 K  |       |        |     |     |       |        |       |                  |     |                 |    |

|        | μPD78083    | 8 K-16 K  |       | _      | _   |     |       |        |       | 1ch(UART:1ch)    | 33本 | ]               | _  |

| インバータ  | μPD780988   | 16 K-60 K | 3ch   | 注      | _   | 1ch | _     | 8ch    | _     | 3ch(UART:2ch)    | 47本 | 4.0 V           | 0  |

| 制御用    |             |           |       |        |     |     |       |        |       |                  |     |                 |    |

| VFD    | μPD780208   | 32 K-60 K | 2ch   | 1ch    | 1ch | 1ch | 8ch   | _      | _     | 2ch              | 74本 | 2.7 V           | _  |

| 駆動用    | μPD780232   | 16 K-24 K | 3ch   | _      | _   |     | 4ch   |        |       |                  | 40本 | 4.5 V           |    |

|        | μPD78044H   | 32 K-48 K | 2ch   | 1ch    | 1ch |     | 8ch   |        |       | 1ch              | 68本 | 2.7 V           |    |

|        | μPD78044F   | 16 K-40 K |       |        |     |     |       |        |       | 2ch              |     |                 |    |

| LCD    | μPD780354   | 24K-32 K  | 4ch   | 1ch    | 1ch | 1ch | _     | 8ch    | _     | 3ch(UART:1ch)    | 66本 | 1.8 V           | _  |

| 駆動用    | μPD780344   |           |       |        |     |     | 8ch   | _      |       |                  |     |                 |    |

|        | μPD780338   | 48 K-60 K | 3ch   | 2ch    |     |     | -     | 10ch   | 1ch   | 2ch (UART:1ch)   | 54本 |                 |    |

|        | μPD780328   |           |       |        |     |     |       |        |       |                  | 62本 |                 |    |

|        | μPD780318   |           |       |        |     |     |       |        |       |                  | 70本 |                 |    |

|        | μPD780308   | 48 K-60 K | 2ch   | 1ch    |     |     | 8ch   | _      | _     | 3ch(時分割UART:1ch) | 57本 | 2.0 V           |    |

|        | μPD78064B   | 32 K      |       |        |     |     |       |        |       | 2ch (UART:1ch)   |     |                 |    |

|        | μPD78064    | 16 K-32 K |       |        |     |     |       |        |       |                  |     |                 |    |

| バス・イン  | μPD780948   | 60 K      | 2ch   | 2ch    | 1ch | 1ch | 8ch   | _      | _     | 3ch(UART:1ch)    | 79本 | 4.0 V           | 0  |

| タフェース  | μPD78098B   | 40 K-60 K |       | 1ch    |     |     |       |        | 2ch   |                  | 69本 | 2.7 V           | _  |

| 対応     | μPD780816   | 32 K-60 K |       | 2ch    |     |     | 12ch  |        | _     | 2ch (UART:1ch)   | 46本 | 4.0 V           | L  |

| メータ    | μPD780958   | 48 K-60 K | 4ch   | 2ch    | _   | 1ch | _     | _      | _     | 2ch (UART:1ch)   | 69本 | 2.2 V           | _  |

| 制御用    |             |           |       |        |     |     |       |        |       |                  |     |                 |    |

| ダッシュ   | μPD780852   | 32 K-40 K | 3ch   | 1ch    | 1ch | 1ch | 5ch   | _      | _     | 3ch(UART:1ch)    | 56本 | 4.0 V           | -  |

| ボード制御用 | μPD780828B  | 32 K-60 K |       |        |     |     |       |        |       |                  | 59本 | ]               |    |

注 16ビット・タイマ: 2チャネル

10ビット・タイマ:1 チャネル

## ・Yサブシリーズ

| 機能F     |             | ROM容量     | タイマ   |        | 8-bit | 10-bit | 8-bit | シリアル・ | I/O | V <sub>DD</sub>            | 外部  |       |    |

|---------|-------------|-----------|-------|--------|-------|--------|-------|-------|-----|----------------------------|-----|-------|----|

| サブシリーズ名 |             | (バイト)     | 8-bit | 16-bit | 時計    | WDT    | A/D   | A/D   | D/A | インタフェース                    |     | MIN.值 | 拡張 |

| 制御用     | μPD78078Y   | 48 K-60 K | 4ch   | 1ch    | 1ch   | 1ch    | 8ch   | _     | 2ch | 3ch(UART:1ch,              | 88本 | 1.8 V | 0  |

|         | μ PD78070AY | _         |       |        |       |        |       |       |     | I <sup>2</sup> C:1ch)      | 61本 | 2.7 V |    |

|         | μPD780018AY | 48 K-60 K |       |        |       |        |       |       | _   | 3ch (I <sup>2</sup> C:1ch) | 88本 |       |    |

|         | μPD780058Y  | 24 K-60 K | 2ch   |        |       |        |       |       | 2ch | 3ch(時分割UART:               | 68本 | 1.8 V |    |

|         |             |           |       |        |       |        |       |       |     | 1ch, I <sup>2</sup> C:1ch) |     |       |    |

|         | μ PD78058FY | 48 K-60 K |       |        |       |        |       |       |     | 3ch(UART:1ch,              | 69本 | 2.7 V |    |

|         | μ PD78054Y  | 16 K-60 K |       |        |       |        |       |       |     | I <sup>2</sup> C:1ch)      |     | 2.0 V |    |

|         | μ PD780078Y | 48 K-60 K |       | 2ch    |       |        | _     | 8ch   | _   | 4ch(UART:2ch,              | 52本 | 1.8 V |    |

|         |             |           |       |        |       |        |       |       |     | I <sup>2</sup> C:1ch)      |     |       |    |

|         | μPD780034AY | 8 K-32 K  |       | 1ch    |       |        |       |       |     | 3ch(UART:1ch,              | 51本 |       |    |

|         | μPD780024AY |           |       |        |       |        | 8ch   | _     |     | I <sup>2</sup> C:1ch)      |     |       |    |

|         | μPD78018FY  | 8 K-60 K  |       |        |       |        |       |       |     | 2ch (I <sup>2</sup> C:1ch) | 53本 |       |    |

| LCD     | μPD780354Y  | 24 K-32 K | 4ch   | 1ch    | 1ch   | 1ch    | _     | 8ch   | _   | 4ch(UART:1ch,              | 66本 | 1.8 V | _  |

| 駆動用     | μPD780344Y  |           |       |        |       |        | 8ch   | _     |     | I <sup>2</sup> C:1ch)      |     |       |    |

|         | μPD780308Y  | 48 K-60 K | 2ch   |        |       |        |       |       |     | 3ch(時分割UART:               | 57本 | 2.0 V |    |

|         |             |           |       |        |       |        |       |       |     | 1ch, I <sup>2</sup> C:1ch) |     |       |    |

|         | μPD78064Y   | 16 K-32 K |       |        |       |        |       |       |     | 2ch(UART:1ch,              |     |       |    |

|         |             |           |       |        |       |        |       |       |     | I <sup>2</sup> C:1ch)      |     |       |    |

| バス・イン   | μPD780702Y  | 60 K      | 3ch   | 2ch    | 1ch   | 1ch    | 16ch  | _     | _   | 4ch(UART:1ch,              | 67本 | 3.5 V | _  |

| タフェース   | μPD780703AY | 59.5 K    |       |        |       |        |       |       |     | I <sup>2</sup> C:1ch)      |     |       |    |

| 対応      | μPD780833Y  | 60 K      |       |        |       |        |       |       |     |                            | 65本 | 4.5 V |    |

備考 YなしサブシリーズとYサブシリーズは、シリアル・インタフェース以外の機能は共通です(Yなしサブシリーズがある場合)。

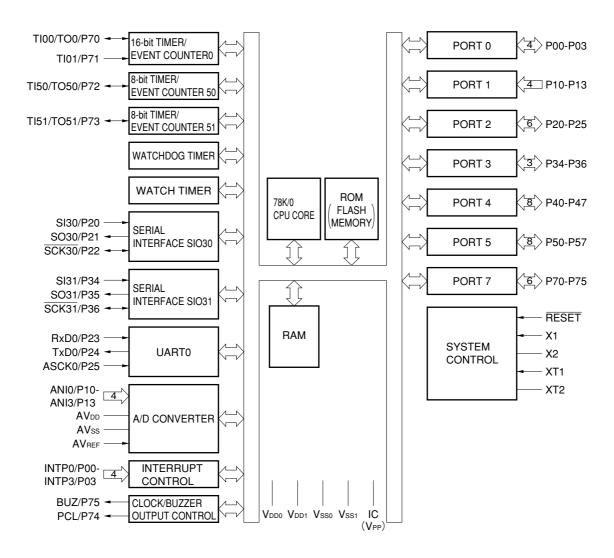

## 1.7 ブロック図

備考1. 内部ROM, RAM容量は製品によって異なります。

**2.** ( )内はμPD78F0034BSのとき。

## 1.8 機能概要

| 品名               | μPD780021AS                                                                                                                              | μPD780022AS                        | μPD780023AS | μPD780024AS | μPD78F0034BS         |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------|-------------|----------------------|--|--|--|--|

| 項目               | μPD780031AS                                                                                                                              | μPD780032AS                        | μPD780033AS | μPD780034AS |                      |  |  |  |  |

| 内部メモリ ROM        | 8 Kバイト                                                                                                                                   | 16 Kバイト                            | 24 Kバイト     | 32 Kバイト     | 32 Kバイト <sup>注</sup> |  |  |  |  |

|                  | (マスクROM)                                                                                                                                 | (マスクROM)                           | (マスクROM)    | (マスクROM)    | (フラッシュ・メモリ)          |  |  |  |  |

| 高速RAM            | 512バイト                                                                                                                                   |                                    | 1024バイト     |             | 1024バイト <sup>注</sup> |  |  |  |  |

| メモリ空間            | 64 Kバイト                                                                                                                                  | 64 Kバイト                            |             |             |                      |  |  |  |  |

| 汎用レジスタ           | 8ビット×32レジスタ(8ビット×8レジスタ×4バンク)                                                                                                             |                                    |             |             |                      |  |  |  |  |

| 最小命令実行時間         | 最小命令実行時間の可変機能内蔵                                                                                                                          |                                    |             |             |                      |  |  |  |  |

| メイン・システム・クロック選択時 | $0.166 \mu\text{s}/0.333 \mu\text{s}/0.666 \mu\text{s}/1.33 \mu\text{s}/2.66 \mu\text{s}$ (12 MHz, $V_{DD} = 4.5 \sim 5.5 \text{V}$ 動作時) |                                    |             |             |                      |  |  |  |  |

| サブシステム・クロック選択時   | 122 μs (32.768 k                                                                                                                         | Hz動作時)                             |             |             |                      |  |  |  |  |

| 命令セット            | ・16ビット演算                                                                                                                                 |                                    |             |             |                      |  |  |  |  |

|                  | ・乗除算(8ビッ                                                                                                                                 | ト×8ビット, 16년                        | ビット÷8ビット)   |             |                      |  |  |  |  |

|                  | ・ビット操作(セ                                                                                                                                 | ・ビット操作(セット,リセット,テスト,ブール演算)・BCD補正など |             |             |                      |  |  |  |  |

| I/Oポート           | 合計                                                                                                                                       | 合計 : 39本                           |             |             |                      |  |  |  |  |

|                  | ・CMOS入力                                                                                                                                  |                                    | : 4本        |             |                      |  |  |  |  |

|                  | ・CMOS入出力                                                                                                                                 |                                    | : 35本       |             |                      |  |  |  |  |

| A/Dコンバータ         | ・ 8 ビット分解能× 4 チャネル( µ PD780021AS, 780022AS, 780023AS, 780024ASのみ)                                                                        |                                    |             |             |                      |  |  |  |  |

|                  | ・10ビット分解能×4チャネル(μPD780031AS, 780032AS, 780033AS, 780034AS, 78F0034BSのみ)                                                                  |                                    |             |             |                      |  |  |  |  |

|                  | ・低電圧動作可能:AV <sub>DD</sub> = 1.8~5.5 V                                                                                                    |                                    |             |             |                      |  |  |  |  |

| シリアル・インタフェース     | ・3線式シリアルI/Oモード:2チャネル                                                                                                                     |                                    |             |             |                      |  |  |  |  |

|                  | ・UARTモード : 1チャネル                                                                                                                         |                                    |             |             |                      |  |  |  |  |

| タイマ              | ・16ビット・タイマ/イベント・カウンタ:1 チャネル                                                                                                              |                                    |             |             |                      |  |  |  |  |

|                  | ・8ビット・タイマ/イベント・カウンタ:2チャネル                                                                                                                |                                    |             |             |                      |  |  |  |  |

|                  | ・時計用タイマ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                              |                                    |             |             |                      |  |  |  |  |

|                  | ・ウォッチドッグ・タイマ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                          |                                    |             |             |                      |  |  |  |  |

| タイマ出力            | 3本 (8ビットPWM出力可能: 2本)                                                                                                                     |                                    |             |             |                      |  |  |  |  |

| クロック出力           | • 93.7 kHz, 187 kHz, 375 kHz, 750 kHz, 1.5 MHz, 3 MHz, 6 MHz, 12 MHz                                                                     |                                    |             |             |                      |  |  |  |  |

|                  | (メイン・システム・クロック:12 MHz, V <sub>DD</sub> = 4.5~5.5 V動作時)                                                                                   |                                    |             |             |                      |  |  |  |  |

|                  | ・32.768 kHz(サブシステム・クロック:32.768 kHz動作時)                                                                                                   |                                    |             |             |                      |  |  |  |  |

| ブザー出力            | 1.46 kHz, 2.92 kHz, 5.85 kHz, 11.7 kHz(メイン・システム・クロック:12 MHz, Vdd = 4.5~5.5 V動作時)                                                         |                                    |             |             |                      |  |  |  |  |

| ベクタ マスカブル        | 内部:13, 外部:5                                                                                                                              |                                    |             |             |                      |  |  |  |  |

| 割り込み ノンマスカブル     | 内部: 1                                                                                                                                    |                                    |             |             |                      |  |  |  |  |

| 要因 ソフトウエア        | 1                                                                                                                                        |                                    |             |             |                      |  |  |  |  |

| 電源電圧             | V <sub>DD</sub> = 1.8∼5.5 V                                                                                                              |                                    |             |             |                      |  |  |  |  |

| 動作周囲温度           | T <sub>A</sub> = −40~+85 °C                                                                                                              |                                    |             |             |                      |  |  |  |  |

|                  |                                                                                                                                          |                                    |             |             |                      |  |  |  |  |

注 メモリ・サイズ切り替えレジスタ (IMS) により、内部フラッシュ・メモリ、内部高速RAM容量の変更可能。

タイマ/イベント・カウンタの概要(詳細は第6章 16ビット・タイマ/イベント・カウンタ 0, 第7章 8ビット・タイマ/イベント・カウンタ50,51, 第8章 時計用タイマ, 第9章 ウォッチドッグ・タイマを参照)を次に示します。

|     |             | 16ビット・タイマ/イベント・カウンタ | 8ビット・タイマ/イベント・カウンタ | 時計用タイマ                | ウォッチドッグ・タイマ           |

|-----|-------------|---------------------|--------------------|-----------------------|-----------------------|

| 動作  | インターバル・タイマ  | 1 チャネル              | 2 チャネル             | 1 チャネル <sup>注 1</sup> | 1 チャネル <sup>注 2</sup> |

| モード | 外部イベント・カウンタ | 0                   | 0                  | _                     | _                     |

| 機能  | タイマ出力       | 0                   | 0                  | _                     | _                     |

|     | PPG出力       | 0                   | _                  | _                     | _                     |

|     | PWM出力       | _                   | 0                  | _                     | _                     |

|     | パルス幅測定      | 0                   | _                  | _                     | _                     |

|     | 方形波出力       | 0                   | 0                  | _                     | _                     |

|     | 割り込み要求      | 0                   | 0                  | 0                     | 0                     |

- 注1. 時計用タイマは時計用タイマとインターバル・タイマの機能を同時に使用可能です。

- 2. ウォッチドッグ・タイマはウォッチドッグ・タイマとインターバル・タイマの機能がありますが、いずれか一方を選択して使用してください。

## 1.9 標準水準品と特別水準品との違いについて

標準水準品: μPD780021AS, 780022AS, 780023AS, 780024AS μPD780031AS, 780032AS, 780033AS, 780034AS, 78F0034BS

特別水準品: μPD780021AS(A), 780022AS(A), 780023AS(A), 780024AS(A)

μPD780031AS(A), 780032AS(A), 780033AS(A), 780034AS(A), 780034BS(A)

標準製品と特別製品は、品質水準のみが異なります。

## 第2章 端子機能

## 2.1 端子機能一覧

## (1)ポート端子

| 端子名称    | 入出力 | 機能                                  | リセット時 | 兼用端子        |

|---------|-----|-------------------------------------|-------|-------------|

| P00     | 入出力 | ポート0。                               | 入力    | INTP0       |

| P01     | 1   | 4ビット入出力ポート。                         |       | INTP1       |

| P02     | 1   | 1ビット単位で入力/出力の指定可能。                  |       | INTP2       |

| P03     | 1   | ソフトウエアの設定により、内蔵プルアップ抵抗を使用可能。        |       | INTP3/ADTRG |

| P10-P13 | 入力  | ポート1。                               | 入力    | ANI0-ANI3   |

|         |     | 4ビット入力専用ポート。                        |       |             |

| P20     | 入出力 | ポート2。                               | 入力    | SI30        |

| P21     | 1   | 6ビット入出力ポート。                         |       | SO30        |

| P22     | 1   | 1ビット単位で入力/出力の指定可能。                  |       | SCK30       |

| P23     | 1   | ソフトウエアの設定により、内蔵プルアップ抵抗を使用可能。        |       | RxD0        |

| P24     | 1   |                                     |       | TxD0        |

| P25     | 1   |                                     |       | ASCK0       |

| P34     | 入出力 | ポート3。                               | 入力    | SI31        |

| P35     | 1   | 3ビット入出力ポート。                         |       | SO31        |

| P36     | 1   | 1ビット単位で入力/出力の指定可能。                  |       | SCK31       |

|         |     | ソフトウエアの設定により、内蔵プルアップ抵抗を使用可能。        |       |             |

| P40-P47 | 入出力 | ポート4。                               | 入力    | _           |

|         |     | 8ビット入出力ポート。                         |       |             |

|         |     | 1ビット単位で入力/出力の指定可能。                  |       |             |

|         |     | ソフトウエアの設定により、内蔵プルアップ抵抗を使用可能。        |       |             |

|         |     | 立ち下がりエッジの検出により、割り込み要求フラグ(KRIF)を1にセッ |       |             |

|         |     | ١,٠                                 |       |             |

| P50-P57 | 入出力 | ポート5。                               | 入力    | _           |

|         |     | 8ビット入出力ポート。                         |       |             |

|         |     | LEDを直接駆動可能。                         |       |             |

|         |     | 1ビット単位で入力/出力の指定可能。                  |       |             |

|         |     | ソフトウエアの設定により,内蔵プルアップ抵抗を使用可能。        |       |             |

| P70     | 入出力 | ポート7。                               | 入力    | TI00/TO0    |

| P71     | 1   | 6ビット入出力ポート。                         |       | TI01        |

| P72     | 1   | 1ビット単位で入力/出力の指定可能。                  |       | TI50/TO50   |

| P73     | 1   | ソフトウエアの設定により、内蔵プルアップ抵抗を使用可能。        |       | TI51/TO51   |

| P74     | 1   |                                     |       | PCL         |

| P75     | 1   |                                     |       | BUZ         |

## (2) ポート以外の端子

| 端子名称             | 入出力 | 機能                                      | リセット時 | 兼用端子      |

|------------------|-----|-----------------------------------------|-------|-----------|

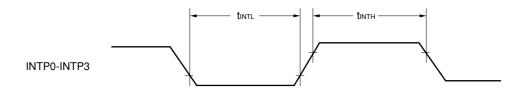

| INTP0            | 入力  | 有効エッジ(立ち上がりエッジ、立ち下がりエッジ、立ち上がりエッジおよ      | 入力    | P00       |

| INTP1            |     | び立ち下がりエッジの両エッジ)指定可能な外部割り込み要求入力。         |       | P01       |

| INTP2            |     |                                         |       | P02       |

| INTP3            |     |                                         |       | P03/ADTRG |

| SI30             | 入力  | シリアル・インタフェースのシリアル・データ入力。                | 入力    | P20       |

| SI31             |     |                                         |       | P34       |

| SO30             | 出力  | シリアル・インタフェースのシリアル・データ出力。                | 入力    | P21       |

| SO31             |     |                                         |       | P35       |

| SCK30            | 入出力 | シリアル・インタフェースのシリアル・クロック入力/出力。            | 入力    | P22       |

| SCK31            |     |                                         |       | P36       |

| RxD0             | 入力  | アシンクロナス・シリアル・インタフェース用シリアル・データ入力。        | 入力    | P23       |

| TxD0             | 出力  | アシンクロナス・シリアル・インタフェース用シリアル・データ出力。        | 入力    | P24       |

| ASCK0            | 入力  | アシンクロナス・シリアル・インタフェース用シリアル・クロック入力。       | 入力    | P25       |

| TI00             | 入力  | 16ビット・タイマ/イベント・カウンタ 0 への外部カウント・クロック入力。  | 入力    | P70/TO0   |

|                  |     | 16ビット・タイマ/イベント・カウンタ 0 のキャプチャ・レジスタ(CR00, |       |           |

|                  |     | CR01) へのキャプチャ・トリガ入力。                    |       |           |

| TI01             |     | 16ビット・タイマ/イベント・カウンタ 0 のキャプチャ・レジスタ(CR00) |       | P71       |

|                  |     | へのキャプチャ・トリガ入力。                          |       |           |

| TI50             |     | 8ビット・タイマ/イベント・カウンタ50への外部カウント・クロック入力。    |       | P72/TO50  |

| TI51             |     | 8ビット・タイマ/イベント・カウンタ51への外部カウント・クロック入力。    |       | P73/TO51  |

| TO0              | 出力  | 16ビット・タイマ/イベント・カウンタ 0 出力。               | 入力    | P70/TI00  |

| TO50             |     | 8ビット・タイマ/イベント・カウンタ50出力(8ビットPWM出力と兼      | 入力    | P72/TI50  |

|                  |     | 用)。                                     |       |           |

| TO51             |     | 8ビット・タイマ/イベント・カウンタ51出力(8ビットPWM出力と兼      |       | P73/TI51  |

|                  |     | 用)。                                     |       |           |

| PCL              | 出力  | クロック出力(メイン・システム・クロック、サブシステム・クロックのト      | 入力    | P74       |

|                  |     | リミング用)。                                 |       |           |

| BUZ              | 出力  | ブザー出力。                                  | 入力    | P75       |

| ANI0-ANI3        | 入力  | A/Dコンバータのアナログ入力。                        | 入力    | P10-P13   |

| ADTRG            | 入力  | A/Dコンバータのトリガ信号入力。                       | 入力    | P03/INTP3 |

| AVREF            | 入力  | A/Dコンバータの基準電圧入力。                        | 入力    | _         |

| AVDD             | _   | A/Dコンバータのアナログ電源。VppgまたはVppgと同電位にしてください。 | _     | _         |

| AVss             | _   | A/Dコンバータのグランド電位。VssoまたはVss1と同電位にしてください。 | _     | _         |

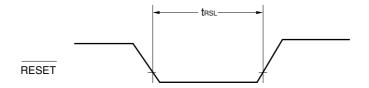

| RESET            | 入力  | システム・リセット入力。                            | 入力    | _         |

| X1               | 入力  | メイン・システム・クロック発振用水晶/セラミック接続。             |       | _         |

| X2               | _   |                                         | _     | _         |

| XT1              | 入力  | サブシステム・クロック発振用水晶接続。                     | _     | _         |

| XT2              | _   |                                         | _     | _         |

| V <sub>DD0</sub> | _   | ポート部の正電源。                               | _     | _         |

| V <sub>DD1</sub> |     | 正電源(ポート部を除く)。                           |       | _         |

| V <sub>SS0</sub> | _   | ポート部のグランド電位。                            | _     | _         |

| V <sub>SS1</sub> |     | グランド電位(ポート部を除く)。                        |       | _         |

| IC               | _   | 内部接続されています。VssoまたはVss1に直接接続してください。      | _     | _         |

| V <sub>PP</sub>  |     | プログラム書き込み/ベリファイ時の高電圧印加。                 |       |           |

\*

## 2.2 端子機能の説明

## 2.2.1 P00-P03(Port0)

4 ビットの入出力ポートです。入出力ポートのほかに、外部割り込み入力、A/Dコンバータの外部トリガ入力があります。

1ビット単位で次のような動作モードを指定できます。

#### (1) ポート・モード

4ビットの入出力ポートとして機能します。

P00-P03はポート・モード・レジスタ 0 (PM0) により、1 ビット単位で入力ポートまたは出力ポートに指定できます。プルアップ抵抗オプション・レジスタ0 (PU0) により、内蔵プルアップ抵抗を使用できます。

#### (2) コントロール・モード

外部割り込み要求入力、A/Dコンバータの外部トリガ入力として機能します。

#### (a) INTP0-INTP3

INTPO-INTP3は、有効エッジ(立ち上がりエッジ、立ち下がりエッジ、立ち上がりおよび立ち下がりの両エッジ)指定可能な外部割り込み要求入力端子です。

#### (b) ADTRG

A/Dコンバータの外部トリガ入力端子です。

注意 P03をA/Dコンバータの外部トリガ入力として使用する場合は、A/Dコンバータ・モード・レジスタ(ADM0)のビット1、2(EGA00, EGA01)で有効エッジを指定し、割り込みマスク・フラグ(PMK3)を1に設定してください。

## 2.2.2 P10-P13(Port1)

4 ビットの入力専用ポートです。入力ポートのほかにA/Dコンバータのアナログ入力機能があります。 1 ビット単位で次のような動作モードを指定できます。

## (1) ポート・モード

4ビットの入力専用ポートとして機能します。

#### (2) コントロール・モード

A/Dコンバータのアナログ入力端子(ANIO-ANI3)として機能します。

## 2.2.3 P20-P25(Port2)

6 ビットの入出力ポートです。入出力ポートのほかにシリアル・インタフェースのデータ入出力、クロック入出力機能があります。

1ビット単位で次のような動作モードを指定できます。

## (1) ポート・モード

6 ビットの入出力ポートとして機能します。ポート・モード・レジスタ 2 (PM2) により、1 ビット単位で入力ポートまたは出力ポートに指定できます。プルアップ抵抗オプション・レジスタ 2 (PU2) により、内蔵プルアップ抵抗を使用できます。

#### (2) コントロール・モード

シリアル・インタフェースのデータ入出力、クロック入出力として機能します。

#### (a) SI30, SO30

シリアル・インタフェースのシリアル・データの入出力端子です。

#### (b) SCK30

シリアル・インタフェースのシリアル・クロックの入出力端子です。

#### (c) RxD0, TxD0

アシンクロナス・シリアル・インタフェースのシリアル・データの入出力端子です。

#### (d) ASCK0

アシンクロナス・シリアル・インタフェースのシリアル・クロックの入力端子です。

#### 2.2.4 P34-P36(Port3)

3 ビットの入出力ポートです。入出力ポートのほかにシリアル・インタフェースのデータ入出力、クロック入出力機能があります。

1ビット単位で次のような動作モードを指定できます。

#### (1) ポート・モード

3ビットの入出力ポートとして機能します。ポート・モード・レジスタ 3 (PM3) により、1ビット単位で入力ポートまたは出力ポートに指定できます。

プルアップ抵抗オプション・レジスタ 3 (PU3) により、内蔵プルアップ抵抗を使用できます。

#### (2) コントロール・モード

シリアル・インタフェースのデータ入出力、クロック入出力として機能します。

(a) SI31, SO31

シリアル・インタフェースのシリアル・データの入出力端子です。

## (b) SCK31

シリアル・インタフェースのシリアル・クロックの入出力端子です。

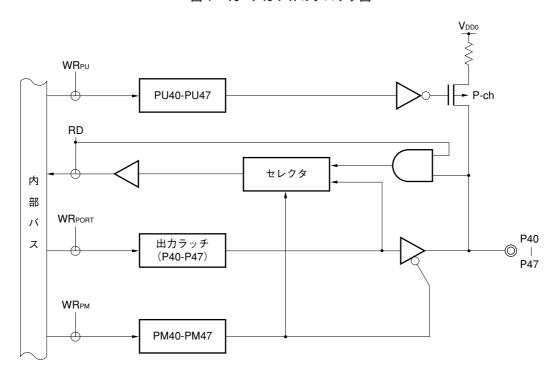

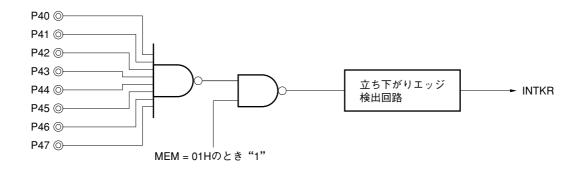

## 2.2.5 P40-P47(Port4)

8ビットの入出力ポートです。

立ち下がりエッジの検出により、割り込み要求フラグ(KRIF)を1にセットできます。

1ビット単位で次のような動作モードを指定できます。

注意 立ち下がりエッジ検出割り込み (INTKR) を使用する場合,メモリ拡張モード・レジスタ (MEM) を 必ず01Hに設定してください。

## (1) ポート・モード

8 ビットの入出力ポートとして機能します。ポート・モード・レジスタ 4 (PM4) により、1 ビット単位で入力ポートまたは出力ポートに指定できます。プルアップ抵抗オプション・レジスタ 4 (PU4) により、内蔵プルアップ抵抗を使用できます。

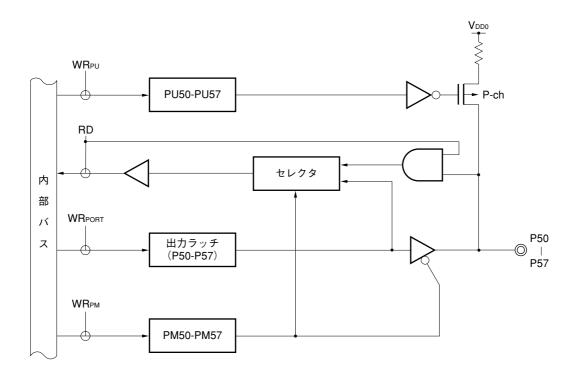

#### 2.2.6 P50-P57(Port5)

8ビットの入出力ポートです。

LEDを直接駆動可能です。

1ビット単位で次のような動作モードを指定できます。

## (1) ポート・モード

8 ビットの入出力ポートとして機能します。ポート・モード・レジスタ 5 (PM5) により、1 ビット単位で入力ポートまたは出力ポートに指定できます。プルアップ抵抗オプション・レジスタ 5 (PU5) により、内蔵プルアップ抵抗を使用できます。

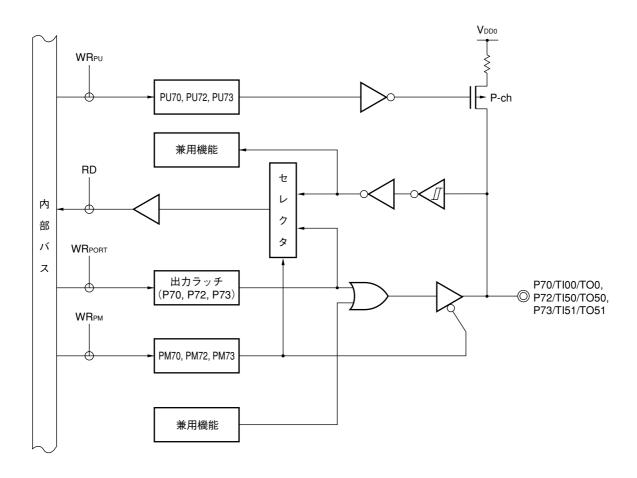

## 2.2.7 P70-P75(Port7)

6 ビットの入出力ポートです。入出力ポートのほかにタイマの入出力、クロック出力、ブザー出力機能があります。

1ビット単位で次のような動作モードを指定できます。

#### (1) ポート・モード

6 ビットの入出力ポートとして機能します。ポート・モード・レジスタ 7 (PM7) により、1 ビット単位で入力ポートまたは出力ポートに指定できます。プルアップ抵抗オプション・レジスタ 7 (PU7) により、内蔵プルアップ抵抗を使用できます。また、P70、P71は、有効エッジの入力により、16ビット・タイマ/イベント・カウンタのキャプチャ・トリガ信号入力端子にもなります。

#### (2) コントロール・モード

タイマの入出力、クロック出力、ブザー出力として機能します。

#### (a) TI00

16ビット・タイマ/イベント・カウンタへの外部カウント・クロック入力端子および16ビット・タイマ/イベント・カウンタのキャプチャ・レジスタ(CR00, CR01)へのキャプチャ・トリガ信号入力端子です。

#### (b) TI01

16ビット・タイマ/イベント・カウンタのキャプチャ・レジスタ(CR00)へのキャプチャ・トリガ信 号入力端子です。

#### (c) TI50, TI51

8ビット・タイマ/イベント・カウンタへの外部カウント・クロック入力端子です。

## (d) TO0, TO50, TO51

タイマ出力端子です。

#### (e) PCL

クロック出力端子です。

## (f) BUZ

ブザー出力端子です。

## 2.2.8 AVREF

A/Dコンバータの基準電圧入力端子です。

A/Dコンバータを使用しない場合は、VssoまたはVss1に直接接続してください。

## 2.2.9 AVDD

A/Dコンバータのアナログ電源端子です。A/Dコンバータを使用しないときでも、常にVDDO端子またはVDD1端子と同電位で使用してください。

## 2.2.10 AVss

A/Dコンバータのグランド電位端子です。A/Dコンバータを使用しないときでも、常にVsso端子またはVssi端子と同電位で使用してください。

## 2.2.11 RESET

ロウ・レベル・アクティブのシステム・リセット入力端子です。

## 2.2.12 X1, X2

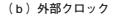

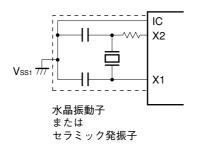

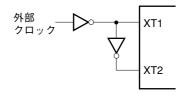

メイン・システム・クロック発振用水晶/セラミック振動子接続端子です。 外部クロックを供給するときは、X1に入力し、X2にその反転信号を入力してください。

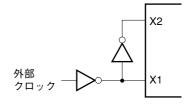

## 2.2.13 XT1, XT2

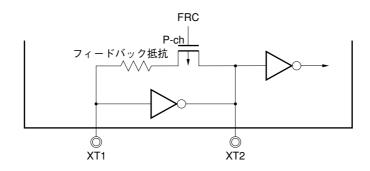

サブシステム・クロック発振用水晶振動子接続端子です。

外部クロックを供給するときは、XT1に入力し、XT2にその反転信号を入力してください。

## 2.2.14 VDD0, VDD1

VDD0は、ポート部の正電源供給端子です。

VDD1は、ポート部以外の正電源供給端子です。

## 2.2.15 Vsso, Vss1

Vssoは、ポート部のグランド電位端子です。

Vss1は、ポート部以外のグランド電位端子です。

## 2.2.16 Vpp(フラッシュ・メモリ製品のみ)

フラッシュ・メモリ・プログラミング・モード設定およびプログラム書き込み/ベリファイ時の高電圧印加端 子です。

次のどちらかの端子処理をしてください。

- ・個別に10 kΩのプルダウン抵抗を接続する。

- ・ボード上のジャンパで、プログラミング・モード時は専用フラッシュ・ライタに、通常動作モード時はVsso またはVss1に直接接続するように切り替える。

VPP端子とVsso端子またはVss1端子間の配線の引き回しが長い場合や、VPP端子に外来ノイズが加わった場合などで、VPP端子とVsso端子またはVss1端子間に電位差が生じたときには、お客様のプログラムが正常に動作しないことがあります。

## 2.2.17 IC(マスクROM製品のみ)

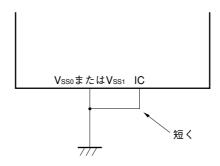

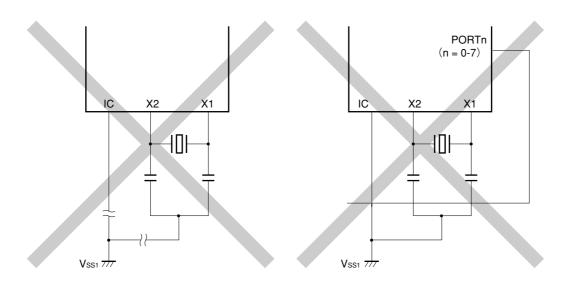

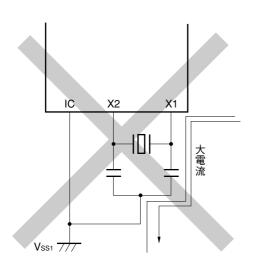

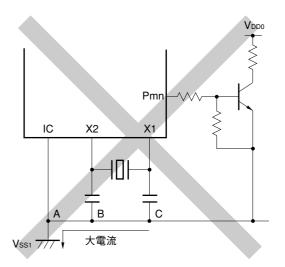

IC(Internally Connected)端子は、当社出荷時に  $\mu$  PD780024AS, 780034ASサブシリーズを検査するためのテスト・モードに設定するための端子です。通常動作モード時には、IC端子をVsso端子またはVsst端子に直接接続し、その配線長を極力短くしてください。

IC端子とVsso端子またはVss1端子間の配線の引き回しが長い場合や、IC端子に外来ノイズが加わった場合などで、IC端子とVsso端子またはVss1端子間に電位差が生じたときには、お客様のプログラムが正常に動作しないことがあります。

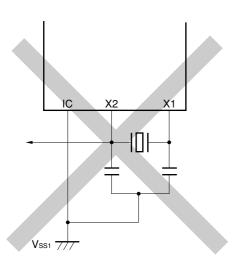

## ○IC端子をVsso端子またはVss1端子に直接接続してください。

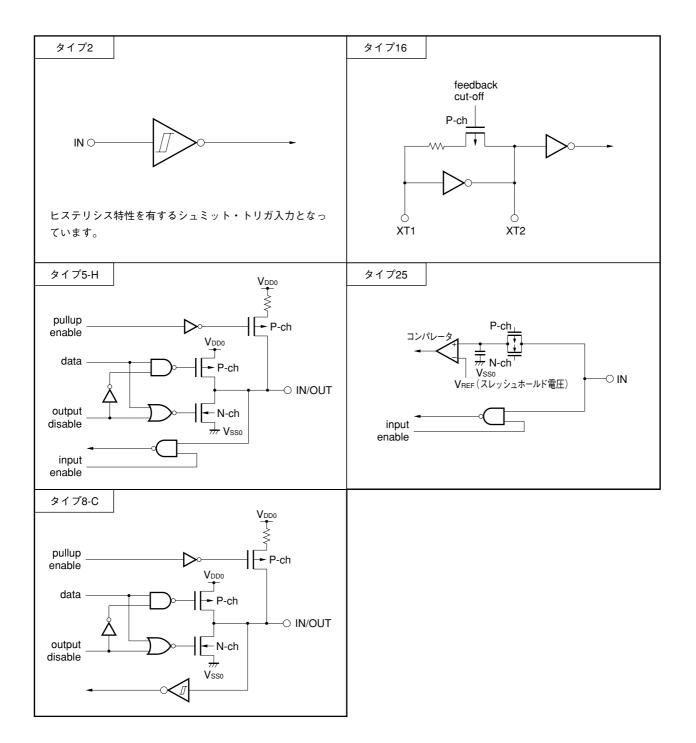

## 2.3 端子の入出力回路と未使用端子の処理

各端子の入出力回路タイプと、未使用端子の処理を表 2-1 に示します。 また、各タイプの入出力回路の構成は、図 2-1 を参照してください。

表 2 - 1 各端子の入出力回路タイプ

| 端子名                 | 入出力回路タイプ | 入出力 | 未使用時の推奨接続方法                                                                                 |

|---------------------|----------|-----|---------------------------------------------------------------------------------------------|

| P00/INTP0-P02/INTP2 | 8-C      | 入出力 | 入力時:個別に抵抗を介して、VssoまたはVss1に接続してく                                                             |

| P03/INTP3/ADTRG     |          |     | ださい。                                                                                        |

|                     |          |     | 出力時:オープンにしてください。                                                                            |

| P10/ANI0-P13/ANI3   | 25       | 入力  | V <sub>DD0</sub> , V <sub>DD1</sub> , V <sub>SS0</sub> , V <sub>SS1</sub> のいずれかに直接接続してください。 |

| P20/SI30            | 8-C      | 入出力 | 入力時:個別に抵抗を介して、VDDO, VDD1, VSSO, VSS1のいず                                                     |

| P21/SO30            | 5-H      |     | れかに接続してください                                                                                 |

| P22/SCK30           | 8-C      |     | 出力時:オープンにしてください。                                                                            |

| P23/RxD0            |          |     |                                                                                             |

| P24/TxD0            | 5-H      |     |                                                                                             |

| P25/ASCK0           | 8-C      |     |                                                                                             |

| P34/SI31            | 8-C      |     | 入力時:個別に抵抗を介して, VDD0, VDD1, VSS0, VSS1のいず                                                    |

| P35/SO31            | 5-H      |     | れかに接続してください。                                                                                |

| P36/SCK31           | 8-C      |     | 出力時:オープンにしてください。                                                                            |

| P40-P47             | 5-H      |     | 入力時:個別に抵抗を介して、VDDOまたはVDD1に接続してく                                                             |

|                     |          |     | ださい。                                                                                        |

|                     |          |     | 出力時:オープンにしてください。                                                                            |

| P50-P57             | 5-H      |     | 入力時:個別に抵抗を介して, VDDO, VDD1, VSSO, VSS1のいず                                                    |

| P70/TI00/TO0        | 8-C      |     | れかに接続してください。                                                                                |

| P71/TI01            |          |     | 出力時:オープンにしてください。                                                                            |

| P72/TI50/TO50       |          |     |                                                                                             |

| P73/TI51/TO51       |          |     |                                                                                             |

| P74/PCL             | 5-H      |     |                                                                                             |

| P75/BUZ             |          |     |                                                                                             |

| RESET               | 2        | 入力  | -                                                                                           |

| XT1                 | 16       |     | VDD0またはVDD1に直接接続してください。                                                                     |

| XT2                 |          | _   | オープンにしてください。                                                                                |

| AVDD                | _        |     | VDDOまたはVDD1に直接接続してください。                                                                     |

| AVREF               | ]        |     | VssoまたはVss1に直接接続してください。                                                                     |

| AVss                |          |     |                                                                                             |

| IC(マスクROM製品)        | ]        |     |                                                                                             |

| Vpp(フラッシュ・メモリ製品)    |          |     | 個別に10 kΩのプルダウン抵抗を接続するか,Vssoまたは                                                              |

|                     |          |     | Vss1に直接接続してください。                                                                            |

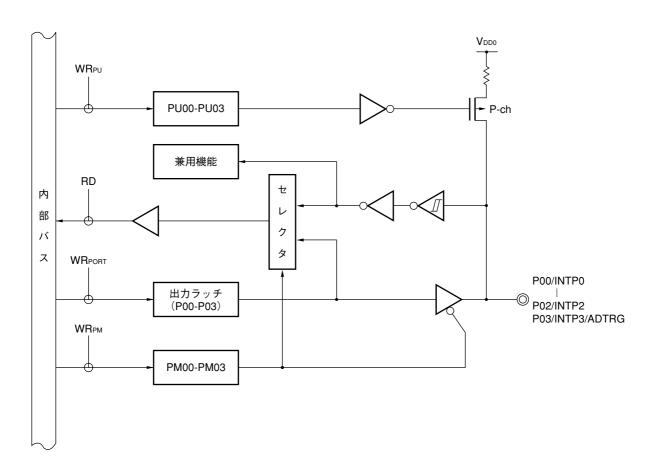

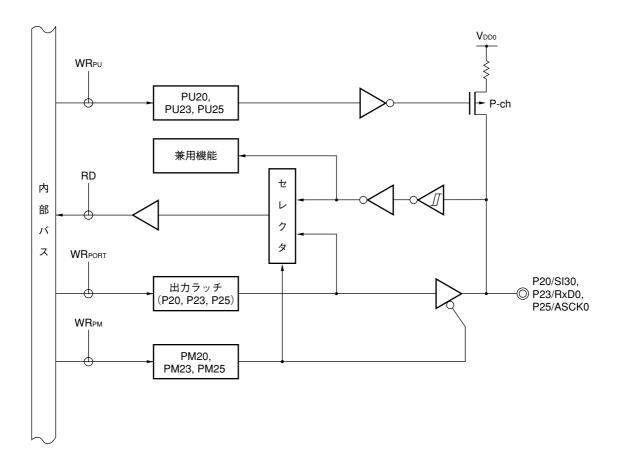

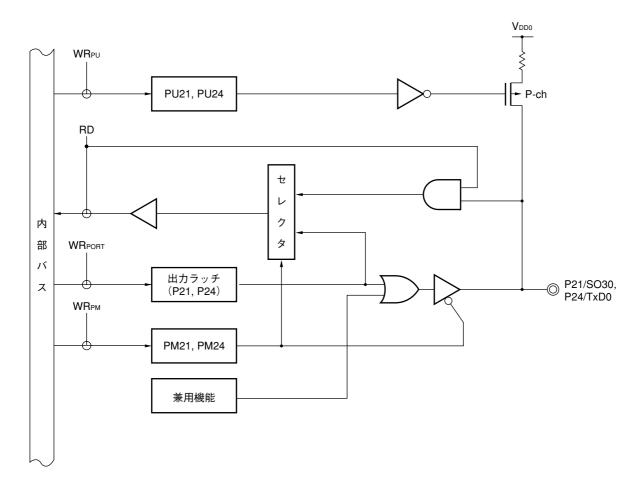

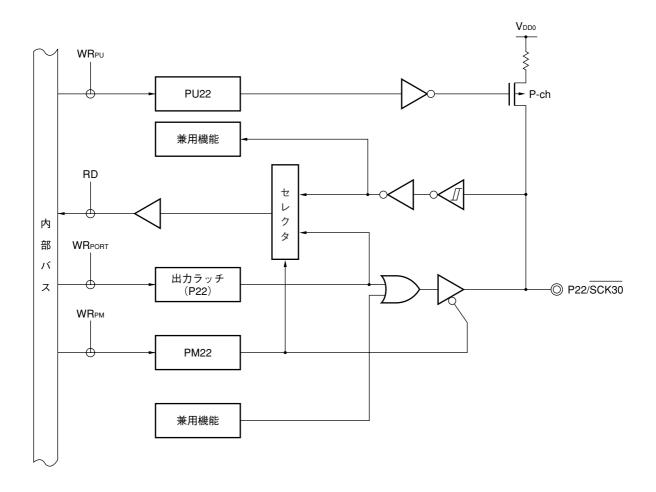

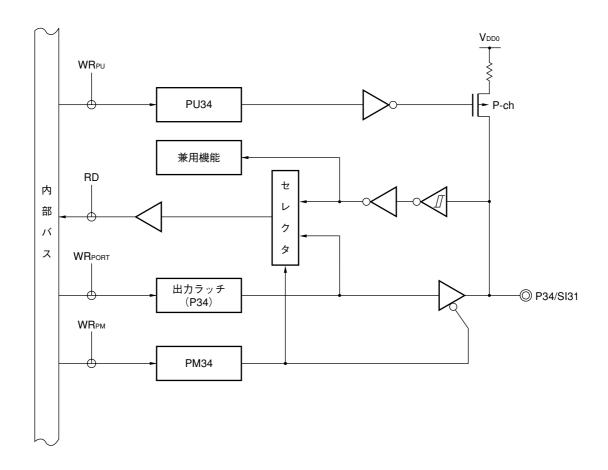

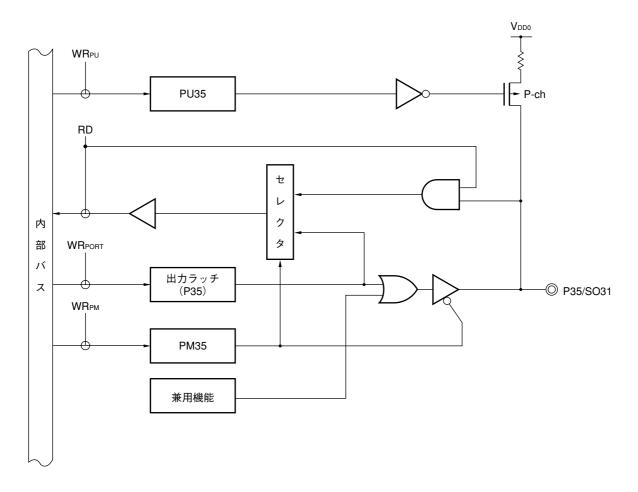

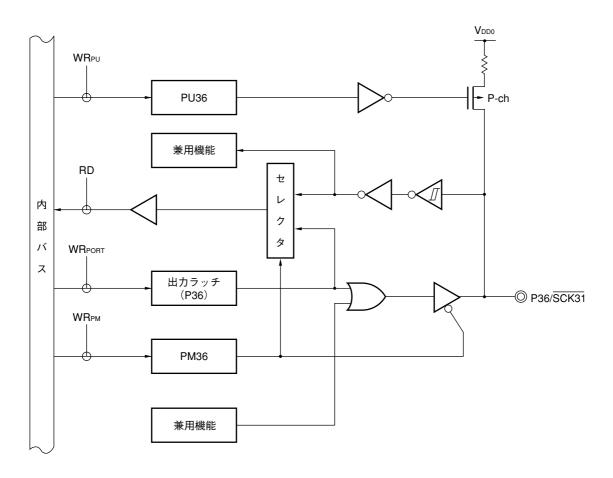

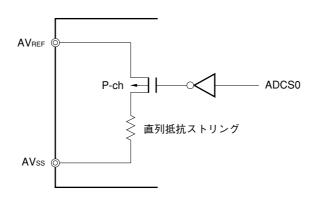

図2-1 端子の入出力回路一覧

## 第3章 CPUアーキテクチャ

## 3.1 メモリ空間

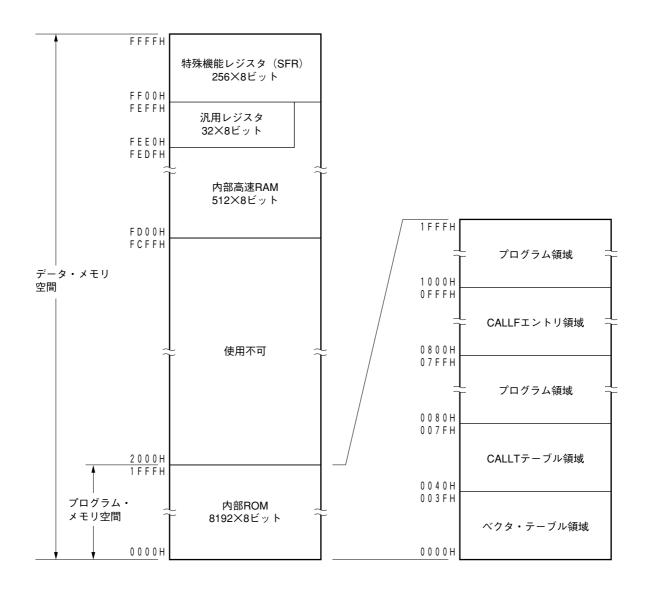

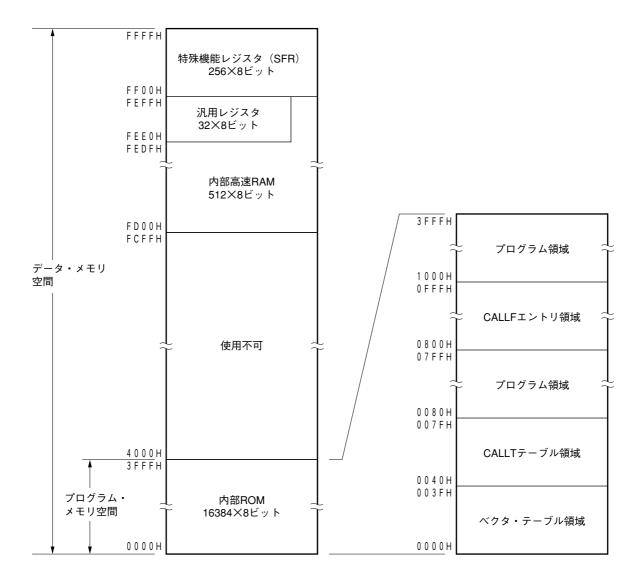

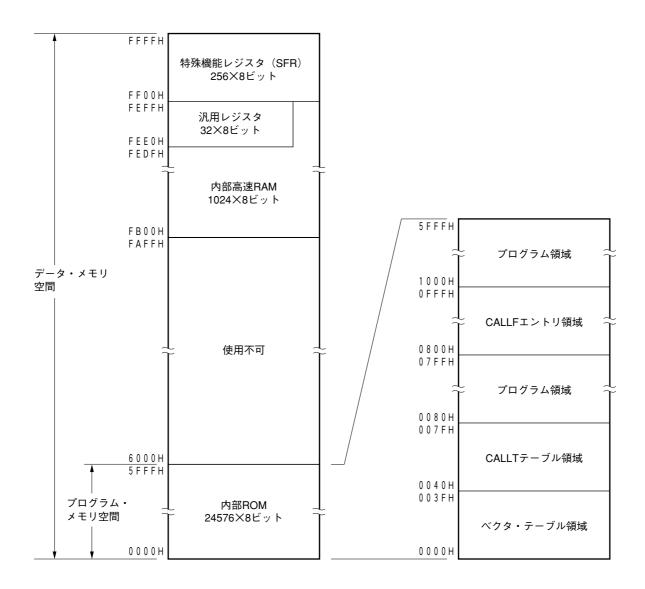

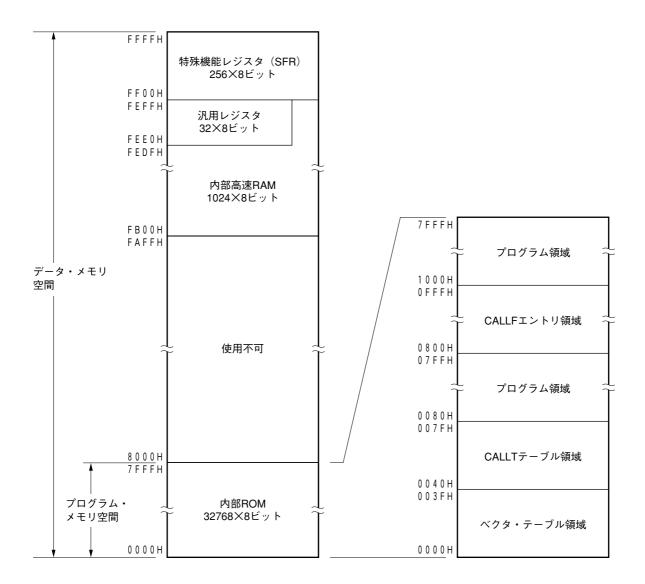

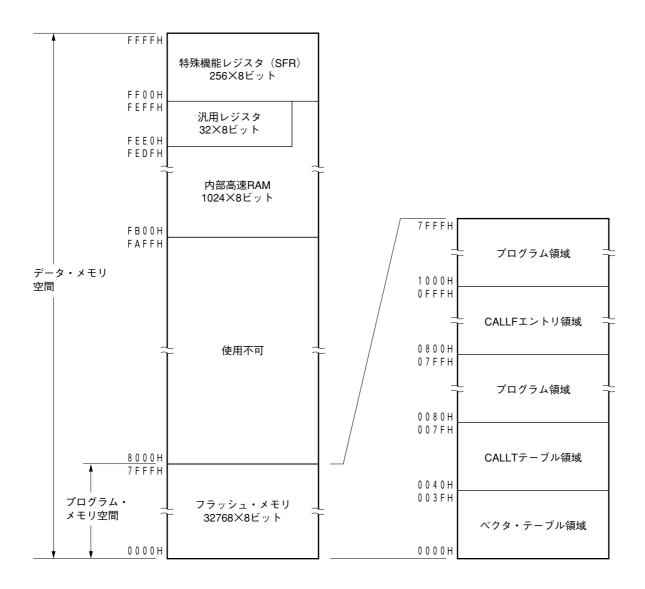

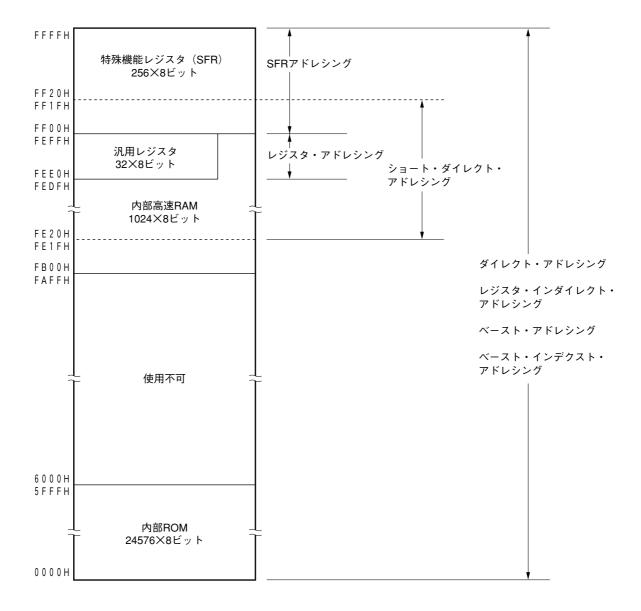

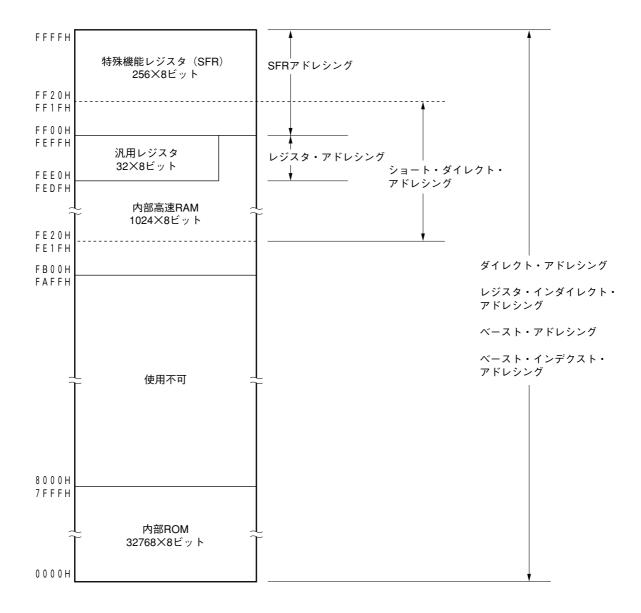

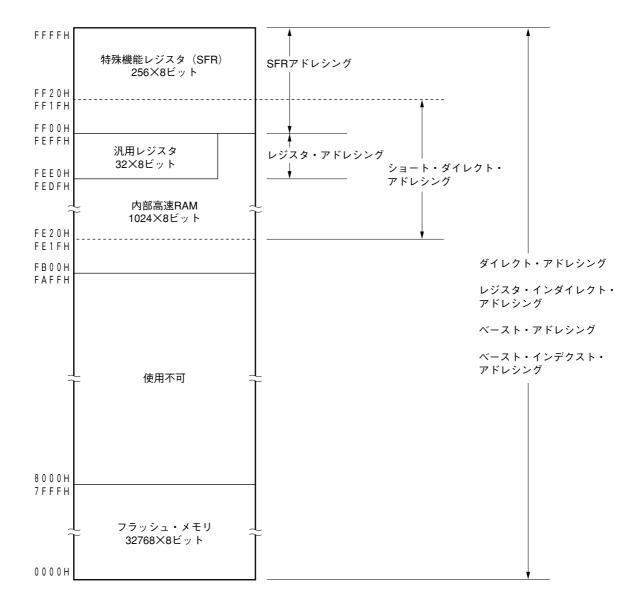

$\mu$ PD780024AS, 780034ASサブシリーズは、それぞれ64 Kバイトのメモリ空間をアクセスできます。図 3-1 から図 3-5 に、メモリ・マップを示します。

注意 メモリ・サイズ切り替えレジスタ (IMS) の初期値は、内部メモリ容量にかかわらず、 $\mu$ PD780024AS、780034ASサブシリーズすべての製品において一定 (IMS = CFH) となっています。したがって、初期設定で各製品ごとに次に示す値を設定して使用してください。

$\mu$  PD780021AS, 780031AS : 42H  $\mu$  PD780022AS, 780032AS : 44H  $\mu$  PD780023AS, 780033AS : C6H  $\mu$  PD780024AS, 780034AS : C8H

μ PD78F0034BS :マスクROM製品に対応した値

#### 図 3 -1 メモリ・マップ ( $\mu$ PD780021AS, 780031AS)

## 図 3 -2 メモリ・マップ ( $\mu$ PD780022AS, 780032AS)

## 図 3 - 3 メモリ・マップ ( $\mu$ PD780023AS, 780033AS)

#### 図 3 -4 メモリ・マップ ( $\mu$ PD780024AS, 780034AS)

## 図 3 -5 メモリ・マップ ( $\mu$ PD78F0034BS)

## 3.1.1 内部プログラム・メモリ空間

内部プログラム・メモリ空間にはプログラムおよびテーブル・データなど格納します。通常、プログラム・カウンタ(PC)でアドレスします。

$\mu$ PD780024AS, 780034ASサブシリーズは、各製品ごとに次に示す内部ROM(マスクROMまたはフラッシュ・メモリ)を内蔵しています。

| 製 品                   | 構造        | 容量                       |

|-----------------------|-----------|--------------------------|

| μPD780021AS, 780031AS | マスクROM    | 8192×8ビット(0000H-1FFFH)   |

| μPD780022AS, 780032AS |           | 16384×8ビット (0000H-3FFFH) |

| μPD780023AS, 780033AS |           | 24576×8ビット (0000H-5FFFH) |

| μPD780024AS, 780034AS |           | 32768×8ビット (0000H-7FFFH) |

| μPD78F0034BS          | フラッシュ・メモリ | 32768×8ビット (0000H-7FFFH) |

表 3 - 1 内部ROM容量

内部プログラム・メモリ空間には、次に示す領域を割り付けています。

#### (1) ベクタ・テーブル領域

0000H-003FHの64バイト領域はベクタ・テーブル領域として予約されています。ベクタ・テーブル領域には、RESET入力、各割り込み要求発生により分岐するときのプログラム・スタート・アドレスを格納しておきます。

16ビット・アドレスのうち下位8ビットが偶数アドレスに、上位8ビットが奇数アドレスに格納されます。

| ベクタ・テーブル・アドレス | 割り込み要因   | ベクタ・テーブル・アドレス | 割り込み要因   |

|---------------|----------|---------------|----------|

| 0000H         | RESET入力  | 0016H         | INTCSI31 |

| 0004H         | INTWDT   | 001AH         | INTWTI   |

| 0006H         | INTP0    | 001CH         | INTTM00  |

| 0008H         | INTP1    | 001EH         | INTTM01  |

| 000AH         | INTP2    | 0020H         | INTTM50  |

| 000CH         | INTP3    | 0022H         | INTTM51  |

| 000EH         | INTSER0  | 0024H         | INTAD0   |

| 0010H         | INTSR0   | 0026H         | INTWT    |

| 0012H         | INTST0   | 0028H         | INTKR    |

| 0014H         | INTCSI30 | 003EH         | BRK      |

表 3 - 2 ベクタ・テーブル

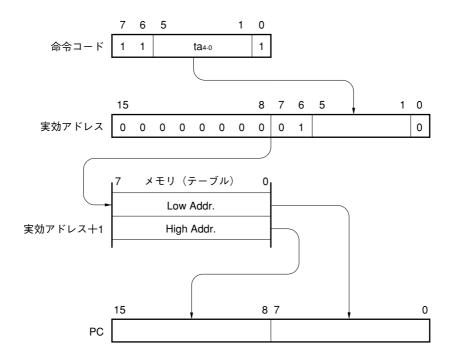

#### (2) CALLT命令テーブル領域

0040H-007FHの64バイト領域には、1 バイト・コール命令(CALLT)のサブルーチン・エントリ・アドレスを格納できます。

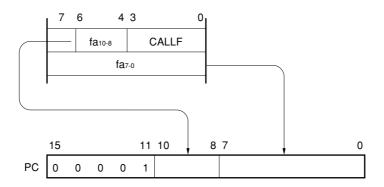

#### (3) CALLF命令エントリ領域

0800H-0FFFHの領域は、2バイト・コール命令(CALLF)で直接サブルーチン・コールできます。

## 3.1.2 内部データ・メモリ空間

μPD780024AS, 780034ASサブシリーズは、次に示す内部高速RAMを内蔵しています。

表 3 一 3 内部高速RAM容量

| 製 品                   | 内部高速RAM                |

|-----------------------|------------------------|

| μPD780021AS, 780031AS | 512×8ビット(FD00H-FEFFH)  |

| μPD780022AS, 780032AS |                        |

| μPD780023AS, 780033AS | 1024×8ビット(FB00H-FEFFH) |

| μPD780024AS, 780034AS |                        |

| μPD78F0034BS          |                        |

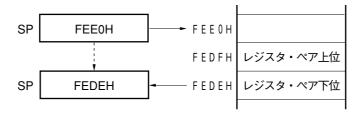

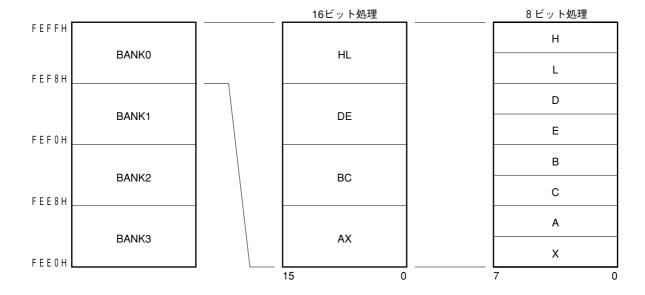

このうちFEE0H-FEFFHの32バイトの領域には、8ビット・レジスタ8個を1バンクとする汎用レジスタが、4バンク割り付けられます。

プログラム領域として命令を書いて実行することはできません。

また、内部高速RAMはスタック・メモリとしても使用できます。

## 3.1.3 特殊機能レジスタ(SFR: Special Function Register)領域

FF00H-FFFFHの領域には、オン・チップ周辺ハードウエアの特殊機能レジスタ(SFR)が割り付けられています (3.2.3 特殊機能レジスタ(SFR: Special Function Register)の表 3 - 5 特殊機能レジスタ一覧参照)。

注意 SFRを割り付けていないアドレスをアクセスしないでください。

## 3.1.4 外部メモリ空間

メモリ拡張モード・レジスタ (MEM) の設定によりアクセスが可能な外部メモリ空間です。プログラム、テーブル・データなどの格納、および周辺デバイスを割り付けることができます。

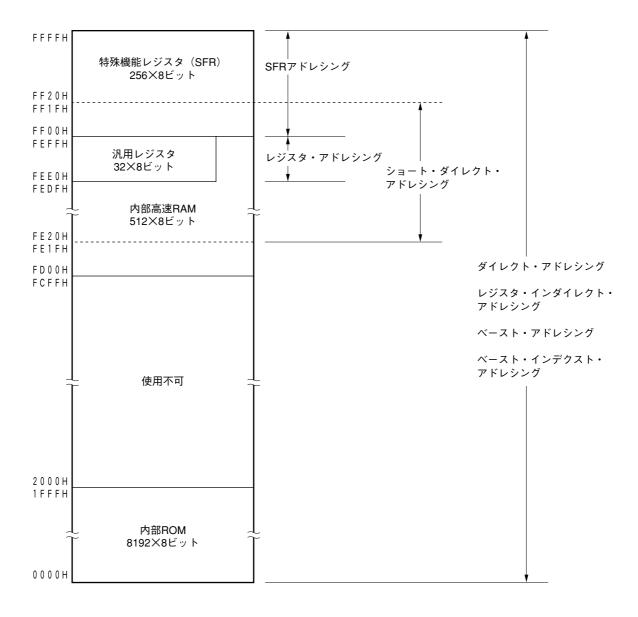

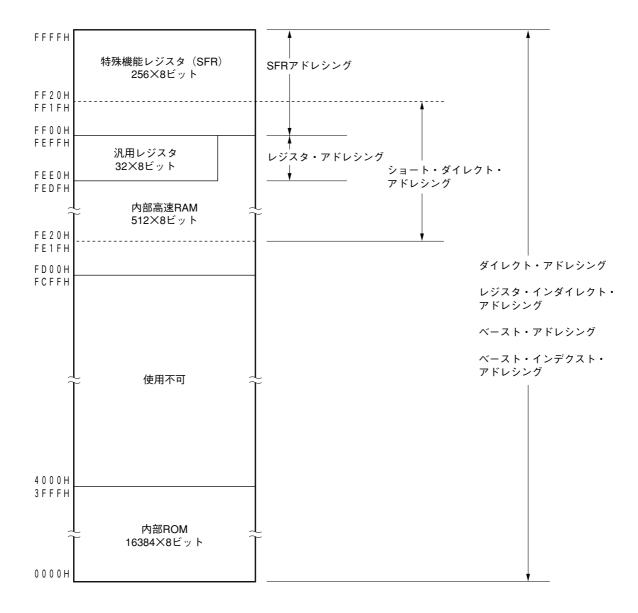

## 3.1.5 データ・メモリ・アドレシング

次に実行する命令のアドレスを指定したり、命令を実行する際に操作対象となるレジスタやメモリなどのアドレスを指定する方法をアドレシングといいます。

命令を実行する際に操作対象となるメモリのアドレシングについて、 $\mu$ PD780024AS, 780034ASサブシリーズでは、その操作性などを考慮して豊富なアドレシング・モードを備えました。特にデータ・メモリを内蔵している領域では、特殊機能レジスタ(SFR)や汎用レジスタなど、それぞれの持つ機能にあわせて特有のアドレシングが可能です。図 3 -6 から図 3 -10にデータ・メモリとアドレシングの対応を示します。各アドレシングの詳細については、3.4 オペランド・アドレスのアドレシングを参照してください。

図 3 - 6 データ・メモリとアドレシングの対応 (μPD780021AS, 780031AS)

#### 図 3 - 7 データ・メモリとアドレシングの対応 (µPD780022AS, 780032AS)

図 3 - 8 データ・メモリとアドレシングの対応 ( µ PD780023AS, 780033AS)

#### 図 3 - 9 データ・メモリとアドレシングの対応 (µPD780024AS, 780034AS)

図 3 -10 データ・メモリとアドレシングの対応 (μPD78F0034BS)

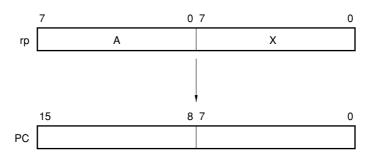

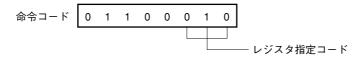

## 3.2 プロセッサ・レジスタ

$\mu$ PD780024AS, 780034ASサブシリーズは、次のプロセッサ・レジスタを内蔵しています。

#### 3.2.1 制御レジスタ

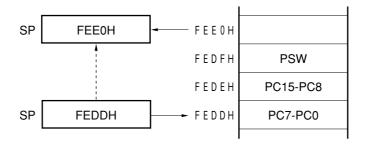

プログラム・シーケンス、ステータス、スタック・メモリの制御など専用の機能を持ったレジスタです。制御レジスタには、プログラム・カウンタ(PC)、プログラム・ステータス・ワード(PSW)、スタック・ポインタ (SP) があります。

#### (1) プログラム・カウンタ(PC)

プログラム・カウンタは、次に実行するプログラムのアドレス情報を保持する16ビット・レジスタです。 通常動作時には、フェッチする命令のバイト数に応じて、自動的にインクリメントされます。分岐命令実 行時には、イミーディエト・データやレジスタの内容がセットされます。

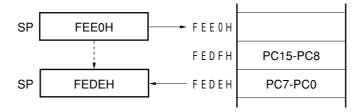

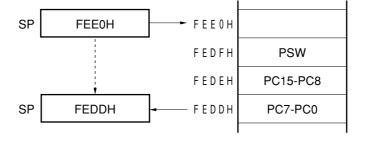

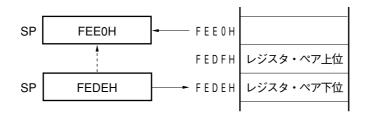

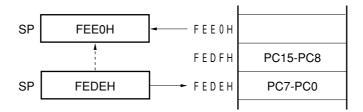

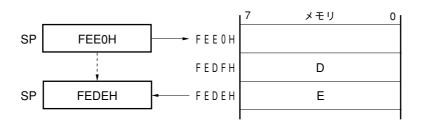

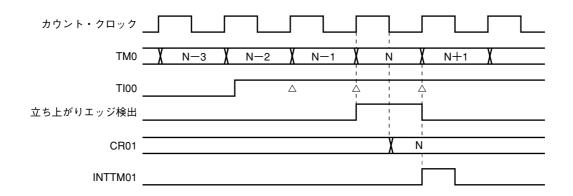

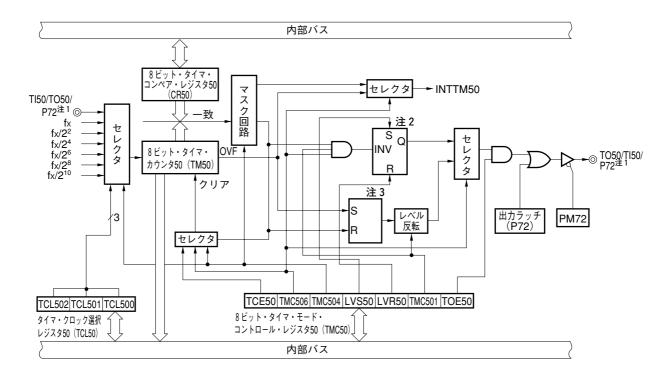

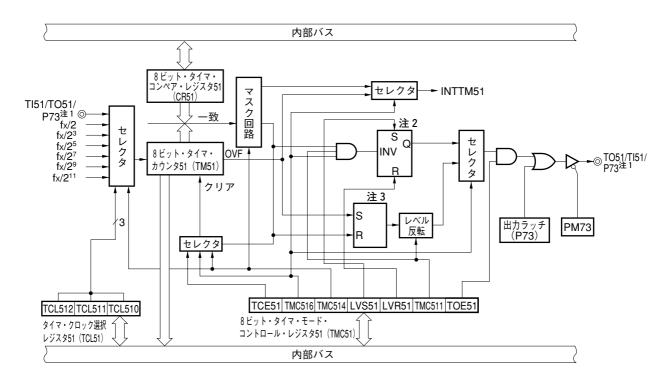

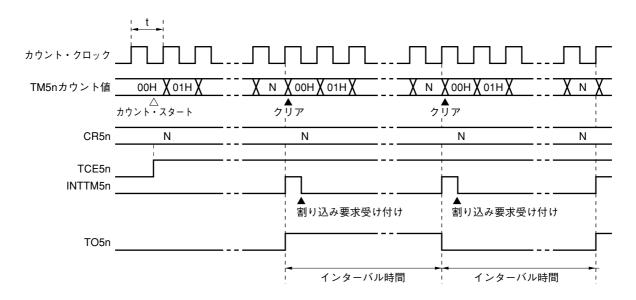

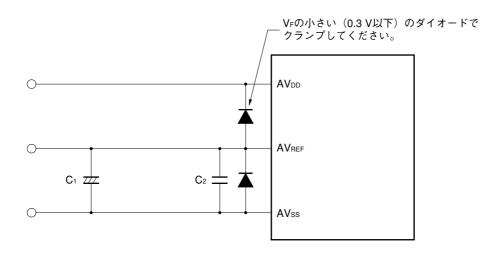

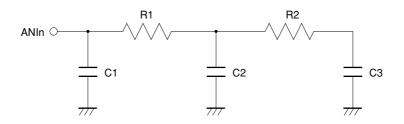

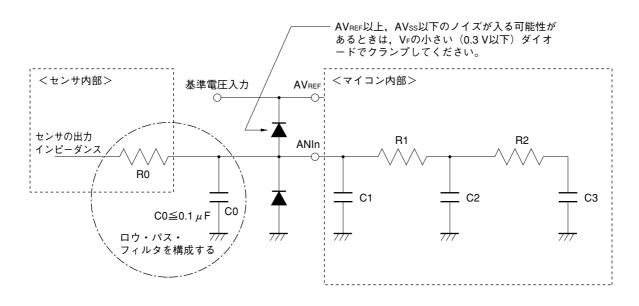

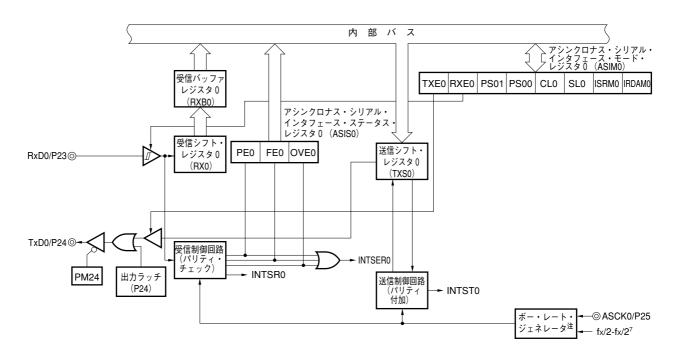

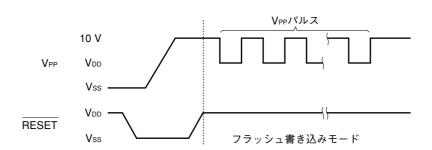

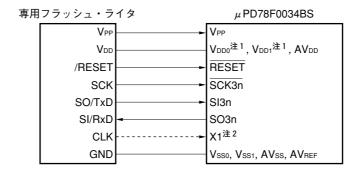

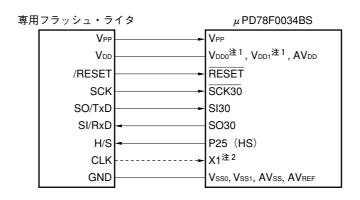

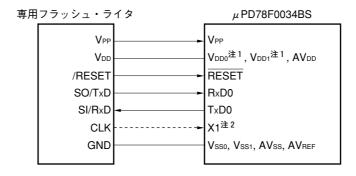

RESET入力により、0000Hと0001H番地のリセット・ベクタ・テーブルの値がプログラム・カウンタにセットされます。