# IE850 インサーキットエミュレータ用 POD

RTE7701460EPA00000R

ユーザーズマニュアル

対象デバイス RH850/D1x シリーズ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

www.renesas.com

# ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を 説明するものです。お客様の機器・システムの設計において、回路、ソフトウェアおよびこれらに関連す る情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因して生じた損害 (お客様または第三者いずれに生じた損害も含みます。以下同じです。)に関し、当社は、一切その責任 を負いません。

- 2. 当社製品、本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行うものではなく、また責任を負うものではありません。

- 3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を、全部または一部を問わず、改造、改変、複製、その他の不適切に使用しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、

家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通制御(信号)、大規模通信機器、

金融端末基幹システム、各種安全制御装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(宇宙、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等)に使用されることを意図しておらず、これらの用途に使用することはできません。たとえ、意図しない用途に当社製品を使用したことにより損害が生じても、当社は一切その責任を負いません。

- 6. 当社製品をご使用の際は、最新の製品情報(データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等)をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 9. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。また、当社製品および技術を、(1)核兵器、化学兵器、生物兵器等の大量破壊兵器およびこれらを運搬することができるミサイル(無人航空機を含みます。)の開発、設計、製造、使用もしくは貯蔵等の目的、(2)通常兵器の開発、設計、製造または使用の目的、または(3)その他の国際的な平和および安全の維持の妨げとなる目的で、自ら使用せず、かつ、第三者に使用、販売、譲渡、輸出、賃貸もしくは使用許諾しないでください。

- 当社製品および技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定めるところに従い必要な手続きを行ってください。

- 10.お客様の転売、貸与等により、本書(本ご注意書きを含みます。)記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は一切その責任を負わず、お客様にかかる使用に基づく当社への請求につき当社を免責いただきます。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 12. 本資料に記載された情報または当社製品に関し、ご不明点がある場合には、当社営業にお問い合わせください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

# 重要事項

本エミュレータをご使用になる前に、必ずユーザーズマニュアルをよく読んで理解してください。 ユーザーズマニュアルは、必ず保管し、使用上不明な点がある場合は再読してください。

#### エミュレータとは:

本資料においてエミュレータとは、ルネサス エレクトロニクス株式会社が製作した次の製品を指します。

(1) IE850 エミュレータ本体、(2) POD

お客様のターゲットシステムおよびホストマシンは含みません。

### エミュレータの使用目的:

本エミュレータは、当社製マイクロコントローラ RH850/D1x シリーズを使用したシステムの開発を支援する装置です。ソフトウェアとハードウェアの両面から、システム開発を支援します。

この使用目的に従って、本エミュレータを正しく使用してください。本目的以外の使用を堅くお断りします。

### エミュレータを使用する人は:

本エミュレータは、ユーザーズマニュアルをよく読み、理解した人のみがご使用ください。

本エミュレータを使用する上で、電気回路、論理回路およびマイクロコンピュータの基本的な知識が必要です。

### エミュレータご利用に際して:

- (1) 本エミュレータは、プログラムの開発、評価段階に使用する開発支援装置です。開発の完了したプログラムを量産に用いる場合には、必ず事前に実装評価、試験などにより、お客様の責任において適用可否を判断してください。

- (2) 本エミュレータを使用したことによるお客様での開発結果については、一切の責任を負いません。

- (3) 弊社は、製品不具合に対する回避策の提示または、不具合改修などについて、有償もしくは無償の対応に努めます。ただし、いかなる場合でも回避策の提示または不具合改修を保証するものではありません。

- (4) 本エミュレータは、プログラムの開発、評価用に実験室での使用を想定して準備された製品です。国内の使用に際し、電気用品安全法及び電磁波障害対策の適用を受けておりません。

- (5) 弊社は、潜在的な危険が存在するおそれのあるすべての起こりうる諸状況や誤使用を予見できません。したがって、このユーザーズマニュアルと本エミュレータに貼付されている警告がすべてではありません。お客様の責任で、本エミュレータを正しく安全に使用してください。

- (6) 本エミュレータは、日本国外の UL などの安全規格、IEC などの規格を取得しておりません。したがって、日本国内から海外に持ち出される場合は、この点をご承知おきください。

- (7) 本エミュレータの偶発的な故障または誤動作によって生じたお客様での直接および間接の損害については、責任を負いません。

### 廃棄について:

本エミュレータを廃棄する時は必ず産業廃棄物として法令に従って処分してください。

### 使用制限:

本エミュレータは、開発支援用として開発したものです。したがって、機器組み込み用として使用しないでください。また、以下に示す開発用途に対しても使用しないでください。

- (1)運輸、移動体用

- (2) 医療用 (人命に関わる装置用)

- (3) 航空宇宙用

- (4)原子力制御用

- (5) 海底中継用

このような目的で本エミュレータの採用をお考えのお客様は、ルネサス エレクトロニクス株式会社 または特約店へご連絡頂きますようお願い致します。

### 製品の変更について:

弊社は、本エミュレータのデザイン、性能を絶えず改良する方針をとっています。したがって、予告なく仕様、デザイン、およびユーザーズマニュアルを変更することがあります。

### 権利について:

- (1)本資料に記載された情報、製品または回路の使用に起因する損害または特許権その他権利の侵害に関しては、弊社は一切その責任を負いません。

- (2) 本資料によって第三者または弊社の特許権その他権利の実施権を許諾するものではありません。

- (3) このユーザーズマニュアルおよび本エミュレータは著作権で保護されており、すべての権利は弊社に帰属しています。このユーザーズマニュアルの一部であろうと全部であろうといかなる箇所も、弊社の書面による事前の承諾なしに、複写、複製、転載することはできません。

### 図について:

このユーザーズマニュアルの一部の図は、実物と違っていることがあります

# 安全事項

安全事項では、その絵表示と意味を示し、安全に正しく使用するための注意事項を説明しますの で、必ずお読みください。また、ここに記載している内容をよく理解してからお使いください。内容 が十分に理解できない場合は当社まで問い合せください。

**↑ 警告** 警告は、回避しないと、死亡または重傷に結びつくものを示します。

注意は、回避しないと、軽傷または中程度の傷害に結びつくものを招く可能 性がある潜在的に危険な状況および物的損害の発生を招く可能性がある潜在 **注意** 的に危険な状況を示しています。

上の2表示に加えて、適宜以下の表示を同時に示します。

△表示は、警告・注意を示します。

○表示は、禁止を示します。

●表示は、強制・指示する内容を示します。

# 警告

### 電源に関して:

別売の電源アダプタの AC 電源ケーブルがコンセントの形状に合わない場合、AC 電源ケーブルを改造したり、無理に入れるなどの行為は絶対に行わないでください。感電事故または火災の原因となります。

日本向け電源アダプタの AC 電源ケーブルは日本の電気用品安全法に適合しています。日本国外で使用する時は、その国の安全規格に適合している AC 電源ケーブルを使用してください。

濡れた手で AC 電源ケーブルのプラグに触れないでください。感電の原因となります。

本エミュレータはシグナルグランドとフレームグランドを接続しています。本エミュレータを用いて開発する製品がトランスレス(AC 電源に絶縁トランスを使用していない)製品である場合、感電する危険があります。また、本エミュレータと開発対象製品に修復不可能な損害を与える場合があります。

開発中はこれらの危険性を回避するために開発対象製品の AC 電源は絶縁トランスを経由して商用電源に接続してください。

本エミュレータのグランドとターゲットシステムのグランド間に電位差が生じないように、 本エミュレータとターゲットシステムを接続時に AC 電源ケーブルのプラグをコンセントに 接続してください。

本エミュレータと同じコンセントに他の装置を接続する場合は、電源電圧および電源電流が過負荷にならないようにしてください。

AC 電源ケーブルの接地端子は、必ずしっかりした接地接続を行ってください。

使用中に異臭・異音がしたり、煙が出る場合は、直ちに電源を切り AC 電源ケーブルをコンセントから抜いてください。

また、感電事故、または火災の原因になりますので、そのまま使用しないで、ルネサス エレクトロニクス株式会社または特約店までご連絡ください。

本エミュレータの設置や他の装置との接続時には、AC 電源を切るか AC 電源ケーブルを抜いて怪我や故障を防いでください。

# ⚠ 警告

### 本エミュレータの取り扱いに関して:

本エミュレータを分解または改造しないでください。分解または改造された場合、感電などにより傷害を負う可能性があります。また分解または改造による故障については、修理を受け付けることができません。

通風口から水・金属片・可燃物などの異物を入れないでください。

空冷用ファンが取り付けられている製品では、下記にご注意ください。

故障等の原因によりファンが動作しない場合、本エミュレータは非常に高温となり、接触によって傷害(やけど等)をおこす可能性があります。万が一、本エミュレータの電源を入れた後ファンが動作しない場合は、すぐに電源を切り、修理にお申し込みください。

### 設置に関して:

湿度が高いところおよび水などで濡れるところには設置しないでください。水などが内部に こぼれた場合、修理不能な故障の原因となります。

### 周辺温度に関して:

本エミュレータの使用における周辺温度の上限(最高定格周辺温度)を越えないように注意してください。

# 注意

### 電源アダプタに関して:

電源アダプタは、別売の専用品以外は使用しないでください。また、本電源アダプタを他の機器に使用しないでください。

#### 電源の投入順序に関して:

電源投入と切断は以下の順序で行ってください。順序を間違えると、ターゲットシステムや エミュレータが故障する場合があります。

電源を ON する場合: ①エミュレータの電源 ON、②ターゲットシステムの電源 ON、

③デバッガ(エミュレータソフトウェア)の接続

電源を OFF する場合: ①デバッガ(エミュレータソフトウェア)の切断、

②ターゲットシステムの電源 OFF、③エミュレータの電源 OFF

### 本エミュレータの取り扱いに関して:

本エミュレータは慎重に扱い、落下・倒れなどによる強い衝撃を与えないでください。

エミュレータやターゲットシステムの接続コネクタの端子は、直接手で触らないでください。 静電気により内部回路を破壊する恐れがあります。

POD ケーブルの抜き差し時には、POD ケーブル部分が引っ張られないように持ち手部分(コネクタなど)を持ち、抜き差ししてください。通信インタフェースケーブルやターゲットシステム接続用ケーブルで、接続した本エミュレータや基板などを引っ張らないでください。POD ケーブルが断線する恐れがあります。

また設置の際に、POD ケーブルを過度に曲げたりしないでください。POD ケーブルが断線する恐れがあります。

本エミュレータにインチサイズのネジを使用しないでください。本エミュレータに使用しているネジはすべて ISO タイプ(メートルサイズ)のネジです。

### 異常動作に関して:

外来ノイズなどの妨害が原因でエミュレータの動作が異常になった場合、次の手順で処置してください。

- ① デバッガ(エミュレータソフトウェア)を終了し、エミュレータとターゲットシステム の電源を OFF する。

- ② 10 秒以上経過してから、再度エミュレータとターゲットシステムの電源を ON し、デバッガ(エミュレータソフトウェア) を起動する。

# 注意

### 使用中の発熱に関して:

長時間使用していると、高温になることがあります。低温やけどなど、高温になることによる障害にご注意ください。

# POD カバーに関して:

POD カバーは必ず取り付けてご使用ください。

# 製品の輸送方法に関して:

修理のために製品を輸送される場合、製品の梱包箱、クッション材を用いて精密機器扱いで 発送してください。製品の梱包が不十分な場合、輸送中に損傷する恐れがあります。 やむをえず他の手段で輸送する場合、精密機器として厳重に梱包してください。 また製品を梱包する場合、必ず製品添付の導電性ポリ袋をご使用ください。 他の袋をご使用になられた場合、静電気の発生などにより製品に別の故障を引き起こす恐れがあります。

### 廃棄に関して:

廃棄する時は必ず産業廃棄物として法令に従って処分してください。

# European Union regulatory notices

Renesas Electronics Europe GmbH can take back end of life equipment, register for this service at "http://www.renesas.eu/weee".

# このマニュアルの使い方

**対象者** このマニュアルは、RTE7701460EPA00000R(以降 POD) を使ってデバッグを行うエンジニア を対象とします。

このマニュアルを読むエンジニアは、デバイスの機能と使用方法を熟知し、デバッガの知識 があることを前提とします。

- **目 的** このマニュアルは、POD の基本仕様と正しい使用方法を理解していただくことを目的としています。

- 構成 このマニュアルは、大きく分けて次の内容で構成します。

- 概説

- ハードウェアの名称と機能

- セットアップ

- 注意事項

- オプション製品

- 保守と保証

- 読み方 このマニュアルの読者には、電気、論理回路、マイクロコンピュータに関する一般知識が必要です。このマニュアルでは、基本的なセットアップ手順とスイッチ類の設定内容を記載しています。

基本仕様と使用方法を一通り理解しようとするとき

→ 目次に従ってお読みください。

IE850 の操作方法やコマンドの機能など、ソフトウェアに関する設定について知りたいとき

→ 使用するデバッガのマニュアルを参照してください。

凡 例 注 : 本文中につけた注の説明

注意 : 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2 進数 ··· xxxx または xxxxB

10 進数 ··· xxxx

16 進数 ··· xxxxH

2のべき数を示す接頭語(アドレス空間、メモリ容量):

$K (+ \square) : 2^{10} = 1024$

M (メガ) : 2<sup>20</sup> = 1024<sup>2</sup>

# 用語 このマニュアルで使用する用語について、その意味を下表に示します。

| 114 - 114 |                                      |  |

|-----------|--------------------------------------|--|

| 対象デバイス    | エミュレーションの対象となっているデバイスです。             |  |

| ターゲットシステム | デバッグの対象となるシステムです(お客様の作成したシステム)。お客    |  |

|           | 様が作成したハードウェアとソフトウェアを含みます。            |  |

| IE850     | IE850 エミュレータシステムの愛称です。               |  |

| IE850 本体  | QB-V850E2 です。                        |  |

| POD       | IE850 本体と組み合わせて使用する製品です。             |  |

| エミュレータ    | 対象デバイスをエミュレーションする製品です。本書では、IE850 本体と |  |

|           | POD が該当します。                          |  |

関連資料 このマニュアル以外に以下の関連資料を参照いただき、ご使用ください。

| 資料名                 |                                                                                 | 資料番号       |            |

|---------------------|---------------------------------------------------------------------------------|------------|------------|

|                     |                                                                                 | 和文         | 英文         |

| リリースノート             | RH850 ファミリ E1/E20/E2 エミュレータ・RH850<br>対応 IE850 用 POD リリースノート<br>(CS+使用時の制限事項)    | R20UT3695J | R20UT3695E |

| IE850 本体            | IE850 インサーキットエミュレータ本体<br>QB-V850E2 ユーザーズマニュアル                                   | R20UT0824J | R20UT0824E |

| エクスチェンジ<br>アダプタ(EA) | BGA484 ピン向けエクスチェンジアダプタ<br>RTE7701412CBF484T000R                                 | R20UT2991J | R20UT2991E |

|                     | BGA376 ピン向けエクスチェンジアダプタ<br>RTE7701410CBF376T000R                                 | R20UT2992J | R20UT2992E |

|                     | BGA272 ピン向けエクスチェンジアダプタ<br>RTE7701461CBF272T000R                                 | R20UT3899J | R20UT3899E |

|                     | QFP176 ピン向けエクスチェンジアダプタ<br>RTE7701463CFK176T000R                                 | R20UT3900J | R20UT3900E |

|                     | QFP144 ピン向けエクスチェンジアダプタ<br>RTE7701422CFK144T000R<br>(旧型名: RTE7701401CFK144T000R) | R20UT3901J | R20UT3901E |

|                     | QFP144 ピン向けエクスチェンジアダプタ<br>RTE7701421CFK144T000R                                 | R20UT3902J | R20UT3902E |

注意:上記関連資料は、予告なしに内容を変更することがあります。設計などには、必ず最新の資料を使用してください。

# 目次

| 里  | 安争垻.            |                       | 3   |

|----|-----------------|-----------------------|-----|

| 安  | 全事項.            |                       | 5   |

| ٦  | のマニュ            | ュアルの使い方1              | 0   |

| 1. | 概説.             | 1                     | 6   |

|    | 1. 1            | ハードウェア仕様1             | 7   |

|    | 1. 2            | システム概要1               | 8   |

|    | 1.3             | 機能概要2                 | 22  |

|    | 1. 3. 1         | プログラム実行機能 2           | 24  |

|    | 1. 3. 2         | リセット                  | 24  |

|    | 1. 3. 3         | ブレーク(プログラムの実行停止)2     | 24  |

|    | 1. 3. 4         | イベント (特定の動作検出)2       | 25  |

|    | 1. 3. 5         |                       |     |

|    | 1. 3. 6         | パフォーマンス測定 2           | 27  |

|    | 1. 3. 7         | マスク 2                 | 27  |

|    | 1. 3. 8         | リアルタイム RAM モニタ 2      | 28  |

|    | 1. 3. 9         | ダイレクトメモリ変更 2          | 28  |

|    | 1. 3. 1         | 0 周辺ブレーク 2            | 8.  |

|    | 1.4             | 規制に関する情報2             | 9   |

|    | 1.5             | エミュレーションの概要           | 0   |

|    | 1.6             | 梱包内容3                 | 1   |

| 2. | /\ <del>-</del> | ・<br>ドウェアの名称と機能3      | 32  |

|    |                 | POD                   |     |

|    |                 | IE850 本体              |     |

|    | Z. Z            | 12000 本体              | , o |

| 3. | セット             | トアップ3                 | 35  |

| ,  | 3. 1            | デバッガのインストール3          | 36  |

| ,  | 3. 2            | IE850 本体の設定 3         | 36  |

| ;  | 3. 3            | POD の設定、IE850 本体との接続3 | 36  |

|    | 3. 3. 1         | POD カバーの取り外し3         | 36  |

|    | 3. 3. 2         | クロックの設定3              | 37  |

|    | 3. 3. 3         | IE850 本体と POD の接続     | 8   |

| ;  | 3. 4            | ターゲットシステムの接続3         | 39  |

|    | 3. 4. 1         | POD とターゲットシステムの接続 3   | }9  |

|    | 3. 4. 2         | USB ケーブル、AC アダプタの接続4  | 10  |

| ;  | 3. 5            | IE850 の起動 4           | 11  |

|    | 3. 6            | ターゲットシステムの起動4         | 11  |

|    | 3.7 デバ   | 「ッガの起動                                                                        | 42 |

|----|----------|-------------------------------------------------------------------------------|----|

|    | 3.8 シャ   | ットダウン手順                                                                       | 42 |

|    |          |                                                                               |    |

| 4. |          |                                                                               |    |

|    | 4.1 実デ   | ・バイスとエミュレータの相違に関する注意                                                          | 43 |

|    | 4. 1. 1  | ターゲットシステム電源投入後の動作                                                             | 43 |

|    | 4. 1. 2  | ダウンロードするプログラムについて                                                             | 43 |

|    | 4. 1. 3  | オンチップデバッギングエミュレータの機能                                                          | 43 |

|    | 4. 1. 4  | DBTRAP 命令                                                                     | 43 |

|    | 4. 1. 5  | シリアルプログラミング機能                                                                 | 43 |

|    | 4. 1. 6  | HALT モード (欠番)                                                                 | 43 |

|    | 4. 1. 7  | 消費電流                                                                          | 43 |

|    | 4. 1. 8  | ECC エラー                                                                       | 44 |

|    | 4. 1. 9  | OTP フラグ                                                                       | 44 |

|    | 4. 1. 10 | エミュレータ使用時のリセットと割り込みの動作(欠番)                                                    | 44 |

|    | 4. 1. 11 | オプションバイトレジスタ                                                                  | 44 |

|    | 4. 1. 12 | 発振回路                                                                          | 44 |

|    | 4. 1. 13 | SDR-SDRAM I/F                                                                 | 44 |

|    | 4. 1. 14 | DDR2-SDRAM I/F                                                                | 45 |

|    | 4. 1. 15 | REGOVCC, OSCVCC, ISOVDD, REG1VCC, PLLVCC, SDRBVCC, SDRBCKVCC, SDRAVCC 端子について. | 45 |

|    | 4. 1. 16 | REGOC, REG1C1, REG1C2, REG1C3, REG1C4 端子について                                  | 45 |

|    | 4. 1. 17 | 各電源の VSS 端子について                                                               | 45 |

|    | 4. 1. 18 | A/D コンバータについて                                                                 | 45 |

|    | 4. 1. 19 | Power-On-Clear Reset 0 (POCORES)                                              | 46 |

|    | 4. 1. 20 | Power-On-Clear Reset 1 (POC1RES)                                              | 46 |

|    | 4. 1. 21 | ISOPWRES                                                                      | 46 |

|    | 4. 1. 22 | PWRCTL 端子                                                                     | 46 |

|    | 4. 1. 23 | FCU RAM                                                                       | 46 |

|    | 4. 1. 24 | OCTA                                                                          | 46 |

|    | 4. 1. 25 | Serial RGB                                                                    | 46 |

|    | 4. 1. 26 | Hyper BUS                                                                     | 46 |

|    | 4. 1. 27 | SFMA0                                                                         | 46 |

|    | 4. 1. 28 | SFMA1                                                                         | 47 |

|    | 4. 1. 29 | SFMA2                                                                         | 47 |

|    | 4. 1. 30 | NANDC                                                                         | 47 |

|    | 4. 1. 31 | Error Control Module (ECM)                                                    | 47 |

|    | 4. 1. 32 | Performance Monitor                                                           | 47 |

|    | 4. 1. 33 | Open LDI                                                                      | 48 |

|    | 4.2 デバ   | ・<br>バッグ時の注意                                                                  | 49 |

|    | 4. 2. 1  | ハードウェアブレーク(アクセス)機能について(ブレークが発生するタイミング)                                        | 49 |

|    | 4. 2. 2  | ハードウェアブレーク(アクセス)機能(リード/ライトアクセス検出不可)                                           | 49 |

|    | 4. 2. 3  | ハードウェアブレーク(アクセス)機能(EI INT テーブル)                                               | 49 |

|    | 4. 2. 4  | RAM 領域の初期化について                                                                |    |

|    | 4. 2. 5  | 端子リセット (欠番)                                                                   | 49 |

| 4            | . 2. 6  | トレース機能                                  | 50 |

|--------------|---------|-----------------------------------------|----|

| 4            | . 2. 7  | パワーセーブモード                               | 50 |

| 4            | . 2. 8  | PBG について                                | 50 |

| 4            | . 2. 9  | エミュレータ使用時のリセットについて                      | 51 |

| 4            | . 2. 10 | エミュレータ使用時の割り込みについて                      | 52 |

|              |         | HALT モードと                               | 52 |

| 4            | . 2. 11 | HALT 命令のステップ実行について                      | 52 |

| 4            | . 2. 12 | DEEPSTOP モードへの遷移が発生する命令のステップ実行について      | 52 |

| 4            | . 2. 13 | エミュレータ接続時の注意点(端子リセット)                   | 53 |

| 4            | . 2. 14 | マイコン内蔵の I/0 資源のアクセスについて                 | 53 |

| 4            | . 2. 15 | 周辺モジュールのレジスタについて                        | 53 |

| 4            | . 2. 16 | パフォーマンス計測について                           | 53 |

| 4            | . 2. 17 | リセット                                    | 53 |

| 4            | . 2. 18 | 内蔵フラッシュメモリ書き換え時の注意点(RAM)                | 53 |

| 4            | . 2. 19 | 内蔵フラッシュメモリ書き換え時の注意点(クロックモニタ)            | 54 |

| 4            | . 2. 20 | 内蔵フラッシュメモリ書き換え時の注意点(レジスタ値)              | 54 |

| 4            | . 2. 21 | クロック設定中のブレークについて                        | 55 |

| 4            | . 2. 22 | イベント機能(64bit アクセス)                      | 55 |

| 4            | . 2. 23 | イベント機能(イベント検出順)                         | 55 |

| 4            | . 2. 24 | イベント機能(ビット操作命令)                         | 55 |

| 4            | . 2. 25 | ブレーク成立条件の競合                             | 55 |

| 4            | . 2. 26 | ソフトウェアブレーク機能(RAM 領域)                    | 55 |

| 4            | . 2. 27 | 端子リセットマスク機能について                         | 55 |

| 4            | . 2. 28 | トレースリングモードについて                          | 56 |

| 4            | . 2. 29 | ユーザプログラム中のエミュレータ検出機能                    | 56 |

| 5. 7         | ナプション   | - 製品                                    | 57 |

| 5. 1         | 長時      | 間トレースオプション                              | 57 |

| • • •        | i. 1. 1 | 概要                                      |    |

| 5            | 5. 1. 2 | セットアップ手順                                |    |

|              |         | QB-V850E2-SP 使用時の注意事項                   |    |

| 6 4          | 果守と保証   | 正                                       | 59 |

| 6. 1         |         | ザ登録                                     |    |

| 6. 2         |         |                                         |    |

| 6. 3         |         |                                         |    |

| 6. 4         |         | 内容                                      |    |

| 6. 4<br>6. 5 |         | 規定                                      |    |

| υ. 5         | ) 116理  | 以积기,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | UΙ |

| 付録 /         | A ターケ   | <sup>*</sup> ットインタフェースの特性               | 62 |

# 1. 概説

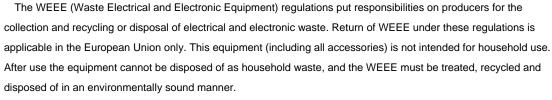

RTE7701460EPA00000R (以降 POD) は、当社製マイクロコントローラ RH850/D1x シリーズをエミュレーションするために、QB-V850E2 (以降 IE850 本体) と組み合わせて使用する製品です。

IE850 を使用することで、対象デバイスを用いたシステム開発においてハードウェア、ソフトウェアを効率的にデバッグできます。

図 1-1 外観

# 1.1 ハードウェア仕様

POD のハードウェア仕様を以下に示します。

# 表 1.1 POD のハードウェア仕様

| 項目             | 仕様                          |

|----------------|-----------------------------|

| エミュレーション対象デバイス | BGA 484pin : RH850/D1M2H    |

|                | BGA 376pin : RH850/D1M2     |

|                | BGA 272pin : RH850/D1M1A    |

|                | BGA 272pin : RH850/D1M1H    |

|                | QFP 176pin : RH850/D1M1     |

|                | QFP 176pin : RH850/D1L2H    |

|                | QFP 144pin : RH850/D1L2     |

|                | QFP 144pin : RH850/D1L1     |

| エミュレータシステム電源   | 5.5V, 3.3V (IE850 本体から供給)   |

| ターゲットシステム電源    | ターゲットデバイスの仕様に従う             |

| 最大動作周波数        | 240MHz                      |

| 発振回路入力周波数      | 8MHz (出荷時、POD 上に搭載している発振回路) |

| 動作温度範囲         | 0~40°C (結露なきこと)             |

| 保存温度範囲         | -15~60°C (結露なきこと)           |

# 1.2 システム概要

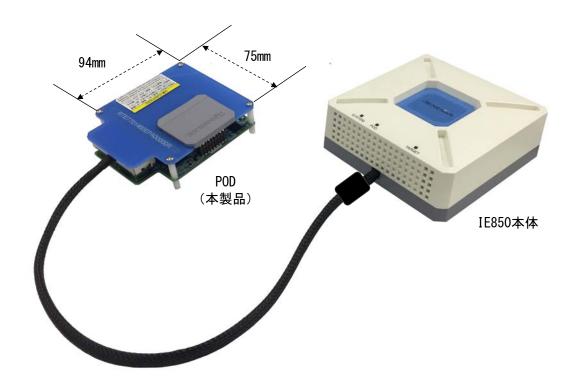

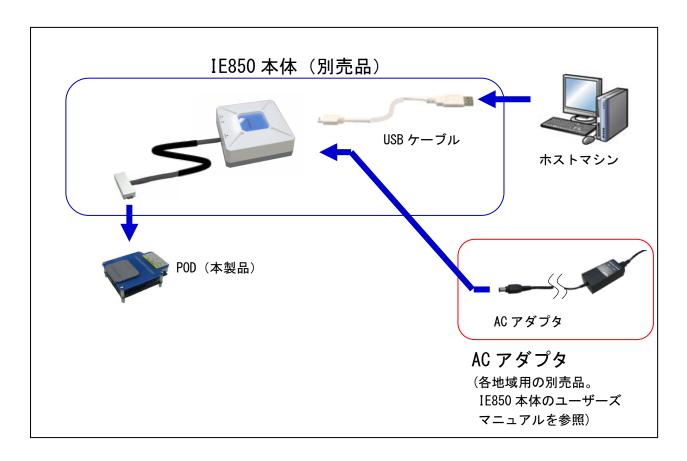

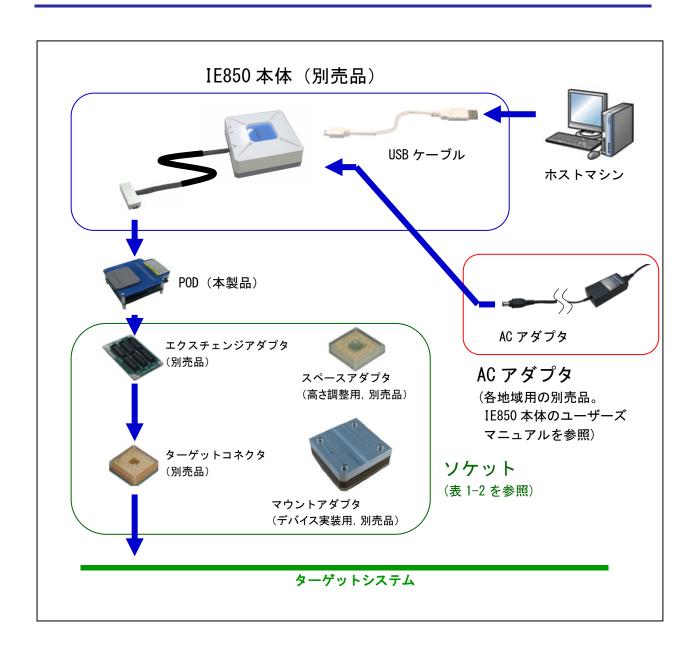

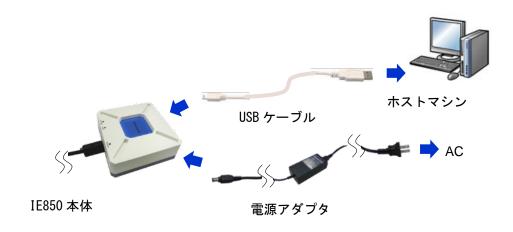

システム概要を以下に示します。POD を使用するためには、別売の IE850 本体、AC アダプタおよび ソケットが必要です。

図 1-2 システム構成(ターゲットシステム未接続時)

図 1-3 システム構成(QFP パッケージ選択時)

図 1-4 システム構成(BGA パッケージ選択時)

対象デバイスに対応するソケットの一覧を下表に示します。 ソケット製品は、本製品(POD)とは 別売品になります。BGAパッケージのターゲットコネクタ(BSSOCKET)、スペースアダプタ(CSSOCKET)、 マウントアダプタ(LSPACK)は、東京エレテック株式会社から購入可能です。 その他は弊社より購入 可能です。

# 表 1.2 対応ソケット一覧

| パッケージ                    | エクスチェンジ               | エミュレータ          | ターゲッ                  | スペース                                         | マウント                                           |

|--------------------------|-----------------------|-----------------|-----------------------|----------------------------------------------|------------------------------------------------|

| デバイス                     | アダプタ                  | コネクタ            | トコネクタ                 | アダプタ                                         | アダプタ                                           |

| BGA484<br>D1M2H          | RTE7701412CBF484T000R | -               | BSSOCKET484Z2627RE21N | CSS0CKET484Z2627RE03<br>CSS0CKET484Z2627RE04 | LSPACK484Z2627RE01                             |

| BGA376<br>D1M2           | RTE7701410CBF376T000R | -               | BSSOCKET376Z2223RE21N | CSSOCKET376Z2223RE03<br>CSSOCKET376Z2223RE04 | LSPACK376Z2223RE01                             |

| BGA272<br>D1M1A<br>D1M1H | RTE7701461CBF272T000R | _               | BSSOCKET272Z2021RE21N | CSS0CKET272Z2021RE03                         | LSPACK272Z2021RE11<br>LSPACK272Z2021RE12<br>*1 |

| QFP176<br>D1M1<br>D1L2H  | RTE7701463CFK176T000R | QB-176GM-YQ-01T | QB-176GM-NQ-01T       | QB-176GM-YS-01T                              | QB-176GM-HQ-01T                                |

| QFP144<br>D1L2           | RTE7701422CFK144T000R | QB-144GJ-YQ-01T | QB-144GJ-NQ-01T       | QB-144GJ-YS-01T                              | QB-144GJ-HQ-01T                                |

| QFP144<br>D1L1           | RTE7701421CFK144T000R | QB-144GJ-YQ-01T | QB-144GJ-NQ-01T       | QB-144GJ-YS-01T                              | QB-144GJ-HQ-01T                                |

\*1: 東京エレテック株式会社にお問い合わせの上、ターゲットシステムの部品配置に応じてどちらかを選択してください。

# 1.3 機能概要

IE850 は対象デバイスの動作をエミュレーションする以外に、プログラムのデバッグを効率的に行えるようデバッグ機能を豊富に搭載しています。ここでは、その機能概要を説明します。

使用するデバッガによってはサポートしていない機能もあります。使用するデバッガのマニュアル 等も合わせて確認してください。

# 表 1.3 機能一覧

| 項目      |                  | 仕様                                              |

|---------|------------------|-------------------------------------------------|

| プログラム実行 | リアルタイム実行         | 可能                                              |

|         | ステップ実行           | 可能                                              |

| リセット    | 強制リセット           | 可能                                              |

| ブレーク    | ソフトウェアブレーク       | ROM / RAM 空間: 2000 点                            |

|         | ハードウェアブレーク       | 実行・CPU アクセス兼用で 12 点                             |

|         |                  | (実行専用8点、実行・アクセス兼用4点)                            |

|         | 強制ブレーク           | 可能                                              |

|         | トレースフルブレーク       | 可能                                              |

|         | トレースディレイブレ<br>ーク | 可能                                              |

| イベント    | 設定可能数            | 実行:8点 / CPU アクセス:8点                             |

|         |                  | DMA アクセス 4 点                                    |

|         | イベント使用機能         | ブレーク、トレース、パフォーマンス測定                             |

|         | イベント組み合わせ        | OR / シーケンシャル                                    |

| トレース    | トレース取得の優先度       | リアルタイムトレースモード                                   |

|         |                  | ノンリアルタイムトレースモード                                 |

|         | トレースメモリ容量        | IE850 本体 : 9M バイト(512K フレーム)                    |

|         |                  | QB-V850E2-SP(長時間トレースオプション):2.25G バイト(128M フレーム) |

|         |                  | 1 フレーム=1 分岐情報(分岐元/先 PC)                         |

|         | 記録データ            | 分岐情報、データアクセスサイクル、DMA アクセスサイクル、タイムスタンプ、ソフトトレース情報 |

|         | 記録開始/終了条件        | プログラムの実行停止、イベントによる条件設定                          |

|         | データトレース条件        | イベント条件                                          |

|         | トレースメモリ          | リングモード(上書きモード)                                  |

|         | 記録方式             | トレースフルストップモード                                   |

|         |                  | トレースディレイストップモード                                 |

|         |                  | トレースフルブレークモード                                   |

|         |                  | トレースディレイブレークモード                                 |

| 項目                   |       |             | 仕様                                                                                                                       |

|----------------------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------|

| パフォーマンス              | 時     | 測定区間        | 実行開始~停止                                                                                                                  |

| 測定                   | 1     | 測定内容        | 実行時間                                                                                                                     |

|                      |       | 性能          | 32bit カウンタ                                                                                                               |

|                      | 時     | 測定区間        | 実行開始~停止、イベント2点間                                                                                                          |

|                      | 1 (2) | 測定内容        | 実行時間、総実行時間、パスカウント                                                                                                        |

|                      |       |             | 最大実行時間、最小実行時間                                                                                                            |

|                      |       | 性能          | 32bit カウンタ (3 区間)                                                                                                        |

|                      | 時間以外  | 測定項目        | 実行命令数(全て、分岐のみ)、割り込み受け付け回数(EI レベル、FE レベル)、例外受け付け回数(命令非同期、命令同期)、クロックサイクル(全て、割り込み禁止状態、割り込み処理中以外)、命令フェッチリクエスト回数、命令キャッシュヒット回数 |

|                      |       | 測定区間        | 実行開始~停止、イベント2点間                                                                                                          |

|                      |       | 測定内容        | 最大値、最小値、最新値、積算値、パスカウント                                                                                                   |

|                      |       | 性能          | 32bit カウンタ (4 区間)                                                                                                        |

| マスク                  |       | リセットマスク     | 可能                                                                                                                       |

|                      |       | リセット端子のみマスク | 不可                                                                                                                       |

|                      |       | PWRGD 信号マスク | 可能(POD 上で、PWRCTL 端子を折り返し接続します)                                                                                           |

| 疑似リアルタイム             | RAM   | モニタ         | 可能(バスを占有します(サイクルスチール))【注 1】                                                                                              |

| ダイレクトメモリ変更           |       |             | 可能(バスを占有します(サイクルスチール))【注 1】                                                                                              |

| 周辺ブレーク               |       |             | 可能【注 2】                                                                                                                  |

| ICUS の ON 設定         |       |             | 可能 (OFF は不可)                                                                                                             |

| ユーザプログラム中のエミュレータ検出機能 |       | エミュレータ検出機能  | 可能【注 3】                                                                                                                  |

|                      |       |             | デバッグスタートアップレジスタ                                                                                                          |

|                      |       |             | 初期値:0000 0000 <sub>H</sub>                                                                                               |

|                      |       |             | アドレス:FA00 2078 <sub>H</sub> (CPU1)                                                                                       |

【注1】Local RAM領域に対してのみ可能です。

【注 2】ブレーク中に周辺 I/0 の動作を停止させる機能のことを周辺ブレーク機能と呼びます。デバッガ上で、周辺エミュレーション機能を停止する/しないを設定することができます。設定方法については、ご利用のデバッガのマニュアルをご確認ください。周辺エミュレーション機能を停止する/しないの選択については、ご使用マイコンのマニュアルにてご確認ください。

【注 3】 エミュレータ接続中にデバッガからデバッグ情報として任意の 32bit データをデバッグスタートアップレジスタに設定し、保持する機能です。

本機能を使用してユーザプログラム上でエミュレータ接続/未接続状態を判定することができます (4.2.29 注意事項参照)。

# 1.3.1 プログラム実行機能

プログラム実行機能によって、対象デバイスと等価なプログラム実行が可能です。実行したプログラムは、ブレーク機能によってさまざまな条件で停止できます。また、任意のアドレスからプログラムを実行できるため、ある関数だけプログラムを実行して動作確認することもできます。

また、ステップ実行機能として、アセンブル命令単位で1命令ずつ実行できるシングルステップと C 言語ソースを1行ずつ実行できるソースレベルステップが可能です。

# 1.3.2 リセット

強制リセット機能によって、デバッガから CPU リセットを行うことができます。プログラム実行をリセットベクタから開始したい場合、デバッグ途中で一度 CPU を初期化したい場合などに使用します。

# 1.3.3 ブレーク(プログラムの実行停止)

ブレーク機能は、プログラムの実行を停止する機能です。IE850 では、次に示すようなさまざまな条件でプログラムの実行を停止することができます。

各ブレーク機能の概要は(1)~(4)で説明します。

### 表 1.4 ブレーク条件とブレークの種類

| ブレーク条件                 | ブレークの種類        |

|------------------------|----------------|

| あるアドレスを実行する際に停止する      | ハードウェアブレーク機能   |

|                        | ソフトウェアブレーク機能   |

| ある変数にアクセスしたら停止する       | ハードウェアブレーク機能   |

| 強制的に停止する               | 強制ブレーク         |

| トレース取得が一定の条件に一致したら停止する | トレースフルブレーク機能   |

|                        | トレースディレイブレーク機能 |

### (1) ハードウェアブレーク

ハードウェアブレーク機能は、特定のフェッチやアクセスに対してブレークする機能です。例 えば、あるアドレスを実行した、ある変数にアクセスしたなどの状態を検出してブレークしま す。

### (2) ソフトウェアブレーク

ソフトウェアブレーク機能は、特定のアドレスを実行(フェッチ)した時にブレークする機能です。指定したアドレスの命令コードを一時的にブレーク用命令に置き換えてブレークします。

注意:内蔵フラッシュメモリにソフトウェアブレーク機能を使用すると、設定/削除やブレーク した際に内蔵フラッシュメモリを書き換えます。そのため、ソフトウェアブレーク未使用 時よりもフラッシュメモリの書き換え寿命が短くなります。

### (3) 強制ブレーク

プログラムを停止したいときに、強制的に停止する機能です。

### (4) その他ブレーク

- ・トレースフルブレークトレースメモリが満杯(フル)になったときに、プログラムを停止する機能です。

- ・ディレイトリガブレーク

あるイベント条件にヒットしてトレースデータを一定量取得した後に、プログラムを停止 する機能です。

### 1.3.4 イベント(特定の動作検出)

イベント機能とは、CPU 及び DMA などの外部マスタのバスサイクルを監視して特定のフェッチや、アクセスを検出する機能です。CPU があるアドレスを実行した、CPU や外部マスタがある変数にアクセスしたなどの動作を検出できます。このような特定の動作をイベントと呼びます。イベント機能は、ブレーク機能、トレース機能、パフォーマンス測定機能で使用します。

# 1.3.5 トレース (プログラムの実行履歴)

トレース機能は、CPU 及び DMA などの外部マスタの実行履歴(トレース情報)を確認できる機能です。IE850 では(1)  $\sim$  (4) に示す様々な機能が利用できます。

(1) トレース取得の優先度 トレース取得の優先度を選択できます。

### 表 1.5 トレース取得の優先度

| トレース取得の優先度      | 詳細説明                                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|

| リアルタイムトレースモード   | プログラム実行を優先するモードです。トレース出力が間に合わない場合、トレース情報の出力を一時的に停止します。そのため、プログラムはリアルタイムに動作しますが、実行するプログラムによってはトレース情報が欠落(ロスト)する場合があります。 |

| ノンリアルタイムトレースモード | トレース取得を優先するモードです。トレース出力が間に合わない場合、CPUの動作を一時的に停止します。そのため、トレース情報が欠落(ロスト)することを抑制************************************      |

# (2) トレースデータタイプ トレースデータタイプ(取得可能なトレース情報)は以下に示す通りです。

# 表 1.6 トレースデータタイプ一覧

| トレースデータタイプ     | 詳細説明                                    |

|----------------|-----------------------------------------|

| 分岐元 PC         | 分岐元 PC と分岐先 PC を履歴に残すことができます。分岐間に実行され   |

| 分岐先 PC         | たプログラムはデバッガが補完して表示します。そのため、実質的に実        |

| (PC=プログラムカウンタ) | 行されたプログラムが確認できます。                       |

|                | 注意:表示可能な実行履歴は取得した分岐数に依存します。             |

| アクセス実行 PC      | CPU からメモリや周辺 I/O レジスタに対するアクセス命令の実行 PC、ア |

| アクセスアドレス       | クセスアドレス、およびアクセスデータの履歴を残せます。リード/ラ        |

| アクセスデータ        | イトの履歴も残せます。                             |

|                | 注意: CPU のプログラムレジスタ(r1 や r2 など)、システムレジス  |

|                | タに対するアクセスは履歴に残せません。                     |

| DMA アクセスサイクル   | DMA からメモリや周辺 I/O レジスタに対するアクセスアドレス、および   |

|                | アクセスデータの履歴を残せます。リード/ライトの履歴も残せます。        |

| タイムスタンプ        | トレースデータ間の経過時間を各トレースデータに付加できます。タイ        |

| (タイムタグ)        | ムスタンプの計測クロックは CPU クロックです。               |

## (3) トレースメモリ記録条件

トレースメモリをどのように使用するかを選択できます。

### 表 1.7 トレースメモリ記録条件一覧

| トレースメモリ記録条件    | 詳細説明                                                                                                                 |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| リングモード         | 古い情報に新しい情報を上書きして、常に最新の情報を取得                                                                                          |

| (上書きモード)       | します。ブレークするまでトレース取得を継続します。                                                                                            |

| トレースフルストップモード  | トレースメモリがフルになった場合に、その後のトレースを<br>取得しません。プログラムは継続して実行されます。                                                              |

| トレースフルブレークモード  | トレースメモリがフルになった場合に、その後のトレースを<br>取得せず、プログラムも停止させます。                                                                    |

| ディレイトリガストップモード | 特定条件が発生するまでは古い情報に新しい情報を上書き<br>して常に最新の情報を取得します。特定条件が発生すると選<br>択したサイズ分トレース情報を取得し、その後のトレースを<br>取得しません。プログラムは継続して実行されます。 |

| ディレイトリガブレークモード | 特定条件が発生するまでは古い情報に新しい情報を上書き<br>して常に最新の情報を取得します。特定条件が発生すると選<br>択したサイズ分トレース情報を取得し、その後のトレースを<br>取得しません。プログラムも停止させます。     |

### 1.3.6 パフォーマンス測定

プログラムの実行開始から停止までの実行時間、特定区間の実行時間や表 1.3 機能一覧に示す項目を測定する機能です。

# 1.3.7 マスク

マスク機能を使うことで、意図しないリセットの発生が原因と思われる現象や、ターゲットシステム上の信号レベルに疑いがある場合のデバッグを補助する機能として、マスク機能があります。以下の要因をマスクすることができます。

# (1) システムリセットマスク

システムリセットすべてをマスク(端子リセット及び内部リセットをマスク)することが 可能です。デバッグチップ(マイコン)内の設定によってマスクを実現します。

注意: 端子リセットのみのマスクは、本 POD ではできません。

デバッガによっては、端子リセットマスクを選択することができますが、本 POD の場合、そのマスク選択は無効です。

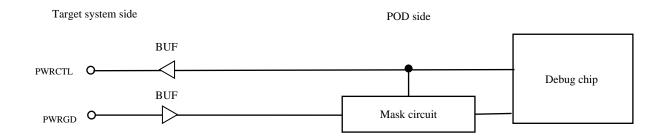

## (2) PWRGD 信号マスク

ターゲットシステムの PWRGD 信号をマスクし、POD 上で、デバッグチップ(マイコン)内の PWRCTL 信号を PWRGD 信号に折り返し入力します。

# 1.3.8 リアルタイム RAM モニタ

プログラム実行中に内蔵 RAM 領域の表示が可能です。

# 1.3.9 ダイレクトメモリ変更

プログラム実行中に内蔵 RAM を任意の値に変更可能です。

# 1.3.10 周辺ブレーク

ブレーク機能でプログラム実行を停止したとき、ウォッチドッグタイマ以外の周辺機能は基本的に 動作を続けますが、周辺ブレーク機能によって停止できる周辺機能があります。停止できる周辺機能 は、対象デバイスのハードウェアマニュアルを参照してください。

#### 1.4 規制に関する情報

# European Union regulatory notices

This product complies with the following EU Directives. (These directives are only valid in the European Union.)

### **CE Certifications:**

This product complies with the following European EMC standards.

EMC Directive (2014/30/EU)

EN 55032 Class A

WARNING: This is a Class A product. This equipment can cause radio frequency noise when used in the residential area. In such cases, the user/operator of the equipment may be required to take appropriate countermeasures under his responsibility.

EN 55024

# Information for traceability:

Authorised representative & Manufacturer

Name: Renesas Electronics Corporation

Address: TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo, 135-0061, Japan

Person responsible for placing on the market

Name: Renesas Electronics Europe GmbH

Address: Arcadiastrasse 10, 40472 Dusseldorf, Germany

Trademark and Type name

Trademark: Renesas

Product name: IE850 Emulator

Type name: RTE7701460EPA00000R

## **Environmental Compliance and Certifications:**

- Waste Electrical and Electronic Equipment (WEEE) Directive 2012/19/EC

### United States Regulatory notices on Electromagnetic compatibility

This product complies with the following EMC regulation. (This is only valid in the United States.)

### FCC Certifications:

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

CAUTION: Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### 1.5 エミュレーションの概要

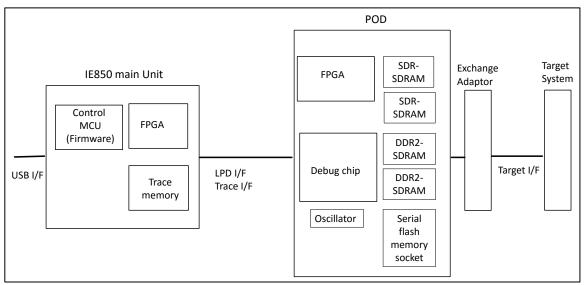

本 POD の内部ブロック図は以下の通りです。

図 1-5 内部ブロック概要

### デバッグチップ:

RH850/D1x シリーズの各対象デバイスの動作をエミュレーションするデバイスです。

### Oscillator:

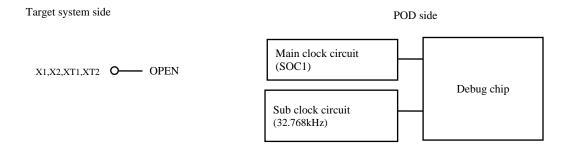

発振特性を考慮し、メイン発振回路、サブ発振回路についてはターゲットシステム上の発振回路を利 用せず、POD上の Oscillator を使います。デバッグチップは、POD上の Oscillator で動作します。詳 しくは3.3.2クロックの設定をご確認ください。

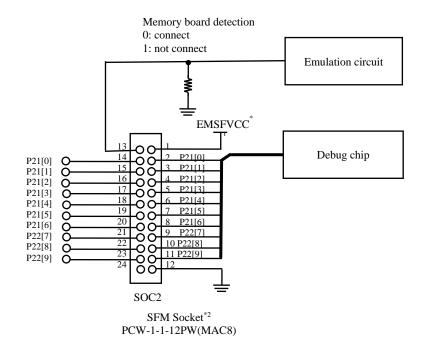

## Serial Flash memory socket :

シリアルフラッシュメモリを搭載可能なソケットです。高速 I/F であるため、デバッグチップからタ ーゲットシステム上のシリアルフラッシュメモリへのアクセスが困難な場合があります。その場合 は、ターゲットシステム上のシリアルフラッシュメモリと等価なメモリ回路を本メモリソケット上に 形成していただき、シリアルフラッシュメモリのアクセスをエミュレーションしてください。

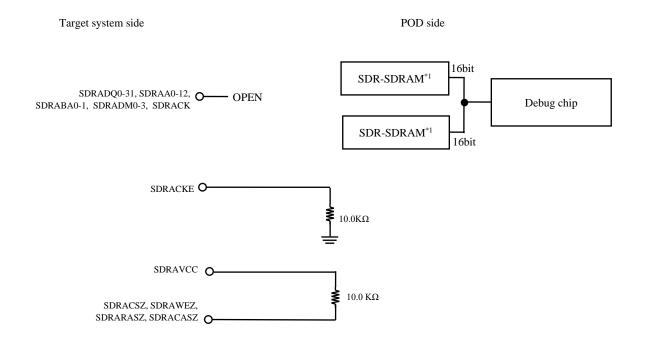

### SDR-SDRAM:

D1M1H の SDR-SDRAM I/F は高速 I/F であるため、デバッグチップが EA など各種ソケットを介してター ゲットシステム上の SDR-SDRAM にアクセスするのは困難です。POD 上に SDR-SDRAM (ISSI 社 IS42S16320x\*-6BL (\*:version D 以上)) を搭載し、POD 上の SDR-SDRAM をユーザターゲットシステム のメモリであるかのように使用することで SDR-SDRAM I/F のエミュレーションを実現します。したが って、ターゲットシステム上の SDR-SDRAM にはアクセスしていません。

### DDR2-SDRAM:

D1M2 (H) シリーズの DDR2-SDRAM I/F は高速 I/F であるため、デバッグチップが EA など各種ソケット を介してターゲットシステム上の SDR-SDRAM にアクセスするのは困難です。POD 上に DDR2 メモリ (Micron 社 MT47H128M16-25E-C) を搭載し、POD 上の DDR2 メモリをユーザターゲットシステムのメモ リであるかのように使用することで DDR2-SDRAM I/F のエミュレーションを実現します。したがって、 ターゲットシステム上の DDR2 メモリにはアクセスしていません。

# 1.6 梱包内容

RTE7701460EPA00000R パッケージに含まれる梱包品は以下に示す通りです。製品ご購入後は、同梱される梱包明細書で確認してください。

RTE7701460EPA00000R の同梱品:

- -POD

- 一有毒有害物質又は元素の含有表

- ーフェライトコア

#### ハードウェアの名称と機能 2.

ハードウェアの名称と機能を以降の各節に記述します。

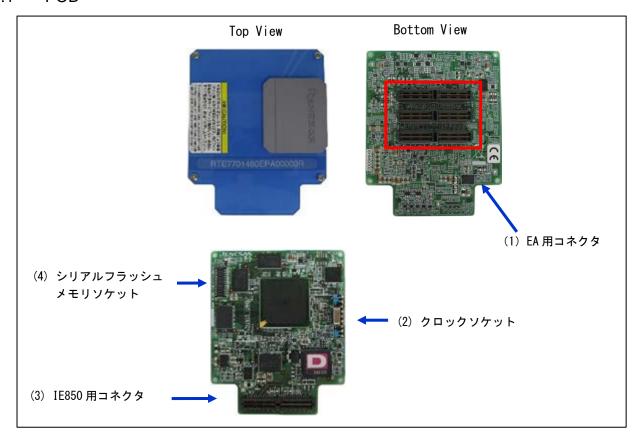

#### 2.1 POD

### 図 2-1 POD 各部の名称

- (1) EA 用コネクタ

- エクスチェンジアダプタ(EA)を接続するためのコネクタです。

- (2) クロックソケット (SOC1) メイン発振回路用のソケットです。出荷時は8MHzの発振回路が実装されています。

- (3) IE850 用コネクタ IE850 本体の POD ケーブルを接続するためのコネクタです。

- (4) シリアルフラッシュメモリソケット (SOC2)

シリアルフラッシュメモリを POD 上に搭載するためのソケットです。出荷時はショートピ ンで短絡されています。 シリアルフラッシュメモリを搭載しない場合は、必ずショートピン を接続したままでご利用ください。搭載する場合は、付録 A ターゲットインタフェースの特 性を参照してください。

#### 2.2 IE850 本体

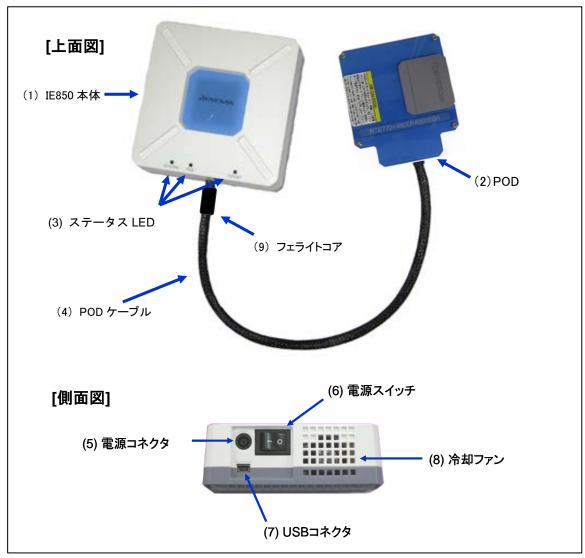

図 2-2 IE850 各部の名称

# (1) IE850 本体

IE850 本体は主にデバッグ機能を制御するユニットです。別売品です。

接続する POD に応じて、制御プログラム(Firmware) および FPGA データを書き換える必要があり ます。書き換えに関する詳細については、http://www.renesas.com/IE850 にてご確認ください。

# (2) POD

本製品です。前節を参照してください。

# (3) ステータス LED

ステータス LED は、下表に示すとおり特定の状態で、点灯/点滅します。LED が点灯/点滅しな い場合、IE850 本体の故障が考えられますので、当社営業窓口または特約店までお問い合わせくだ さい。

| LED 名称 | 仕様                                      |

|--------|-----------------------------------------|

| SYSTEM | 電源スイッチを ON にしたとき、点灯します。                 |

|        | IE850 本体内部の FPGA が正常に動作しない場合、点滅します。この場合 |

|        | は、故障の可能性があります。                          |

| POD    | PODとの通信が正常のとき、点灯します。                    |

| TARGET | ターゲットシステムの電源を ON にしたとき、点灯します。           |

## (4) POD ケーブル

IE850 本体と POD を接続する同軸ケーブルです。ケーブル長は 37cm です。過度にまげると断線 することがありますので注意してください。

### (5) 電源コネクタ

AC アダプタ用のコネクタです。

### (6) 電源スイッチ

電源を ON/OFF するスイッチです。" | "が電源 ON で、"O"が電源 OFF です。

### (7) USB コネクタ

USB ケーブルを接続するコネクタです。

### (8) 冷却ファン

IE850 本体内部を冷却するファンです。風穴をふさがないようにしてください。

# (9) フェライトコア

EMI対策用部品です。

# 3. セットアップ

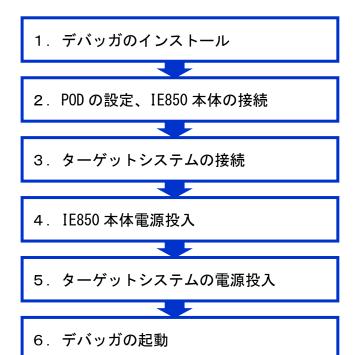

この章では、IE850本体と POD およびターゲットシステム接続までのセットアップ手順について説明します。また、IE850本体と POD のみの接続でもデバッガを起動させることで、ユーザプログラムの開発も可能となります。お客様の用途に合わせ、セットアップしてください。

この章に掲載した順序でインストール/設定を行っていくことでセットアップを完了できます。

セットアップは次の手順に沿って行います。デバッグを終了する場合は、3.8 シャットダウン手順を参照してください。

# 3.1 デバッガのインストール

ハードウェアのセッティングをする前に、必要なデバッガをインストールしてください。インストール方法については、デバッガのユーザーズマニュアルを参照してください。デバッガとは、CS+、Green Hills Software 社製等の統合開発環境 MULTI を指します。

## 3.2 IE850 本体の設定

使用する POD に応じて、IE850 本体の制御プログラム(Firmware) および FPGA データを書きかえる必要があります。本 POD をご利用の場合は、RH850 用の最新データに書き換える必要があります。 IE850 情報サイト http://www.renesas.com/IE850 をご確認ください。

# 3.3 POD の設定、IE850 本体との接続

POD 上のクロック設定を行い、IE850 本体との接続を行います。

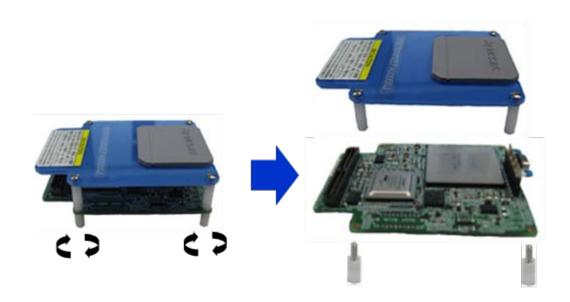

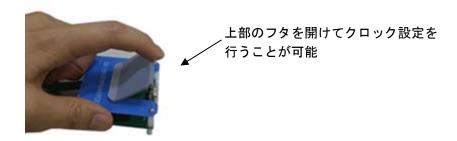

# 3.3.1 POD カバーの取り外し

以下に示すように、POD カバーを取り外してください。

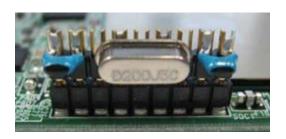

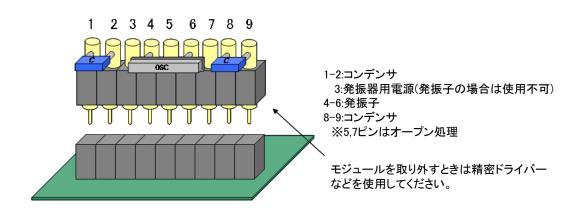

#### 3.3.2 クロックの設定

メイン発振回路によるクロックは、下図に示す POD 上の発振回路によって生成されます。

本製品は、8MHz の発振子を搭載しています。ターゲットシステム上の発振回路と同じ周波数に変更したい場合は、下図の発振子、コンデンサの配置を参考にして、発振回路を形成してください。

注意:本製品はターゲットシステム上の発振回路によるクロックはサポートしていません。 また、サブ発振回路によるクロックは、POD 上で生成された 32.768KHz のクロックを使用します。

補足:本製品は、下図のように POD 上部のフタを開けてクロック設定を行うことができます。

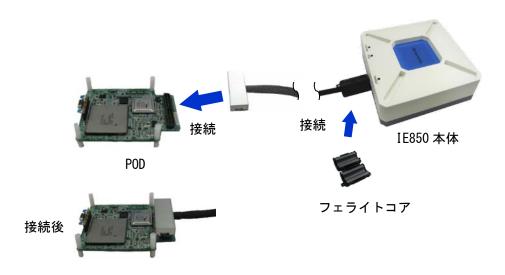

#### 3.3.3 IE850 本体と POD の接続

以下に示すように、IE850本体とPOD、フェライトコアを接続してください。

最後に POD カバーを取り付けて完了です。

#### 3.4 ターゲットシステムの接続

ここでは、ターゲットシステム接続までの全体接続について説明します。

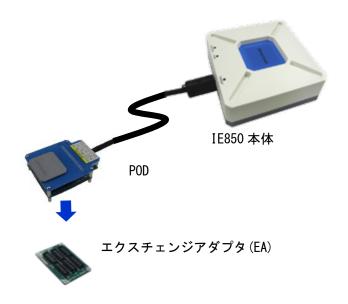

#### 3.4.1 POD とターゲットシステムの接続

ターゲットシステムに接続するために、POD にエクスチェンジアダプタ(EA)、エミュレータコネクタ(EC)、ターゲットコネクタ(TC) などのソケット類を接続してください。

エミュレータコネクタ (EC)、ターゲットコネクタ (TC)の接続については、対象デバイス対応 エクスチェンジアダプタ(EA)用のユーザーズマニュアルを参照してください。

POD とターゲットシステム接続の際、POD ケーブルに過度の曲がりがないように注意してください。 以下に参考で IE850 本体、POD とエクスチェンジアダプタ(EA)の接続イメージを示します。

PODとEAを取り外す場合は、PODのEA取り外しスティック挿入位置シルクに併せて、PODとEAの間にスティックを差し込み、テコの原理でPODを少しずつ引き上げてください。POD裏面の部品がはがれないよう挿入位置にご注意ください。EA取り外しスティックはIE850本体(QB-V850E2)の添付品です。

EA 取り外しスティック挿入位置シルク

## 3.4.2 USB ケーブル、AC アダプタの接続

USB ケーブルと AC アダプタを接続してください。このとき IE850 本体の電源が OFF になっていることを確認してから行ってください。

#### [側面図]

電源アダプタを接続

USB ケーブルを接続

#### 3.5 IE850 の起動

IE850 本体の電源スイッチを ON にしてください。この際、ターゲットシステムの電源が投入されていないことを確認してから行ってください。

スイッチ ON 後、IE850 本体の SYSTEM と POD の LED が点灯します。点灯しない場合は、故障の可能性がありますので、当社営業窓口または特約店までお問い合わせください。

電源スイッチを ON

#### [上面図]

スイッチ ON 後、SYSTEM と POD の LED が 点灯します。

#### 3.6 ターゲットシステムの起動

ターゲットシステムの電源を投入してください。IE850本体のTARGETのLEDが点灯します。点灯しない場合は、接触不良、もしくは故障の可能性があります。接触不良がないか確認し、解決されない場合は、当社営業窓口または特約店までお問い合わせください。

## [上面図]

ターゲットシステムの電源投入後、 TARGET の LED が点灯します。

#### 3.7 デバッガの起動

デバッガを起動してください。以降の操作に関しては、デバッガのユーザーズマニュアルを参照してください。

#### 3.8 シャットダウン手順

開発システムをシャットダウンする場合は、以下に示す手順で行ってください。

- 1. デバッガを終了

- 2. ターゲットシステムの電源を OFF

- 3. IE850 本体の電源を OFF

- 4. 開発システムのシャットダウン

#### 4. 注意事項

IE850 の注意事項を記述します。

#### 4.1 実デバイスとエミュレータの相違に関する注意

エミュレータとターゲットシステムを接続してデバッグした場合、ターゲットシステム上であたかも実デバイスが動作しているようにエミュレーションしますが、実デバイスとエミュレータでは次の点で動作が異なります。このため、量産投入前の最終評価では、実デバイスを使用して評価し、お客様の責任において適用可否を判断してください。

#### 4.1.1 ターゲットシステム電源投入後の動作

ターゲットシステムに実装された対象デバイスは、電源投入後、リセットが解除された時点でプログラムを実行します。しかしエミュレータではデバッガでプログラムをダウンロード後、実行開始の操作を行うまでプログラムを実行しません。

また、エミュレータは変数の初期値情報などを ROM 化する前でもオブジェクトをダウンロードして 実行できますが、実際のデバイスは、ROM 化したオブジェクトでなければ正常に動作しません。

#### 4.1.2 ダウンロードするプログラムについて

プログラムは POD に実装されたデバッグチップのフラッシュメモリにダウンロードされます。ただし、プログラムが正常に実行されるよう、デバッグ開始時は必ずプログラムをダウンロードするようにしてください。

#### 4.1.3 オンチップデバッギングエミュレータの機能

オンチップデバッギングエミュレータをターゲットシステムに接続してデバッグすることはできません。

#### 4.1.4 DBTRAP 命令

DBTRAP 命令はソフトウェアブレーク用に使用するため、プログラムには使用できません。

#### 4.1.5 シリアルプログラミング機能

デバッグ時、シリアルプログラミング機能のエミュレーションはできません。

#### 4.1.6 HALT モード (欠番)

4.2.11に統合。

#### 4.1.7 消費電流

エミュレータの消費電流は、一部電源をエミュレータが供給するため実デバイスよりも少ない場合があります。そのため、量産投入前の最終評価では、実デバイスを使用して評価し、お客様の責任において適用可否を判断してください。

#### 4.1.8 ECC エラー

エミュレータ起動時は、Local RAM 領域が H'0000 0000 に初期化されます。このため、実際のデバイスとは以下のような違いがあります。

- 起動直後の RAM の初期値がデバイス本来の初期値(不定値)とは異なります。

- RAM 未初期化による ECC エラー検出は発生しません。

ECC エラーのエミュレーションを行いたい場合は、以下のオプションを設定してください。

- 起動時に RAM 領域を初期化しない

なお、ワーク RAM 領域(FEBF DA00H~FEBF FFFFH)については、"起動時に RAM 領域を初期化しない" オプションに関わらず、エミュレータ起動時に(エミュレータが)初期化してからエミュレーションを開始するため、ECC エラー検出が発生しない場合があります。

#### 4.1.9 OTP フラグ

セルフプログラミングによって OTP(One Time Programming) フラグを設定しないでください。設定した場合は、デバッガからフラッシュメモリヘダウンロードができなくなります。ご注意ください。

4.1.10 エミュレータ使用時のリセットと割り込みの動作(欠番)

4.2.9、4.2.10 に統合。

#### 4.1.11 オプションバイトレジスタ

下記のオプションバイトレジスタのビットについてはエミュレータが使用するため、デバッガからこれらのビットを書き換えることはできません。

また、セルフプログラミングによってこれらのビットを書き換えないでください。

- OPJTAG[1-0] (OPBTO [17:16]) ビット OPJTAG [1-0] の値は常に 11B になります。

#### 4.1.12 発振回路

エミュレータはターゲットシステム上の発振回路によるクロック入力をサポートしていません。メインクロックとしては POD メインクロック発振回路を使います(3.3.2 クロックの設定参照)。サブクロックとしては POD 上に実装された 32.768kHz のクロックを使います。

なお、ターゲットシステムの最終評価は、実デバイスを実装し、ターゲットシステム上の発振回路 を使用して確認してください。

#### 4.1.13 SDR-SDRAM I/F

エミュレータはターゲットシステム上にある SDR-SDRAM メモリのアクセスをサポートしていません。POD 上に搭載している SDR-SDRAM メモリは、 Integrated Silicon Solution Inc. 製 . IS42S1632Ox\*-6BL(\*: version D 以上)です。

#### 4.1.14 DDR2-SDRAM I/F

エミュレータはターゲットシステム上にある DDR2-SDRAM メモリのアクセスをサポートしていません。POD 上に搭載している、DDR2-SDRAM メモリは、Micron Technology. Inc. 製 MT47H128M16RT-25E×2 個)です。

# 4.1.15 REG0VCC,OSCVCC,ISOVDD,REG1VCC,PLLVCC,SDRBVCC,SDRBCKVCC,SDRAVCC 端子について

REGOVCC, OSCVCC, ISOVDD, REG1VCC, PLLVCC, SDRBVCC, SDRBCKVCC, SDRAVCC は、POD 上でエミュレータが供給します。ターゲットシステムからの電源供給はできません。

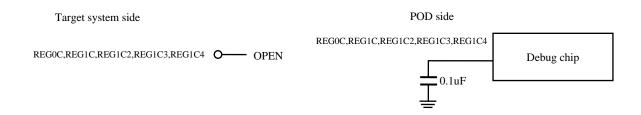

#### 4.1.16 REG0C,REG1C1,REG1C2,REG1C3,REG1C4 端子について

安定化容量接続端子(REGOC, REG1C1, REG1C2, REG1C3, REG1C4)の安定化容量は、POD上で実装されています。これらの端子はターゲットシステムに接続されていません。

#### 4.1.17 各電源の VSS 端子について

次の端子は、エミュレータ内部で共通 GND に接続しています。

PLLVSS, AOVSS, BOVSS, B1VSS, B2VSS, B3VSS, B4VSS, B5VSS, MVSS, SFVSS, ZPDVSS, EVSS, REGOVSS, REG1VSS, RVSS, ISMVSS, OSCVSS, SDRAVSS, ISOVSS, SDRBVSS, SDRBCKVSS

#### 4.1.18 A/D コンバータについて

A/D コンバータは、デバッグチップとターゲットシステムの間にエクスチェンジアダプタなどが存在するため実デバイスとは結果が異なります。

#### 4.1.19 Power-On-Clear Reset 0 (POC0RES)

REGOVCC が降下した場合の POCORES は疑似的にエミュレーションしているため、リセットの動作タイミングは実デバイスと異なります。

ターゲット電源が復帰した際、リセット要因レジスタの値は実デバイスとは異なる場合があります。

#### 4.1.20 Power-On-Clear Reset 1 (POC1RES)

REG1VCC が降下した場合の POC1RES はエミュレーションできません。REG1VCC が降下しても、POC1RES は発生しません。

#### 4.1.21 ISOPWRES

ISOPWRES のエミュレーションはできません。DEEPSTOP モード以外で、PWRGD 端子を"L"レベルにしないでください。

#### 4.1.22 PWRCTL 端子

POC 中の PWRCTL 端子の状態は実デバイスとは異なる場合があります。

#### 4.1.23 FCU RAM

FCU RAM のエミュレーションはできません。

#### 4.1.24 OCTA

OCTA はエミュレーションできません。

#### 4.1.25 Serial RGB

Serial RGB はエミュレーションできません。

#### 4.1.26 Hyper BUS

エミュレーション可能な動作周波数は最大 60MHz です。

#### 4.1.27 SFMA0

本 POD では、SFMAO の最大動作周波数のエミュレーションが可能なことを確認していますが、高速な I/F であるため、ターゲットシステムの状態によっては、ターゲットシステム上のシリアルフラッシュメモリへのアクセスが困難な場合があります。

その場合は、シリアルフラッシュメモリソケット (SOC2)にターゲットシステム上のシリアルフラッシュメモリと等価なメモリ回路を構成してください。

また、SFMAOのドライブ強度設定機能(DSCTRL レジスタにより設定)はエミュレーションできません。

#### 4.1.28 SFMA1

エミュレーション可能な動作周波数は最大 40MHz (SDR I/F)となります。

#### 4.1.29 SFMA2

SFMA2 はエミュレーションできません。

#### 4.1.30 **NANDC**

NANDC の Code flash memory, Data flash memory, Local RAM へのバースト転送はエミュレーション できません。

#### 4.1.31 Error Control Module (ECM)

ECM のエラー入力 INTECM エミュレーションはできません。

#### 4.1.32 **Performance Monitor**

デバッグチップの Performance Monitor における ID のアサインが、実デバイスと異なります。

| PMRID[3:0]<br>PMWID[3:0] | デバッグチップにおけるアサイン            |  |  |

|--------------------------|----------------------------|--|--|

| 0                        | 0: CPU Subsystem(DMA, OCD) |  |  |

| 1                        | 1: CPU Subsystem(CPU)      |  |  |

| 2                        | 2: JCUA                    |  |  |

| 3                        | 3: ETNB                    |  |  |

| 4                        | 4: MLB                     |  |  |

| 5                        | 5: RLE/Sprite UnitO and 1  |  |  |

| 6                        | 6: RLE/Sprite Unit2 and 3  |  |  |

| 7                        | 7: GPU2D (D1M2 emulation)  |  |  |

| 8                        | 8: GPU2D (other emulation) |  |  |

| 9                        | 9: NANDC                   |  |  |

#### 4.1.33 Open LDI

デバッグチップと RH850/D1M1A では、ポートに割り当てられている Open LDI 機能の配置が異なります。

| ポート名称          | デバッグチップのOpen LDI割り当て           | RH850/D1M1AのOpen LDI割り当て       |

|----------------|--------------------------------|--------------------------------|

| P44_10, P44_11 | OLDIO_CH1_P, OLDIO_CH1_N       | _                              |

| P45_0, P45_1   | OLDIO_CHO_CLKP, OLDIO_CHO_CLKN | OLDIO_CHO_CLKP, OLDIO_CHO_CLKN |

| P45_2, P45_3   | OLDIO_CH2_P, OLDIO_CH2_N       | OLDIO_CH1_P, OLDIO_CH1_N       |

| P45_4, P45_5   | OLDIO_CH3_P, OLDIO_CH3_N       | OLDIO_CH2_P, OLDIO_CH2_N       |

| P45_6, P45_7   | OLDIO_CH4_P, OLDIO_CH4_N       | OLDIO_CH3_P, OLDIO_CH3_N       |

| P45_8, P45_9   | -                              | OLDIO_CH4_P, OLDIO_CH4_N       |

本 POD で Open LDI のエミュレーションをする場合は、以下の対応をすべて行う必要があります。

- エクスチェンジアダプタ RTE7701461CBF272T000R 上のスイッチ(SW for [P45\_8, P45\_9]) において、"● Open LDI emulation" を選択します。 これによりデバッグチップの P44\_10, P44\_11 がエクスチェンジアダプタ上で RH850/D1M1A の P45\_8, P45\_9 の端子の位置 に割り当てられます。

Open LDI Emulation を選択している時は、RH850/D1M1A としての P44\_10, P44\_11 の エミュレーションはできません。ターゲットシステム上で P44\_10, P44\_11 を使用しない でください。

Open LDI CH control register (OPLDIOCHCR) デバッグチップの CH 選択を以下のように 設定します。CH1 を CH4、CH2 を CH1、CH3 を CH2、CH4 を CH3 に変更します。こうすることで、RH850/D1M1A の Open LDI 機能のエミュレーションが可能になります。

RH850/D1M1A としての OPLDIOCHCR レジスタの設定を D1M1A\_VALUE とした場合、デバッグチップとしての設定値は以下のように算出可能です。

((D1M1A\_VALUE + 0x0003) & 0x0003) | ((D1M1A\_VALUE + 0x0030) & 0x0030) | ((D1M1A\_VALUE + 0x0300) & 0x0300) | ((D1M1A\_VALUE + 0x3000) & 0x3000)

#### 4.2 デバッグ時の注意

# 4.2.1 ハードウェアブレーク(アクセス)機能について(ブレークが発生するタイミング)

ハードウェアブレーク(アクセス)機能において、データ指定のリードアクセスブレーク、およびデータ指定のリードモディファイライト命令のライトアクセスブレークは実行後ブレークとなります。 それ以外のハードウェアブレーク(アクセス)は実行前ブレークとなります。

4.2.2 ハードウェアブレーク (アクセス) 機能 (リード/ライトアクセス検出不可)

以下の命令によるリード/ライトアクセス条件が成立してもブレークが発生しません。

- (1) CAXI、SET1、CLR1、NOT1、TST1 命令

- (2) PREPARE、DISPOSE、PUSHSP、POPSP、SWITCH、CALLT、SYSCALL 命令 ただし、(1) の命令はデータ条件の指定がない場合のみリードアクセスが検出可能です。

#### 4.2.3 ハードウェアブレーク(アクセス)機能(EIINT テーブル)

EIINTのテーブルアドレスをハードウェアブレーク条件に設定しないでください。ブレークすると EIRET 命令で割り込み処理から元のプログラムに戻れない場合があります。

#### 4.2.4 RAM 領域の初期化について

プログラムで使用する RAM 領域は必ず初期化を行ってください。エミュレータ使用時は、「起動時に RAM 領域を初期化する」に設定した場合、デバッガが RAM 領域を初期化しているため、ECC エラーは発生しません。しかし、RAM 領域の初期化を行わないプログラムで実デバイスを動作させると ECC エラーが発生し、正常にプログラムが動作しません。また、RAM 領域の初期化を行う場合、プログラム実行前に RAM 領域へダウンロードしたデータも初期化されるため、ROM 化も必ず行ってください。ROM 化の詳細は、使用するコンパイラのユーザーズマニュアルを参照してください。

#### 4.2.5 端子リセット(欠番)

4.2.9に統合。

#### 4.2.6 トレース機能

トレース機能には下記制限があります。

- ・PUSHSP 命令、PREPARE 命令実行によるライトデータがトレース取得されない場合があります。

- ・区間(セクション)トレースを設定した時などに、命令フェッチによるトレース開始条件を設定 した命令の直前の命令のアクセスなどがトレースに記録される可能性があります。

- ・トレース取得時は実行するプログラムによっては情報の欠落(ロスト)が発生する場合があります。欠落した情報の復旧は出来ませんが、欠落したことを把握(表示)することができます。

- ・特定アドレスに対するデータアクセスのみをトレースするデータクォリファイトレース (ポイントトレース) の設定において、リードアクセス条件を設定しても、データ条件は無視してトレース されます。データ条件以外の条件でトレースされます。

#### 4.2.7 パワーセーブモード

パワーセーブモード使用時には下記制限があります。

- ・デバッグ時は、プログラム上で WUFMSKO[0]=0 を設定してください。

- ・ユーザプログラム実行中に下記の操作および条件の発生で DEEPSTOP モードは解除されます。 ブレーク成立 メモリアクセス イベントの設定

- ・デバッグ中は、DEEPSTOP モードにおいても、Iso 領域(CPU、RAM、周辺モジュール等)の電源供給は停止しません。そのため、初期値が不定な RAM の値やレジスタの値は保持されるため、RUN モードに復帰後に必ず初期化を行ってください。

#### 4.2.8 PBG について

エミュレータ使用時、PBGの FSGDxxDPROTn レジスタの PROTDEB ビットは、「1」(デバッグマスタアクセスを許可する)から変更しないでください。初期値と異なる場合は、メモリアクセスが正常に行えない場合があります。

#### 4.2.9 エミュレータ使用時のリセットについて

エミュレータ使用時のデバイスの状態とユーザシステムやユーザプログラムが発行するリセット (=ユーザシステムリセット) の動作を表 4.1 に示します。シングルステップ中は、ノンリアルタイムにプログラムのソースコードを1行ずつエミュレーションすることを目的としているため、エミュレータがユーザシステムリセットをマスクします。また、C ソースレベルステップ実行は、デバッガによって実現手段が異なり、シングルステップを利用して実現している場合と、テンポラリのブレークポイントを設定してユーザプログラム実行により実現している場合があります。このため本書でエミュレータがマスクする/しないを定義することができません。デバッガのマニュアルをご確認ください。

|                |                | デバイスの状態        |       |                 |         |

|----------------|----------------|----------------|-------|-----------------|---------|

|                |                | ブレーク中          | シングル  | ユーザプログラ         | Cソースレベル |

|                |                |                | ステップ中 | ム実行中            | ステップ実行中 |

| デバッガ上<br>のリセット | リセット<br>マスクしない | リセットをマスクする【*】  |       | リセットを<br>マスクしない | デバッガ依存  |

| マスク設定          | リセット<br>マスクする  | リセットをマスクする 【*】 |       |                 |         |

表 4.1 デバイスの状態とエミュレータによるユーザシステムリセットのマスク

-デバッガからのリセット(デバッガ上のリセットボタン等)を実行した場合は、リセットマスク有効/無効にかかわらず、常にリセットがかかります。また、デバッガからのリセット後は、すべての CPU はブレークします。

-表 4.1 内の【\*】の状態において発生したリセットは破棄されます。 例えば、ソフトウェアリセットの設定処理をシングルステップ実行した場合や、ブレーク中にソフトウェアリセットの設定レジスタをデバッガ上で操作した場合、ソフトウェアリセット要求は破棄されます。

-ターゲットシステムからの端子リセットは、上記のマスク有無に関わらず、ユーザプログラム実行中以外は、発生させないようにしてください。リセットが発生した場合はデバッガがハングアップする場合があります

#### 4.2.10 エミュレータ使用時の割り込みについて

エミュレータ使用時のデバイスの状態と割り込みの動作を、表 4.2 示します。シングルステップ中は、ノンリアルタイムにプログラムのソースコードを1行ずつエミュレーションすることを目的としているため、エミュレータが割り込みをマスクします。割り込み処理をステップ実行したい場合は、割り込み処理の先頭にブレークポイントを設定し、ユーザプログラム実行中に割り込みを発生させ、割り込み処理の先頭でブレークしてからステップ実行してください。また、Cソースレベルステップ実行は、デバッガによって実現手段が異なり、シングルステップを利用して実現している場合と、テンポラリのブレークポイントを設定してユーザプログラム実行により実現している場合があります。このため本書でエミュレータがマスクする/しないを定義することができません。デバッガのマニュアルをご確認ください。

| デバイスの状態       |       |               |         |  |  |

|---------------|-------|---------------|---------|--|--|

|               | シングル  | ユーザプログラム      | Cソースレベル |  |  |

| ブレーク中         | ステップ中 | 実行中           | ステップ実行中 |  |  |

|               |       | 割り込みをマスクしない   |         |  |  |

| 割り込みをマスクする【*】 |       | (ユーザシステムの設定通り | デバッガ依存  |  |  |

|               |       | に動作)          |         |  |  |

表 4.2 デバイスの状態とエミュレータによる割り込みのマスク

- 表 4.2内の【\*】の状態において発生した割り込み(EIINT と FEINT、FPI)は保留され、マスク解除 後に割り込み処理が実施されます

#### 4.2.11 HALT モードと HALT 命令のステップ実行について

ブレークが発生した場合、HALTモードは解除されます。

HALT 命令をシングルステップ実行(アセンブル命令単位で実行) した場合は、HALT 命令の次の命令でブレークし、HALT モードには遷移しません。HALT 命令を含む C ソースレベルステップ実行において、HALT モードに遷移するかどうかはデバッガの機能に依存します。

#### 4.2.12 DEEPSTOP モードへの遷移が発生する命令のステップ実行について

ステップ実行にはシングルステップ実行(アセンブル命令単位で実行)機能と C ソースレベルステップ実行(C 言語ソースや関数レベルで実行)機能があります。DEEPSTOP モードに遷移する命令をシングルステップ実行(アセンブル命令単位で実行)した場合は、リセット時のアドレスでブレークし、DEEPSTOP モードに遷移しません。DEEPSTOP モードに遷移する命令を含む C ソースレベルステップ実行において、DEEPSTOP モードに遷移するかどうかはデバッガの機能に依存します。

#### 4.2.13 エミュレータ接続時の注意点(端子リセット)

エミュレータ接続時のエミュレータとマイコンとの通信準備中に端子リセットをアサートしたままにすると、同通信が不正動作となります。エミュレータ接続時は、リセットをアサートしたままにしないでください。

#### 4.2.14 マイコン内蔵の I/O 資源のアクセスについて

マイコン内蔵の I/0 資源(レジスタ、RAM)をデバッガからアクセス(メモリウィンドウ、I/0 レジスタウィンドウからのアクセス)した場合は、ユーザプログラム上からアクセスした時と同じ動作となります。

例. (I/0) 資源の実際の動作については、各マイコンのマニュアルを参照してください。)

· PBG エリアへのアクセス

PBG エリアをアクセスした時に、ガードが有効の場合は、正常にアクセスできません。また、エラー 検出の対象となります。

#### 4.2.15 周辺モジュールのレジスタについて

シリアルフラッシュメモリインタフェース A(SFMA)、HyperBus コントローラ(HYPB)、OctaBus コントローラ(OCTA)および CANFD へのクロック供給設定がない状態、または正常な供給設定ではない状態で、SFMA レジスタ、HYPB レジスタ、OCTA レジスタおよび CANFD レジスタにデバッガからアクセス(I/O レジスタウィンドウからのアクセス)した場合、タイムアウトする場合があります。正常なクロック供給設定を行ったうえでデバッガからアクセスするよう注意してください。

#### 4.2.16 パフォーマンス計測について

特定区間のパフォーマンスを計測する際、計測開始から計測終了まで、および、計測終了から次の 計測開始までの間隔が短いと計測できない場合があります。正常に計測するためには十分に長い間隔 (注)をとる必要があります。

注:必要な検出間隔はマイコンの動作周波数と LPD 通信周波数に依存します。LPD 周波数は 20MHz です。

#### 4.2.17 リセット

ユーザプログラム実行中に CPU リセットが発生した場合、デバッグ機能 (ブレーク、イベント、トレース、タイマなど) および、マイコンの動作が不安定になる場合があります。

#### 4.2.18 内蔵フラッシュメモリ書き換え時の注意点(RAM)

デバッガはフラッシュメモリ書き換え時(注)に下記の内蔵 RAM 領域(ワーク RAM 領域)を使用します。DMA や外部マスタが下記領域をアクセスする場合は、ワーク RAM 領域を変更して、DMA や外部マスタが使用しない領域を設定してください。

FEBF DAOOH∼FEBF FFFFH

注:フラッシュメモリ書き換えは、下記の操作時に発生します。

- -内蔵フラッシュメモリへのダウンロード

- -メモリパネルや逆アセンブルパネル等を使用した内蔵フラッシュメモリの変更

- -ソフトウェアブレークの設定・解除

- -ソフトウェアブレーク成立後の再実行(ステップ含む)

#### 4.2.19 内蔵フラッシュメモリ書き換え時の注意点(クロックモニタ)

デバッガはフラッシュメモリ書き換え時 (注) に以下に示すように PLL 逓倍を変更します。このため、フラッシュメモリ書き換え時の周波数は、ご使用の周波数より高速になる場合があります。クロックモニタ (CLMA) で設定した周波数の上限を超える場合は、フラッシュメモリ書き換えを抑止します。デバッガによるクロック周波数の変更が問題になる場合、「フラッシュ書き込み時にクロックを変更しない」に設定してください。

#### 【PLL 逓倍の変更】

・D1M2(H), D1M1A の場合

MainOSC=8MHz 時:30 逓倍します。(CPU クロック:240MHz)

MainOSC=10MHz 時:24 逓倍します。(CPU クロック:240MHz)

MainOSC=12MHz 時:20 逓倍します。(CPU クロック:240MHz)

MainOSC=16MHz 時:15 逓倍します。(CPU クロック:240MHz)

·D1M1H の場合

MainOSC=8MHz 時: 25 逓倍します。(CPU クロック: 200MHz)

MainOSC=10MHz 時: 20 逓倍します。(CPU クロック: 200MHz)

MainOSC=16MHz 時: 12.5 逓倍します。(CPU クロック: 200MHz)

·D1M1 の場合

MainOSC=8MHz 時: 20 逓倍します。(CPU クロック: 160MHz)

MainOSC=10MHz 時: 16 逓倍します。(CPU クロック: 160MHz)

MainOSC=16MHz 時: 10 逓倍します。(CPU クロック: 160MHz)

・D1L1、D1L2(H)の場合

MainOSC=8MHz 時:15 逓倍します。(CPU クロック:120MHz)

MainOSC=10MHz 時:12 逓倍します。(CPU クロック:120MHz)

MainOSC=12MHz 時:10 逓倍します。(CPU クロック:120MHz)

MainOSC=16MHz 時:7.5 逓倍します。(CPU クロック:120MHz)

注:フラッシュメモリ書き換えは、下記の操作時に発生します。

- 内蔵フラッシュメモリへのダウンロード

- ・メモリパネル操作による内蔵フラッシュメモリの変更

- ・ソフトウェアブレークの設定・解除

- ・ソフトウェアブレーク成立後の再実行(ステップ含む)

#### 4.2.20 内蔵フラッシュメモリ書き換え時の注意点(レジスタ値)

デバッガは、フラッシュメモリ書き換え時  $(^{(\pm)})$  に PLL0 を発振させ CPU へ供給します。そのため、 CKSC\_IPLLOS\_ACT. PLLOSACT の値が初期値の 0 から 1 に変わってしまいます。レジスタ値の変更が問題になる場合、「フラッシュ書き込み時にクロックを変更しない」に設定してください。

注:フラッシュメモリ書き換えは、下記の操作時に発生します。

- 内蔵フラッシュメモリへのダウンロード

- ・メモリパネル操作による内蔵フラッシュメモリの変更

- ・ソフトウェアブレークの設定・解除

- ・ソフトウェアブレーク成立後の再実行(ステップ含む)

#### 4.2.21 クロック設定中のブレークについて

クロック設定中にブレークした場合、デバッガからフラッシュメモリの書き換えができません。クロック設定中にブレークした状態で下記の操作を実施する場合は、「フラッシュ書き込み時にクロックを変更しない」に設定してください。

- ・再ダウンロードなどフラッシュメモリの書き換えを伴う操作

- ソフトウェアブレークの設定および解除

また、クロック設定するプログラムにソフトウェアブレークを設定しないでください。

#### 4.2.22 イベント機能(64bit アクセス)

64bit サイズを条件としたアクセスイベントを設定しないでください。64bit アクセスサイズ以外のアクセスを検出する、別のイベントが正常に動作しなくなる、といった場合があります。

#### 4.2.23 イベント機能 (イベント検出順)

以下の場合は命令順とイベント検出順が前後する可能性があるためシーケンシャルイベント、区間 トレース、任意区間の時間測定/パフォーマンス測定ができない場合があります。

- 2 命令を同時に実行する場合があるため、連続する命令に設定したイベント

- ・ライトアクセスとリードアクセスのイベント検出タイミングが異なり、ライト→リードの順に命令を実行してもリード→ライトの順で検出される場合があるため、接近したリード命令とライト命令が検出対象となるアクセスイベント

#### 4.2.24 イベント機能(ビット操作命令)

イベントとしてリード/ライトアクセスを条件に設定している場合、ビット操作命令による Read-Modify-Write のライトサイクルが条件成立しても、イベント検出されません。この条件でブレークやパフォーマンス測定のトリガとしては使用できません。

#### 4.2.25 ブレーク成立条件の競合

強制ブレークやイベントブレーク等でブレーク状態に遷移する直前に別のリードアクセスイベント を検出した場合、再実行時にリードアクセスイベントによるブレーク要求が受け付けられるため、再 実行してすぐに再ブレークします。

#### 4.2.26 ソフトウェアブレーク機能(RAM 領域)

ソフトウェアブレーク機能は命令を置き換えることによって実現しています。そのため、実行中に ユーザプログラムによって、ソフトウェアブレークを設定したアドレスが書き換えられると、ブレー クが発生しませんのでご注意ください。

#### 4.2.27 端子リセットマスク機能について

端子リセットのみをマスクする機能は使用できません。

#### 4.2.28 トレースリングモードについて

本 POD のデバッグチップは、メッセージ出力効率向上のため、リファレンスとなるトレースメッセージ以降は、1つ前の同種トレースメッセージとの差分情報のみをトレース出力します。デバッガは、リファレンスと差分情報からトレースメッセージを復元し、トレース情報として、表示しています。また、エミュレータ回路は、デバッグチップに対して、定期的にリファレンスデータの出力要求を出しています。

このため、トレースメモリ記録条件がトレースリングモード(上書きモード)時、トレースメモリの先頭付近では、リファレンスとなるトレースメッセージが上書きされていて、トレースメッセージを復元することができない場合があります。デバッガによっては、復元できなかったトレースメッセージについては、表示しない場合があるのでご注意ください。

#### 4.2.29 ユーザプログラム中のエミュレータ検出機能

デバッグ情報を設定しても、リセットが発生するとデバッグ情報は 0000 0000<sub>H</sub>に初期化されてしまいますのでご注意ください。リセット後に一旦全 CPU をブレークして、再度ユーザプログラム実行するときに、デバッグ情報が再設定されます。

## 5. オプション製品

#### 5.1 長時間トレースオプション

トレースメモリを拡張するためのオプション製品である QB-V850E2-SP について記述します。

#### 5.1.1 概要

QB-V850E2-SP は IE850 用にトレースメモリを拡張できるオプション製品です。使用する場合は、 デバッガの対応バージョンを確認してください。

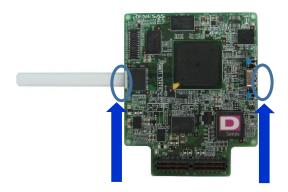

図 5-1 QB-V850E2-SP

#### 5.1.2 セットアップ手順

QB-V850E2-SP を IE850 に接続する手順を示します。

| 1.QB-V850E2-SP の上面にあるカバーを取り外<br>してください。取り外すときは、ドライバー<br>が必要です。                    |  |

|-----------------------------------------------------------------------------------|--|

| 2. IE850 本体から USB ケーブルや AC アダプタ<br>を取り外して、IE850 本体底面にあるカバー<br>を取り外してください。         |  |

| 3. 右図のように QB-V850E2-SP に IE850 本体を<br>接続してください。その後、USB ケーブルや、<br>電源ケーブルを接続してください。 |  |

QB-V850E2-SP を接続すると、IE850 が自動的に検出します。トレースメモリの容量はデバッガで設定してください。

#### 5.1.3 QB-V850E2-SP 使用時の注意事項

- (1) QB-V850E2-SP 及びデバッガのサポートについて QB-V850E2-SP は、Green Hills Software 社製統合環境 MULTI で使用可能です。ルネサス製マイコン用統合環境では使用できません。

- (2) QB-V850E2-SP 使用時のブレーク仕様についてQB-V850E2-SP 使用時は、トレースフルブレークが使用できません。

#### 6. 保守と保証

この章では、本製品の保守方法と保証内容、修理規定と修理の依頼方法を説明しています。

#### 6.1 ユーザ登録

ルネサスエレクトロニクスでは、ツール製品をご購入されたお客様にユーザ登録をお願いしています。ご登録いただくと、新製品のリリース、バージョンアップ、使用上の注意事項などをまとめたツールニュースを電子メールで受け取ることができます。

詳しくは、下記の「ツール製品のユーザ登録のご案内」をご覧ください。

[ツール製品のユーザ登録のご案内]

https://www.renesas.com/registertool\_index

新規ユーザ登録は、下記の My Renesas からご登録をお願いします。

[My Renesas]

https://www.renesas.com/myrenesas

ご登録いただいた内容は、アフターサービスの情報としてのみ利用させていただきます。

#### 6.2 保守

- (1) 本製品に埃や汚れが付着した場合は、乾いた柔らかい布で拭いてください。シンナーなどの溶剤を使用しないでください。塗料が剥げるおそれがあります。

- (2) 本製品を長期間使用しないときは、電源やホストマシン、ターゲットシステムとの接続を取り外して、保管してください。

#### 6.3 保証内容

- (1) 本製品の保証期間は、ご購入後1年間となっております。 取り扱い説明書に基づいた正常なご使用状態のもとで、本製品が万一故障・損傷した場合は、 無償修理または無償交換いたします。

- (2) 保証期間内でも次の項目で、本製品が故障・損傷した場合は、有償修理または有償交換となり

- a) 本製品の誤用、濫用または、その他異常な条件下でのご使用により生じた故障・損傷。

- b) ご購入後の輸送、移動時の落下等、お取り扱いが不適当であったために生じた故障・損傷。

- c)接続している他の機器に起因して本製品に生じた故障・損傷。

- d)火災、地震、落雷、水害、その他天災地変、異常電圧等による故障・損傷。

- e) 弊社以外による改造、修理、調整または、その他の行為にて生じた故障・損傷。

- (3) 消耗品(ソケット、アダプタ等)は修理対象には含みません。

修理を依頼される際は、ご購入された販売元の担当者へご連絡ください。 なお、レンタル中の製品は、レンタル会社または、貸し主とご相談ください。

#### 6.4 修理規定

(1) 有償修理

ご購入後1年を越えて修理依頼される場合は、有償修理となります。

(2) 修理をお断りする場合

次の項目に該当する場合は、修理ではなく、ユニット交換または、新規購入いただく場合があ ります。

- ・機構部分の故障、破損

- ・塗装、メッキ部分の傷、剥がれ、錆

- ・樹脂部分の傷、割れなど

- 使用上の誤り、不当な修理、改造による故障、破損

- ・電源ショートや過電圧、過電流のため電気回路が大きく破損した場合

- ・プリント基板の割れ、パターン焼失

- ・修理費用より交換の費用が安くなる場合

- ・不良箇所が特定できない場合

- (3) 修理期間受付期間

- a) 本製品の修理対応期間は、製品生産中止後3年までです。

- b) 上記修正受付期間中であっても、修理部材が調達できなくなった場合は 修理をお受けできない場合があります。

- (4) 修理依頼時の輸送料など

修理依頼時の輸送料などの費用は、お客様でご負担願います。

#### 6.5 修理依頼方法

製品の故障と診断された場合には、修理依頼方法のサイトから修理依頼書をダウンロードしていただき、必要事項をご記入のうえ、修理依頼書と故障製品を販売元まで送付してください。修理依頼書は、迅速な修理を行うためにも詳しくご記入願います。

[ツール製品の修理依頼方法のご紹介] https://www.renesas.com/ja-jp/repair

#

#### 製品の輸送方法に関して:

修理のために本製品を輸送される場合、本製品の梱包箱、クッション材を用いて精密機器扱いで発送してください。製品の梱包が不十分な場合、輸送中に損傷する恐れがあります。 やむをえず他の手段で輸送する場合、精密機器として厳重に梱包してください。また製品を梱包する場合、必ず製品添付の導電性ポリ袋をご使用ください。他の袋を使用した場合、静電気の発生などにより製品に別の故障を引き起こす恐れがあります。

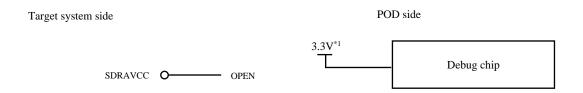

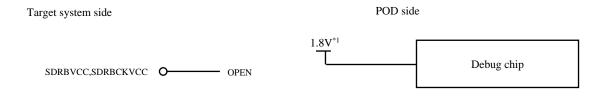

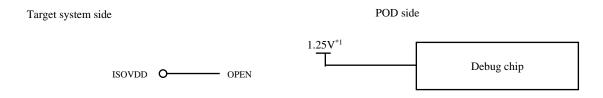

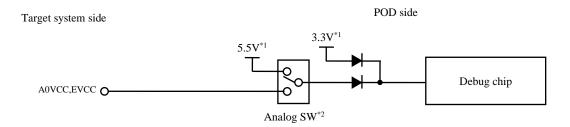

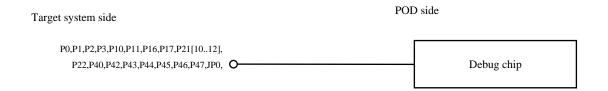

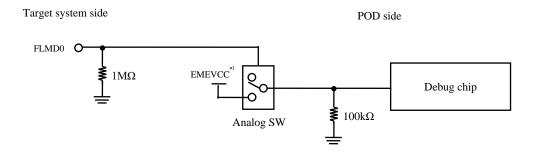

## 付録 A ターゲットインタフェースの特性

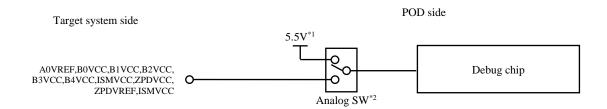

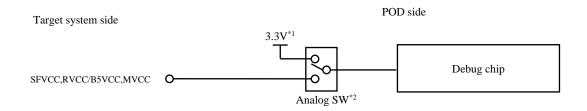

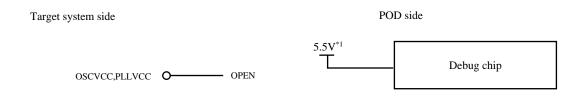

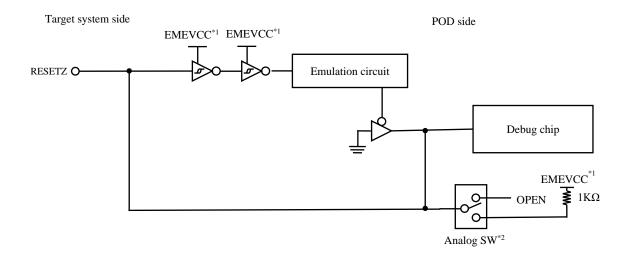

ターゲットインタフェース(インサーキットエミュレータとターゲットシステムを接続する信号)は、機能面ではあたかも実際のデバイスが接続されているような動作をしますが、特性面では実際のデバイスと異なる場合があります。本製品のターゲットインタフェースは以下の等価回路のいずれかになります。

\*1:エミュレーション用内部電源

\*2:ターゲット システム未接続時にエミュレーション用内部電源を供給

#### 図 A-1 等価回路

\*1:エミュレーション用内部電源

\*2:ターゲット システム未接続時にエミュレーション用内部電源を供給

図 A-2 等価回路

図 A-3 等価回路

\*1:エミュレーション用内部電源

\*1:エミュレーション用内部電源

#### 図 A-4 等価回路

\*1:エミュレーション用内部電源

## 図 A-5 等価回路

\*1:エミュレーション用内部電源

図 A-6 等価回路

Target system side

\*1:エミュレーション用内部電源

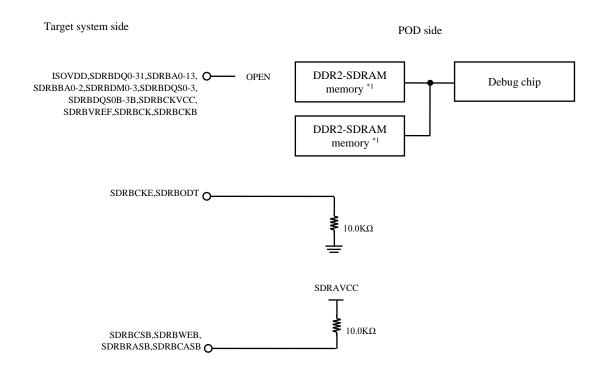

#### 図 A-7 等価回路

\*1:エミュレーション用内部電源

\*2:ターゲット システム未接続時にエミュレーション用内部電源を供給

POD side

#### 図 A-8 等価回路

Target system side POD side

PLLVSS,A0VSS,B0VSS,B1VSS,B2VSS,

B3VSS,B4VSS,B5VSS,MVSS,SFVSS,

ZPDVSS,EVSS,REG0VSS,REG1VSS,

RVSS,ISMVSS,OSCVSS,ISOVSS,

SDRBVSS,SDRBCKVSS,SDRAVSS

図 A-9 等価回路

図 A-10 等価回路

図 A-11 等価回路

図 A-12 等価回路

1:エミュレーション用内部電源

図 A-13 等価回路

\*1:エミュレーション用内部電源 \*2:ターゲット システム接続時に OPEN、ターゲット システム未接続時にプルアップ

図 A-14 等価回路

図 A-15 等価回路

Target system side POD side

\*1:エミュレーション用内部電源 \*2:出荷時はジャンパピンにより短絡しています

図 A-16 等価回路

\*1:IS42S1632Ox\*-6BL(\*: version D以上) (Integrated Silicon Solution Inc.)

#### 図 A-17 等価回路

\*1: MT47H128M16RT-25E (Micron Technology)

図 A-18 等価回路

# ではいる。 TE850 インサーキットエミュレータ用 POD RTE7701460EPA00000R ユーザーズマニュアル

| _             |            |       | 改訂内容                                              |  |  |

|---------------|------------|-------|---------------------------------------------------|--|--|

| Rev. 発行日 Rev. |            | ページ   | ポイント                                              |  |  |

| 1.00          | 2016.12.01 | ı     | 初版                                                |  |  |

| 1.10          | 2017.02.01 | 23    | ユーザプログラム中のエミュレータ検出機能を追加                           |  |  |

|               |            | 47    | 4.1.27 に説明を追加                                     |  |  |

|               |            | 55    | 4.2.29 を追加                                        |  |  |

| 1.20          | 2017.07.01 | 21    | 表 1.2 BGA272 のスペースアダプタから CSSOCKET272Z2021RE04 を削除 |  |  |

|               |            | 29    | 1.4 を更新                                           |  |  |

|               |            | 43-52 | 4.1.6, 4.1.10, 4.2.5 欠番                           |  |  |

|               |            |       | 4.1.8 に説明を追加                                      |  |  |

|               |            |       | 4.1.9 デバッグできない→ダウンロードできないに変更                      |  |  |

|               |            |       | 4.2.1 タイトル変更                                      |  |  |

|               |            |       | 4.2.9 ,4.2.10,4.2.11 タイトル変更と説明を追加                 |  |  |

IE850 インサーキットエミュレータ 用 POD RTE7701460EPA00000R ユーザーズマニュアル

2016年12月01日 Rev. 1.00

発行年月日 2017年02月01日 Rev. 1.10

2017年07月01日 Rev. 1.20

ルネサス エレクトロニクス株式会社 発行 ニュュラ 2004 ままだにま 原典 別の

〒135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

営業お問合せ窓口

http://www.renesas.com

営業お問合せ窓口の住所は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス株式会社 〒135-0061 東京都江東区豊洲3-2-24(豊洲フォレシア)

| 技術的なお問合せおよび資料のご請求は下記へどうぞ。<br>総合お問合せ窓口:https://www.renesas.com/contact/ |  |  |

|------------------------------------------------------------------------|--|--|

|                                                                        |  |  |

|                                                                        |  |  |

|                                                                        |  |  |

|                                                                        |  |  |

# IE850 インサーキットエミュレータ用 POD RTE7701460EPA00000R ユーザーズマニュアル