お客様各位

---

## カタログ等資料中の旧社名の扱いについて

---

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサス テクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサス エレクトロニクス ホームページ (<http://www.renesas.com>)

2010年4月1日

ルネサス エレクトロニクス株式会社

【発行】ルネサス エレクトロニクス株式会社 (<http://www.renesas.com>)

【問い合わせ先】<http://japan.renesas.com/inquiry>

## ご注意書き

1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に關し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

3. 当社製品を改造、改変、複製等しないでください。

4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に關し、当社は、一切その責任を負いません。

5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害があ客様に生じた場合においても、当社は、一切その責任を負いません。

7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができます。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができます。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に關し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準： コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準： 輸送機器（自動車、電車、船舶等）、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器（厚生労働省定義の管理医療機器に相当）

特定水準： 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器（生命維持装置、人体に埋め込み使用するもの、治療行為（患部切り出し等）を行うもの、その他直接人命に影響を与えるもの）（厚生労働省定義の高度管理医療機器に相当）またはシステム等

8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に關して、当社は、一切その責任を負いません。

11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# M16C/6N グループ ( M16C/6N5 )

ハードウェアマニュアル

ルネサスマイクロコンピュータ

M16C ファミリ / M16C/60 シリーズ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、

予告なしに、本資料に記載した製品または仕様を変更することがあります。

ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

## 安全設計に関するお願い

・弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

## 本資料ご利用に際しての留意事項

- ・本資料は、お客様が用途に応じた適切なルネサス テクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサス テクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- ・本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサス テクノロジは責任を負いません。

- ・本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、ルネサス テクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサス テクノロジ半導体製品のご購入に当たりましては、事前にルネサス テクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサス テクノロジホームページ (<http://www.renesas.com>) などを通じて公開される情報に常にご注意ください。

- ・本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起因する損害がお客様に生じた場合には、ルネサス テクノロジはその責任を負いません。

- ・本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサス テクノロジは、適用可否に対する責任は負いません。

- ・本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサス テクノロジ、ルネサス販売または特約店へご照会ください。

- ・本資料の転載、複製については、文書によるルネサス テクノロジの事前の承諾が必要です。

- ・本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサス テクノロジ、ルネサス販売または特約店までご照会ください。

## 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の記載が優先するものとします。

### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。

外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

### 3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。

リセット時、外部発振子（または外部発振回路）を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子（または外部発振回路）を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

(このページは白紙です)

# このマニュアルの使い方

## 1. 目的と対象者

このマニュアルは、本マイコンのハードウェア機能と電気的特性をユーザに理解していただくためのマニュアルです。本マイコンを用いた応用システムを設計するユーザを対象にしています。このマニュアルを使用するには、電気回路、論理回路、マイクロコンピュータに関する基本的な知識が必要です。

このマニュアルは、大きく分類すると、製品の概要、CPU、システム制御機能、周辺機能、電気的特性、使用上の注意で構成されています。

本マイコンは、注意事項を十分確認の上、使用してください。注意事項は、各章の本文中、各章の最後、注意事項の章に記載しています。

改訂記録は旧版の記載内容に対して訂正または追加した主な箇所をまとめたものです。改訂内容すべてを記載したものではありません。詳細は、このマニュアルの本文でご確認ください。

M16C/6Nグループ( M16C/6N5 )では次のドキュメントを用意しています。ドキュメントは最新版を使用してください。最新版はルネサス テクノロジホームページに掲載されています。

| ドキュメントの種類                   | 記載内容                                                                                             | 資料名                                              | 資料番号                               |

|-----------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------|

| データシート                      | ハードウェアの概要と電気的特性                                                                                  | M16C/6Nグループ<br>( M16C/6N5 )<br>データシート            | RJJ03B0004                         |

| ハードウェアマニュアル                 | ハードウェアの仕様( ピン配置、メモリマップ、周辺機能の仕様、電気的特性、タイミング )<br>と動作説明<br><br>周辺機能の使用方法はアプリケーション<br>ノートを参照してください。 | M16C/6Nグループ<br>( M16C/6N5 )<br>ハードウェアマニュアル       | 本ハードウェア<br>マニュアル<br>( RJJ09B0008 ) |

| ソフトウェアマニュアル                 | CPU命令セットの説明                                                                                      | M16C/60、M16C/20、<br>M16C/Tinyシリーズ<br>ソフトウェアマニュアル | RJJ09B0136                         |

| アプリケーションノート                 | 周辺機能の使用方法、応用例<br>参考プログラム<br>アセンブリ言語、C言語によるプログラムの<br>作成方法                                         | ルネサス テクノロジホームページに<br>掲載されています。                   |                                    |

| RENESAS TECHNICAL<br>UPDATE | 製品の仕様、ドキュメント等に関する速報                                                                              |                                                  |                                    |

## 2. 数や記号の表記

このマニュアルで使用するレジスタ名やビット名、数字や記号の表記の凡例を以下に説明します。

### (1) レジスタ名、ビット名、端子名

本文中では、シンボルで表記します。シンボルの後にレジスタ、ビット、端子を付けて区別します。

(例) PM0レジスタのPM03ビット

P3\_5端子、VCC端子

### (2) 数の表記

2進数は数字の後に「b」を付けます。ただし、1ビットの値の場合は何も付けません。16進数は数字の後に「h」を付けます。10進数には数字の後に何も付けません。

(例) 2進数 : 11b

16進数 : EFA0h

10進数 : 1234

### 3. レジスタの表記

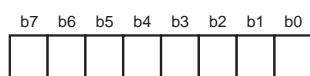

レジスタ図で使用する記号、用語を以下に説明します。

... レジスタ

| シンボル         | アドレス                                          | リセット後の値                                                 |

|--------------|-----------------------------------------------|---------------------------------------------------------|

| ...<br>0 0   | ...                                           | 00h                                                     |

| ビット<br>シンボル  | ビット名                                          | 機能                                                      |

| ... 0        | ... ピット                                       | b1b0<br>00: ...<br>01: ...<br>10: 設定しないでください<br>11: ... |

| ... 1        |                                               | RW<br>RW                                                |

| -<br>(b2)    | 何も配置されていない。書く場合、“0”を書いてください。<br>読んだ場合、その値は不定。 | -                                                       |

| -<br>(b4-b3) | 予約ビット                                         | “0”にしてください                                              |

| ... 5        | ... ピット                                       | WO                                                      |

| ... 6        |                                               | RW                                                      |

| ... 7        | ... ピット                                       | RW<br>RO                                                |

|              |                                               | 0: ...<br>1: ...                                        |

\*1 空白 : 用途に応じて“0”または“1”にしてください。

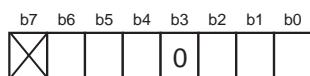

0 : “0”してください。

1 : “1”してください。

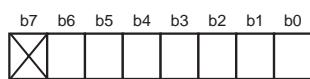

× : 何も配置されてないビットです。

\*2 RW : 読むとビットの状態が読みます。書くと有効データになります。

RO : 読むとビットの状態が読みます。書いた値は無効になります。

WO : 書くと有効データになります。ビットの状態は読みません。

- : 何も配置されてないビットです。

\*3 • 予約ビット

予約ビットです。指定された値にしてください。

\*4 • 何も配置されていない

該当ビットには何も配置されていません。将来、周辺展開により新しい機能を持つ可能性がありますので、書く場合は“0”を書いてください。

• 設定しないでください

設定した場合の動作は保証されません。

• 動作モードによって機能が異なる

周辺機能のモードによってビットの機能が変わります。各モードのレジスタ図を参照してください。

## 4. 略語および略称の説明

| 略語/略称 | フルスペル                                        | 備考                   |

|-------|----------------------------------------------|----------------------|

| ACIA  | Asynchronous Communication Interface Adapter | 調歩同期式通信アダプタ          |

| bps   | bits per second                              | 転送速度を表す単位            |

| CRC   | Cyclic Redundancy Check                      | 巡回冗長検査               |

| DMA   | Direct Memory Access                         |                      |

| DMAC  | Direct Memory Access Controller              |                      |

| GSM   | Global System for Mobile Communications      |                      |

| Hi-Z  | High Impedance                               |                      |

| IEBus | Inter Equipment bus                          | NEC エレクトロニクス社提唱の通信方式 |

| I/O   | Input/Output                                 | 入出力                  |

| IrDA  | Infrared Data Association                    | 赤外線データアソシエーション       |

| LSB   | Least Significant Bit                        | 最下位ビット               |

| MSB   | Most Significant Bit                         | 最上位ビット               |

| NC    | Non-Connection                               | 未接続端子                |

| PLL   | Phase Locked Loop                            | 位相ロックループ             |

| PWM   | Pulse Width Modulation                       | パルス幅変調               |

| SFR   | Special Function Registers                   | 周辺回路制御用レジスタ群         |

| SIM   | Subscriber Identity Module                   | ISO-7816規定のIC カード    |

| UART  | Universal Asynchronous Receiver/Transmitter  | 非同期シリアルインターフェース      |

| VCO   | Voltage Controlled Oscillator                | 電圧制御発振器              |

# 目 次

|                                                     |     |

|-----------------------------------------------------|-----|

| 番地別ページ早見表 .....                                     | B-1 |

| 1 . 概要 .....                                        | 1   |

| 1.1 応用 .....                                        | 1   |

| 1.2 性能概要 .....                                      | 2   |

| 1.3 ブロック図 .....                                     | 3   |

| 1.4 製品一覧 .....                                      | 4   |

| 1.5 ピン接続図 .....                                     | 5   |

| 1.6 端子の機能説明 .....                                   | 9   |

| 2 . 中央演算処理装置( CPU ) .....                           | 12  |

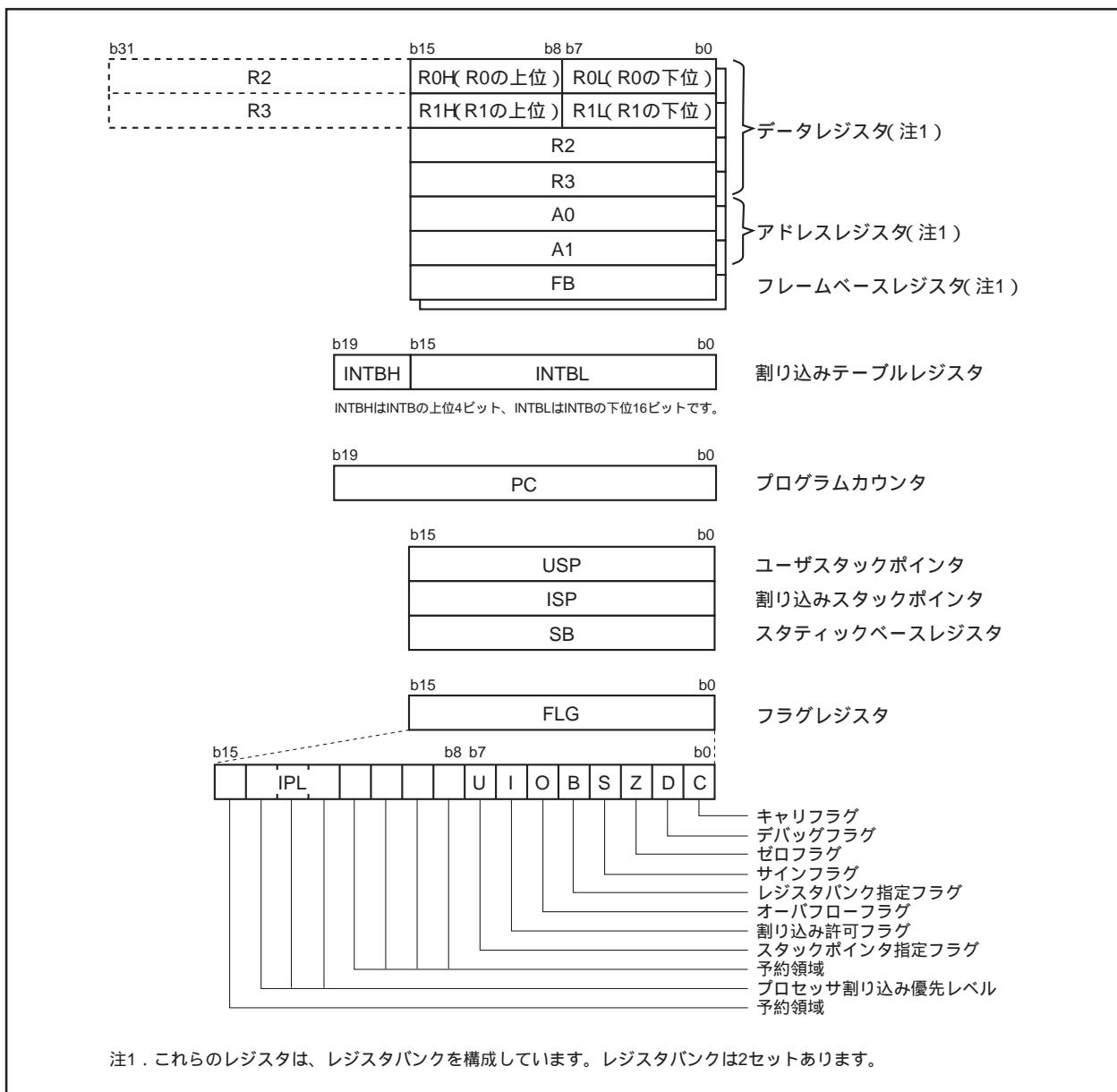

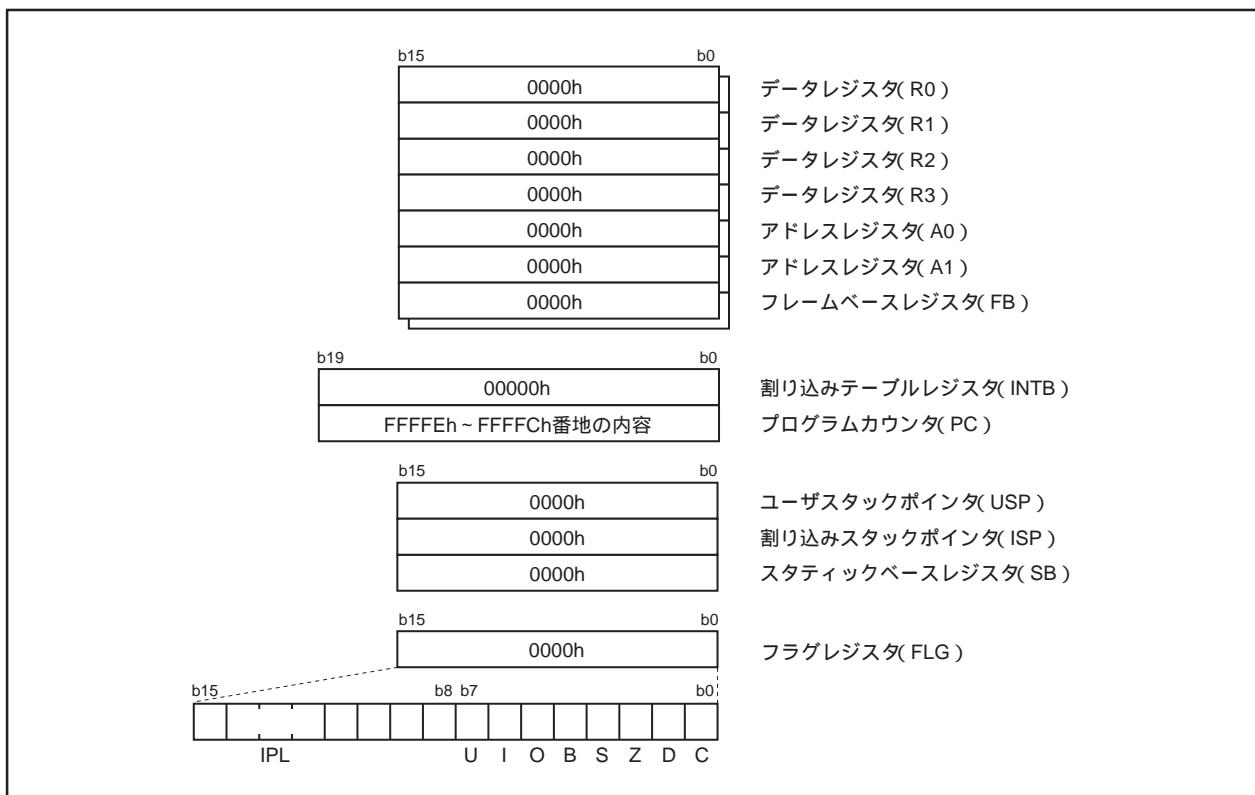

| 2.1 データレジスタ( R0、R1、R2、R3 ) .....                    | 12  |

| 2.2 アドレスレジスタ( A0、A1 ) .....                         | 12  |

| 2.3 フレームベースレジスタ( FB ) .....                         | 13  |

| 2.4 割り込みテーブルレジスタ( INTB ) .....                      | 13  |

| 2.5 プログラムカウンタ( PC ) .....                           | 13  |

| 2.6 ユーザystackポインタ( USP )、割り込みstackポインタ( ISP ) ..... | 13  |

| 2.7 スタティックベースレジスタ( SB ) .....                       | 13  |

| 2.8 フラグレジスタ( FLG ) .....                            | 13  |

| 2.8.1 キャリフラグ( Cフラグ ) .....                          | 13  |

| 2.8.2 デバッグフラグ( Dフラグ ) .....                         | 13  |

| 2.8.3 ゼロフラグ( Zフラグ ) .....                           | 13  |

| 2.8.4 サインフラグ( Sフラグ ) .....                          | 13  |

| 2.8.5 レジスタバンク指定フラグ( Bフラグ ) .....                    | 13  |

| 2.8.6 オーバフローフラグ( Oフラグ ) .....                       | 13  |

| 2.8.7 割り込み許可フラグ( Iフラグ ) .....                       | 13  |

| 2.8.8 スタックポインタ指定フラグ( Uフラグ ) .....                   | 13  |

| 2.8.9 プロセッサ割り込み優先レベル( IPL ) .....                   | 13  |

| 2.8.10 予約領域 .....                                   | 13  |

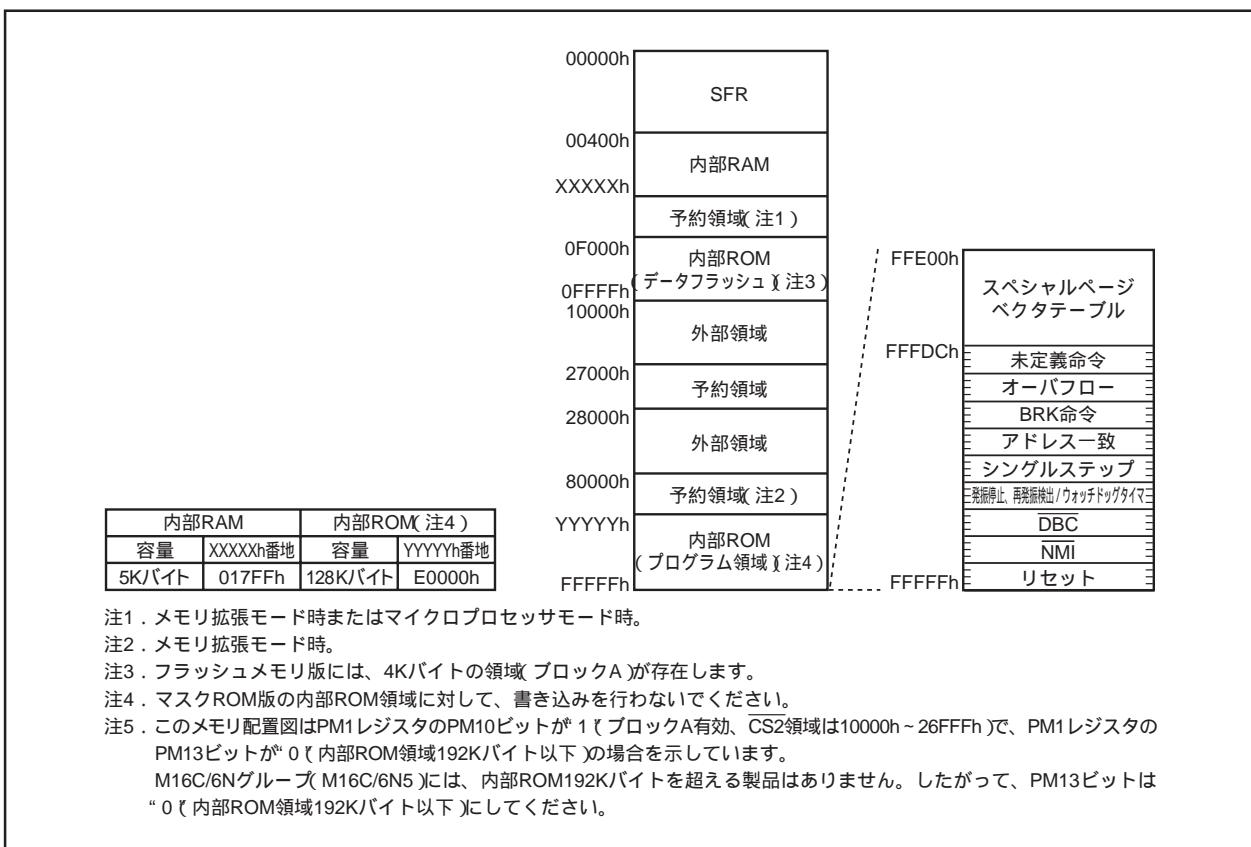

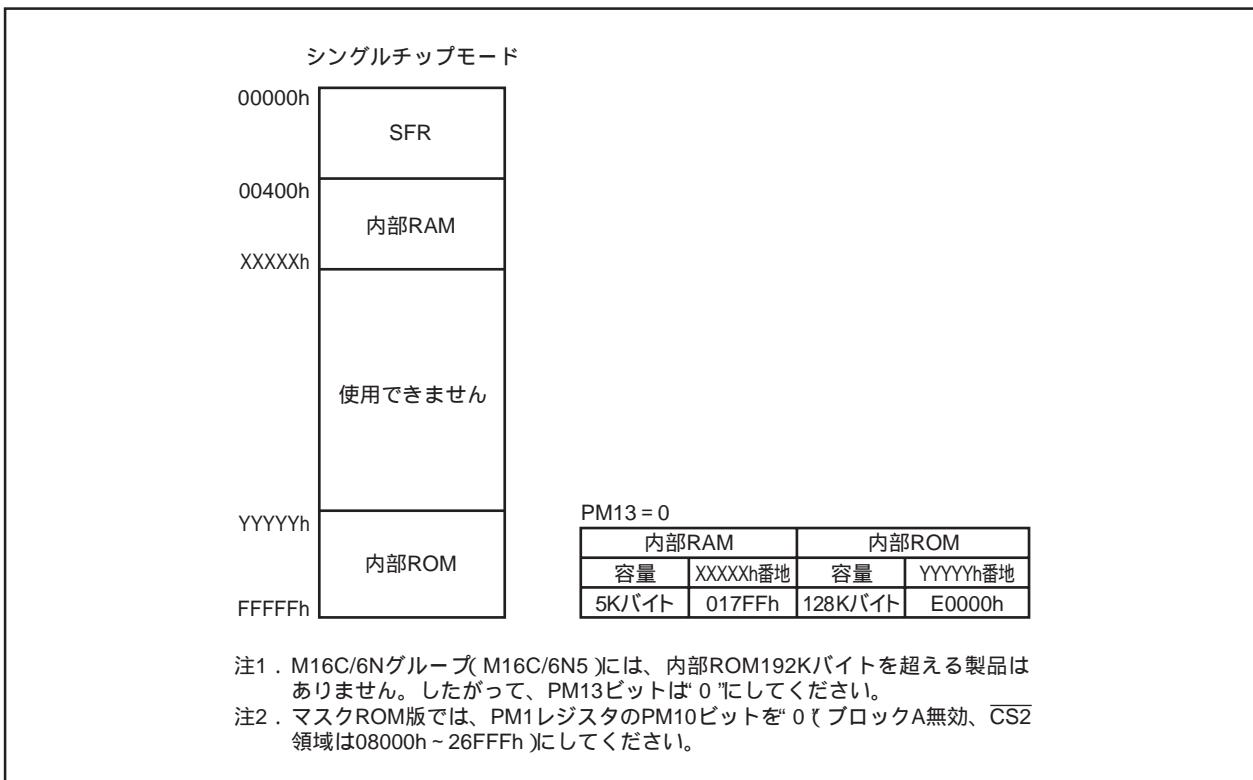

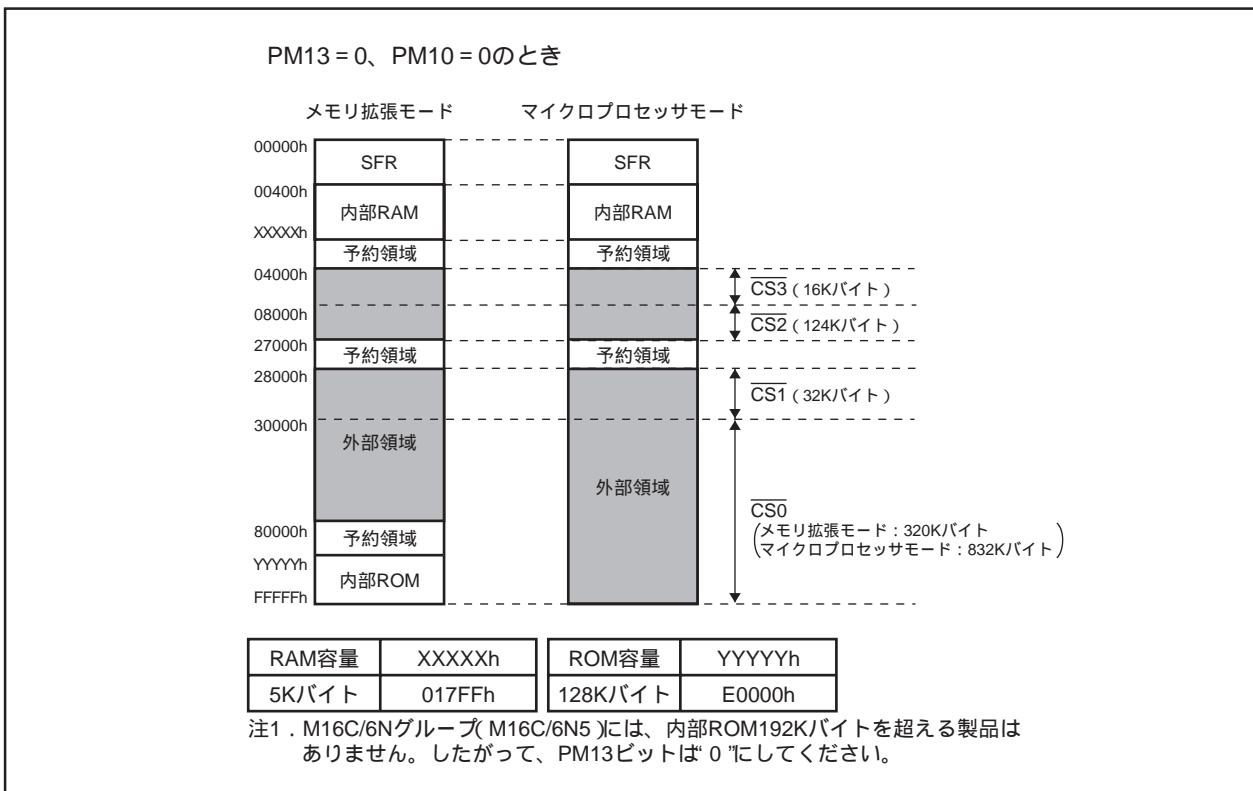

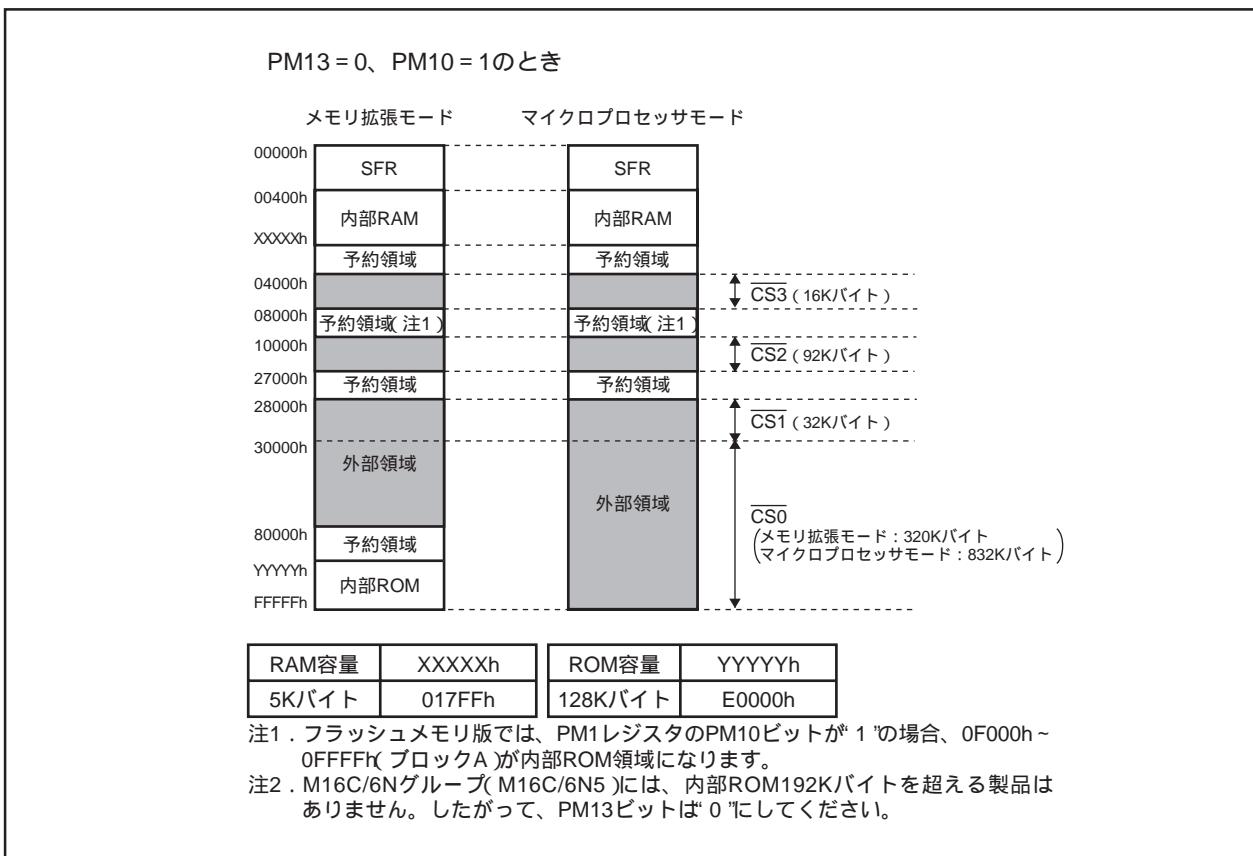

| 3 . メモリ .....                                       | 14  |

| 4 . SFR .....                                       | 15  |

| 5 . リセット .....                                      | 27  |

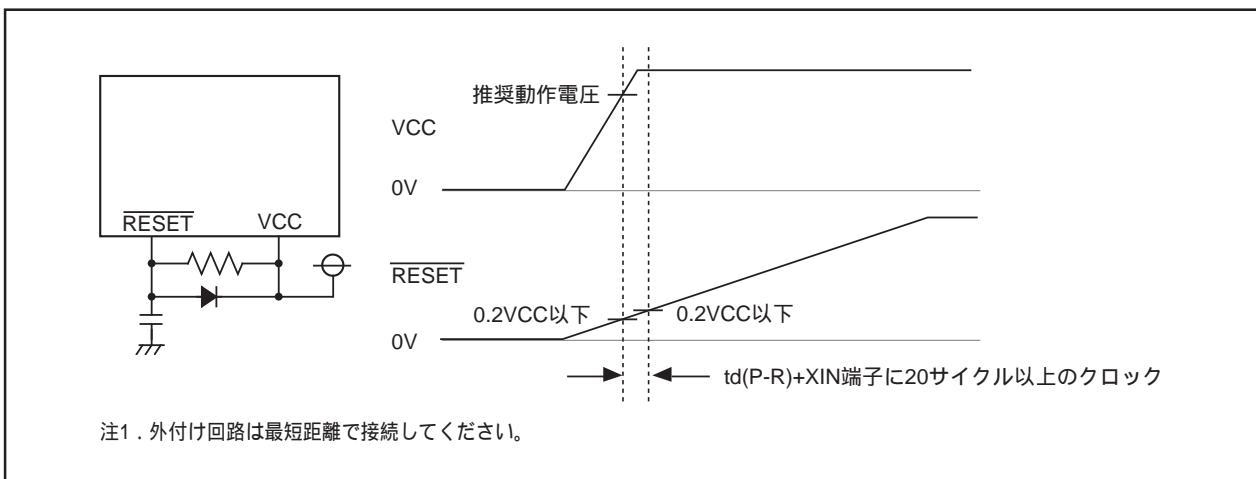

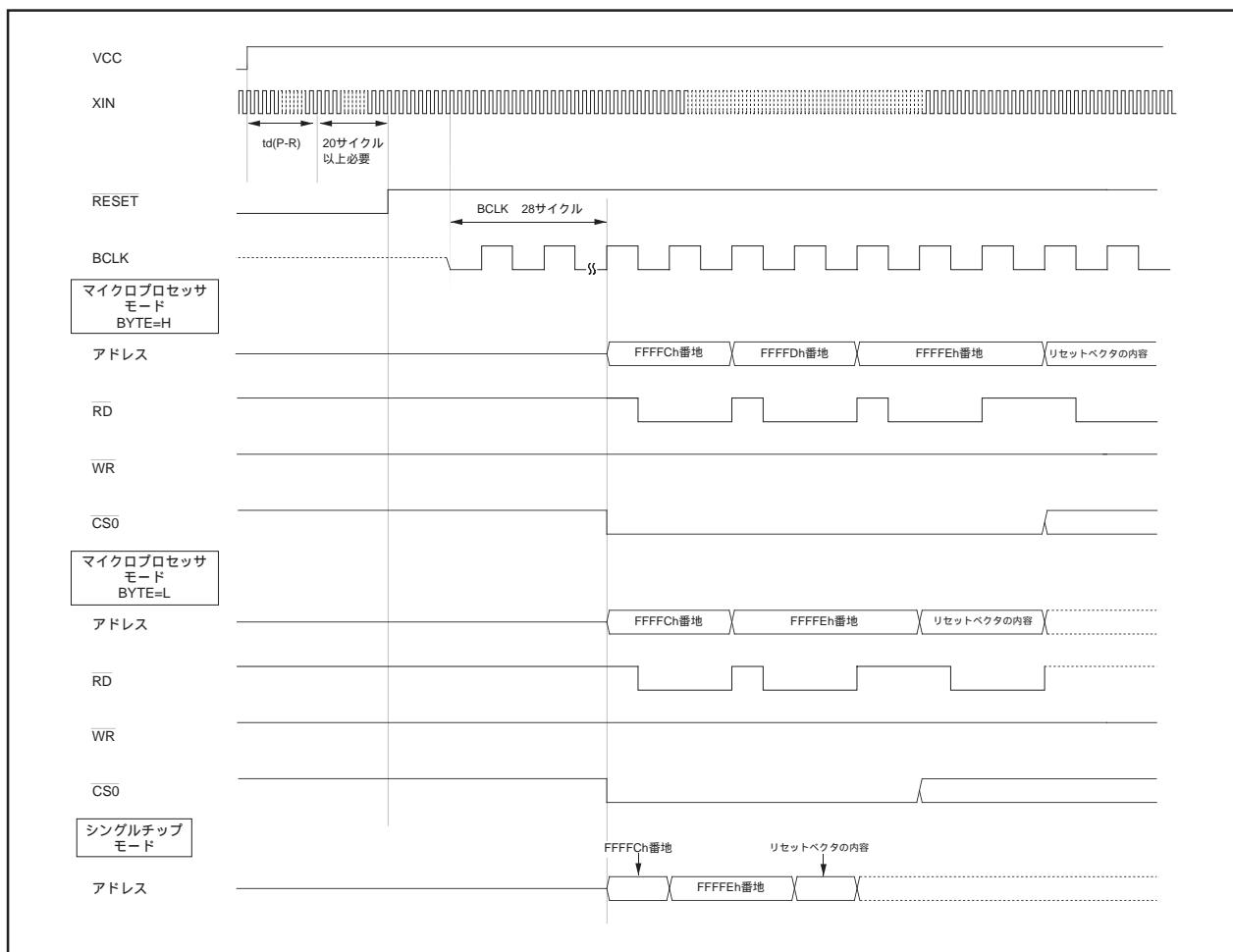

| 5.1 ハードウェアリセット .....                                | 27  |

| 5.1.1 電源安定時 .....                                   | 27  |

| 5.1.2 電源投入時 .....                                   | 27  |

| 5.2 ソフトウェアリセット .....                                | 29  |

| 5.3 ウオッチドッグタイマリセット .....                            | 29  |

| 5.4 発振停止検出リセット .....                                | 29  |

| 5.5 内部領域の状態 .....                                   | 29  |

| 6 . プロセッサモード .....                                  | 30  |

| 6.1 プロセッサモードの種類 .....                               | 30  |

| 6.2 プロセッサモードの設定 .....                               | 30  |

| 7 . バス .....                                        | 35  |

| 7.1 バス形式 .....                                      | 35  |

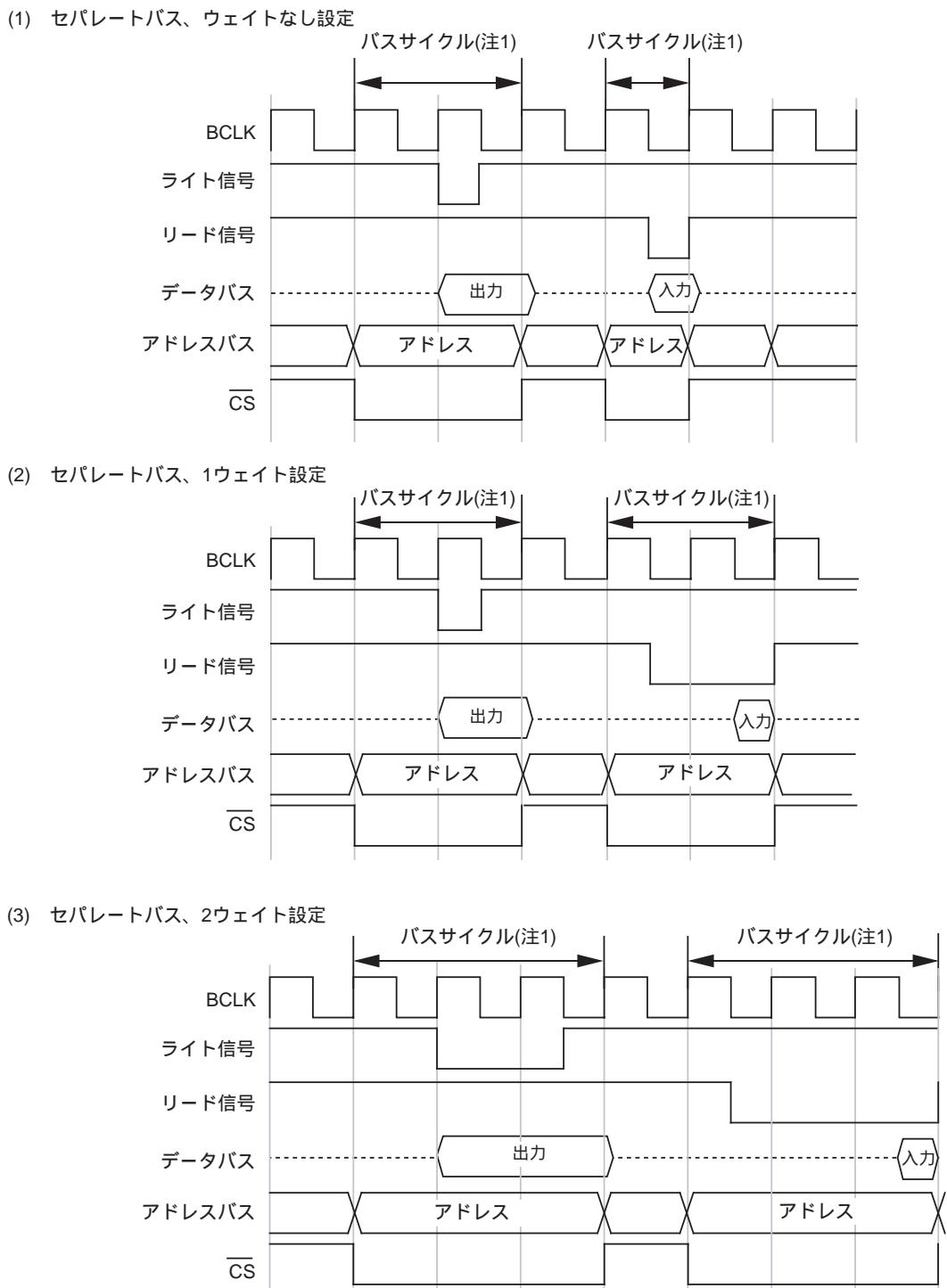

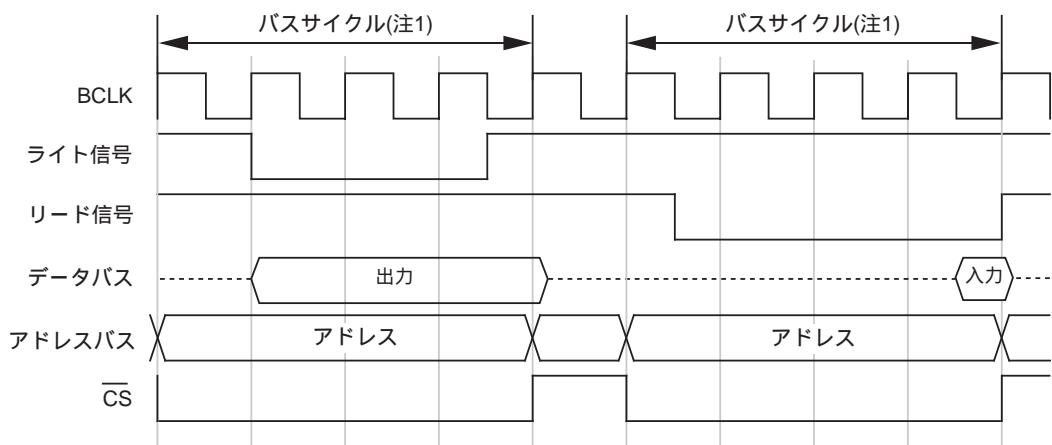

| 7.1.1 セパレートバス .....                                 | 35  |

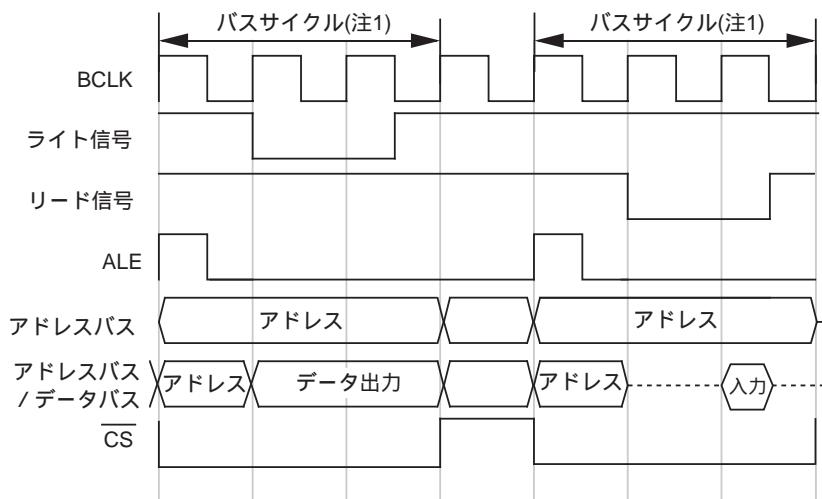

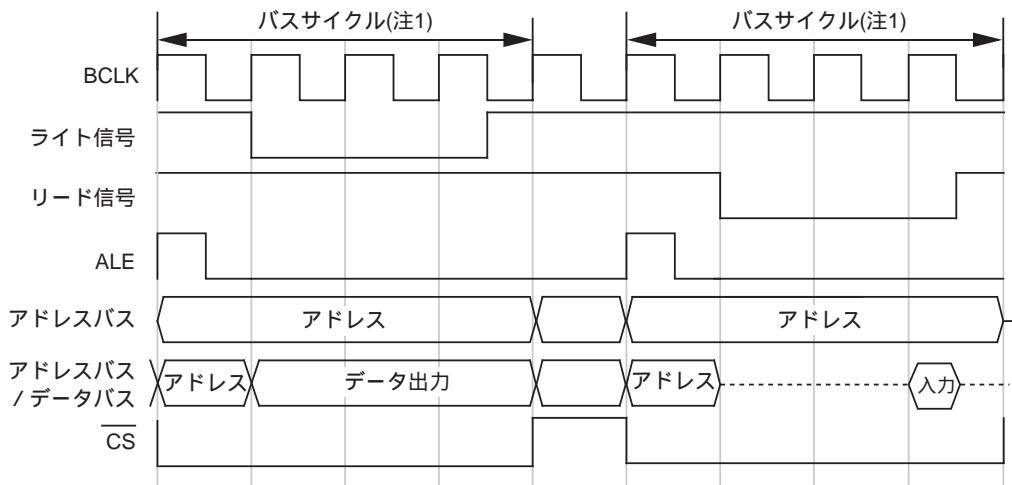

| 7.1.2 マルチプレクスバス .....                               | 35  |

|                                                |    |

|------------------------------------------------|----|

| 7.2 バス制御 .....                                 | 36 |

| 7.2.1 アドレスバス .....                             | 36 |

| 7.2.2 データバス .....                              | 36 |

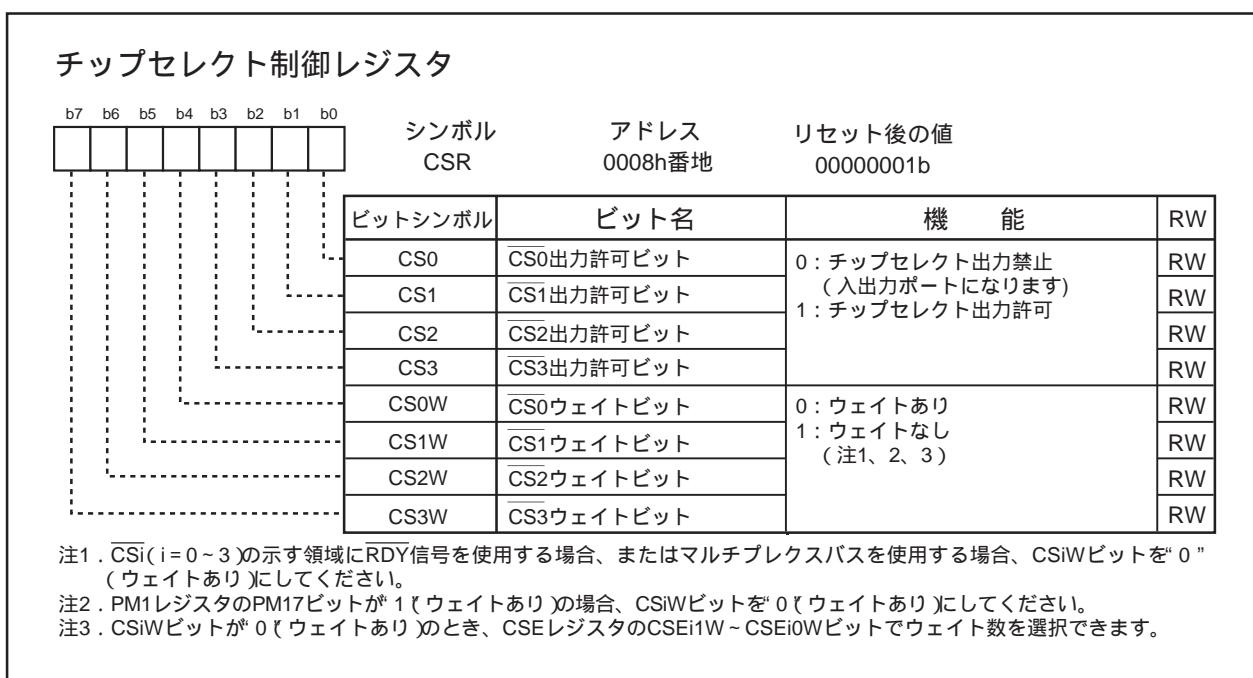

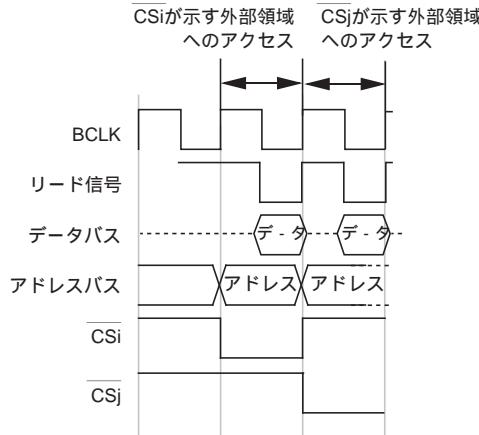

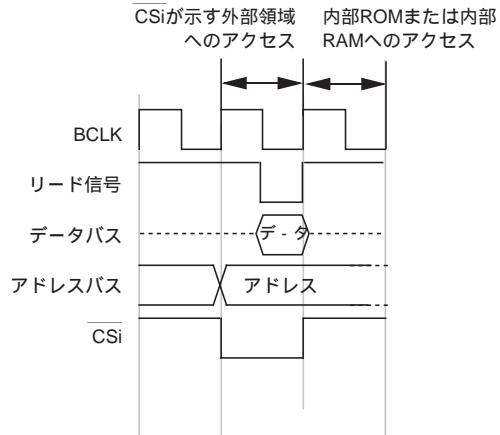

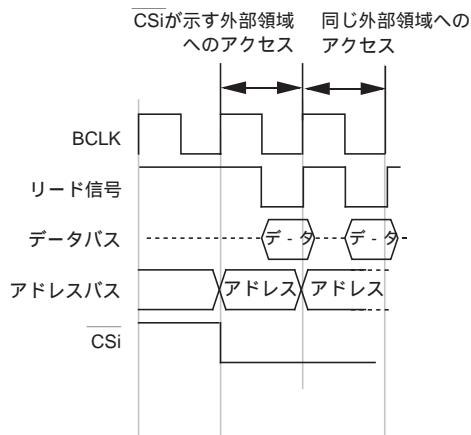

| 7.2.3 チップセレクト信号 .....                          | 36 |

| 7.2.4 リード信号、ライト信号 .....                        | 38 |

| 7.2.5 ALE信号 .....                              | 38 |

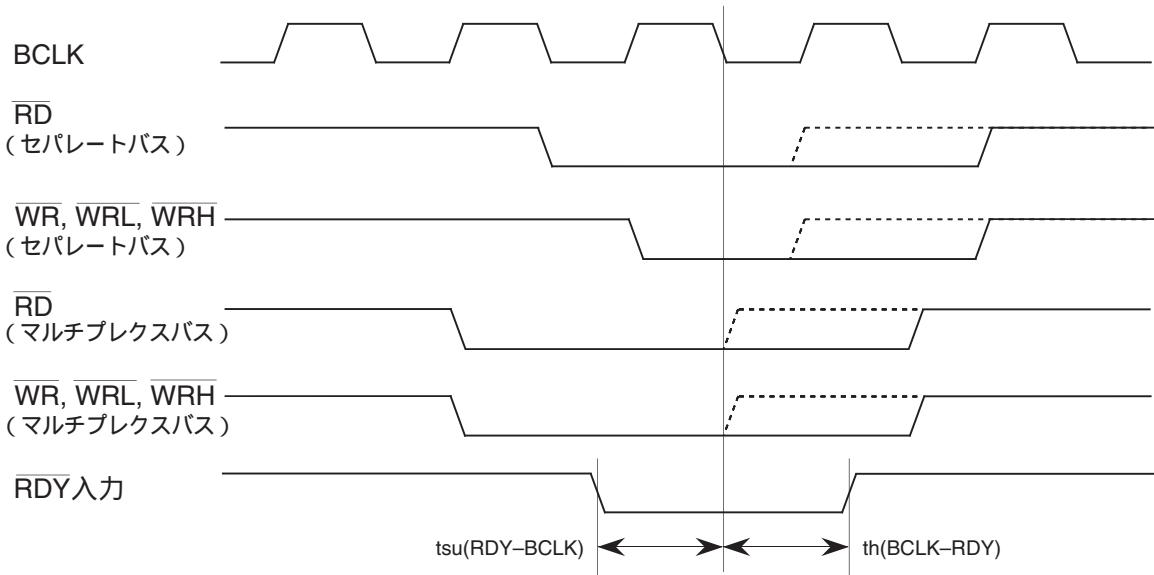

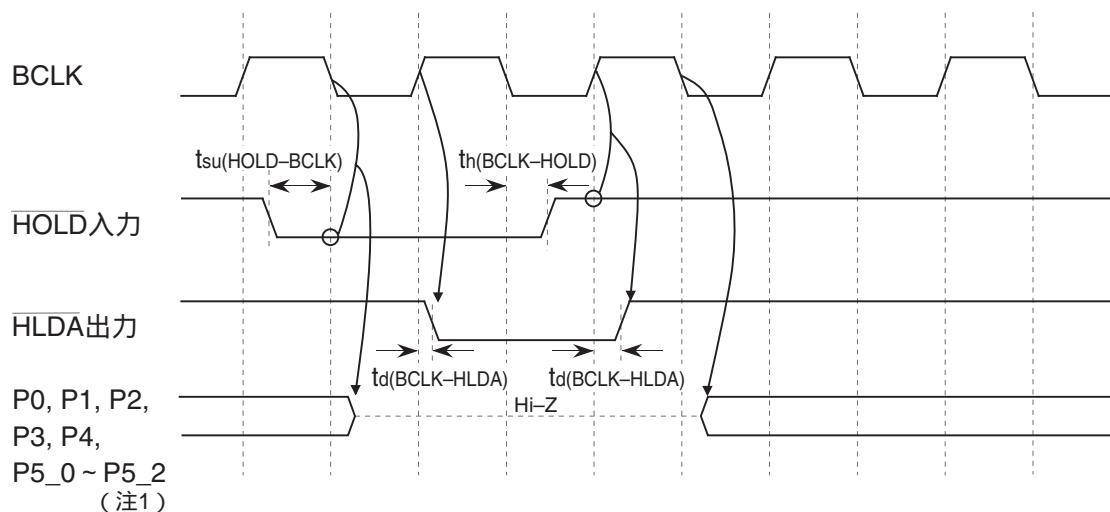

| 7.2.6 RDY信号 .....                              | 39 |

| 7.2.7 HOLD信号 .....                             | 40 |

| 7.2.8 BCLK出力 .....                             | 40 |

| 7.2.9 内部領域をアクセスしたときの外部バスの状態 .....              | 42 |

| 7.2.10 ソフトウェアウェイト .....                        | 42 |

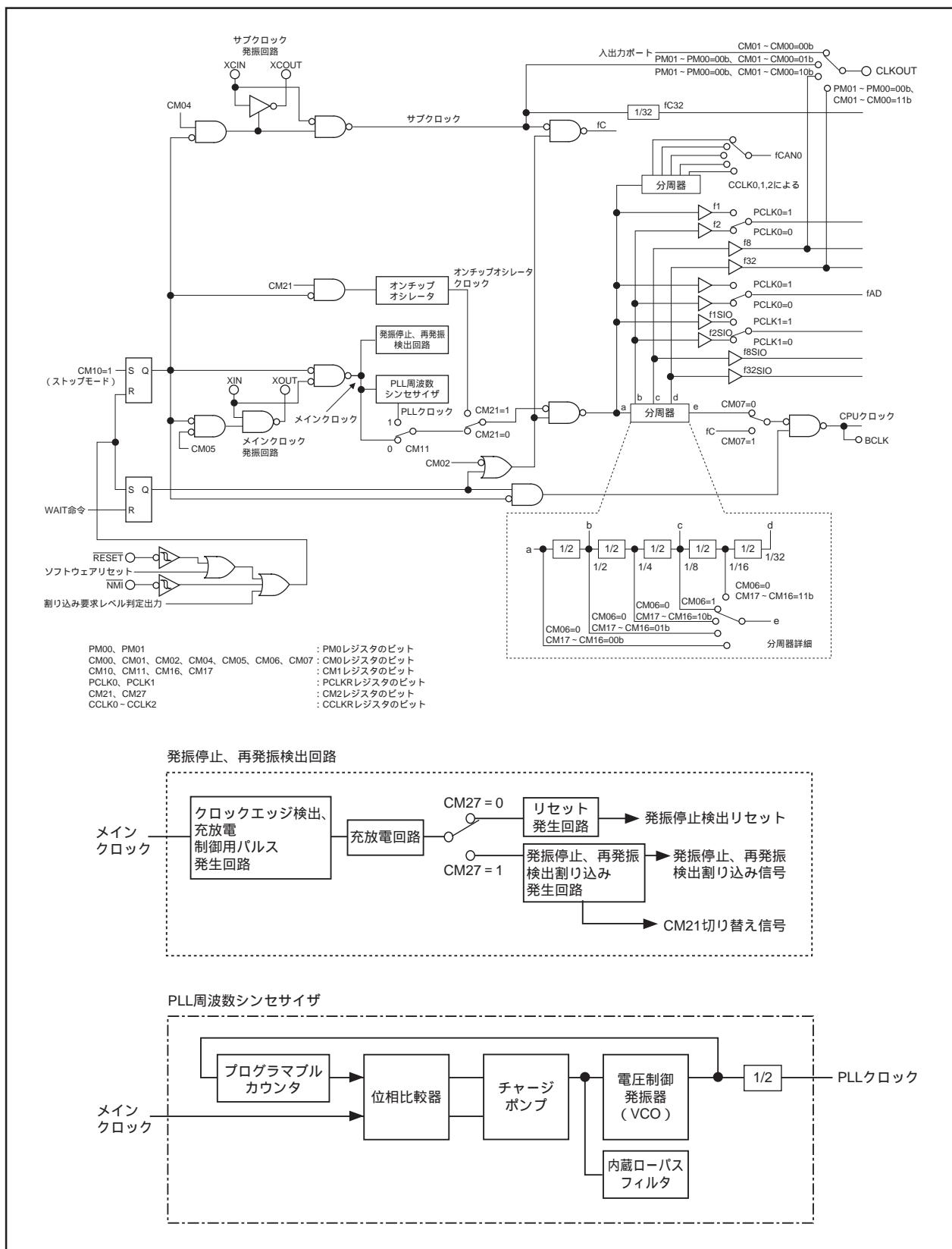

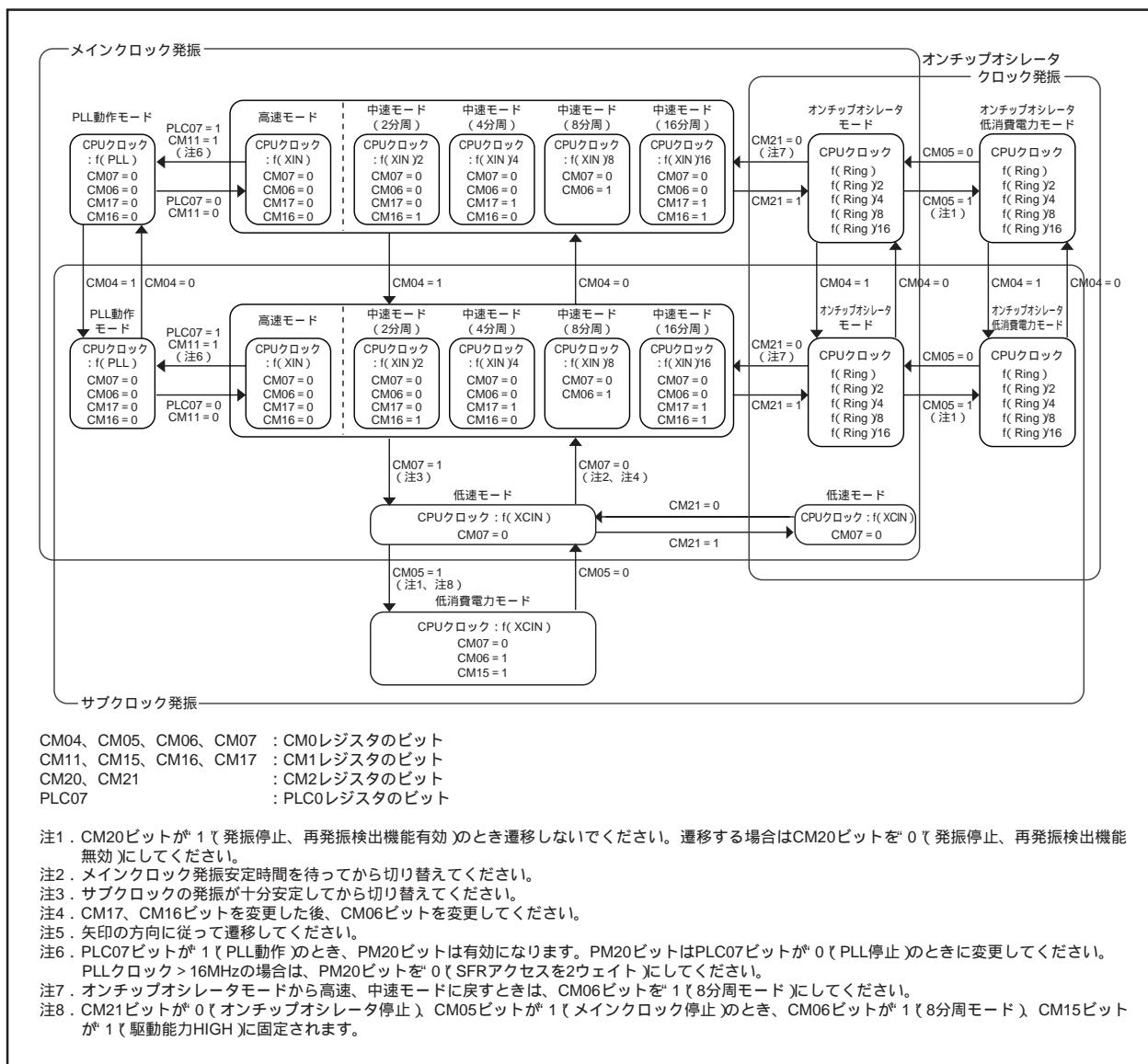

| 8 . クロック発生回路 .....                             | 46 |

| 8.1 クロック発生回路の種類 .....                          | 46 |

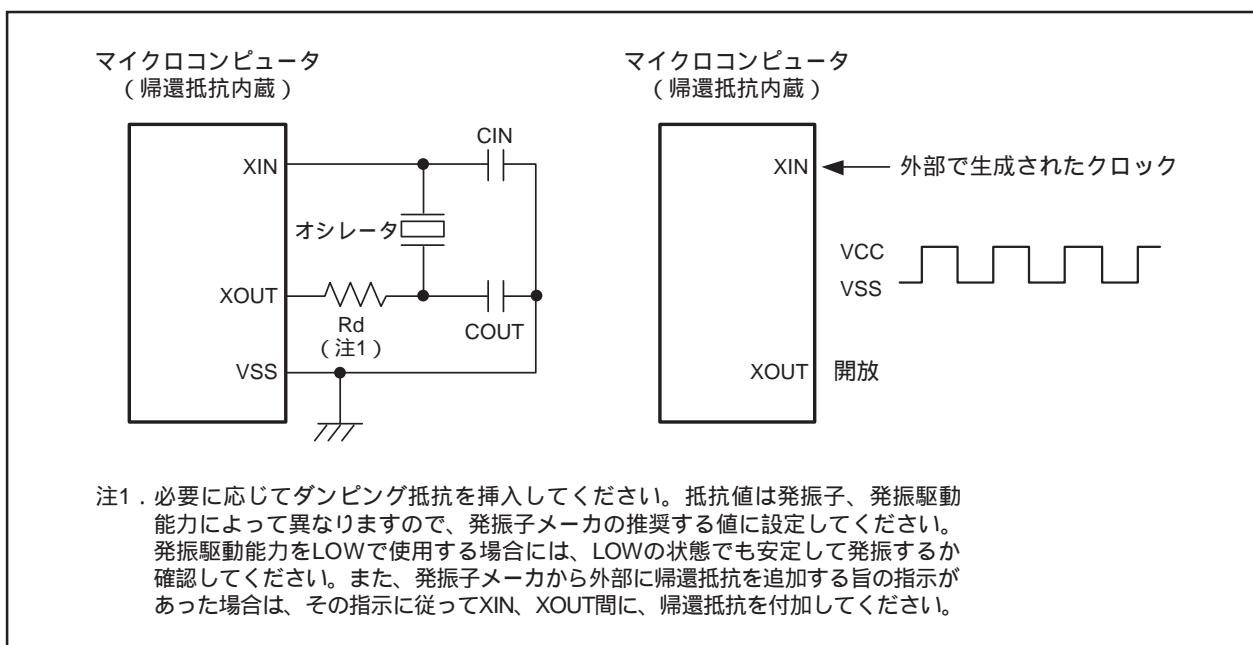

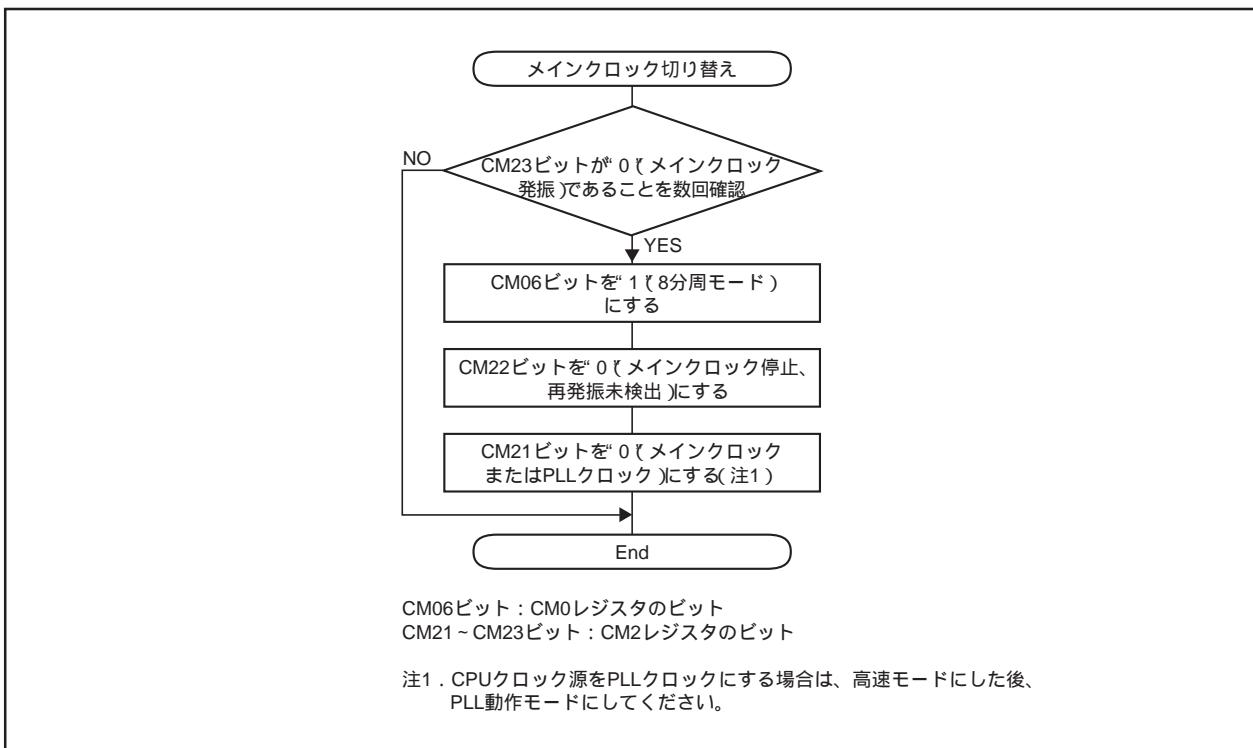

| 8.1.1 メインクロック .....                            | 53 |

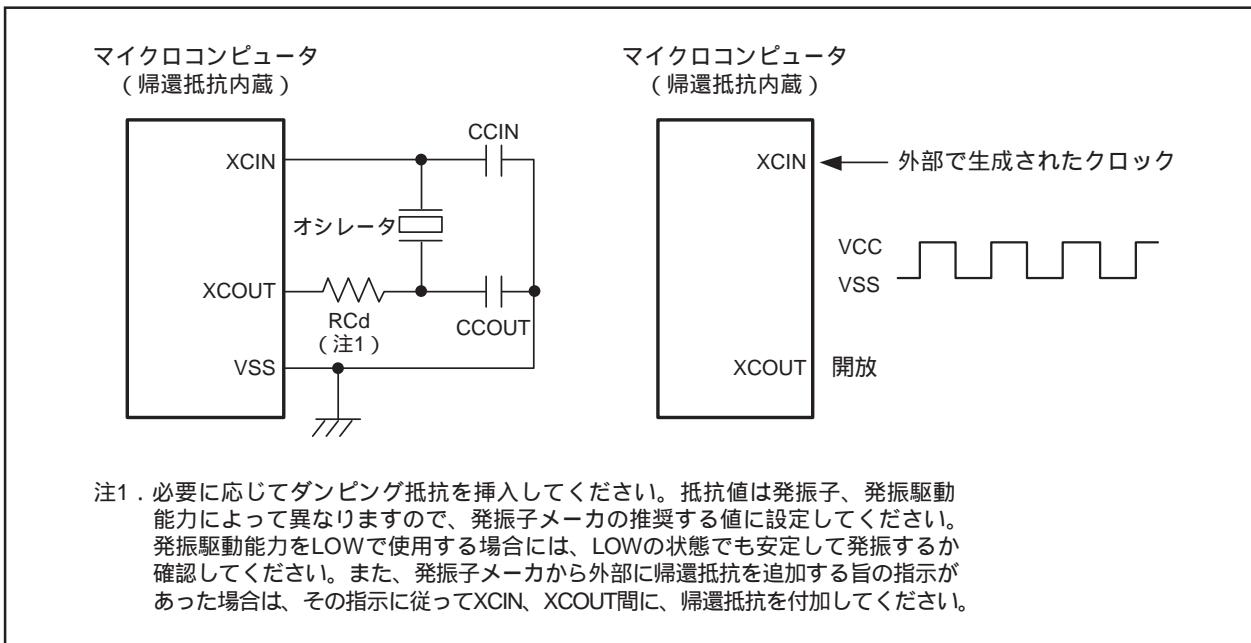

| 8.1.2 サブクロック .....                             | 54 |

| 8.1.3 オンチップオシレータクロック .....                     | 55 |

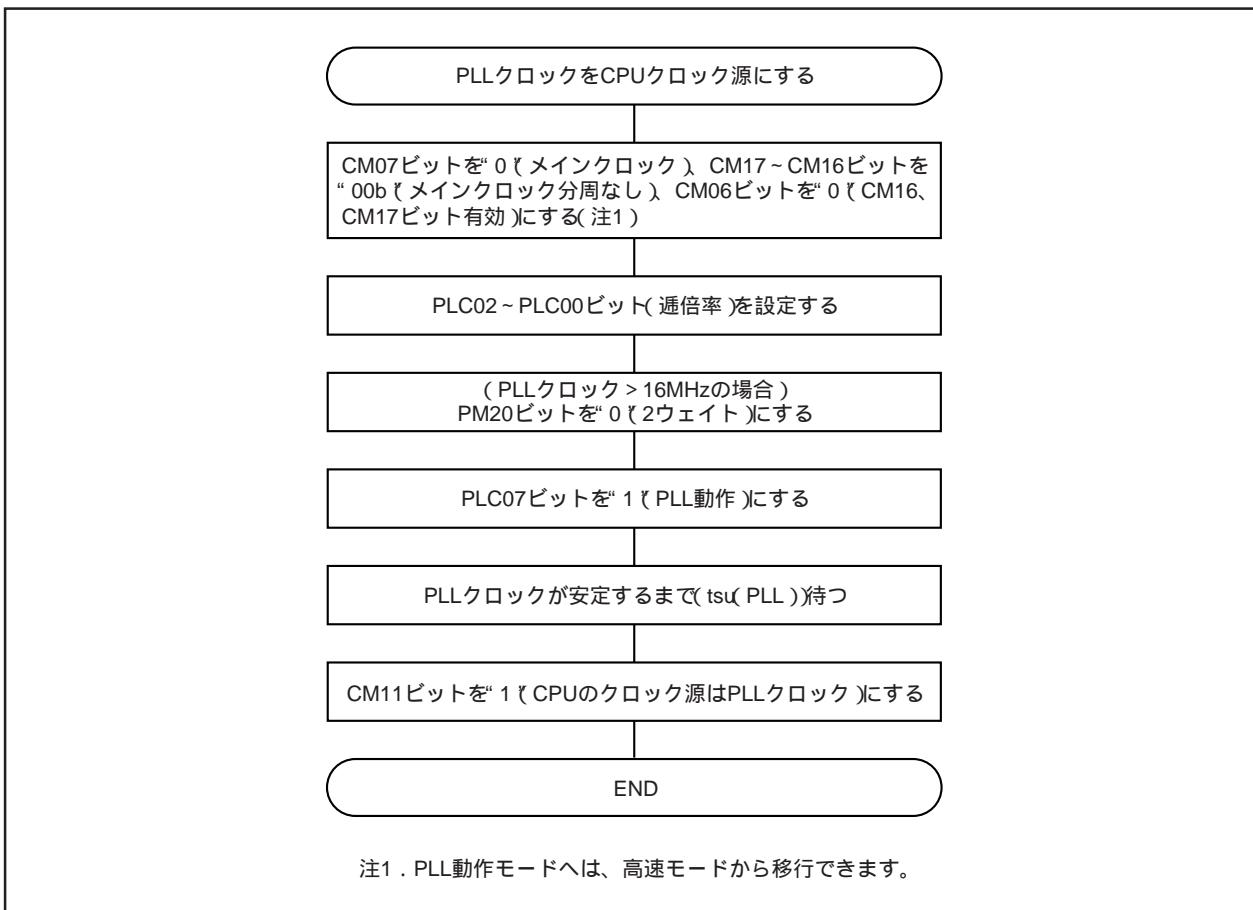

| 8.1.4 PLLクロック .....                            | 55 |

| 8.2 CPUクロックと周辺機能クロック .....                     | 57 |

| 8.2.1 CPUクロックとBCLK .....                       | 57 |

| 8.2.2 周辺機能クロック .....                           | 57 |

| 8.3 クロック出力機能 .....                             | 57 |

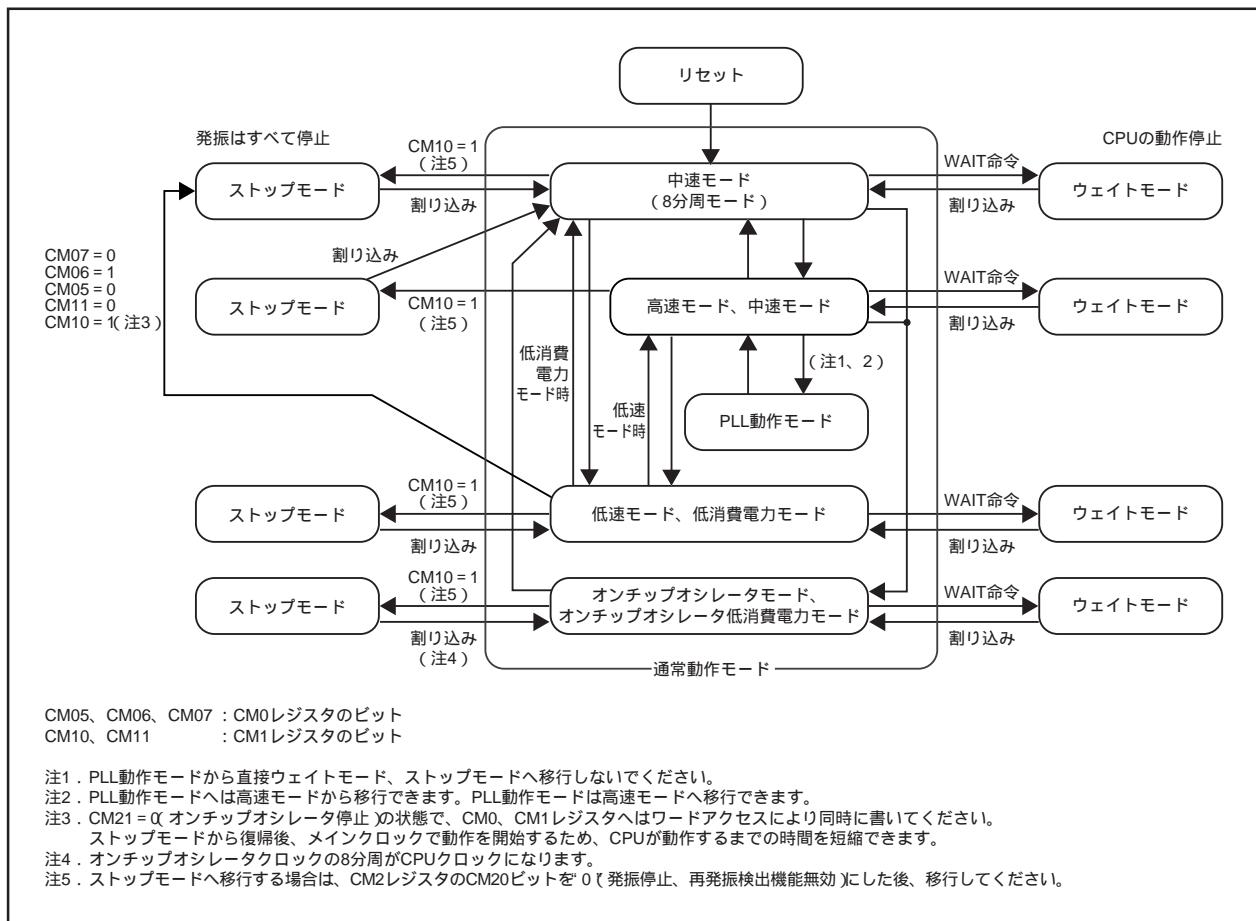

| 8.4 パワーコントロール .....                            | 58 |

| 8.4.1 通常動作モード .....                            | 58 |

| 8.4.2 ウエイトモード .....                            | 60 |

| 8.4.3 ストップモード .....                            | 62 |

| 8.5 発振停止、再発振検出機能 .....                         | 67 |

| 8.5.1 CM27ビットが 0 (リセット) の場合の動作 .....           | 67 |

| 8.5.2 CM27ビットが 1 (発振停止、再発振検出割り込み) の場合の動作 ..... | 67 |

| 8.5.3 発振停止、再発振検出機能使用方法 .....                   | 68 |

| 9 . プロテクト .....                                | 69 |

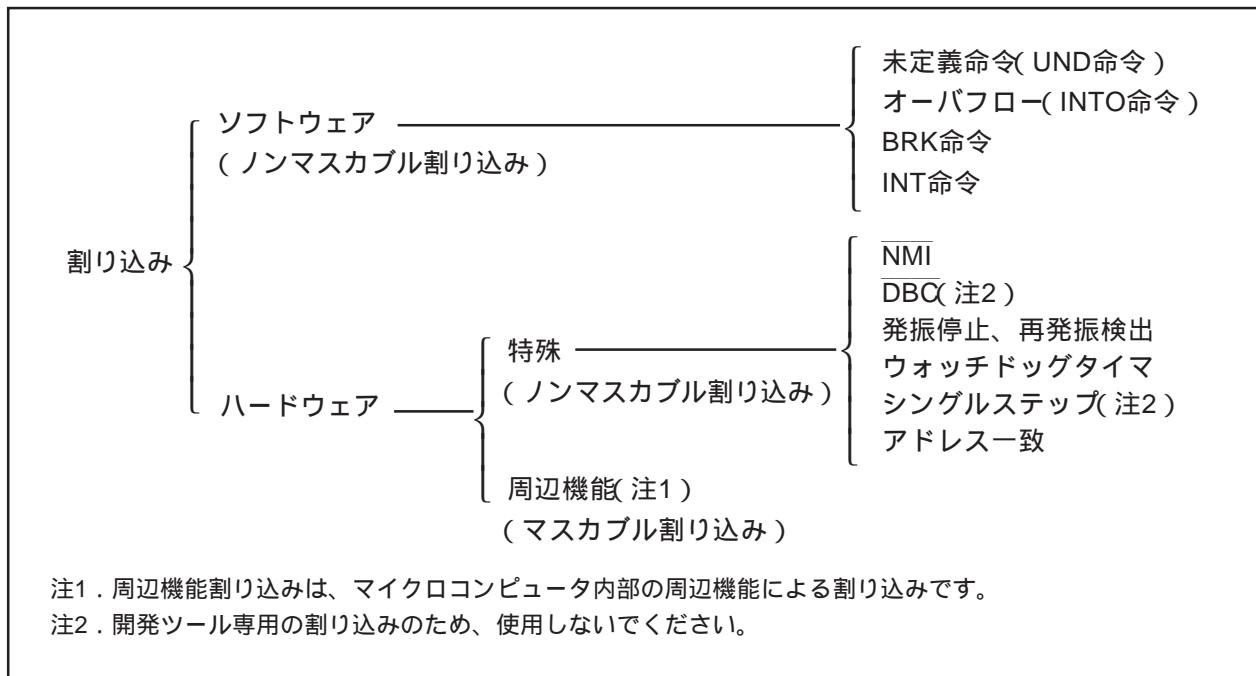

| 10 . 割り込み .....                                | 70 |

| 10.1 割り込みの分類 .....                             | 70 |

| 10.2 ソフトウェア割り込み .....                          | 71 |

| 10.2.1 未定義命令割り込み .....                         | 71 |

| 10.2.2 オーバフロー割り込み .....                        | 71 |

| 10.2.3 BRK割り込み .....                           | 71 |

| 10.2.4 INT命令割り込み .....                         | 71 |

| 10.3 ハードウェア割り込み .....                          | 72 |

| 10.3.1 特殊割り込み .....                            | 72 |

| 10.3.2 周辺機能割り込み .....                          | 72 |

| 10.4 割り込みと割り込みベクタ .....                        | 73 |

| 10.4.1 固定ベクタテーブル .....                         | 73 |

| 10.4.2 可変ベクタテーブル .....                         | 74 |

| 10.5 割り込み制御 .....                              | 75 |

| 10.5.1 Iフラグ .....                              | 77 |

| 10.5.2 IRビット .....                             | 77 |

| 10.5.3 ILVL2～ILVL0ビット、IPL .....                | 77 |

|         |                                     |     |

|---------|-------------------------------------|-----|

| 10.5.4  | 割り込みシーケンス .....                     | 78  |

| 10.5.5  | 割り込み応答時間 .....                      | 79  |

| 10.5.6  | 割り込み要求受付時のIPLの変化 .....              | 79  |

| 10.5.7  | レジスタ退避 .....                        | 80  |

| 10.5.8  | 割り込みルーチンからの復帰 .....                 | 81  |

| 10.5.9  | 割り込み優先順位 .....                      | 81  |

| 10.5.10 | 割り込み優先レベル判定回路 .....                 | 81  |

| 10.6    | INT割り込み .....                       | 83  |

| 10.7    | NMI割り込み .....                       | 85  |

| 10.8    | キー入力割り込み .....                      | 85  |

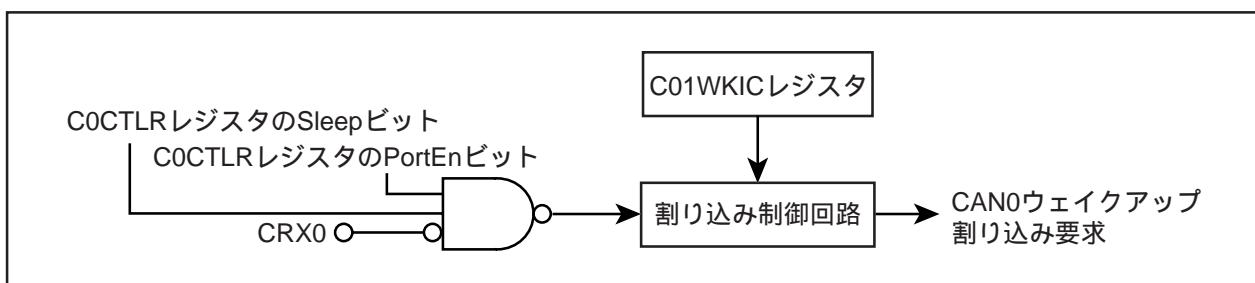

| 10.9    | CAN0ウェイクアップ割り込み .....               | 85  |

| 10.10   | アドレス一致割り込み .....                    | 86  |

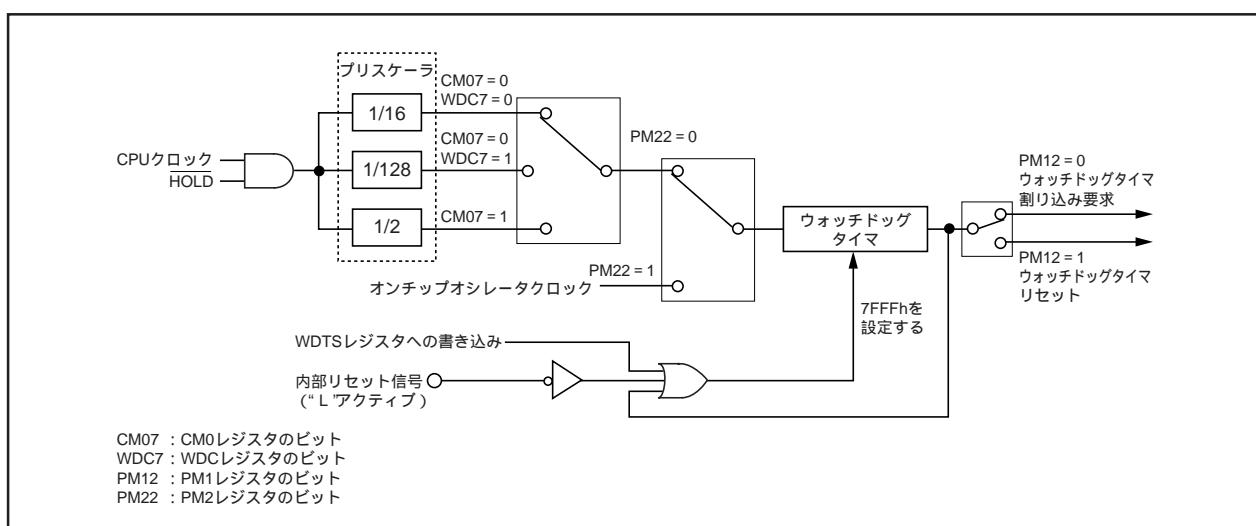

| 11 .    | ウォッチドッグタイマ .....                    | 88  |

| 11.1    | カウントソース保護モード .....                  | 89  |

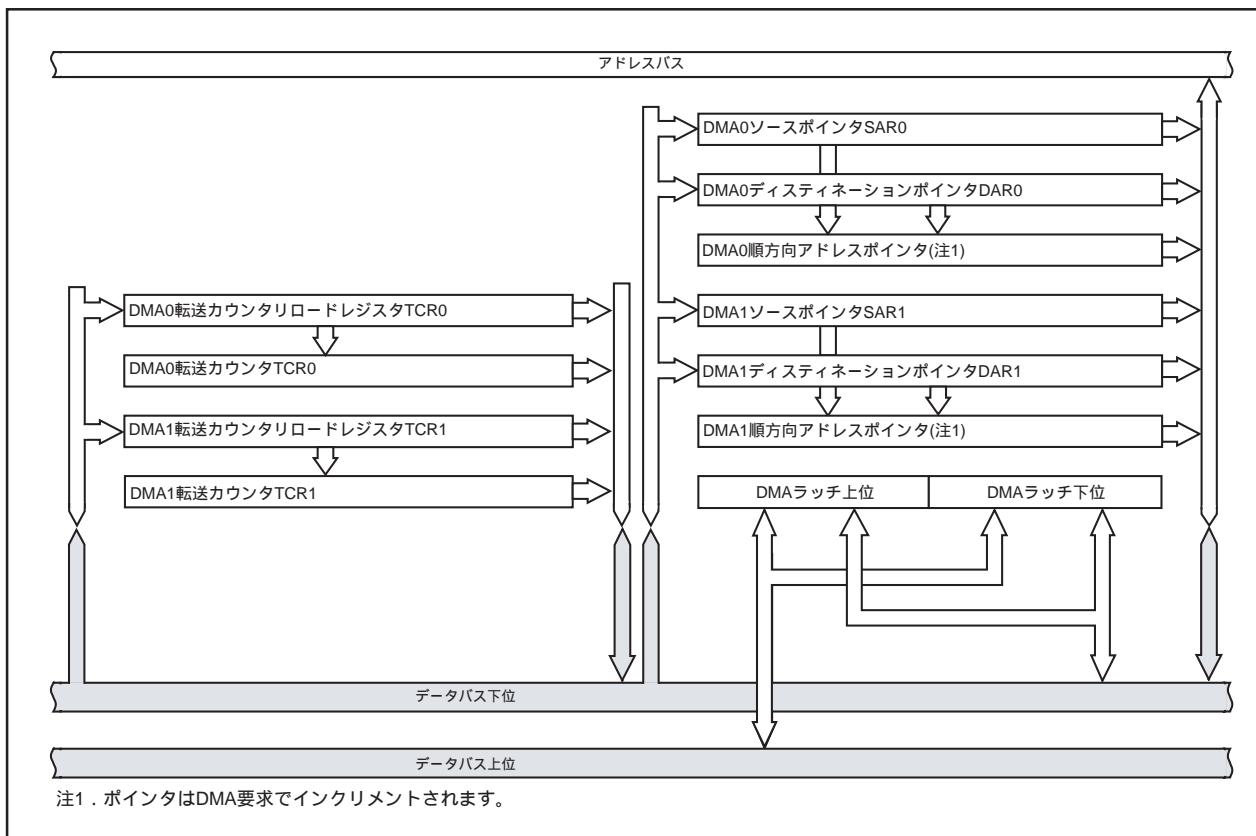

| 12 .    | DMAC .....                          | 90  |

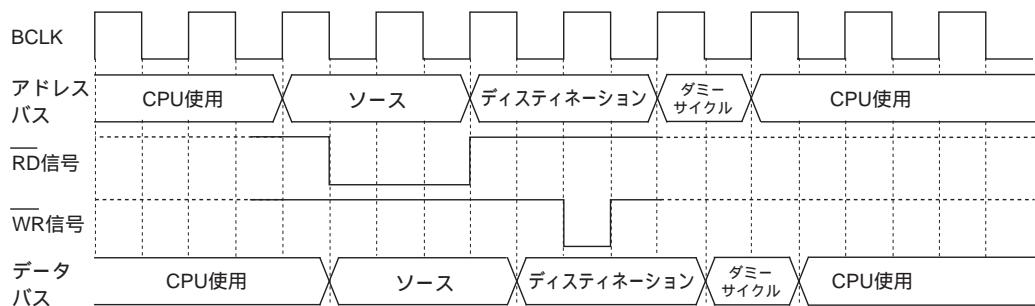

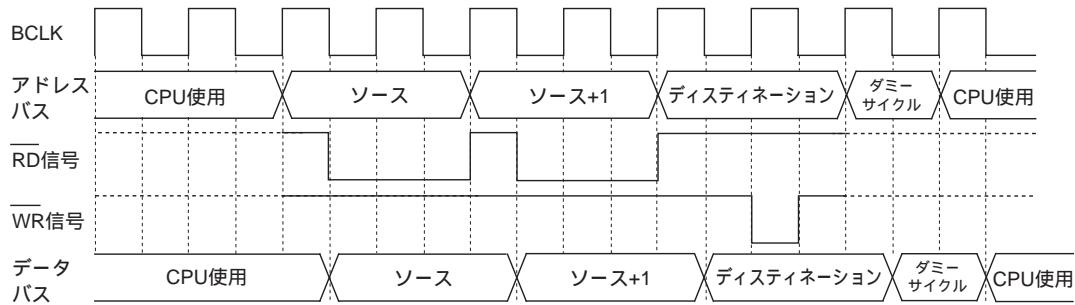

| 12.1    | 転送サイクル .....                        | 95  |

| 12.1.1  | 転送元番地、転送先番地の影響 .....                | 95  |

| 12.1.2  | BYTE端子の影響 .....                     | 95  |

| 12.1.3  | ソフトウェアウェイトの影響 .....                 | 95  |

| 12.1.4  | RDY信号の影響 .....                      | 95  |

| 12.2    | DMACの転送サイクル数 .....                  | 97  |

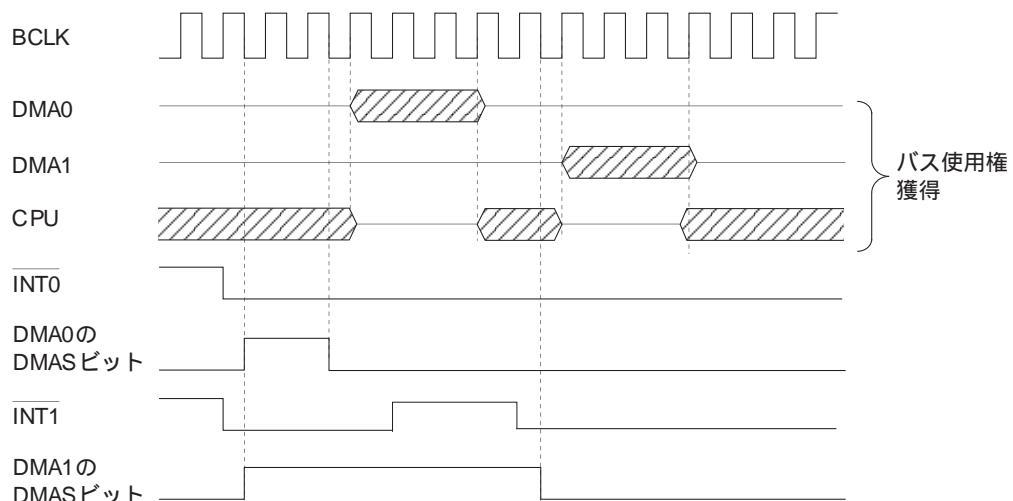

| 12.3    | DMA許可 .....                         | 98  |

| 12.4    | DMA要求 .....                         | 98  |

| 12.5    | チャネルの優先順位とDMA転送タイミング .....          | 99  |

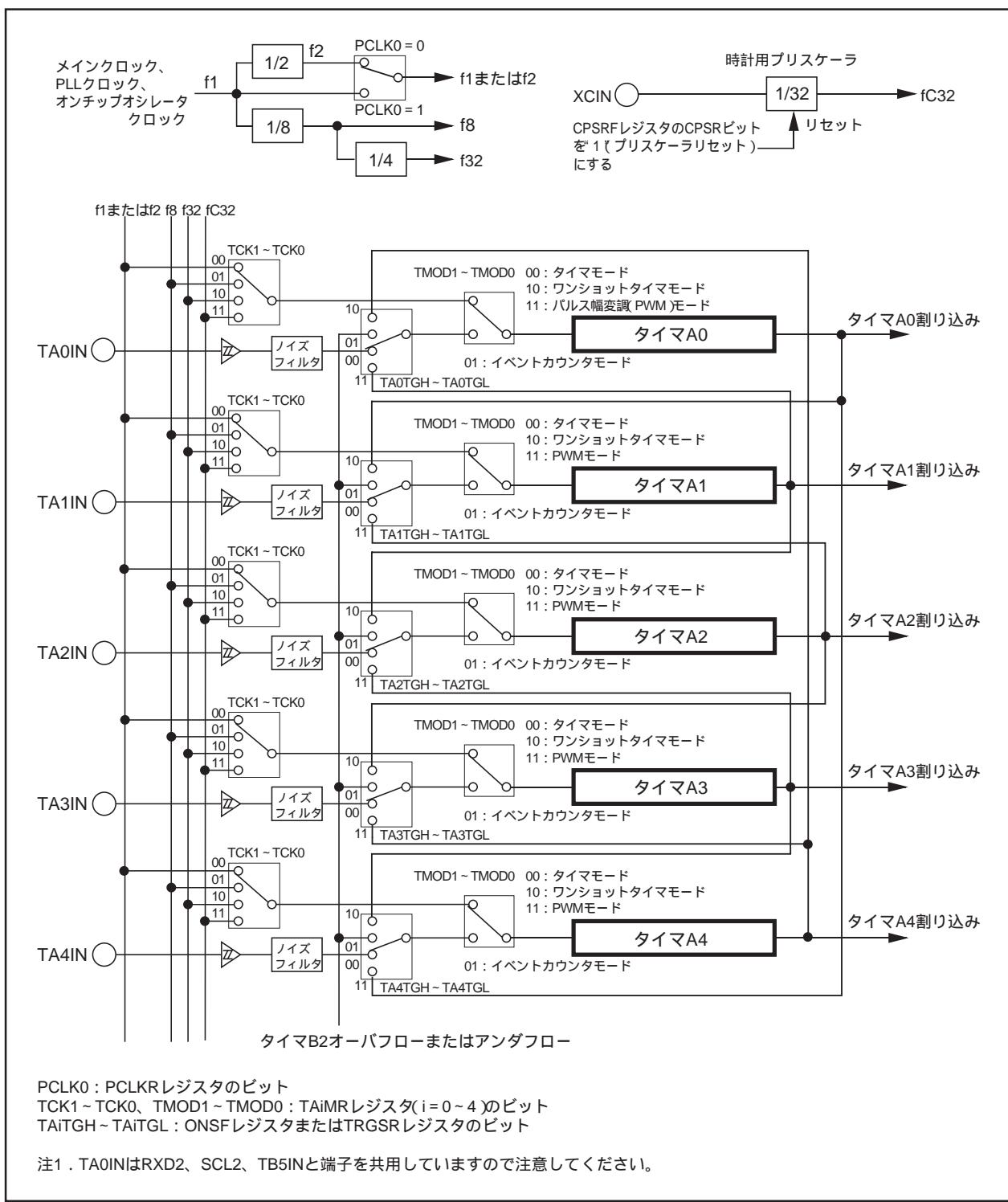

| 13 .    | タイマ .....                           | 100 |

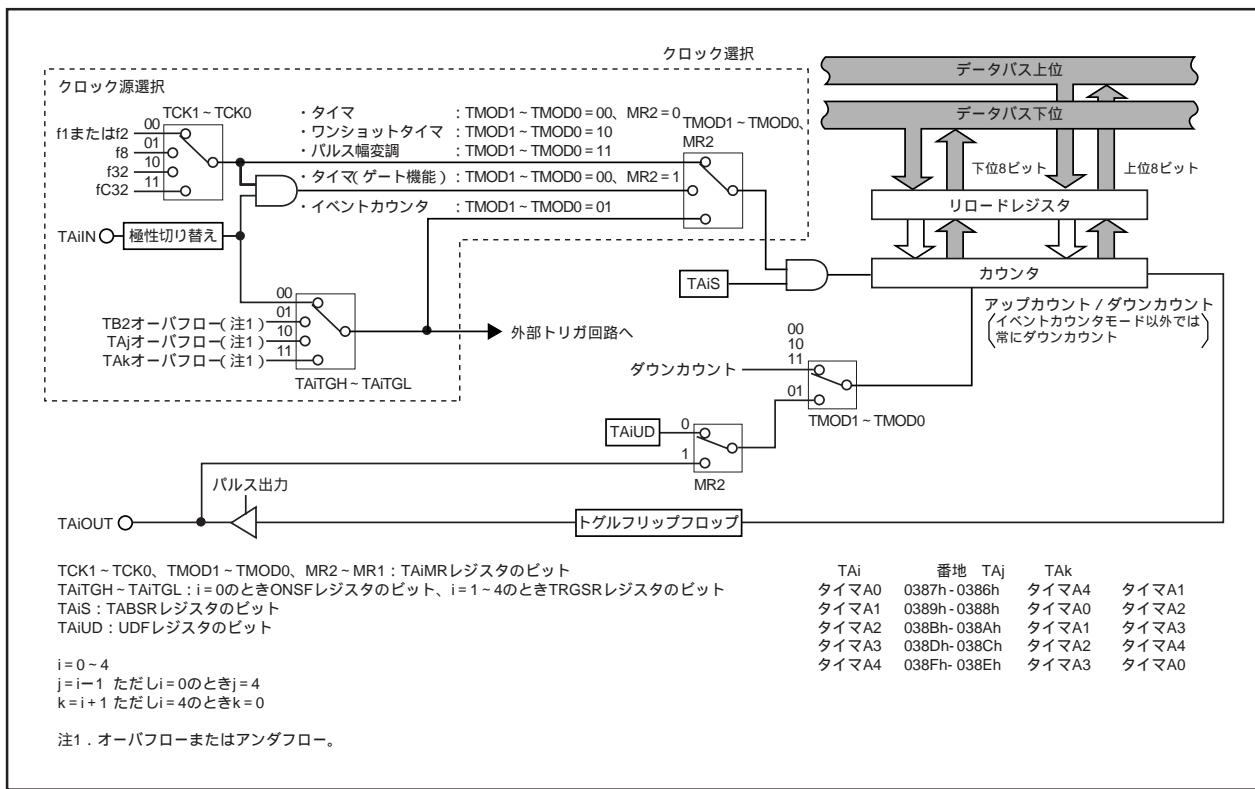

| 13.1    | タイマA .....                          | 102 |

| 13.1.1  | タイマモード .....                        | 106 |

| 13.1.2  | イベントカウンタモード .....                   | 107 |

| 13.1.3  | ワンショットタイマモード .....                  | 112 |

| 13.1.4  | パルス幅変調モード( PWMモード ) .....           | 114 |

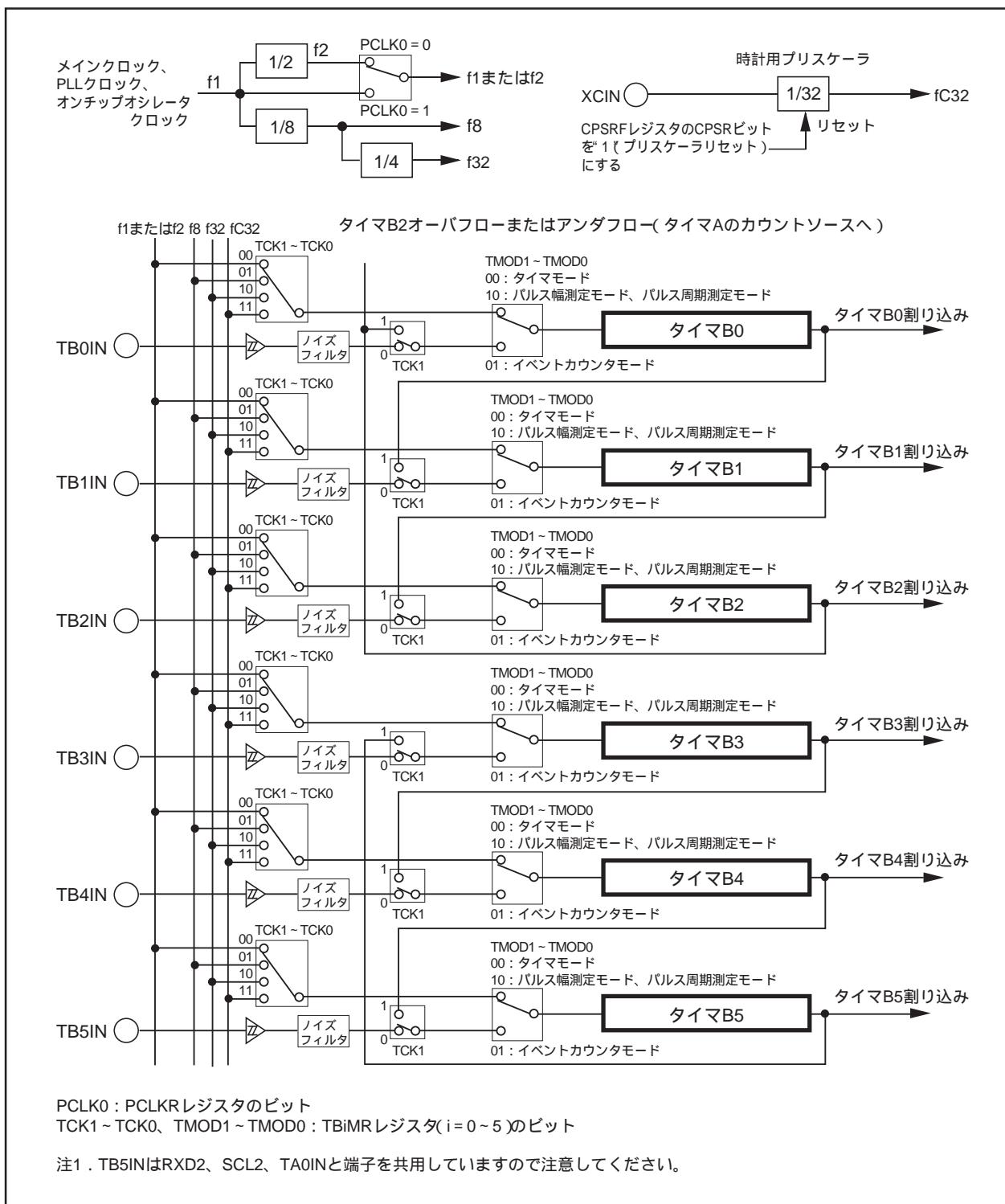

| 13.2    | タイマB .....                          | 117 |

| 13.2.1  | タイマモード .....                        | 120 |

| 13.2.2  | イベントカウンタモード .....                   | 121 |

| 13.2.3  | パルス周期測定、パルス幅測定モード .....             | 122 |

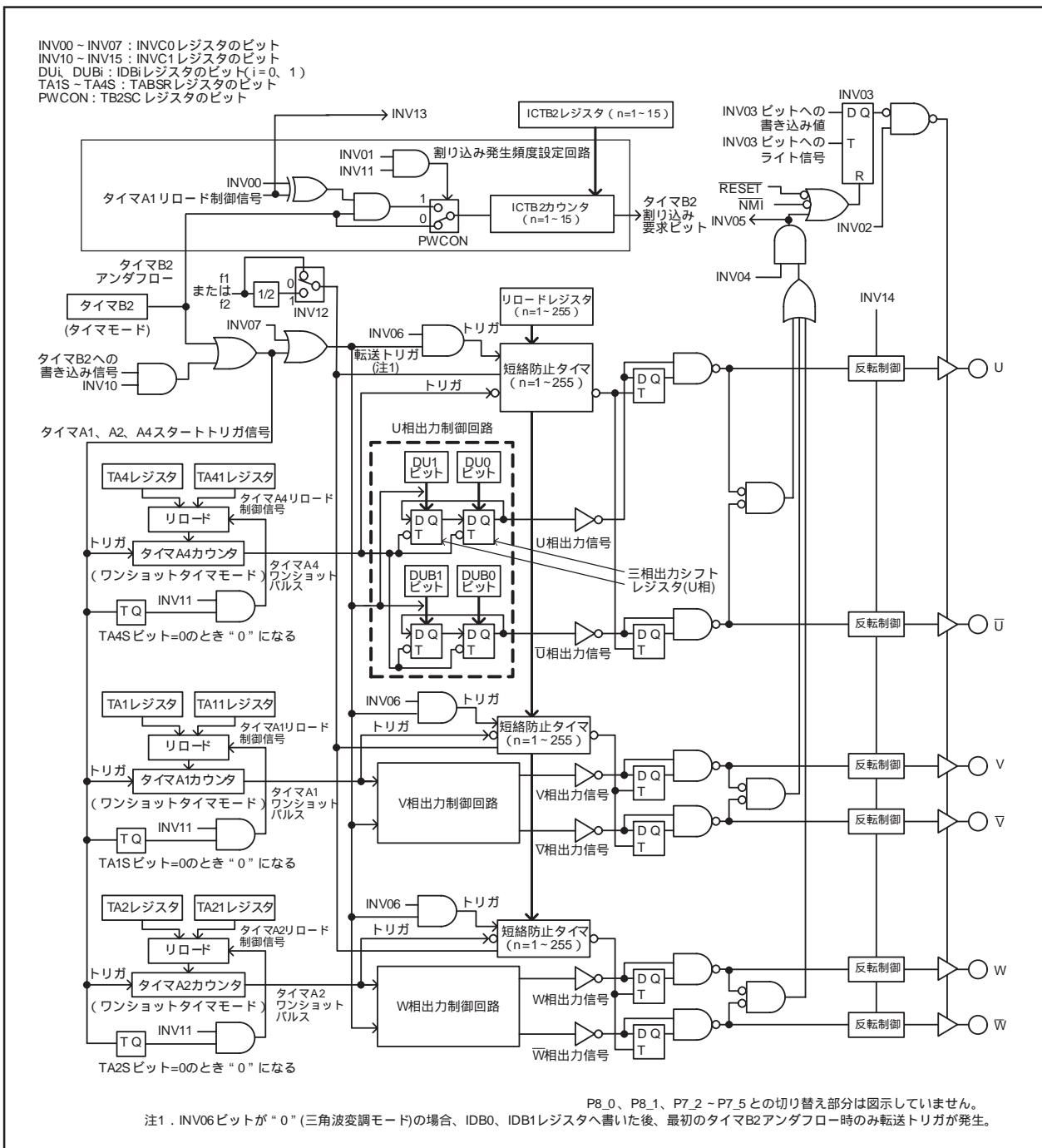

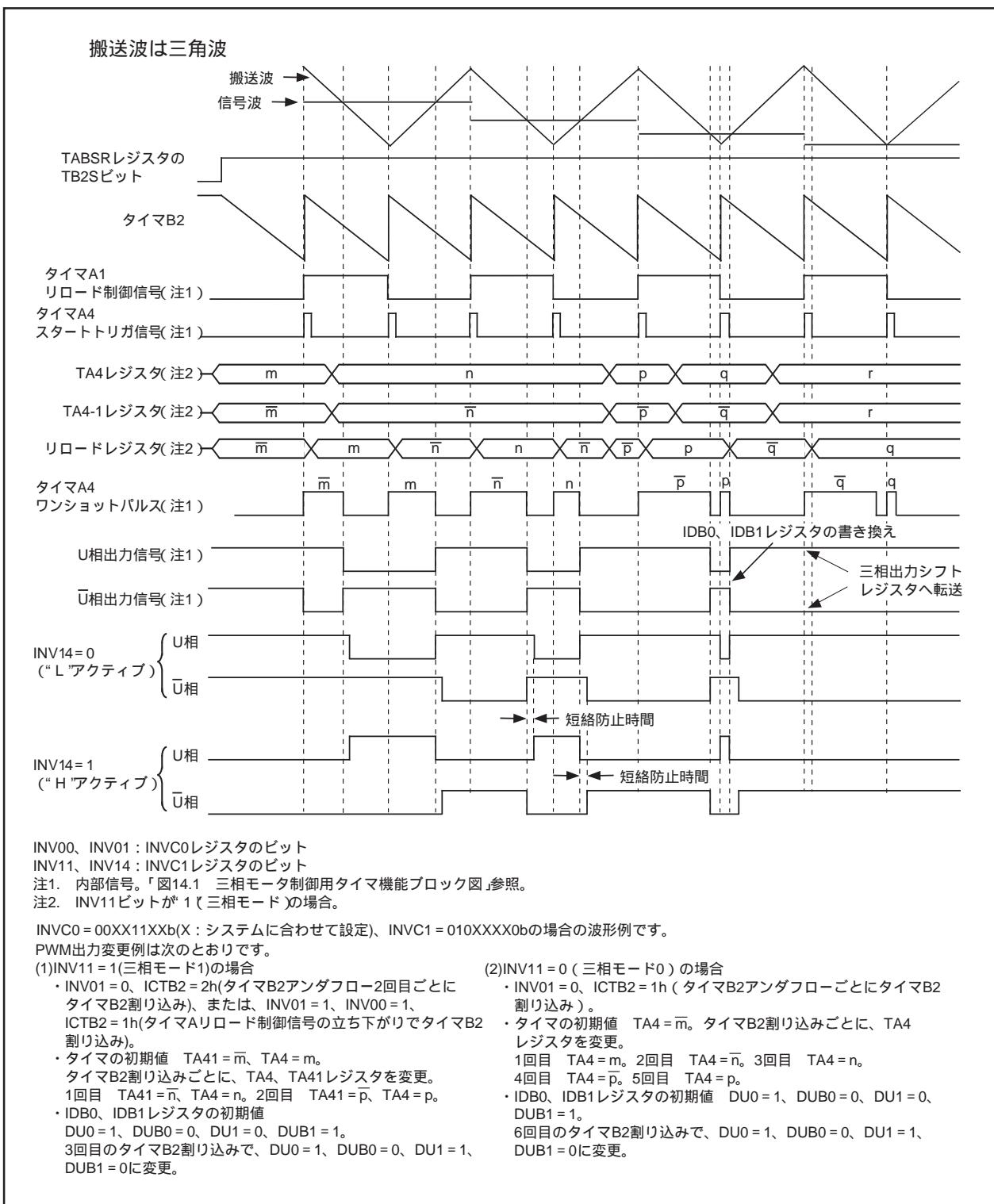

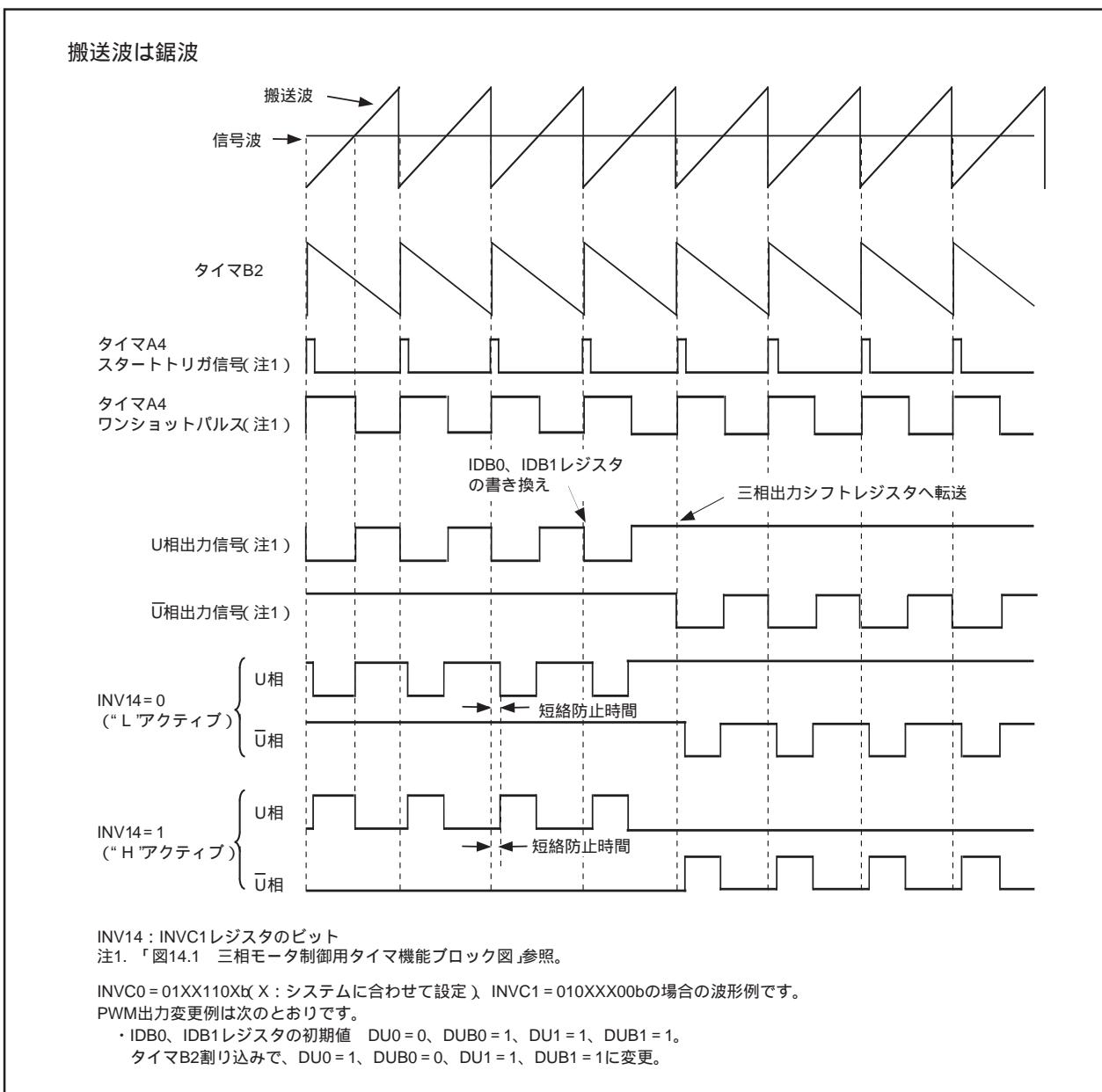

| 14 .    | 三相モータ制御用タイマ機能 .....                 | 125 |

| 15 .    | シリアルインターフェース .....                  | 136 |

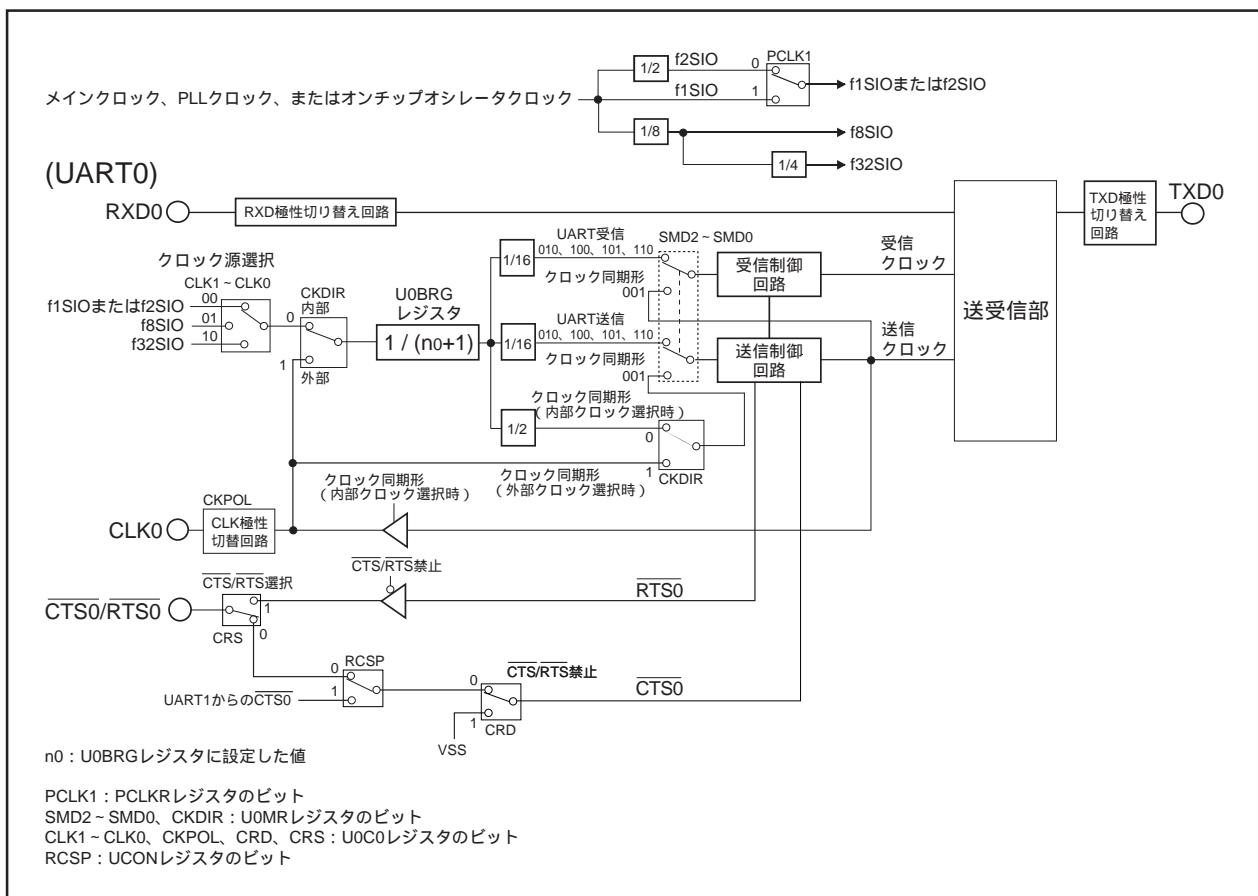

| 15.1    | UART <sub>i</sub> .....             | 136 |

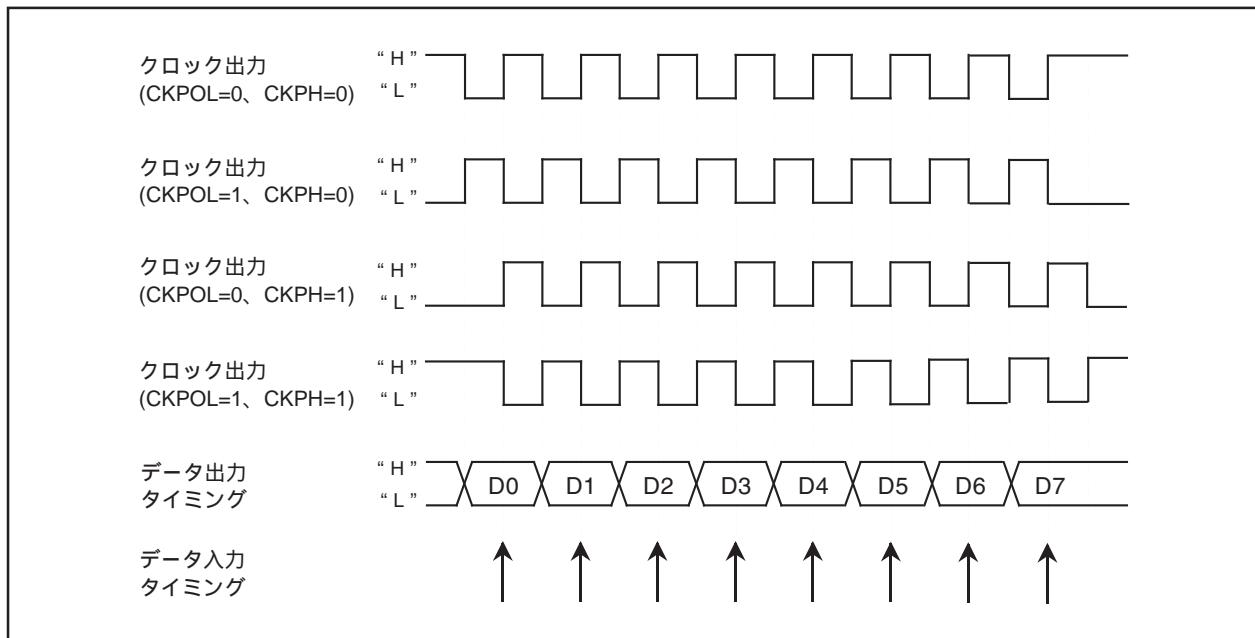

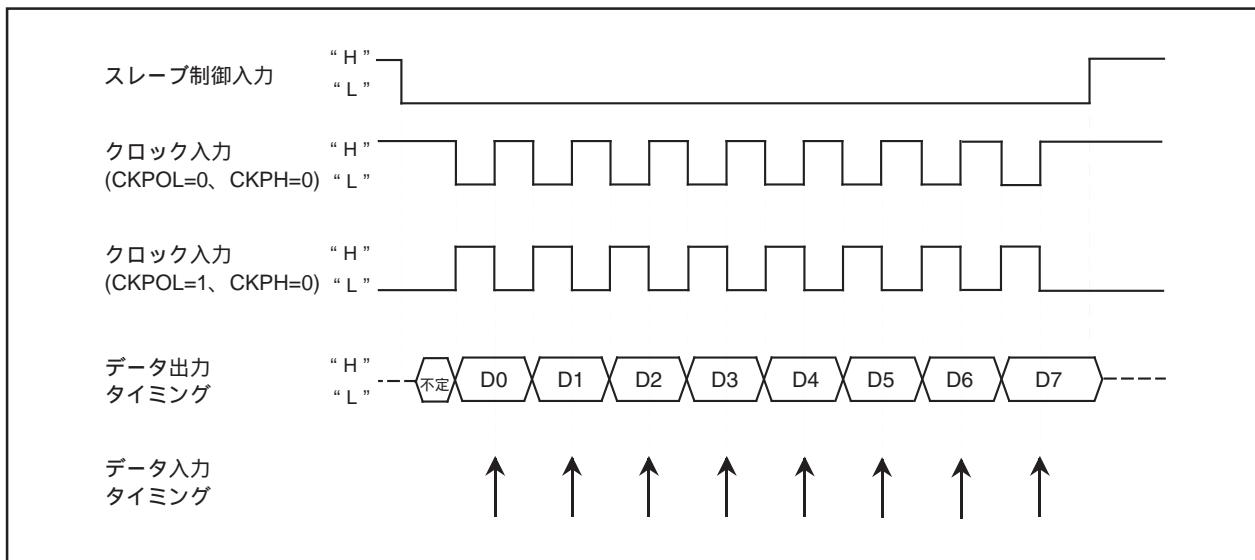

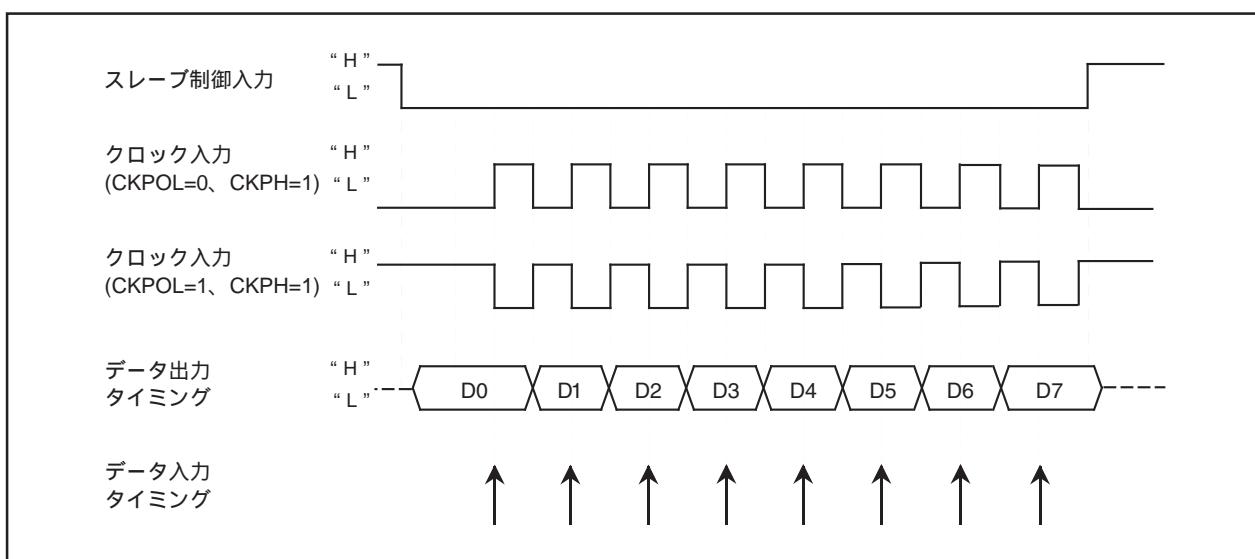

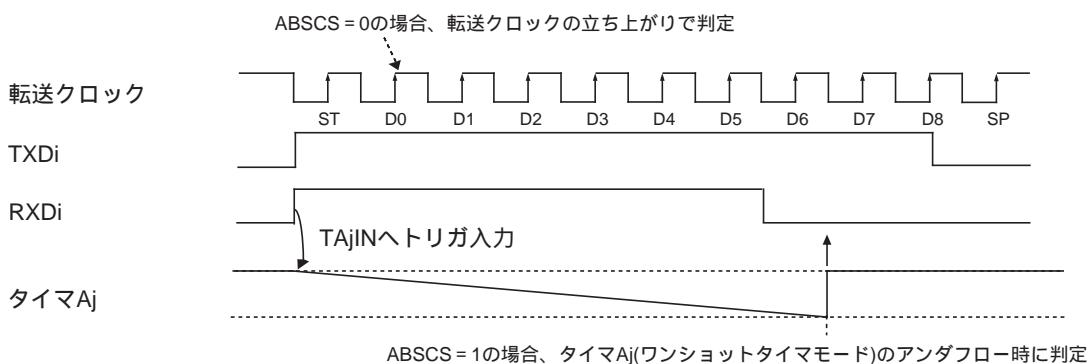

| 15.1.1  | クロック同期形シリアルI/Oモード .....             | 146 |

| 15.1.2  | クロック非同期形シリアルI/O( UART )モード .....    | 154 |

| 15.1.3  | 特殊モード1( I <sup>2</sup> Cモード ) ..... | 162 |

| 15.1.4  | 特殊モード2 .....                        | 171 |

| 15.1.5  | 特殊モード3( IEモード ) .....               | 176 |

| 15.1.6  | 特殊モード4( SIMモード )( UART2 ) .....     | 178 |

| 15.2    | SI/O3 .....                         | 183 |

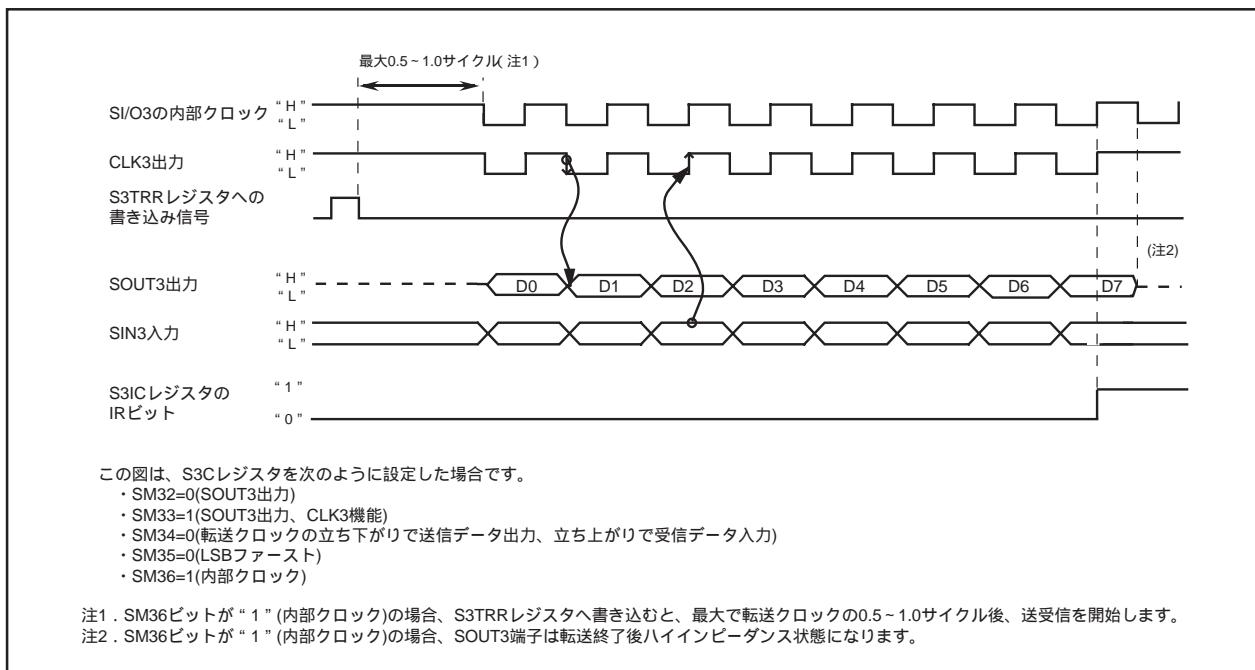

| 15.2.1  | SI/O3動作タイミング .....                  | 186 |

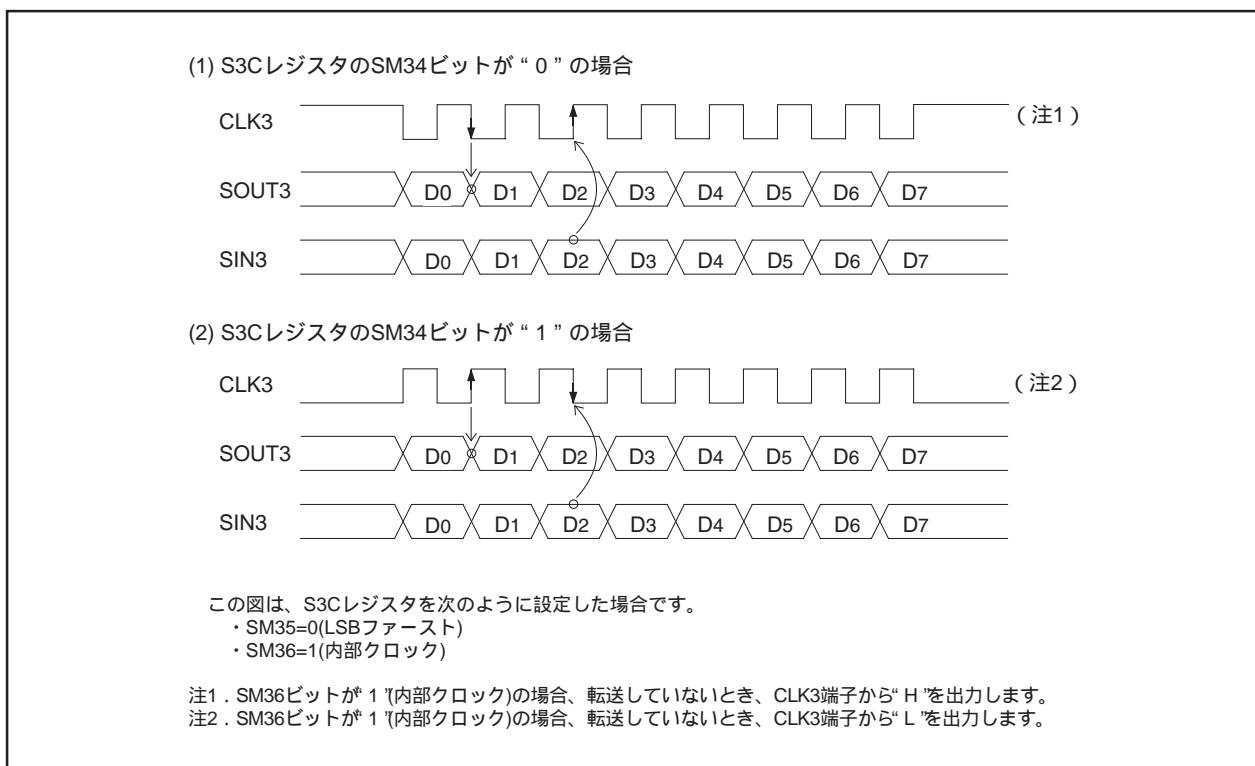

| 15.2.2  | CLK極性選択 .....                       | 186 |

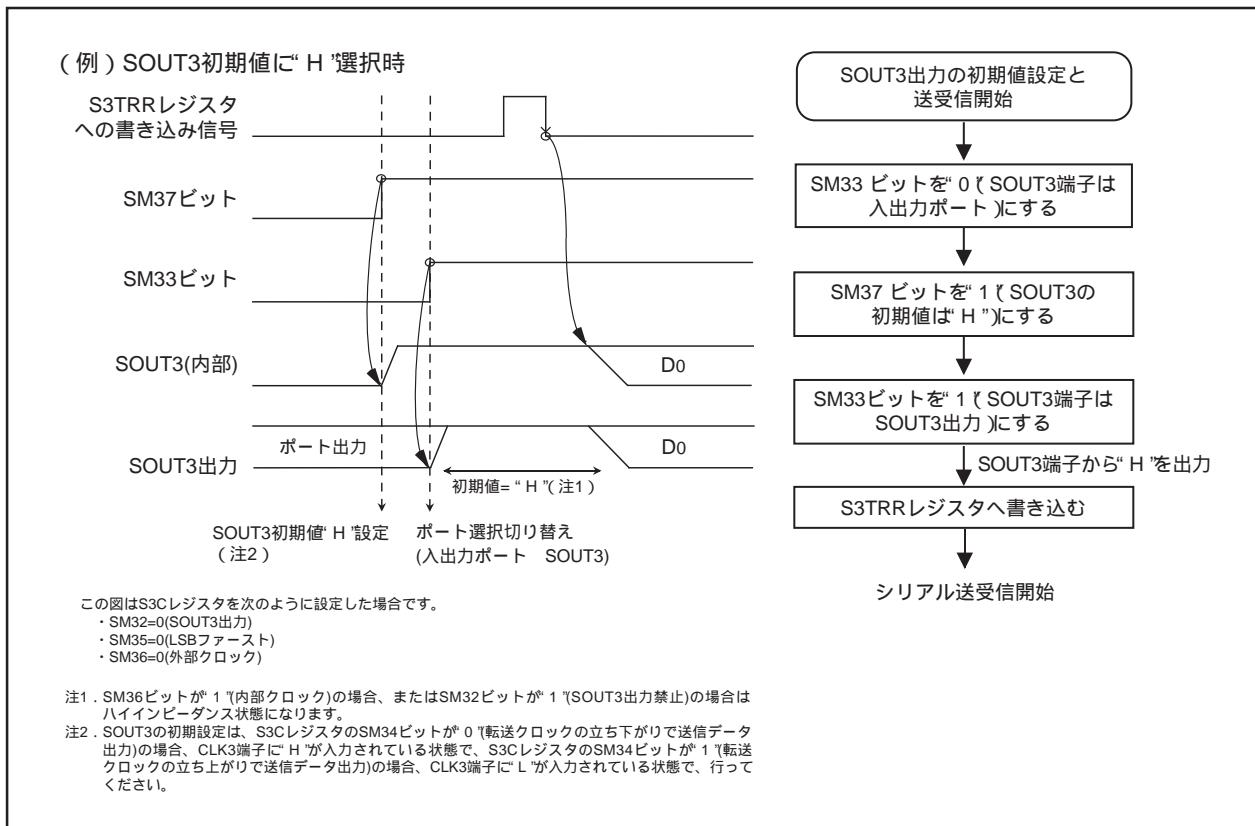

| 15.2.3  | SOUT3初期値設定機能 .....                  | 187 |

|                                        |     |

|----------------------------------------|-----|

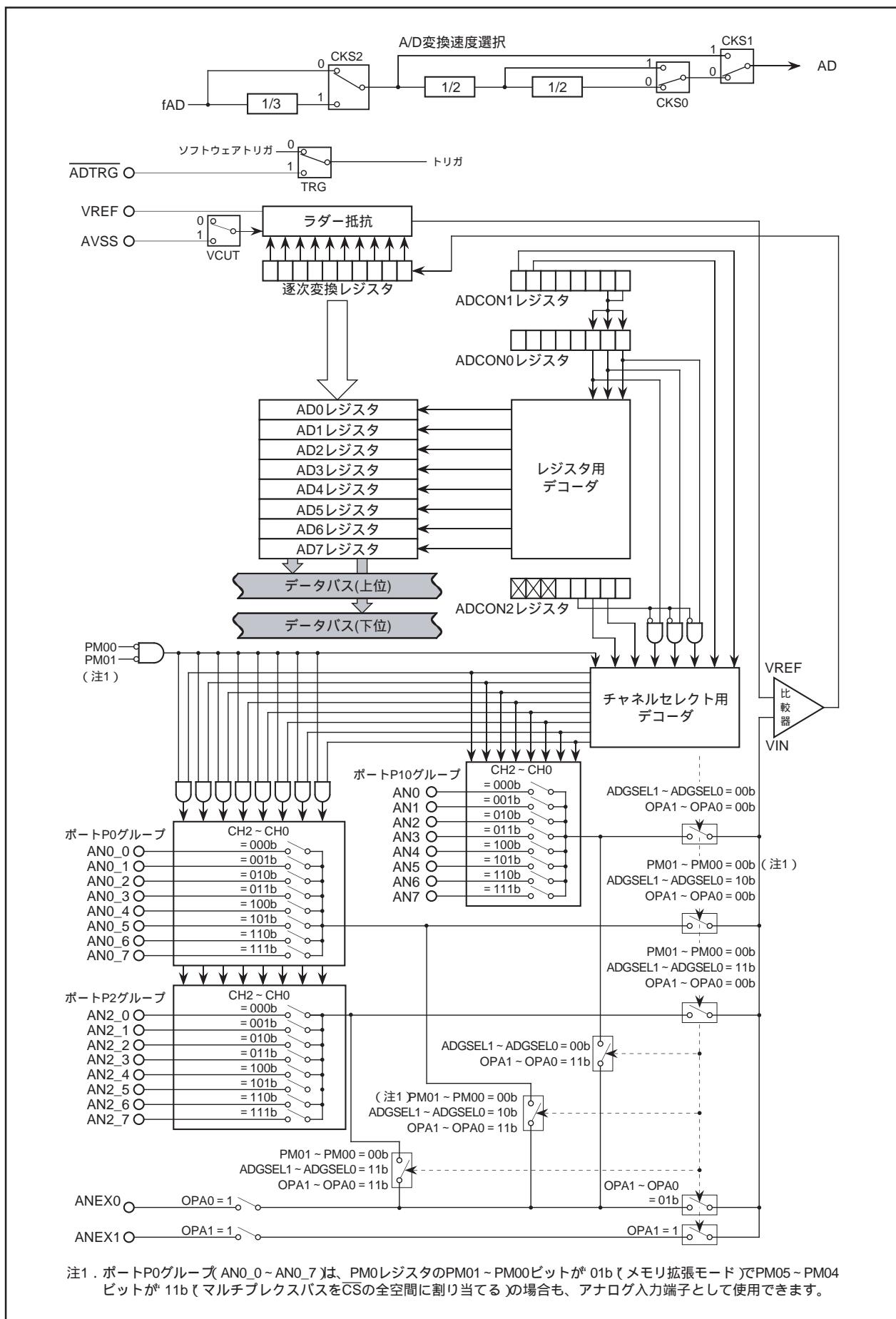

| 16 . A/Dコンバータ .....                    | 188 |

| 16.1 モードの説明 .....                      | 192 |

| 16.1.1 単発モード .....                     | 192 |

| 16.1.2 繰り返しモード .....                   | 194 |

| 16.1.3 単掃引モード .....                    | 196 |

| 16.1.4 繰り返し掃引モード0 .....                | 198 |

| 16.1.5 繰り返し掃引モード1 .....                | 200 |

| 16.2 機能 .....                          | 202 |

| 16.2.1 分解能選択機能 .....                   | 202 |

| 16.2.2 サンプル&ホールド .....                 | 202 |

| 16.2.3 拡張アナログ入力端子 .....                | 202 |

| 16.2.4 外部オペアンプ接続モード .....              | 202 |

| 16.2.5 消費電流低減機能 .....                  | 203 |

| 16.2.6 A/D変換時のセンサーの出力インピーダンス .....     | 203 |

| 17 . D/Aコンバータ .....                    | 205 |

| 18 . CRC演算回路 .....                     | 207 |

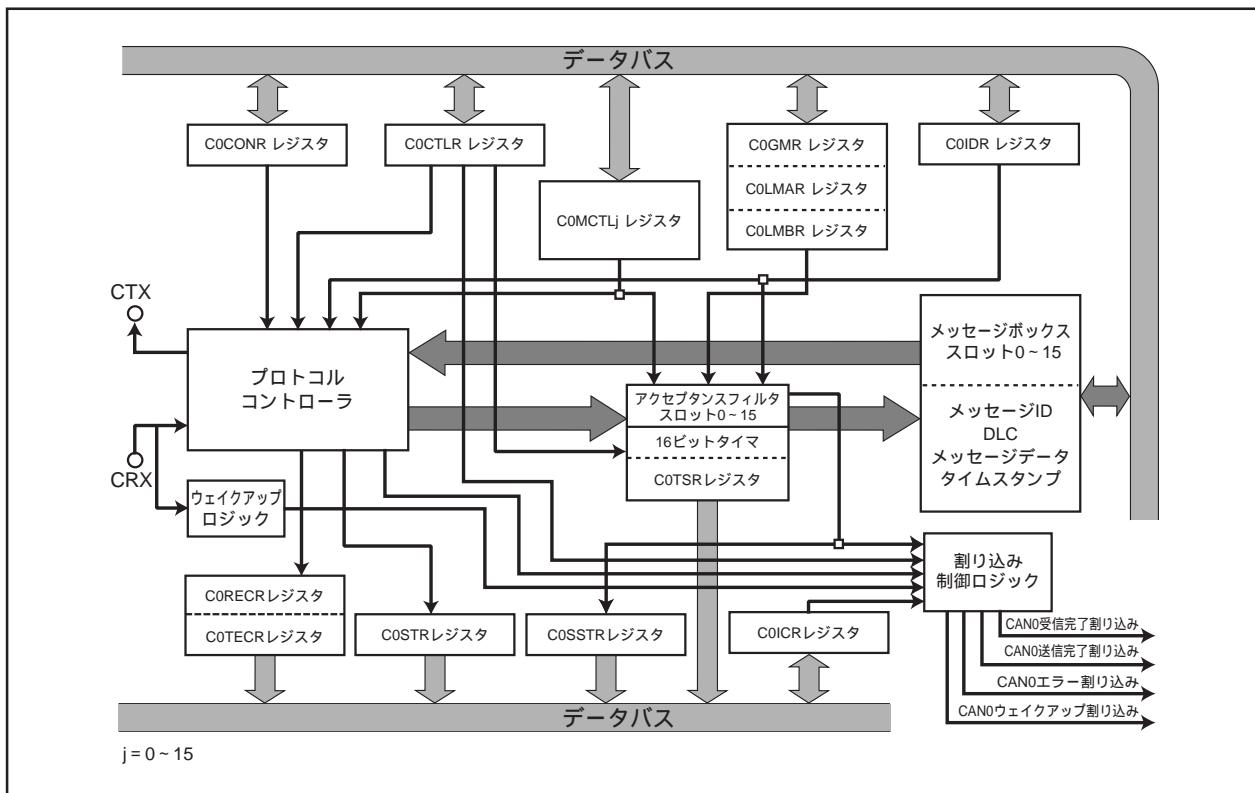

| 19 . CANモジュール .....                    | 209 |

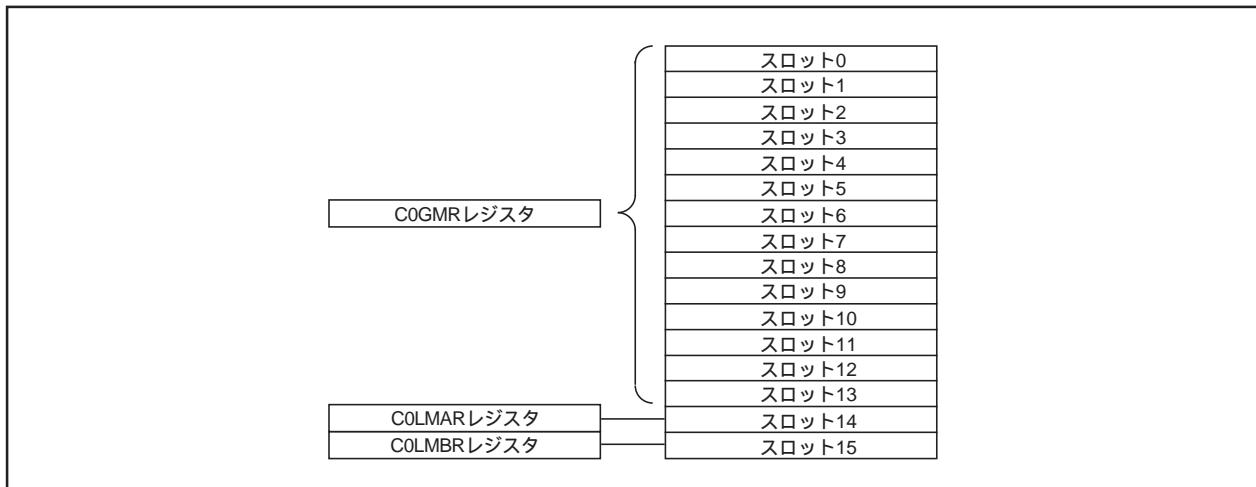

| 19.1 CANモジュール関連レジスタ .....              | 210 |

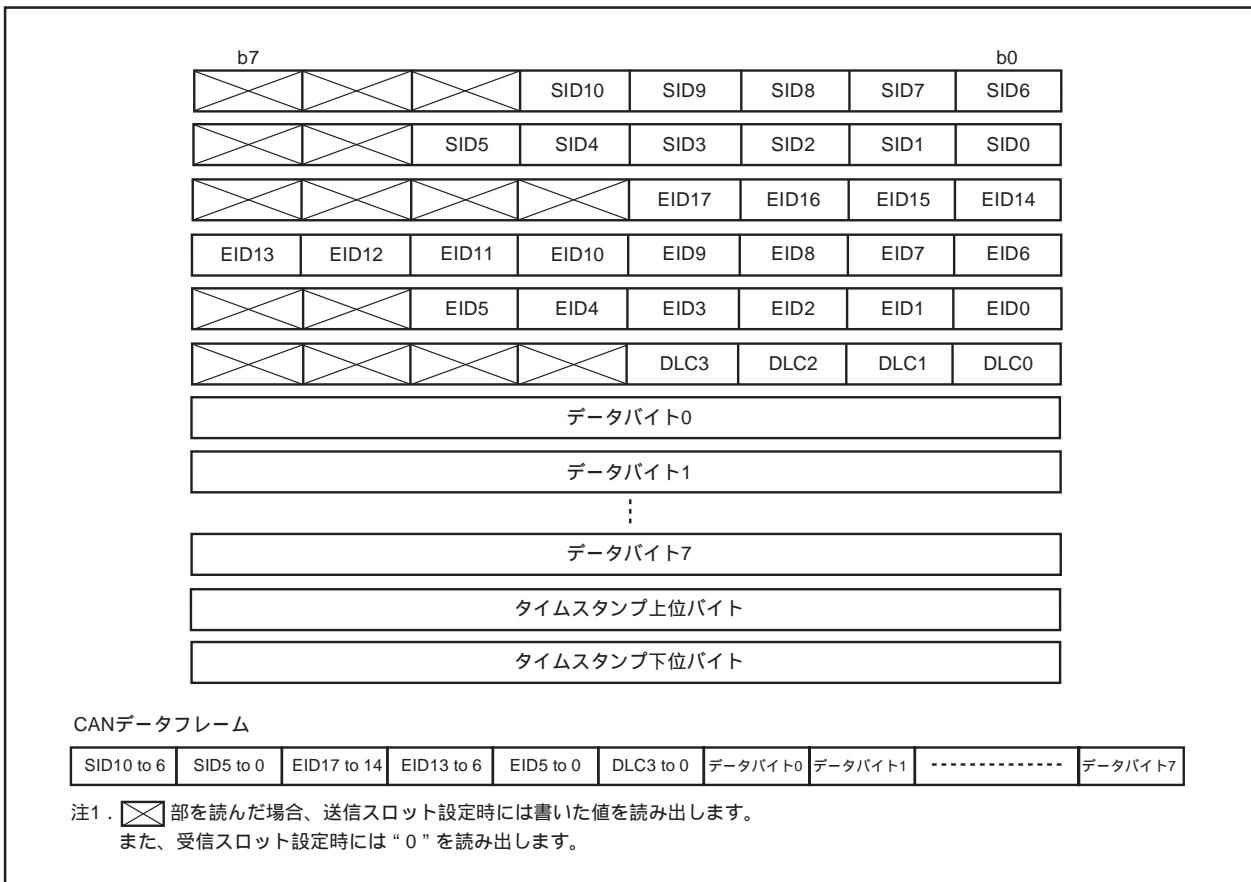

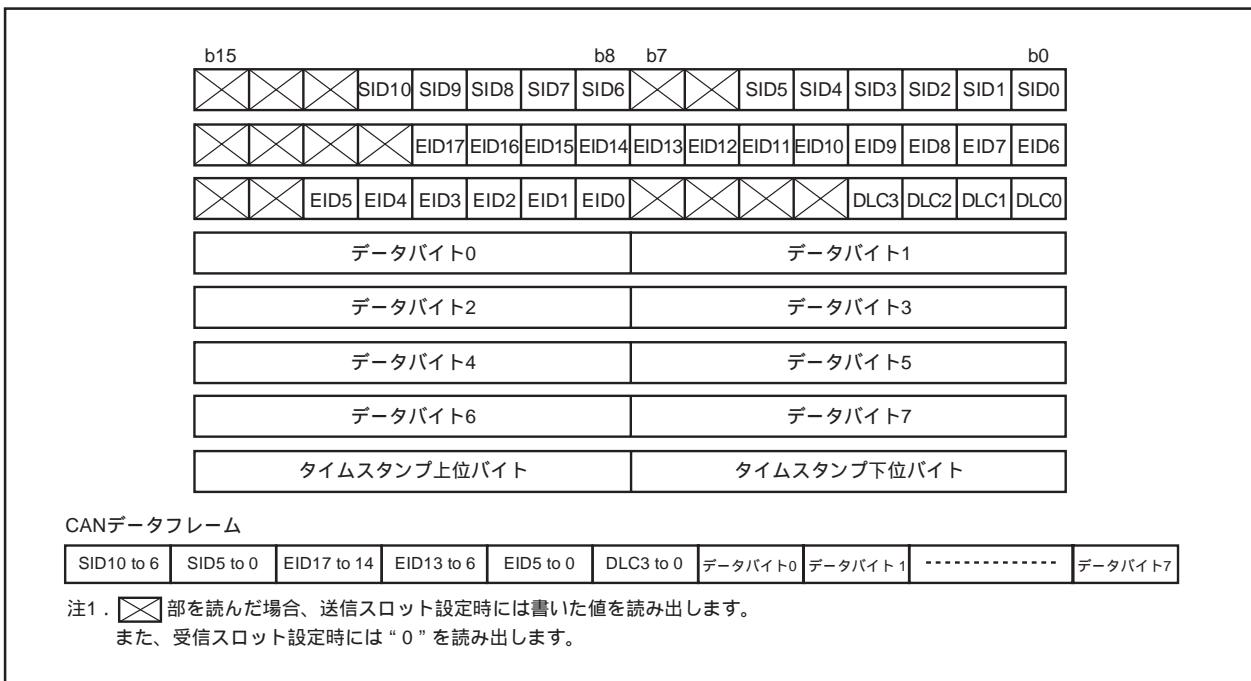

| 19.1.1 CAN0メッセージボックス .....             | 210 |

| 19.1.2 アクセプタンスマスクレジスタ .....            | 210 |

| 19.1.3 CAN専用レジスタ( SFR ) .....          | 210 |

| 19.2 CAN0メッセージボックス .....               | 211 |

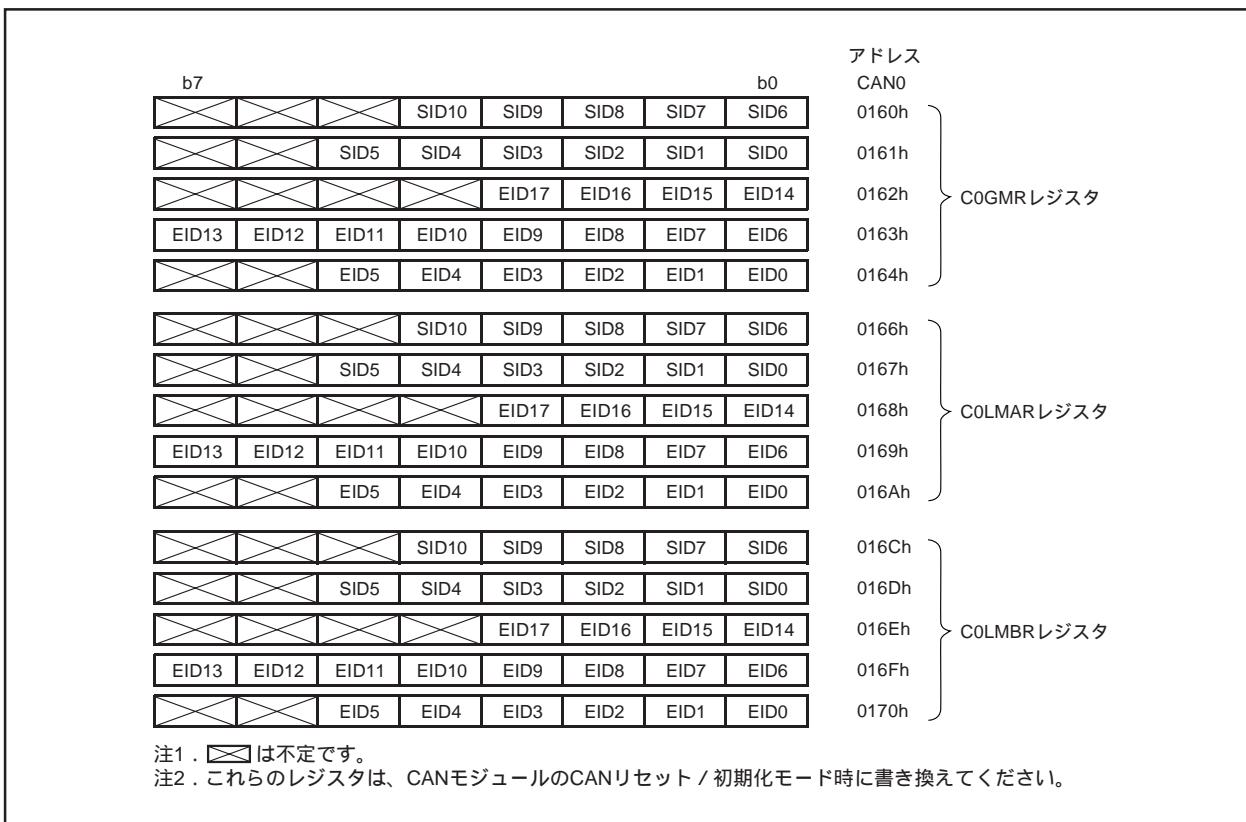

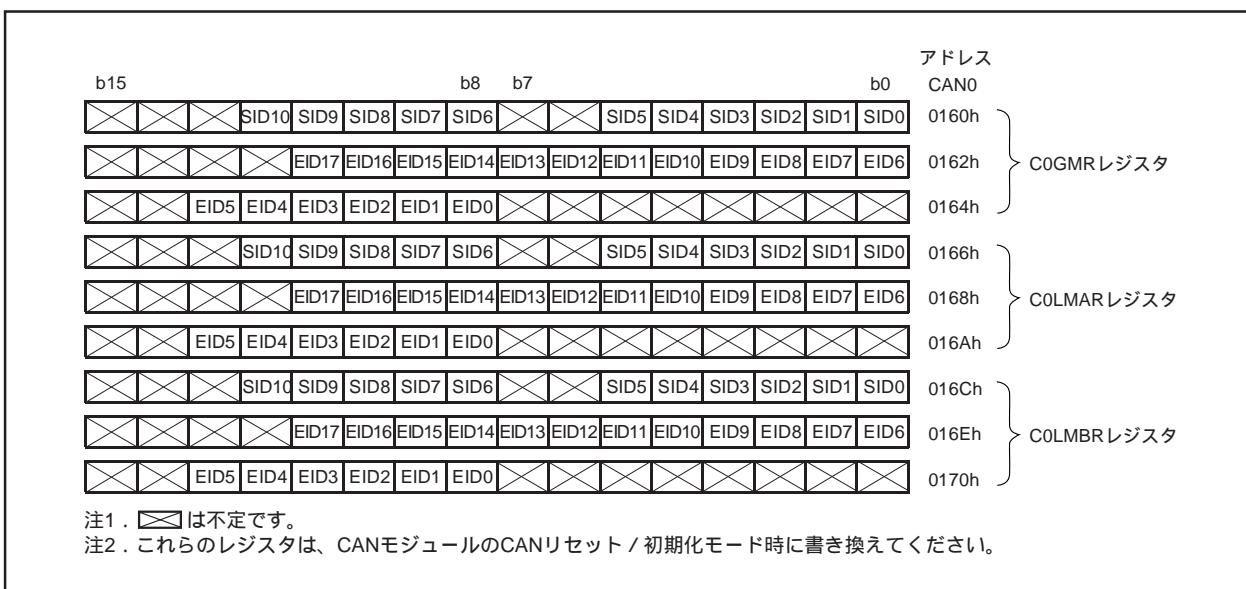

| 19.3 アクセプタンスマスクレジスタ .....              | 213 |

| 19.4 CAN SFRレジスタ .....                 | 214 |

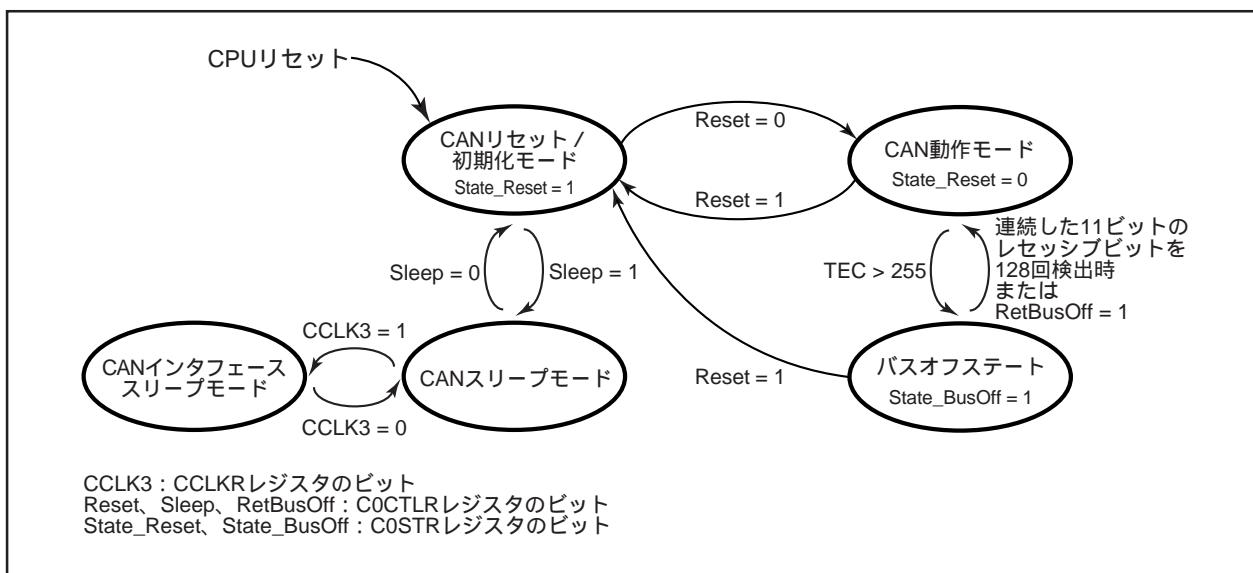

| 19.5 動作モード .....                       | 221 |

| 19.5.1 CANリセット / 初期化モード .....          | 221 |

| 19.5.2 CAN動作モード .....                  | 222 |

| 19.5.3 CANスリープモード .....                | 222 |

| 19.5.4 CANインターフェーススリープモード .....        | 222 |

| 19.5.5 バスオフステート .....                  | 223 |

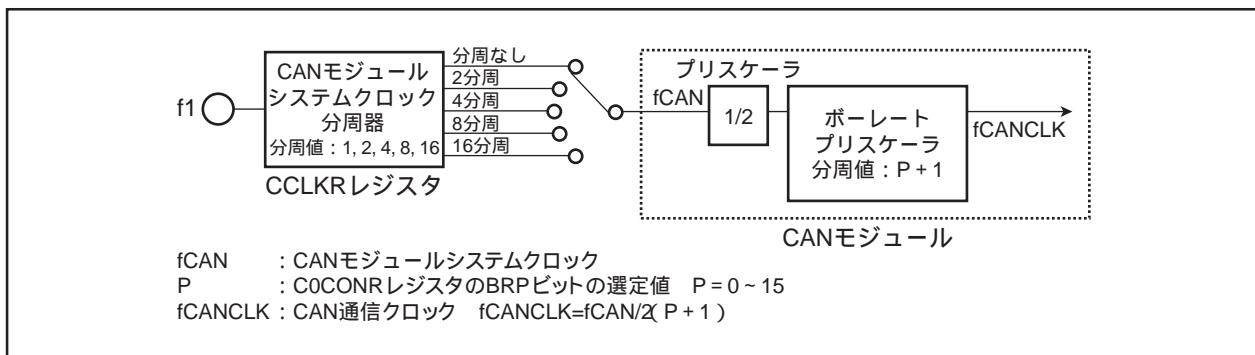

| 19.6 CANモジュールシステムクロックの設定 .....         | 224 |

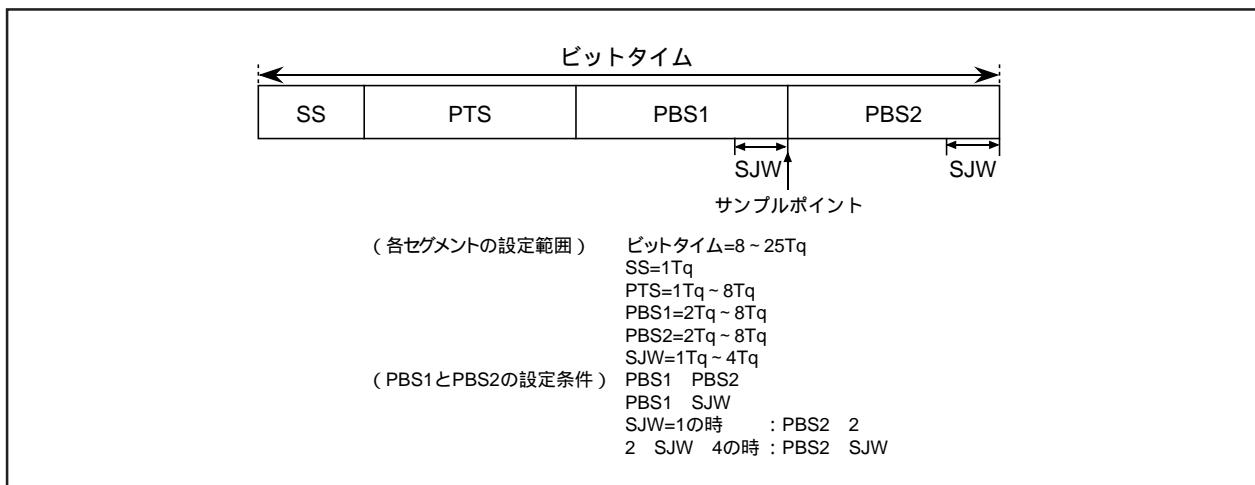

| 19.7 ビットタイミングの設定 .....                 | 224 |

| 19.8 転送速度 .....                        | 225 |

| 19.8.1 転送速度の算出式 .....                  | 225 |

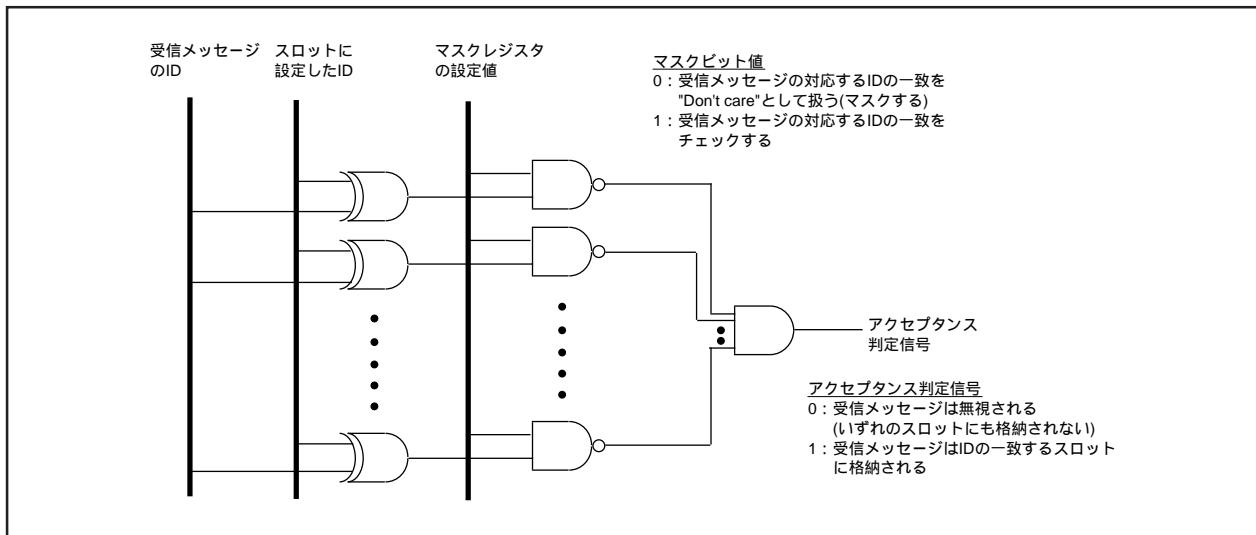

| 19.9 アクセプタンスフィルタ機能とマスク機能 .....         | 226 |

| 19.10 アクセプタンスフィルタサポートユニット( ASU ) ..... | 227 |

| 19.11 Basic CANモード .....               | 228 |

| 19.12 リターンフロムバスオフ機能 .....              | 229 |

| 19.13 タイムスタンプカウンタとタイムスタンプ機能 .....      | 229 |

| 19.14 リッスンオンリーモード .....                | 229 |

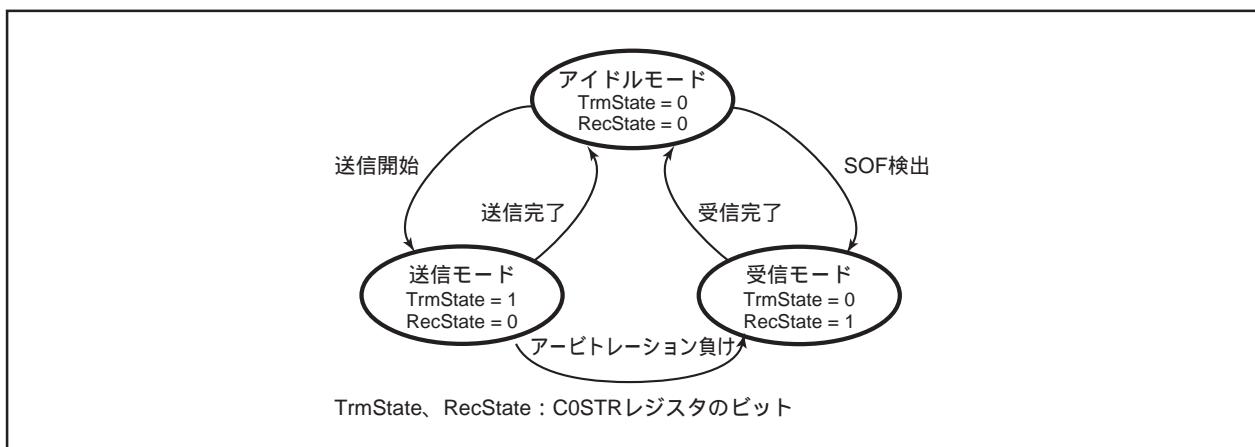

| 19.15 CAN受信とCAN送信 .....                | 230 |

| 19.15.1 受信 .....                       | 231 |

| 19.15.2 送信 .....                       | 232 |

| 19.16 CAN割り込み .....                    | 233 |

|                                       |     |

|---------------------------------------|-----|

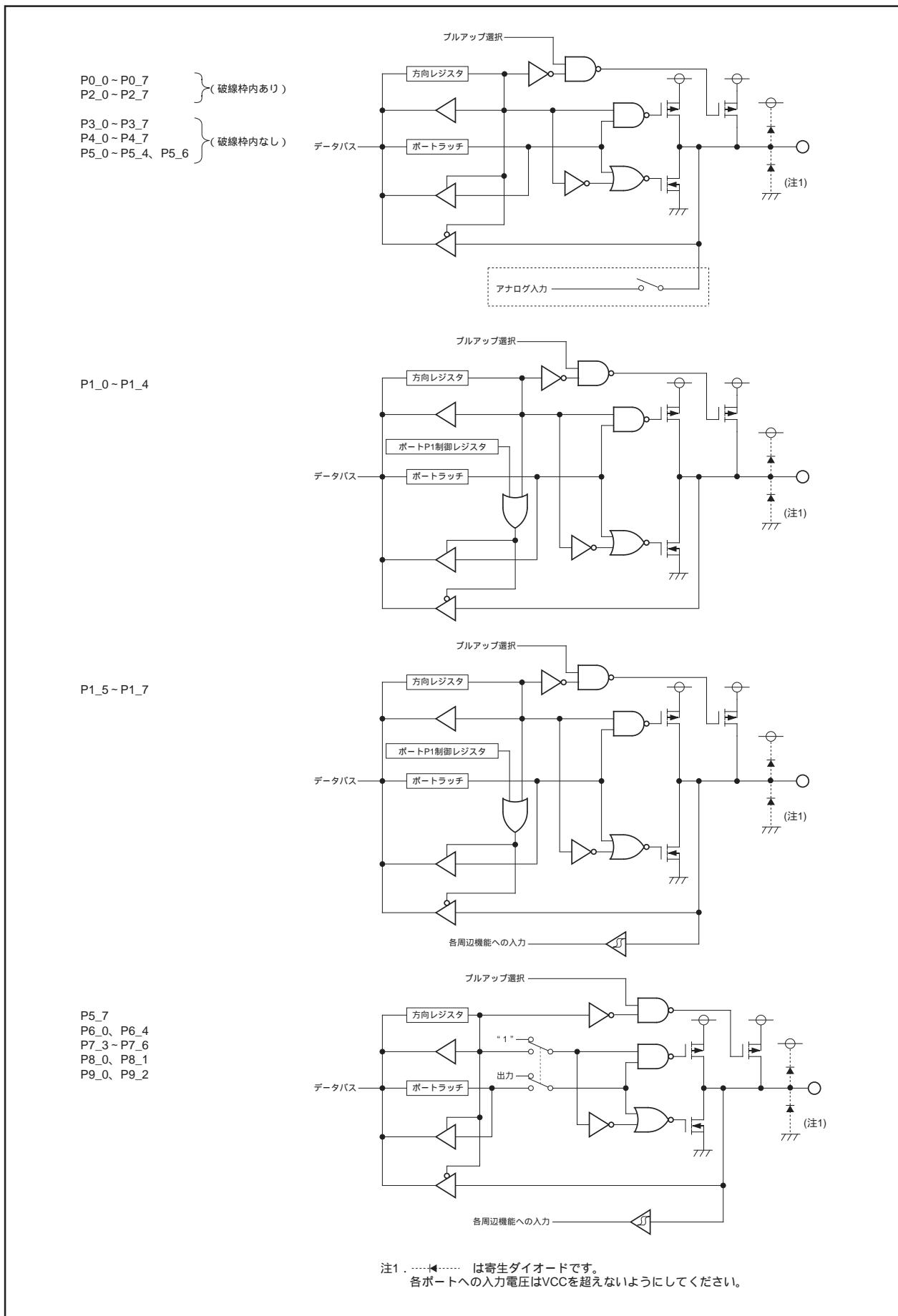

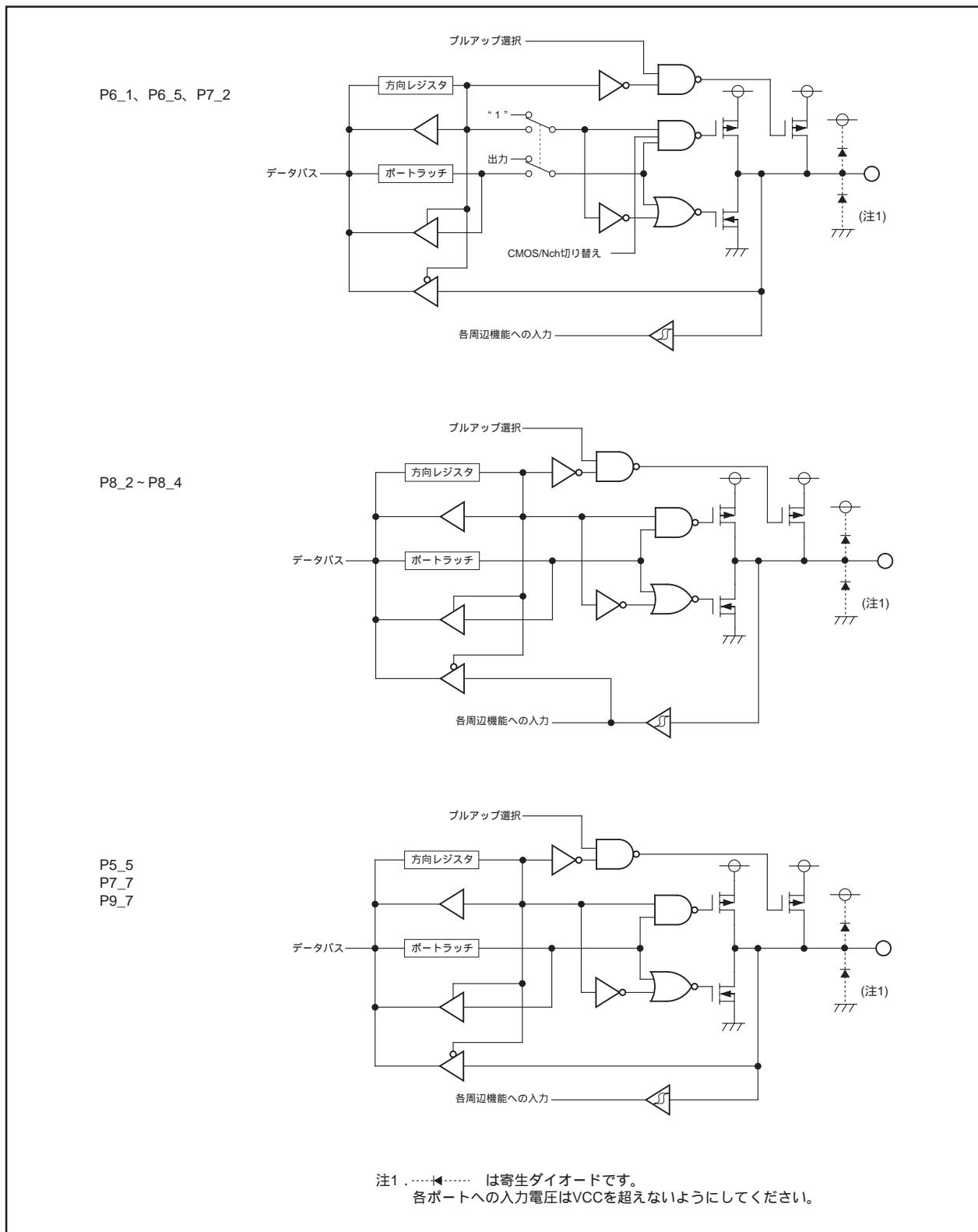

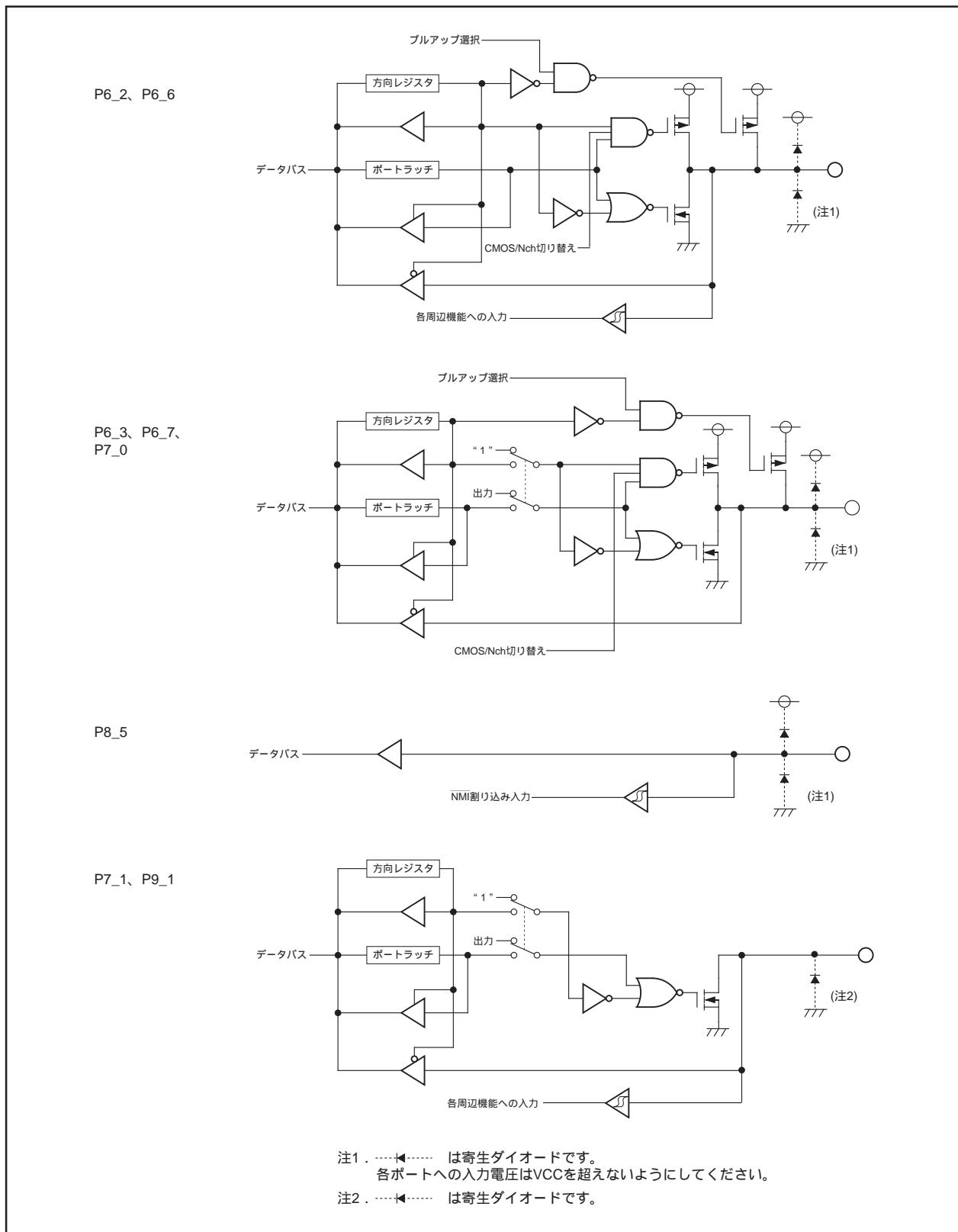

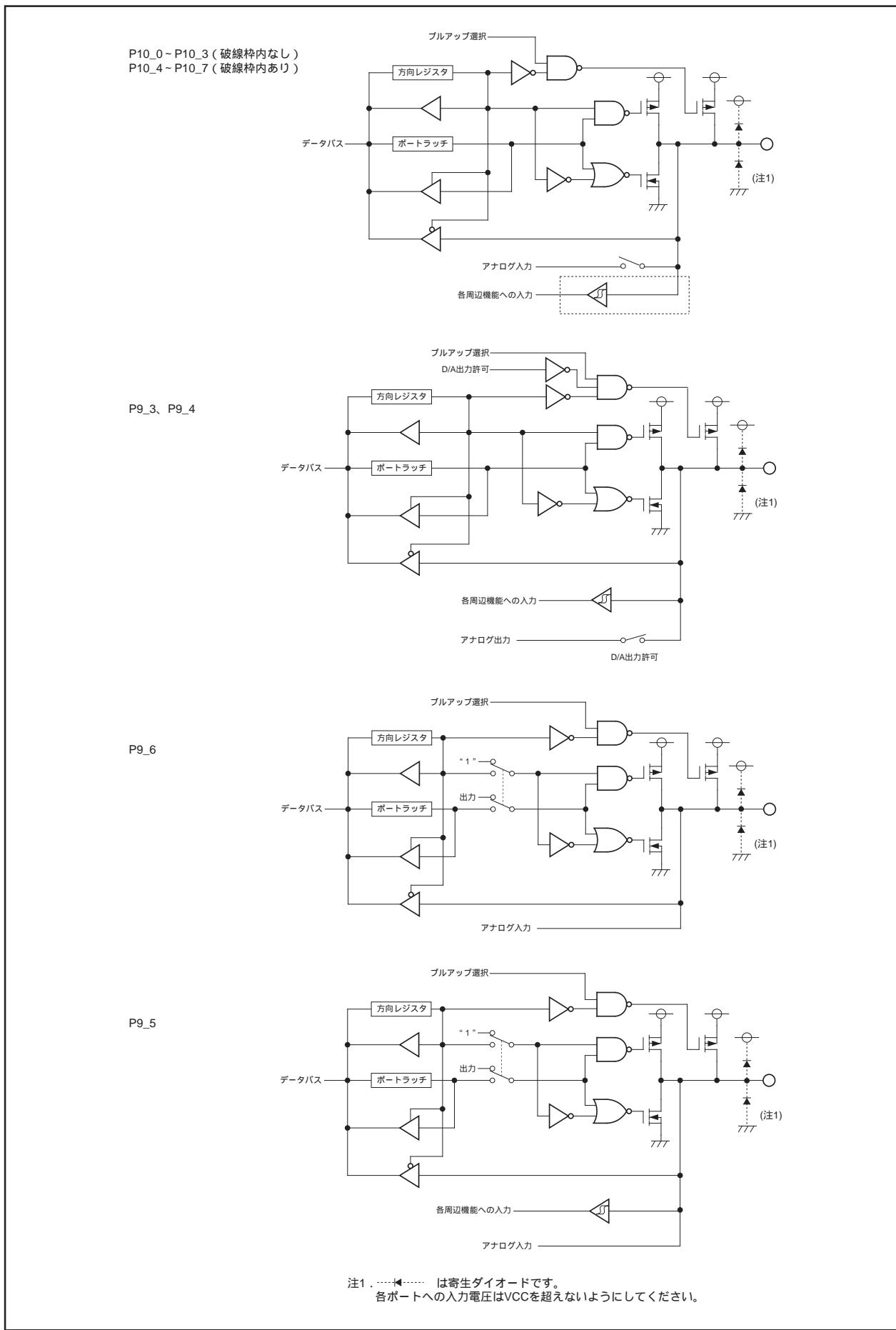

| 20 . プログラマブル入出力ポート .....              | 234 |

| 20.1 PDiレジスタ .....                    | 234 |

| 20.2 Piレジスタ .....                     | 234 |

| 20.3 PURjレジスタ .....                   | 234 |

| 20.4 PCRレジスタ .....                    | 235 |

| 21 . フラッシュメモリ版 .....                  | 247 |

| 21.1 メモリ配置 .....                      | 248 |

| 21.1.1 ブートモード .....                   | 248 |

| 21.2 フラッシュメモリ書き換え禁止機能 .....           | 249 |

| 21.2.1 ROMコードプロテクト機能 .....            | 249 |

| 21.2.2 IDコードチェック機能 .....              | 249 |

| 21.3 CPU書き換えモード .....                 | 251 |

| 21.3.1 EW0モード .....                   | 252 |

| 21.3.2 EW1モード .....                   | 252 |

| 21.3.3 FMR0、FMR1レジスタ .....            | 253 |

| 21.3.4 CPU書き換えモードの注意事項 .....          | 258 |

| 21.3.5 ソフトウェアコマンド .....               | 260 |

| 21.3.6 データ保護機能 .....                  | 265 |

| 21.3.7 ステータスレジスタ(SRDレジスタ) .....       | 265 |

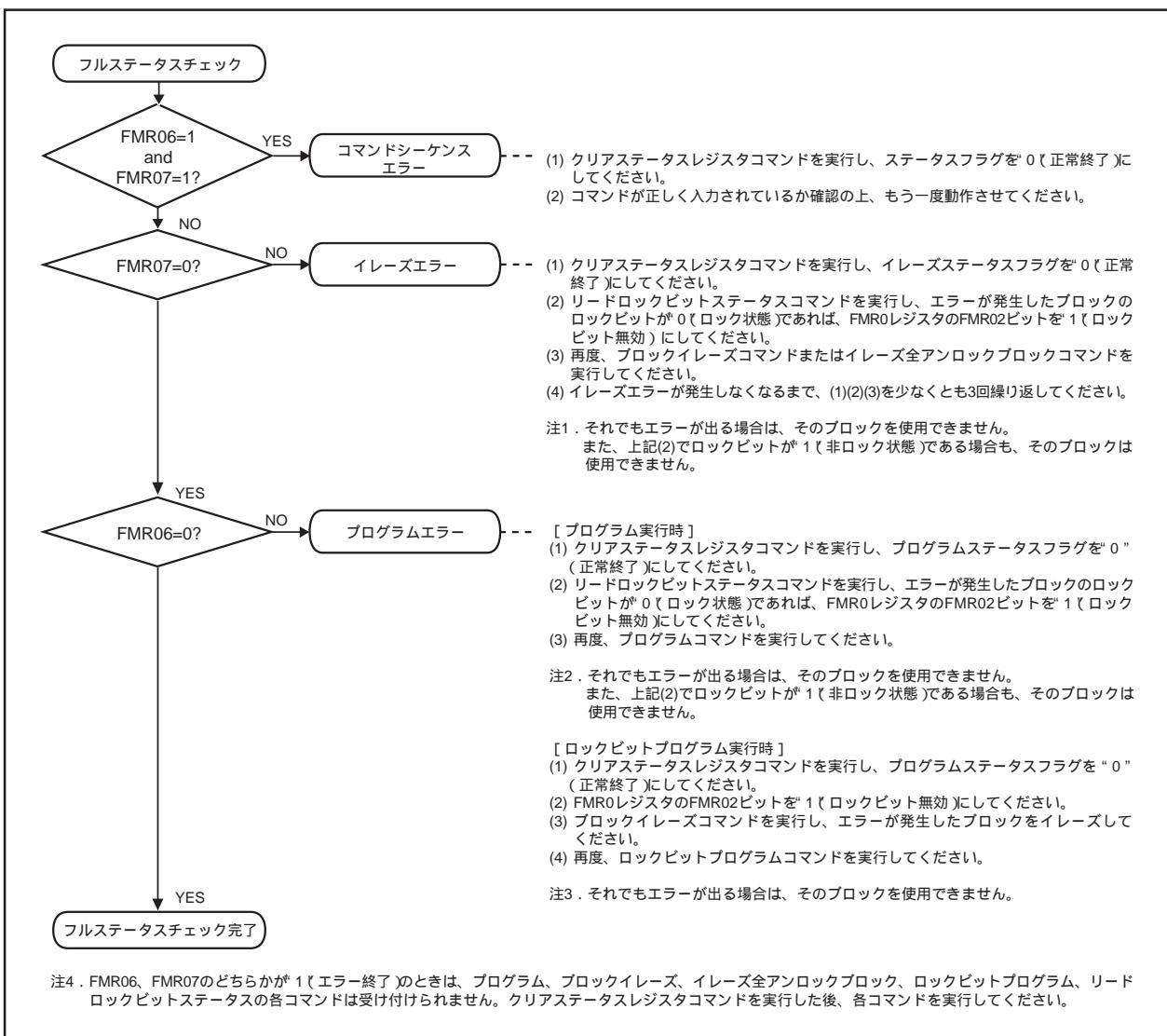

| 21.3.8 フルステータスチェック .....              | 267 |

| 21.4 標準シリアル入出力モード .....               | 269 |

| 21.4.1 IDコードチェック機能 .....              | 269 |

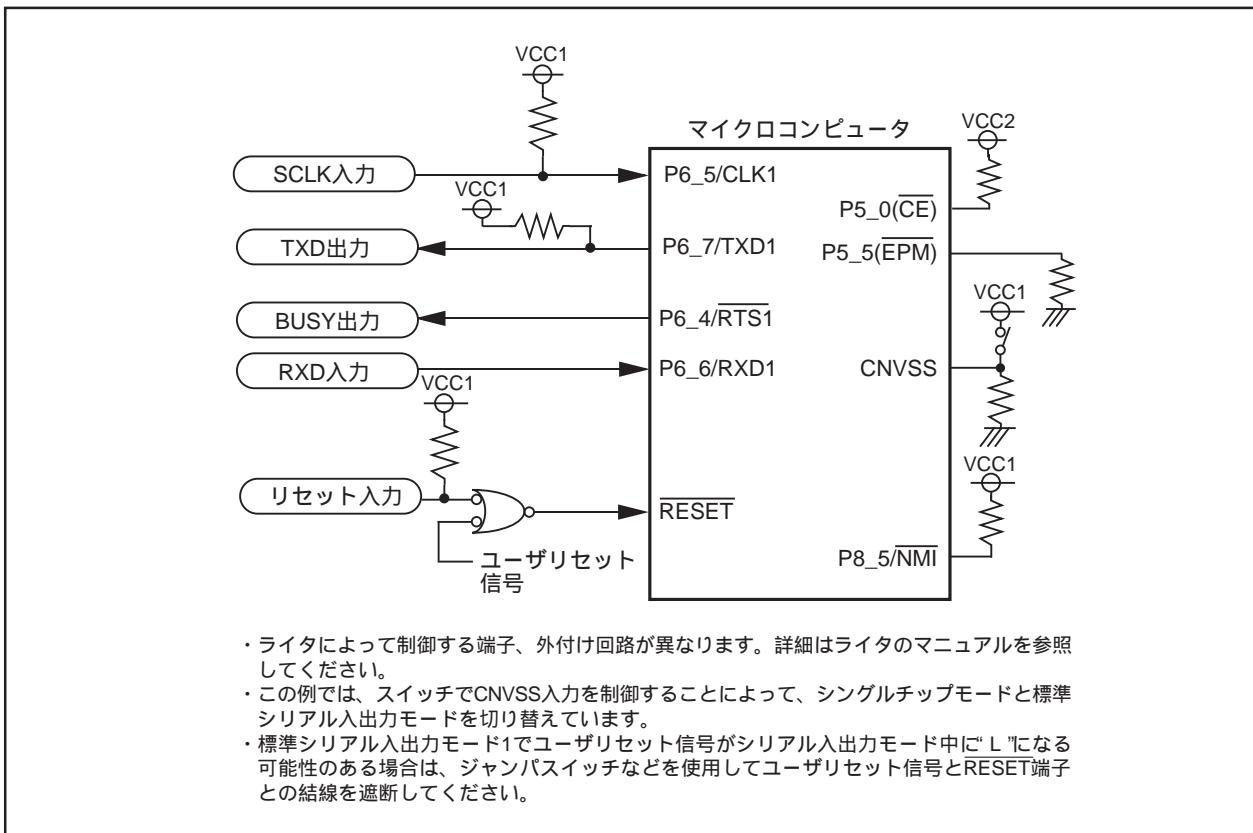

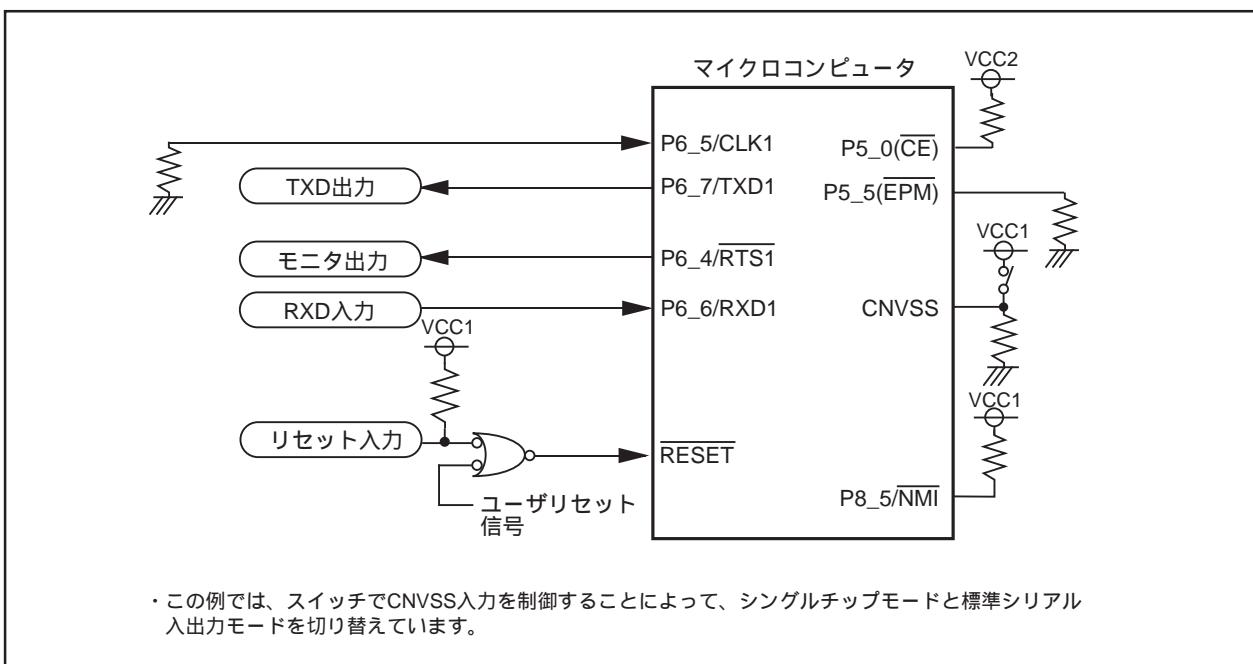

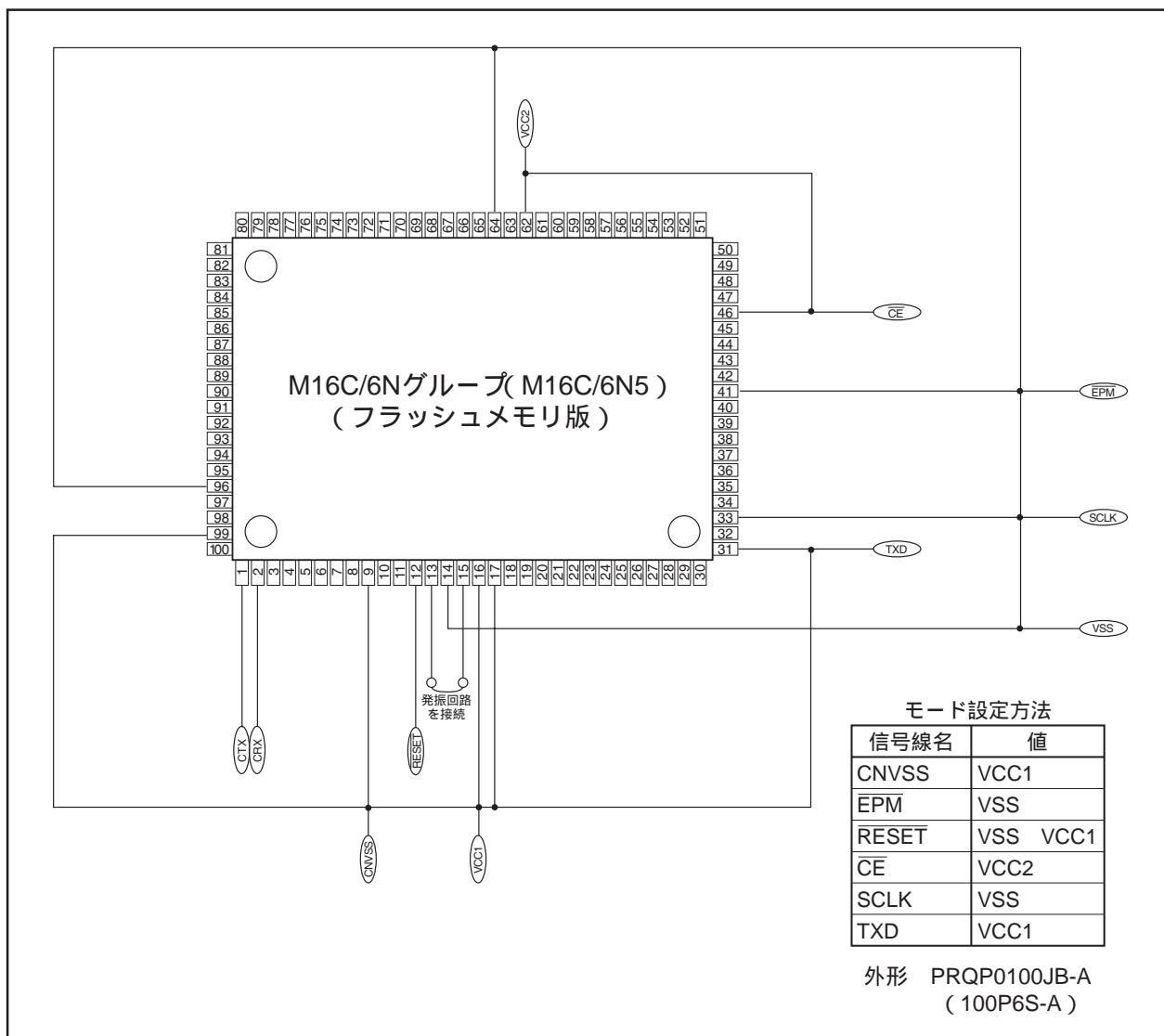

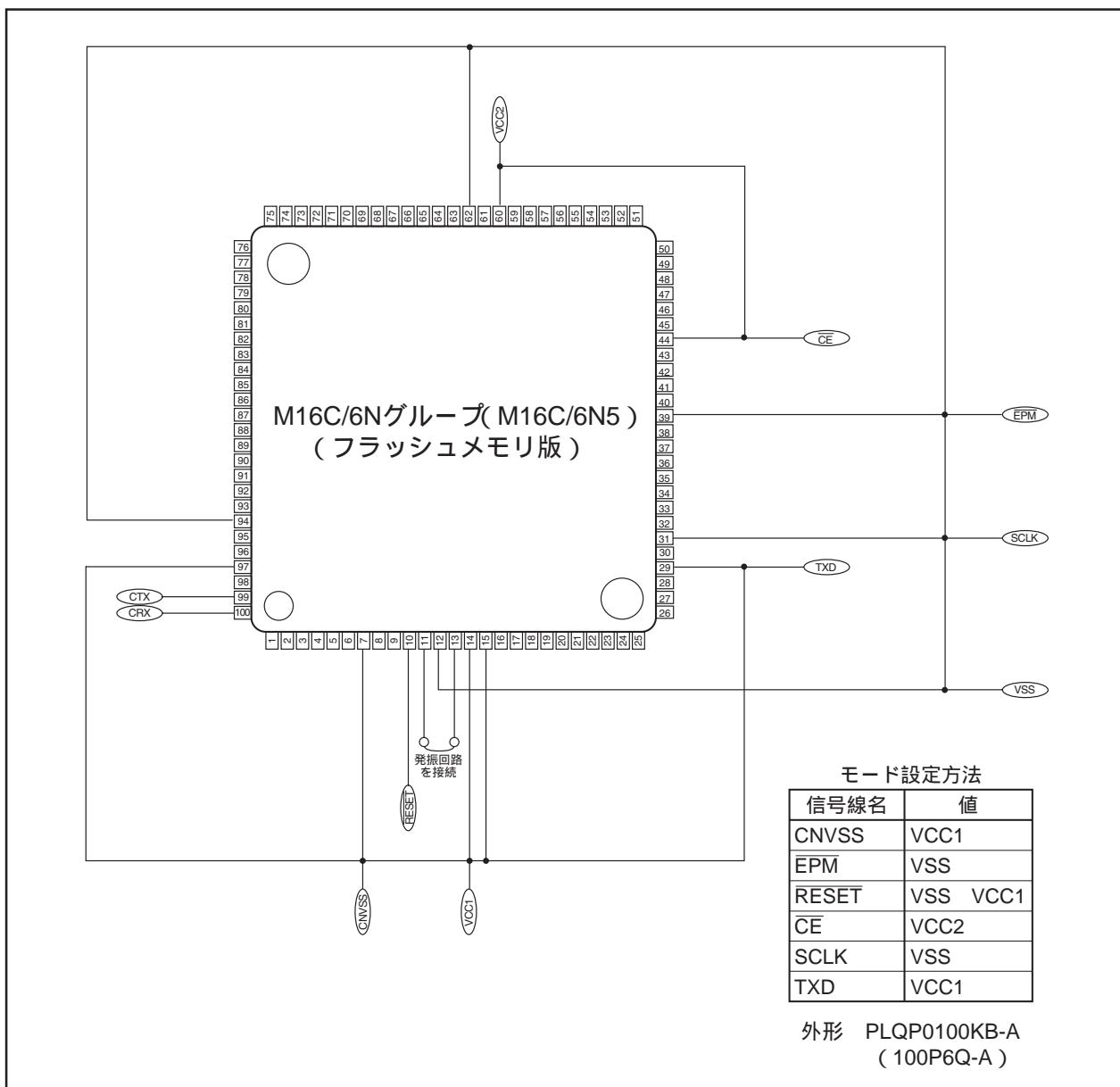

| 21.4.2 標準シリアル入出力モード1および2時の端子処理例 ..... | 273 |

| 21.5 パラレル入出力モード .....                 | 274 |

| 21.5.1 ブートROM領域 .....                 | 274 |

| 21.5.2 ROMコードプロテクト機能 .....            | 274 |

| 21.6 CAN入出力モード .....                  | 275 |

| 21.6.1 IDコードチェック機能 .....              | 275 |

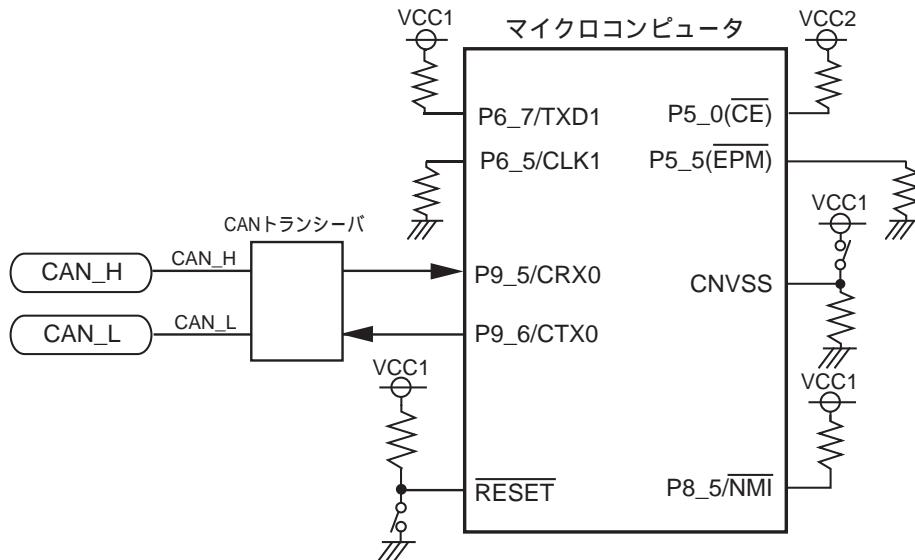

| 21.6.2 CAN入出力モード時の端子処理例 .....         | 278 |

| 21.7 電気的特性 .....                      | 279 |

| 21.7.1 電気的特性(T/V-ver.) .....          | 279 |

| 21.7.2 電気的特性(Normal-ver.) .....       | 280 |

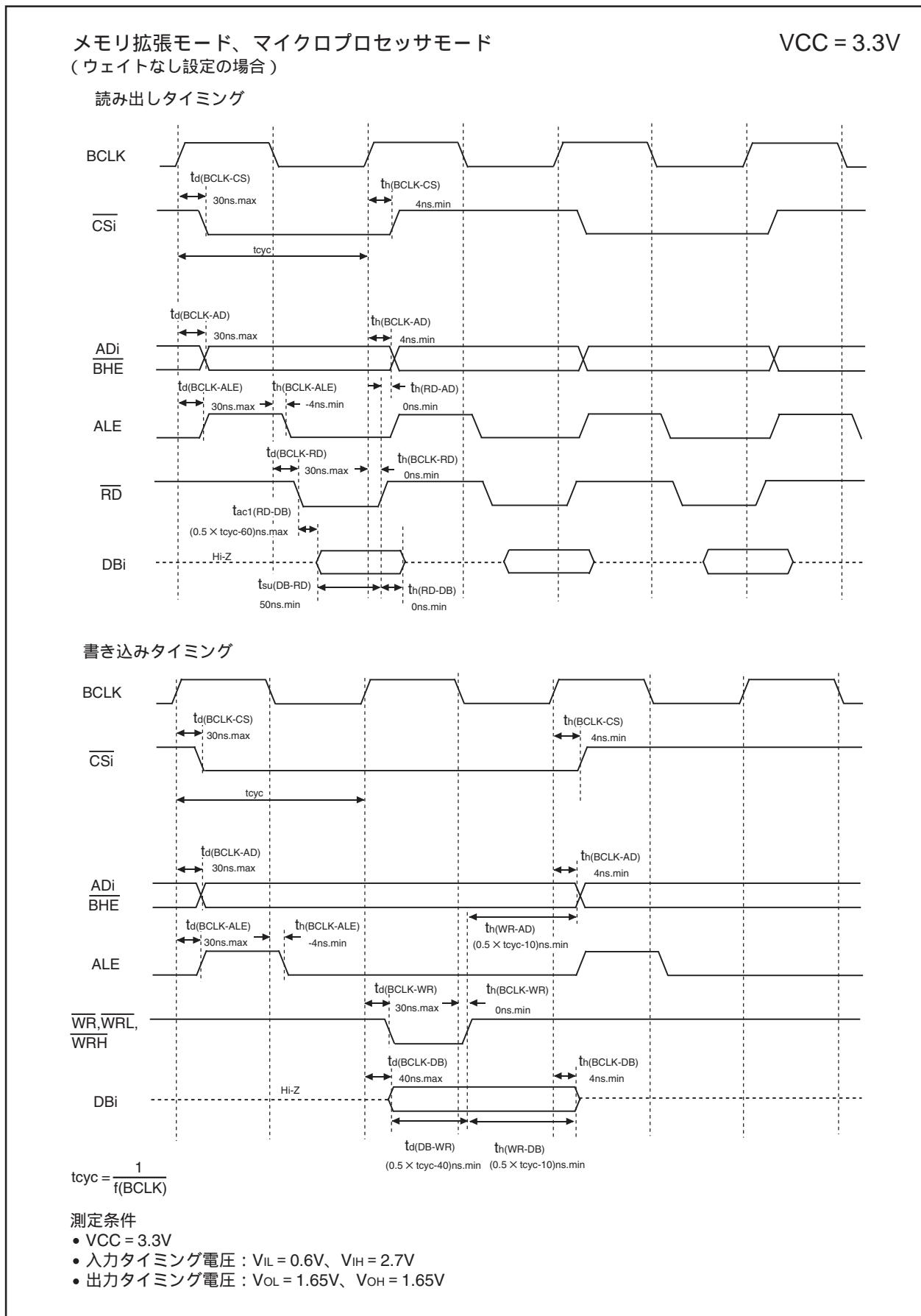

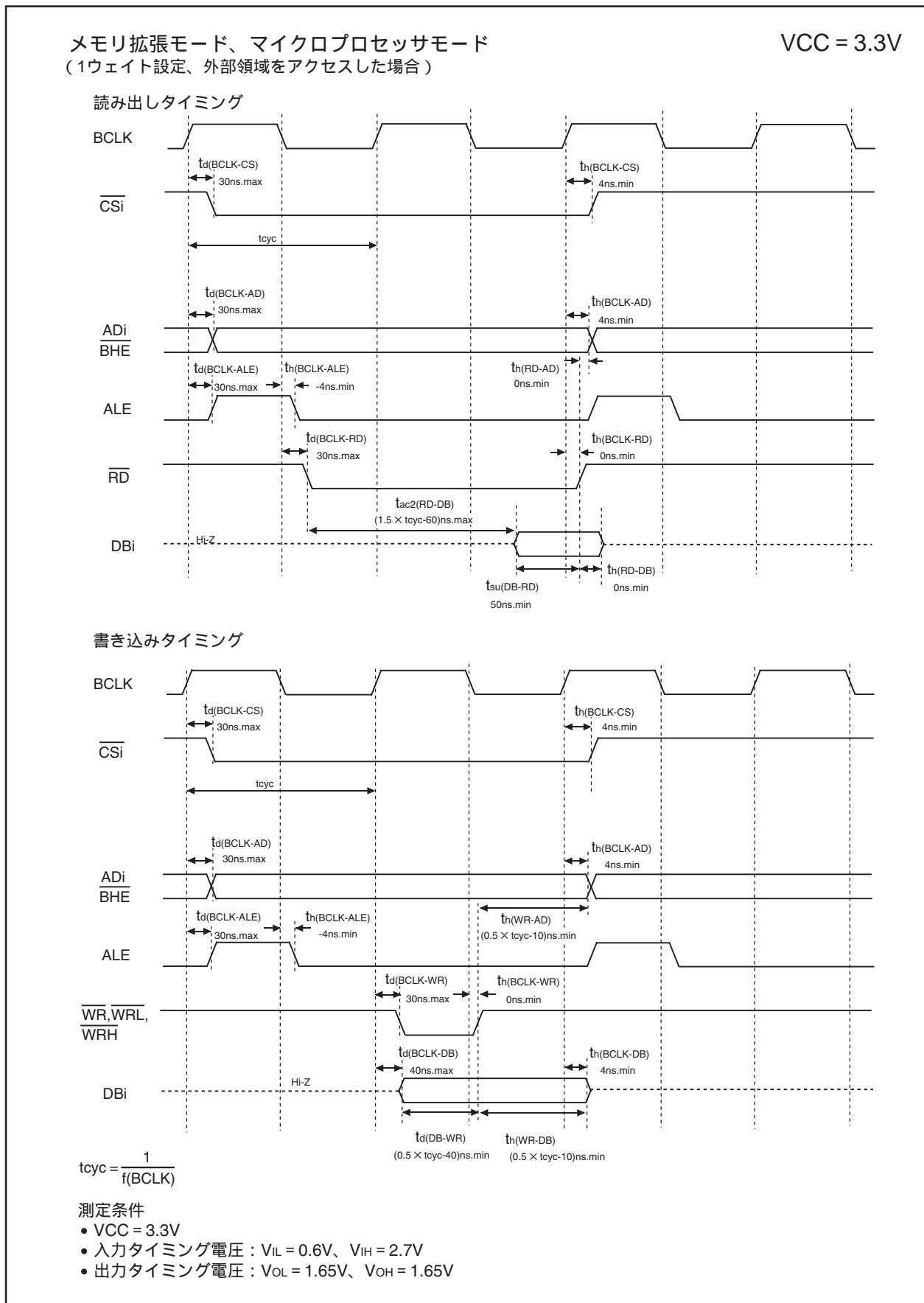

| 22 . 電気的特性 .....                      | 281 |

| 22.1 電気的特性(T/V-ver.) .....            | 281 |

| 22.2 電気的特性(Normal-ver.) .....         | 302 |

| 23 . 使用上の注意 .....                     | 338 |

| 23.1 SFR .....                        | 338 |

| 23.2 外部バス .....                       | 339 |

| 23.3 PLL周波数シンセサイザ .....               | 340 |

| 23.4 パワーコントロール .....                  | 341 |

| 23.5 プロテクト .....                      | 343 |

| 23.6 割り込み .....                       | 344 |

| 23.6.1 00000h番地の読み出し .....            | 344 |

| 23.6.2 SPの設定 .....                    | 344 |

| 23.6.3 NMI割り込み .....                  | 344 |

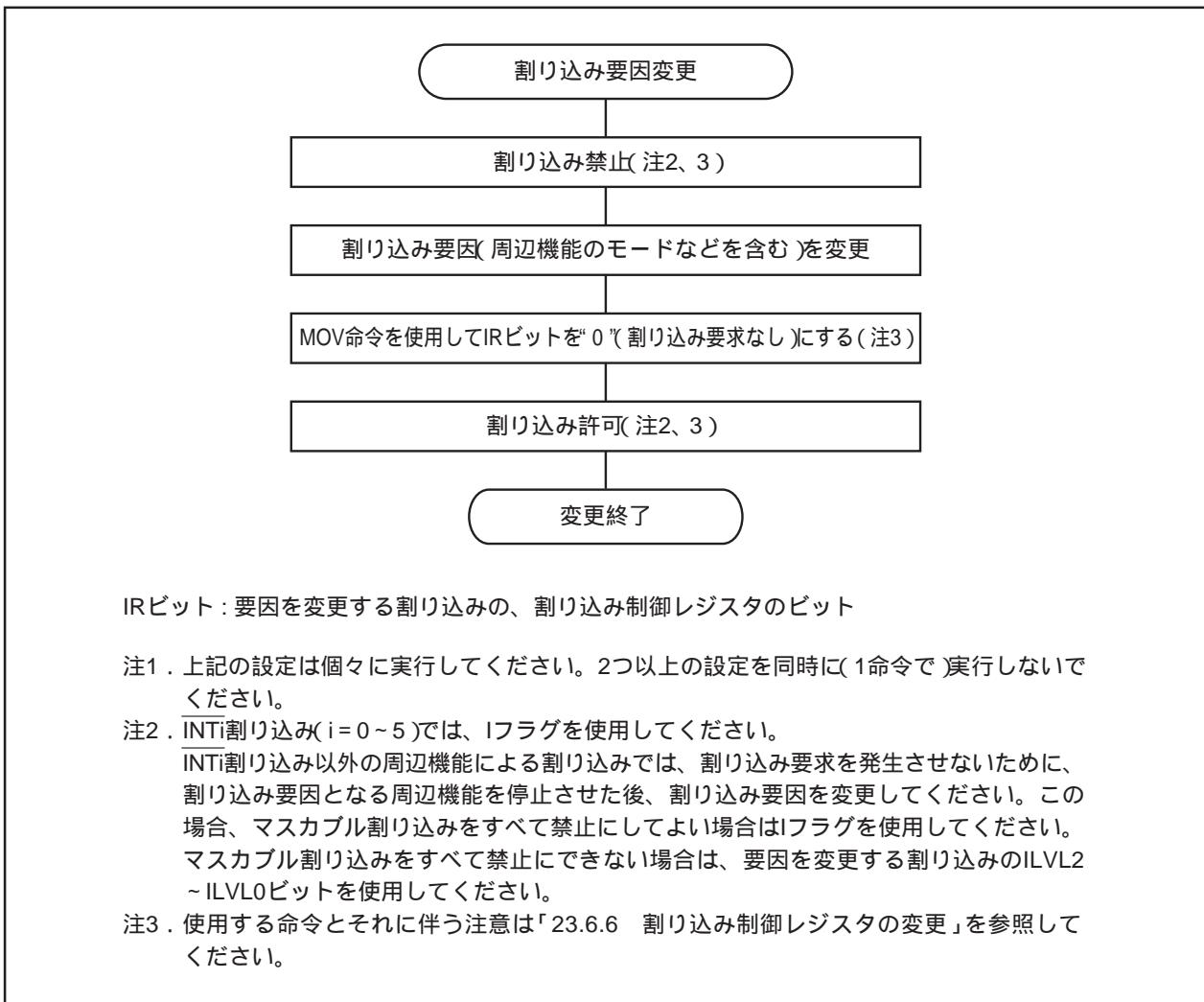

| 23.6.4 割り込み要因の変更 .....                | 345 |

| 23.6.5 INT割り込み .....                  | 345 |

| 23.6.6 割り込み制御レジスタの変更 .....            | 346 |

| 23.6.7 ウオッチドッグタイマ割り込み .....           | 346 |

|          |                                   |            |

|----------|-----------------------------------|------------|

| 23.7     | DMAC .....                        | 347        |

| 23.7.1   | DMICONレジスタのDMAEビットへの書き込み .....    | 347        |

| 23.8     | タイマ .....                         | 348        |

| 23.8.1   | タイマA .....                        | 348        |

| 23.8.2   | タイマB .....                        | 351        |

| 23.9     | シリアルインターフェース .....                | 353        |

| 23.9.1   | クロック同期形シリアルI/Oモード .....           | 353        |

| 23.9.2   | 特殊モード .....                       | 354        |

| 23.9.3   | SI/O3 .....                       | 355        |

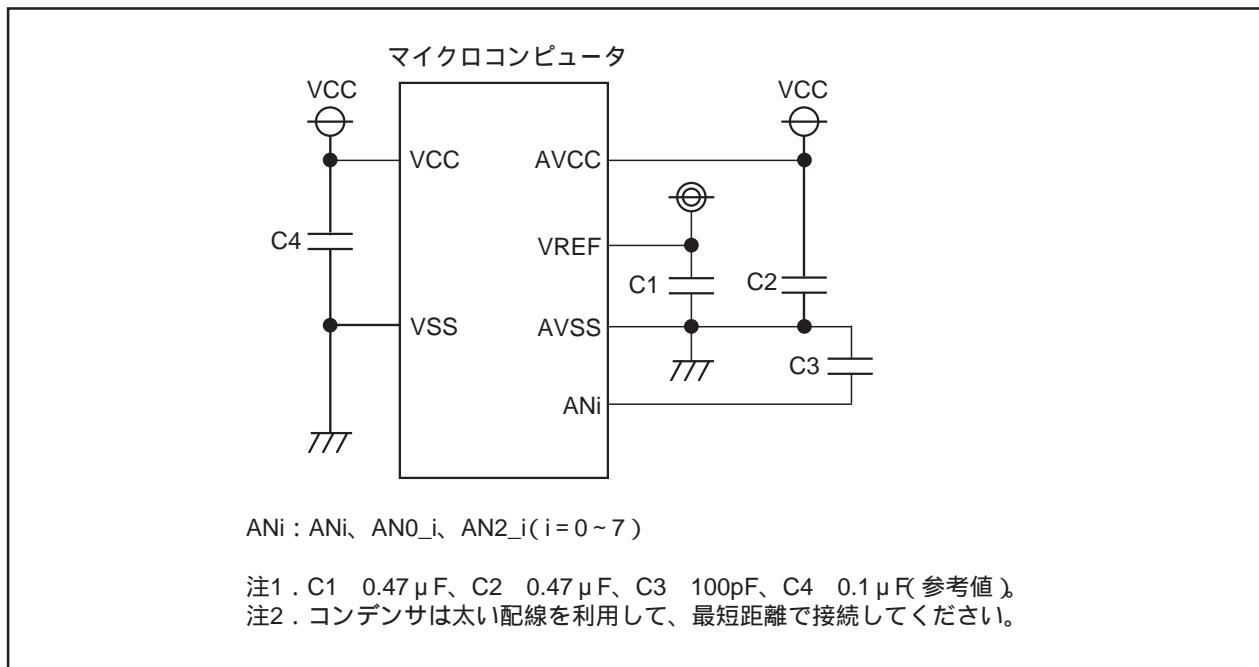

| 23.10    | A/Dコンバータ .....                    | 356        |

| 23.11    | CANモジュール .....                    | 358        |

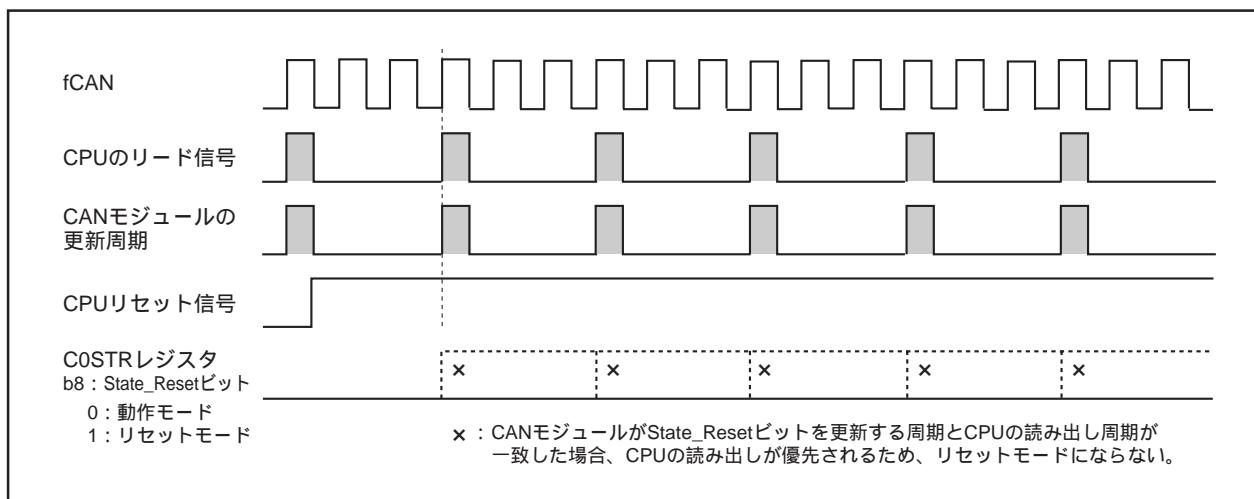

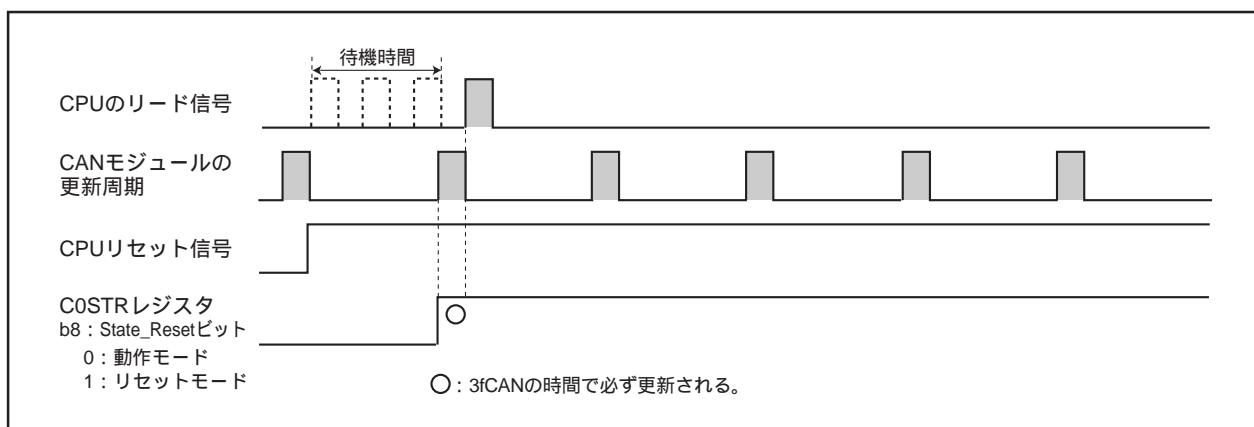

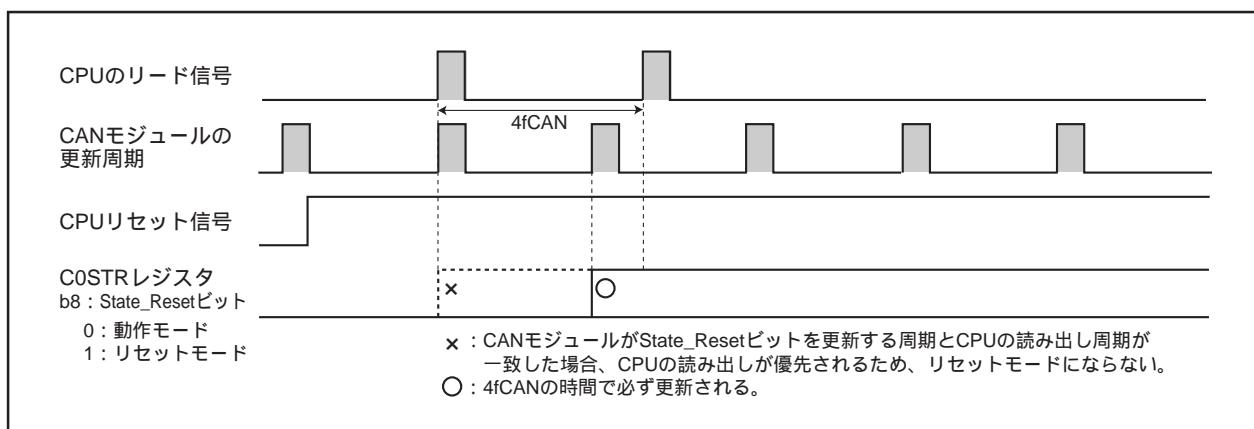

| 23.11.1  | C0STRレジスタの読み出し .....              | 358        |

| 23.11.2  | CAN動作モードとCANリセットモードの移行 .....      | 360        |

| 23.11.3  | 消費電流を小さくするためのポイント .....           | 361        |

| 23.11.4  | 標準ブートプログラム使用時のCANトランシーバ制御 .....   | 362        |

| 23.12    | プログラマブル入出力ポート .....               | 363        |

| 23.13    | フラッシュメモリ版とマスクROM版の相違点 .....       | 364        |

| 23.14    | マスクROM版 .....                     | 365        |

| 23.15    | フラッシュメモリ版 .....                   | 366        |

| 23.15.1  | フラッシュメモリ書き換え禁止機能 .....            | 366        |

| 23.15.2  | ストップモード .....                     | 366        |

| 23.15.3  | ウェイトモード .....                     | 366        |

| 23.15.4  | 低消費電力モード、オンチップオシレータ低消費電力モード ..... | 366        |

| 23.15.5  | コマンド、データの書き込み .....               | 366        |

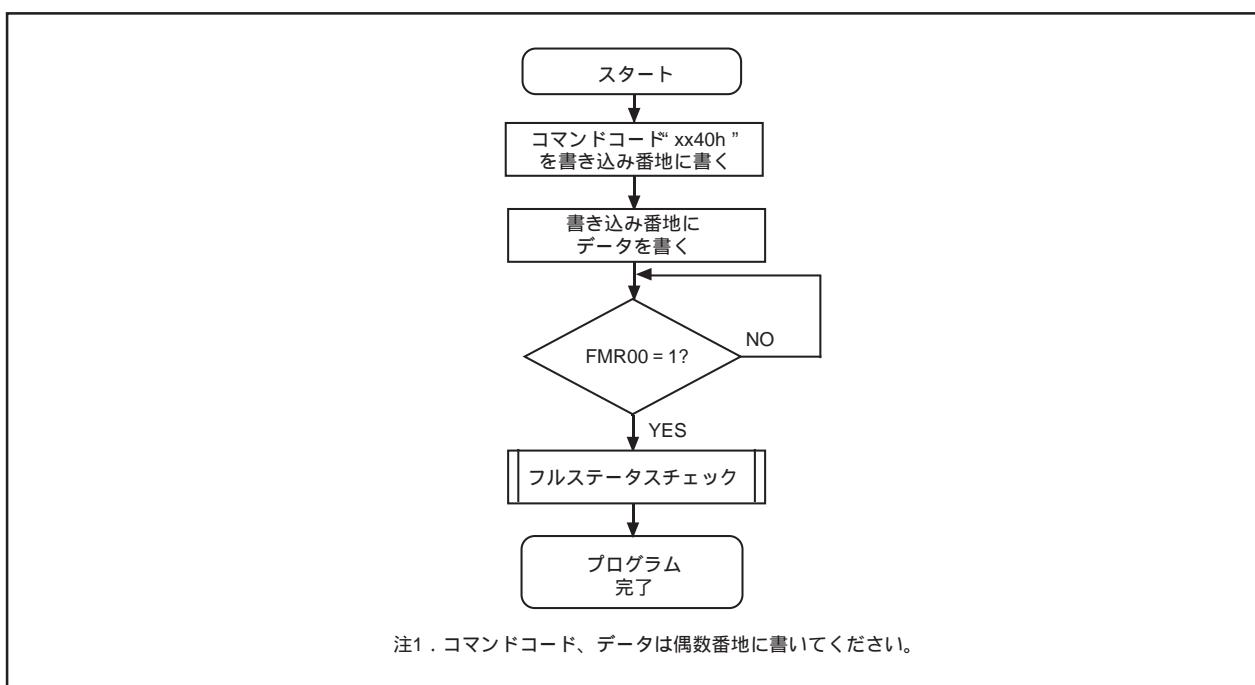

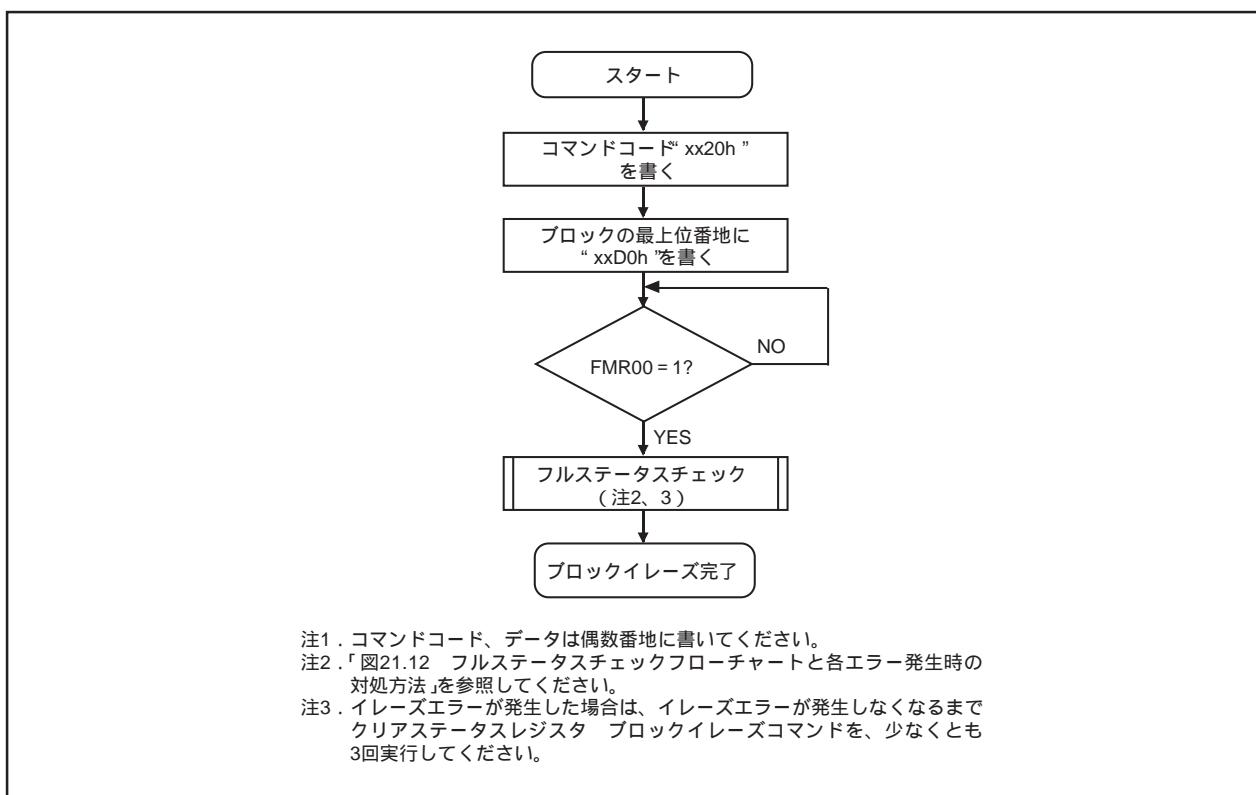

| 23.15.6  | プログラムコマンド .....                   | 366        |

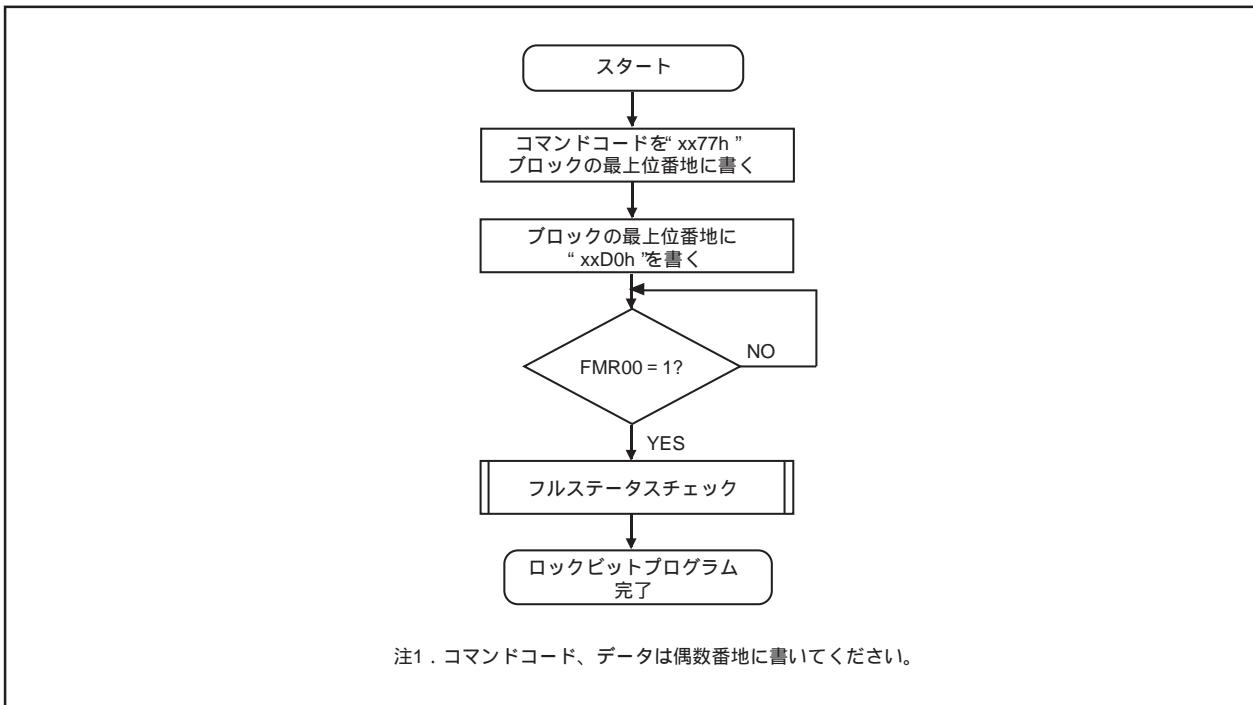

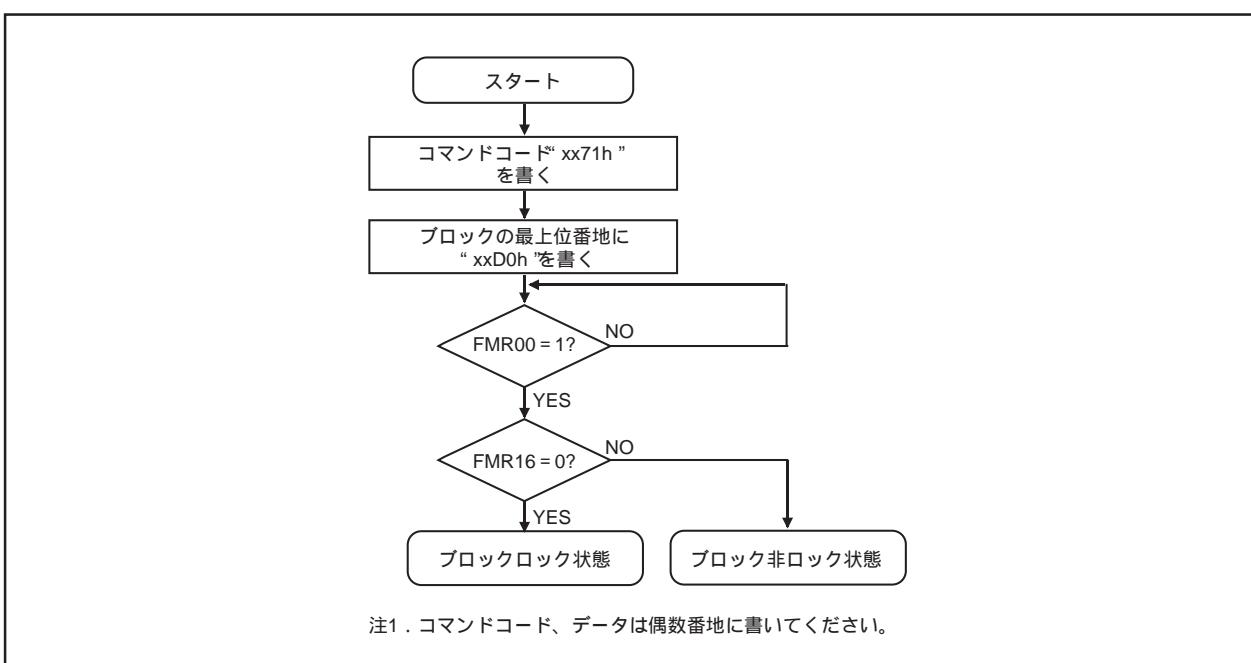

| 23.15.7  | ロックビットプログラムコマンド .....             | 366        |

| 23.15.8  | 動作速度 .....                        | 366        |

| 23.15.9  | 使用禁止命令 .....                      | 367        |

| 23.15.10 | 割り込み .....                        | 367        |

| 23.15.11 | アクセス方法 .....                      | 367        |

| 23.15.12 | ユーザROM領域の書き換え .....               | 367        |

| 23.15.13 | DMA転送 .....                       | 367        |

| 23.16    | 標準ブートプログラムによるフラッシュメモリ書き込み .....   | 368        |

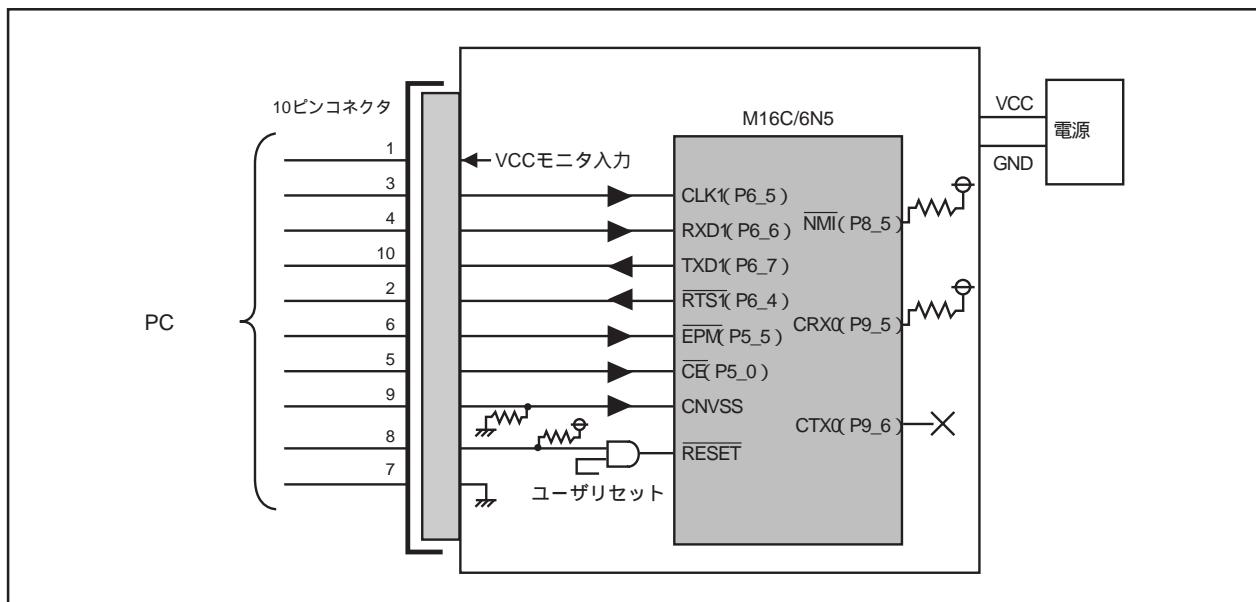

| 23.16.1  | シリアルを利用した書き込みを行う場合 .....          | 368        |

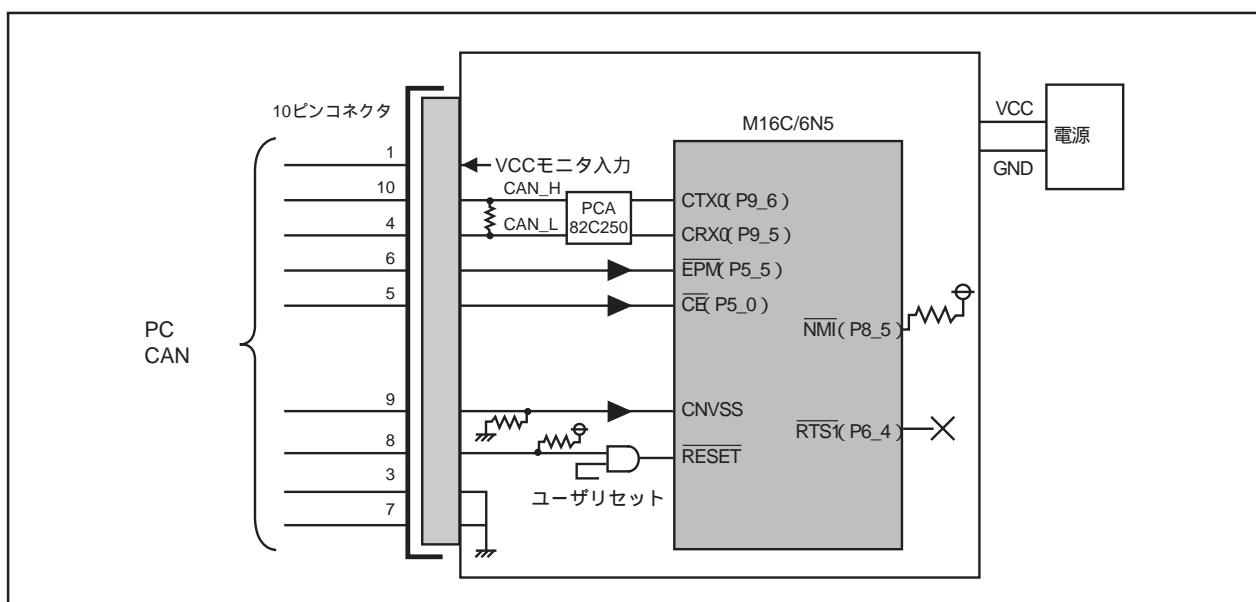

| 23.16.2  | CANを利用した書き込みを行う場合 .....           | 368        |

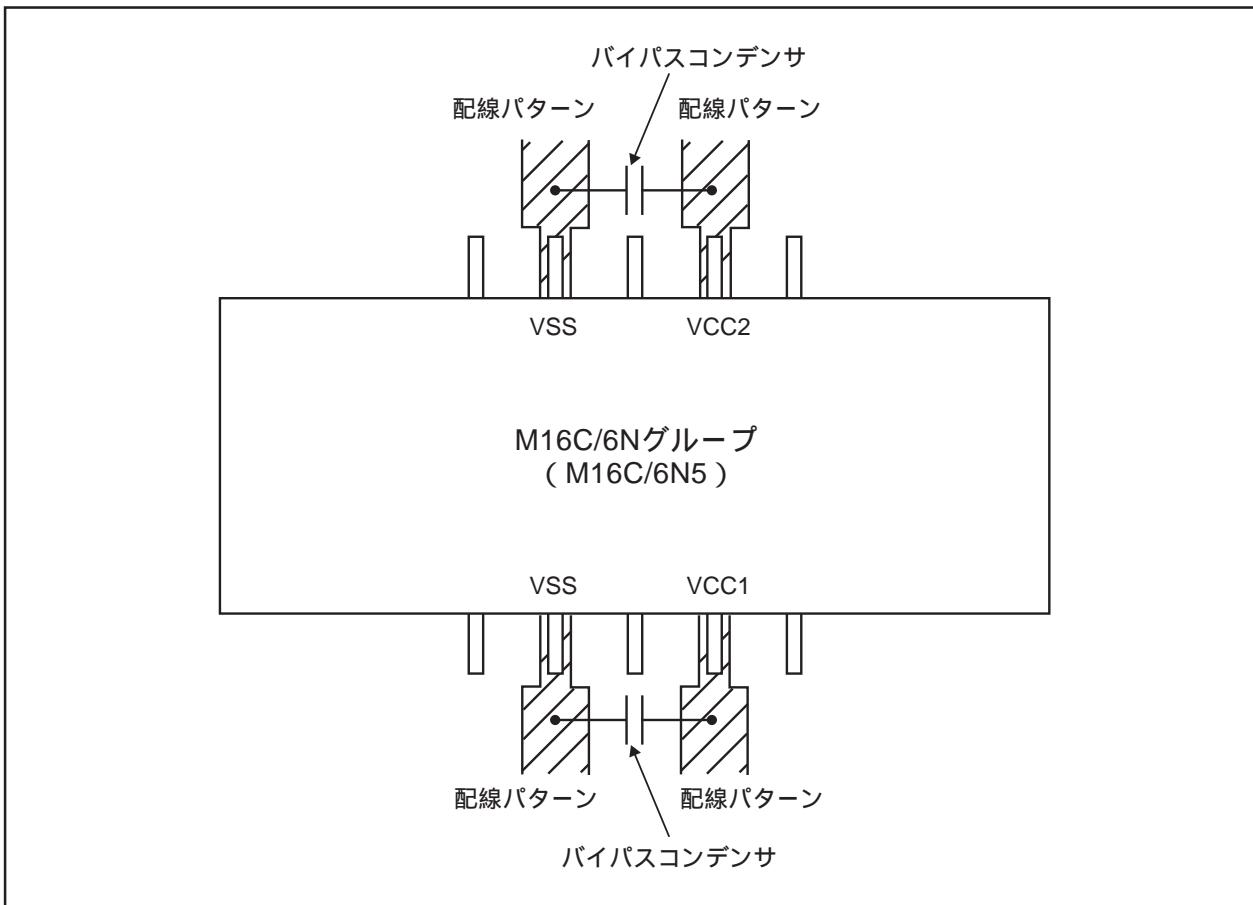

| 23.17    | ノイズ .....                         | 369        |

|          | <b>付録1. 外形寸法図 .....</b>           | <b>370</b> |

|          | <b>レジスタ索引 .....</b>               | <b>371</b> |

本資料はできる限り正確を期すよう努力をしておりますが、誤記がありましたときはご容赦ください。

また、機能向上や性能向上のために仕様を変更する場合がありますので、最新版をご使用ください。

## 番地別ページ早見表

| 番地    | レジスタ               | シンボル   | 掲載ページ |

|-------|--------------------|--------|-------|

| 0000h |                    |        |       |

| 0001h |                    |        |       |

| 0002h |                    |        |       |

| 0003h |                    |        |       |

| 0004h | プロセッサモードレジスタ0      | PM0    | 31    |

| 0005h | プロセッサモードレジスタ1      | PM1    | 32    |

| 0006h | システムクロック制御レジスタ0    | CM0    | 48    |

| 0007h | システムクロック制御レジスタ1    | CM1    | 49    |

| 0008h | チップセレクト制御レジスタ      | CSR    | 36    |

| 0009h | アドレス一致割り込み許可レジスタ   | AIER   | 87    |

| 000Ah | プロテクトレジスタ          | PRCR   | 69    |

| 000Bh |                    |        |       |

| 000Ch | 発振停止検出レジスタ         | CM2    | 50    |

| 000Dh |                    |        |       |

| 000Eh | ウォッチドッグタイマスタートレジスタ | WDTS   | 89    |

| 000Fh | ウォッチドッグタイマ制御レジスタ   | WDC    | 89    |

| 0010h |                    |        |       |

| 0011h | アドレス一致割り込みレジスタ0    | RMAD0  | 87    |

| 0012h |                    |        |       |

| 0013h |                    |        |       |

| 0014h |                    |        |       |

| 0015h | アドレス一致割り込みレジスタ1    | RMAD1  | 87    |

| 0016h |                    |        |       |

| 0017h |                    |        |       |

| 0018h |                    |        |       |

| 0019h |                    |        |       |

| 001Ah |                    |        |       |

| 001Bh | チップセレクト拡張制御レジスタ    | CSE    | 42    |

| 001Ch | PLL制御レジスタ0         | PLC0   | 52    |

| 001Dh |                    |        |       |

| 001Eh | プロセッサモードレジスタ2      | PM2    | 52    |

| 001Fh |                    |        |       |

| 0020h |                    |        |       |

| 0021h | DMA0ソースポインタ        | SAR0   | 94    |

| 0022h |                    |        |       |

| 0023h |                    |        |       |

| 0024h |                    |        |       |

| 0025h | DMA0ディスティネーションポインタ | DAR0   | 94    |

| 0026h |                    |        |       |

| 0027h |                    |        |       |

| 0028h | DMA0転送カウンタ         | TCR0   | 94    |

| 0029h |                    |        |       |

| 002Ah |                    |        |       |

| 002Bh |                    |        |       |

| 002Ch | DMA0制御レジスタ         | DM0CON | 93    |

| 002Dh |                    |        |       |

| 002Eh |                    |        |       |

| 002Fh |                    |        |       |

| 0030h |                    |        |       |

| 0031h | DMA1ソースポインタ        | SAR1   | 94    |

| 0032h |                    |        |       |

| 0033h |                    |        |       |

| 0034h |                    |        |       |

| 0035h | DMA1ディスティネーションポインタ | DAR1   | 94    |

| 0036h |                    |        |       |

| 0037h |                    |        |       |

| 0038h | DMA1転送カウンタ         | TCR1   | 94    |

| 0039h |                    |        |       |

| 003Ah |                    |        |       |

| 003Bh |                    |        |       |

| 003Ch | DMA1制御レジスタ         | DM1CON | 93    |

| 003Dh |                    |        |       |

| 003Eh |                    |        |       |

| 003Fh |                    |        |       |

空欄はすべて予約領域です。

| 番地    | レジスタ                     | シンボル     | 掲載ページ |

|-------|--------------------------|----------|-------|

| 0040h |                          |          |       |

| 0041h | CAN0ウェイクアップ割り込み制御レジスタ    | C01WKIC  | 75    |

| 0042h | CAN0受信完了割り込み制御レジスタ       | C0RECIC  | 75    |

| 0043h | CAN0送信完了割り込み制御レジスタ       | C0TRMIC  | 75    |

| 0044h | INT3割り込み制御レジスタ           | INT3IC   | 76    |

| 0045h | タイマB5割り込み制御レジスタ          | TB5IC    | 75    |

| 0046h | タイマB4割り込み制御レジスタ          | TB4IC    | 75    |

| 0047h | UART1バス衝突検出割り込み制御レジスタ    | U1BCNIC  | 75    |

| 0048h | UART0バス衝突検出割り込み制御レジスタ    | U0BCNIC  | 75    |

| 0049h | INT5割り込み制御レジスタ           | INT5IC   | 76    |

| 004Ah | SI/O3割り込み制御レジスタ          | S3IC     | 76    |

| 004Bh | INT4割り込み制御レジスタ           | INT4IC   | 76    |

| 004Ch | UART2バス衝突検出割り込み制御レジスタ    | U2BCNIC  | 75    |

| 004Dh | DMA0割り込み制御レジスタ           | DM0IC    | 75    |

| 004Eh | DMA1割り込み制御レジスタ           | DM1IC    | 75    |

| 004Fh | CAN0ストート、エラー割り込み制御レジスタ   | C01ERRIC | 75    |

| 0050h | A/D変換割り込み制御レジスタ          | ADIC     | 75    |

| 0051h | キー入力割り込み制御レジスタ           | KUPIC    | 75    |

| 0052h | UART0受信割り込み制御レジスタ        | S0RIC    | 75    |

| 0053h | UART1送信割り込み制御レジスタ        | S1TIC    | 75    |

| 0054h | UART1受信割り込み制御レジスタ        | S1RIC    | 75    |

| 0055h | タイマA0割り込み制御レジスタ          | TA0IC    | 75    |

| 0056h | タイマA1割り込み制御レジスタ          | TA1IC    | 75    |

| 0057h | タイマA2割り込み制御レジスタ          | TA2IC    | 75    |

| 0058h | タイマA3割り込み制御レジスタ          | TA3IC    | 75    |

| 0059h | タイマA4割り込み制御レジスタ          | TA4IC    | 75    |

| 005Ah | タイマB0割り込み制御レジスタ          | TB0IC    | 75    |

| 005Bh | タイマB1割り込み制御レジスタ          | TB1IC    | 75    |

| 005Ch | タイマB2割り込み制御レジスタ          | TB2IC    | 75    |

| 005Dh | INT0割り込み制御レジスタ           | INT0IC   | 76    |

| 005Eh | INT1割り込み制御レジスタ           | INT1IC   | 76    |

| 005Fh | INT2割り込み制御レジスタ           | INT2IC   | 76    |

| 0060h |                          |          |       |

| 0061h |                          |          |       |

| 0062h |                          |          |       |

| 0063h | CAN0スロット0 : メッセージ識別子/DLC |          |       |

| 0064h |                          |          |       |

| 0065h |                          |          |       |

| 0066h |                          |          |       |

| 0067h |                          |          |       |

| 0068h |                          |          |       |

| 0069h | CAN0スロット0 : データフィールド     |          |       |

| 006Ah |                          |          |       |

| 006Bh |                          |          |       |

| 006Ch |                          |          |       |

| 006Dh |                          |          |       |

| 006Eh | CAN0スロット0 : タイムスタンプ      |          |       |

| 006Fh |                          |          |       |

| 0070h |                          |          |       |

| 0071h |                          |          |       |

| 0072h | CAN0スロット1 : メッセージ識別子/DLC |          |       |

| 0073h |                          |          |       |

| 0074h |                          |          |       |

| 0075h |                          |          |       |

| 0076h |                          |          |       |

| 0077h |                          |          |       |

| 0078h |                          |          |       |

| 0079h | CAN0スロット1 : データフィールド     |          |       |

| 007Ah |                          |          |       |

| 007Bh |                          |          |       |

| 007Ch |                          |          |       |

| 007Dh |                          |          |       |

| 007Eh | CAN0スロット1 : タイムスタンプ      |          |       |

| 007Fh |                          |          |       |

211

212

| 番地    | レジスタ                     | シンボル | 掲載ページ | 番地    | レジスタ                     | シンボル | 掲載ページ |

|-------|--------------------------|------|-------|-------|--------------------------|------|-------|

| 0080h | CAN0スロット2 : メッセージ識別子/DLC |      |       | 00C0h | CAN0スロット6 : メッセージ識別子/DLC |      |       |

| 0081h |                          |      |       | 00C1h |                          |      |       |

| 0082h |                          |      |       | 00C2h |                          |      |       |

| 0083h |                          |      |       | 00C3h |                          |      |       |

| 0084h |                          |      |       | 00C4h |                          |      |       |

| 0085h |                          |      |       | 00C5h |                          |      |       |

| 0086h | CAN0スロット2 : データフィールド     |      |       | 00C6h |                          |      |       |

| 0087h |                          |      |       | 00C7h |                          |      |       |

| 0088h |                          |      |       | 00C8h |                          |      |       |

| 0089h |                          |      |       | 00C9h | CAN0スロット6 : データフィールド     |      |       |

| 008Ah |                          |      |       | 00CAh |                          |      |       |

| 008Bh |                          |      |       | 00CBh |                          |      |       |

| 008Ch |                          |      |       | 00CCh |                          |      |       |

| 008Dh |                          |      |       | 00CDh |                          |      |       |

| 008Eh | CAN0スロット2 : タイムスタンプ      |      |       | 00CEh | CAN0スロット6 : タイムスタンプ      |      |       |

| 008Fh |                          |      |       | 00CFh |                          |      |       |

| 0090h | CAN0スロット3 : メッセージ識別子/DLC |      |       | 00D0h |                          |      |       |

| 0091h |                          |      |       | 00D1h |                          |      |       |

| 0092h |                          |      |       | 00D2h | CAN0スロット7 : メッセージ識別子/DLC |      |       |

| 0093h |                          |      |       | 00D3h |                          |      |       |

| 0094h |                          |      |       | 00D4h |                          |      |       |

| 0095h |                          |      |       | 00D5h |                          |      |       |

| 0096h | CAN0スロット3 : データフィールド     |      |       | 00D6h |                          |      |       |

| 0097h |                          |      |       | 00D7h |                          |      |       |

| 0098h |                          |      |       | 00D8h |                          |      |       |

| 0099h |                          |      |       | 00D9h | CAN0スロット7 : データフィールド     |      |       |

| 009Ah |                          |      |       | 00DAh |                          |      |       |

| 009Bh |                          |      |       | 00DBh |                          |      |       |

| 009Ch |                          |      |       | 00DCh |                          |      |       |

| 009Dh |                          |      |       | 00DDh |                          |      |       |

| 009Eh | CAN0スロット3 : タイムスタンプ      |      |       | 00DEh | CAN0スロット7 : タイムスタンプ      |      |       |

| 009Fh |                          |      |       | 00DFh |                          |      |       |

| 00A0h | CAN0スロット4 : メッセージ識別子/DLC |      |       | 00E0h | CAN0スロット8 : メッセージ識別子/DLC |      |       |

| 00A1h |                          |      |       | 00E1h |                          |      |       |

| 00A2h |                          |      |       | 00E2h |                          |      |       |

| 00A3h |                          |      |       | 00E3h |                          |      |       |

| 00A4h |                          |      |       | 00E4h |                          |      |       |

| 00A5h |                          |      |       | 00E5h |                          |      |       |

| 00A6h | CAN0スロット4 : データフィールド     |      |       | 00E6h |                          |      |       |

| 00A7h |                          |      |       | 00E7h |                          |      |       |

| 00A8h |                          |      |       | 00E8h |                          |      |       |

| 00A9h |                          |      |       | 00E9h | CAN0スロット8 : データフィールド     |      |       |

| 00AAh |                          |      |       | 00EAh |                          |      |       |

| 00ABh |                          |      |       | 00EBh |                          |      |       |

| 00ACh |                          |      |       | 00ECh |                          |      |       |

| 00ADh |                          |      |       | 00EDh |                          |      |       |

| 00AEh | CAN0スロット4 : タイムスタンプ      |      |       | 00EEh | CAN0スロット8 : タイムスタンプ      |      |       |

| 00AFh |                          |      |       | 00EFh |                          |      |       |

| 00B0h | CAN0スロット5 : メッセージ識別子/DLC |      |       | 00F0h |                          |      |       |

| 00B1h |                          |      |       | 00F1h |                          |      |       |

| 00B2h |                          |      |       | 00F2h | CAN0スロット9 : メッセージ識別子/DLC |      |       |

| 00B3h |                          |      |       | 00F3h |                          |      |       |

| 00B4h |                          |      |       | 00F4h |                          |      |       |

| 00B5h |                          |      |       | 00F5h |                          |      |       |

| 00B6h | CAN0スロット5 : データフィールド     |      |       | 00F6h |                          |      |       |

| 00B7h |                          |      |       | 00F7h |                          |      |       |

| 00B8h |                          |      |       | 00F8h |                          |      |       |

| 00B9h |                          |      |       | 00F9h | CAN0スロット9 : データフィールド     |      |       |

| 00BAh |                          |      |       | 00FAh |                          |      |       |

| 00BBh |                          |      |       | 00FBh |                          |      |       |

| 00BCh |                          |      |       | 00FCh |                          |      |       |

| 00BDh |                          |      |       | 00FDh |                          |      |       |

| 00BEh | CAN0スロット5 : タイムスタンプ      |      |       | 00FEh | CAN0スロット9 : タイムスタンプ      |      |       |

| 00BFh |                          |      |       | 00FFh |                          |      |       |

| 番地    | レジスタ                      | シンボル | 掲載ページ |

|-------|---------------------------|------|-------|

| 0100h | CAN0スロット10 : メッセージ識別子/DLC |      |       |

| 0101h |                           |      |       |

| 0102h |                           |      |       |

| 0103h |                           |      |       |

| 0104h |                           |      |       |

| 0105h |                           |      |       |

| 0106h | CAN0スロット10 : データフィールド     |      |       |

| 0107h |                           |      |       |

| 0108h |                           |      |       |

| 0109h |                           |      |       |

| 010Ah |                           |      |       |

| 010Bh |                           |      |       |

| 010Ch |                           |      |       |

| 010Dh |                           |      |       |

| 010Eh | CAN0スロット10 : タイムスタンプ      |      |       |

| 010Fh |                           |      |       |

| 0110h | CAN0スロット11 : メッセージ識別子/DLC |      |       |

| 0111h |                           |      |       |

| 0112h |                           |      |       |

| 0113h |                           |      |       |

| 0114h |                           |      |       |

| 0115h |                           |      |       |

| 0116h | CAN0スロット11 : データフィールド     |      |       |

| 0117h |                           |      |       |

| 0118h |                           |      |       |

| 0119h |                           |      |       |

| 011Ah |                           |      |       |

| 011Bh |                           |      |       |

| 011Ch |                           |      |       |

| 011Dh |                           |      |       |

| 011Eh | CAN0スロット11 : タイムスタンプ      |      |       |

| 011Fh |                           |      |       |

| 0120h | CAN0スロット12 : メッセージ識別子/DLC |      |       |

| 0121h |                           |      |       |

| 0122h |                           |      |       |

| 0123h |                           |      |       |

| 0124h |                           |      |       |

| 0125h |                           |      |       |

| 0126h | CAN0スロット12 : データフィールド     |      |       |

| 0127h |                           |      |       |

| 0128h |                           |      |       |

| 0129h |                           |      |       |

| 012Ah |                           |      |       |

| 012Bh |                           |      |       |

| 012Ch |                           |      |       |

| 012Dh |                           |      |       |

| 012Eh | CAN0スロット12 : タイムスタンプ      |      |       |

| 012Fh |                           |      |       |

| 0130h | CAN0スロット13 : メッセージ識別子/DLC |      |       |

| 0131h |                           |      |       |

| 0132h |                           |      |       |

| 0133h |                           |      |       |

| 0134h |                           |      |       |

| 0135h |                           |      |       |

| 0136h | CAN0スロット13 : データフィールド     |      |       |

| 0137h |                           |      |       |

| 0138h |                           |      |       |

| 0139h |                           |      |       |

| 013Ah |                           |      |       |

| 013Bh |                           |      |       |

| 013Ch |                           |      |       |

| 013Dh |                           |      |       |

| 013Eh | CAN0スロット13 : タイムスタンプ      |      |       |

| 013Fh |                           |      |       |

空欄はすべて予約領域です。

| 番地    | レジスタ                      | シンボル   | 掲載ページ |

|-------|---------------------------|--------|-------|

| 0140h | CAN0スロット14 : メッセージ識別子/DLC |        |       |

| 0141h |                           |        |       |

| 0142h |                           |        |       |

| 0143h |                           |        |       |

| 0144h |                           |        |       |

| 0145h |                           |        |       |

| 0146h | CAN0スロット14 : データフィールド     |        |       |

| 0147h |                           |        |       |

| 0148h |                           |        |       |

| 0149h |                           |        |       |

| 014Ah |                           |        |       |

| 014Bh |                           |        |       |

| 014Ch |                           |        |       |

| 014Dh |                           |        |       |

| 014Eh | CAN0スロット14 : タイムスタンプ      |        |       |

| 014Fh |                           |        |       |

| 0150h | CAN0スロット15 : メッセージ識別子/DLC |        |       |

| 0151h |                           |        |       |

| 0152h |                           |        |       |

| 0153h |                           |        |       |

| 0154h |                           |        |       |

| 0155h |                           |        |       |

| 0156h | CAN0スロット15 : データフィールド     |        |       |

| 0157h |                           |        |       |

| 0158h |                           |        |       |

| 0159h |                           |        |       |

| 015Ah |                           |        |       |

| 015Bh |                           |        |       |

| 015Ch |                           |        |       |

| 015Dh |                           |        |       |

| 015Eh | CAN0スロット15 : タイムスタンプ      |        |       |

| 015Fh |                           |        |       |

| 0160h | CAN0グローバルマスクレジスタ          | C0GMR  | 213   |

| 0161h |                           |        |       |

| 0162h |                           |        |       |

| 0163h |                           |        |       |

| 0164h |                           |        |       |

| 0165h |                           |        |       |

| 0166h | CAN0ローカルマスクAレジスタ          | C0LMAR | 213   |

| 0167h |                           |        |       |

| 0168h |                           |        |       |

| 0169h |                           |        |       |

| 016Ah |                           |        |       |

| 016Bh |                           |        |       |

| 016Ch |                           |        |       |

| 016Dh |                           |        |       |

| 016Eh | CAN0ローカルマスクBレジスタ          | C0LMBR | 213   |

| 016Fh |                           |        |       |

| 0170h |                           |        |       |

| 0171h |                           |        |       |

| 0172h |                           |        |       |

| 0173h |                           |        |       |

| 0174h |                           |        |       |

| 0175h |                           |        |       |

| 0176h |                           |        |       |

| 0177h |                           |        |       |

| 0178h |                           |        |       |

| 0179h |                           |        |       |

| 017Ah |                           |        |       |

| 017Bh |                           |        |       |

| 017Ch |                           |        |       |

| 017Dh |                           |        |       |

| 017Eh |                           |        |       |

| 017Fh |                           |        |       |

| 番地    | レジスタ              | シンボル  | 掲載ページ |

|-------|-------------------|-------|-------|

| 0180h |                   |       |       |

| 0181h |                   |       |       |

| 0182h |                   |       |       |

| 0183h |                   |       |       |

| 0184h |                   |       |       |

| 0185h |                   |       |       |

| 0186h |                   |       |       |

| 0187h |                   |       |       |

| 0188h |                   |       |       |

| 0189h |                   |       |       |

| 018Ah |                   |       |       |

| 018Bh |                   |       |       |

| 018Ch |                   |       |       |

| 018Dh |                   |       |       |

| 018Eh |                   |       |       |

| 018Fh |                   |       |       |

| 0190h |                   |       |       |

| 0191h |                   |       |       |

| 0192h |                   |       |       |

| 0193h |                   |       |       |

| 0194h |                   |       |       |

| 0195h |                   |       |       |

| 0196h |                   |       |       |

| 0197h |                   |       |       |

| 0198h |                   |       |       |

| 0199h |                   |       |       |

| 019Ah |                   |       |       |

| 019Bh |                   |       |       |

| 019Ch |                   |       |       |

| 019Dh |                   |       |       |

| 019Eh |                   |       |       |

| 019Fh |                   |       |       |

| 01A0h |                   |       |       |

| 01A1h |                   |       |       |

| 01A2h |                   |       |       |

| 01A3h |                   |       |       |

| 01A4h |                   |       |       |

| 01A5h |                   |       |       |

| 01A6h |                   |       |       |

| 01A7h |                   |       |       |

| 01A8h |                   |       |       |

| 01A9h |                   |       |       |

| 01AAh |                   |       |       |

| 01ABh |                   |       |       |

| 01ACh |                   |       |       |

| 01ADh |                   |       |       |

| 01AEh |                   |       |       |

| 01AFh |                   |       |       |

| 01B0h |                   |       |       |

| 01B1h |                   |       |       |

| 01B2h |                   |       |       |

| 01B3h |                   |       |       |

| 01B4h |                   |       |       |

| 01B5h | フラッシュメモリ制御レジスタ1   | FMR1  | 253   |

| 01B6h |                   |       |       |

| 01B7h | フラッシュメモリ制御レジスタ0   | FMR0  | 253   |

| 01B8h |                   |       |       |

| 01B9h | アドレス一致割り込みレジスタ2   | RMAD2 | 87    |

| 01BAh |                   |       |       |

| 01BBh | アドレス一致割り込み許可レジスタ2 | AIER2 | 87    |

| 01BCh |                   |       |       |

| 01BDh | アドレス一致割り込みレジスタ3   | RMAD3 | 87    |

| 01BEh |                   |       |       |

| 01BFh |                   |       |       |

空欄はすべて予約領域です。

| 番地     | レジスタ                   | シンボル   | 掲載ページ |

|--------|------------------------|--------|-------|

| 01C0h  | タイマB3, B4, B5カウント開始フラグ | TBSR   | 119   |

| 01C1h  |                        |        |       |

| 01C2h  | タイマA1-1レジスタ            | TA11   | 130   |

| 01C3h  |                        |        |       |

| 01C4h  | タイマA2-1レジスタ            | TA21   | 130   |

| 01C5h  |                        |        |       |

| 01C6h  | タイマA4-1レジスタ            | TA41   | 130   |

| 01C7h  |                        |        |       |

| 01C8h  | 三相PWM制御レジスタ0           | INVC0  | 127   |

| 01C9h  | 三相PWM制御レジスタ1           | INVC1  | 128   |

| 01CAh  | 三相出力パッファレジスタ0          | IDB0   | 129   |

| 01CBh  | 三相出力パッファレジスタ1          | IDB1   | 129   |

| 01CCh  | 短絡防止タイマ                | DTT    | 129   |

| 01CDh  | タイマB2割り込み発生頻度設定カウンタ    | ICTB2  | 131   |

| 01CEh  |                        |        |       |

| 01CFh  |                        |        |       |

| 01D0h  | タイマB3レジスタ              | TB3    | 118   |

| 01D1h  |                        |        |       |

| 01D2h  | タイマB4レジスタ              | TB4    | 118   |

| 01D3h  |                        |        |       |

| 01D4h  | タイマB5レジスタ              | TB5    | 118   |

| 01D5h  |                        |        |       |

| 01D6h  |                        |        |       |

| 01D7h  |                        |        |       |

| 01D8h  |                        |        |       |

| 01D9h  |                        |        |       |

| 01DAh  |                        |        |       |

| 01DBh  | タイマB3モードレジスタ           | TB3MR  | 118   |

| 01DCh  | タイマB4モードレジスタ           | TB4MR  | 120   |

| 01DDh  | タイマB5モードレジスタ           | TB5MR  | 121   |

| 01DEh  | 割り込み要因選択レジスタ0          | IFSR0  | 123   |

| 01DFh  | 割り込み要因選択レジスタ1          | IFSR1  | 84    |

| 01E0h  | SI/O3送受信レジスタ           | S3TRR  | 84    |

| 01E1h  |                        |        |       |

| 01E2h  | SI/O3制御レジスタ            | S3C    | 184   |

| 01E3h  | SI/O3ピットレートレジスタ        | S3BRG  | 184   |

| 01E4h  |                        |        |       |

| 01E5h  |                        |        |       |

| 01E6h  |                        |        |       |

| 01E7h  |                        |        |       |

| 01E8h  |                        |        |       |

| 01E9h  |                        |        |       |

| 01EAh  |                        |        |       |

| 01EBh  |                        |        |       |

| 01ECh  | UART0特殊モードレジスタ4        | U0SMR4 | 145   |

| 01EDh  | UART0特殊モードレジスタ3        | U0SMR3 | 144   |

| 01EEh  | UART0特殊モードレジスタ2        | U0SMR2 | 144   |

| 01EFh  | UART0特殊モードレジスタ         | U0SMR  | 143   |

| 01F0h  | UART1特殊モードレジスタ4        | U1SMR4 | 145   |

| 01F1h  | UART1特殊モードレジスタ3        | U1SMR3 | 144   |

| 01F2h  | UART1特殊モードレジスタ2        | U1SMR2 | 144   |

| 01F3h  | UART1特殊モードレジスタ         | U1SMR  | 143   |

| 01F4h  | UART2特殊モードレジスタ4        | U2SMR4 | 145   |

| 01F5h  | UART2特殊モードレジスタ3        | U2SMR3 | 144   |

| 01F6h  | UART2特殊モードレジスタ2        | U2SMR2 | 144   |

| 01F7h  | UART2特殊モードレジスタ         | U2SMR  | 143   |

| 01F8h  | UART2送受信モードレジスタ        | U2MR   | 141   |

| 01F9h  | UART2ピットレートレジスタ        | U2BRG  | 140   |

| 01FAh  | UART2送信バッファレジスタ        | U2TB   | 140   |

| 01FBh  |                        |        |       |

| 01FCCh | UART2送受信制御レジスタ0        | U2C0   | 141   |

| 01FDh  | UART2送受信制御レジスタ1        | U2C1   | 142   |

| 01FEh  | UART2受信バッファレジスタ        | U2RB   | 140   |

| 01FFh  |                        |        |       |

| 番地    | レジスタ              | シンボル     | 掲載ページ |

|-------|-------------------|----------|-------|

| 0200h | CAN0メッセージ制御レジスタ0  | C0MCTL0  | 214   |

| 0201h | CAN0メッセージ制御レジスタ1  | C0MCTL1  |       |

| 0202h | CAN0メッセージ制御レジスタ2  | C0MCTL2  |       |

| 0203h | CAN0メッセージ制御レジスタ3  | C0MCTL3  |       |

| 0204h | CAN0メッセージ制御レジスタ4  | C0MCTL4  |       |

| 0205h | CAN0メッセージ制御レジスタ5  | C0MCTL5  |       |

| 0206h | CAN0メッセージ制御レジスタ6  | C0MCTL6  |       |

| 0207h | CAN0メッセージ制御レジスタ7  | C0MCTL7  |       |

| 0208h | CAN0メッセージ制御レジスタ8  | C0MCTL8  |       |

| 0209h | CAN0メッセージ制御レジスタ9  | C0MCTL9  |       |

| 020Ah | CAN0メッセージ制御レジスタ10 | C0MCTL10 |       |

| 020Bh | CAN0メッセージ制御レジスタ11 | C0MCTL11 |       |

| 020Ch | CAN0メッセージ制御レジスタ12 | C0MCTL12 |       |

| 020Dh | CAN0メッセージ制御レジスタ13 | C0MCTL13 |       |

| 020Eh | CAN0メッセージ制御レジスタ14 | C0MCTL14 |       |

| 020Fh | CAN0メッセージ制御レジスタ15 | C0MCTL15 |       |

| 0210h | CAN0制御レジスタ        | C0CTLR   | 215   |

| 0211h |                   |          |       |

| 0212h | CAN0ステータスレジスタ     | C0STR    | 217   |

| 0213h |                   |          |       |

| 0214h | CAN0スロットステータスレジスタ | C0SSTR   | 218   |

| 0215h |                   |          |       |

| 0216h | CAN0割り込み制御レジスタ    | C0ICR    | 218   |

| 0217h |                   |          |       |

| 0218h | CAN0拡張IDレジスタ      | C0IDR    | 218   |

| 0219h |                   |          |       |

| 021Ah | CAN0パステイミング制御レジスタ | C0CONR   | 219   |

| 021Bh |                   |          |       |

| 021Ch | CAN0受信エラーカウントレジスタ | C0RECR   | 220   |

| 021Dh | CAN0送信エラーカウントレジスタ | C0TECR   | 220   |

| 021Eh |                   |          |       |

| 021Fh | CAN0タイムスタンプレジスタ   | C0TSR    | 220   |

| 0220h |                   |          |       |

| 0221h |                   |          |       |

| 0222h |                   |          |       |

| 0223h |                   |          |       |

| 0224h |                   |          |       |

| 0225h |                   |          |       |

| 0226h |                   |          |       |

| 0227h |                   |          |       |

| 0228h |                   |          |       |

| 0229h |                   |          |       |

| 022Ah |                   |          |       |

| 022Bh |                   |          |       |

| 022Ch |                   |          |       |

| 022Dh |                   |          |       |

| 022Eh |                   |          |       |

| 022Fh |                   |          |       |

| 0230h | CAN1制御レジスタ        | C1CTLR   | 216   |

| 0231h |                   |          |       |

| 0232h |                   |          |       |

| 0233h |                   |          |       |

| 0234h |                   |          |       |

| 0235h |                   |          |       |

| 0236h |                   |          |       |

| 0237h |                   |          |       |

| 0238h |                   |          |       |

| 0239h |                   |          |       |

| 023Ah |                   |          |       |

| 023Bh |                   |          |       |

| 023Ch |                   |          |       |

| 023Dh |                   |          |       |

| 023Eh |                   |          |       |

| 023Fh |                   |          |       |

空欄はすべて予約領域です。

| 番地    | レジスタ                    | シンボル  | 掲載ページ |

|-------|-------------------------|-------|-------|

| 0240h |                         |       |       |

| 0241h |                         |       |       |

| 0242h | CAN0アクセプタンスフィルタサポートレジスタ | C0AFS | 220   |

| 0243h |                         |       |       |

| 0244h |                         |       |       |

| 0245h |                         |       |       |

| 0246h |                         |       |       |

| 0247h |                         |       |       |

| 0248h |                         |       |       |

| 0249h |                         |       |       |

| 024Ah |                         |       |       |

| 024Bh |                         |       |       |

| 024Ch |                         |       |       |

| 024Dh |                         |       |       |

| 024Eh |                         |       |       |

| 024Fh |                         |       |       |

| 0250h |                         |       |       |

| 0251h |                         |       |       |

| 0252h |                         |       |       |

| 0253h |                         |       |       |

| 0254h |                         |       |       |

| 0255h |                         |       |       |

| 0256h |                         |       |       |

| 0257h |                         |       |       |

| 0258h |                         |       |       |

| 0259h |                         |       |       |

| 025Ah |                         |       |       |

| 025Bh |                         |       |       |

| 025Ch |                         |       |       |

| 025Dh |                         |       |       |

| 025Eh | 周辺クロック選択レジスタ            | PCLKR | 51    |

| 025Fh | CAN0クロック選択レジスタ          | CCLKR | 51    |

| 0260h |                         |       |       |

| 0261h |                         |       |       |

| 0262h |                         |       |       |

| 0263h |                         |       |       |

| 0264h |                         |       |       |

| 0265h |                         |       |       |

| 0266h |                         |       |       |

| 0267h |                         |       |       |

| 0268h |                         |       |       |

| 0269h |                         |       |       |

| 026Ah |                         |       |       |

| 026Bh |                         |       |       |

| 026Ch |                         |       |       |

| 026Dh |                         |       |       |

| 026Eh |                         |       |       |

| 026Fh |                         |       |       |

| 0270h |                         |       |       |

| 0372h |                         |       |       |

| 0373h |                         |       |       |

| 0374h |                         |       |       |

| 0375h |                         |       |       |

| 0376h |                         |       |       |

| 0377h |                         |       |       |

| 0378h |                         |       |       |

| 0379h |                         |       |       |

| 037Ah |                         |       |       |

| 037Bh |                         |       |       |

| 037Ch |                         |       |       |

| 037Dh |                         |       |       |

| 037Eh |                         |       |       |

| 037Fh |                         |       |       |

| 番地    | レジスタ             | シンポル  | 掲載ページ          |

|-------|------------------|-------|----------------|

| 0380h | カウント開始フラグ        | TABSR | 104,119,132    |

| 0381h | 時計用ブリスケーラリセットフラグ | CPSRF | 105,119        |

| 0382h | ワンショット開始フラグ      | ONSF  | 105            |

| 0383h | トリガ選択レジスタ        | TRGSR | 105,132        |

| 0384h | アップダウンフラグ        | UDF   | 104            |

| 0385h |                  |       |                |

| 0386h |                  |       |                |

| 0387h | タイマA0レジスタ        | TA0   | 13             |

| 0388h | タイマA1レジスタ        | TA1   | 103<br>130     |

| 038Ah | タイマA2レジスタ        | TA2   | 103<br>130     |

| 038Bh | タイマA3レジスタ        | TA3   | 103            |

| 038Ch | タイマA4レジスタ        | TA4   | 103<br>130     |

| 0390h | タイマB0レジスタ        | TB0   | 118            |

| 0391h | タイマB1レジスタ        | TB1   | 118            |

| 0394h | タイマB2レジスタ        | TB2   | 118<br>130     |

| 0395h |                  |       |                |

| 0396h | タイマA0モードレジスタ     | TA0MR | 103            |

| 0397h | タイマA1モードレジスタ     | TA1MR | 106<br>133     |

| 0398h | タイマA2モードレジスタ     | TA2MR | 108<br>110,133 |

| 0399h | タイマA3モードレジスタ     | TA3MR | 113<br>110     |

| 039Ah | タイマA4モードレジスタ     | TA4MR | 115<br>110,133 |

| 039Bh | タイマB0モードレジスタ     | TB0MR | 118,120        |

| 039Ch | タイマB1モードレジスタ     | TB1MR | 121,123        |

| 039Dh | タイマB2モードレジスタ     | TB2MR | 133            |

| 039Eh | タイマB2特殊モードレジスタ   | TB2SC | 131            |

| 039Fh |                  |       |                |

| 03A0h | UART0送受信モードレジスタ  | U0MR  | 141            |

| 03A1h | UART0ビットレートレジスタ  | U0BRG | 140            |

| 03A2h | UART0送信バッファレジスタ  | U0TB  | 140            |

| 03A3h |                  |       |                |

| 03A4h | UART0送受信制御レジスタ0  | U0C0  | 141            |

| 03A5h | UART0送受信制御レジスタ1  | U0C1  | 142            |

| 03A6h | UART0受信バッファレジスタ  | U0RB  | 140            |

| 03A7h |                  |       |                |

| 03A8h | UART1送受信モードレジスタ  | U1MR  | 141            |

| 03A9h | UART1ビットレートレジスタ  | U1BRG | 140            |

| 03AAh | UART1送信バッファレジスタ  | U1TB  | 140            |

| 03ABh |                  |       |                |

| 03ACh | UART1送受信制御レジスタ0  | U1C0  | 141            |

| 03ADh | UART1送受信制御レジスタ1  | U1C1  | 142            |

| 03AEh | UART1受信バッファレジスタ  | U1RB  | 140            |

| 03AFh |                  |       |                |

| 03B0h | UART送受信制御レジスタ2   | UCON  | 143            |

| 03B1h |                  |       |                |

| 03B2h |                  |       |                |

| 03B3h |                  |       |                |

| 03B4h |                  |       |                |

| 03B5h |                  |       |                |

| 03B6h |                  |       |                |

| 03B7h |                  |       |                |

| 03B8h | DMA0要因選択レジスタ     | DM0SL | 92             |

| 03B9h |                  |       |                |

| 03BAh | DMA1要因選択レジスタ     | DM1SL | 93             |

| 03BBh |                  |       |                |

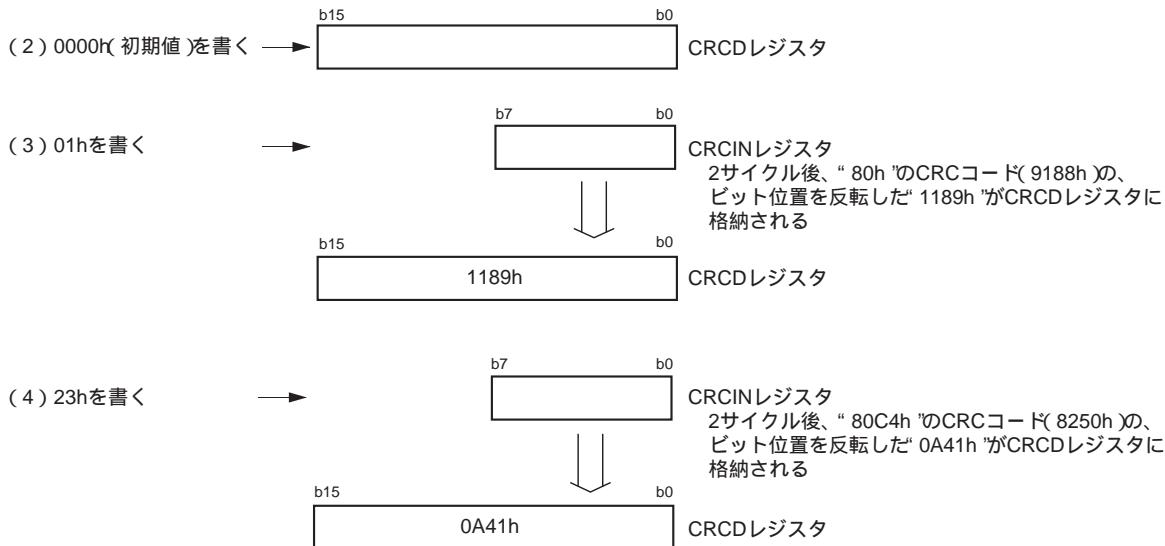

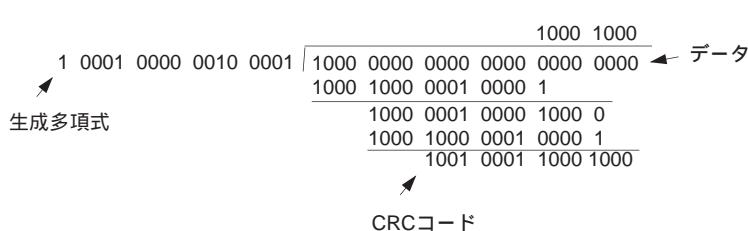

| 03BCh | CRCデータレジスタ       | CRCD  | 207            |

| 03BDh |                  |       |                |

| 03BEh | CRCインプットレジスタ     | CRCIN | 207            |

| 03BFh |                  |       |                |

空欄はすべて予約領域です。

| 番地     | レジスタ         | シンポル   | 掲載ページ       |

|--------|--------------|--------|-------------|

| 03C0h  | A/Dレジスタ0     | AD0    |             |

| 03C1h  |              |        |             |

| 03C2h  | A/Dレジスタ1     | AD1    |             |

| 03C3h  |              |        |             |

| 03C4h  | A/Dレジスタ2     | AD2    |             |

| 03C5h  |              |        |             |

| 03C6h  | A/Dレジスタ3     | AD3    |             |

| 03C7h  |              |        |             |

| 03C8h  | A/Dレジスタ4     | AD4    |             |

| 03C9h  |              |        |             |

| 03CAh  | A/Dレジスタ5     | AD5    |             |

| 03CBh  |              |        |             |

| 03CCh  | A/Dレジスタ6     | AD6    |             |

| 03CDh  |              |        |             |

| 03CEh  | A/Dレジスタ7     | AD7    |             |

| 03CFh  |              |        |             |

| 03D0h  |              |        |             |

| 03D1h  |              |        |             |

| 03D2h  |              |        |             |

| 03D3h  |              |        |             |

| 03D4h  | A/D制御レジスタ2   | ADCON2 | 191         |

| 03D5h  |              |        |             |

| 03D6h  | A/D制御レジスタ0   | ADCON0 | 190,193,195 |

| 03D7h  | A/D制御レジスタ1   | ADCON1 | 197,199,201 |

| 03D8h  | D/Aレジスタ0     | DA0    | 206         |

| 03D9h  |              |        |             |

| 03DAh  | D/Aレジスタ1     | DA1    | 206         |

| 03DBh  |              |        |             |

| 03DCh  | D/A制御レジスタ    | DACON  | 206         |

| 03DDh  |              |        |             |

| 03DEh  |              |        |             |

| 03DFh  |              |        |             |

| 03E0h  | ポートP0レジスタ    | P0     | 242         |

| 03E1h  | ポートP1レジスタ    | P1     | 242         |

| 03E2h  | ポートP0方向レジスタ  | PD0    | 241         |

| 03E3h  | ポートP1方向レジスタ  | PD1    | 241         |

| 03E4h  | ポートP2レジスタ    | P2     | 242         |

| 03E5h  | ポートP3レジスタ    | P3     | 242         |

| 03E6h  | ポートP2方向レジスタ  | PD2    | 241         |

| 03E7h  | ポートP3方向レジスタ  | PD3    | 241         |

| 03E8h  | ポートP4レジスタ    | P4     | 242         |

| 03E9h  | ポートP5レジスタ    | P5     | 242         |

| 03EAh  | ポートP4方向レジスタ  | PD4    | 241         |

| 03EBh  | ポートP5方向レジスタ  | PD5    | 241         |

| 03ECCh | ポートP6レジスタ    | P6     | 242         |

| 03EDh  | ポートP7レジスタ    | P7     | 242         |

| 03EEh  | ポートP6方向レジスタ  | PD6    | 241         |

| 03EFh  | ポートP7方向レジスタ  | PD7    | 241         |

| 03F0h  | ポートP8レジスタ    | P8     | 242         |

| 03F1h  | ポートP9レジスタ    | P9     | 242         |

| 03F2h  | ポートP8方向レジスタ  | PD8    | 241         |

| 03F3h  | ポートP9方向レジスタ  | PD9    | 241         |

| 03F4h  | ポートP10レジスタ   | P10    | 242         |

| 03F5h  |              |        |             |

| 03F6h  | ポートP10方向レジスタ | PD10   | 241         |

| 03F7h  |              |        |             |

| 03F8h  |              |        |             |

| 03F9h  |              |        |             |

| 03FAh  |              |        |             |

| 03FBh  |              |        |             |

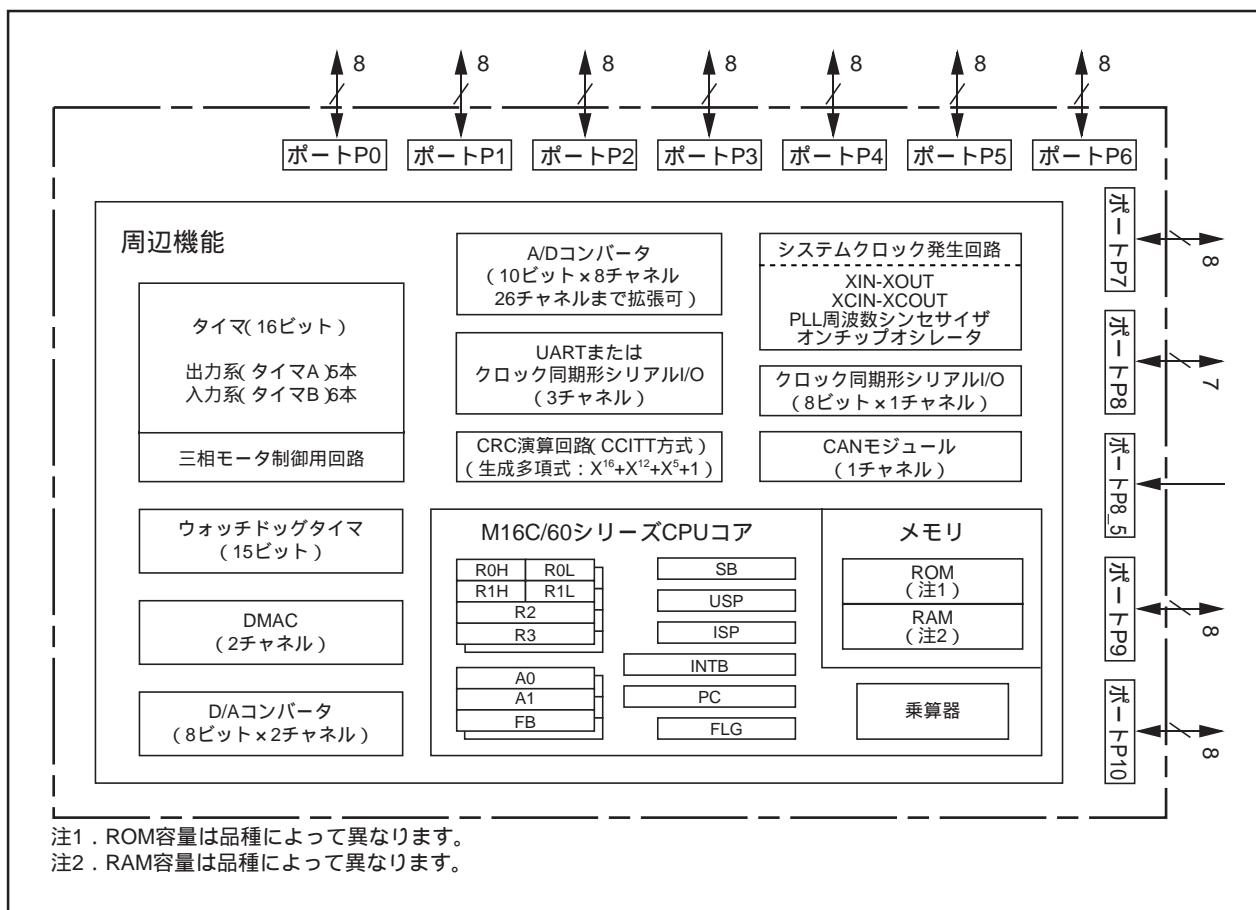

| 03FCCh | ブルアップ制御レジスタ0 | PUR0   | 243         |

| 03FDh  | ブルアップ制御レジスタ1 | PUR1   | 243         |

| 03FEh  | ブルアップ制御レジスタ2 | PUR2   | 243         |

| 03FFh  | ポート制御レジスタ    | PCR    | 244         |

## 1. 概要

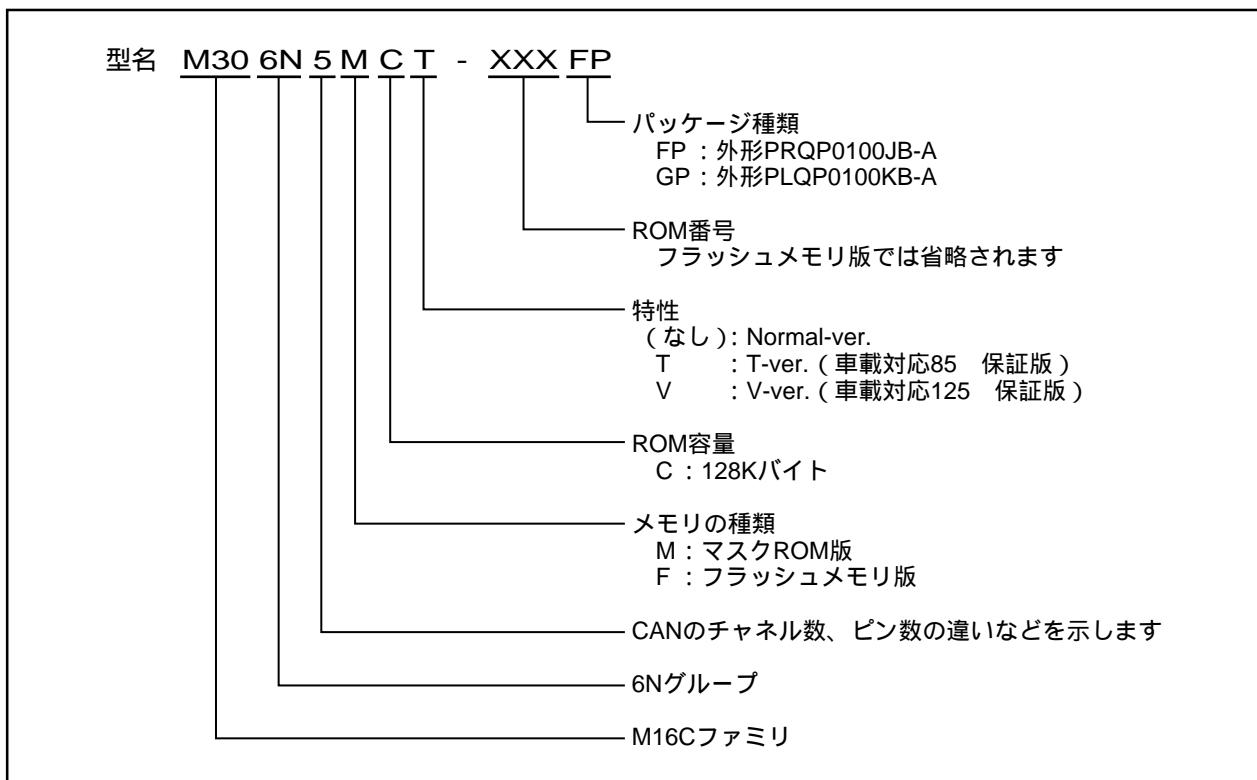

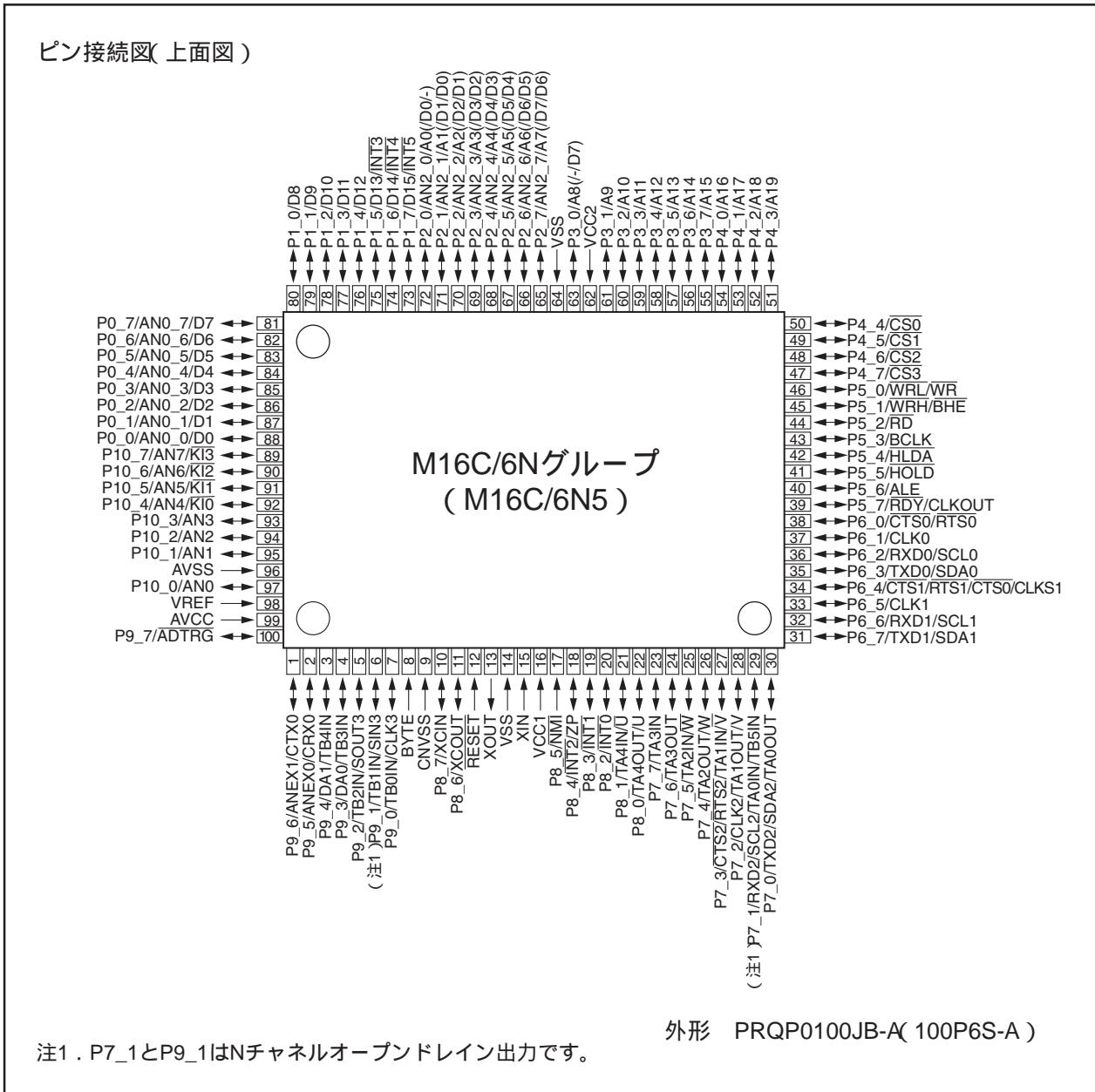

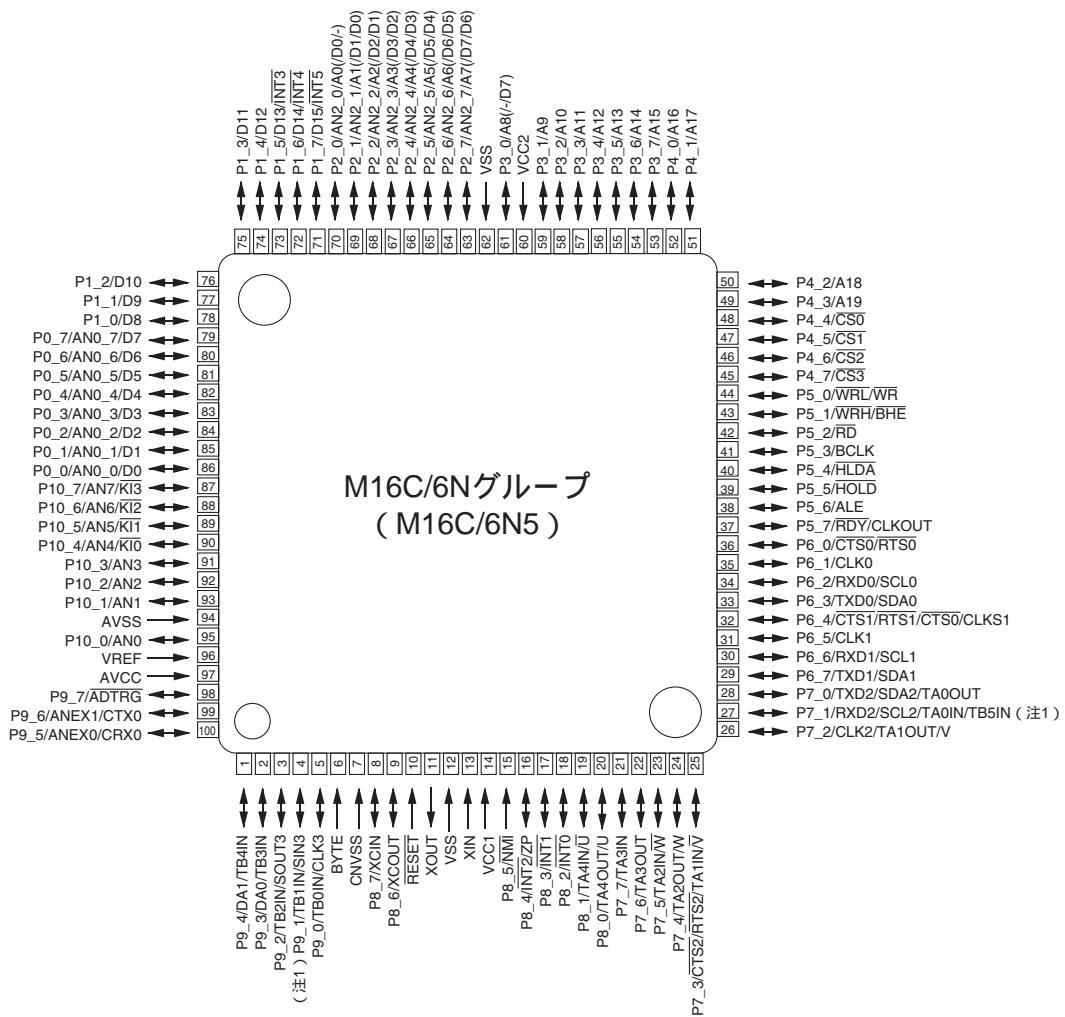

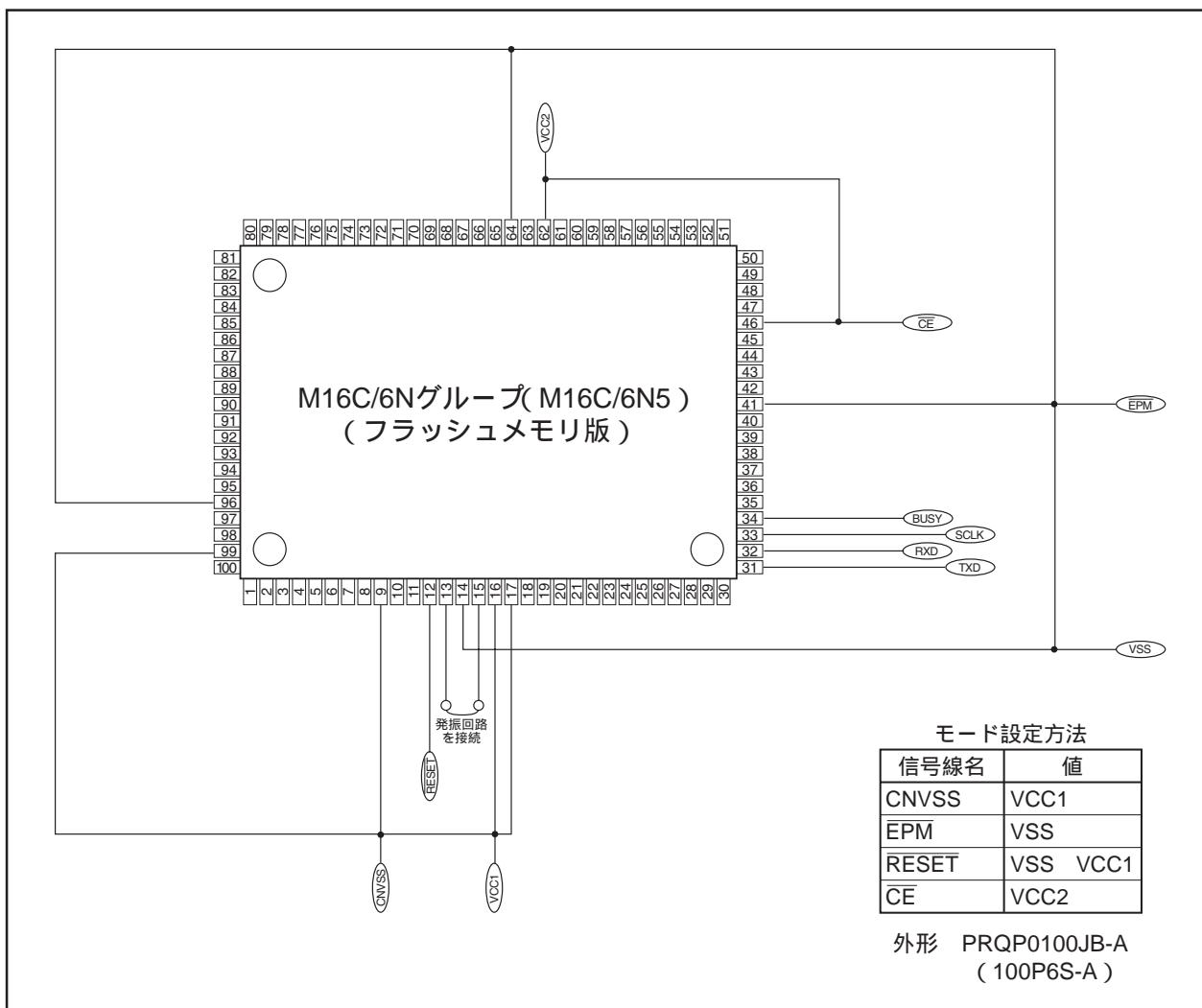

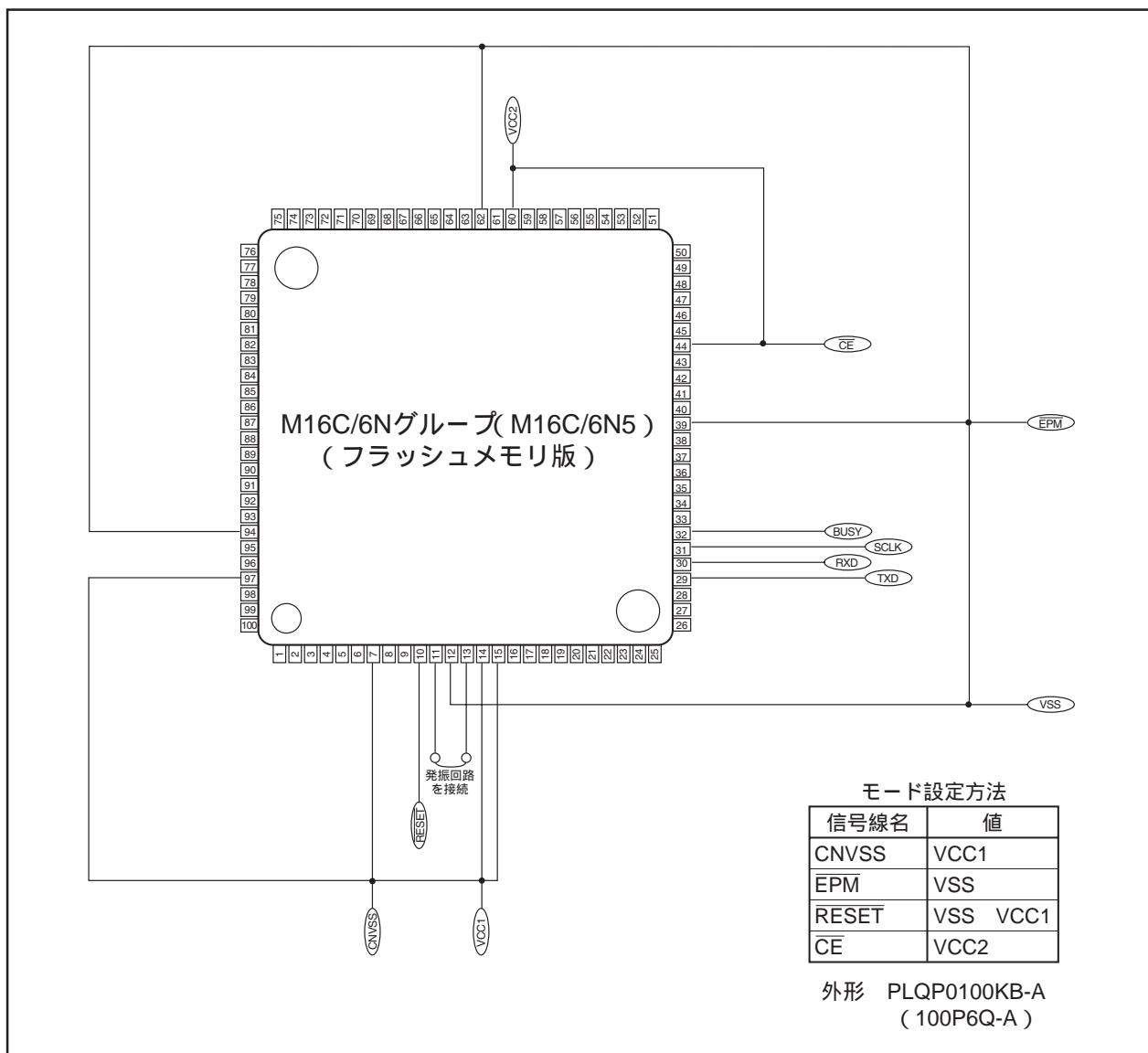

M16C/6Nグループ( M16C/6N5 )は、高性能シリコンゲートCMOSプロセスを採用しM16C/60シリーズCPUコアを搭載したマイクロコンピュータで、100ピンプラスチックモールドQFPまたはLQFPに収められています。このマイクロコンピュータは、高機能命令を持ちながら高い命令効率を持ち、1Mバイトのアドレス空間と、命令を高速に実行する能力を備えています。CANモジュールを1チャネル内蔵し、車載やFAのLANシステムに適したマイクロコンピュータです。また、乗算器、DMACがあるため、高速な演算処理が必要なOA、通信機器、産業機器の制御にも適しています。

### 1.1 応用

- ・車載、FAのLANシステム、他( T/V-ver.品 )

- ・カーオーディオ、産業機器、他( Normal-ver.品 )

## 1.2 性能概要

表1.1に性能概要を示します。

表1.1 性能概要

| 項目        |                                                                                                   | 性能                                                                                                            |                                                          |

|-----------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|           |                                                                                                   | Normal-ver.                                                                                                   | T/V-ver.                                                 |

| CPU       | 基本命令数                                                                                             | 91命令                                                                                                          |                                                          |

|           | 最小命令実行時間                                                                                          | 41.7ns( f(BCLK) = 24MHz、<br>1/1プリスケーラ、ウェイトなし時)                                                                | 50.0ns( f(BCLK) = 20MHz、<br>1/1プリスケーラ、ウェイトなし時)           |

|           | 動作モード                                                                                             | シングルチップ、メモリ拡張、マイクロプロセッサ                                                                                       |                                                          |

|           | アドレス空間                                                                                            | 1Mバイト                                                                                                         |                                                          |

|           | メモリ容量                                                                                             | 「表1.2 製品一覧表」を参照してください                                                                                         |                                                          |

| 周辺機能      | ポート                                                                                               | 入出力 : 87本、入力 : 1本                                                                                             |                                                          |

|           | 多機能タイマ                                                                                            | タイマA : 16ビット×5チャネル<br>タイマB : 16ビット×6チャネル<br>三相モータ制御回路                                                         |                                                          |

|           | シリアルインターフェース                                                                                      | 3チャネル<br>クロック同期形シリアルI/O、クロック非同期形シリアルI/O、<br>I <sup>2</sup> C bus( 注1 )、IEBus( 注2 )<br>1チャネル<br>クロック同期形シリアルI/O |                                                          |

|           | A/Dコンバータ                                                                                          | 10ビットA/Dコンバータ : 1回路、26チャネル                                                                                    |                                                          |

|           | D/Aコンバータ                                                                                          | 8ビット×2チャネル                                                                                                    |                                                          |

|           | DMAC                                                                                              | 2チャネル                                                                                                         |                                                          |

|           | CRC演算回路                                                                                           | CRC-CCITT方式                                                                                                   |                                                          |

|           | CANモジュール                                                                                          | 1チャネル、2.0B対応                                                                                                  |                                                          |

|           | ウォッチドッグタイマ                                                                                        | 15ビット×1チャネル( プリスケーラ付 )                                                                                        |                                                          |

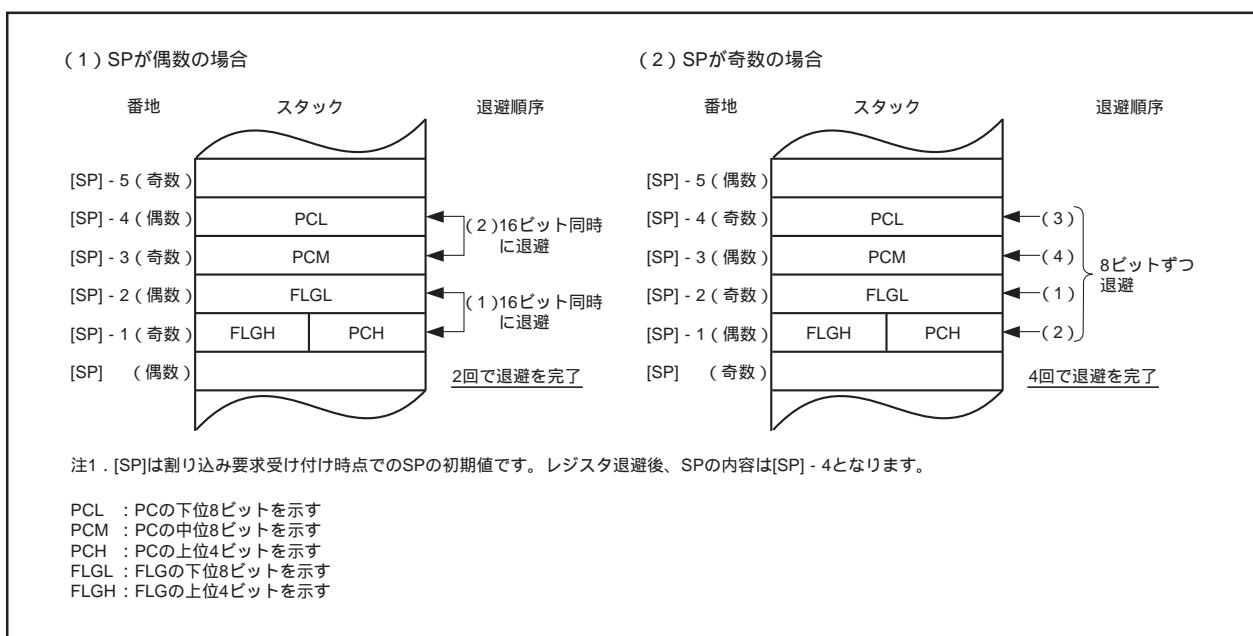

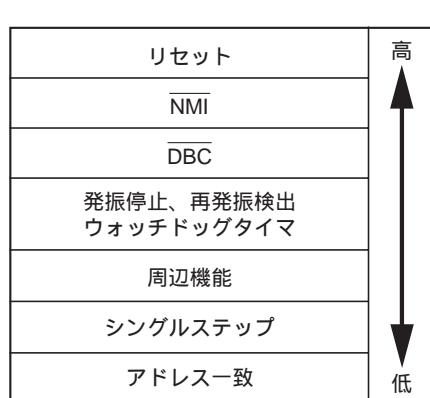

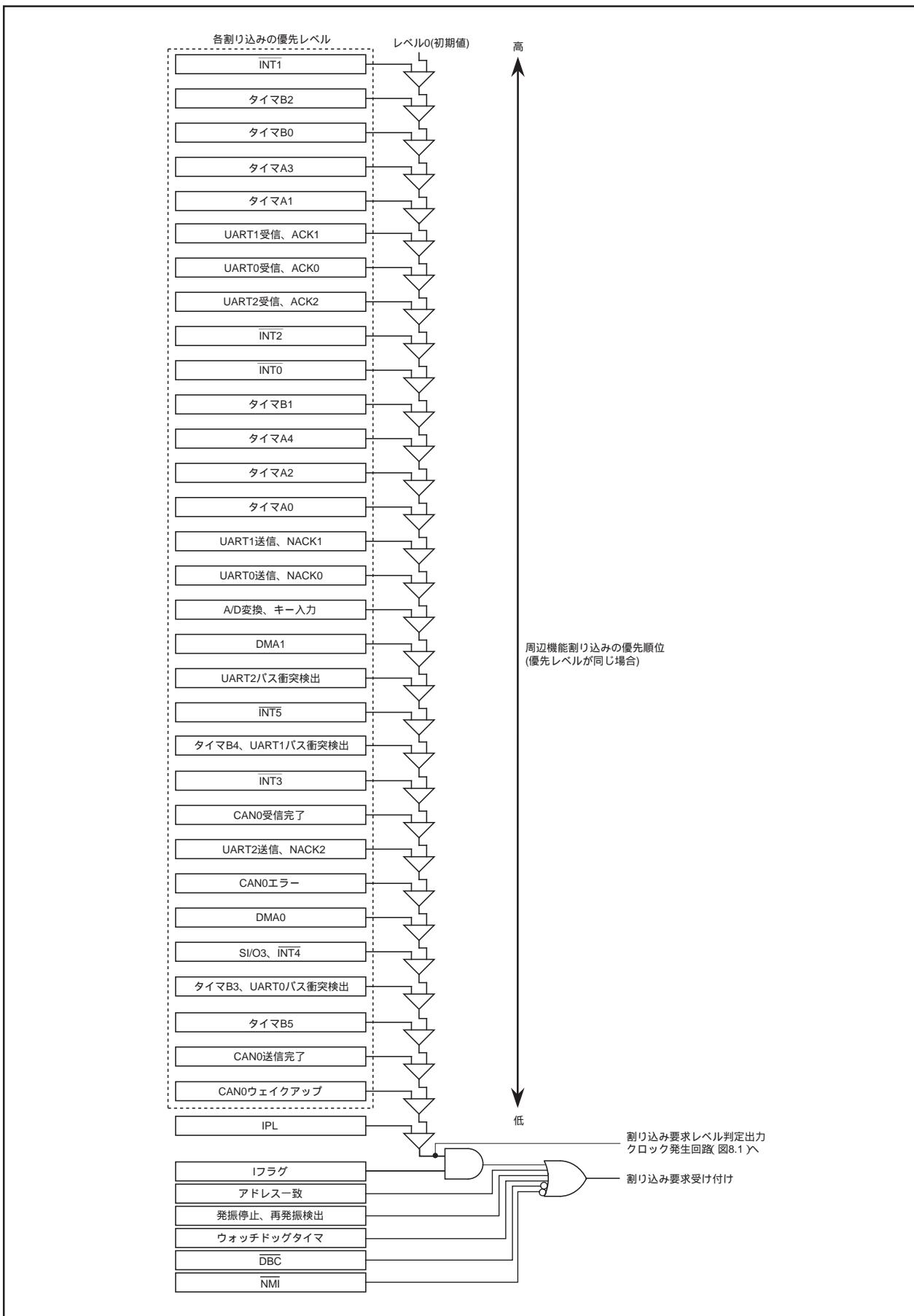

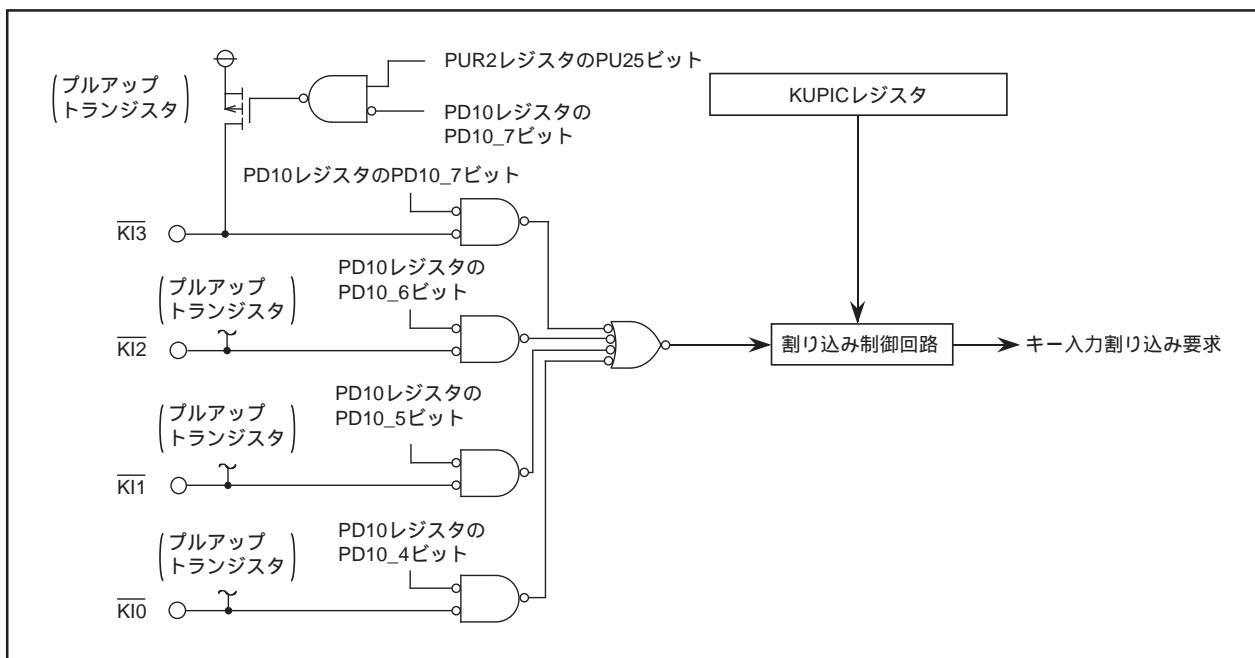

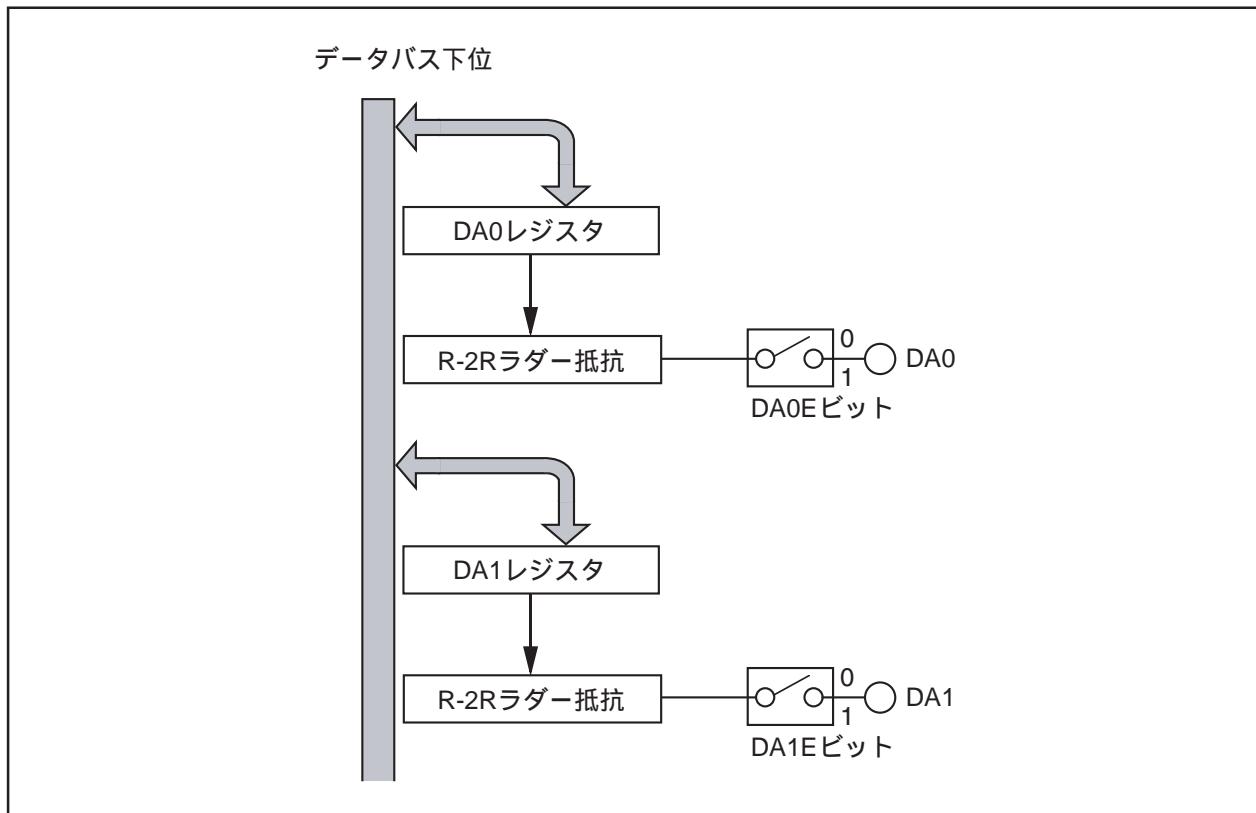

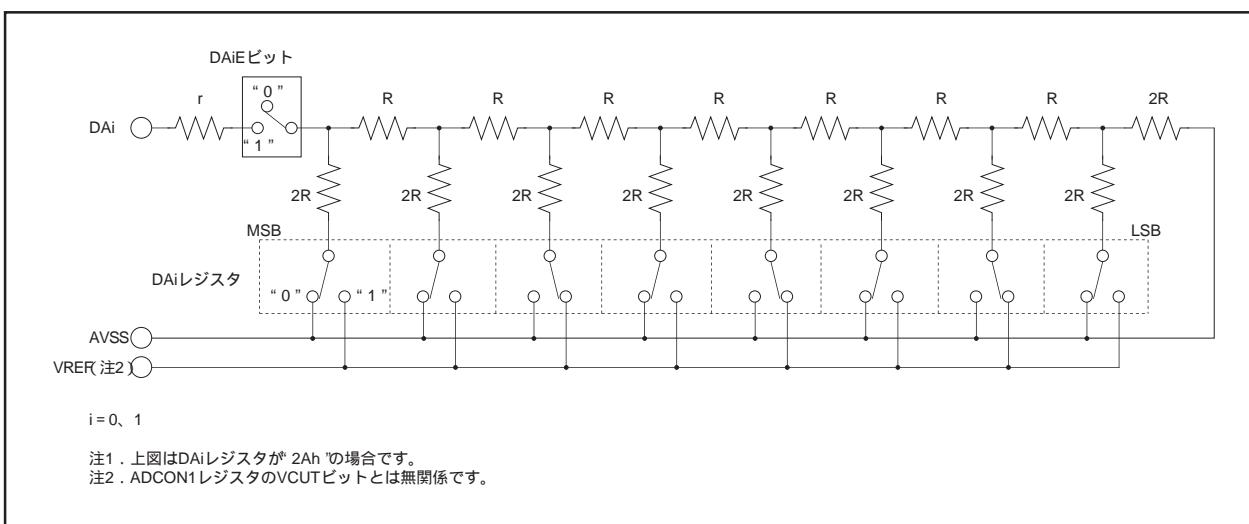

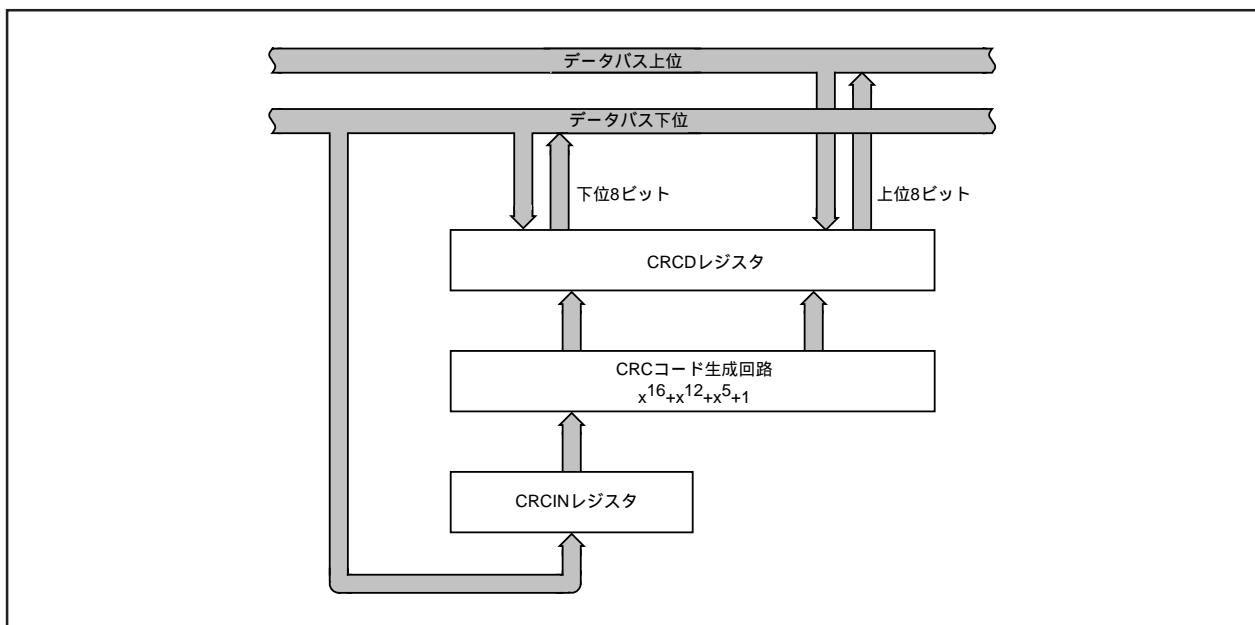

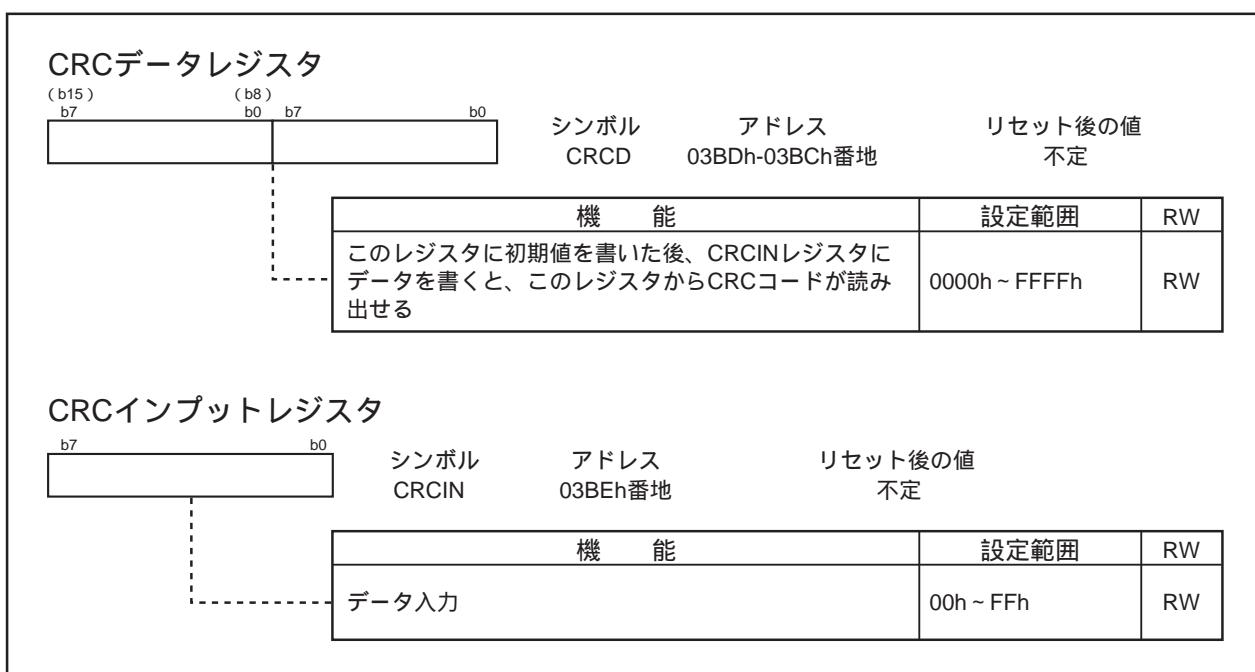

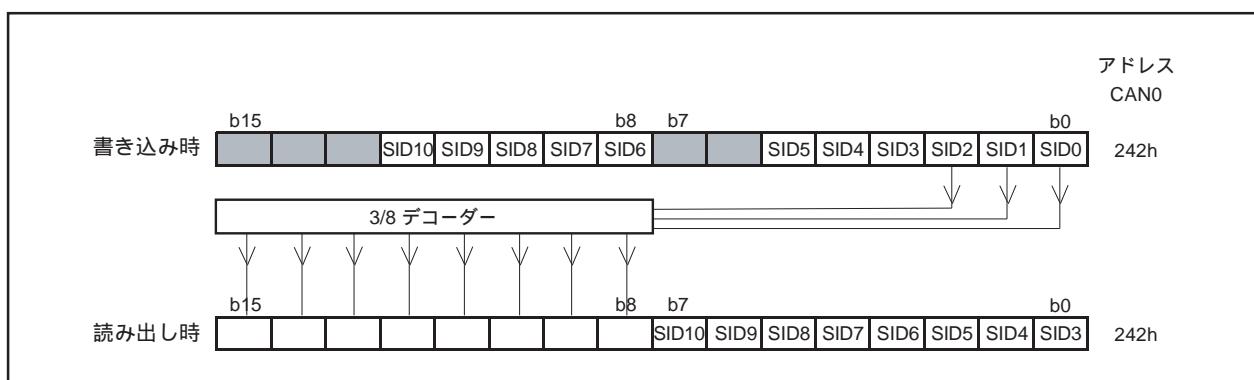

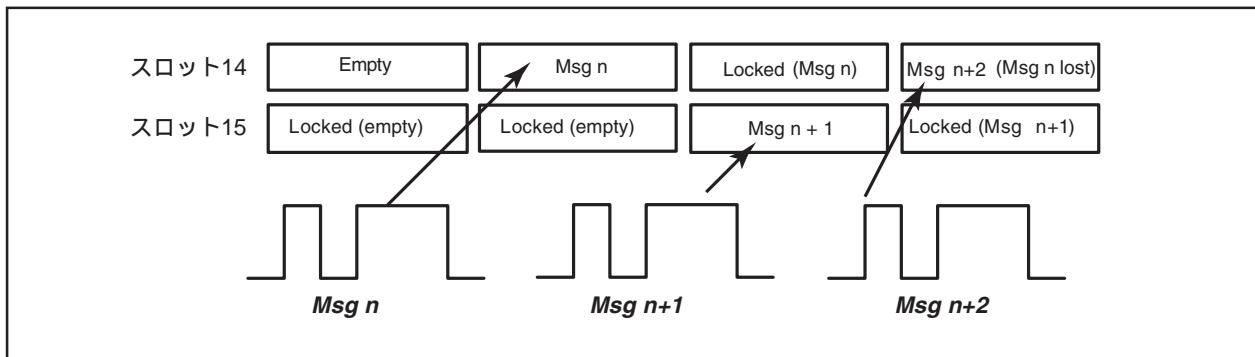

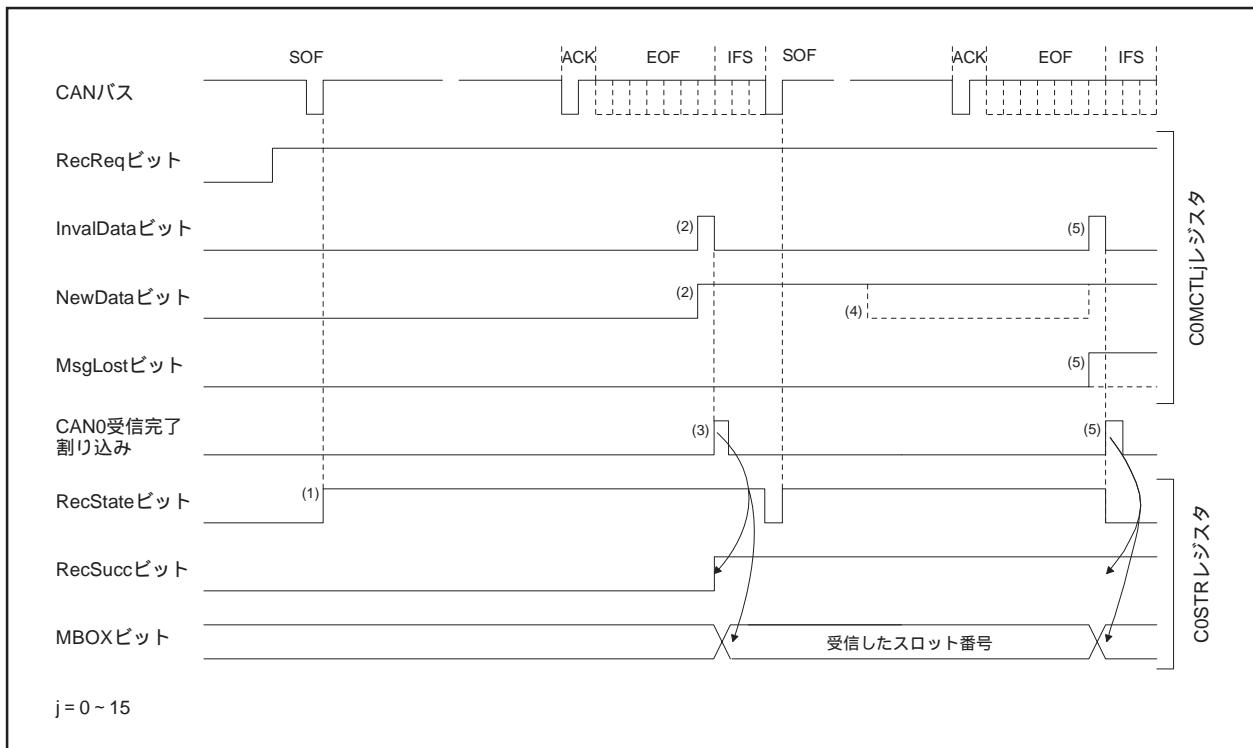

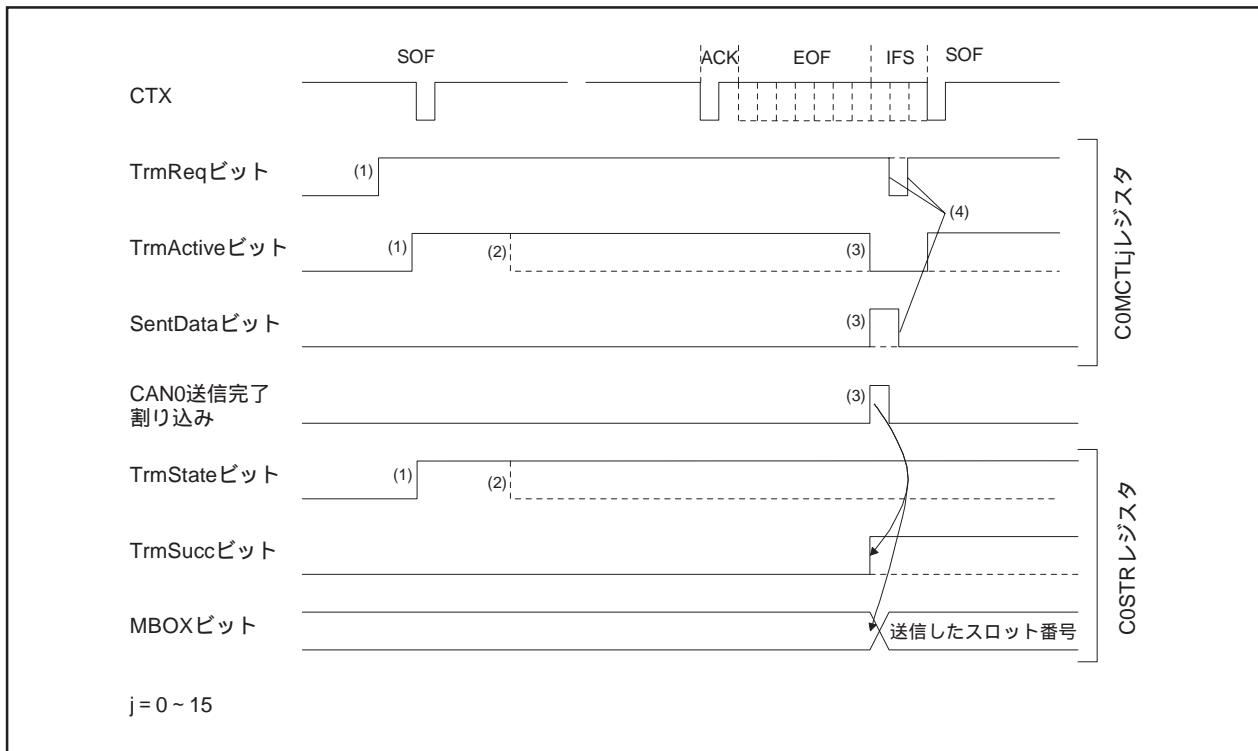

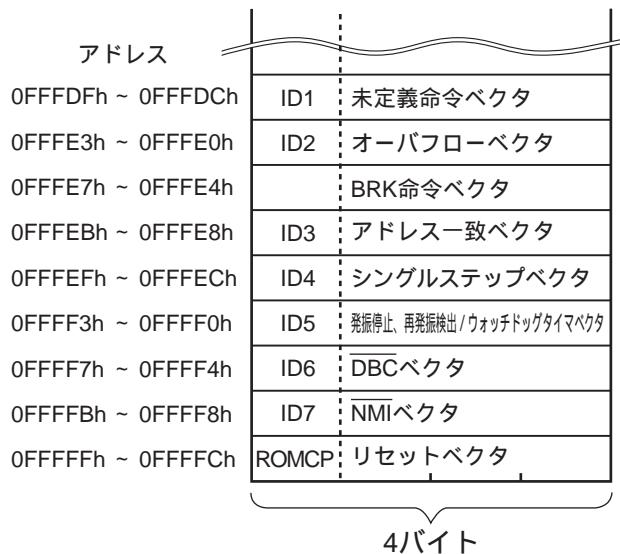

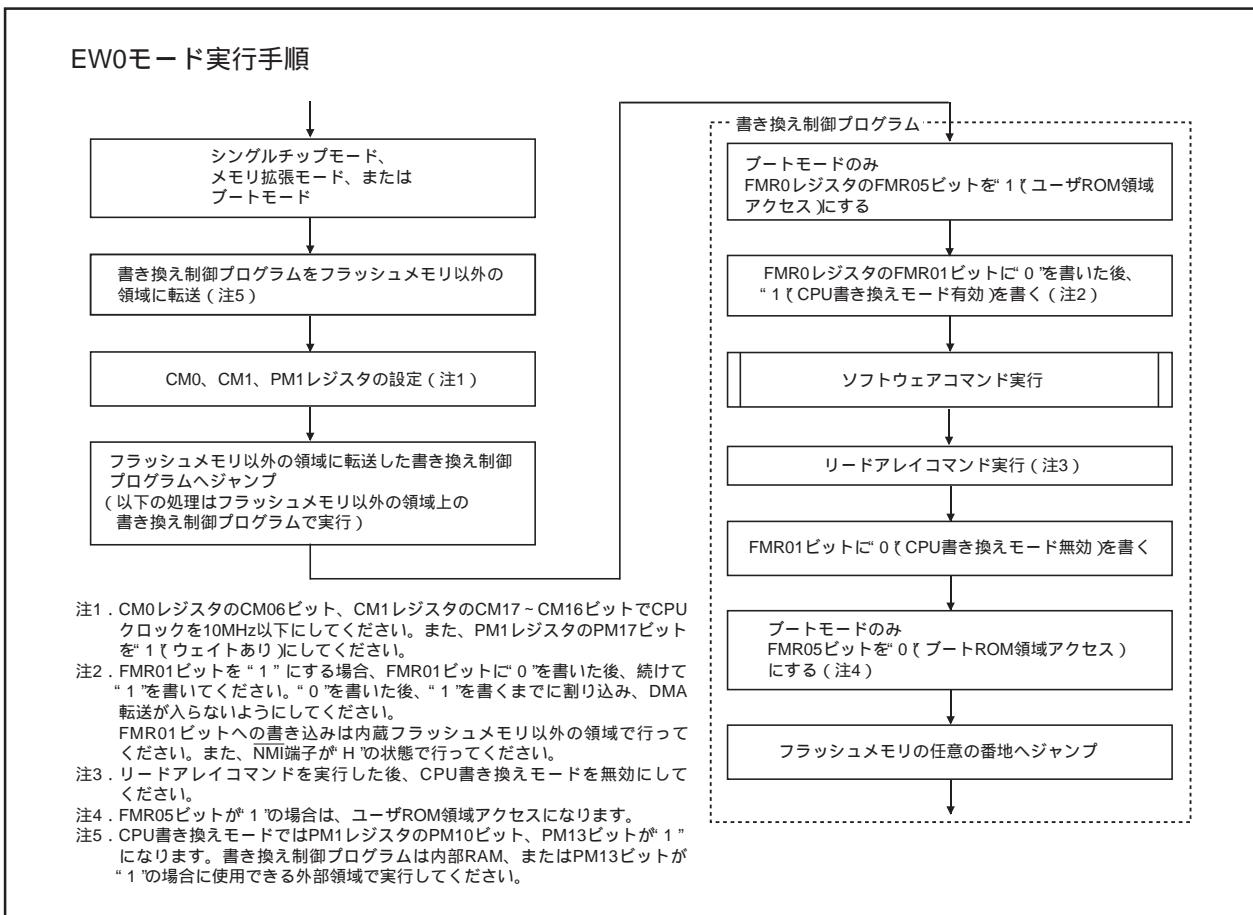

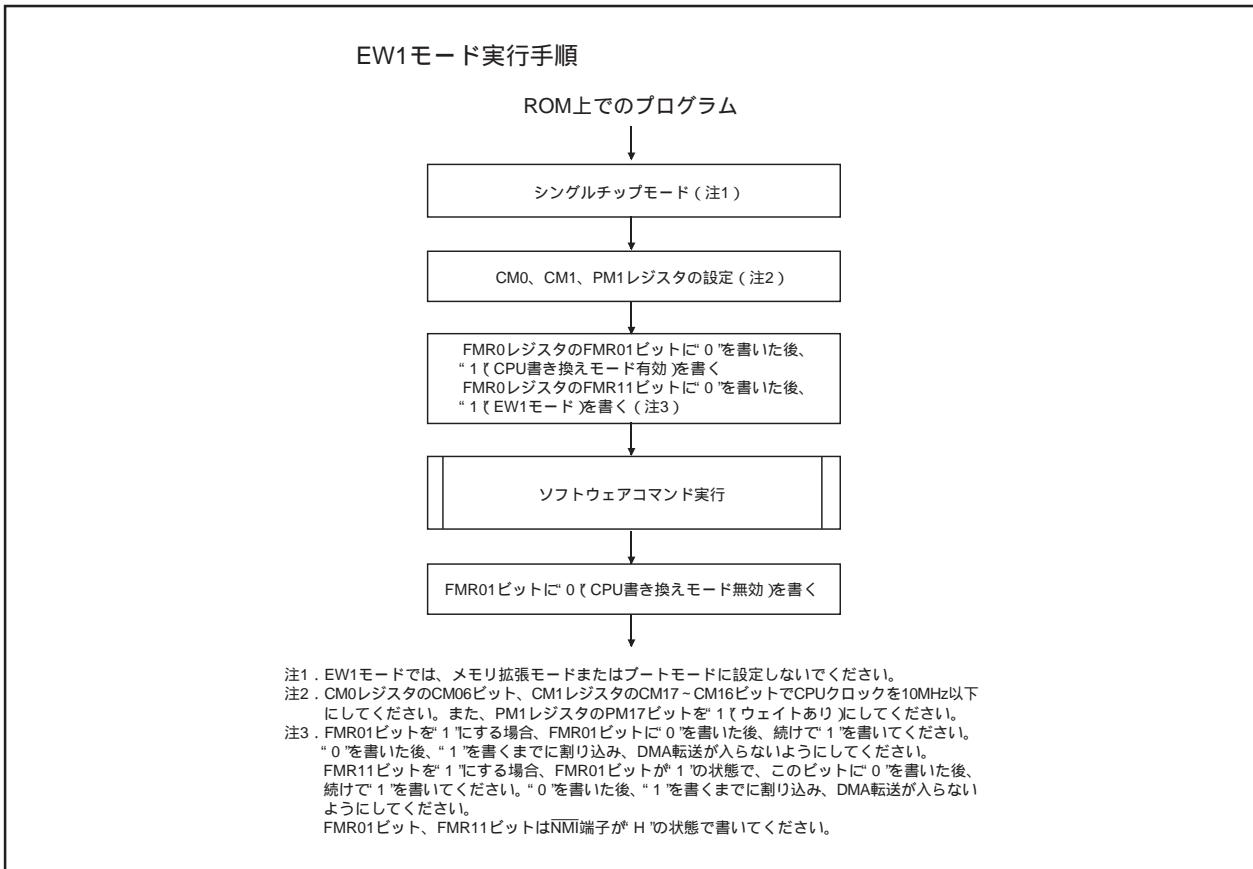

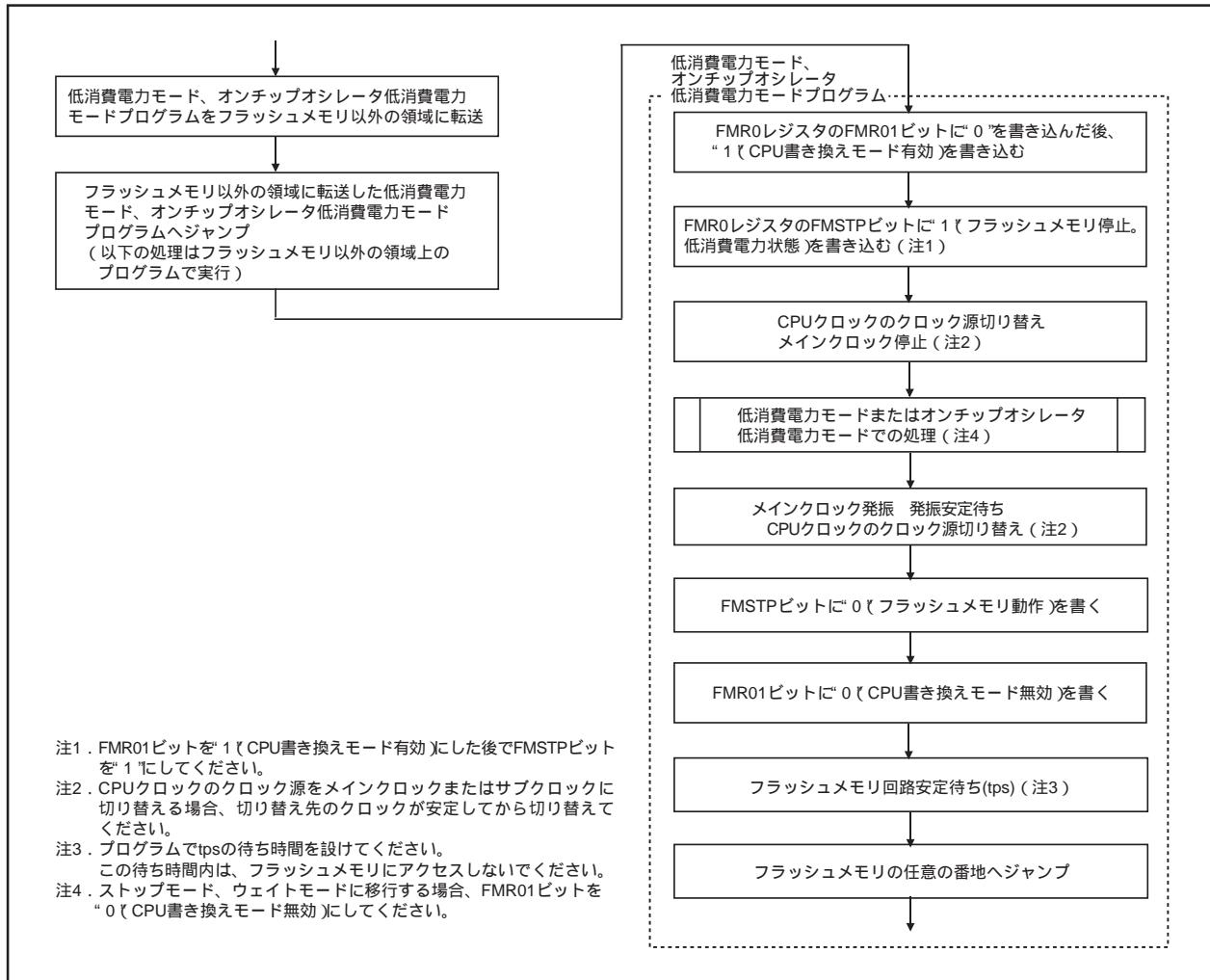

|           | 割り込み                                                                                              | 内部 : 29要因、外部 : 9要因、ソフトウェア : 4要因<br>割り込み優先レベル : 7レベル                                                           |                                                          |