# **RENESAS** VersaClock<sup>®</sup> 3S - 5P35021 Evaluation Board

# Introduction

The evaluation board is designed to help the customer evaluate the 5P35021, the latest addition to the family of programmable devices in IDT's Timing portfolio. When the board is connected to a PC running IDT Timing Commander<sup>™</sup> Software through USB, the device can be configured and programmed to generate different combinations of frequencies.

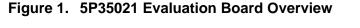

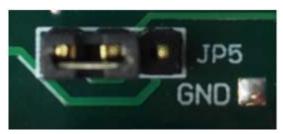

# **Board Overview**

Use Figure 1 and Table 1 to identify: power supply jacks, USB connector, input and output frequency SMA connectors.

# Table 1: Evaluation Board Pins and Functions

| Item         | Name                     | On-Board Connector Label | Function                                                                                                     |

|--------------|--------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|

| 0            | Power supply jack        | J18                      | Connect to 1.8V, 2.5V, or 3.3V for the output voltage of the device                                          |

| 1            | Ground jack              | J19                      | If J18 & J17are used for power supply, this is the return power                                              |

| 2            | Output voltage jack      | J17                      | Connect to 3.3V core voltage of the device                                                                   |

| 3            | USB connector            | J3                       | Connect this USB to your PC to run IDT Timing<br>Commander                                                   |

| 4            | DIP switch               | U6                       | This is used to configure the device in different modes                                                      |

| 5            | Differential clock input | CLKIN/CLKINB             | A differential clock can be connected as source for the device                                               |

| 5<br>(cont.) | Single-ended clock input | CLKINB                   | A Single-ended clock can be connected as source for the device using CLKINB only                             |

| 6            | Crystal, 25 MHz          | Y1                       | This crystal is used as a reference source for the clock signal                                              |

| 7            | Differential output      | DIFF_C1/T1               | This can be a differential pair, or two single-ended outputs. By default, it's a LPHCSL differential output. |

| 8            | Differential output      | DIFF_C0/T0               | This can be a differential pair, or two single-ended outputs. By default, it's a LPHCSL differential output. |

| 9            | Single-ended output      | SE_1                     | This is the single-ended output. By default it's an LVCMOS single-ended output                               |

# **Board Power Supply**

### **Power Supply Options**

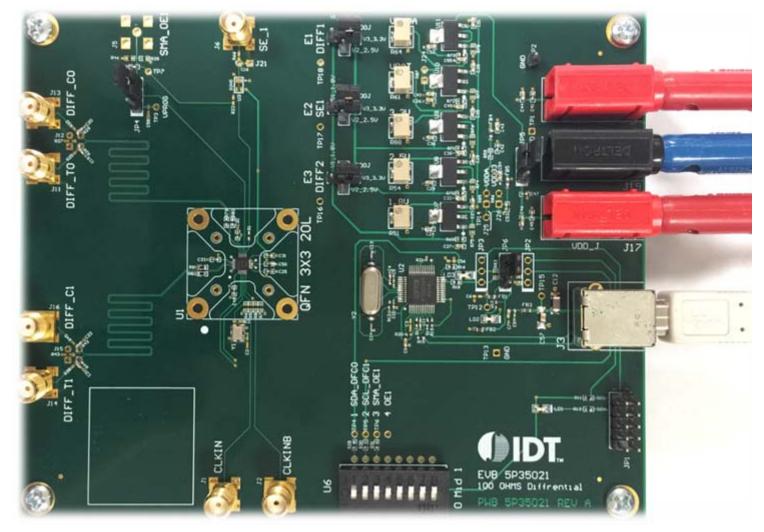

The core voltage includes a digital voltage VDD33 and an analog voltage VDDA. Both core voltages can be powered by an external bench power supply or by USB.

- Bench Power Supply To supply VDD33 with a bench power supply, connect power to J17. To supply VDDA with a bench power supply, connect power to J18. At the same time, place the jumpers as shown in Figure 2B.

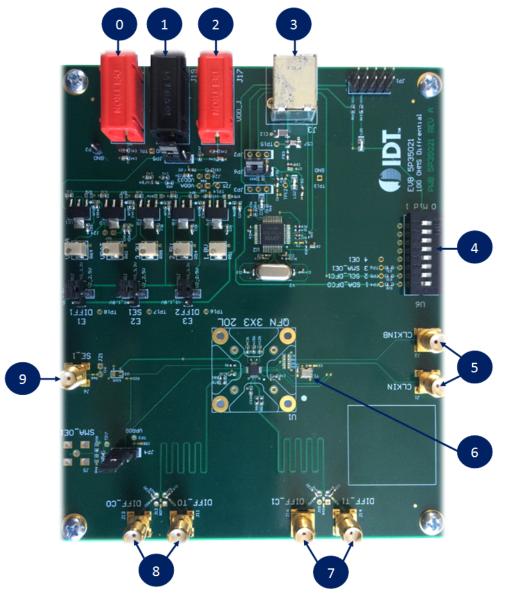

- USB Power Supply When the board is connected to a PC through a USB cable, on-board voltage regulators will generate a 3.3V for the device. In this case, place the jumper as shown in Figure 2A. See JP5 jumper position for the on-board voltage regulators in the following figure. USB power source is recommended because it's readily available right from your laptop.

- Figure 2. Jumping to the Pin configuration as shown (Figure 2A.) will select power source from on-board voltage regulators powered by USB; Jumping to the Pin configuration as shown (Figure 2B.) will select the bench power supply

Figure 2A. (JP5: Pin 1 - 2 to Voltage Regulators)

Figure 2B. (JP5: Pin 2 - 3 to Banana Jack)

#### **Output Clock Voltages**

Like VDDA and VDD33 having two sources, each output voltage is also provided with two sources to choose from: bench power supply or powered from USB. The selection is made by a 4-way header as shown in Figure 3 below.

The jumper can be used to select a voltage for E1, E2, E3, E4, and E5 respectively. The on-board voltage regulators powered by USB are 1.8V, 2.5V and 3.3V; VDDOJ is from bench power supply connecting to JP17 and JP18. Each output voltage can be individually selected. Use the label on the evaluation board: E1 for VDDDIFF1, E2 for VDDSE1, E3 for VDDDIFF2, E4 for VDDSE2 and E5 for VDDSE3. The JP6 on the EVB needs to be in the default position as supplied by the manufacturer.

Note: Connect the USB to the board when using external power supply

Figure 3. Jumper Configuration for On-board Voltage Regulators

# **Connecting the Board**

The board is connected to a PC through a USB connector for configuring and programming the device, as shown in Figure 4 below. The USB interface will also provide +5V power supply to the board, from which on-board voltage regulators generate various voltages for the core as well as for each output.

The board can also be powered by a bench power supply by connecting two banana jacks J17, J18 for output and core voltages, respectively. Please see board power supply section for details.

Note: The USB port only supports USB 2.0; USB 3.0 is not supported at this time.

### Figure 4. Connecting the Board with USB Port for Communications with Timing Commander Software

## **On-Board Crystal**

A 25MHz crystal is installed on the board. It is used as a source for reference frequency.

# **Board Default Frequency Output**

# Table 2: Board Default Frequency Output

| Serial | Output                           | Output Frequency |

|--------|----------------------------------|------------------|

| 1      | SE_1 (Single-ended)              | _                |

| 2      | DIFF_CO/TO (Differential Output) | 100 MHz          |

| 3      | DIFF_C1/T1 (Differential Output) | 100 MHz          |

## DIP Switch (U6)

## Table 3:DIP Switch (U6)

| Serial | DIP Switch Pin Number | DIP Switch Pin Name       | State             | Mode |

|--------|-----------------------|---------------------------|-------------------|------|

| А      | 1                     | SDA_DFCO                  | Floating/Tristate | -    |

| В      | 2                     | SCL_DFC1                  | High or 1         | I2C  |

| С      | 3, 5, 7               | SMA_OE1, SMA_OE2, SMA_OE3 | High or 1         | -    |

| D      | 4, 6, 8               | OE1, OE2, OE3             | High or 1         | -    |

# Configuration and Setup

## Table 4: Configuration and Setup from I2C Port

| Step No. | Steps                                                                                             | Comments                                                                  |

|----------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 1        | Set SCL_OFC1 Pin (DIP Switch PIN 2)                                                               | High or 1                                                                 |

| 2        | Launch 5P35021 Timing Commander Software                                                          | Refer to 5P35021 Timing Commander User Guide<br>Timing Commander Software |

| 3        | Follow the "Getting Started Steps" – in Timing Commander Software                                 | _                                                                         |

| 4        | Using the Timing Commander GUI, start a new settings file, or open a pre-optimized file.          | Configure the Timing Commander Software for the required sets of Outputs  |

| 5        | Connect J3 to a USB Port using the supplied I2C cable                                             | An I2C connection is established between GUI software and VC3S device     |

| 6        | Connect to the EVB by clicking on the microchip icon located at the right of the timing commander | Connect to the chip                                                       |

| Step No. | Steps                                                                                                                                   | Comments                        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 7        | Once configured, new options will be available on a green background indicating that the EVB has successfully connected with the board. | _                               |

| 8        | Write the setting to the device by clicking on the write all registers to the chip option                                               | Write all registers to the chip |

| 9        | All intended outputs should be available for measurement.                                                                               | _                               |

## **Board Schematics**

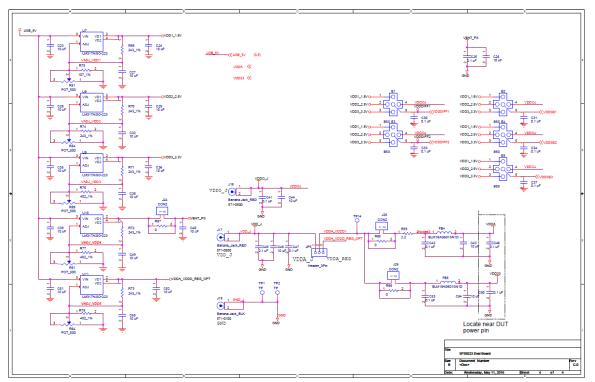

Evaluation board schematics are shown on the following pages.

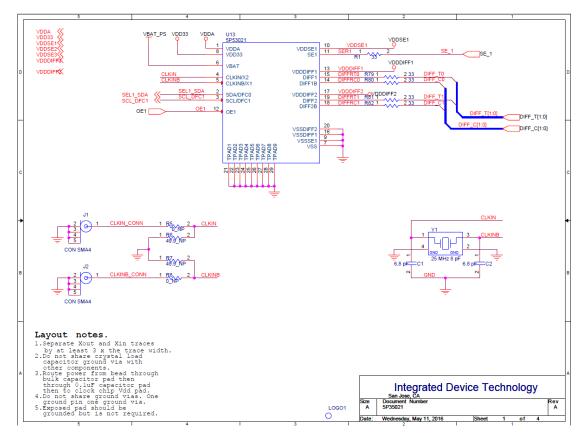

## Figure 5. Evaluation Board Schematic (I)

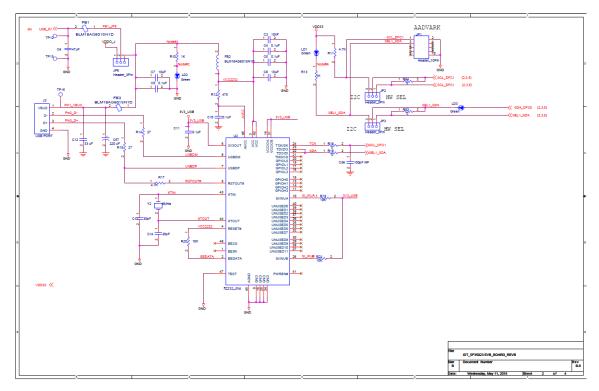

Figure 6. Evaluation Board Schematic (II)

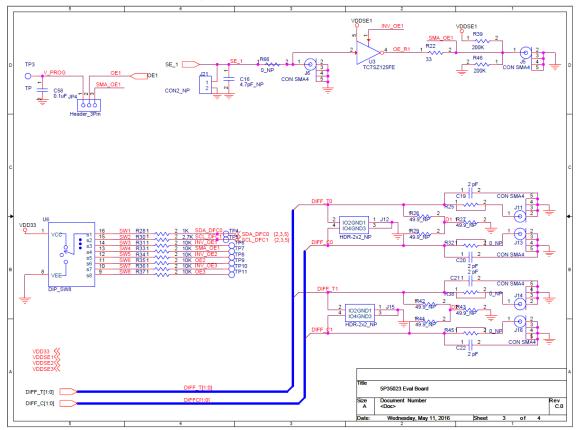

Figure 7. Evaluation Board Schematic (III)

## **Signal Termination Options**

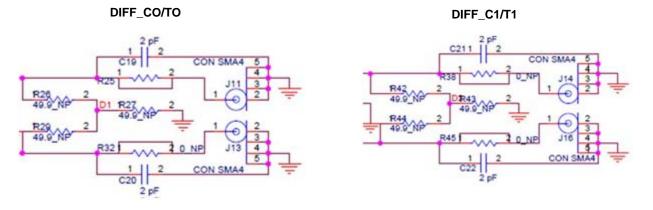

Termination options for Differential Output 1 - 2 in the evaluation board are displayed in Figure 9. The termination circuits are designed to optionally terminate the output clocks in LVPECL, LVDS, LVCMOS and HCSL signal types by populating (or not-populating) some resistors. DC or AC coupling of these outputs are also supported.

Table 5 and Table 6, below, tabulates component installations to support LVPECL, HCSL, LVCMOS and LVDS signal types for OUTPUT1 - 2, respectively. Please note that by doing so, the output signals will be measured and terminated by an oscilloscope with a  $50\Omega$  internal termination.

#### Figure 9. Output Termination Options

### Table 5: Termination Options for Differential Output 1 (DIFF\_CO/TO)

| Signal Type | Series Resistors: | Series Capacitors: | Resistor Network:       |

|-------------|-------------------|--------------------|-------------------------|

|             | R79, R80          | C19, C20           | R25, R26, R27, R29, R32 |

| **LPHCSL    | 33Ω               | 2pF                | Not installed           |

#### Table 6: Termination Options for Differential Output 2 (DIFF\_C1/T1)

| Signal Type | Series Resistors: | Series Capacitors: | Resistor Network:       |

|-------------|-------------------|--------------------|-------------------------|

|             | R81, R82          | C21, C22           | R38, R42, R43, R44, R45 |

| **LPHCSL    | 33Ω               | 2pF                | Not installed           |

As noted, 4-resistor network is not installed in Table 5 and Table 6 because oscilloscope with internal  $50\Omega$  termination is utilized for signal termination and measurement. If an AC-coupled, stand-alone LVPECL output is needed (without oscilloscope connections), the 4-resistor network needs to be installed accordingly.

#### Table 7: Termination for Single-ended Output 1 (SE\_1)

| Signal Type | Series Resistors:<br>R1 | Series Capacitors:<br>C16 |

|-------------|-------------------------|---------------------------|

| *LVCMOS     | 33Ω                     | Not installed             |

#### Table 8: Termination for Differential and Single-ended Input)

| Signal Type              | Series Resistor:<br>R8 | Series Resistor:<br>R5 |

|--------------------------|------------------------|------------------------|

| Differential Clock Input | Not installed          | Not installed          |

| Single-ended Clock Input | Not installed          | Not installed          |

**Note:** \*\* The differential output is applicable to LPHCSL which is the default configuration of the board.

\* The single-ended output is applicable to LVCMOS which is the default configuration of the board.

Contact IDT if user wants to change termination configuration to support other output signal types.

#### **Orderable Part Numbers**

The following evaluation board part numbers are available for order.

#### Table 9: Orderable Part Numbers

| Part Number | Description                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------|

| EVK5P35021  | Evaluation board with all differential outputs terminated as LPHCSL, Single-ended terminated as LVCMOS |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.