## Hardware

# V850E/PHO3

32-bit Single-Chip Microcontroller

µPD70F3441 µPD70F3483

> All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

### **Notice**

- All information included in this document is current as of the date this document is issued. Such

information, however, is subject to change without any prior notice. Before purchasing or using any

Renesas Electronics products listed herein, please confirm the latest product information with a

Renesas Electronics sales office. Also, please pay regular and careful attention to additional and

different information to be disclosed by Renesas Electronics such as that disclosed through our

website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other

intellectual property rights of third parties by or arising from the use of Renesas Electronics

products or technical information described in this document. No license, express, implied or

otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of

Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics.

The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and

measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control

systems; anti-disaster systems; anti-crime systems; safety equipment; and

medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control

systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to

human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### **General Precautions in the Handling of MPU/MCU Products**

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

### 1. Handling of unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

### 2. Processing at power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

### 3. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

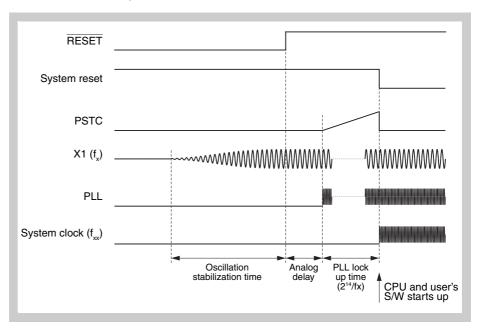

### 4. Clock signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

### 5. Differences between products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

### **Preface**

**Readers** This manual is intended for users who want to understand the functions of the

concerned microcontrollers.

**Purpose** This manual presents the hardware manual for the concerned microcontrollers.

**Organization** This system specification describes the following sections:

• Pin function

• CPU function

· Internal peripheral function

Module instances These microcontrollers may contain several instances of a dedicated module.

In general the different instances of such modules are identified by the index

"n", where "n" counts from 0 to the number of instances minus one.

Legend Symbols and notation are used as follows:

• Weight in data notation: Left is high order column, right is low order

column

• Active low notation:  $\overline{xxx}$  (pin or signal name is over-scored) or

/xxx (slash before signal name)

• Memory map address: High order at high stage and low order at low

stage

Note Additional remark or tip

Caution Item deserving extra attention

Numeric notation: • Binary: xxxx or xxx<sub>B</sub>

• Decimal: xxxx

Hexadecimal: xxxx<sub>H</sub> or 0x xxxx

**Prefixes** representing powers of 2 (address space, memory capacity):

• K (kilo):  $2^{10} = 1024$

M (mega): 2<sup>20</sup> = 1024<sup>2</sup> = 1,048,576

G (giga): 2<sup>30</sup> = 1024<sup>3</sup> = 1,073,741,824

Register contents: X, x = don't care

Diagrams Block diagrams do not necessarily show the exact wiring in hardware but the

functional structure.

Timing diagrams are for functional explanation purposes only, without any

relevance to the real hardware implementation.

Further Information For further information see <a href="http://www.renesas.eu/">http://www.renesas.eu/</a>.

$\begin{tabular}{ll} SuperFlash^{(R)} & SuperFlash^{(R)} is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan. \\ \end{tabular}$

This product uses  $SuperFlash^{(R)}$  technology licensed from Silicon Technology, Inc.

FlexRay™ FlexRay™ is a trademark of DaimlerChrysler AG.

FlexRay™ IP- The FlexRay™ IP-Module is licensed from the Robert Bosch GmbH.

Module

## **Table of Contents**

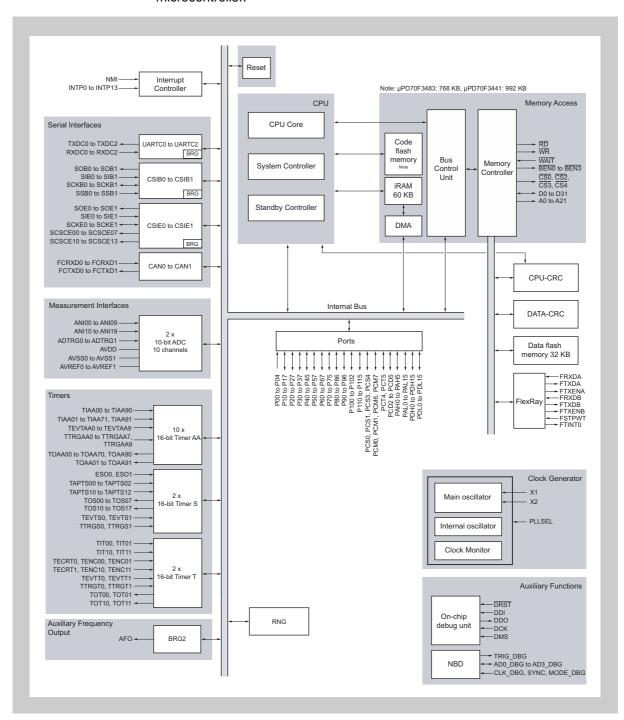

| Chap | ter 1   | Introduction                     | 20 |

|------|---------|----------------------------------|----|

| 1.1  | Genera  | ıl                               | 20 |

| 1.2  | Feature | es Summary                       | 21 |

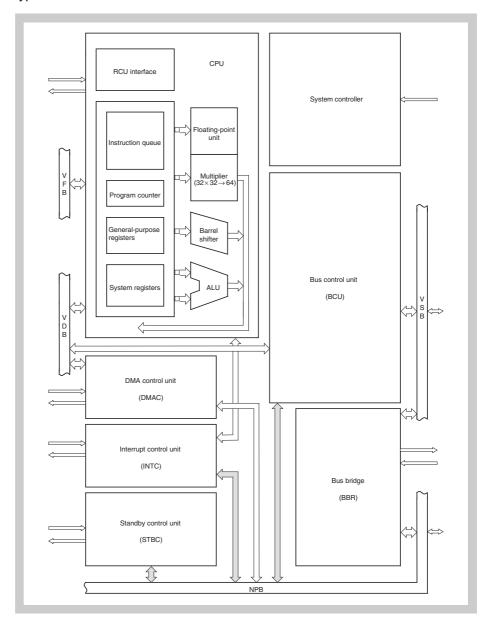

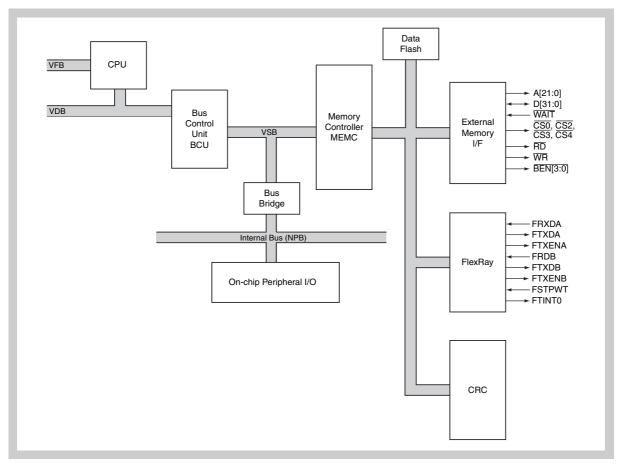

| 1.3  | Descrip | otion                            | 24 |

|      | 1.3.1   | Internal units                   | 25 |

|      | 1.3.2   | Structure of the manual          | 27 |

|      |         |                                  |    |

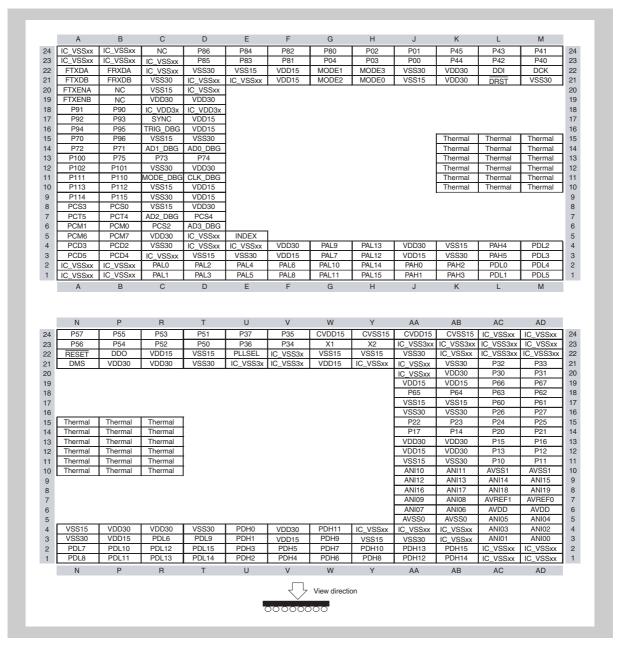

| Chap | ter 2   | Pin Functions                    | 28 |

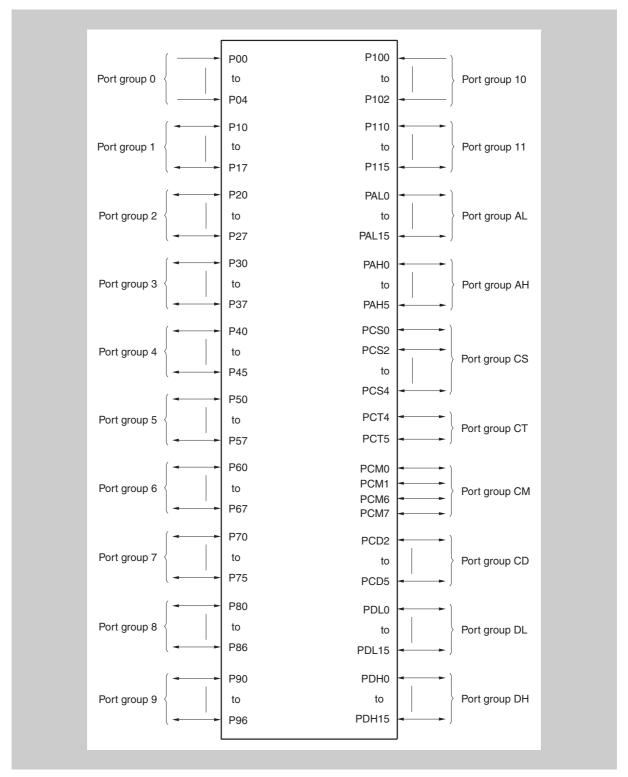

| 2.1  | Overvi  | ew                               | 28 |

|      | 2.1.1   | Description                      | 29 |

|      | 2.1.2   | Terms                            | 32 |

|      | 2.1.3   | Noise elimination                | 32 |

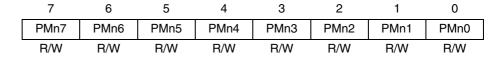

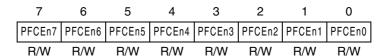

| 2.2  | Port Gr | oup Configuration Registers      | 33 |

|      | 2.2.1   | Overview                         | 33 |

|      | 2.2.2   | Pin function configuration       | 34 |

|      | 2.2.3   | Pin data input/output            | 38 |

|      | 2.2.4   | Emergency shut-off configuration | 40 |

|      | 2.2.5   | Write enable register            | 44 |

| 2.3  | Port Gr | oup Configuration                | 46 |

|      | 2.3.1   | Port group configuration lists   | 46 |

|      | 2.3.2   | Non-port pins                    | 50 |

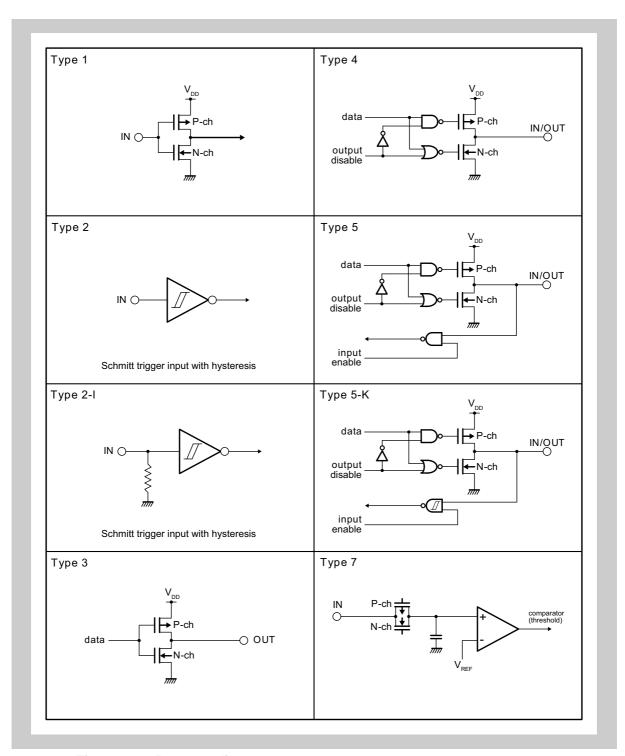

|      | 2.3.3   | Port Types Diagrams              | 52 |

|      | 2.3.4   | Alphabetic pin function list     | 53 |

|      | 2.3.5   | Port group 0                     | 61 |

|      | 2.3.6   | Port group 1                     | 62 |

|      | 2.3.7   | Port group 2                     | 63 |

|      | 2.3.8   | Port group 3                     | 64 |

|      | 2.3.9   | Port group 4                     | 65 |

|      | 2.3.10  | Port group 5                     |    |

|      | 2.3.11  | Port group 6                     |    |

|      | 2.3.12  | Port group 7                     |    |

|      | 2.3.13  | Port group 8                     |    |

|      | 2.3.14  | Port group 9                     |    |

|      | 2.3.15  | Port group 10                    |    |

|      | 2.3.16  | Port group 11                    |    |

|      | 2.3.17  | Port group AL                    |    |

|      | 2.3.18  | Port group AH                    |    |

|      | 2.3.19  | Port group CS                    |    |

|      | 2.3.20  | Port group CT                    |    |

|      | 2.3.21  | Port group CM                    |    |

|      | 2.3.22  | Port group CD                    |    |

|      | 2.3.23  | Port group DL                    |    |

|      | 2.3.24  | Port group DH                    |    |

| 2.4  |         | Elimination                      |    |

|      | 2.4.1   | Analog filtered inputs           |    |

|      | 2.4.2   | Digitally filtered inputs        |    |

| 2.5  | Pin Fur | nctions during and after Reset   | 88 |

| 2.6<br>2.7 | Recommended Connection of unused Pins |                                              |      |

|------------|---------------------------------------|----------------------------------------------|------|

| Chap       | ter 3                                 | CPU System Functions                         | . 93 |

| 3.1        | Overvi                                | ew                                           | . 93 |

|            | 3.1.1                                 | Description                                  | . 94 |

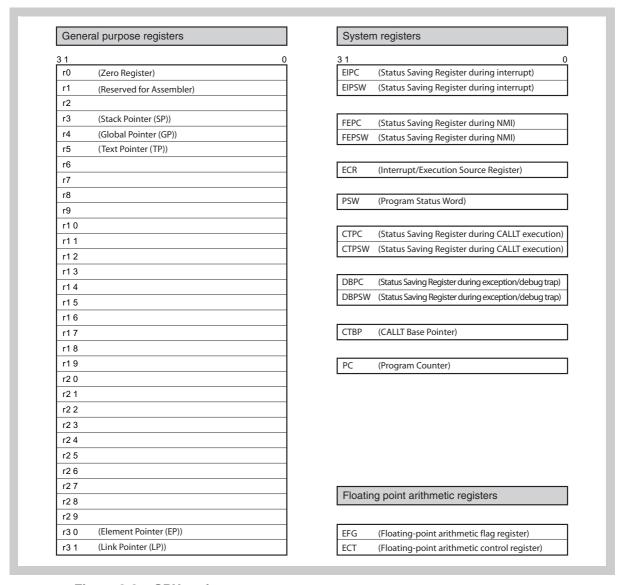

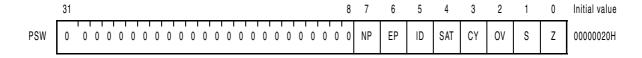

| 3.2        | CPU Re                                | egister Set                                  | . 95 |

|            | 3.2.1                                 | General purpose registers (r0 to r31)        | . 96 |

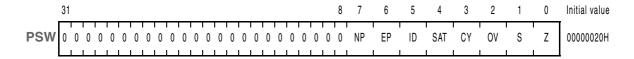

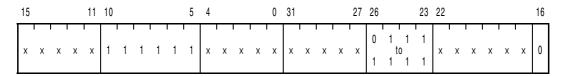

|            | 3.2.2                                 | System register set                          | . 97 |

|            | 3.2.3                                 | Floating-point arithmetic registers          | 104  |

| 3.3        | Operat                                | ion Modes                                    | 106  |

|            | 3.3.1                                 | Normal operation mode                        | 106  |

|            | 3.3.2                                 | Flash programming mode                       | 106  |

|            | 3.3.3                                 | Boundary scan mode                           | 107  |

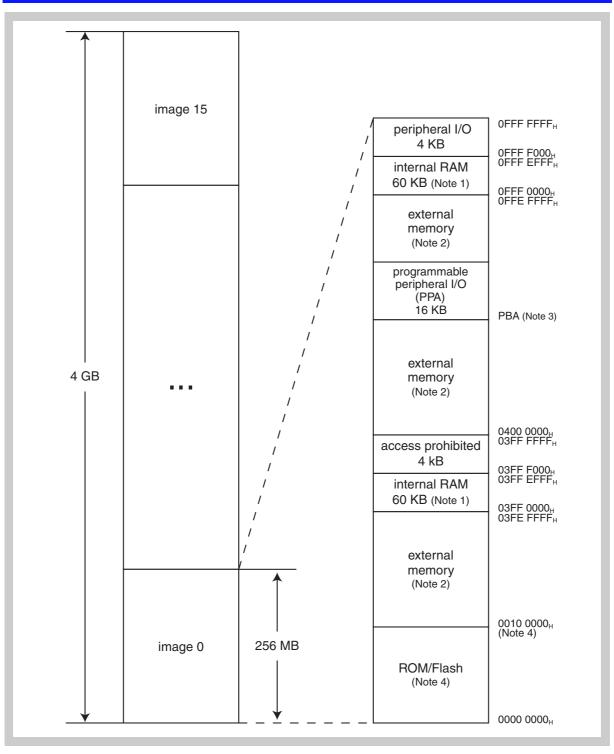

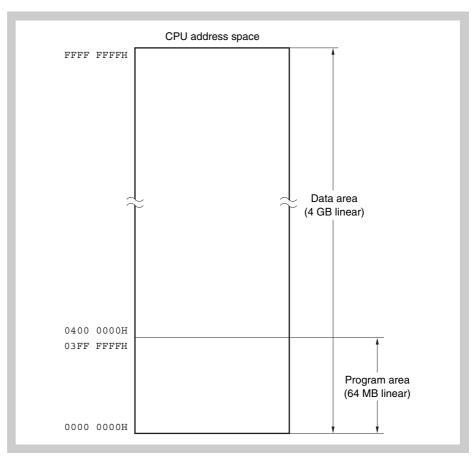

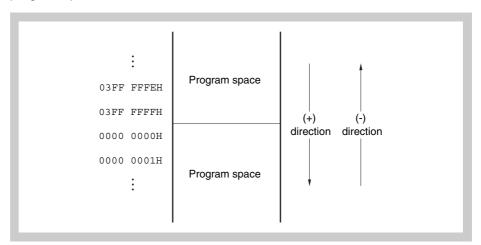

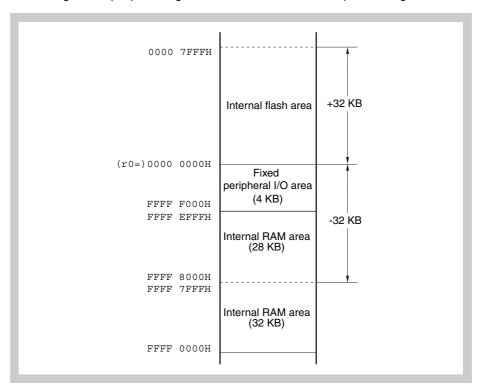

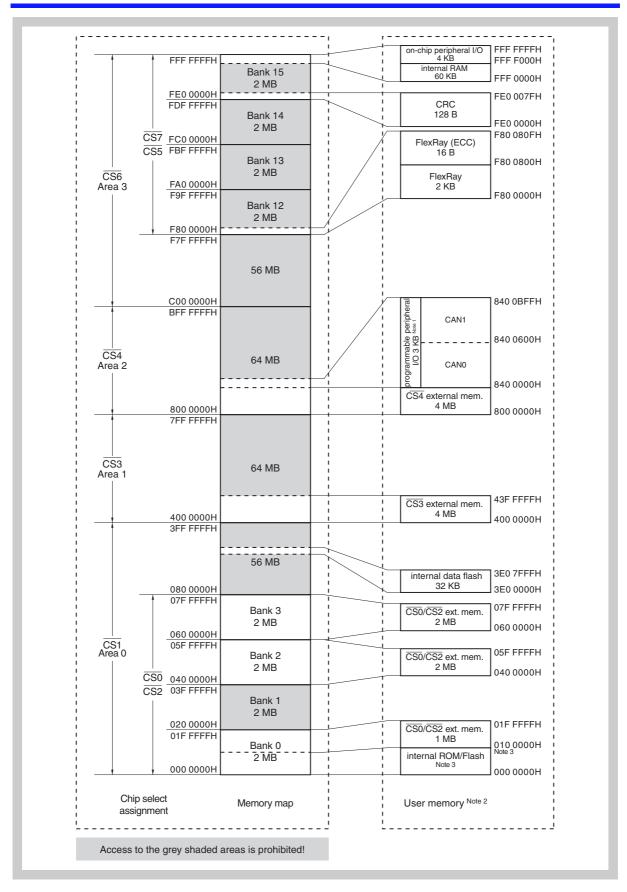

| 3.4        | Addres                                | ss Space.                                    | 107  |

|            | 3.4.1                                 | CPU address space and physical address space | 107  |

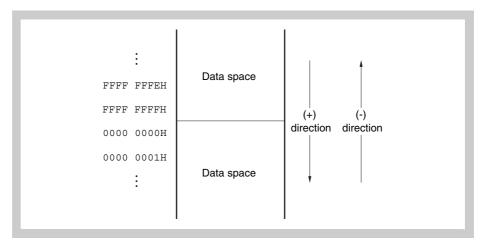

|            | 3.4.2                                 | Program and data space                       |      |

| 3.5        | Memor                                 | y                                            | 111  |

|            | 3.5.1                                 | Memory areas                                 |      |

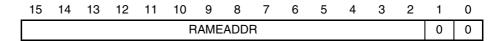

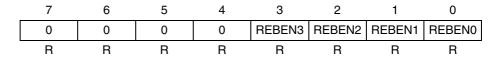

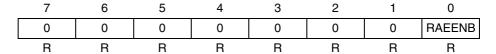

| 3.6        | RAM E                                 | CC error detection                           |      |

|            | 3.6.1                                 | RAM ECC initialization                       | 113  |

|            | 3.6.2                                 | RAM ECC registers                            | 114  |

|            | 3.6.3                                 | RAM ECC function check                       |      |

|            | 3.6.4                                 | Recommended use of data address space        | 118  |

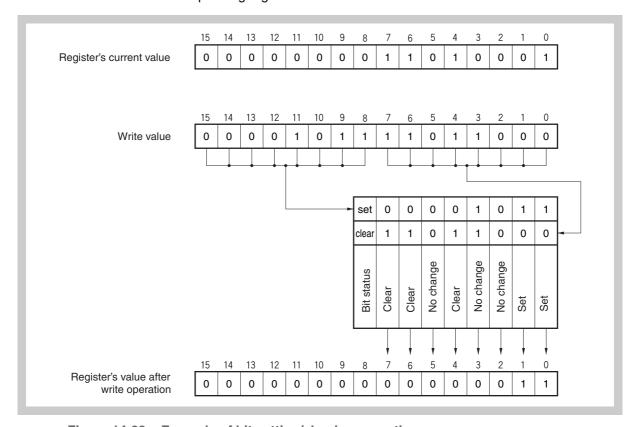

| 3.7        | Write P                               | Protected Registers                          |      |

|            |                                       | · ·                                          |      |

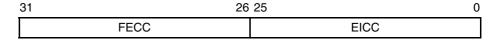

| Chap       | ter 4                                 | Interrupt Controller (INTC)                  | 121  |

| 4.1        | Feature                               | es                                           | 121  |

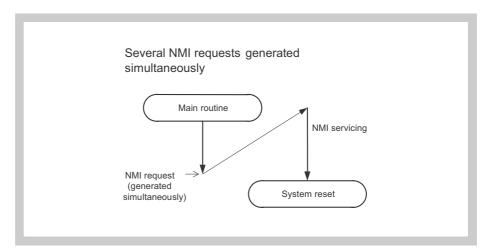

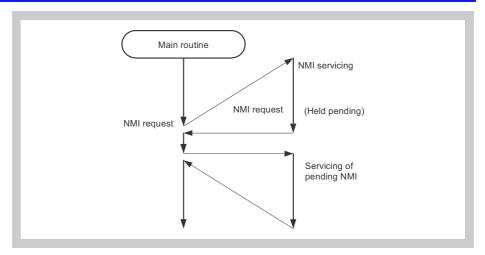

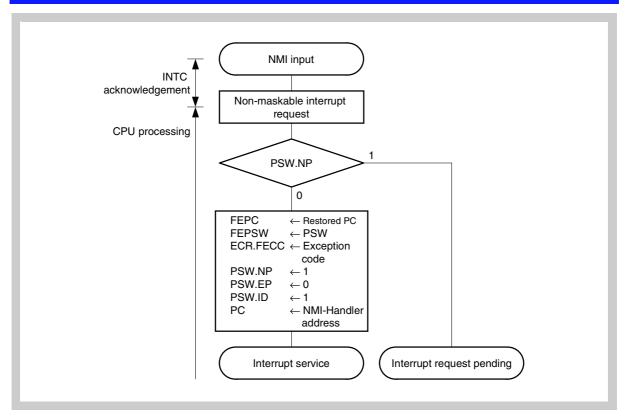

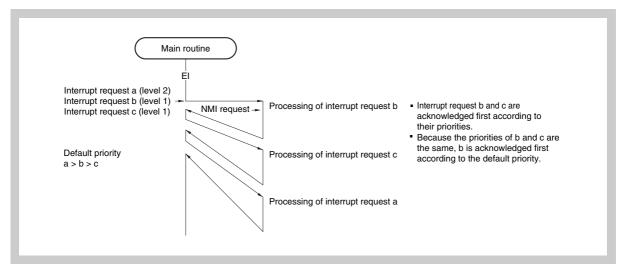

| 4.2        | Non-Ma                                | askable Interrupts                           | 128  |

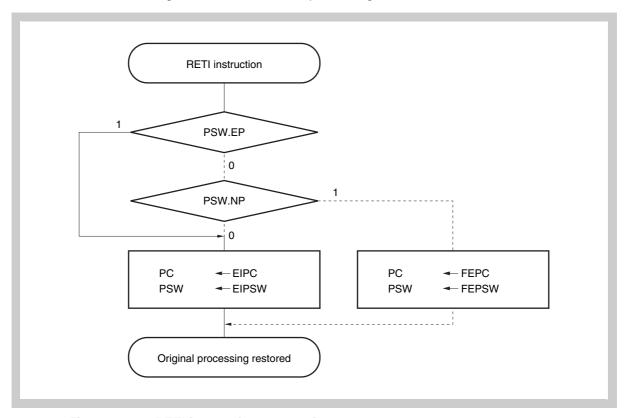

|            | 4.2.1                                 | Operation                                    | 129  |

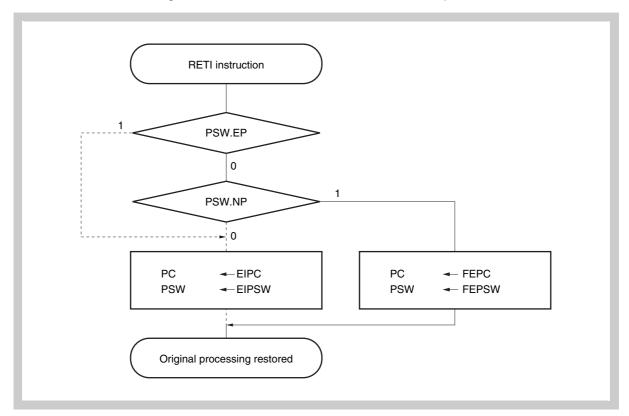

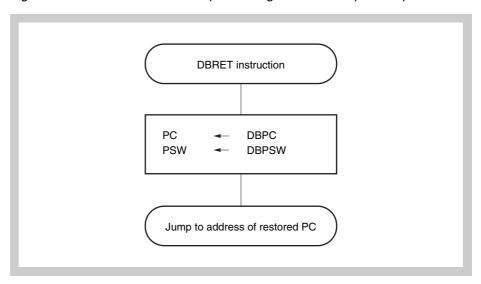

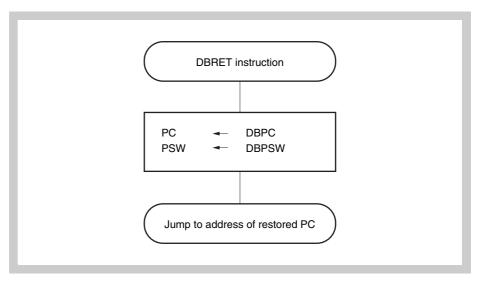

|            | 4.2.2                                 | Restore                                      | 131  |

|            | 4.2.3                                 | Non-maskable interrupt status flag (NP)      | 132  |

|            | 4.2.4                                 | NMI control                                  | 132  |

| 4.3        | Maskal                                | ble Interrupts                               | 133  |

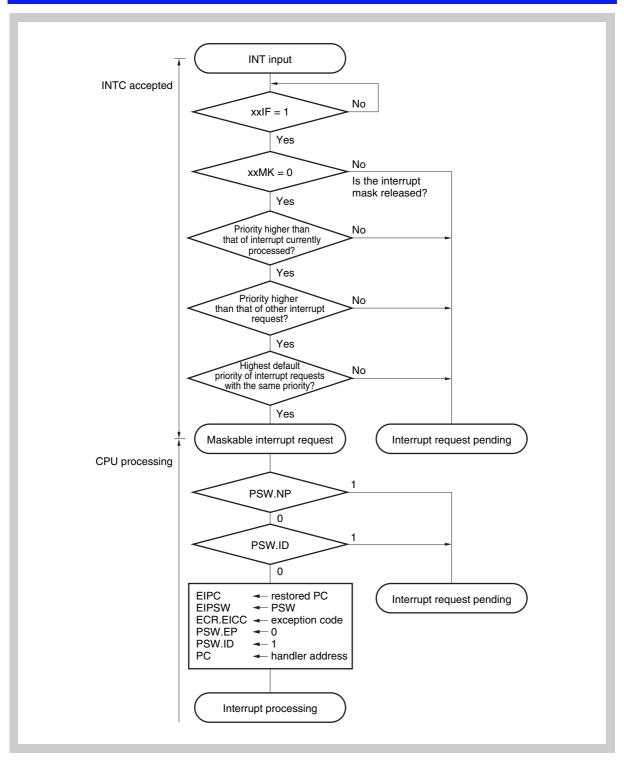

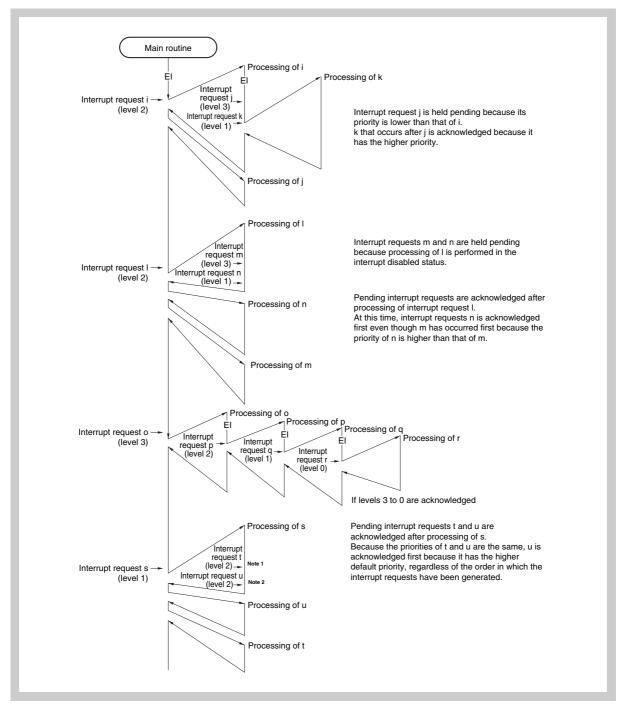

|            | 4.3.1                                 | Operation                                    | 133  |

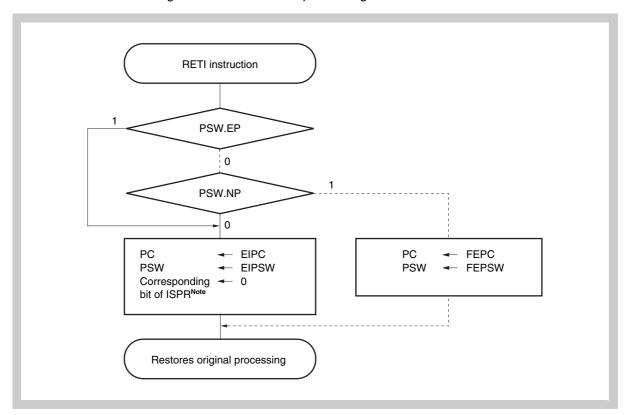

|            | 4.3.2                                 | Restore                                      | 135  |

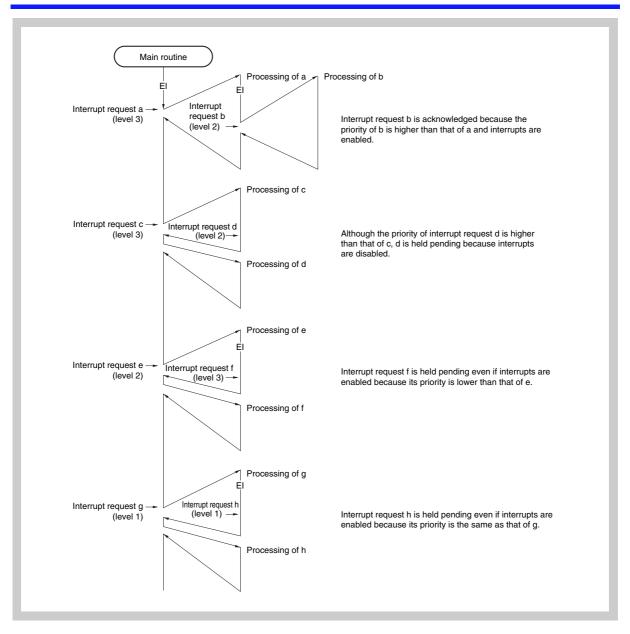

|            | 4.3.3                                 | Priorities of maskable interrupts            | 136  |

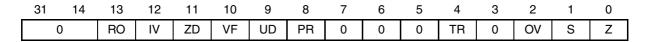

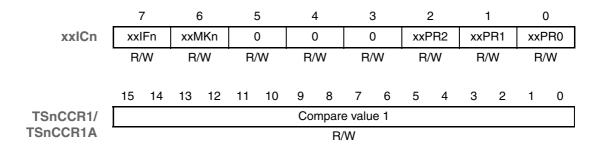

|            | 4.3.4                                 | xxICn - Maskable interrupts control register | 140  |

|            | 4.3.5                                 | IMR0 to IMR7 - Interrupt mask registers      | 143  |

|            | 4.3.6                                 | ISPR - In-service priority register          | 145  |

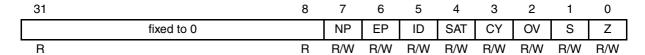

|            | 4.3.7                                 | Maskable interrupt status flag (ID)          | 146  |

|            | 4.3.8                                 | External maskable interrupts                 | 146  |

| 4.4        | Edge a                                | nd Level Detection Configuration             | 147  |

| 4.5        | _                                     | pt Sharing                                   |      |

| 4.6        |                                       | re Exception                                 |      |

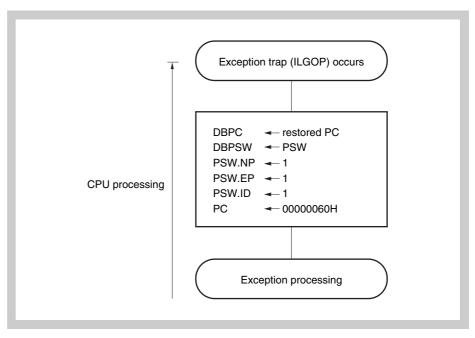

|            | 4.6.1                                 | Operation                                    |      |

|            | 4.6.2                                 | Restore                                      |      |

|            | 4.6.3                                 | Exception status flag (EP)                   |      |

| 4.7        |                                       | ion Trap                                     |      |

|      | 4.7.1   | Illegal opcode definition                       |       |

|------|---------|-------------------------------------------------|-------|

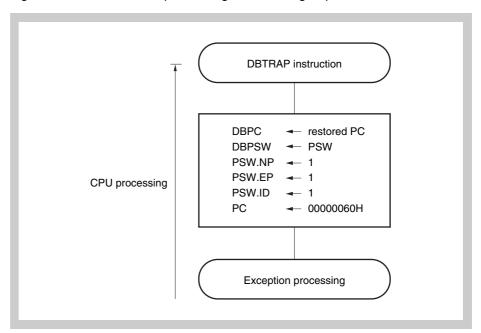

|      | 4.7.2   | Debug trap                                      |       |

| 4.8  | -       | le Interrupt Processing Control                 |       |

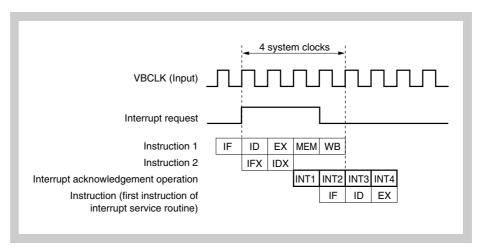

| 4.9  |         | pt Response Time                                |       |

| 4.10 | Period  | s in Which Interrupts Are Not Acknowledged      | 164   |

| Chap | oter 5  | CRC Function (CRC)                              | 165   |

| 5.1  |         | es                                              |       |

|      | 5.1.1   | CPU-CRC                                         | . 165 |

|      | 5.1.2   | DATA-CRC                                        | . 165 |

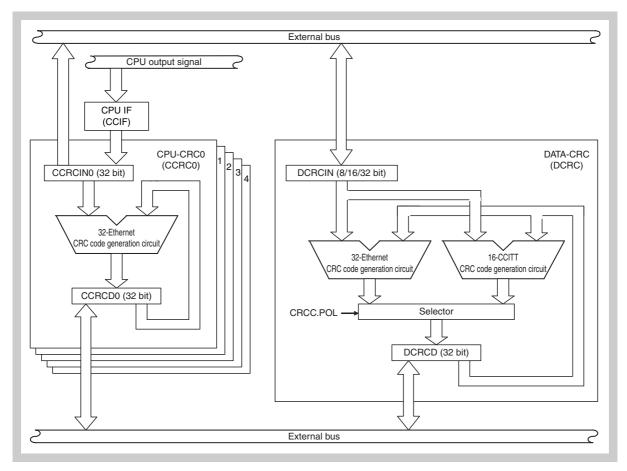

| 5.2  | Config  | uration                                         | . 166 |

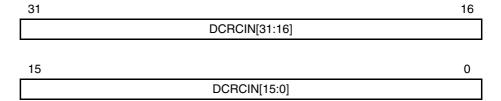

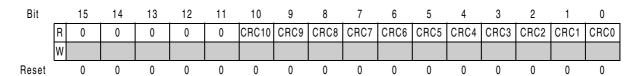

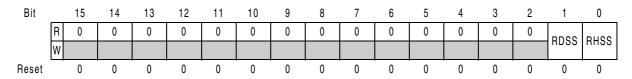

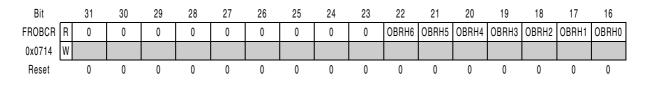

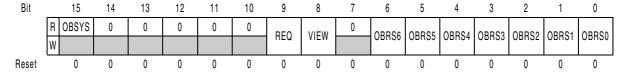

| 5.3  | CRC R   | egisters                                        | . 167 |

| 5.4  | Operat  | tion                                            | . 172 |

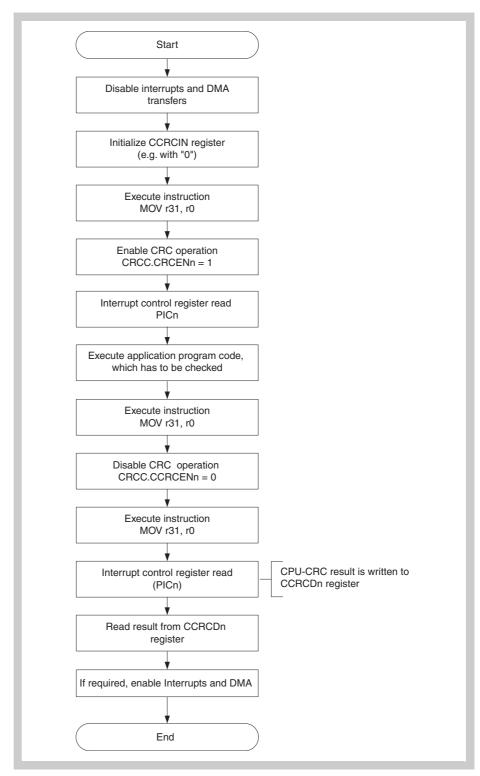

|      | 5.4.1   | CPU-CRC                                         | . 172 |

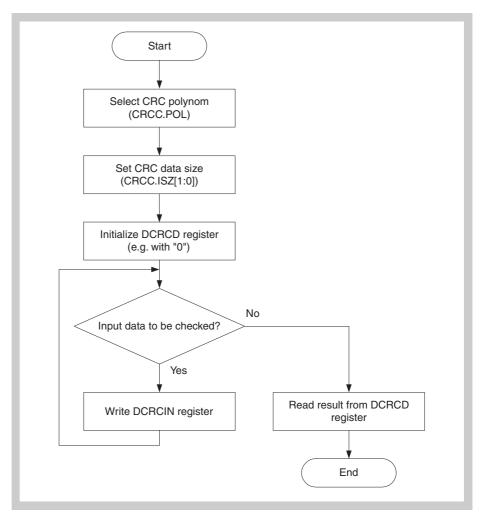

|      | 5.4.2   | DATA-CRC                                        | 174   |

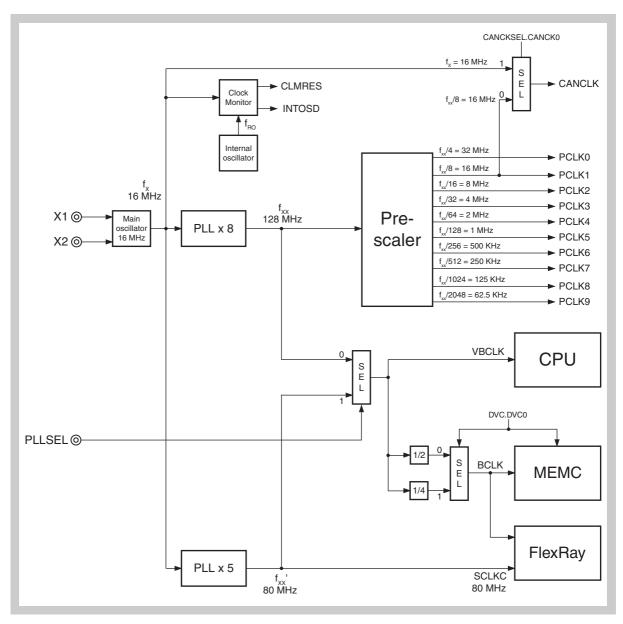

| Char | oter 6  | Clock Generator                                 | 175   |

| 6.1  |         | ew                                              |       |

| 0    | 6.1.1   | Features                                        |       |

|      | 6.1.2   | Description                                     |       |

| 6.2  | Contro  | l Registers                                     |       |

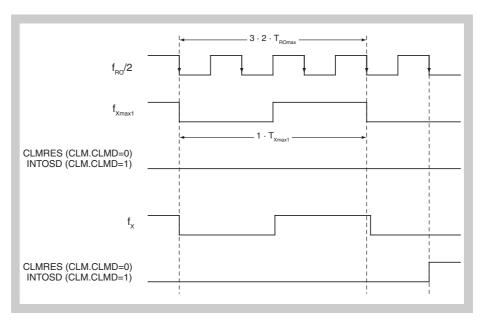

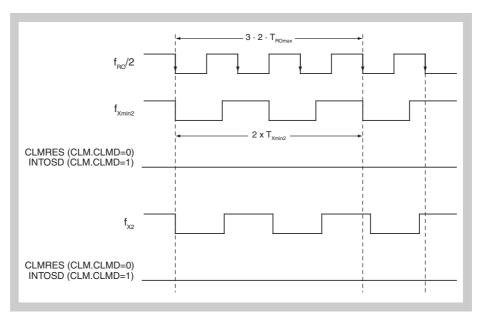

| 6.3  |         | Monitor                                         |       |

|      | 6.3.1   | Clock Monitor registers                         | . 179 |

|      | 6.3.2   | Operation of the Clock Monitor                  | . 181 |

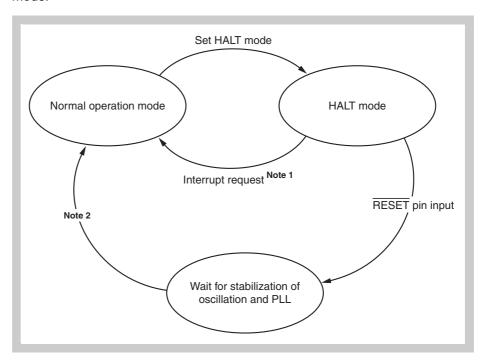

| 6.4  | Power   | Save Control                                    | 183   |

|      | 6.4.1   | HALT mode                                       | . 184 |

| Char | oter 7  | Flash Memory                                    | 186   |

| 7.1  | Code F  | Flash Memory Overview                           |       |

|      | 711     | Code flash memory features                      |       |

|      | 7.1.2   | Code flash memory mapping                       |       |

|      | 7.1.3   | Code flash memory functional outline            |       |

|      | 7.1.4   | Code flash memory erasure and rewrite           | . 191 |

|      | 7.1.5   | Code flash memory error detection               | . 193 |

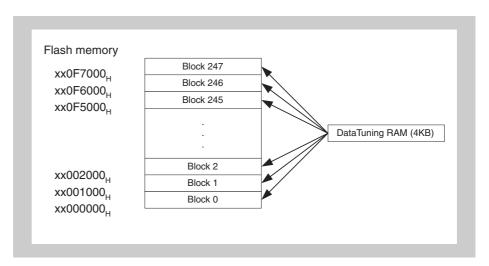

| 7.2  | Data F  | lash Memory                                     | . 195 |

|      | 7.2.1   | Data flash memory features                      | . 195 |

|      | 7.2.2   | Data flash memory map                           | . 195 |

|      | 7.2.3   | Data flash control register                     | . 196 |

|      | 7.2.4   | Data flash reading                              | . 196 |

|      | 7.2.5   | Data flash writing                              | 196   |

| 7.3  | Flash I | Programming with Flash Programmer               | 197   |

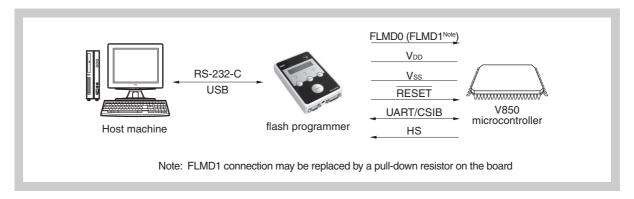

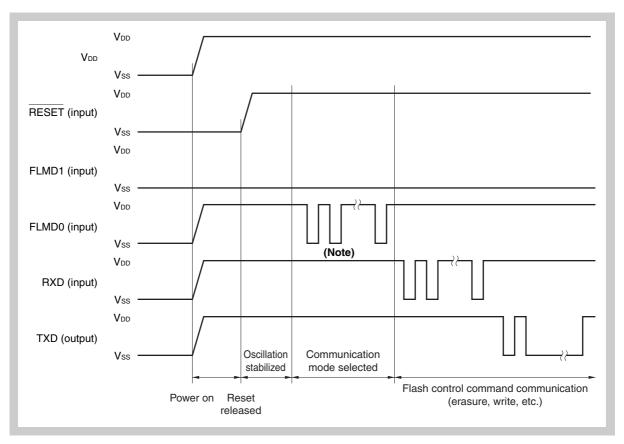

|      | 7.3.1   | Programming environment                         |       |

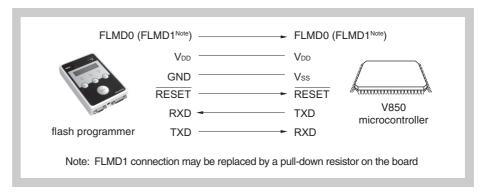

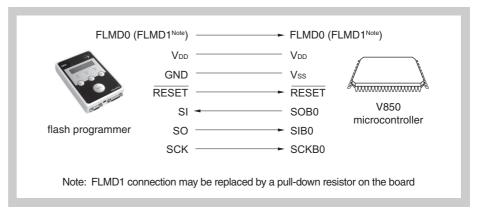

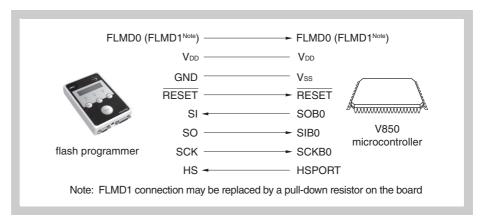

|      | 7.3.2   | Communication mode                              |       |

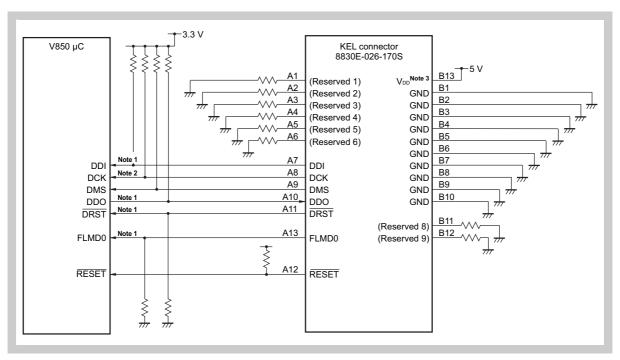

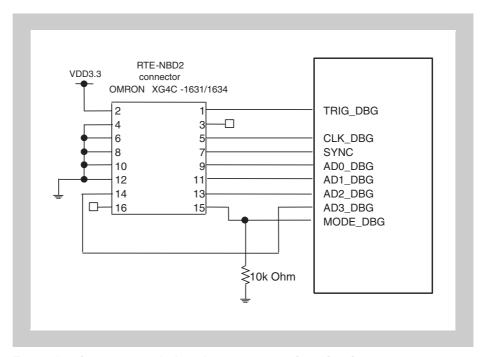

|      | 7.3.3   | Pin connection with flash programmer PG-FP5     |       |

| _    | 7.3.4   | Flash memory programming control                |       |

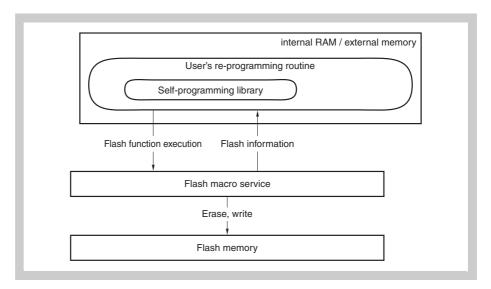

| 7.4  |         | Flash Self-Programming                          |       |

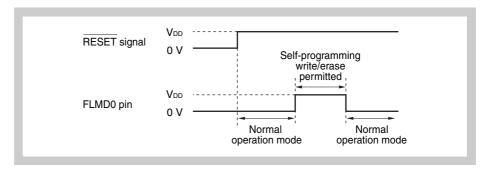

|      | 7.4.1   | Self-programming enable                         |       |

|      | 7.4.2   | Self-programming library functions              |       |

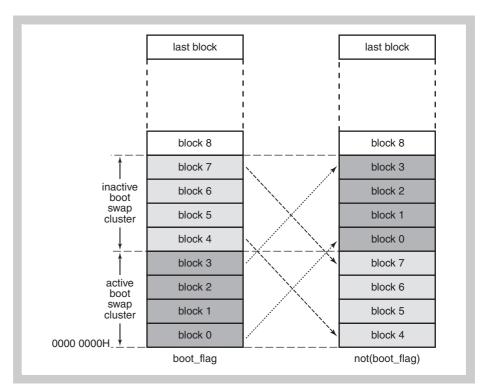

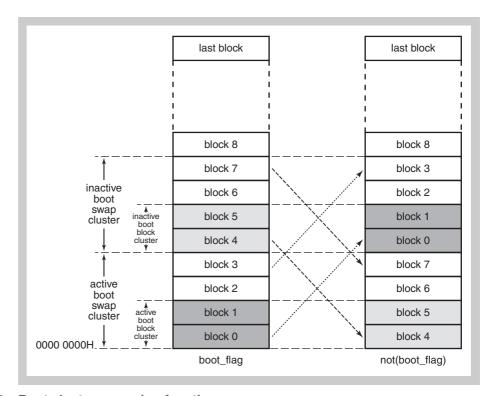

|      | 7.4.3   | Secure self-programming (boot cluster swapping) | 210   |

|      | 7.4.4   | Interrupt handling during flash self-programming | . 213 |

|------|---------|--------------------------------------------------|-------|

| Chap | ter 8   | Data Protection and Security                     | . 214 |

| 8.1  | Overvie | ew                                               | . 214 |

| 8.2  | N-Wire  | Debug Interface Protection                       | . 214 |

| 8.3  | Flash P | Programmer and Self-Programming Protection       | . 216 |

|      |         |                                                  |       |

| Chap |         | Bus and Memory Control (BCU, MEMC)               |       |

| 9.1  | Overvie | ew                                               | . 219 |

|      | 9.1.1   | Description                                      |       |

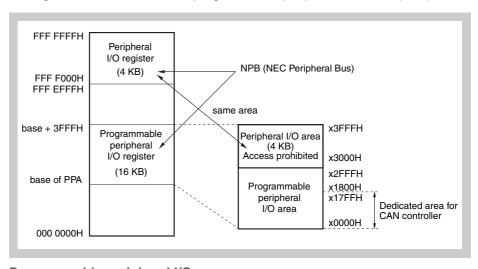

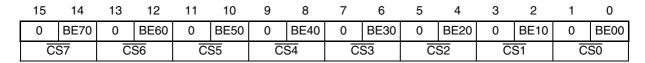

|      | 9.1.2   | Memory areas/banks and chip select signals       | . 222 |

|      | 9.1.3   | Peripheral I/O areas                             | . 225 |

|      | 9.1.4   | Data flash access                                | . 227 |

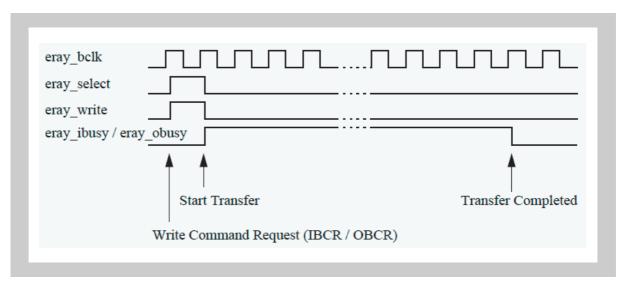

|      | 9.1.5   | FlexRay access                                   | . 228 |

|      | 9.1.6   | CRC module access                                | . 229 |

|      | 9.1.7   | Chip select priority control                     | . 230 |

|      | 9.1.8   | Bus properties                                   | . 231 |

|      | 9.1.9   | Boundary operation conditions                    | . 232 |

|      | 9.1.10  | Initialization for access to external devices    | . 233 |

|      | 9.1.11  | External bus during internal access              | . 234 |

| 9.2  | Registe | ers                                              | . 235 |

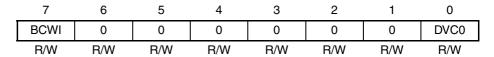

|      | 9.2.1   | BCU registers                                    | . 236 |

|      | 9.2.2   | Memory Controller registers                      | . 243 |

| 9.3  | Configu | uration of Memory Access                         | . 252 |

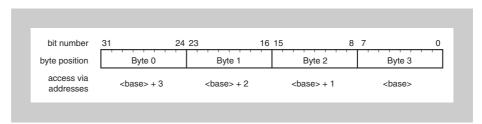

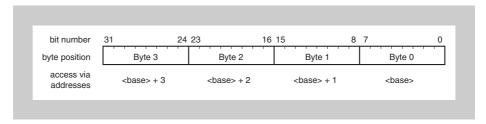

|      | 9.3.1   | Endian format                                    | . 252 |

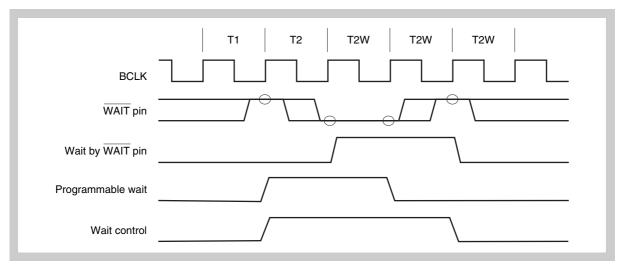

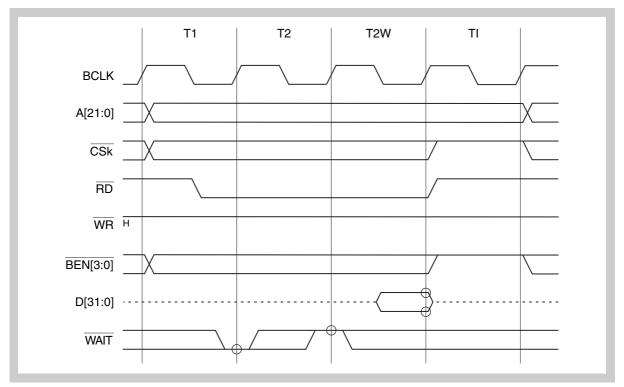

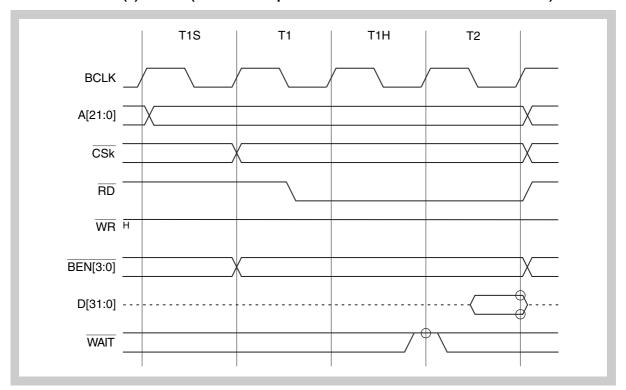

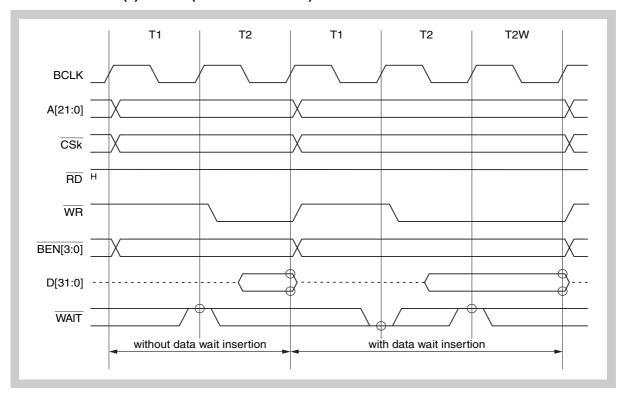

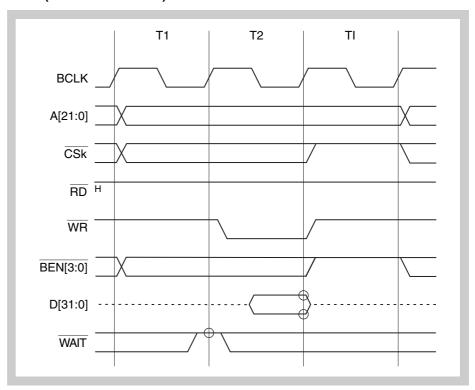

|      | 9.3.2   | Wait functions                                   |       |

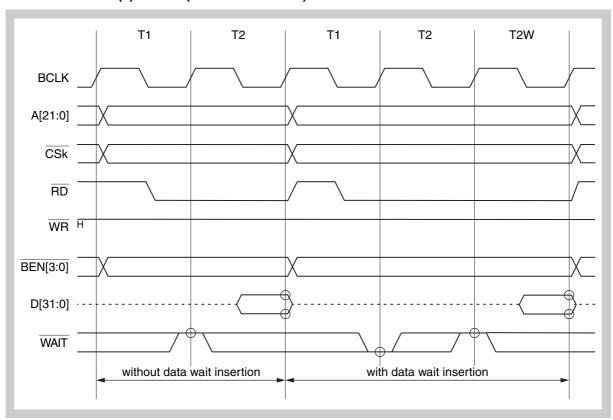

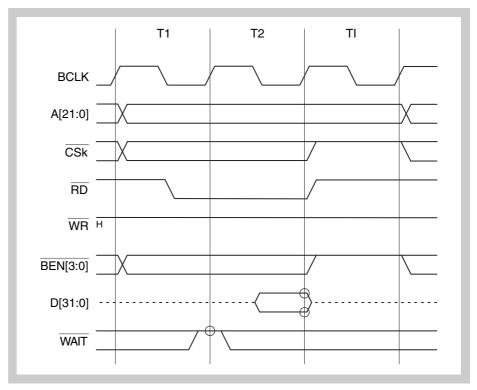

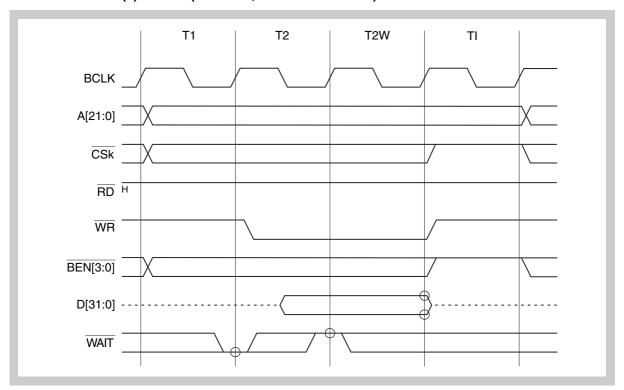

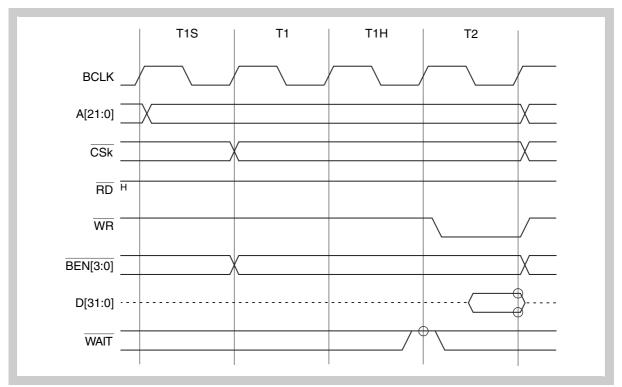

|      | 9.3.3   | External wait function                           |       |

| 9.4  |         | al Devices Interface Timing                      |       |

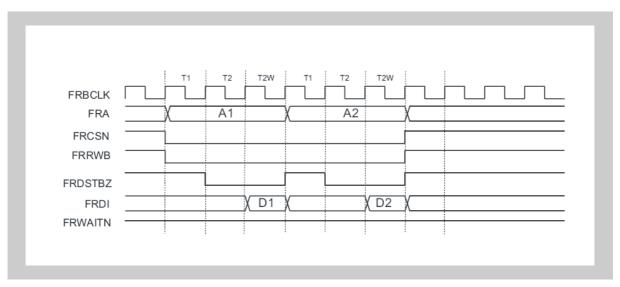

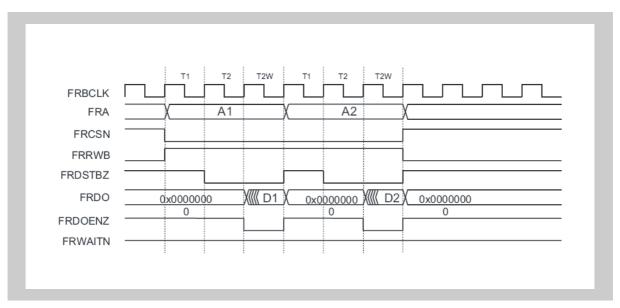

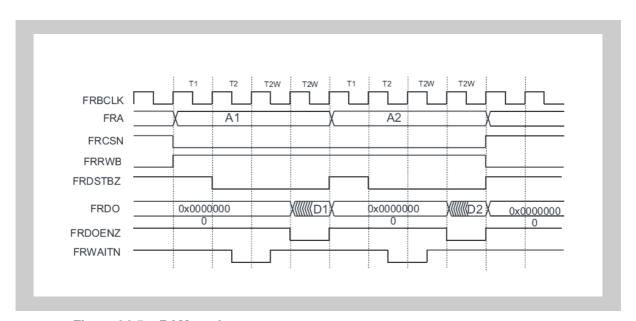

|      | 9.4.1   | SRAM, external ROM, external I/O access          |       |

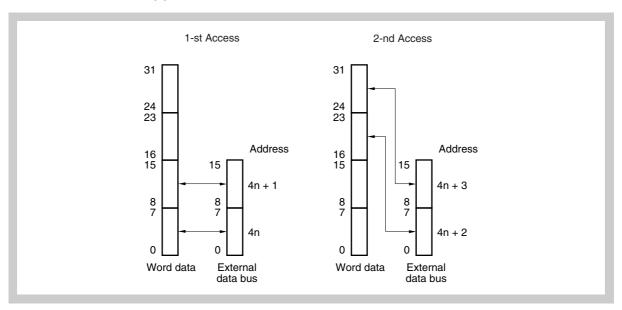

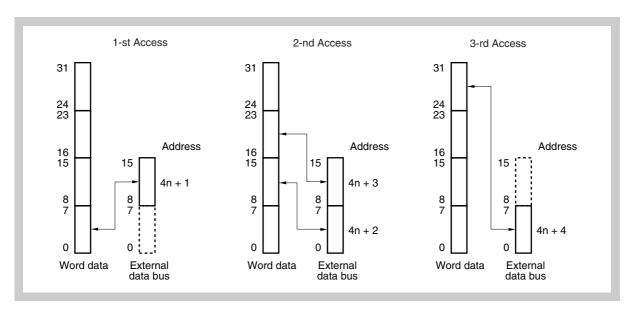

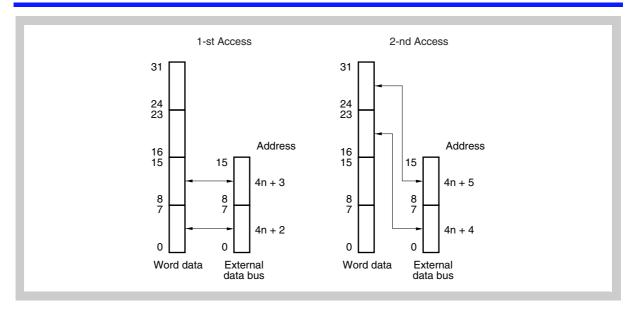

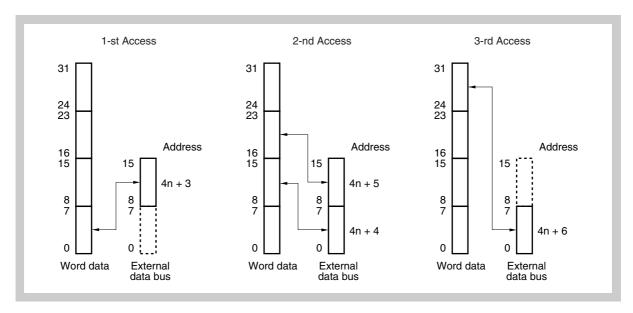

| 9.5  | Data Ad | ccess Order                                      |       |

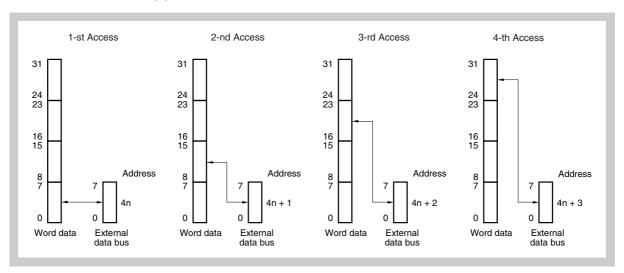

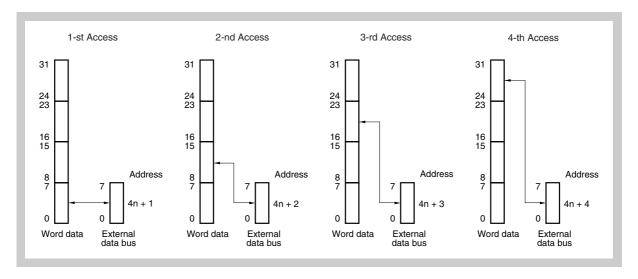

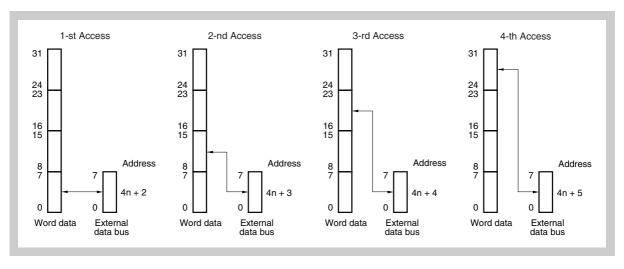

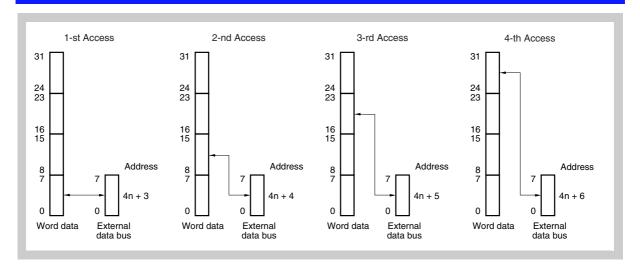

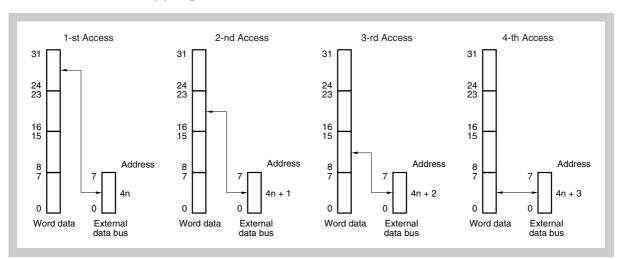

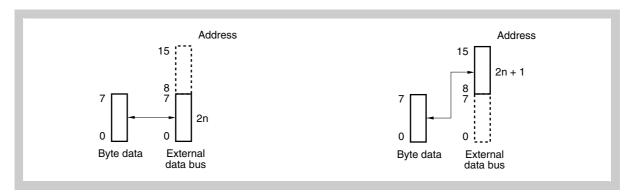

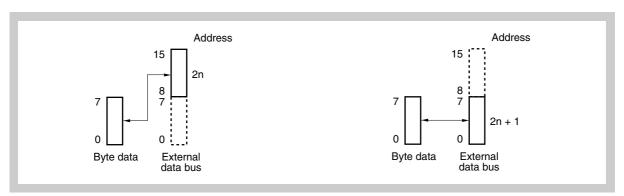

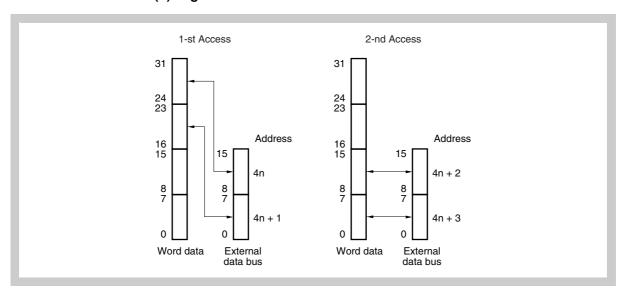

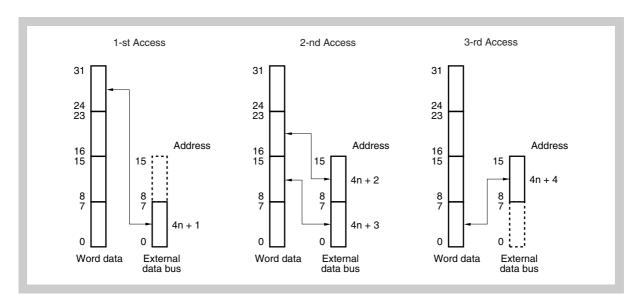

|      | 9.5.1   | Access to 8-bit data busses                      |       |

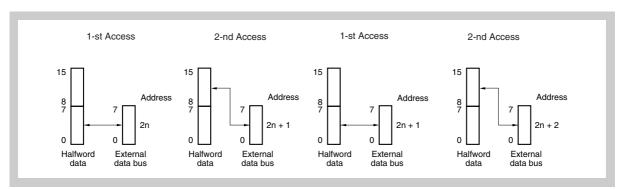

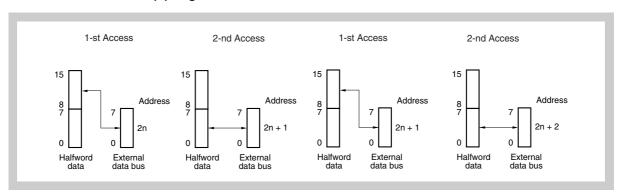

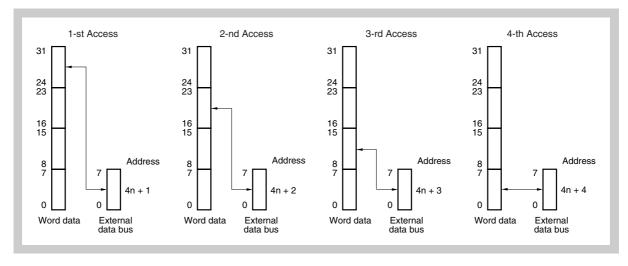

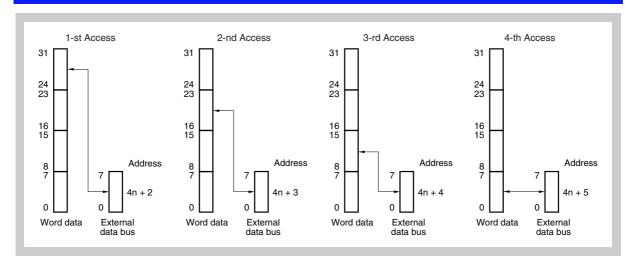

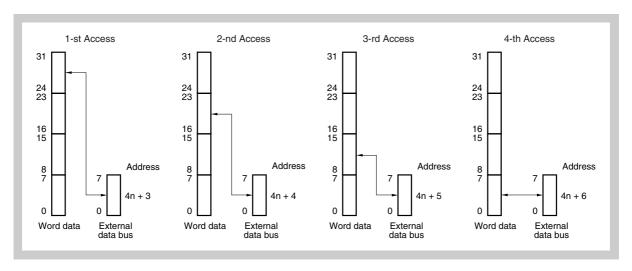

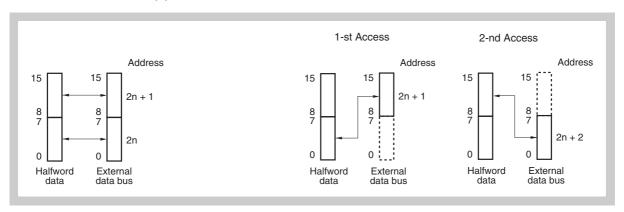

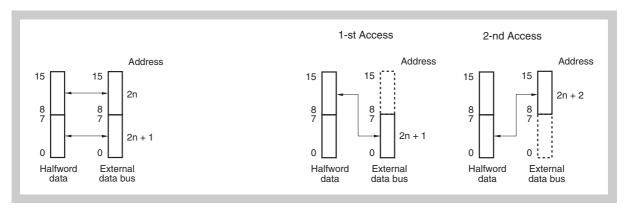

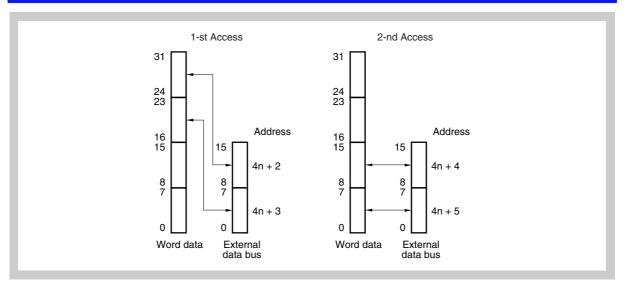

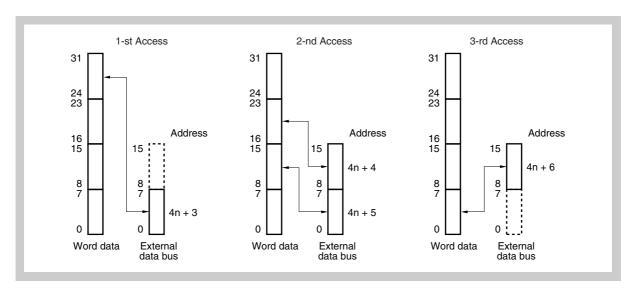

|      |         | Access to 16-bit data busses                     |       |

|      | 0.0.2   |                                                  | 00    |

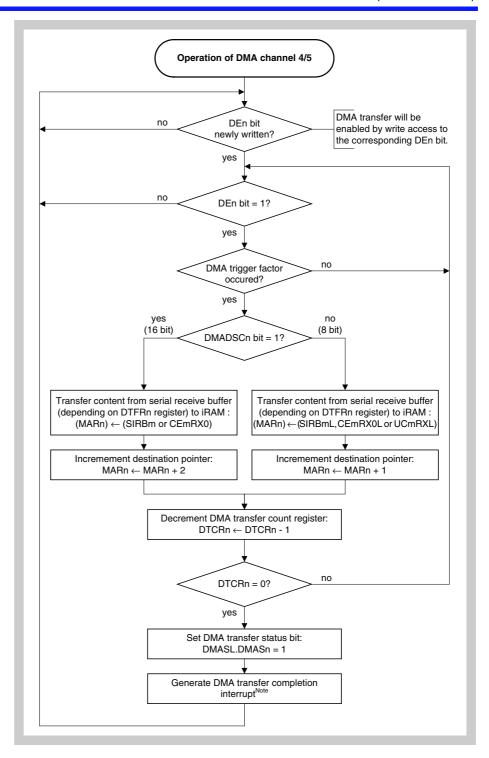

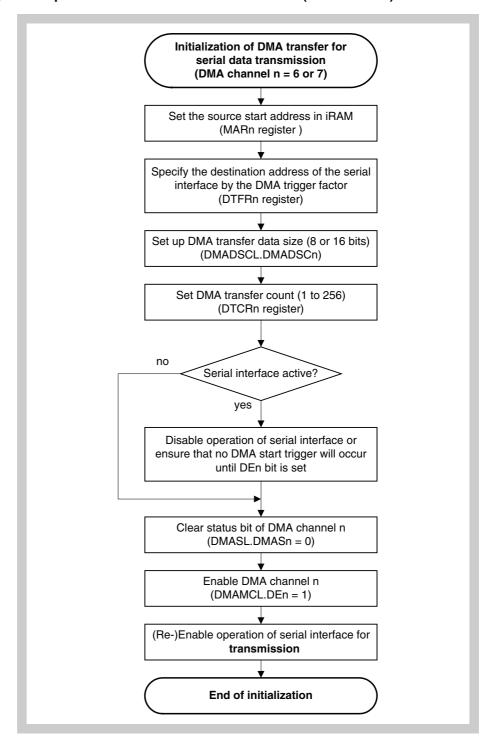

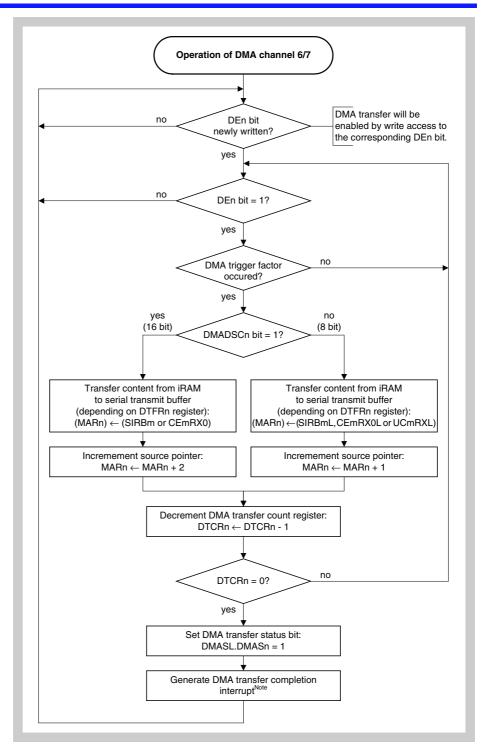

| Chap | ter 10  | DMA Functions (DMA Controller)                   | . 274 |

| 10.1 | Overvie | 9WW                                              | . 274 |

|      | 10.1.1  | Principle of operation                           | . 274 |

|      | 10.1.2  | Forcible termination of DMA transfer             | . 275 |

|      | 10.1.3  | DMA interrupt function                           | . 276 |

| 10.2 | Registe | ers                                              | . 277 |

| 10.3 | Transfe | er Details                                       | . 286 |

|      | 10.3.1  | DMA transfer from A/D Converter                  | . 286 |

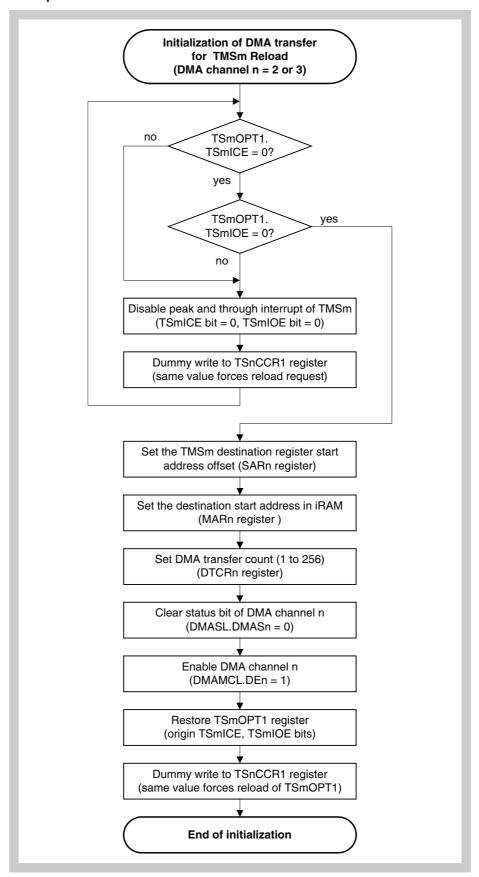

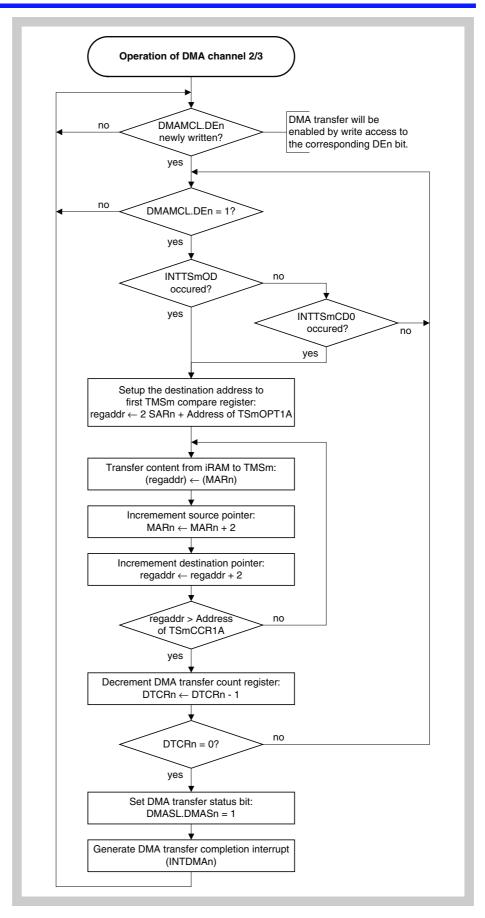

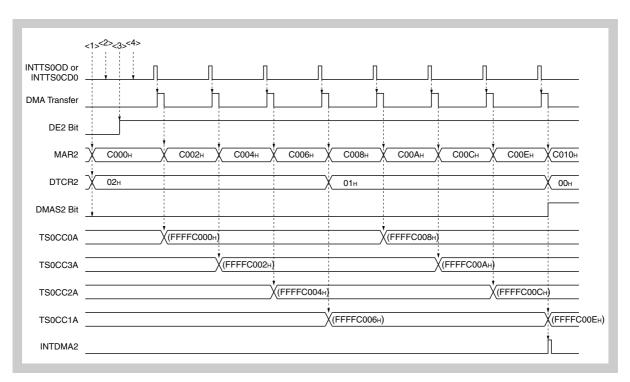

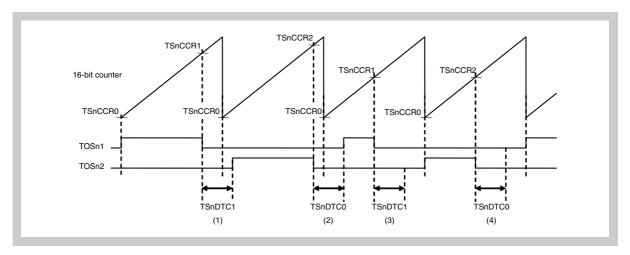

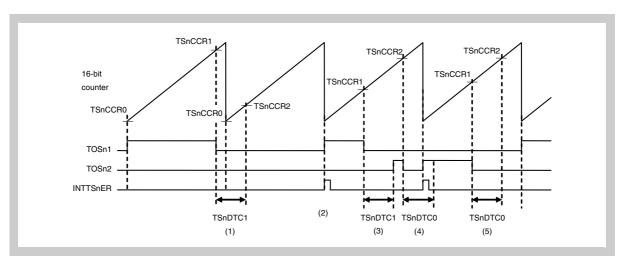

|      | 10.3.2  | DMA transfer to Timer S                          | . 290 |

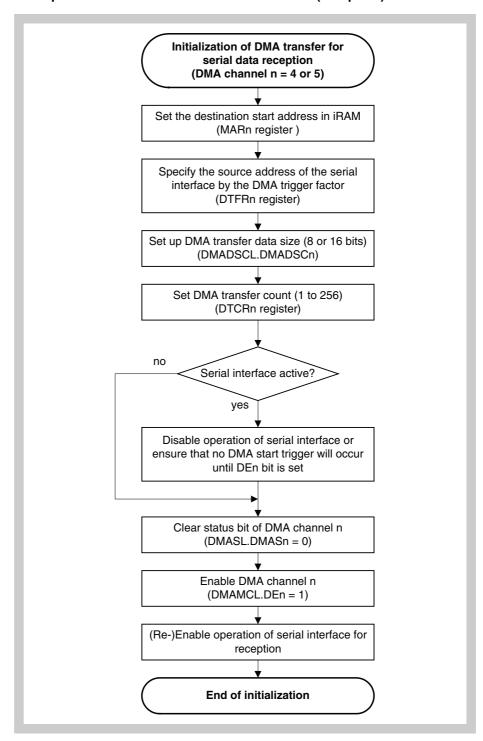

|      | 10.3.3  | DMA transfer to/from serial interfaces           | . 295 |

|      | 10.3.4  | Example of forcible termination of DMA transfer  |       |

|      |         |                                                  |       |

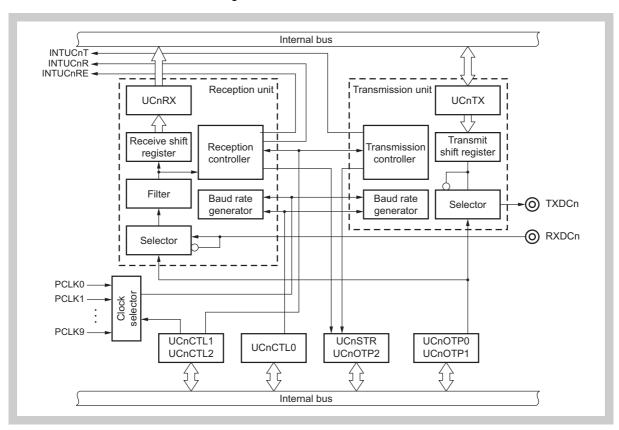

| Chap | ter 11  | Asynchronous Serial Interface (UARTC)            | . 304 |

| 11.1 | Feature | 98                                               | . 304 |

| 11.2 |         | uration                                          |       |

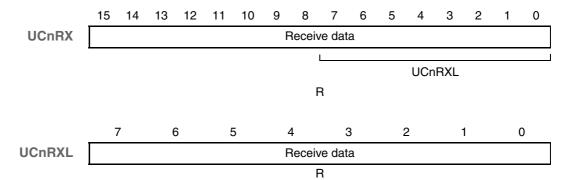

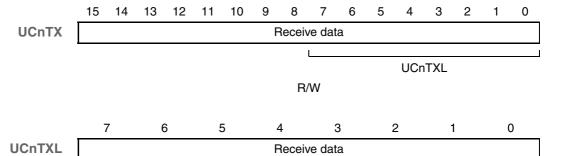

| 11.3 | •       | Registers                                        |       |

| 11.4 | Interru | pt Request Signals                                              | 318  |

|------|---------|-----------------------------------------------------------------|------|

| 11.5 | _       | ion                                                             |      |

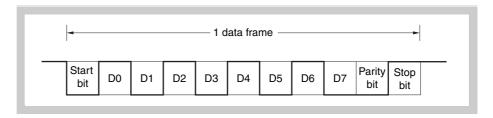

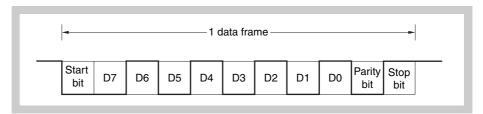

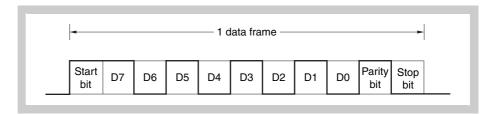

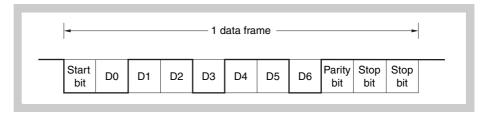

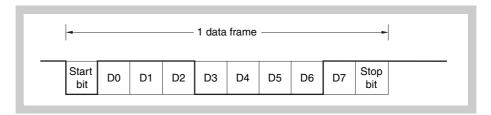

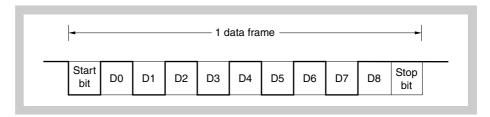

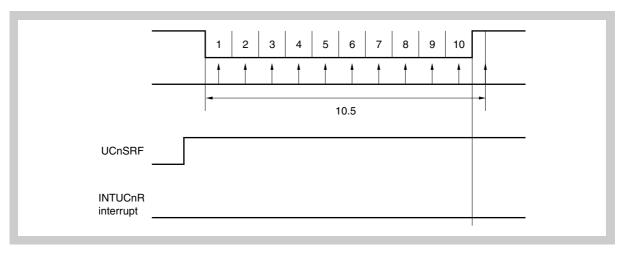

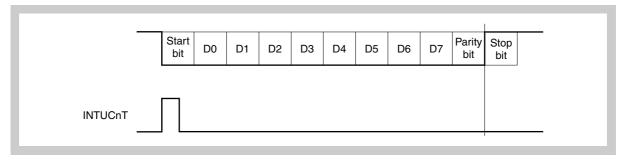

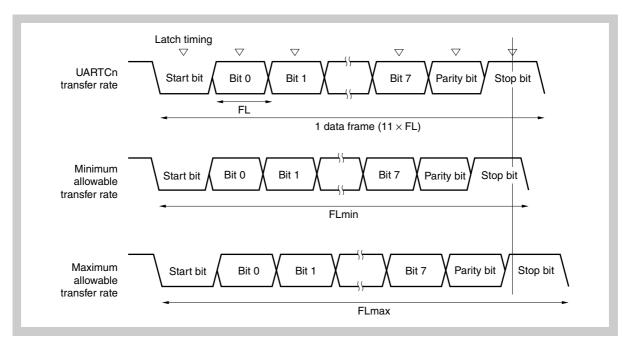

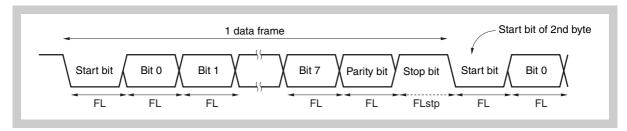

| 11.5 | 11.5.1  | Data format                                                     |      |

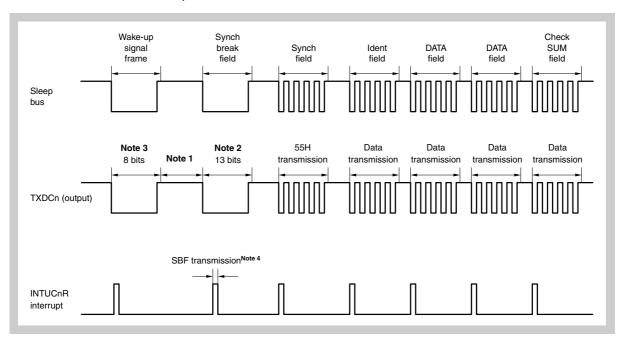

|      | 11.5.1  | SBF transmission/reception format                               |      |

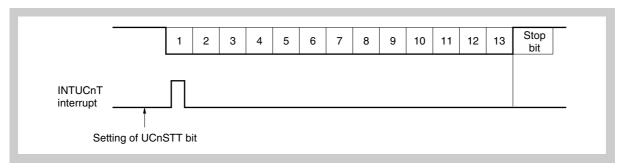

|      | 11.5.2  | SBF transmission                                                |      |

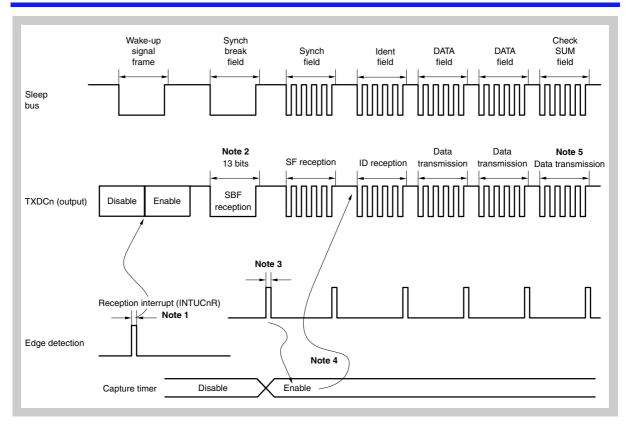

|      | 11.5.3  |                                                                 |      |

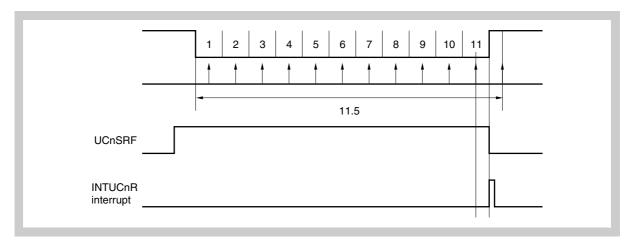

|      | _       | SBF reception                                                   |      |

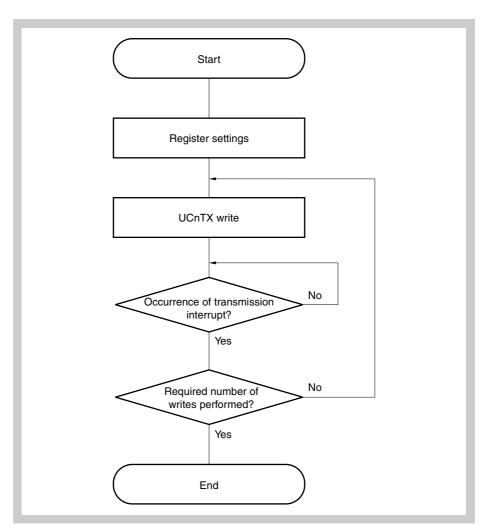

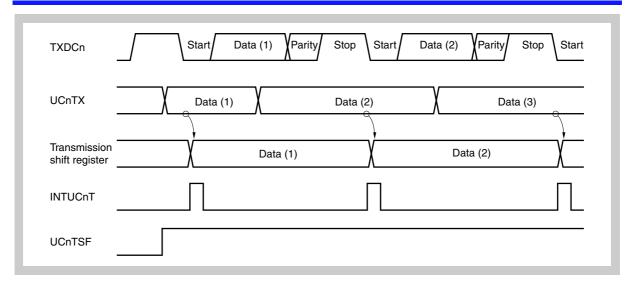

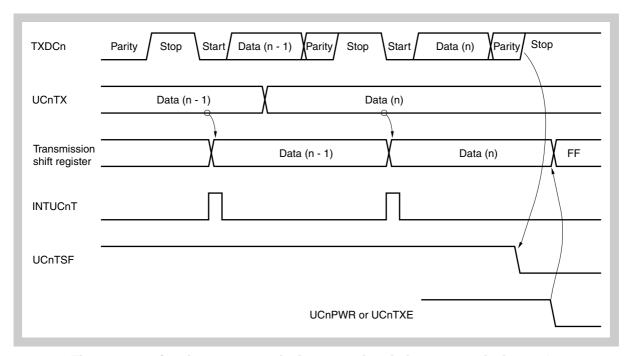

|      | 11.5.5  | UART transmission                                               |      |

|      | 11.5.6  | Continuous transmission procedure                               |      |

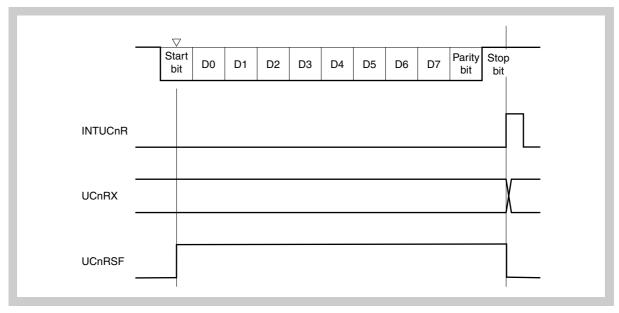

|      | 11.5.7  | UART reception                                                  |      |

|      | 11.5.8  | Reception errors                                                |      |

|      | 11.5.9  | Parity types and operations                                     |      |

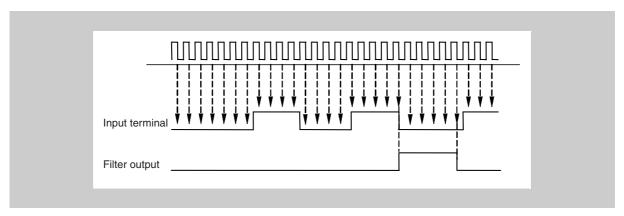

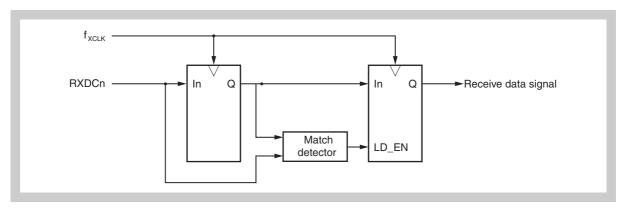

|      |         | Receive data noise filter                                       |      |

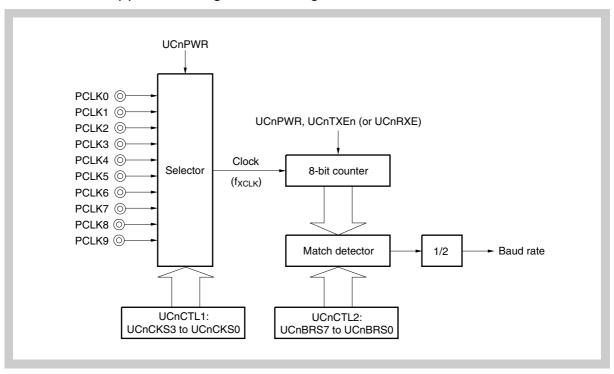

| 11.6 |         | Rate Generator                                                  |      |

| 11.7 | Caution | ns                                                              | 340  |

| 01   |         | OL 1 10 111 ( (OOLD)                                            |      |

| Cha  | oter 12 | Clocked Serial Interface (CSIB)                                 | 341  |

| 12.1 | Feature | 98                                                              | 341  |

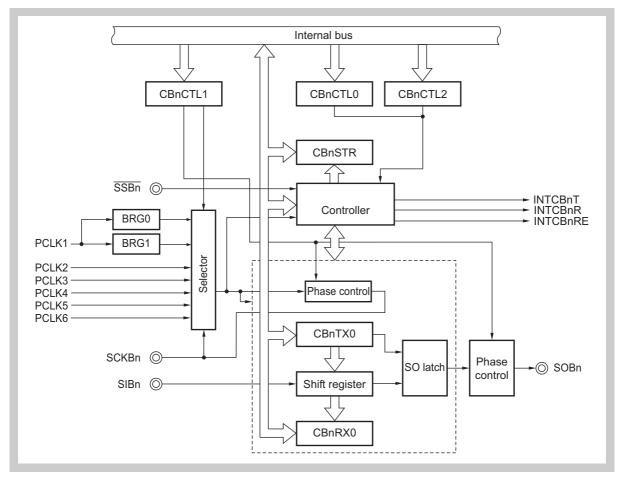

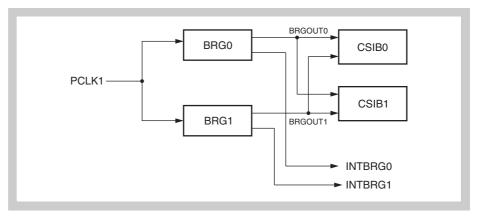

| 12.2 | Config  | uration                                                         | 342  |

| 12.3 | CSIB C  | ontrol Registers                                                | 344  |

| 12.4 | Operati | ion                                                             | 351  |

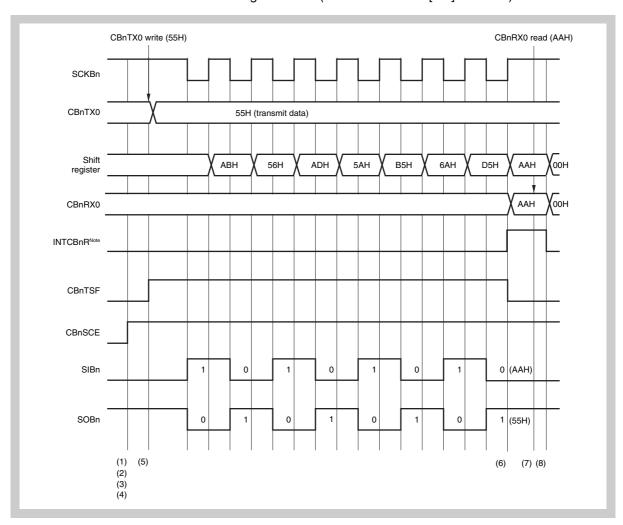

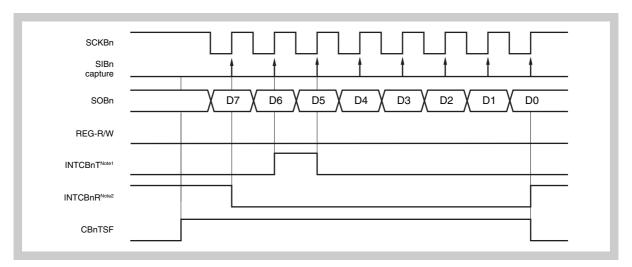

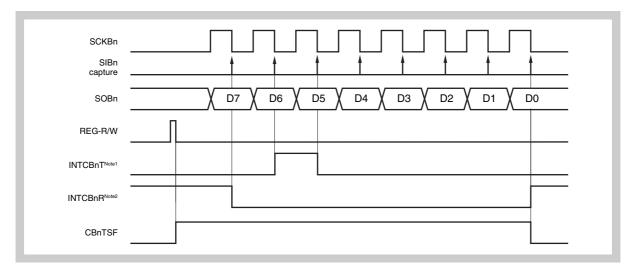

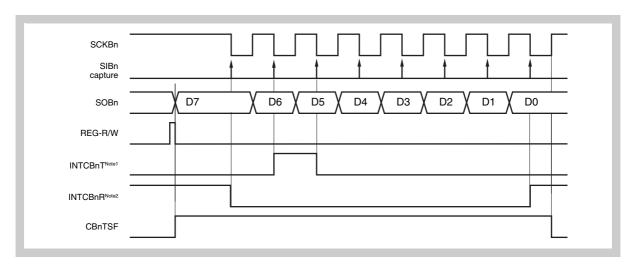

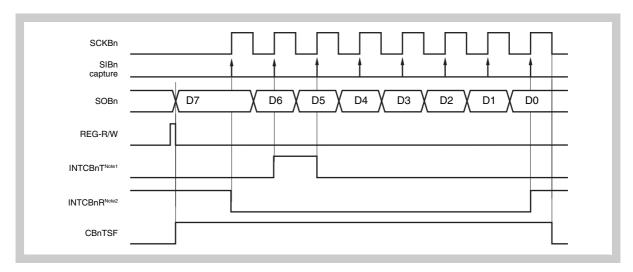

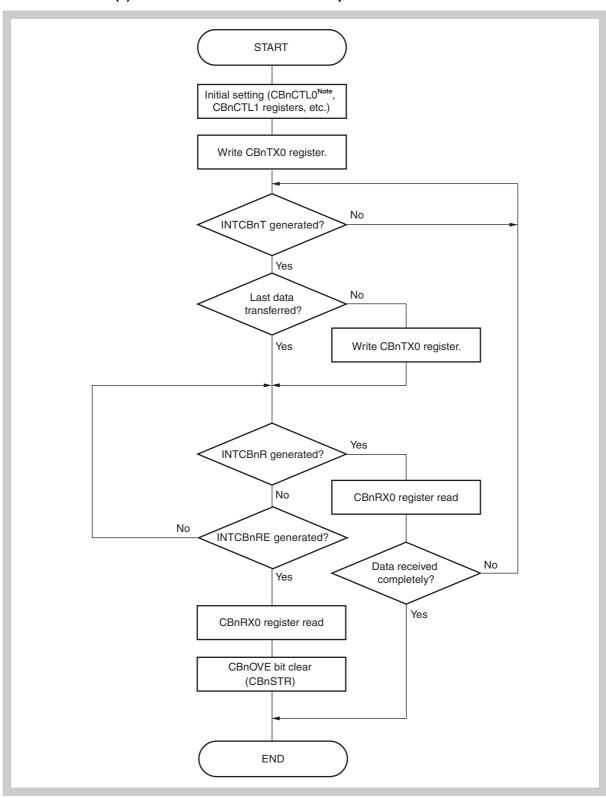

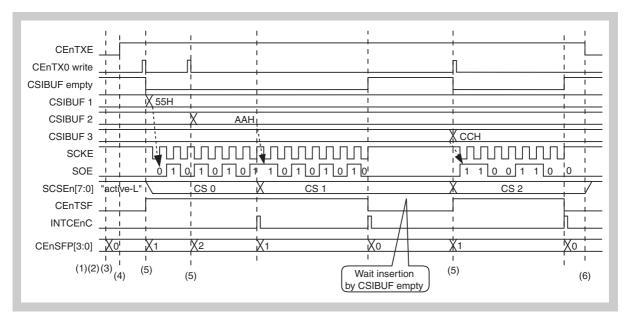

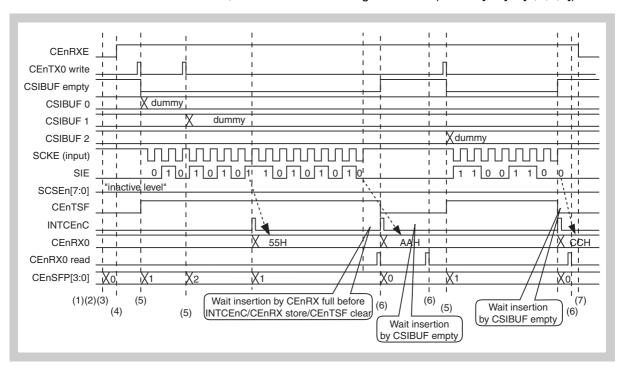

|      | 12.4.1  | Single transfer mode (master mode, transmission/reception mode) | 351  |

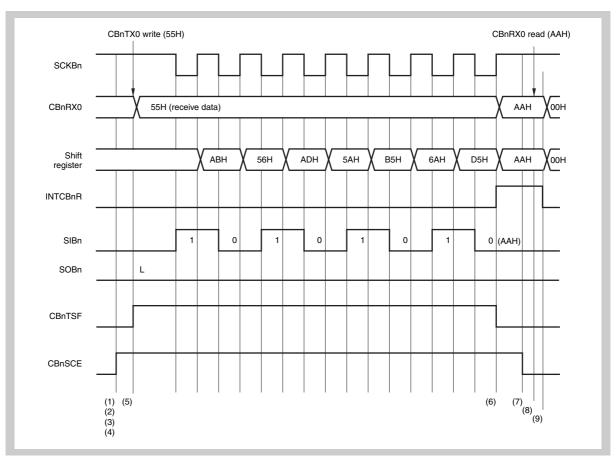

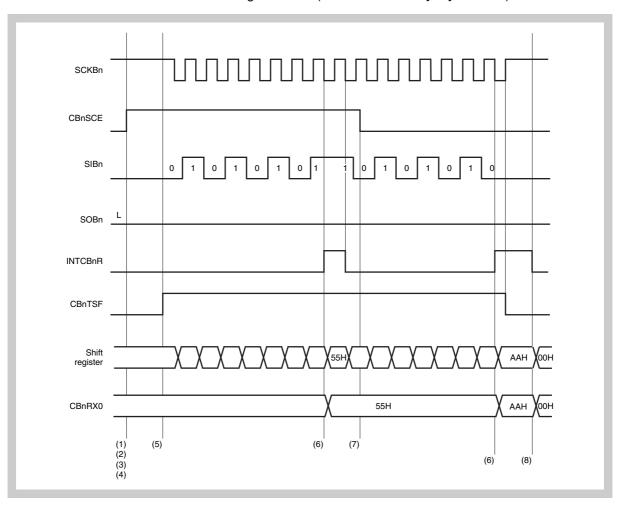

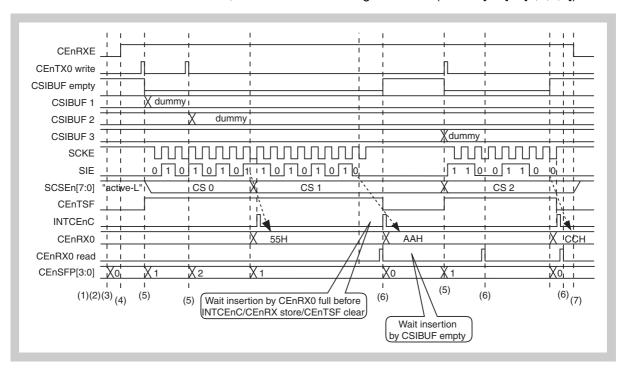

|      | 12.4.2  | Single transfer mode (master mode, reception mode)              | 353  |

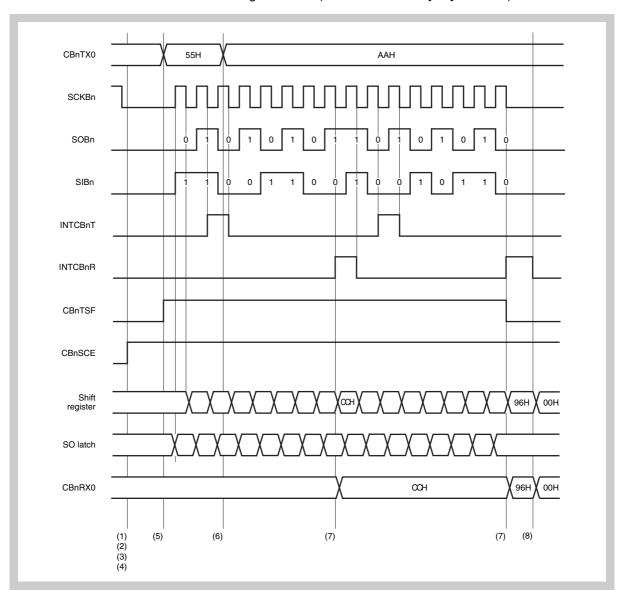

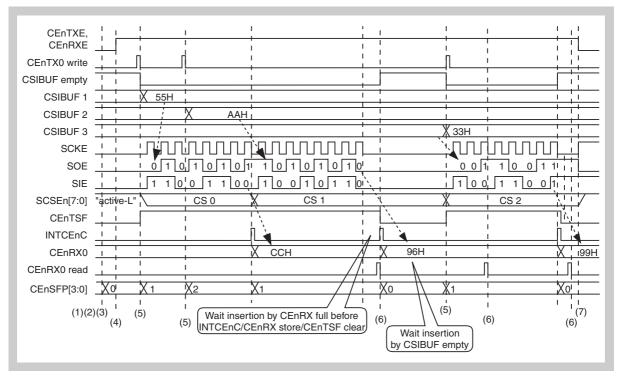

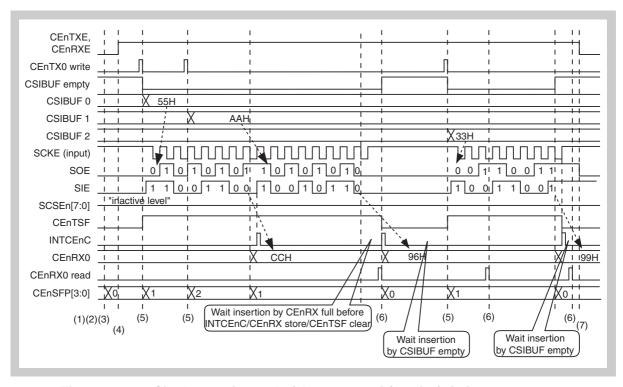

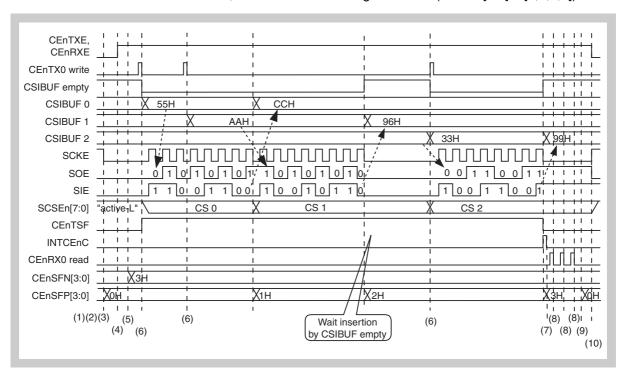

|      | 12.4.3  | Continuous mode (master mode, transmission/reception mode)      | 354  |

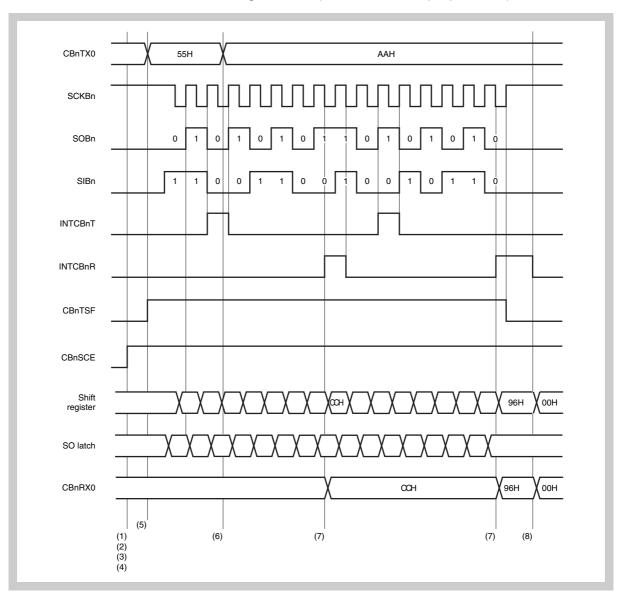

|      | 12.4.4  | Continuous mode (master mode, reception mode)                   | 356  |

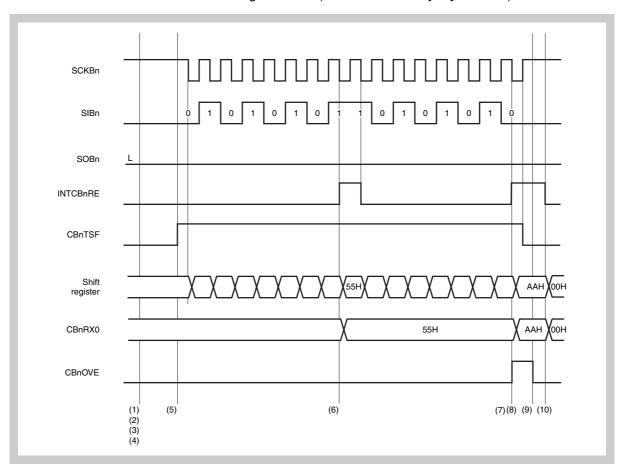

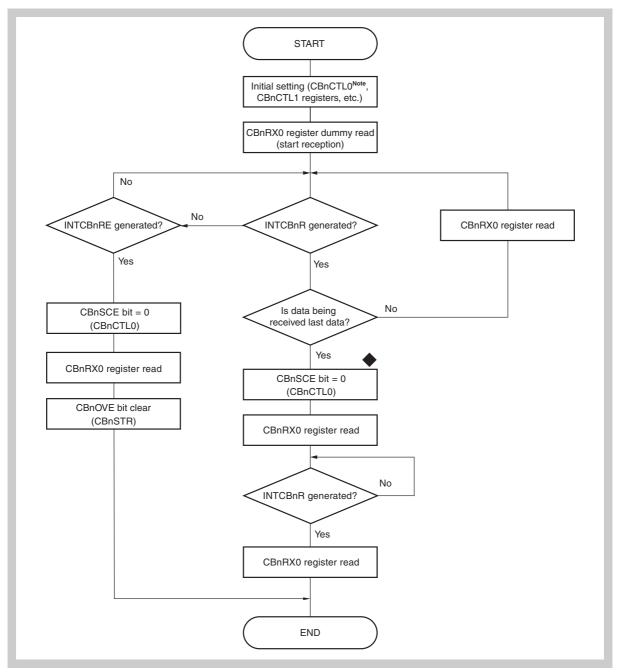

|      | 12.4.5  | Continuous reception mode (error)                               |      |

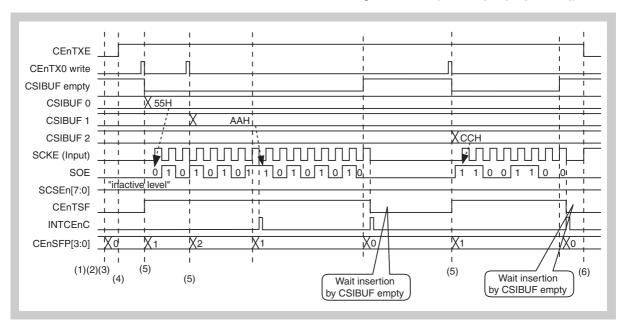

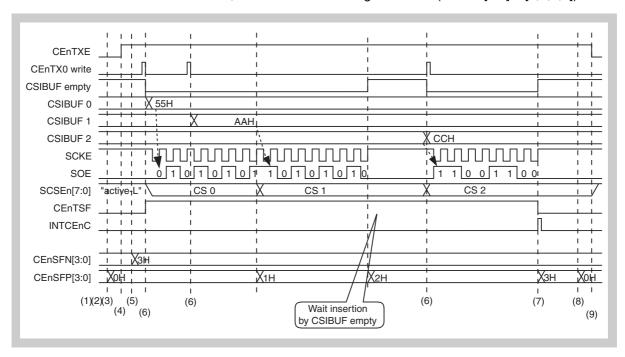

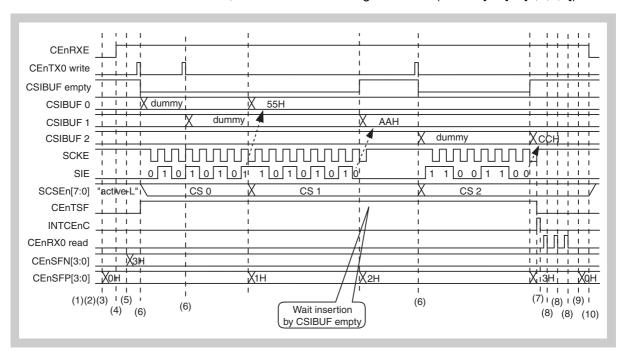

|      | 12.4.6  | Continuous mode (slave mode, transmission/reception mode)       |      |

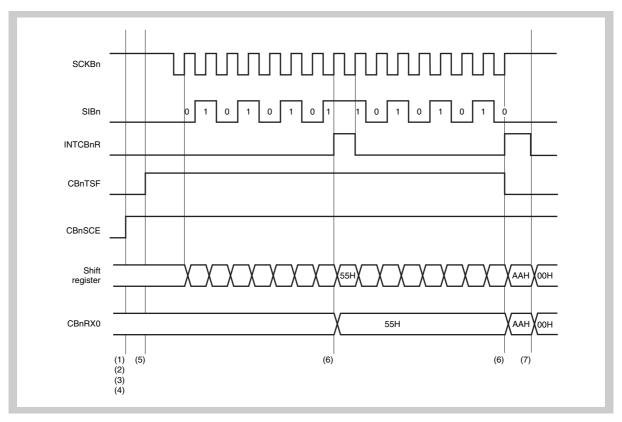

|      | 12.4.7  | Continuous mode (slave mode, reception mode)                    |      |

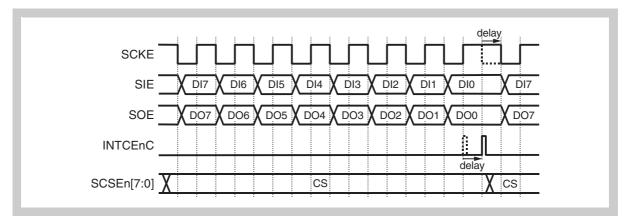

|      | 12.4.8  | Clock timing                                                    |      |

| 12.5 |         | Pins                                                            |      |

| 12.6 | -       | ion Flow                                                        |      |

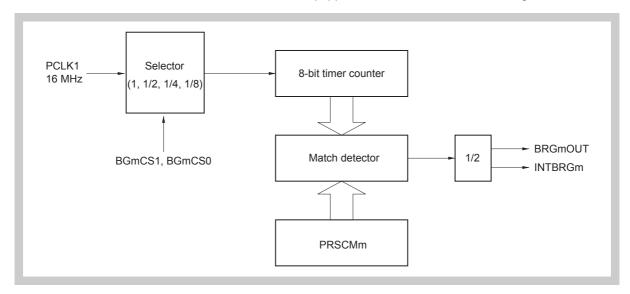

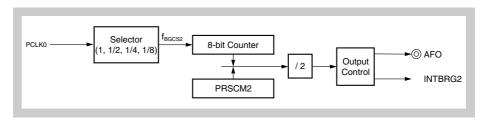

| 12.7 | •       | Rate Generator                                                  |      |

| 12.7 |         | Overview                                                        |      |

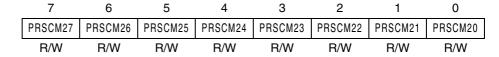

|      | 12.7.1  | Baud rate generator registers                                   |      |

|      | 12.7.2  | Baud rate generation                                            |      |

| 12.8 | _       | ns                                                              |      |

| 12.0 | 12.8.1  | CSIB operation stop                                             |      |

|      | 12.0.1  | Cold operation stop                                             | 374  |

| Chai | ator 12 | Enhanced Queued Clocked Sorial Interface (C                     | CIE) |

| Cita | olei 13 | Enhanced Queued Clocked Serial Interface (C                     | SIL) |

|      |         | 375                                                             |      |

| 13.1 | Feature | 9\$                                                             | 375  |

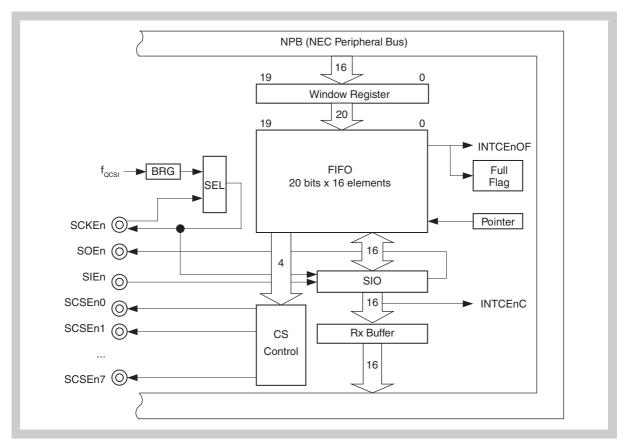

|      | 13.1.1  | Queued CSI block diagram                                        | 376  |

|      | 13.1.2  | Input/Output pins                                               | 377  |

| 13.2 | Queue   | d CSI Control Registers                                         | 378  |

| 13.3 |         | ation of Queued CSI Functions                                   |      |

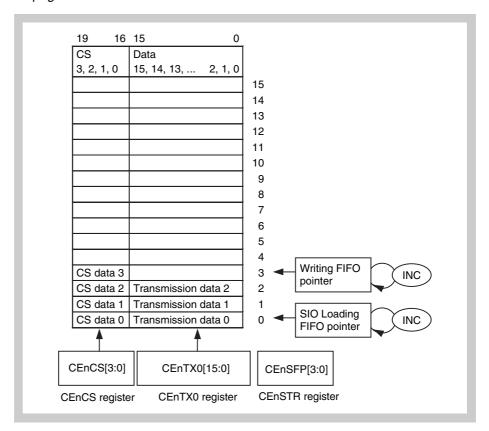

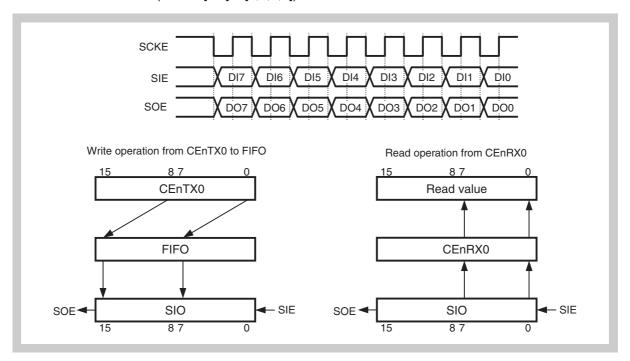

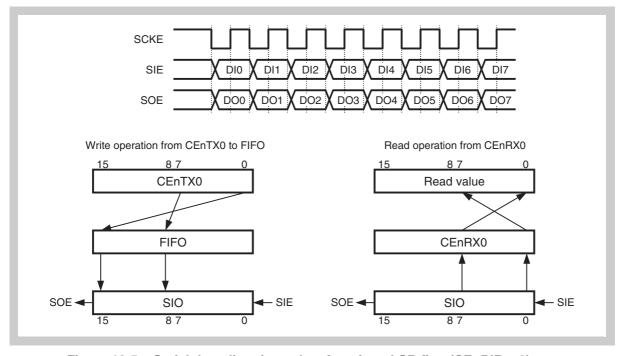

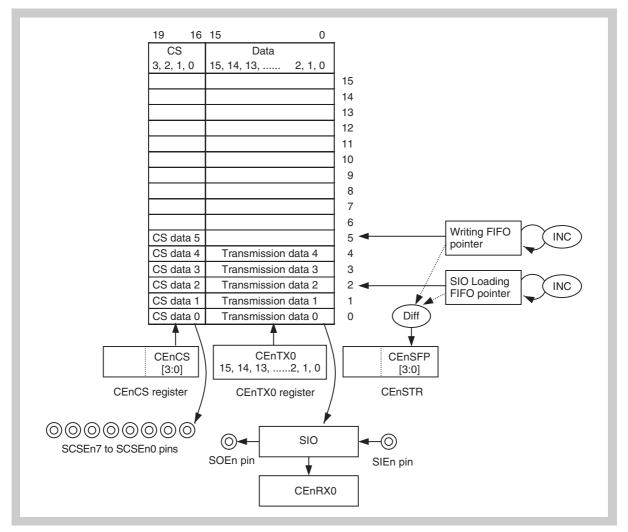

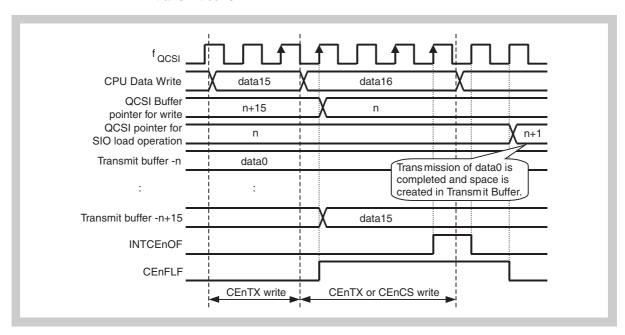

|      | 13.3.1  | Transmit buffer                                                 | 398  |

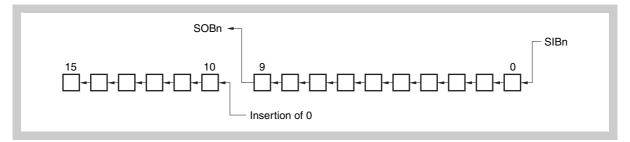

|      | 13.3.2  | Serial data direction select function                           |      |

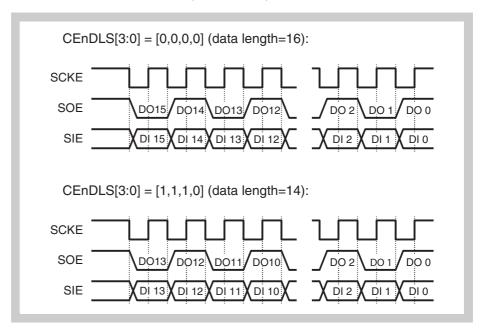

|      | 13.3.3  | Data length select function                                     |      |

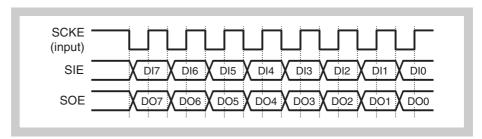

|      | 13.3.4  | Slave mode                                                      |      |

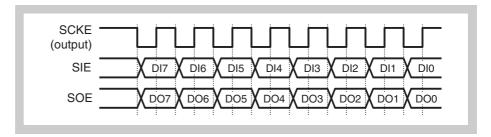

|      | 13.3.5  | Master mode                                                     |      |

|      |         |                                                                 |      |

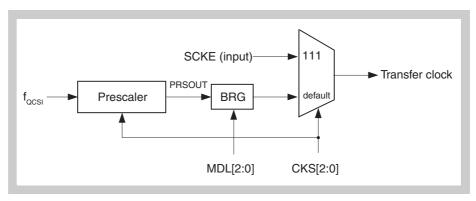

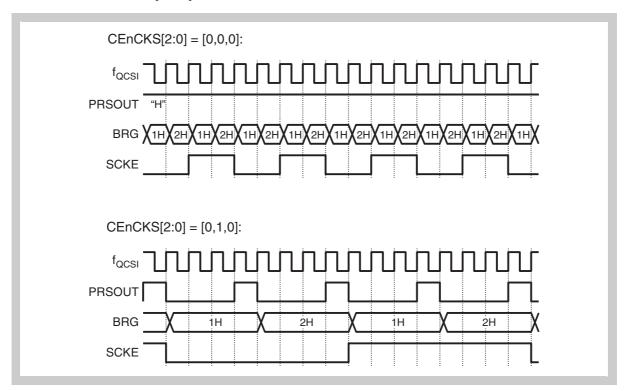

|       | 13.3.6                     | Transmission clock select function                        | 401        |

|-------|----------------------------|-----------------------------------------------------------|------------|

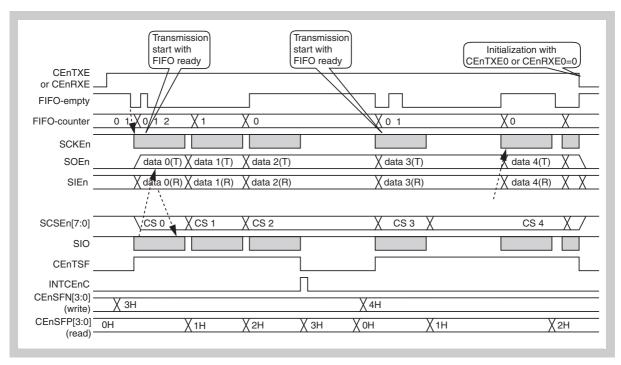

|       | 13.3.7                     | Description of the single transfer mode                   | 402        |

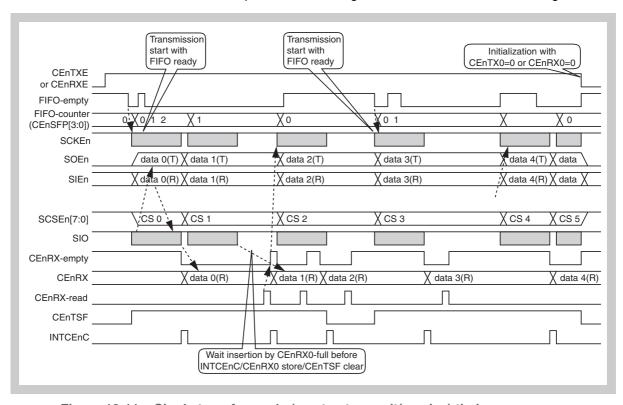

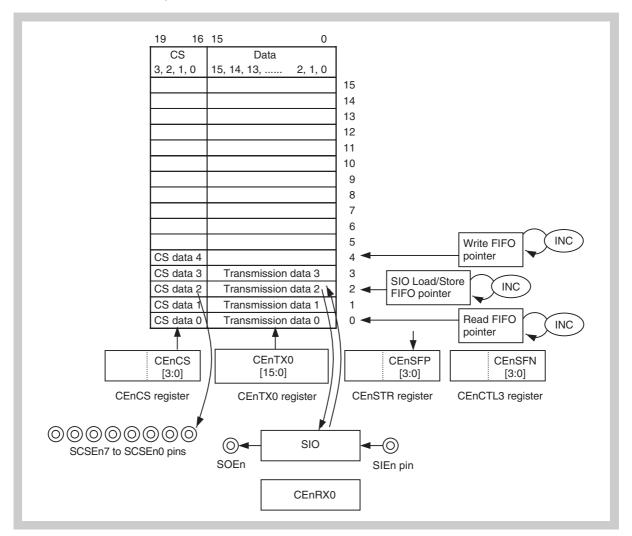

|       | 13.3.8                     | Description of the block transfer mode                    | 404        |

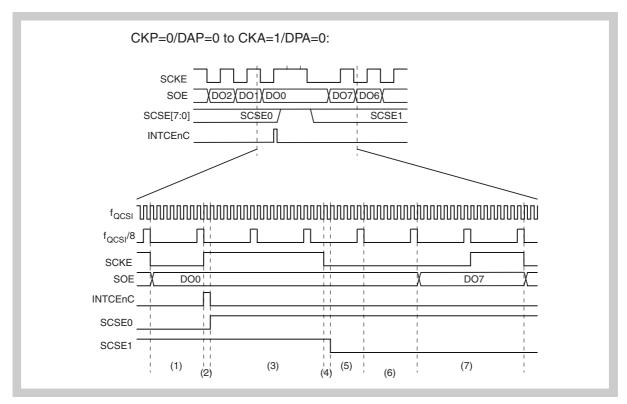

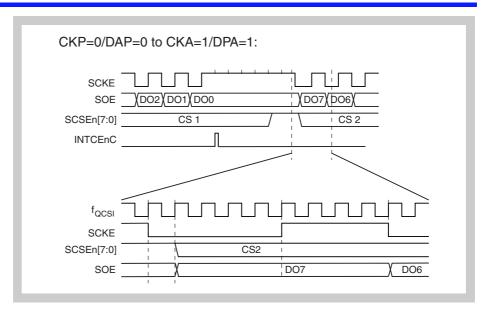

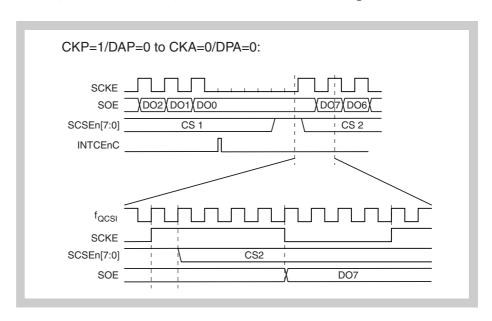

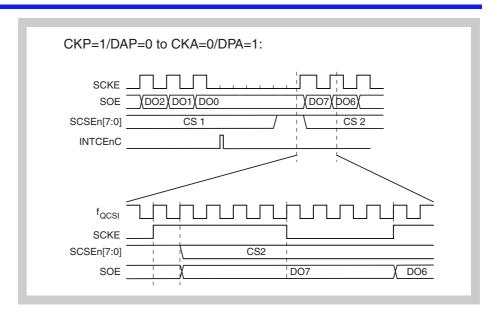

|       | 13.3.9                     | Description of the operation modes                        |            |

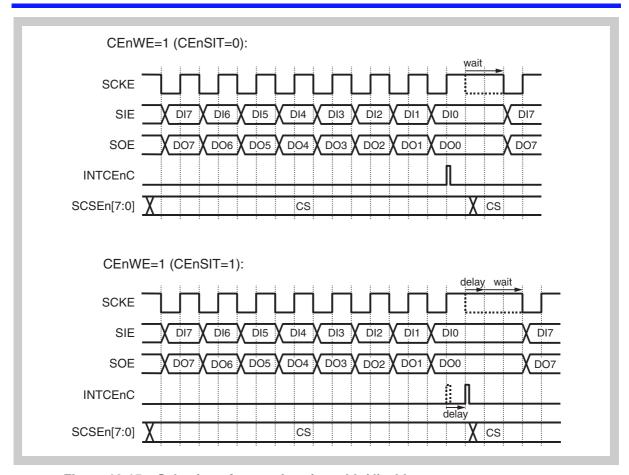

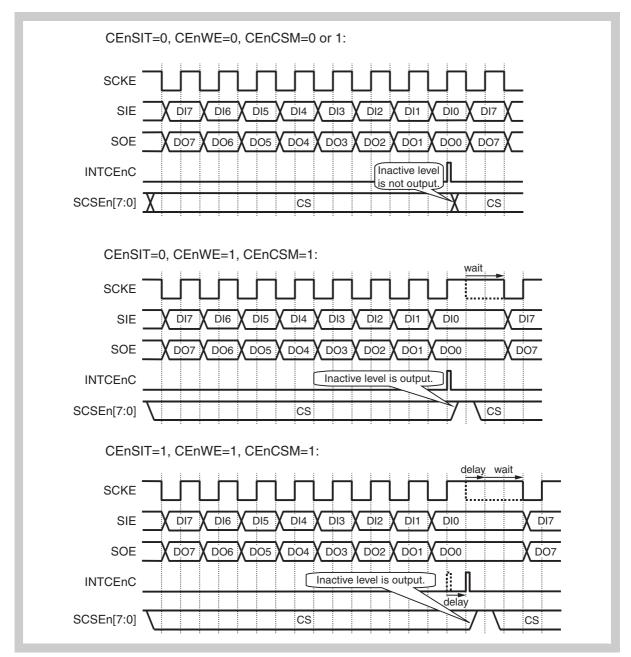

|       | 13.3.10                    | Additional timing and delay selections                    |            |

|       |                            | Default pin levels                                        |            |

|       |                            | Transmit buffer overflow interrupt signal (INTCEnOF)      |            |

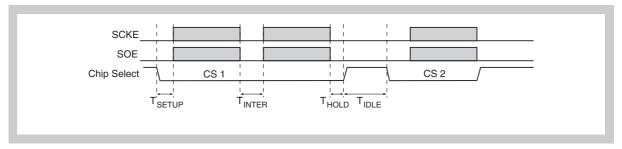

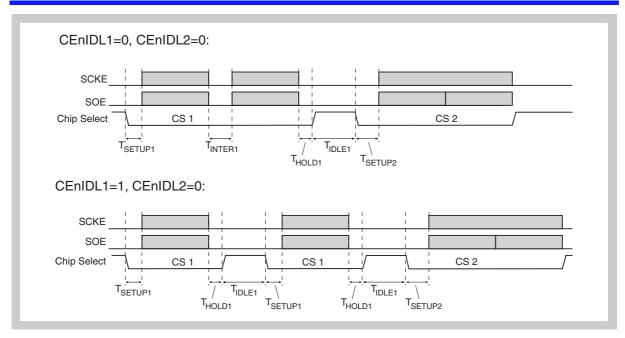

|       |                            | Enhanced chip select timing                               |            |

| 13.4  |                            | ng Procedure                                              |            |

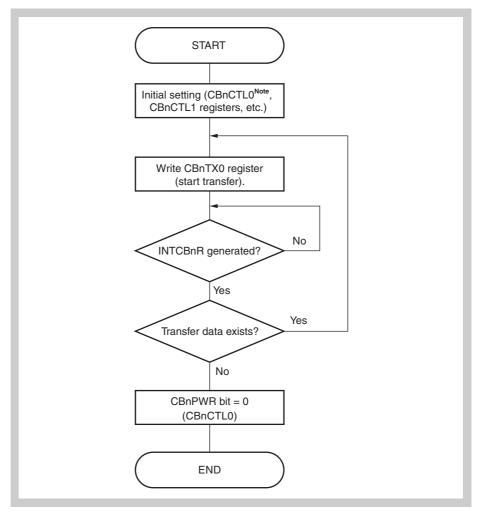

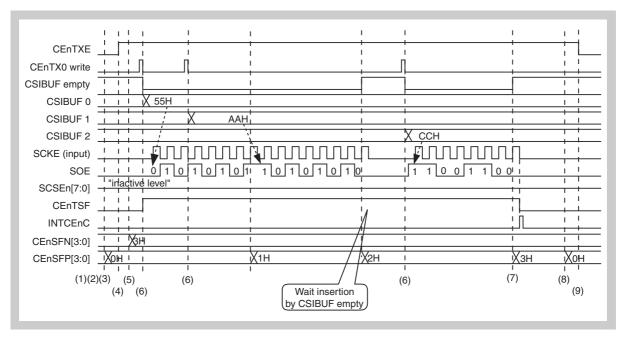

|       | 13.4.1                     | Single transfer mode (master mode, transmit only mode)    |            |

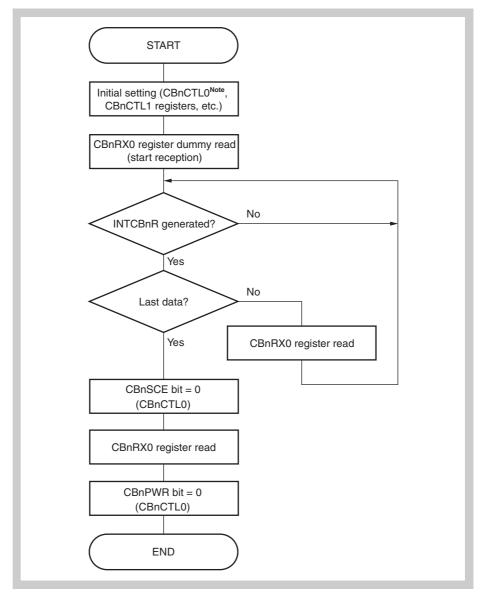

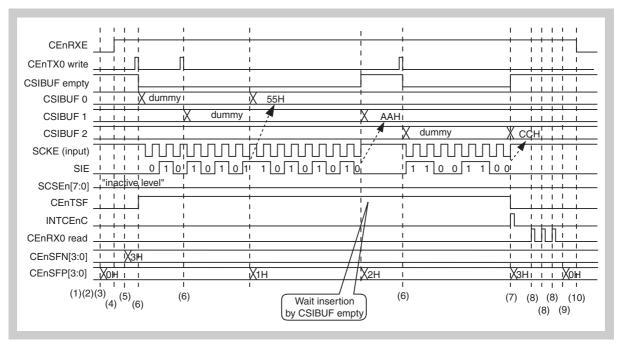

|       | 13.4.2                     | Single transfer mode (master mode, receive only mode)     |            |

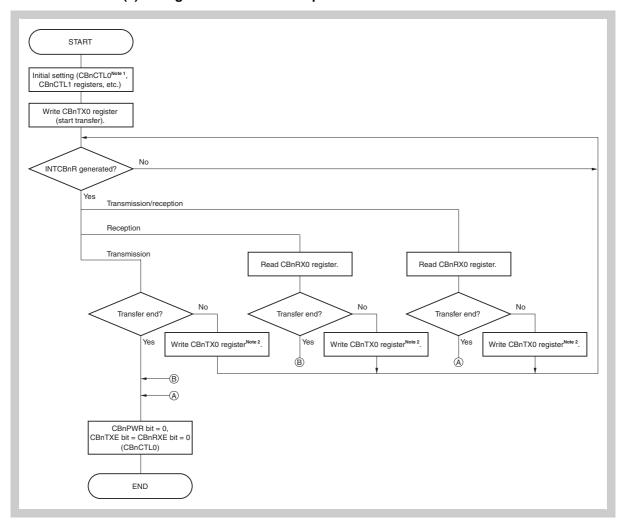

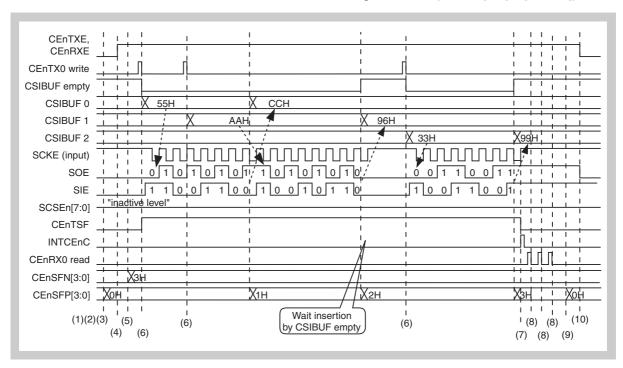

|       | 13.4.3                     | Single transfer mode (master mode, transmit/receive mode) |            |

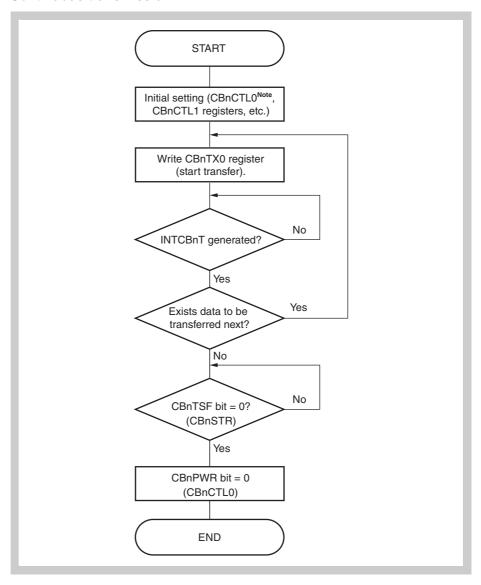

|       | 13.4.4                     | Single transfer mode (slave mode, transmit only mode)     |            |

|       | 13.4.5                     | Single transfer mode (slave mode, receive only mode)      |            |

|       | 13.4.6                     | Single transfer mode (slave mode, transmit/receive mode)  |            |

|       | 13.4.7                     | Block transfer mode (master mode, transmit only mode)     |            |

|       | 13.4.8                     | Block transfer mode (master mode, receive only mode)      |            |

|       | 13.4.9                     | Block transfer mode (master mode, transmit/receive mode)  |            |

|       |                            | Block transfer mode (slave mode, transmit only mode)      |            |

|       |                            | Block transfer mode (slave mode, receive only mode)       |            |

|       |                            | Block transfer mode (slave mode, transmit/receive mode)   |            |

| 13.5  |                            | ns                                                        |            |

|       | 13.5.1                     | Inconsistent read data in master mode                     |            |

|       | 13.5.2                     | Transmit/receive enable after CEnTX0 write                |            |

|       |                            |                                                           |            |

| Char  | oter 14                    | CAN Controller (CAN)                                      | 431        |

| 14.1  |                            | s                                                         |            |

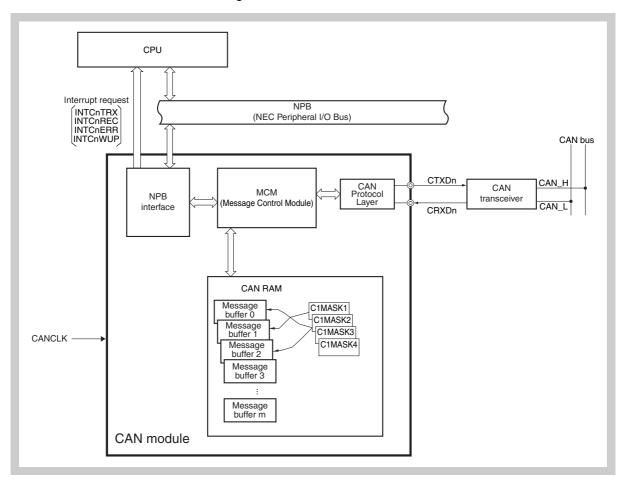

| 1-7-1 | 14.1.1                     | Overview of functions                                     |            |

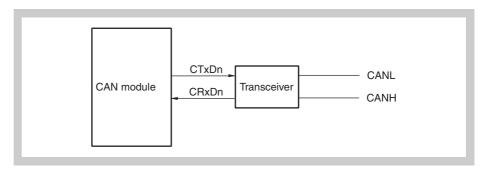

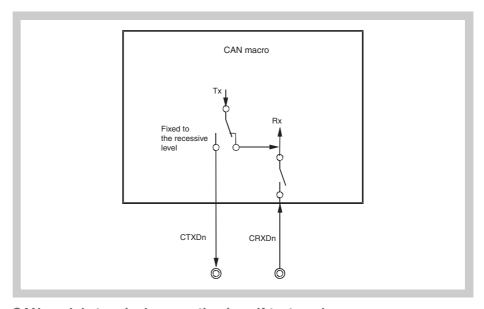

|       | 14.1.2                     | Configuration                                             |            |

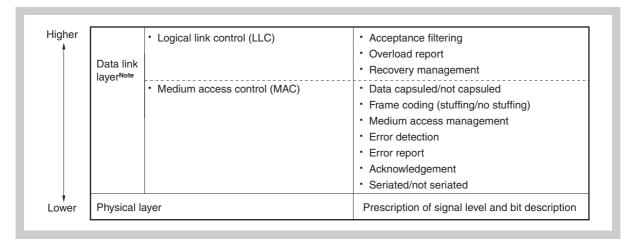

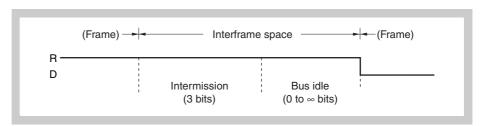

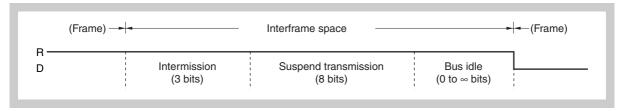

| 14.2  |                            | otocol                                                    |            |

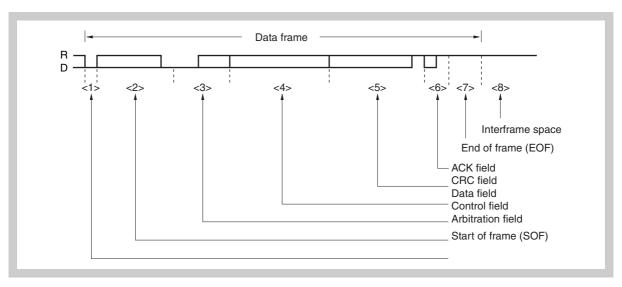

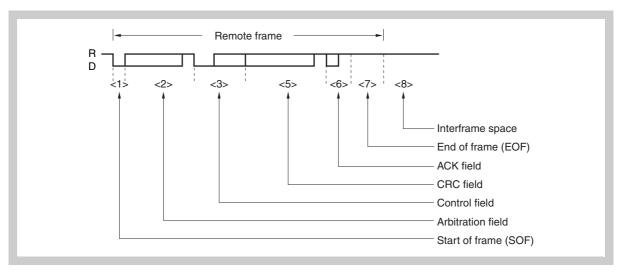

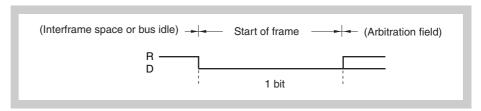

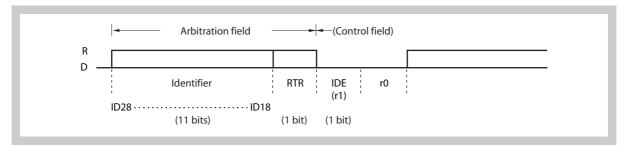

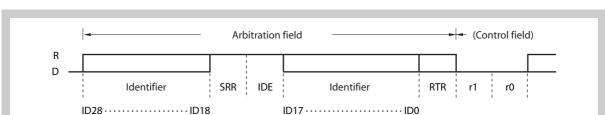

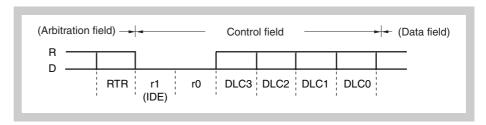

|       | 14.2.1                     | Frame format                                              |            |

|       | 14.2.2                     | Frame types                                               |            |

|       | 14.2.3                     | Data frame and remote frame                               |            |

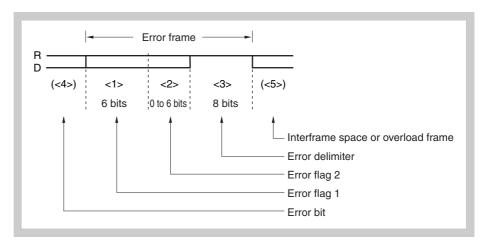

|       | 14.2.4                     | Error frame                                               |            |

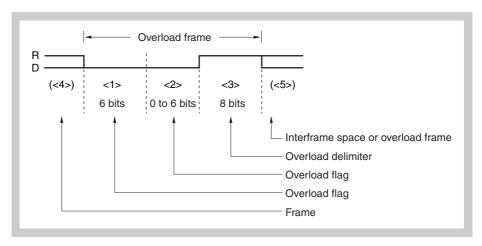

|       | 14.2.5                     | Overload frame                                            |            |

| 14.3  |                            | ons                                                       |            |

| 14.0  | 14.3.1                     | Determining bus priority                                  |            |

|       | 14.3.2                     | Bit stuffing                                              |            |

|       | 14.3.3                     | Multi masters                                             |            |

|       | 14.3.4                     | Multi cast                                                | _          |

|       | 14.3.5                     | CAN sleep mode/CAN stop mode function                     |            |

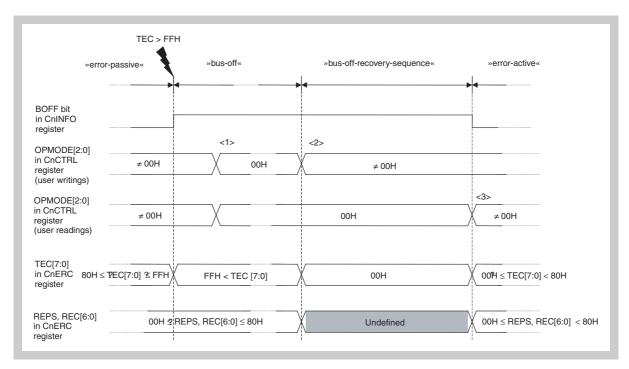

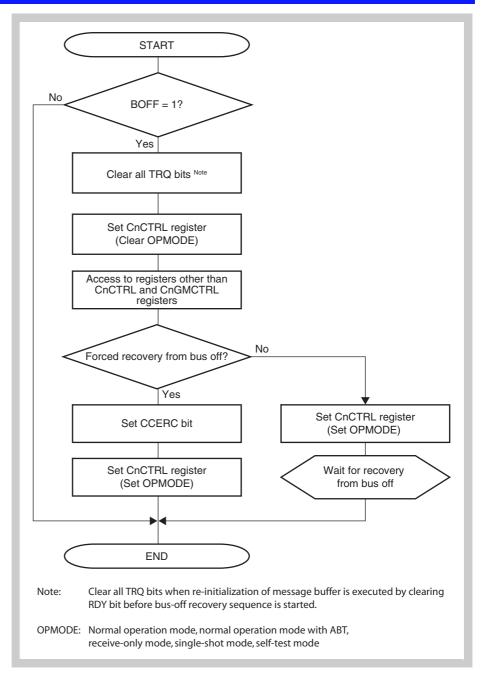

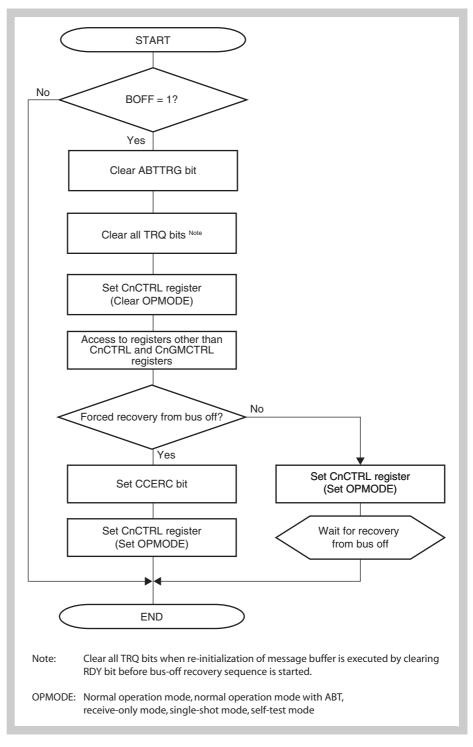

|       | 14.3.6                     | Error control function                                    |            |

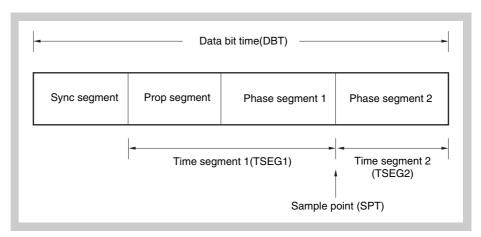

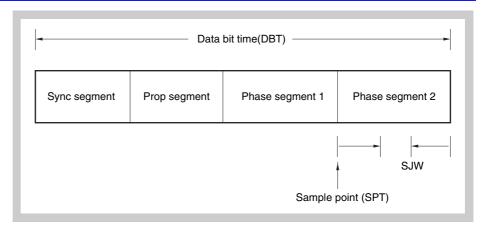

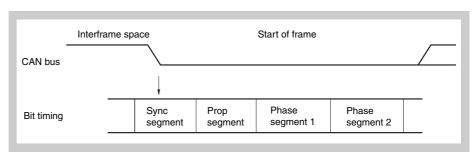

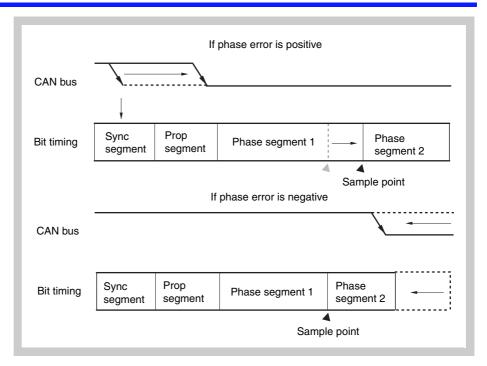

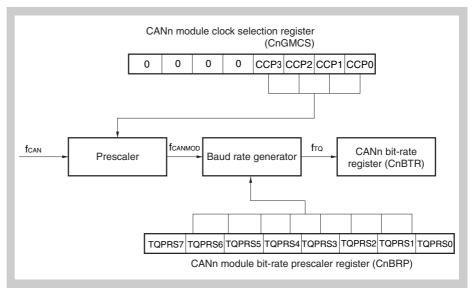

|       | 14.3.7                     | Baud rate control function                                |            |

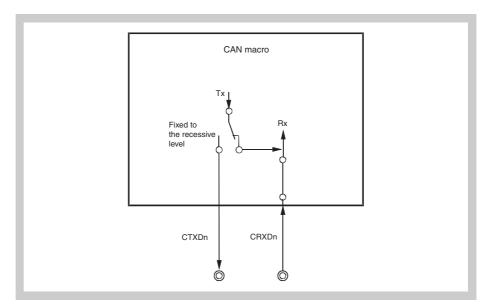

| 14.4  |                            | etion with Target System                                  |            |

| 14.5  |                            | Registers of CAN Controller                               |            |

| 17.5  | 14.5.1                     | CAN module register and message buffer addresses          |            |

|       |                            | Ora module register and message buller addresses          | +50        |

|       |                            | CAN Controller configuration                              | 457        |

|       | 14.5.2                     | CAN Controller configuration                              |            |

|       | 14.5.2<br>14.5.3           | CAN registers overview                                    | 458        |

| 14.6  | 14.5.2<br>14.5.3<br>14.5.4 | _                                                         | 458<br>460 |

| 14.7   |           | Registers                                             |       |

|--------|-----------|-------------------------------------------------------|-------|

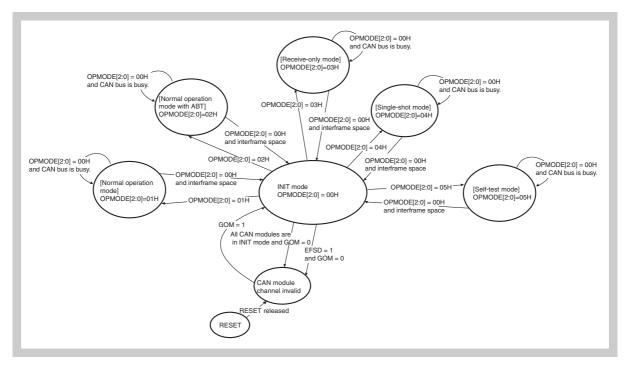

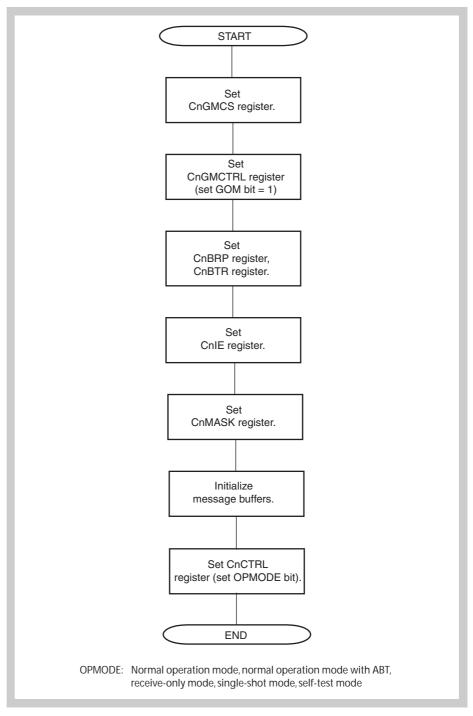

| 14.8   | CAN Co    | ontroller Initialization                              |       |

|        | 14.8.1    | Initialization of CAN module                          | . 501 |

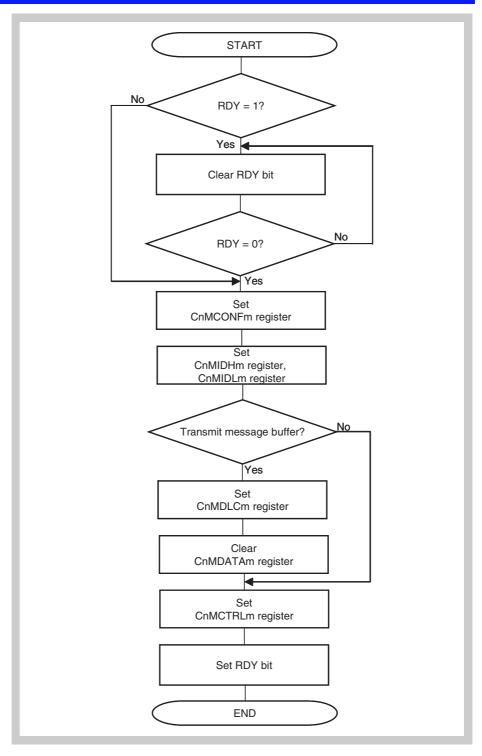

|        | 14.8.2    | Initialization of message buffer                      |       |

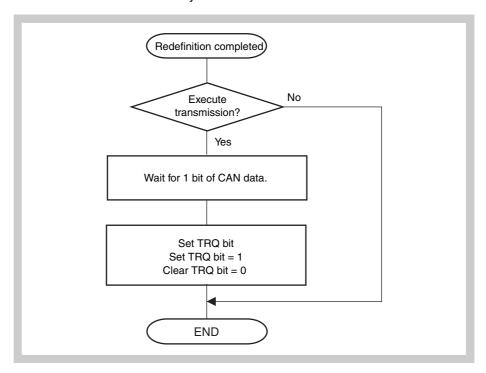

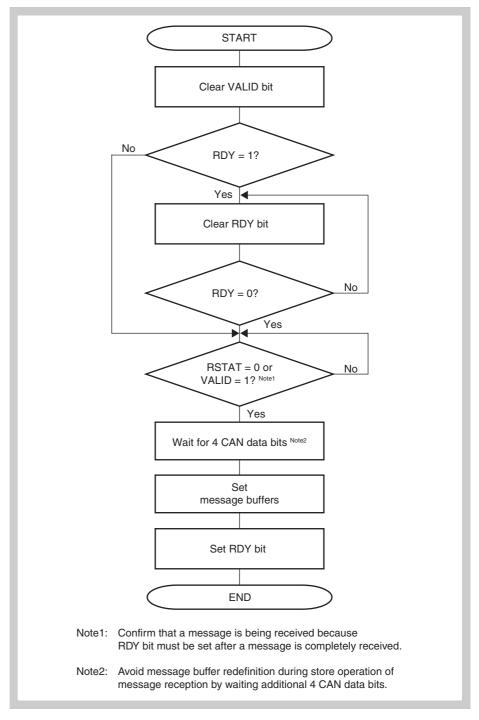

|        | 14.8.3    | Redefinition of message buffer                        | . 501 |

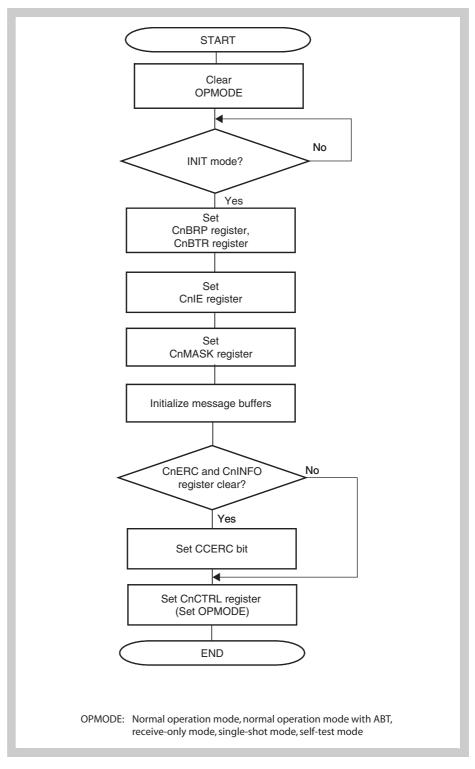

|        | 14.8.4    | Transition from initialization mode to operation mode | . 503 |

|        | 14.8.5    | Resetting error counter CnERC of CAN module           | . 504 |

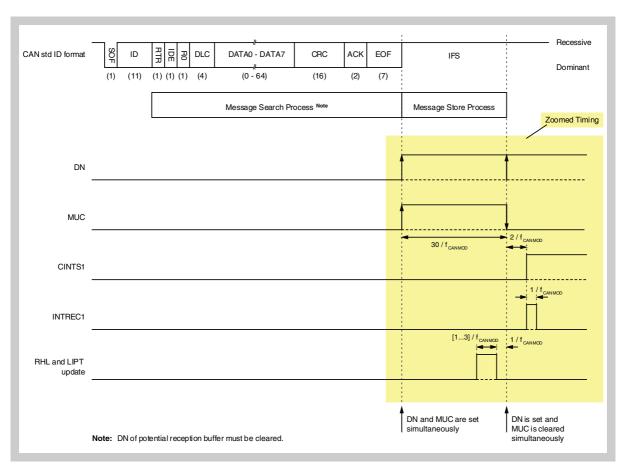

| 14.9   | Messag    | e Reception                                           | . 505 |

|        | 14.9.1    | Message reception                                     | . 505 |

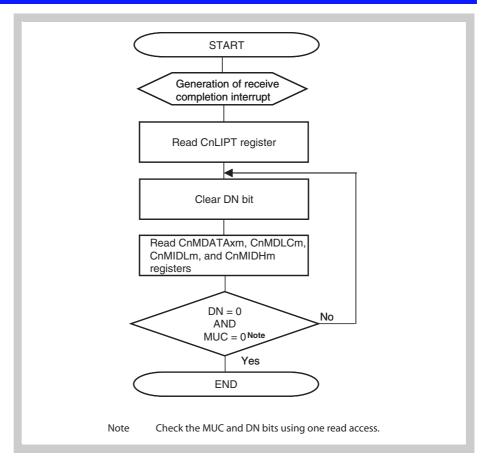

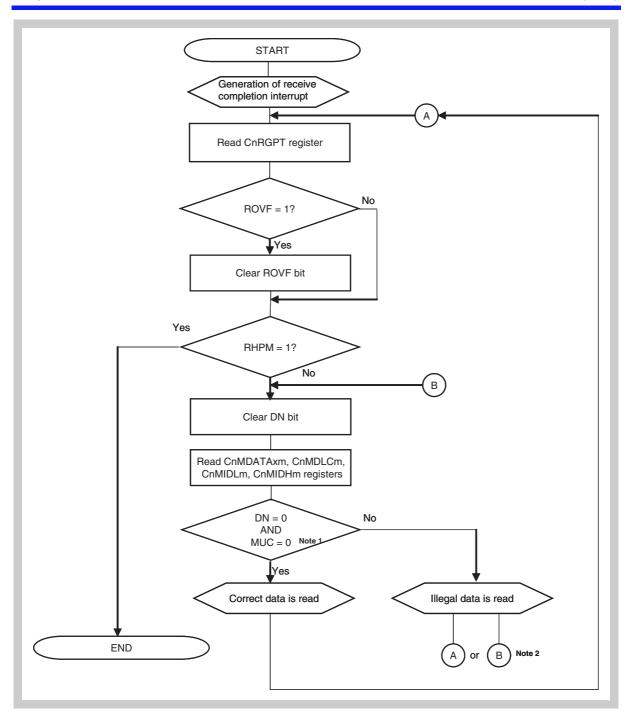

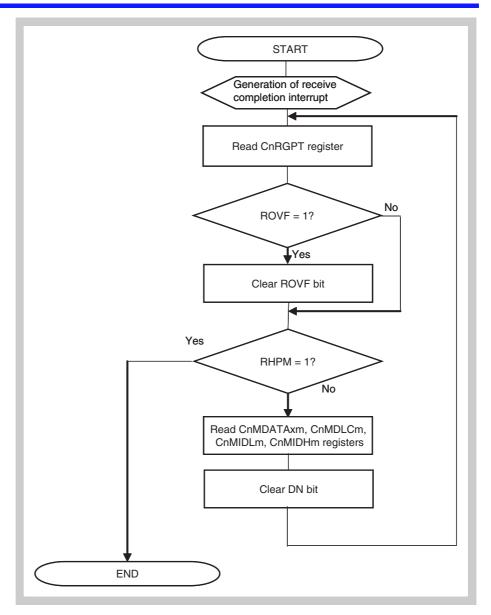

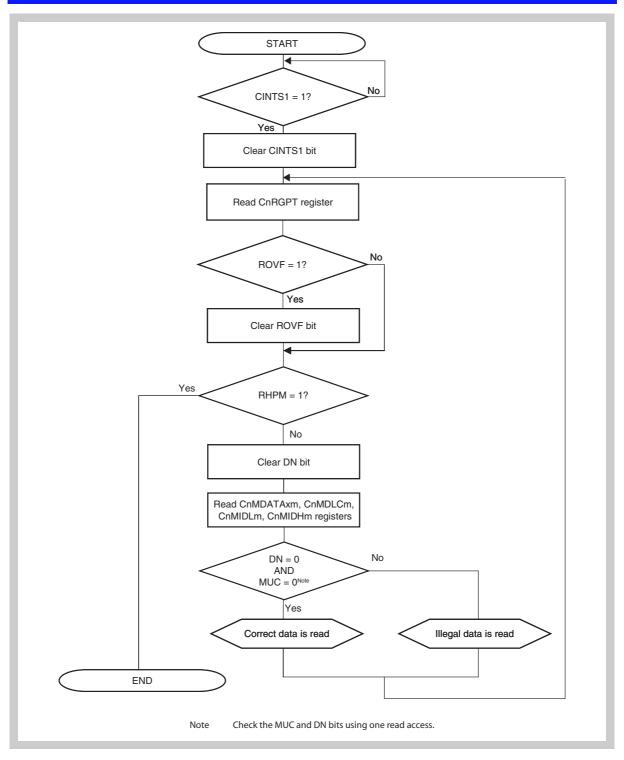

|        | 14.9.2    | Receive data read                                     | . 506 |

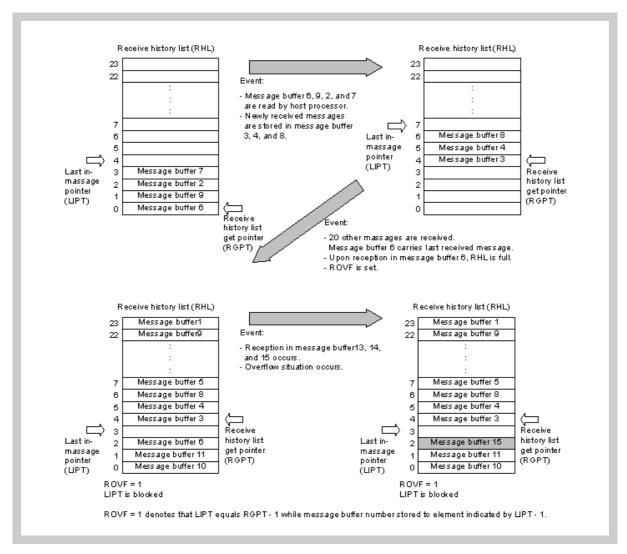

|        | 14.9.3    | Receive history list function                         | . 507 |

|        | 14.9.4    | Mask function                                         | . 509 |

|        | 14.9.5    | Multi buffer receive block function                   | . 511 |

|        | 14.9.6    | Remote frame reception                                | . 512 |

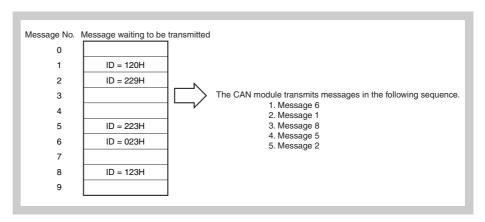

| 14.10  | Messag    | e Transmission                                        | . 513 |

|        | 14.10.1   | Message transmission                                  | . 513 |

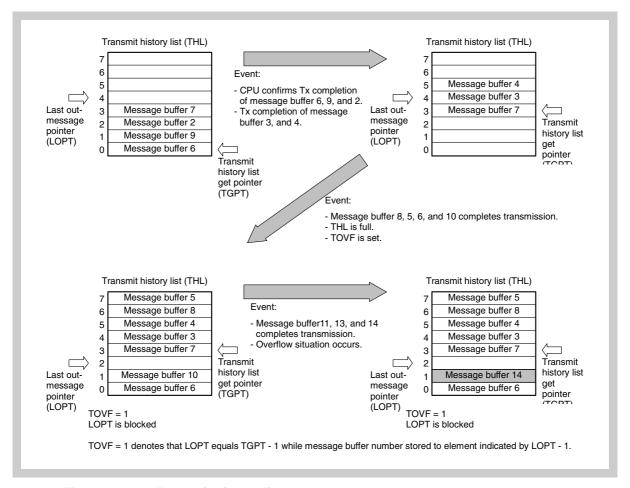

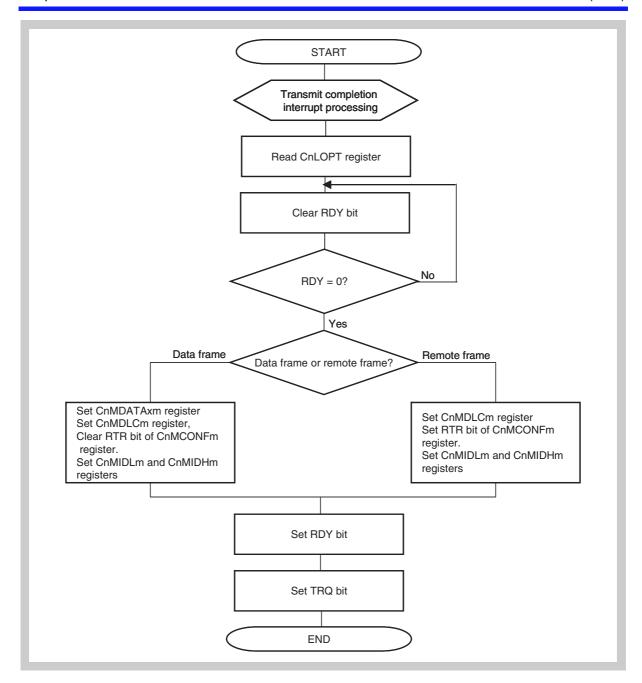

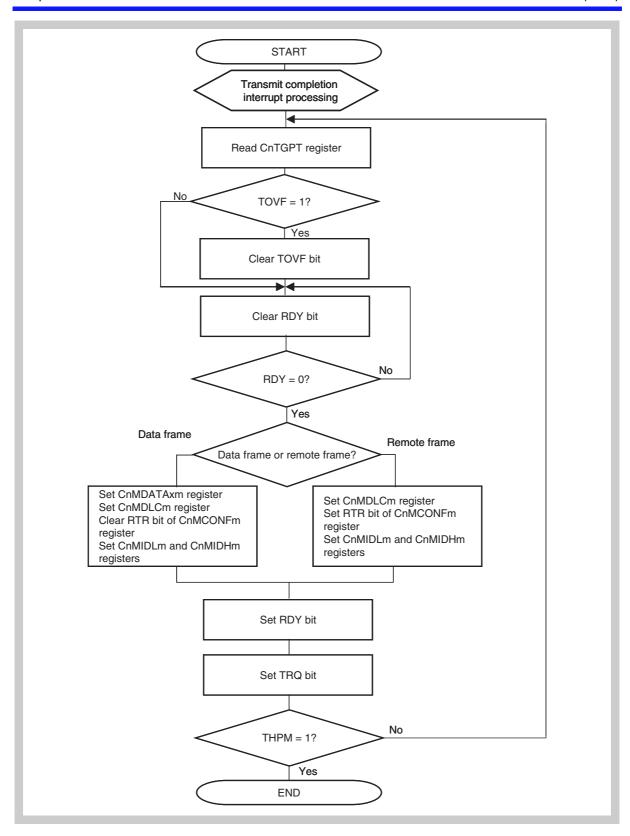

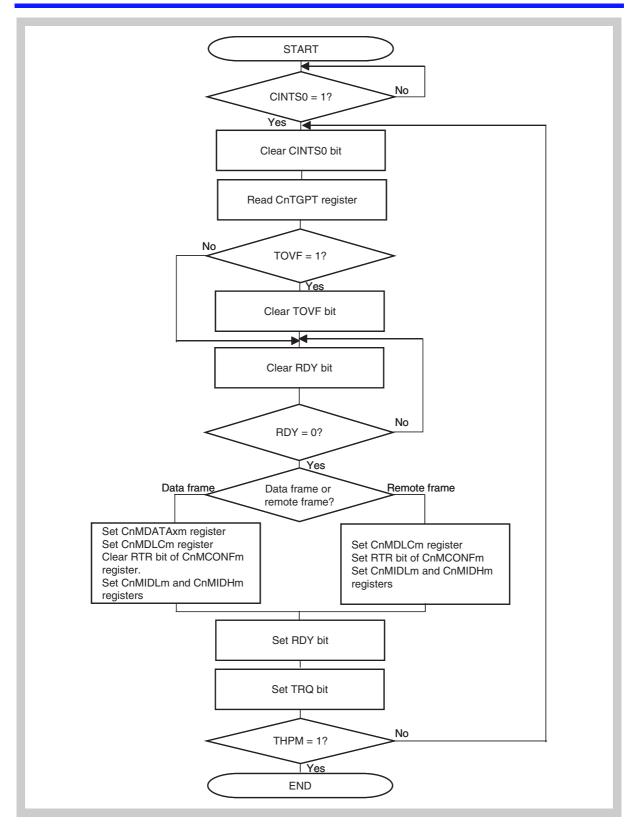

|        |           | Transmit history list function                        |       |

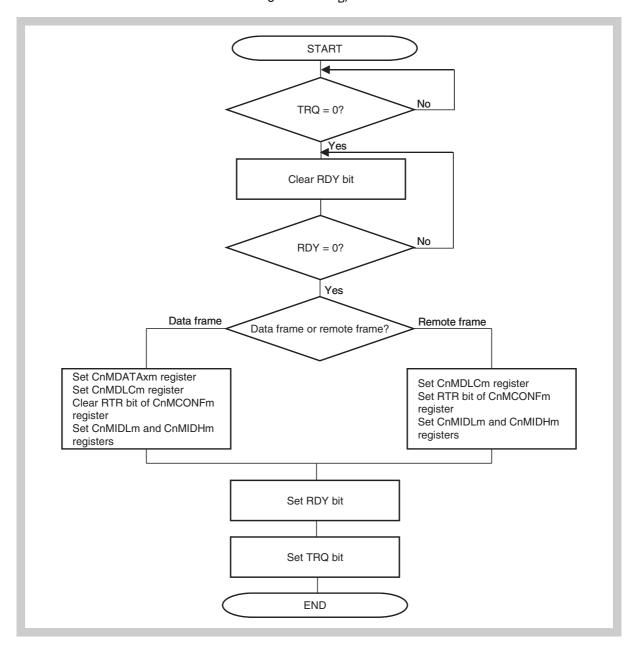

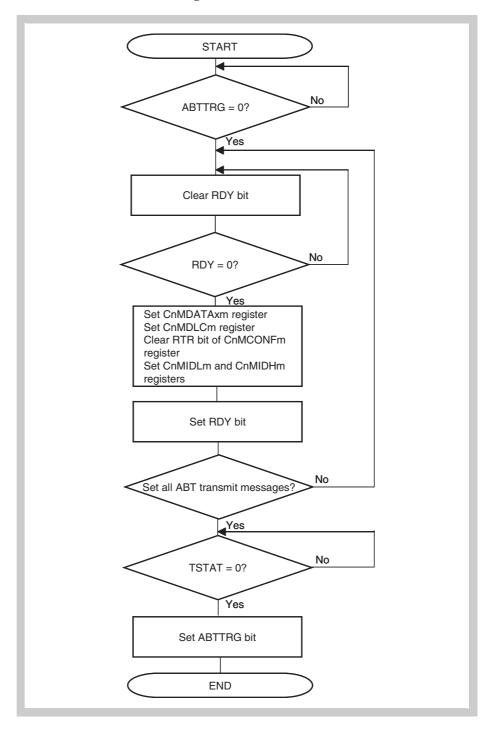

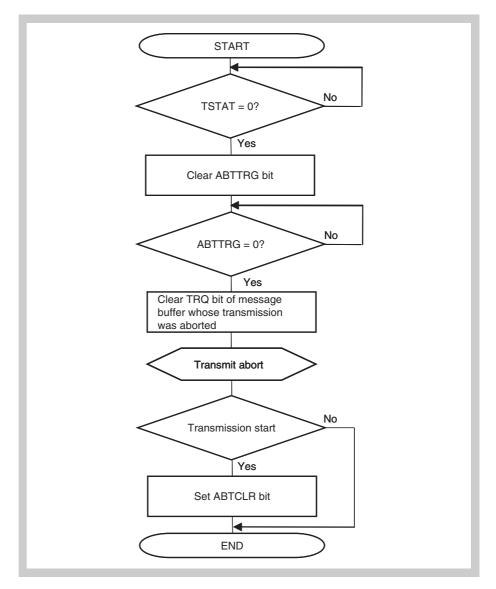

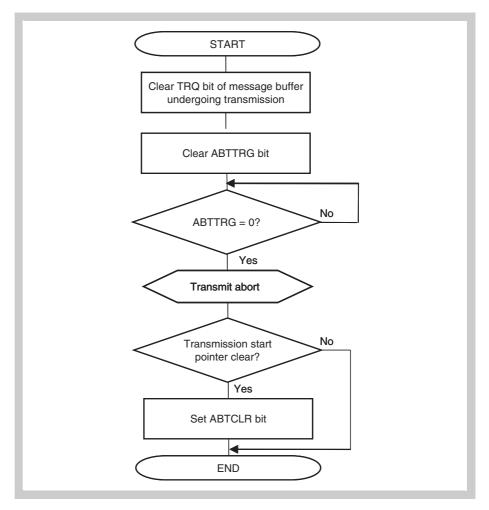

|        |           | Automatic block transmission (ABT)                    |       |

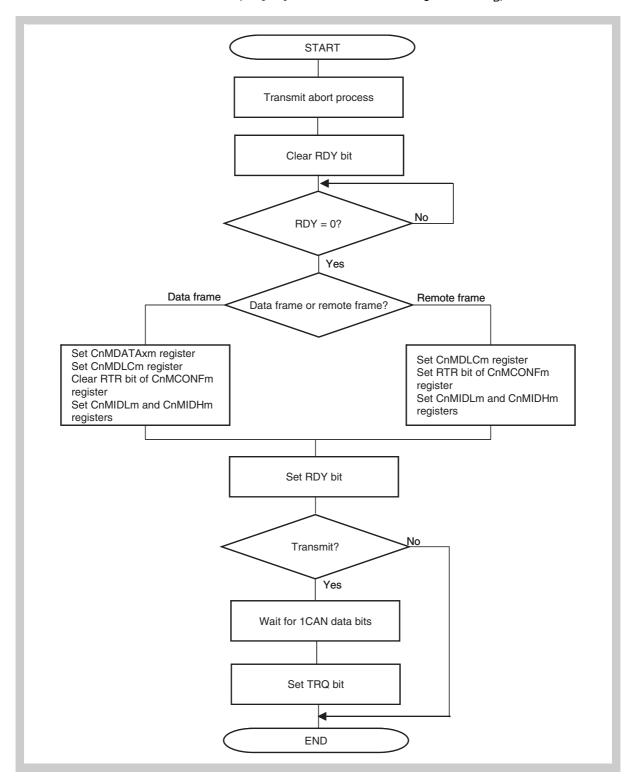

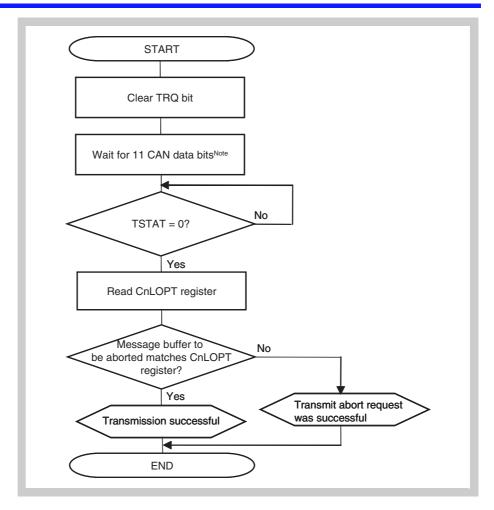

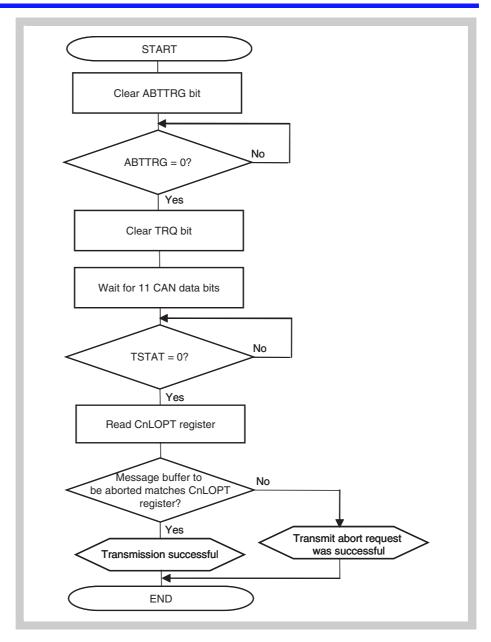

|        |           | Transmission abort process                            |       |

|        |           | Remote frame transmission                             |       |

| 14.11  |           | Saving Modes                                          |       |

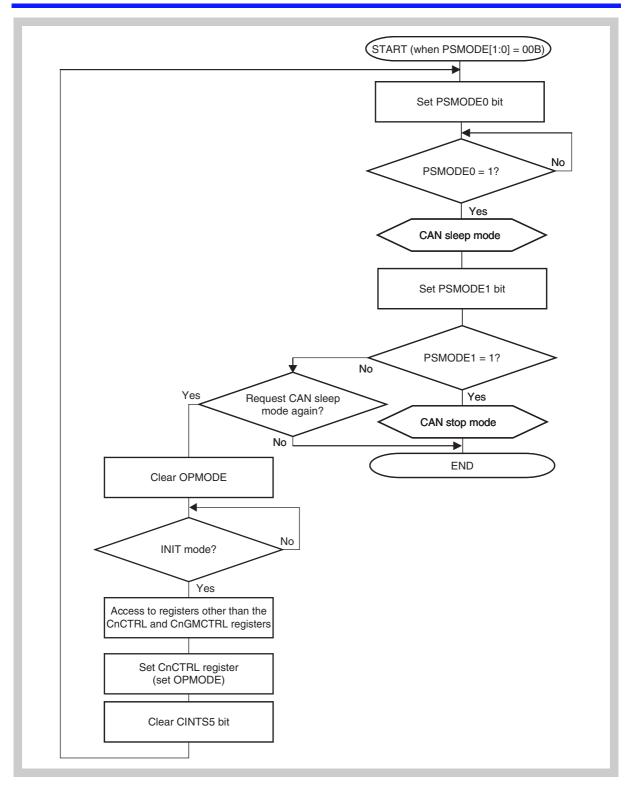

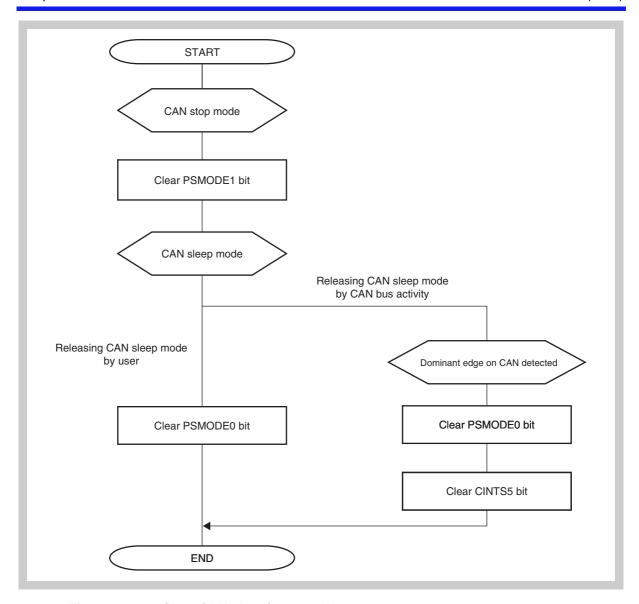

|        |           | CAN sleep mode                                        |       |

|        |           | CAN stop mode                                         |       |

|        |           | Example of using power saving modes                   |       |

| 14.12  |           | ot Function                                           |       |

| 14.13  | -         | sis Functions and Special Operational Modes           |       |

| 1 1110 | •         | Receive-only mode                                     |       |

|        |           | Single-shot mode                                      |       |

|        |           | Self-test mode                                        |       |

|        |           | Receive/transmit operation in each operation mode     |       |

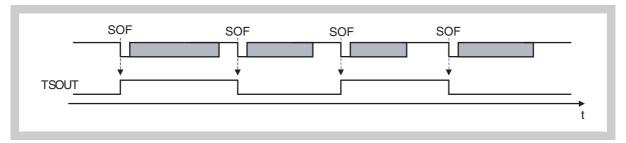

| 14.14  |           | amp Function                                          |       |

| 14.14  |           | Time stamp function                                   |       |

| 14.15  |           | ate Settings                                          |       |

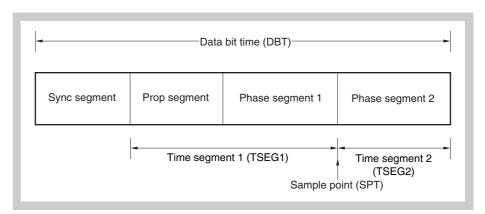

| 14.15  |           | Baud rate setting conditions                          |       |

|        |           | Representative examples of baud rate settings         |       |

| 1416   |           | •                                                     |       |

| 14.16  | Operation | on of CAN Controller                                  | . 540 |

| Char   | tor 15    | A/D Convertor (ADC)                                   |       |

| -      |           | A/D Converter (ADC)                                   |       |

| 15.1   |           | S                                                     |       |

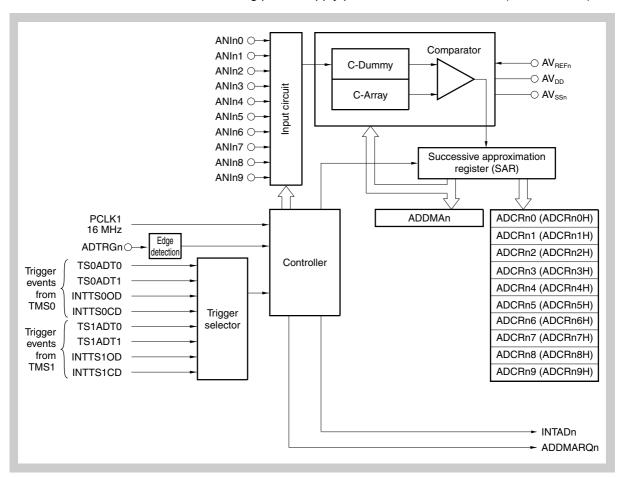

| 15.2   | Configu   | ıration                                               | . 570 |

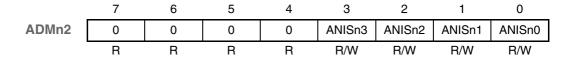

| 15.3   | Control   | Registers                                             | . 573 |

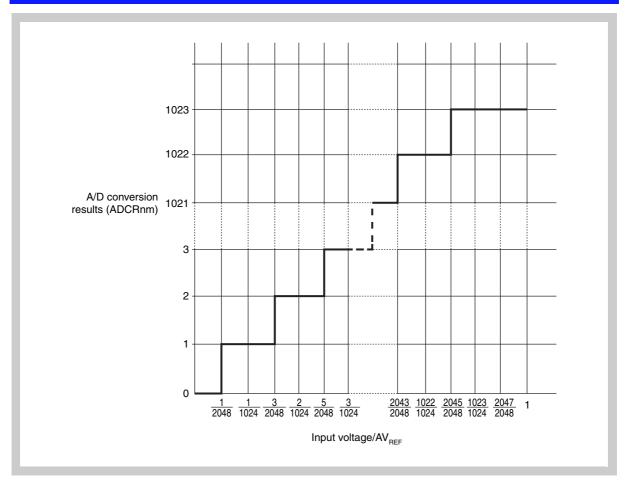

| 15.4   | Operation | on                                                    | . 582 |

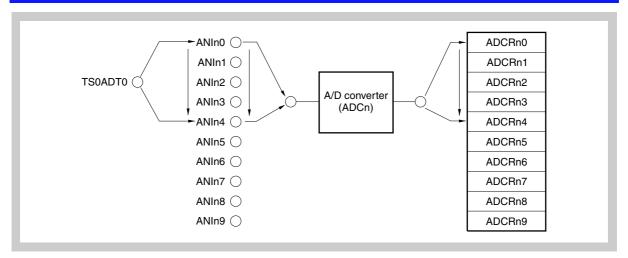

|        | 15.4.1    | Basic operation                                       | . 582 |

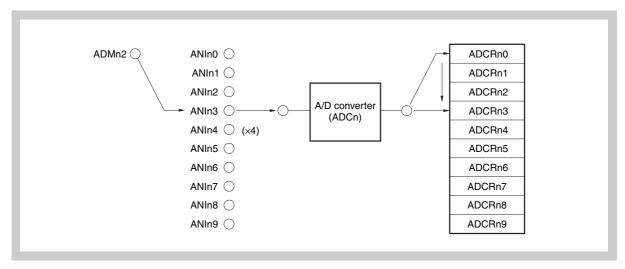

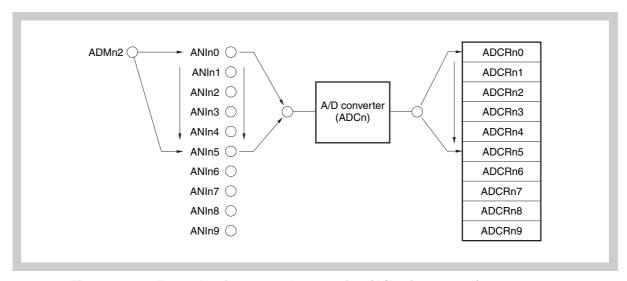

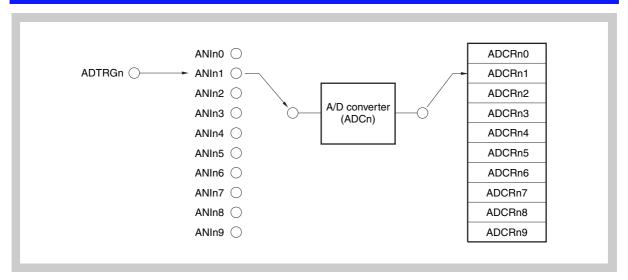

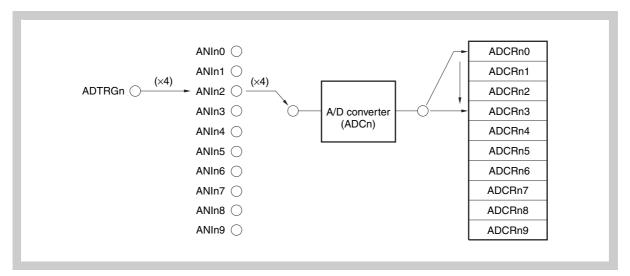

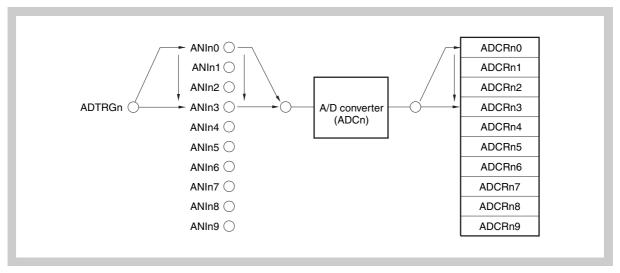

|        | 15.4.2    | Operation mode and trigger mode                       | . 583 |

| 15.5   | Operation | on in A/D Trigger Mode                                | . 588 |

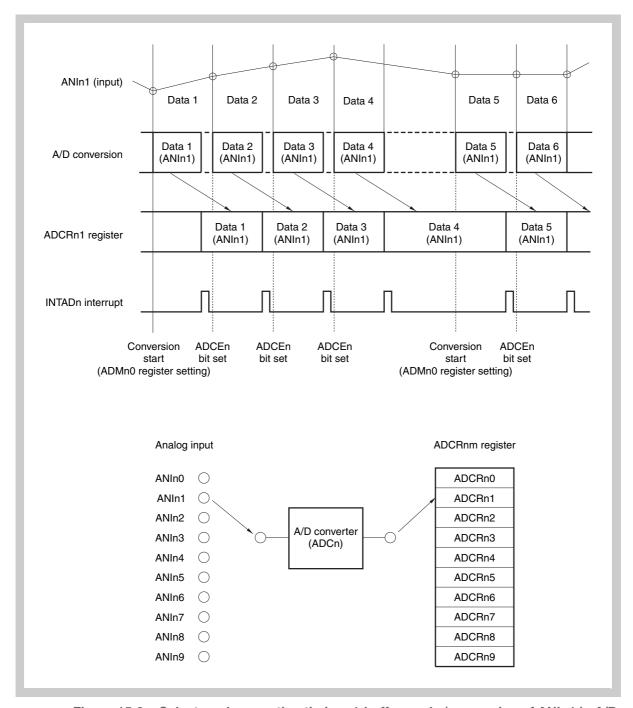

|        | 15.5.1    | Select mode operation                                 | . 588 |

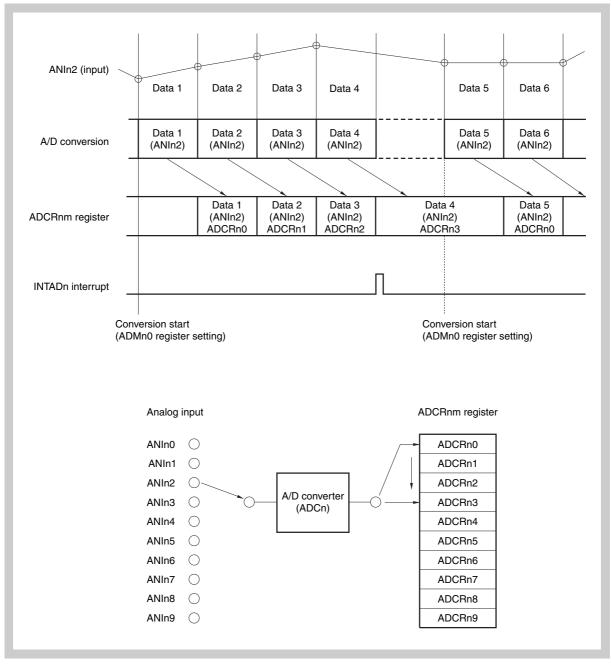

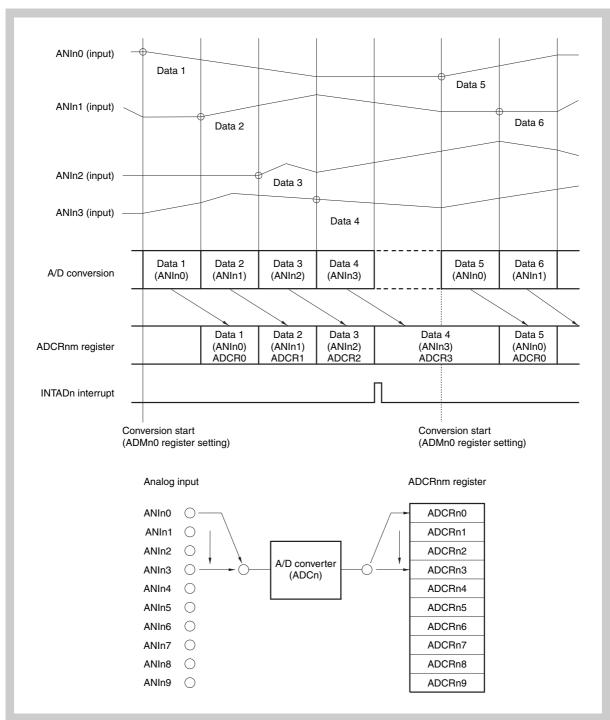

|        | 15.5.2    | Scan mode operation                                   | . 590 |

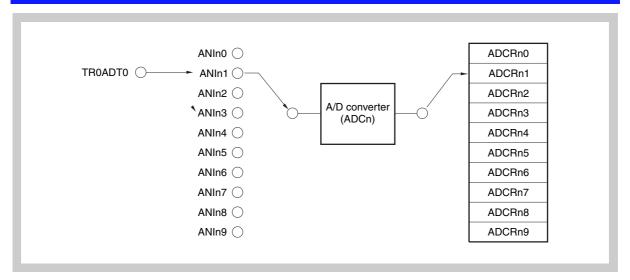

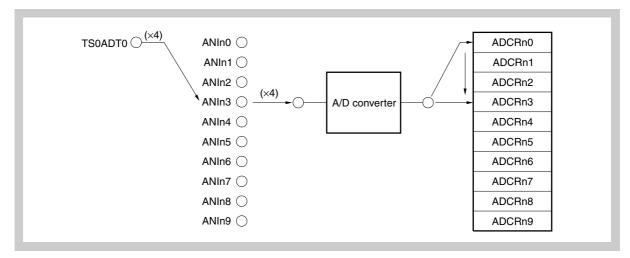

| 15.6   | Operation | on in Timer Trigger Mode                              | . 592 |

|        | 15.6.1    | Select mode operation                                 | . 592 |

|        | 15.6.2    | Scan mode operation                                   | . 595 |

|        |           |                                                       |       |

| 15.7         | Operati                                                                                                                                                          | on in External Trigger Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 597                                                                                     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|              | 15.7.1                                                                                                                                                           | Select mode operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 597                                                                                     |

|              | 15.7.2                                                                                                                                                           | Scan mode operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 599                                                                                     |

| 15.8         | Precaut                                                                                                                                                          | tions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 601                                                                                     |

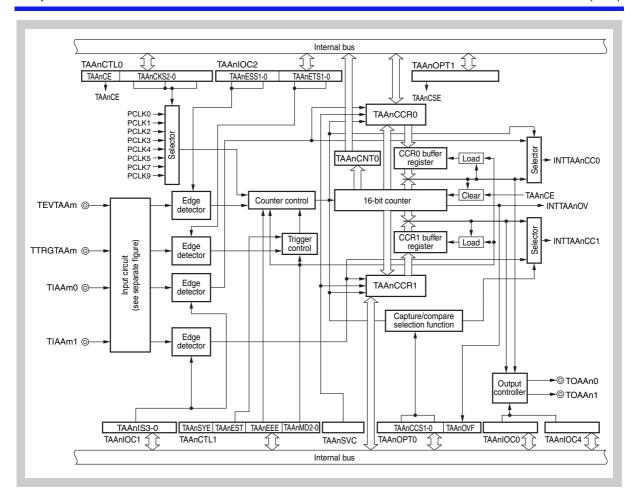

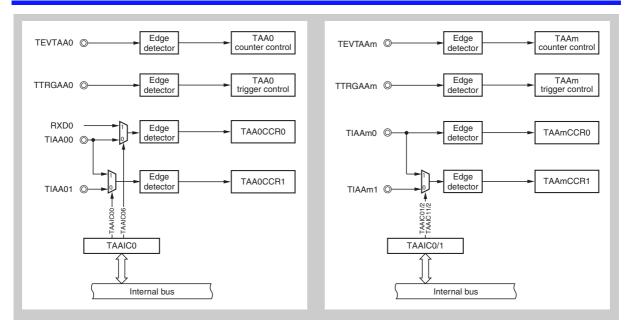

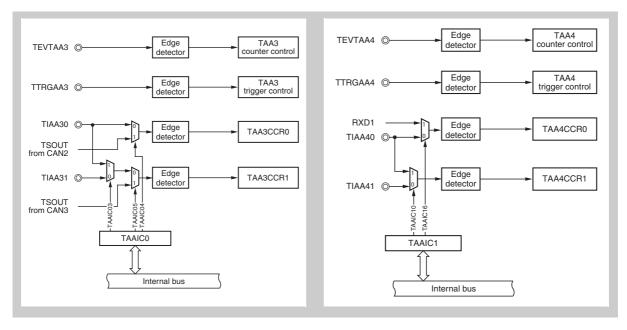

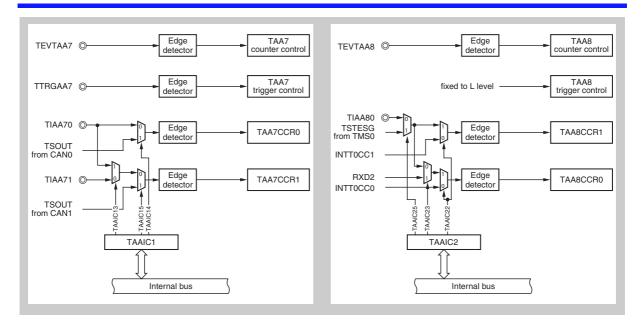

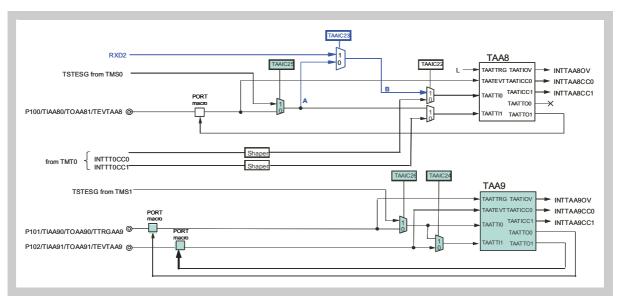

| Char         | oter 16                                                                                                                                                          | 16-Bit Timer/Event Counter AA (TAA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 604                                                                                     |

| 16.1         |                                                                                                                                                                  | s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

| 16.2         |                                                                                                                                                                  | on Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

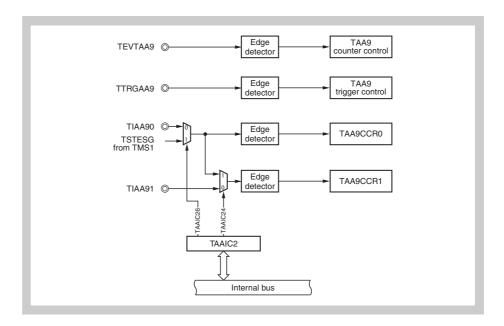

| 16.3         |                                                                                                                                                                  | ıration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

| 16.4         | Input Se                                                                                                                                                         | election Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 612                                                                                     |

| 16.5         | Control                                                                                                                                                          | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 615                                                                                     |

| 16.6         | Operati                                                                                                                                                          | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 627                                                                                     |

|              | 16.6.1                                                                                                                                                           | Anytime write and reload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 628                                                                                     |

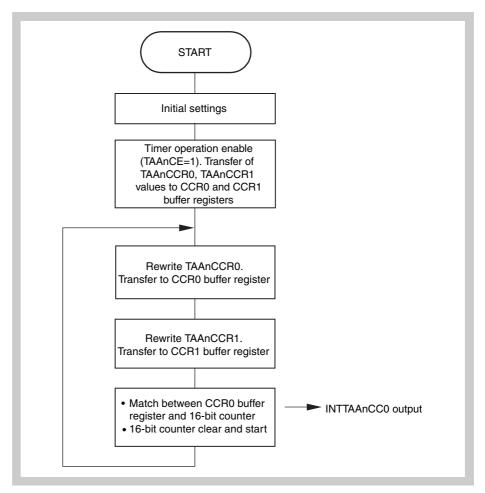

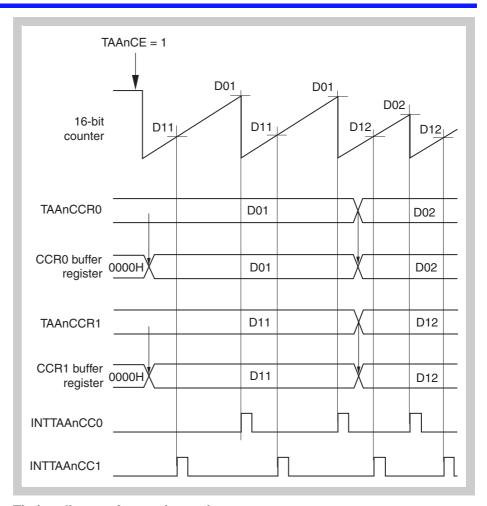

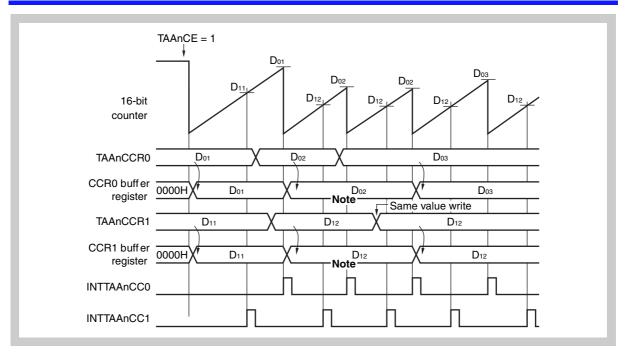

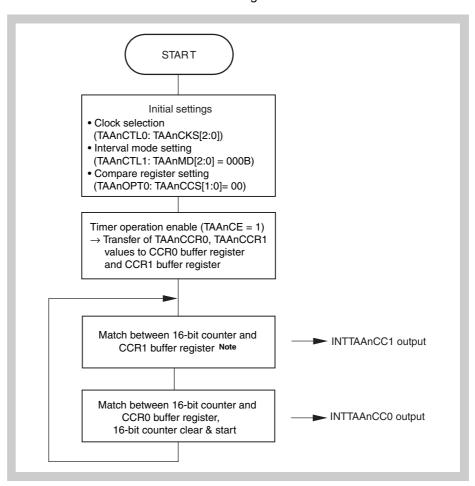

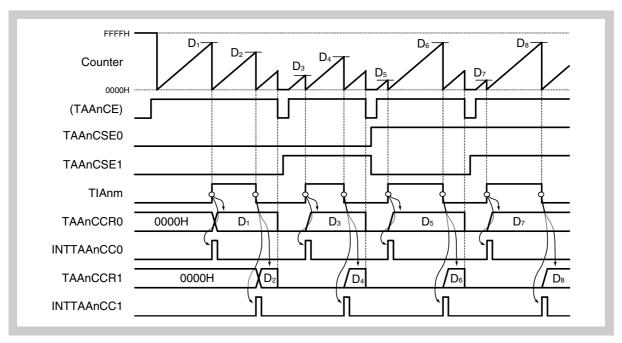

|              | 16.6.2                                                                                                                                                           | Interval timer mode (TAAnMD2 to TAAnMD0 = 000 <sub>B</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 632                                                                                     |

|              | 16.6.3                                                                                                                                                           | External event counter mode (TAAnMD2 to TAAnMD0 = 001 <sub>B</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 635                                                                                     |

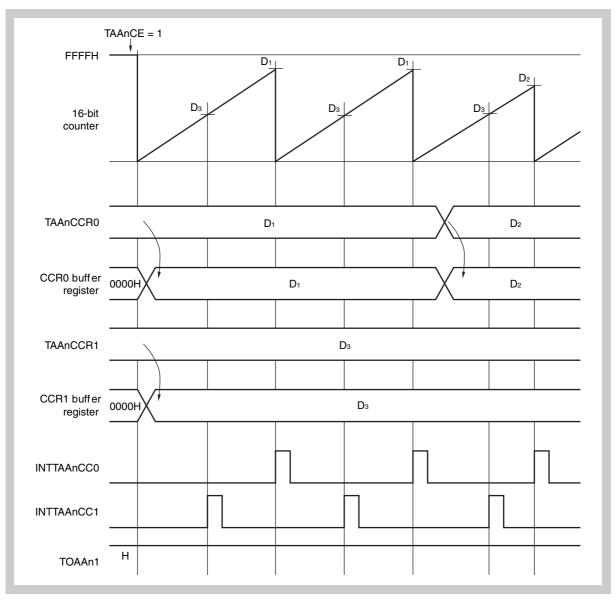

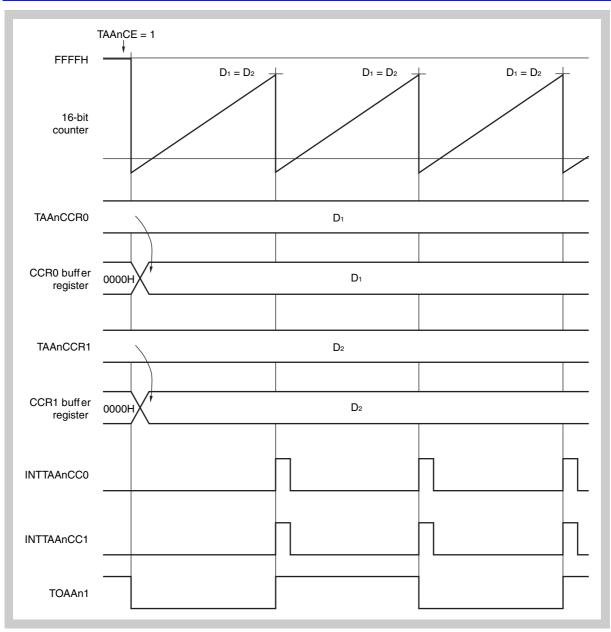

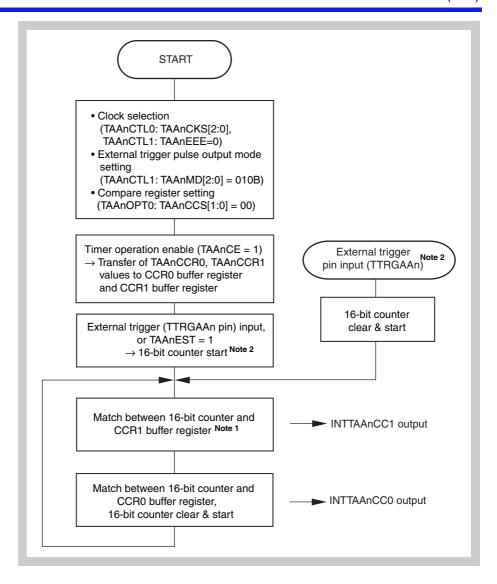

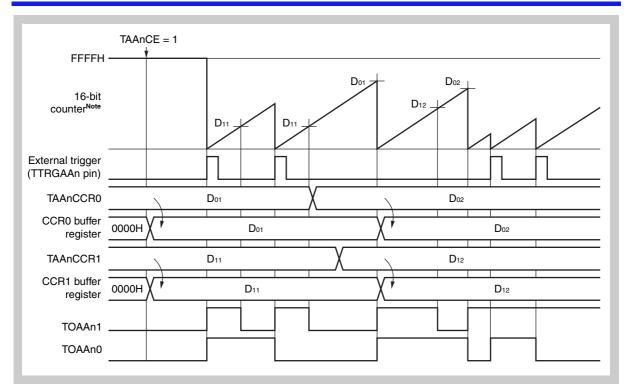

|              | 16.6.4                                                                                                                                                           | External trigger pulse mode (TAAnMD2 to TAAnMD0 = 010 <sub>B</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 639                                                                                     |

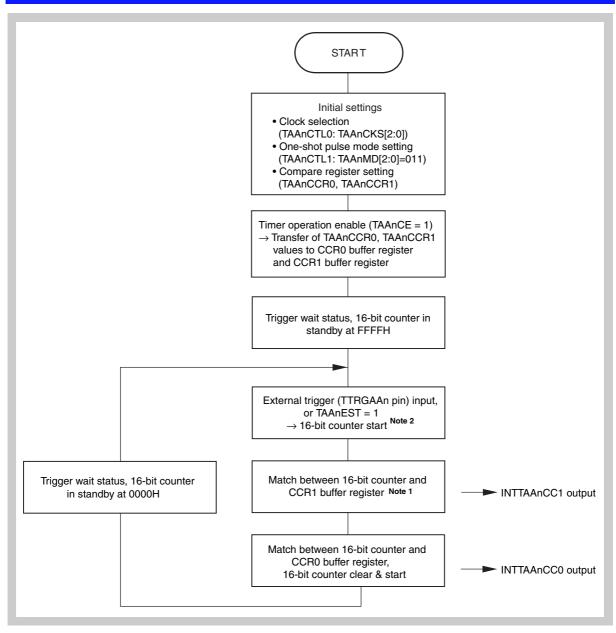

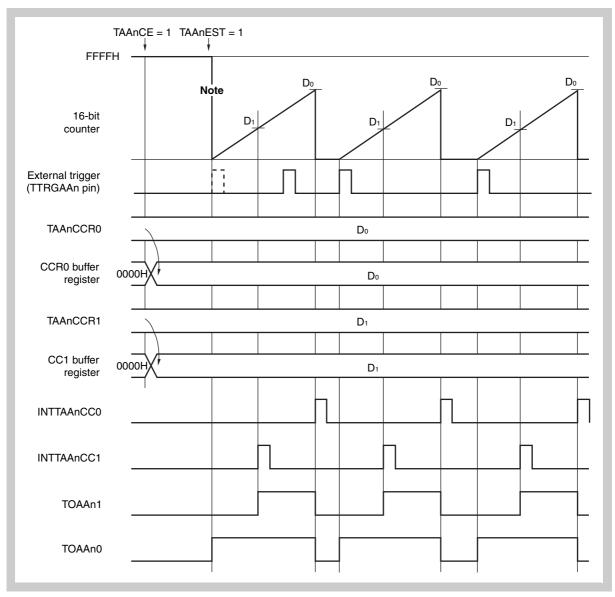

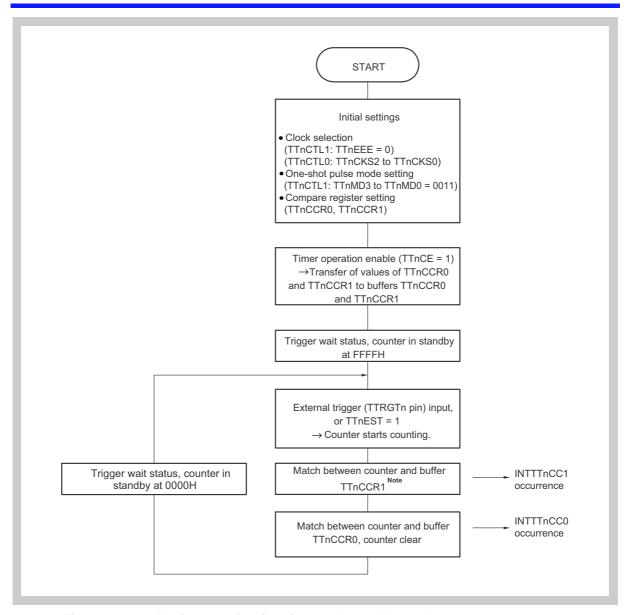

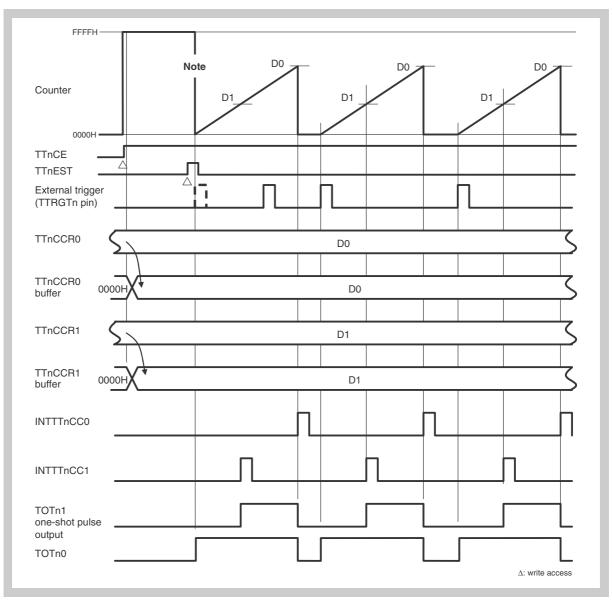

|              | 16.6.5                                                                                                                                                           | One-shot pulse mode (TAAnMD2 to TAAnMD0 = 011 <sub>B</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

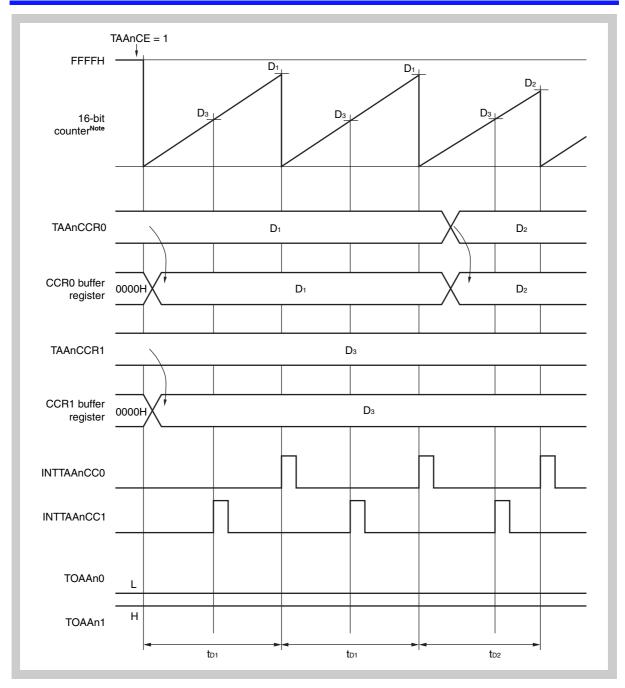

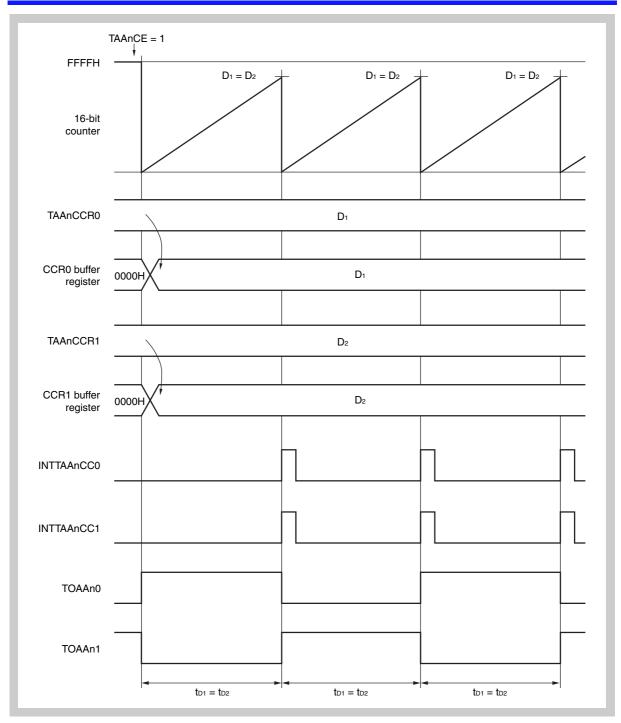

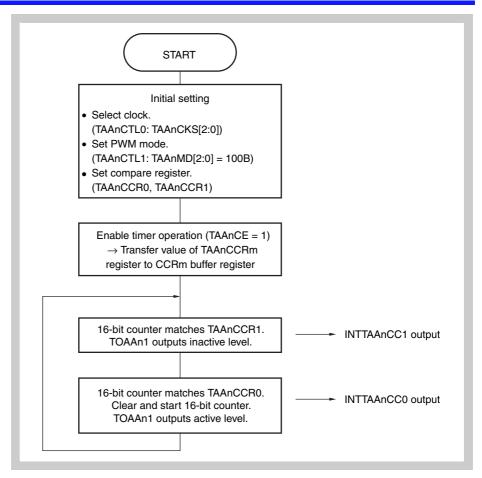

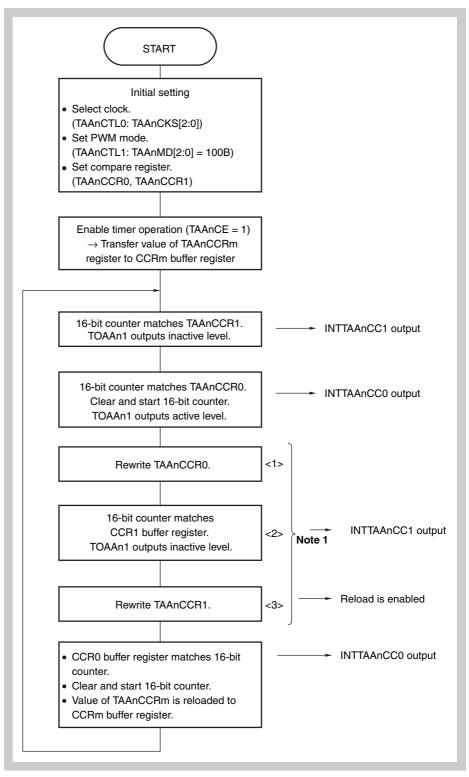

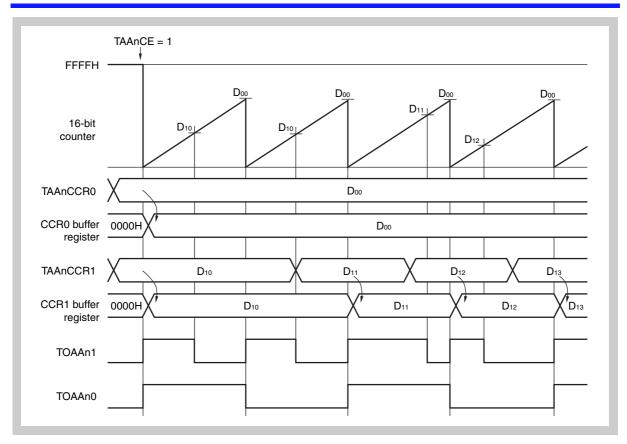

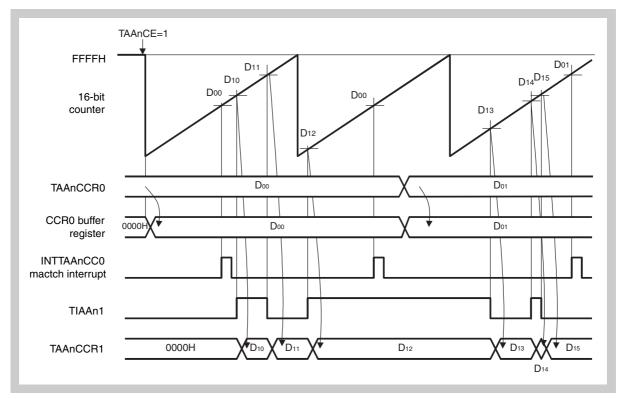

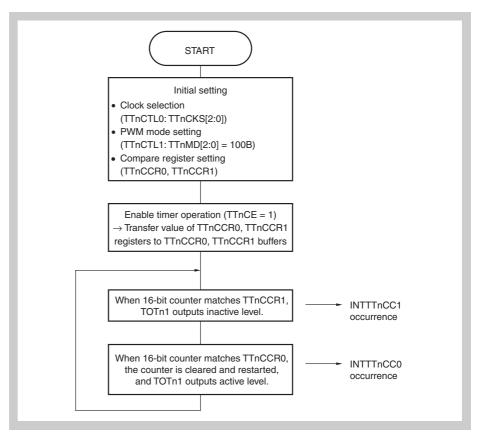

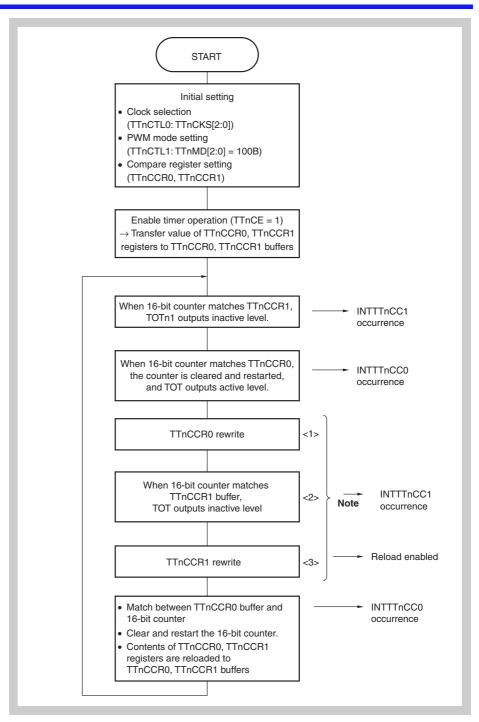

|              | 16.6.6                                                                                                                                                           | PWM mode (TAAnMD2 to TAAnMD0 = 100 <sub>B</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

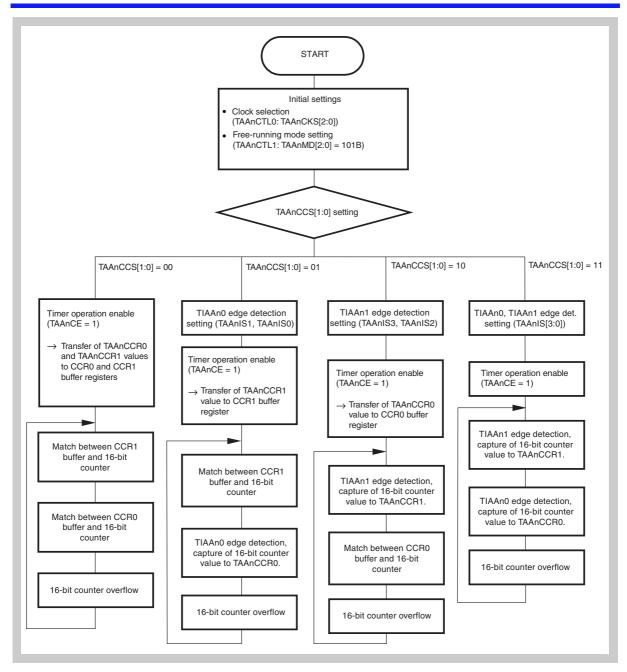

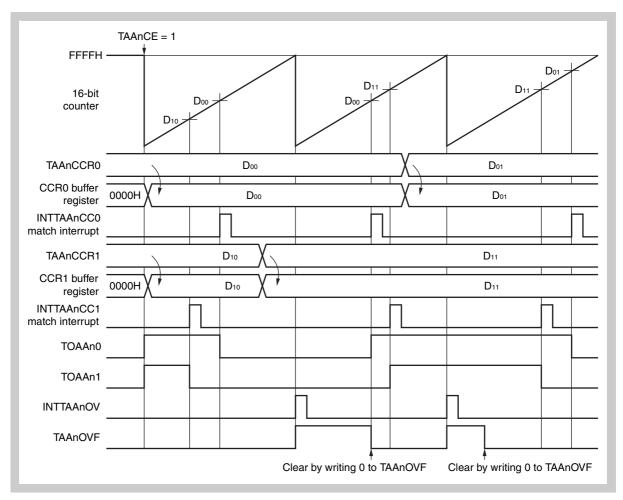

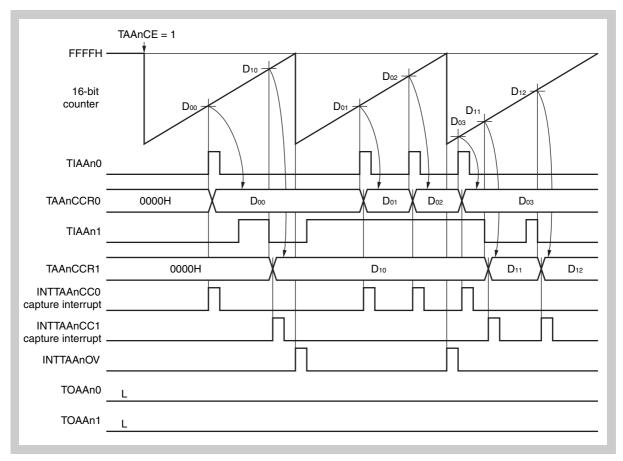

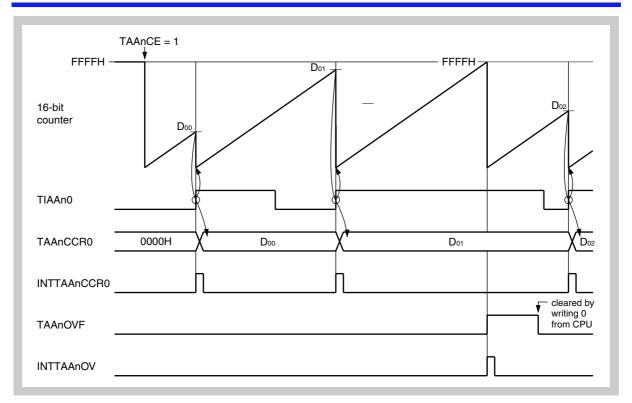

|              | 16.6.7                                                                                                                                                           | Free-running mode (TAAnMD2 to TAAnMD0 = 101 <sub>B</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

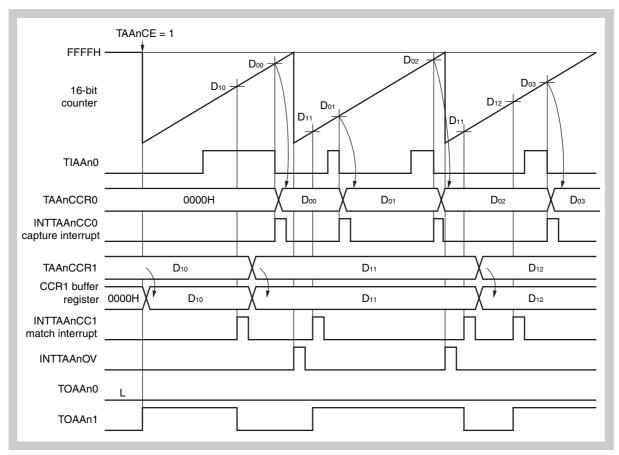

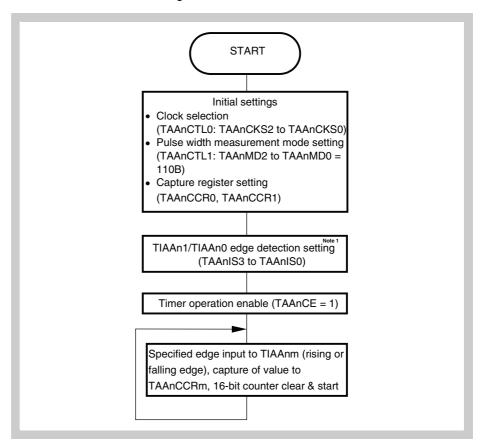

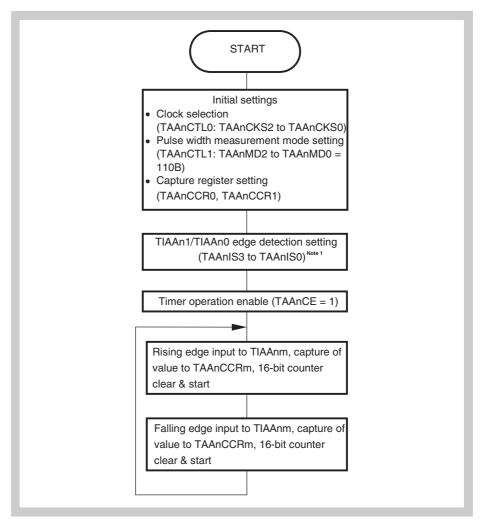

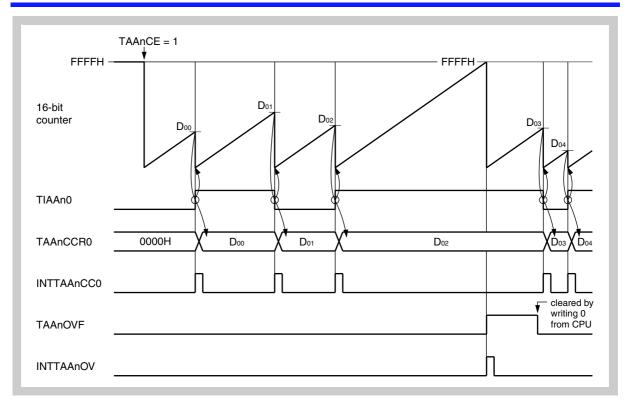

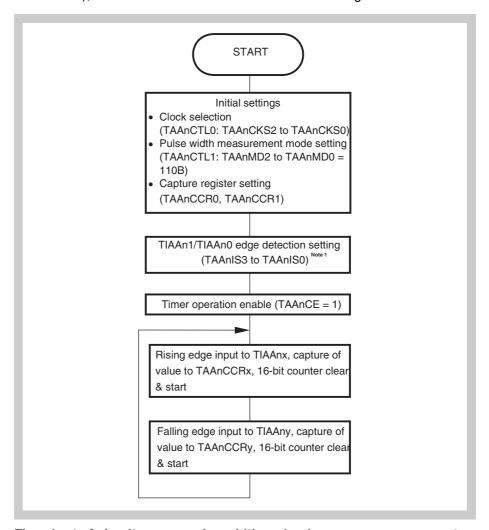

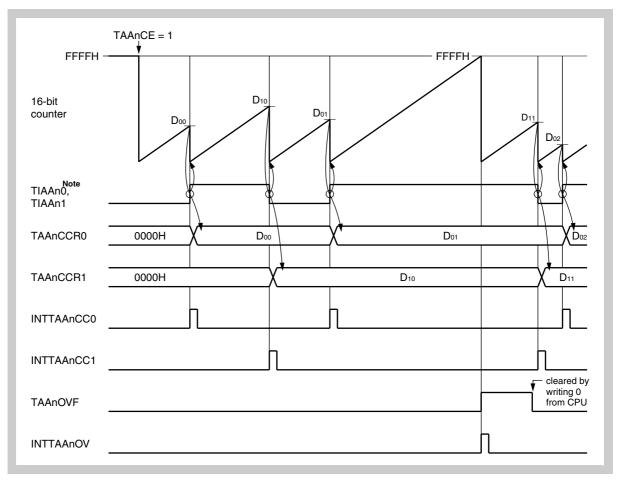

|              | 16.6.8                                                                                                                                                           | Pulse width measurement mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 000                                                                                     |

|              | 10.0.6                                                                                                                                                           | (TAAnMD2 to TAAnMD0 = 110B)656                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

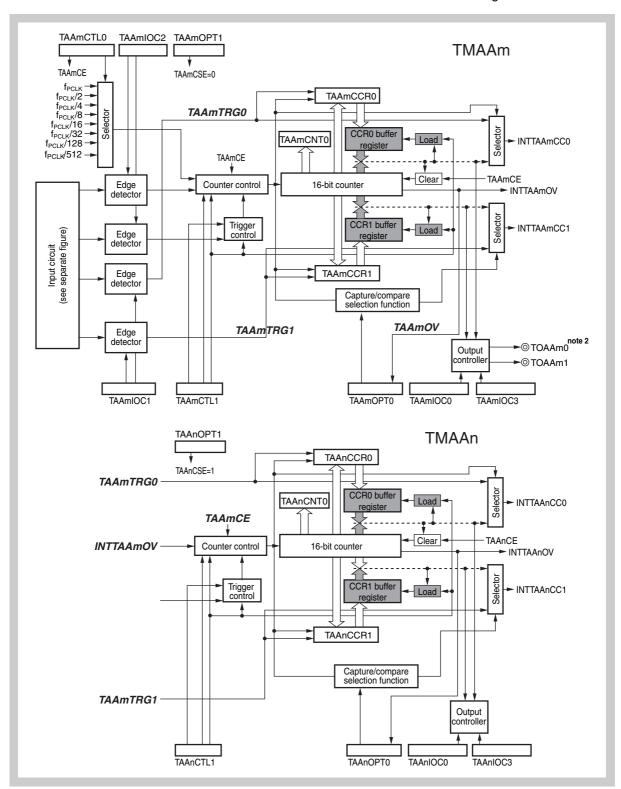

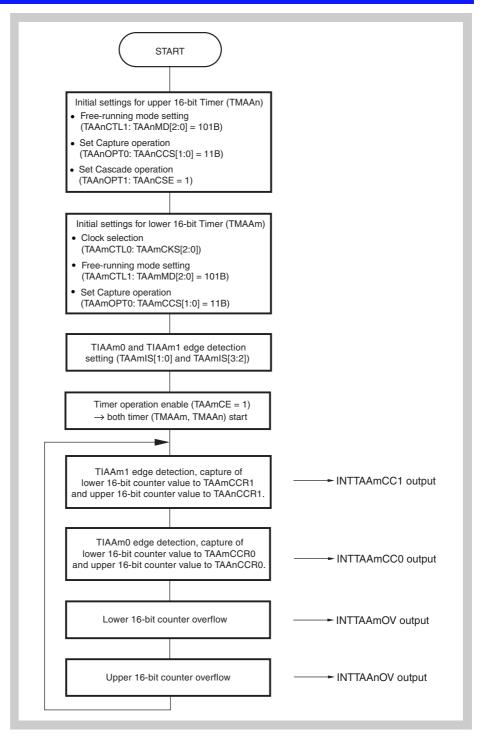

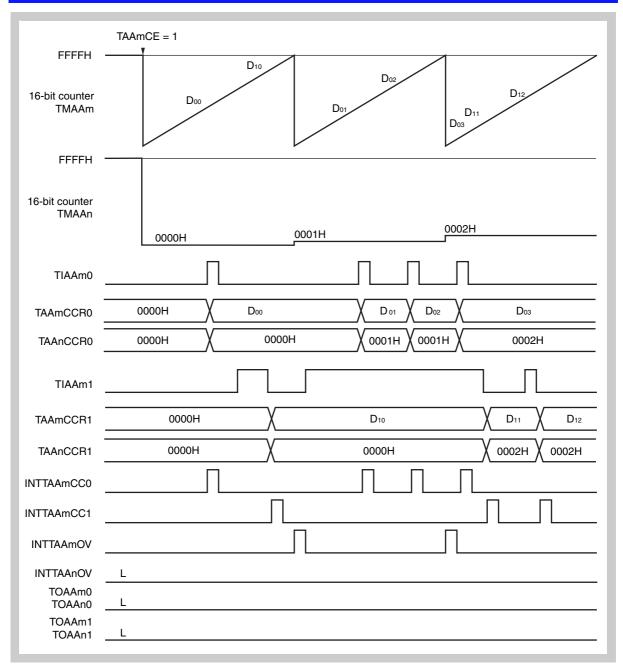

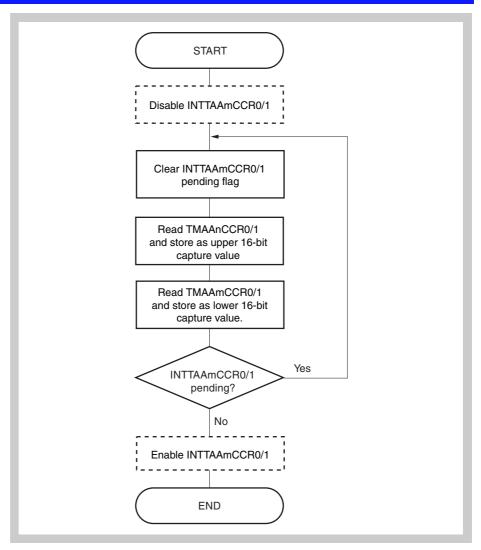

|              | 16.6.9                                                                                                                                                           | 32-bit Capture in free-running cascade mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 663                                                                                     |

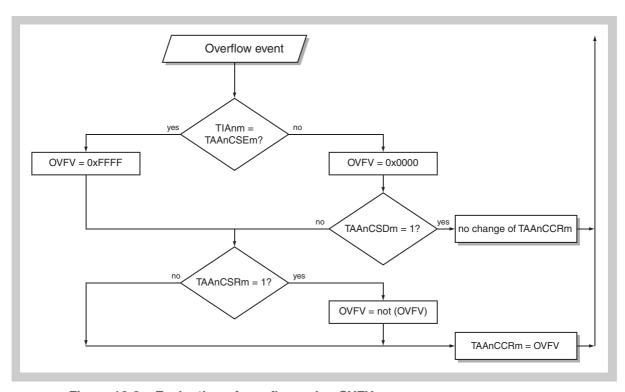

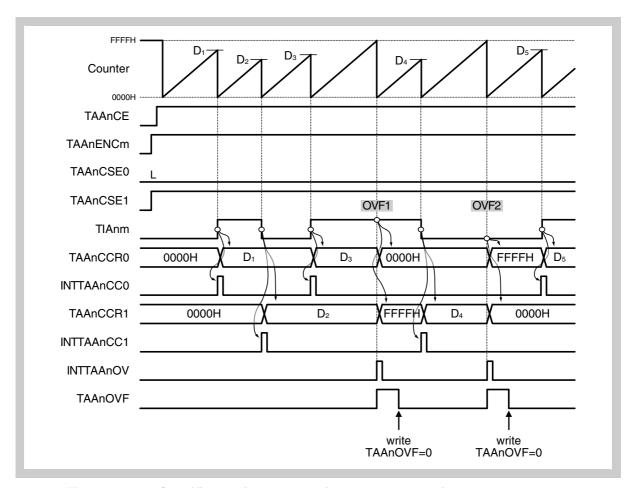

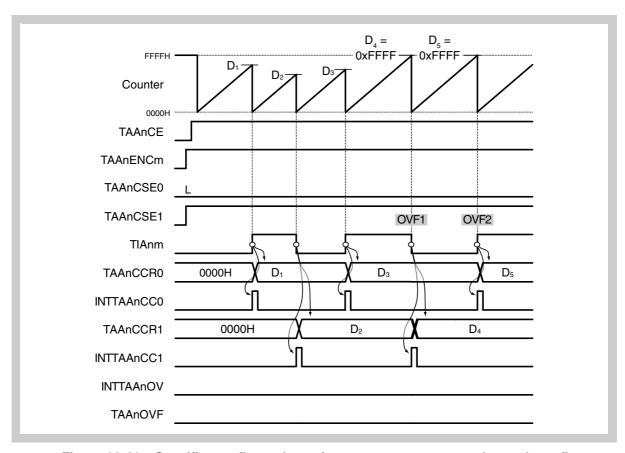

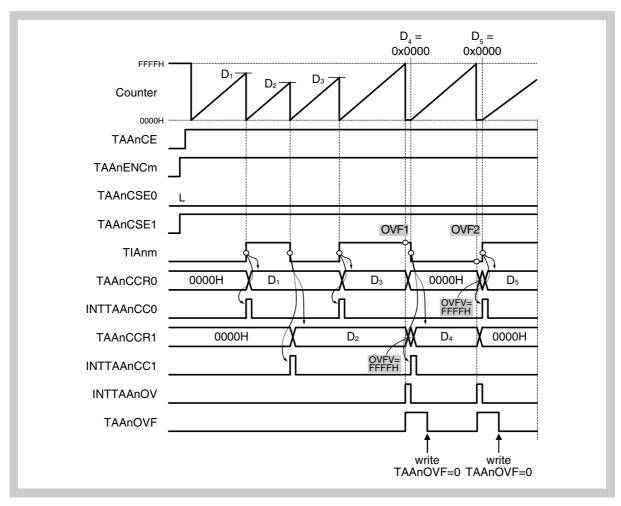

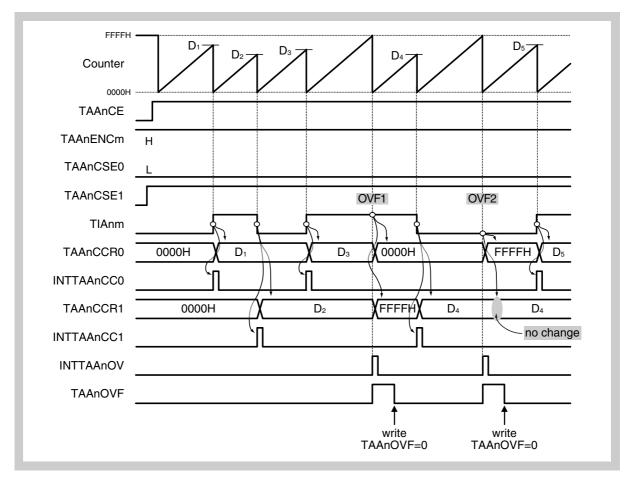

|              | 16.6.10                                                                                                                                                          | Specific TAAnCCRm overflow value write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| 16.7         |                                                                                                                                                                  | Synchronization Operation Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

|              |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

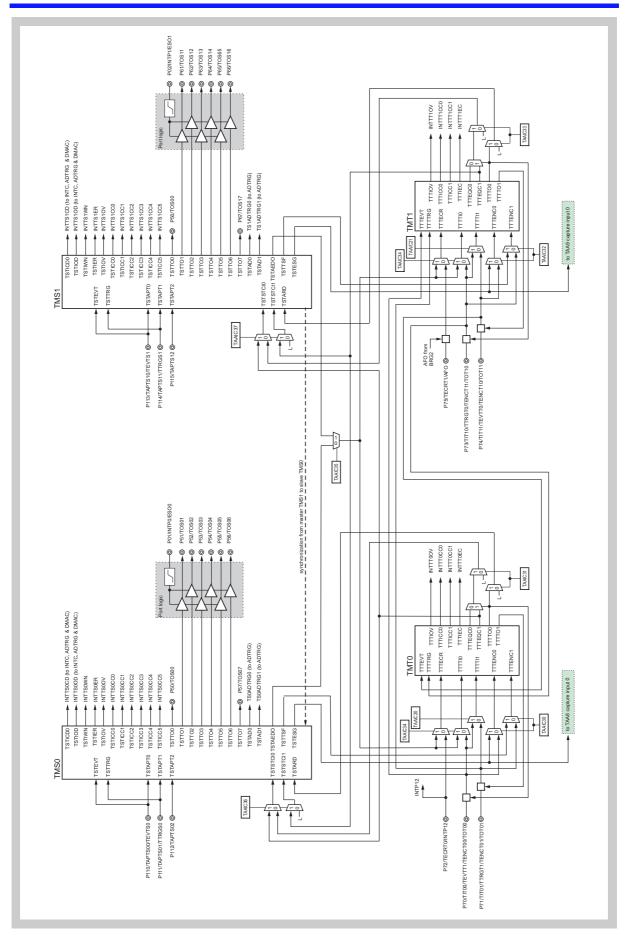

| _            |                                                                                                                                                                  | 16-Bit Timer/Event Counter S (TMS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

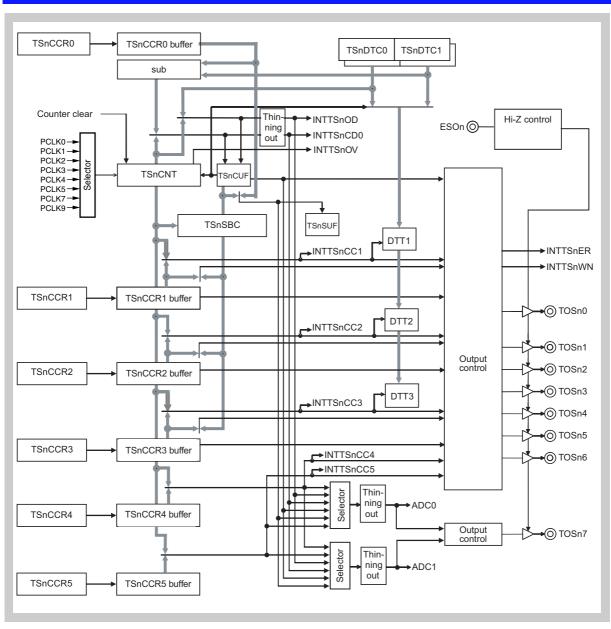

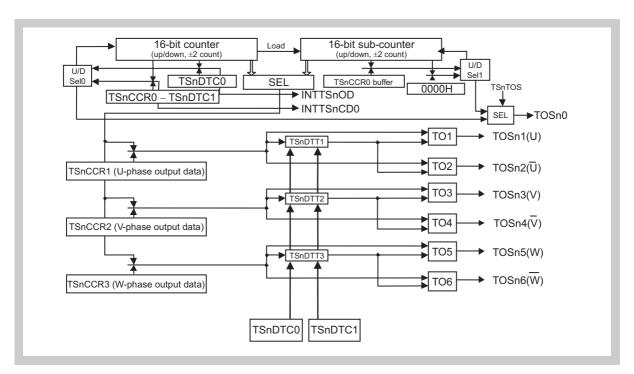

| 17.1         |                                                                                                                                                                  | s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

| 17.2         | •                                                                                                                                                                | uration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

| 17.3         |                                                                                                                                                                  | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | คดก                                                                                     |

| 17.4         | D ! - 0                                                                                                                                                          | No. 2 - 2 - 2 - 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

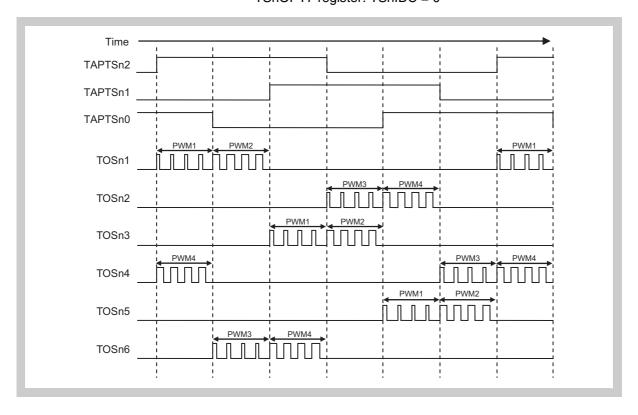

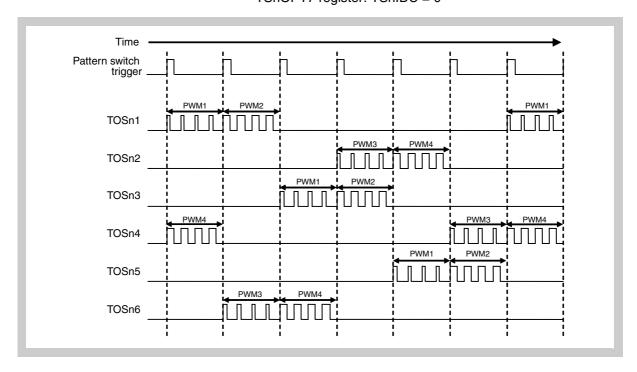

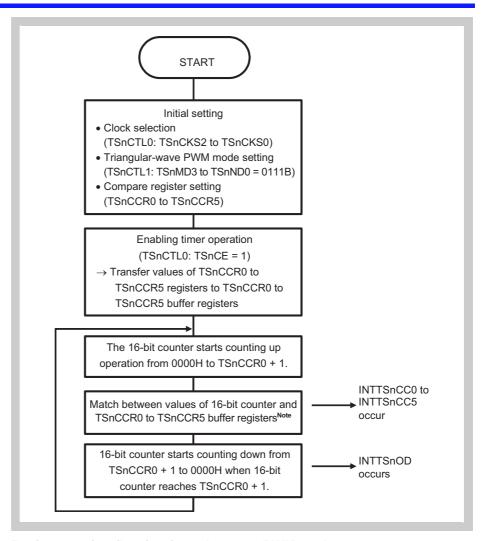

|              |                                                                                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 752                                                                                     |

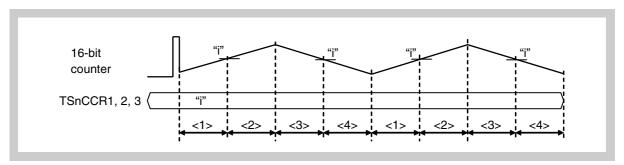

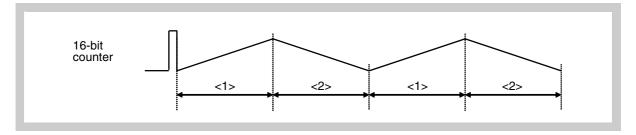

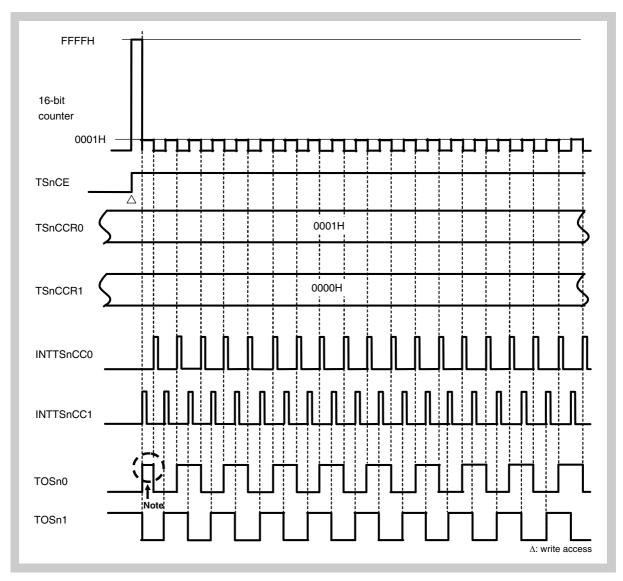

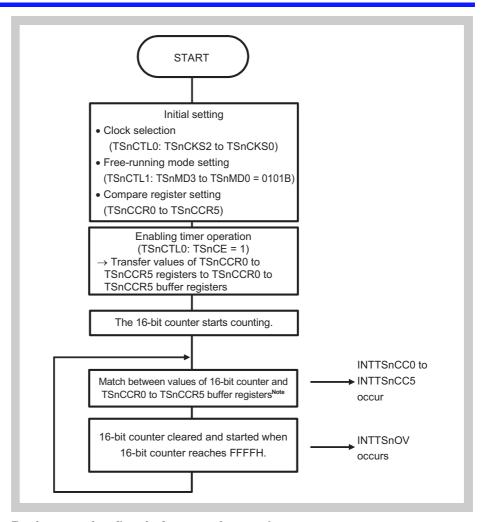

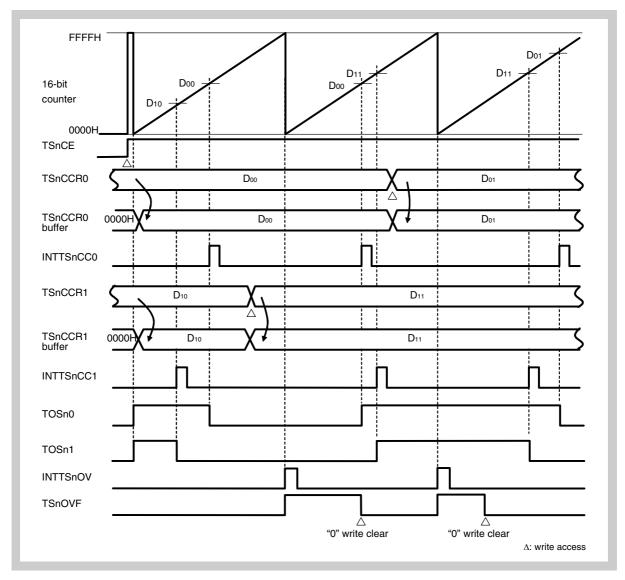

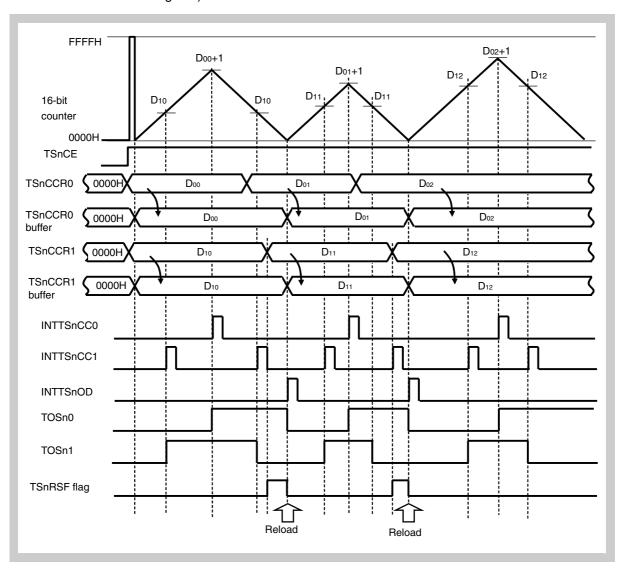

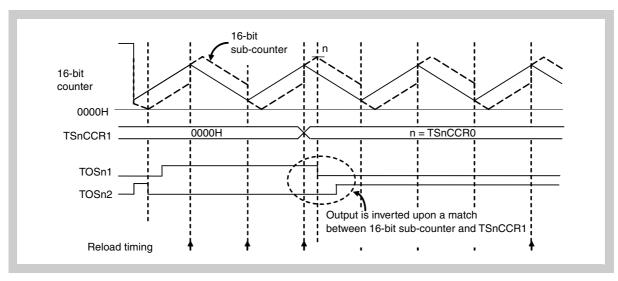

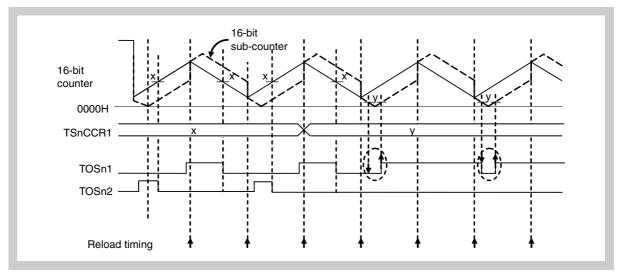

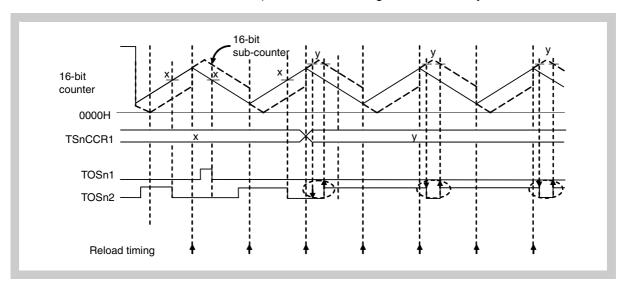

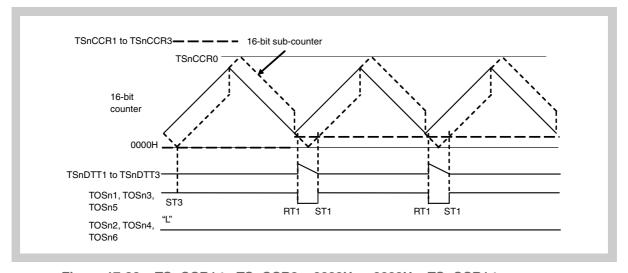

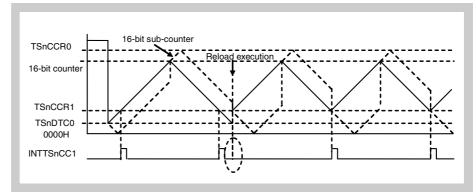

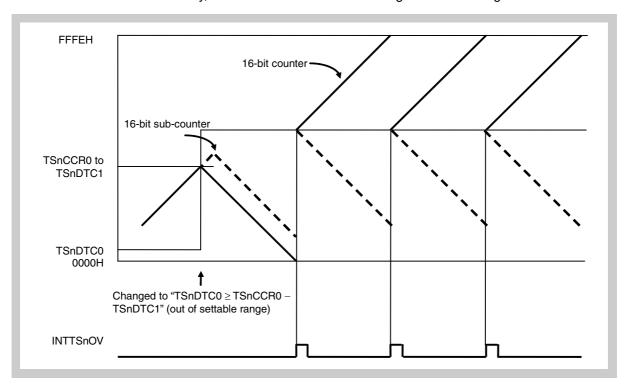

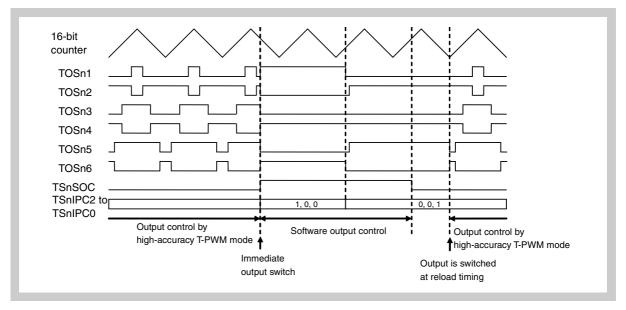

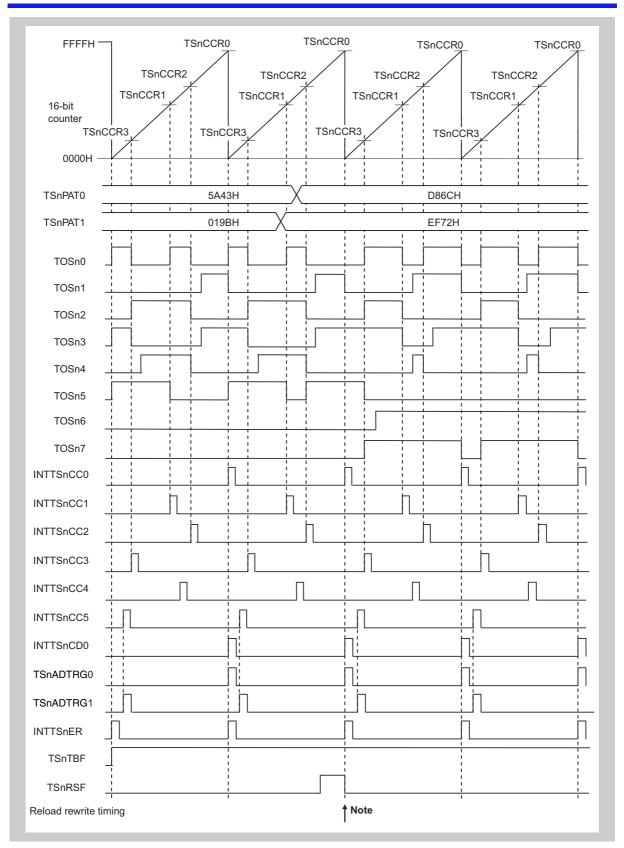

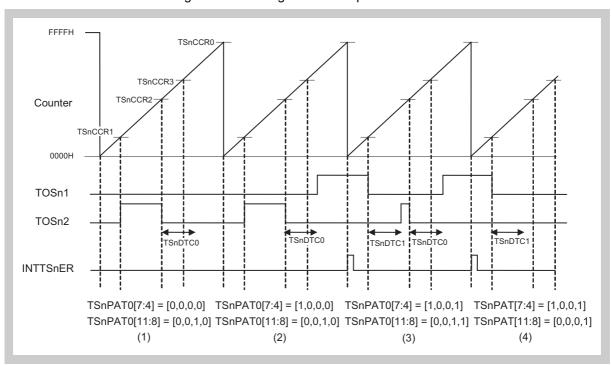

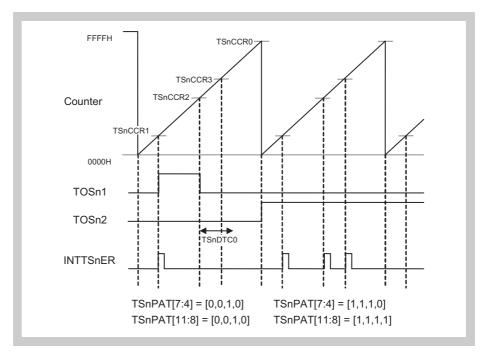

|              | 17.4.1                                                                                                                                                           | 16-bit counter basic operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 752<br>752                                                                              |

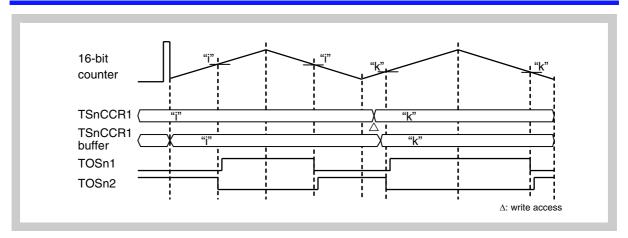

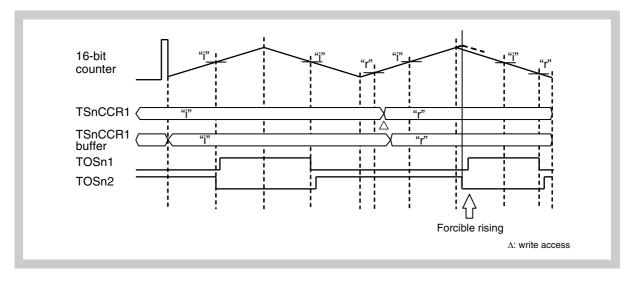

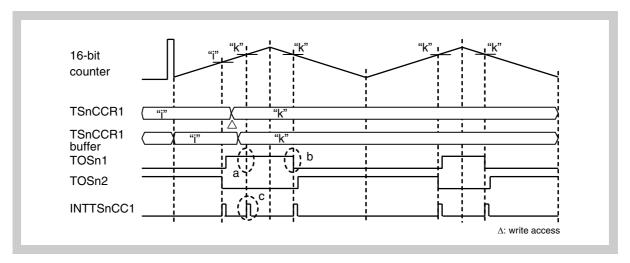

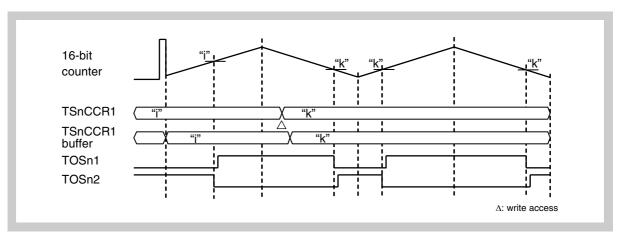

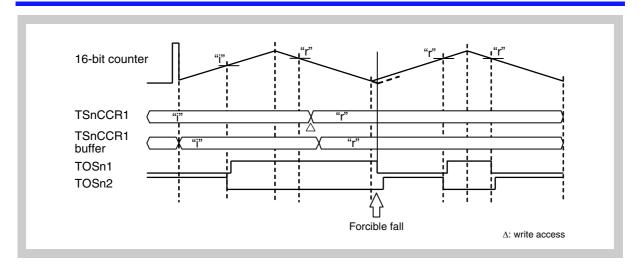

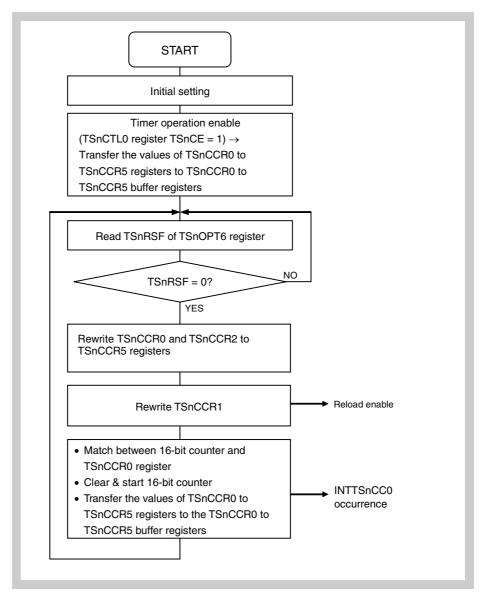

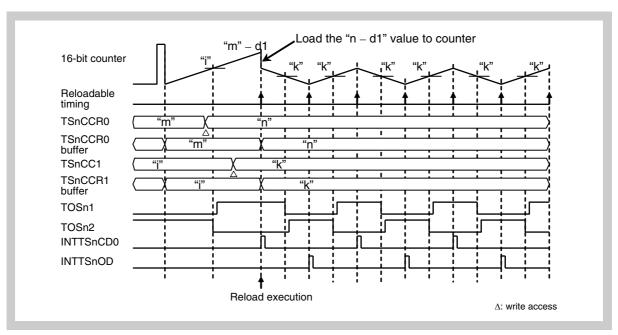

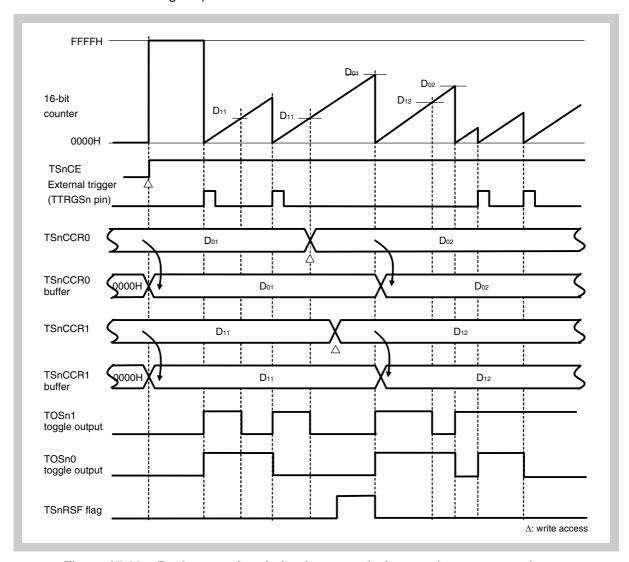

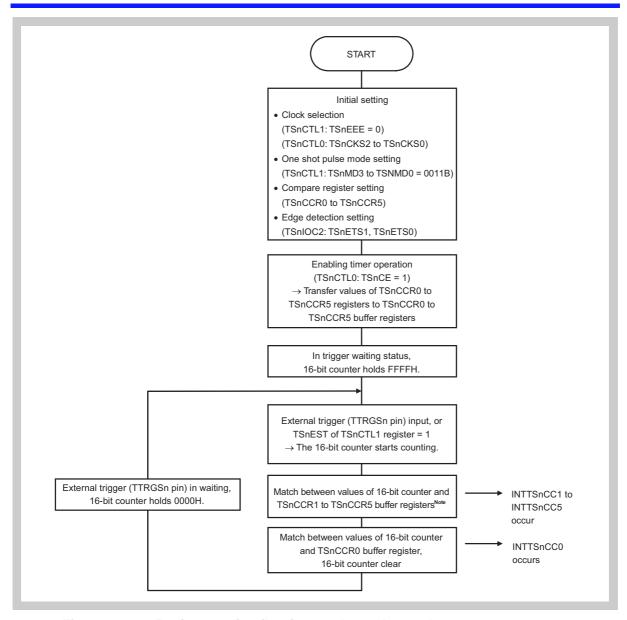

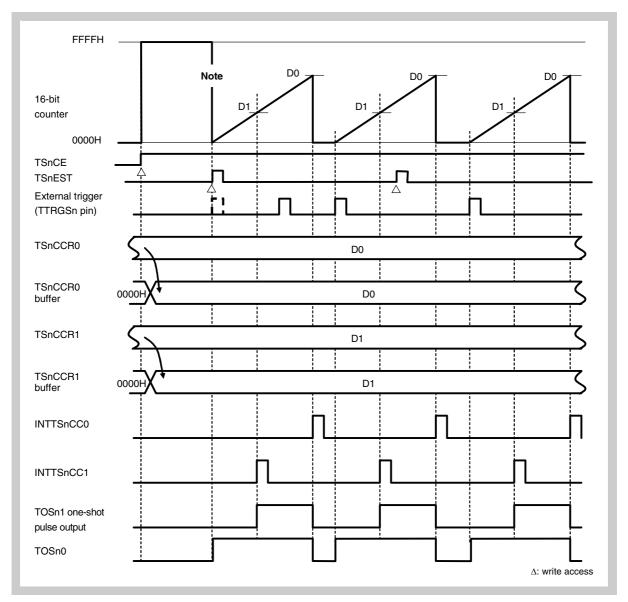

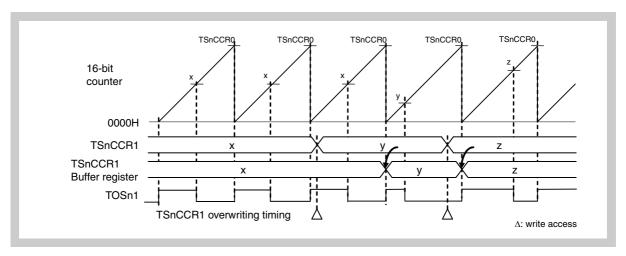

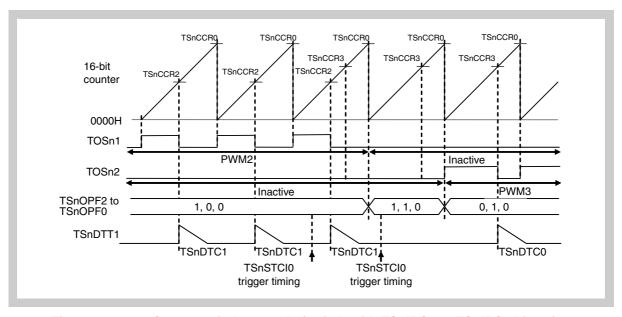

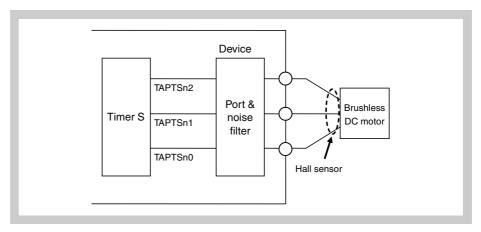

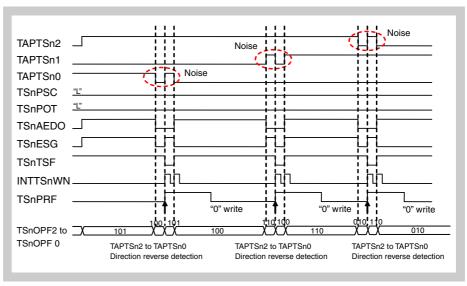

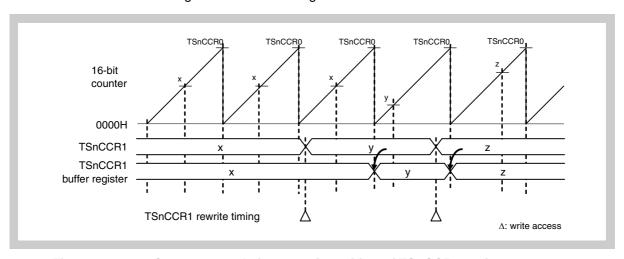

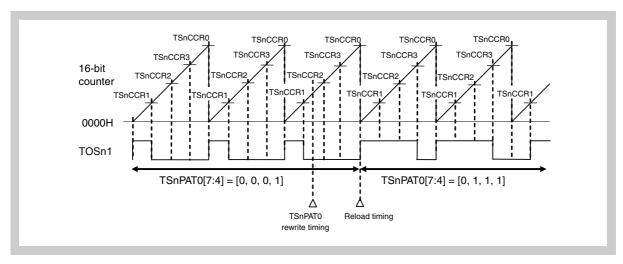

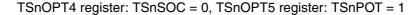

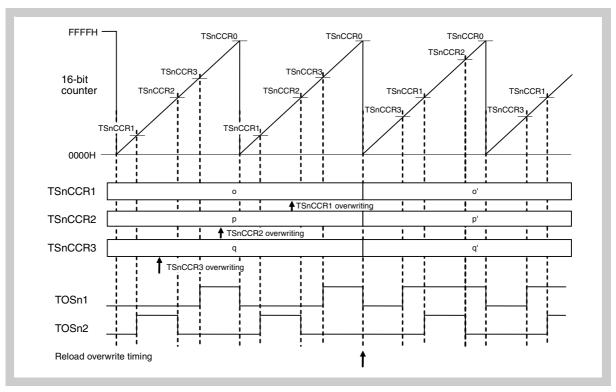

|              | 17.4.1<br>17.4.2                                                                                                                                                 | 16-bit counter basic operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 752<br>752<br>754                                                                       |

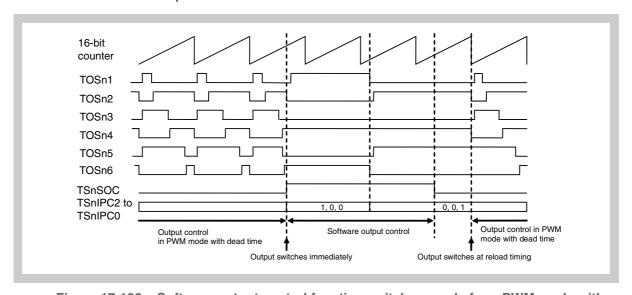

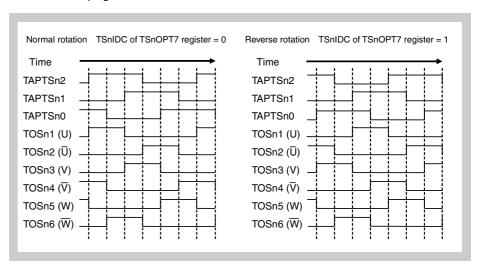

| 17 5         | 17.4.1<br>17.4.2<br>17.4.3                                                                                                                                       | 16-bit counter basic operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 752<br>752<br>754<br>768                                                                |

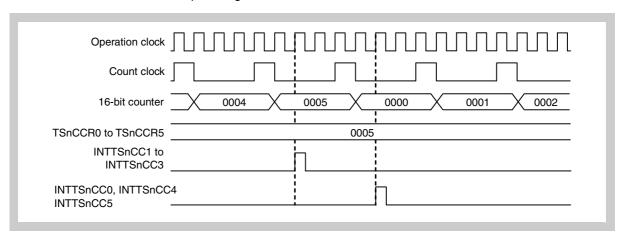

| 17.5         | 17.4.1<br>17.4.2<br>17.4.3<br><b>Match I</b>                                                                                                                     | 16-bit counter basic operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 752<br>752<br>754<br>768                                                                |

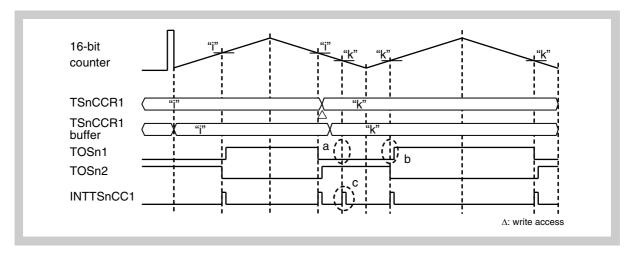

|              | 17.4.1<br>17.4.2<br>17.4.3<br><b>Match I</b><br>17.5.1                                                                                                           | 16-bit counter basic operation.  Compare register rewriting.  Output list in each mode.  nterrupt  Caution on compare match interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                           | 752<br>752<br>754<br>768<br>776                                                         |

| 17.5<br>17.6 | 17.4.1<br>17.4.2<br>17.4.3<br><b>Match I</b><br>17.5.1<br><b>Flags</b>                                                                                           | 16-bit counter basic operation.  Compare register rewriting.  Output list in each mode  nterrupt  Caution on compare match interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                            | 752<br>754<br>768<br>776<br>778                                                         |

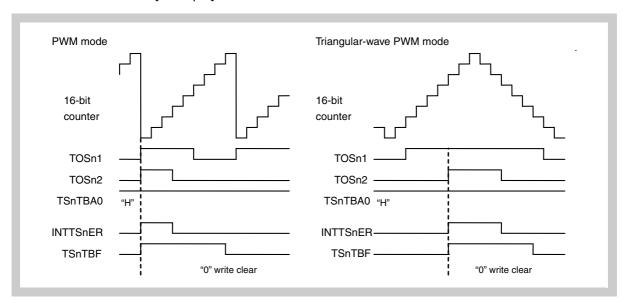

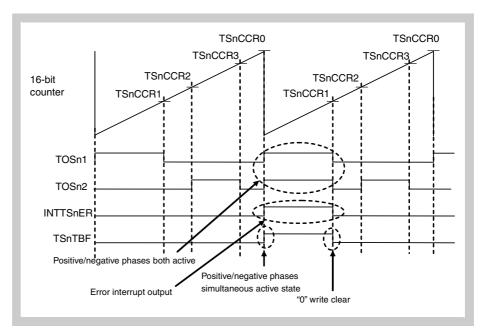

|              | 17.4.1<br>17.4.2<br>17.4.3<br><b>Match I</b><br>17.5.1<br><b>Flags</b>                                                                                           | 16-bit counter basic operation.  Compare register rewriting.  Output list in each mode.  nterrupt  Caution on compare match interrupt.  Count-up flags (TSnCUF, TSnSUF).                                                                                                                                                                                                                                                                                                                                                                                                         | 752<br>754<br>768<br>776<br>778<br>779                                                  |

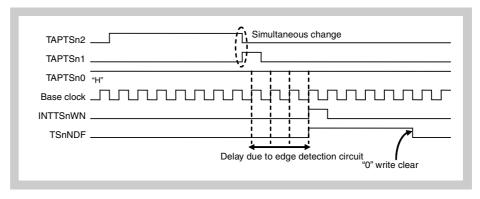

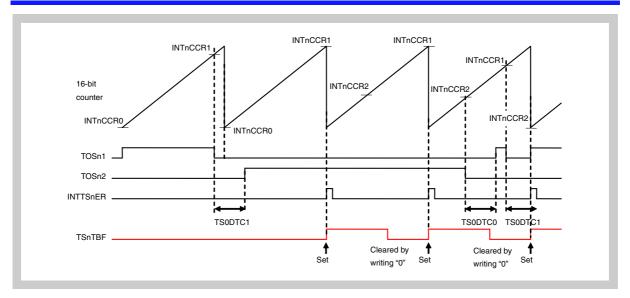

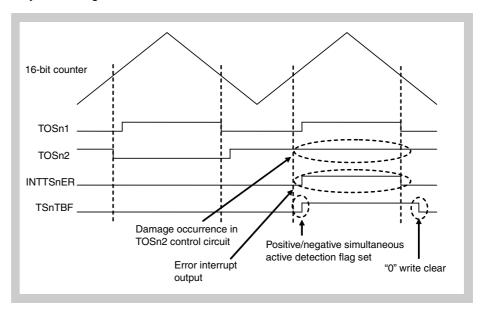

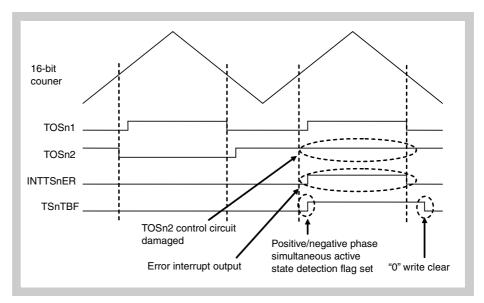

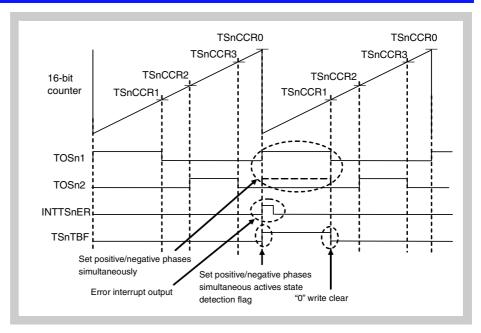

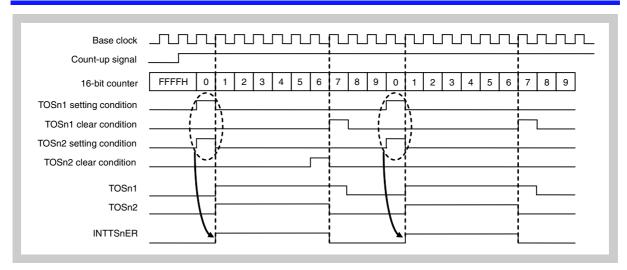

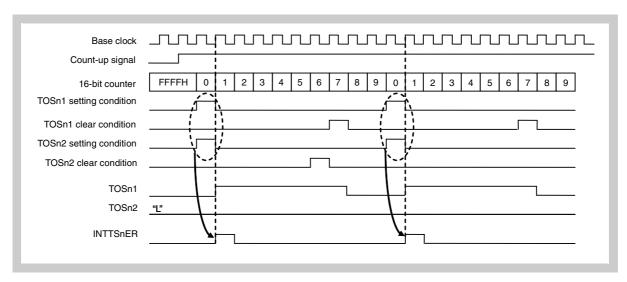

|              | 17.4.1<br>17.4.2<br>17.4.3<br><b>Match I</b><br>17.5.1<br><b>Flags</b><br>17.6.1<br>17.6.2                                                                       | 16-bit counter basic operation.  Compare register rewriting.  Output list in each mode  nterrupt  Caution on compare match interrupt  Count-up flags (TSnCUF, TSnSUF)  Positive/negative-phase simultaneous active detection flag (TSnTBF).                                                                                                                                                                                                                                                                                                                                      | 752<br>754<br>768<br>776<br>778<br>779<br>780                                           |

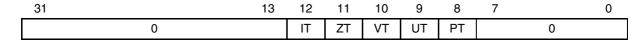

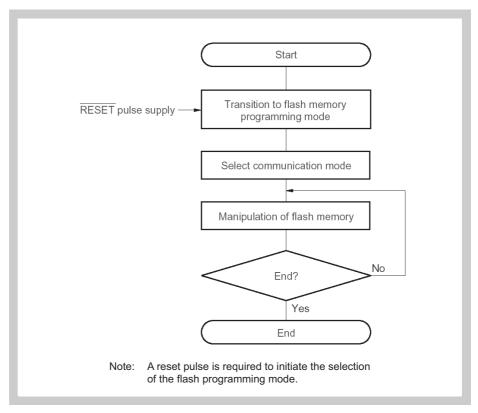

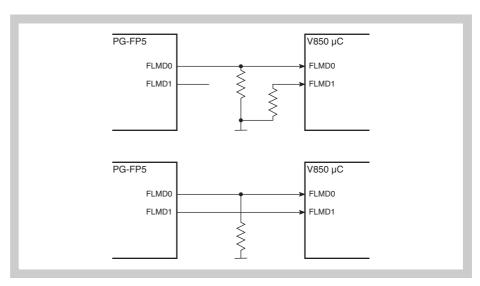

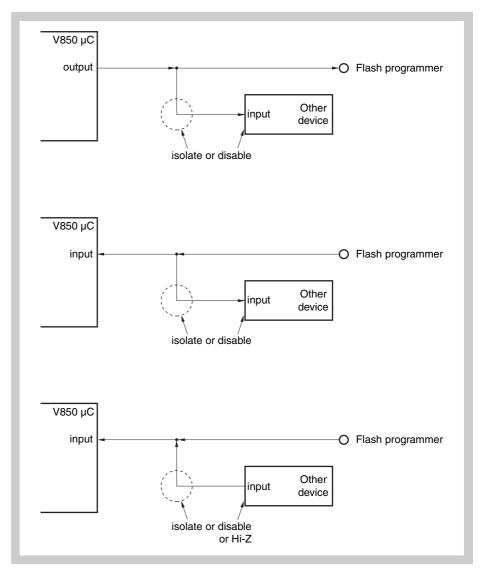

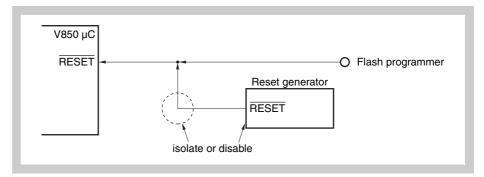

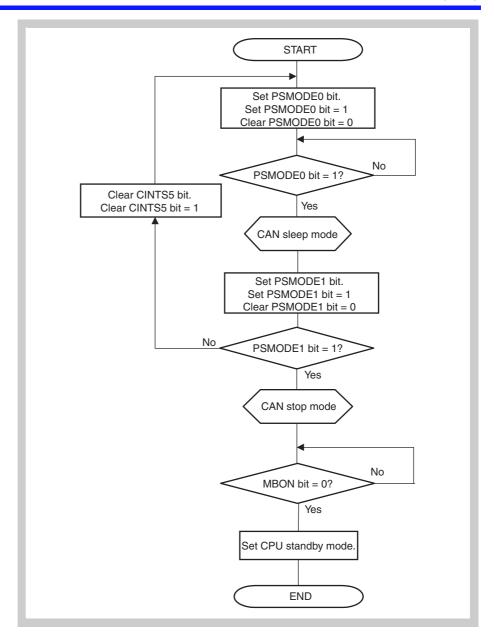

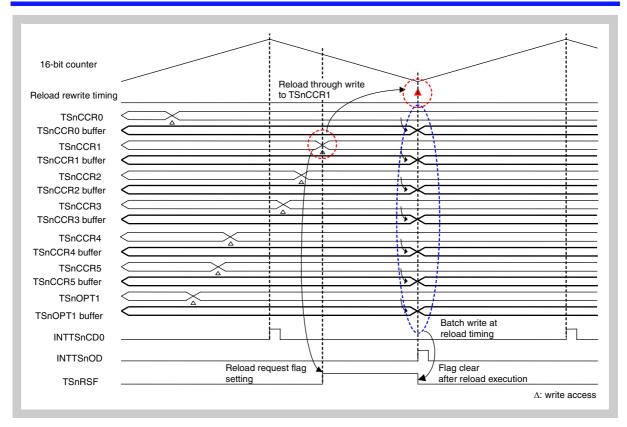

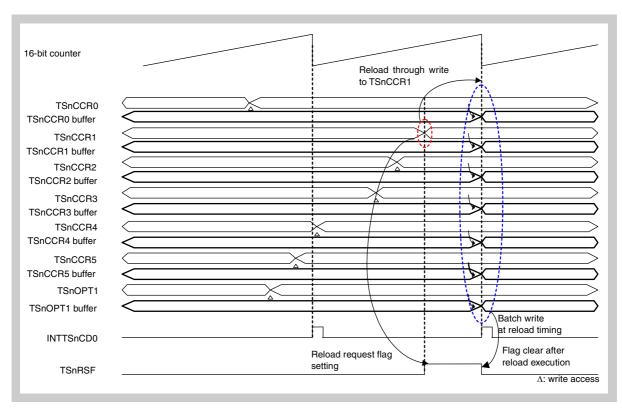

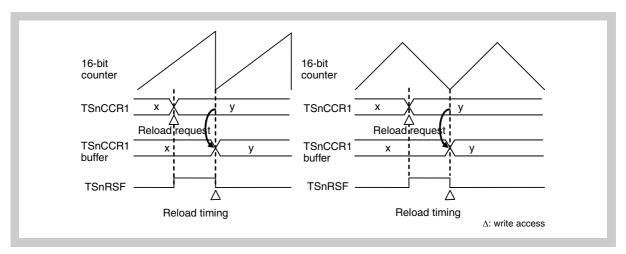

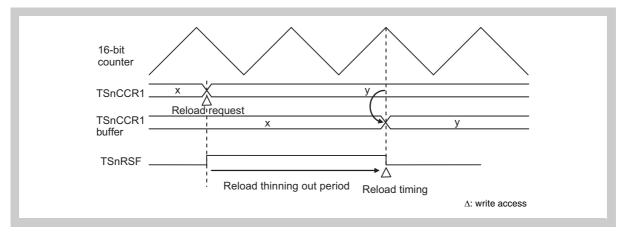

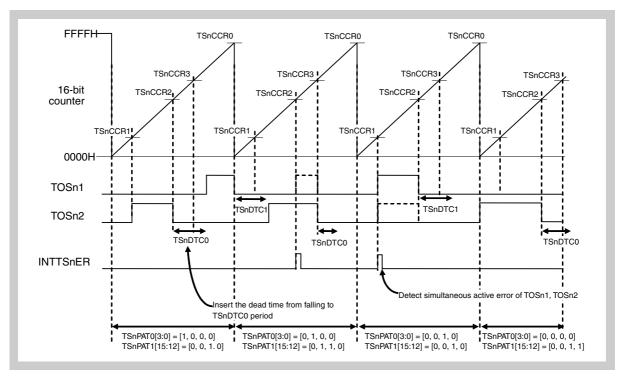

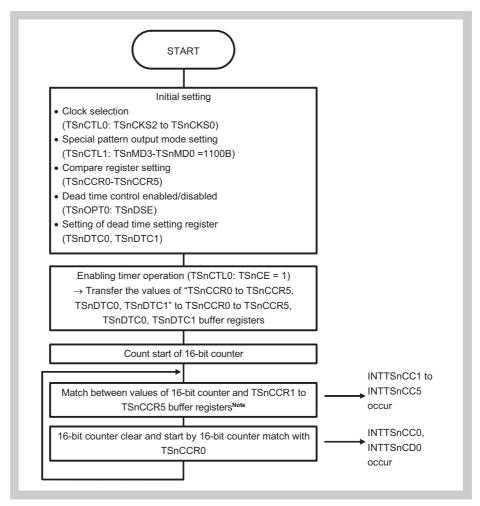

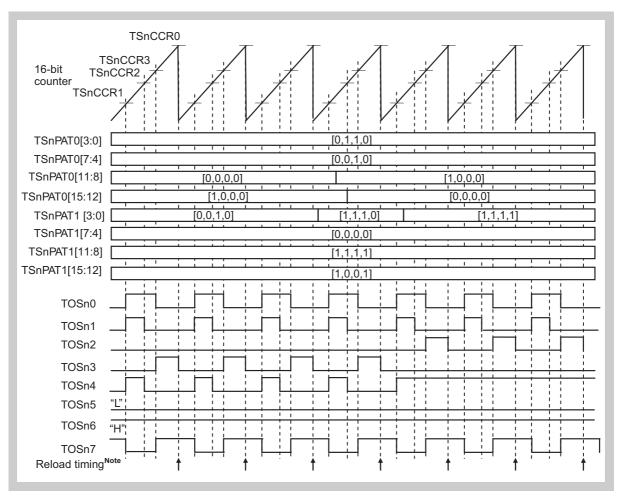

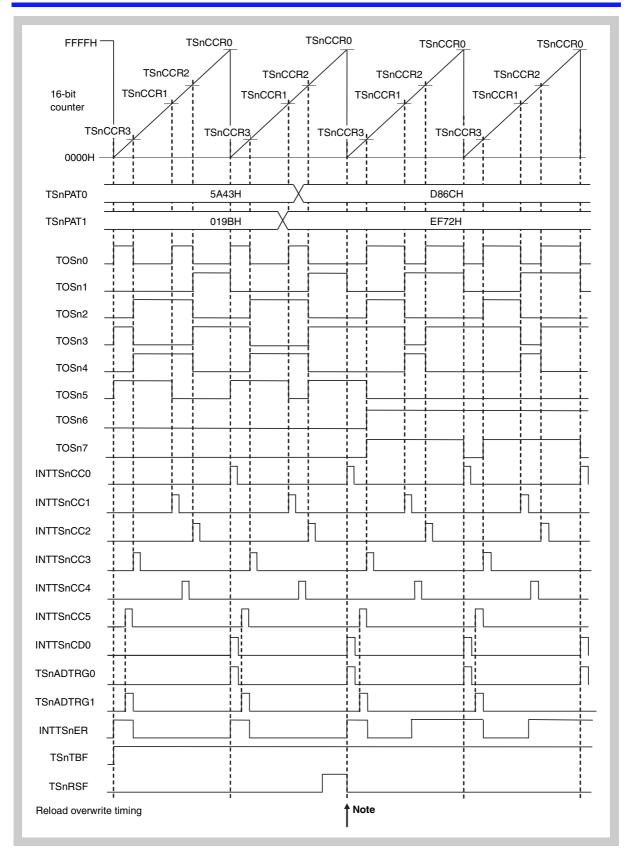

|              | 17.4.1<br>17.4.2<br>17.4.3<br><b>Match I</b><br>17.5.1<br><b>Flags</b><br>17.6.1<br>17.6.2<br>17.6.3                                                             | 16-bit counter basic operation.  Compare register rewriting.  Output list in each mode.  nterrupt.  Caution on compare match interrupt.  Count-up flags (TSnCUF, TSnSUF).  Positive/negative-phase simultaneous active detection flag (TSnTBF).  Reload request flag (TSnRSF).                                                                                                                                                                                                                                                                                                   | 752<br>752<br>754<br>768<br>776<br>779<br>780<br>783<br>784                             |