# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

# μPD789800サプシリーズ

8ビット・シングルチップ・マイクロコンピュータ

μPD789800 μPD78F9801

資料番号 U12978JJ3V3UD00 (第3版) 発行年月 August 2005 N CP(K)

# 目次要約

第1章 概 説 ... 22

第2章 端子機能 ... 29

第3章 CPUアーキテクチャ ... 36

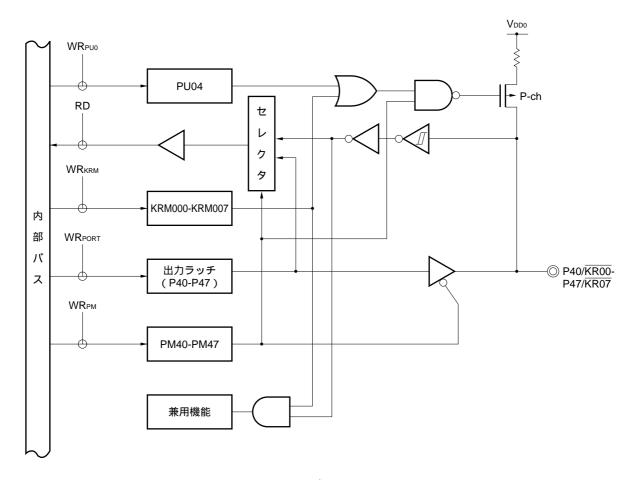

第4章 ポート機能 ... 58

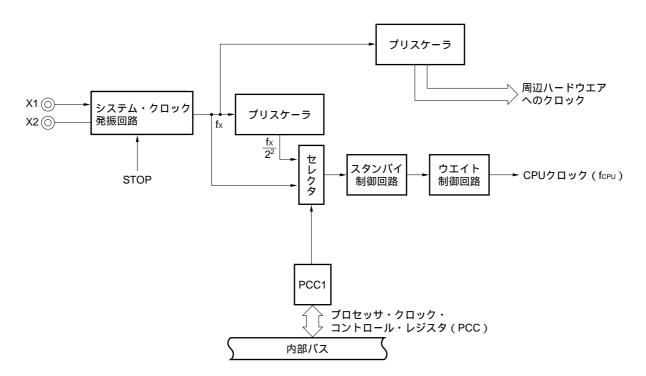

**第5章 クロック発生回路** ... 74

**第6章 8ビット・タイマ/イベント・カウンタ**00,01 ... 81

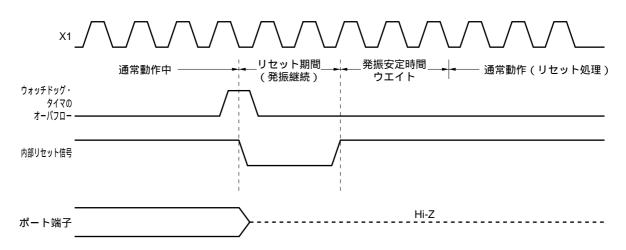

第7章 ウォッチドッグ・タイマ ... 93

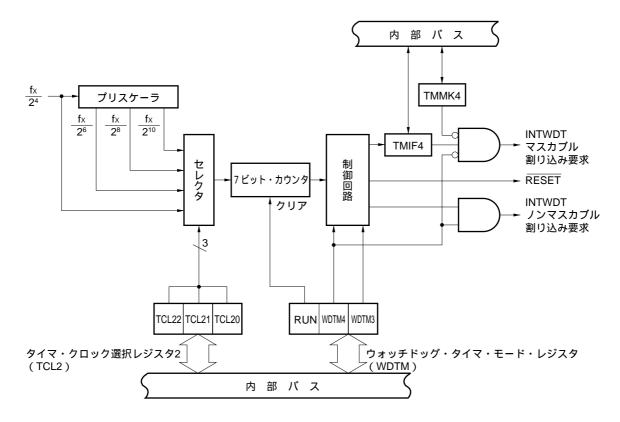

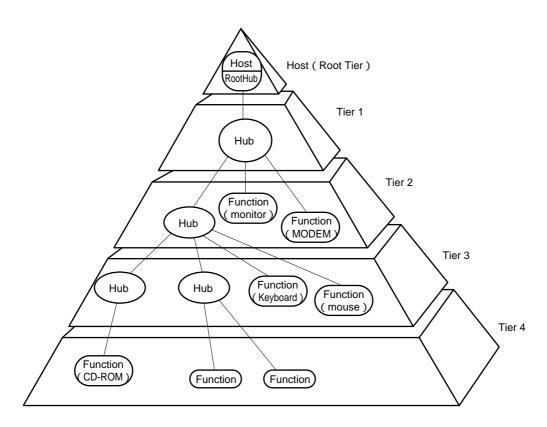

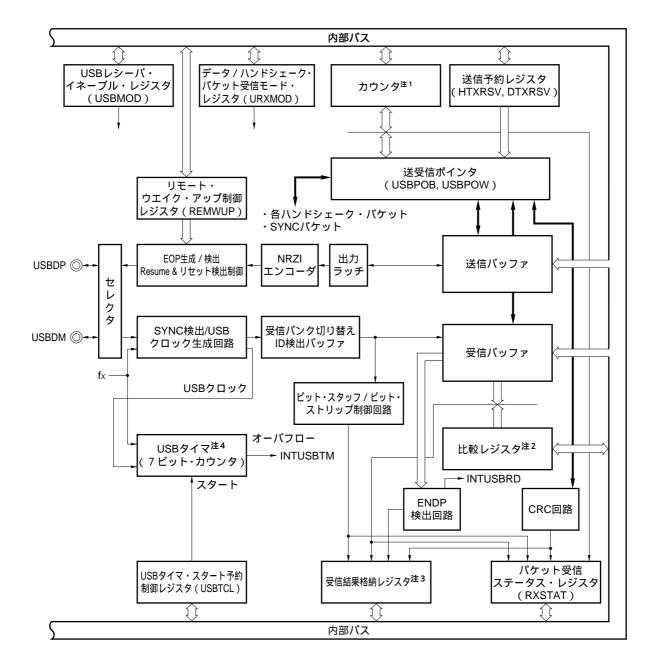

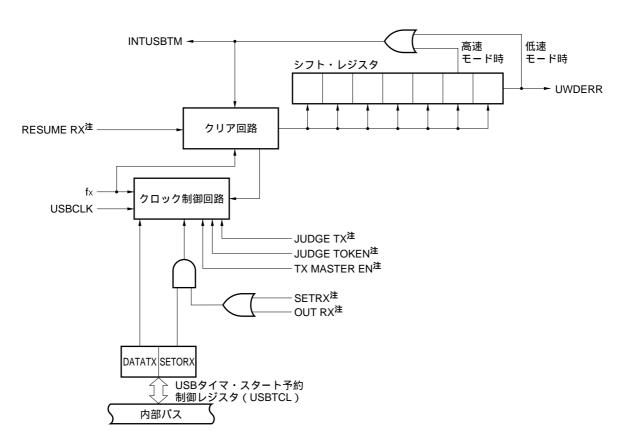

**第8章** USBファンクション ... 99

第9章 シリアル・インタフェース10 ... 159

第10章 レギュレータ ... 167

第11章 割り込み機能 ... 168

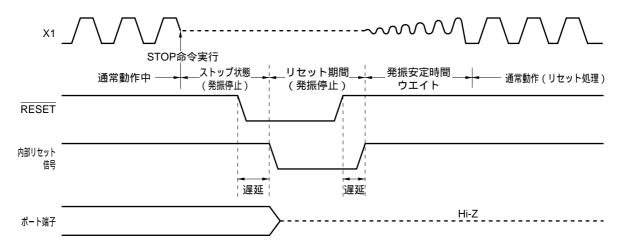

第12章 スタンパイ機能 ... 183

第13章 リセット機能 ... 191

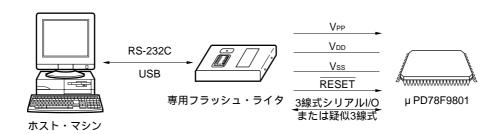

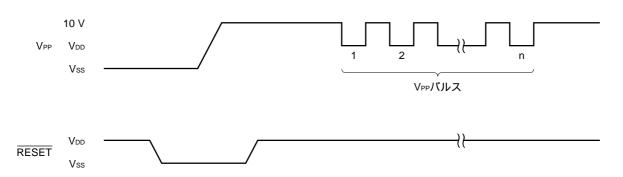

**第**14**章** μ PD78F9801 ... 195

第15章 命令セットの概要 ... 205

第16章 電気的特性 ... 216

第17章 外形図 ... 225

第18章 半田付け推奨条件 ... 226

付録A 開発ツール ... 227

付録B レジスタ索引 ... 235

付録C 改版履歴 ... 240

### CMOSデバイスの一般的注意事項

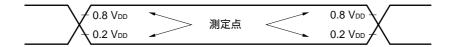

#### 入力端子の印加波形

#### 入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

CMOSデバイスの入力がノイズなどに起因して, $V_L$ (MAX.)から $V_H$ (MIN.)までの領域にとどまるような場合は,誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん, $V_L$ (MAX.)から $V_H$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

#### 未使用入力の処理

#### CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVpoまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については,その内容を守ってください。

#### 静電気対策

#### MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また, MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 初期化以前の状態

#### 電源投入時, MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

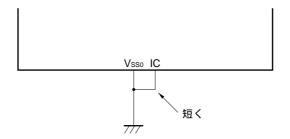

#### 電源投入切断順序

内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には,原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により,内部素子に過電圧が印加され,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源投入切断シーケンス」についての記載のある製品については、その内容を守ってください。

#### 電源OFF時における入力信号

当該デバイスの電源がOFF状態の時に,入力信号や入出力プルアップ電源を入れないでください。 入力信号や入出力プルアップ電源からの電流注入により,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

FIPは, NECエレクトロニクス株式会社の登録商標です。

EEPROMは, NECエレクトロニクス株式会社の商標です。

WindowsおよびWindowsNTは,米国Microsoft Corporationの米国およびその他の国における登録商標または商標です。

PC/ATは,米国IBM社の商標です。

HP9000シリーズ700, HP-UXは,米国ヒューレット・パッカード社の商標です。

SPARCstationは,米国SPARC International, Inc.の商標です。

Solaris, SunOSは,米国サン・マイクロシステムズ社の商標です。

本製品のうち,外国為替および外国貿易管理法の規定により規制貨物等(または役務)に該当するものについては,日本国外に輸出する際に,同法に基づき日本国政府の輸出許可が必要です。

非該当品 : μ PD78F9801 ユーザ判定品 : μ PD789800

- ◆本資料に記載されている内容は2005年8月現在のもので,今後,予告なく変更することがあります。量 産設計の際には最新の個別データ・シート等をご参照ください。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は,本資料の誤りに関し,一切 その責を負いません。

- 当社は,本資料に記載された当社製品の使用に関連し発生した第三者の特許権,著作権その他の知的財産権の侵害等に関し,一切その責を負いません。当社は,本資料に基づき当社または第三者の特許権,著作権その他の知的財産権を何ら許諾するものではありません。

- 本資料に記載された回路, ソフトウエアおよびこれらに関する情報は, 半導体製品の動作例, 応用例を 説明するものです。お客様の機器の設計において, 回路, ソフトウエアおよびこれらに関する情報を使 用する場合には, お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し, 当社は, 一切その責を負いません。

- 当社は,当社製品の品質,信頼性の向上に努めておりますが,当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命,身体および財産に対する損害の危険を最小限度にするために,冗長設計,延焼対策設計,誤動作防止設計等安全設計を行ってください。

- 当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定していただく「特定水準」に分類しております。また,各品質水準は,以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認ください。

標準水準:コンピュータ,OA機器,通信機器,計測機器,AV機器,家電,工作機械,パーソナル機器,産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート,データ・ブック等の資料で特に品質水準の表示がない場合は,標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には,事前に当社販売窓口までお問い合わせください。

(注)

- (1)本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2)本事項において使用されている「当社製品」とは、(1)において定義された当社の開発、製造製品をいう。

M8E 02.11

# 本版で改訂された主な箇所(1/2)

| 箇 所              | 内 容                                                                        |

|------------------|----------------------------------------------------------------------------|

| 全 般              | CUタイプとGB-3BSタイプのパッケージを削除                                                   |

|                  | μ PD78F9801を開発中から開発済みに変更                                                   |

| p.22             | 1.1 特徴のフラッシュ・メモリ書き込み時の動作周囲温度を変更                                            |

| p.28             | 1.7 機能概要にタイマの概要を追加                                                         |

| p.30, 32-34      | REGC端子,Vpp端子の端子処理を変更                                                       |

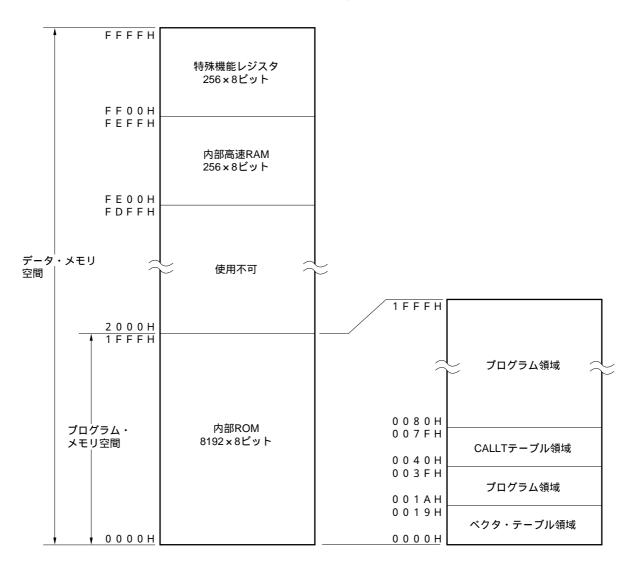

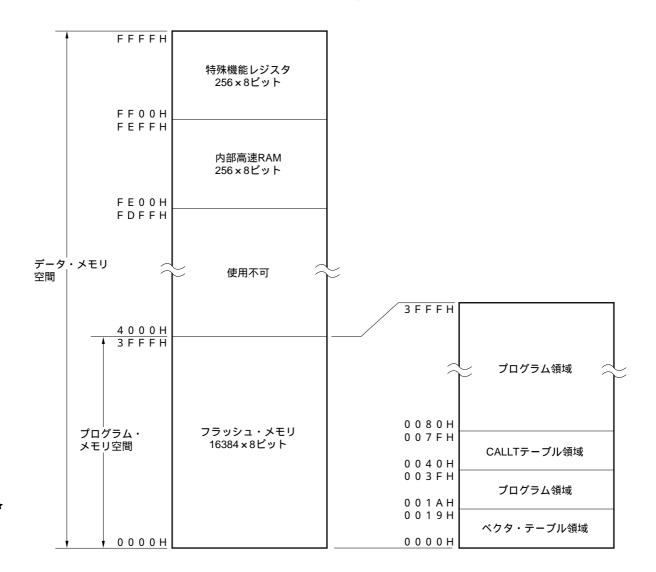

| p.36, 37         | 図3 - 1 メモリ・マップ (µPD789800), 図3 - 2 メモリ・マップ (µPD78F9801)のアド                 |

|                  | レス値を訂正                                                                     |

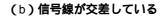

| p.76             | <b>図</b> 5 - 3 <b>システム・クロック発振回路</b> の外付け回路の <b>(</b> b <b>) 外部クロック</b> を変更 |

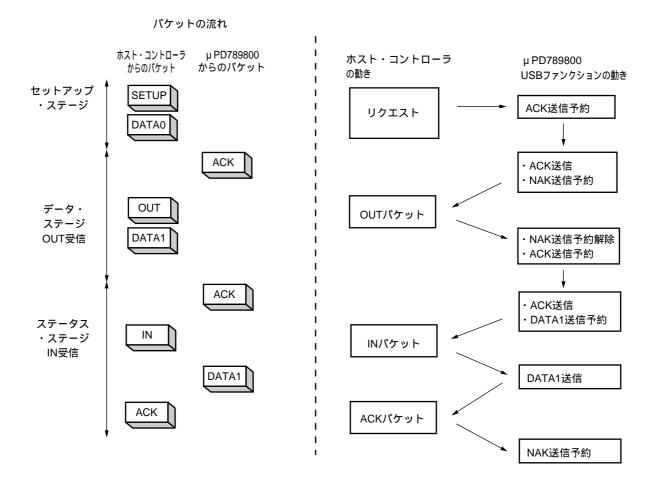

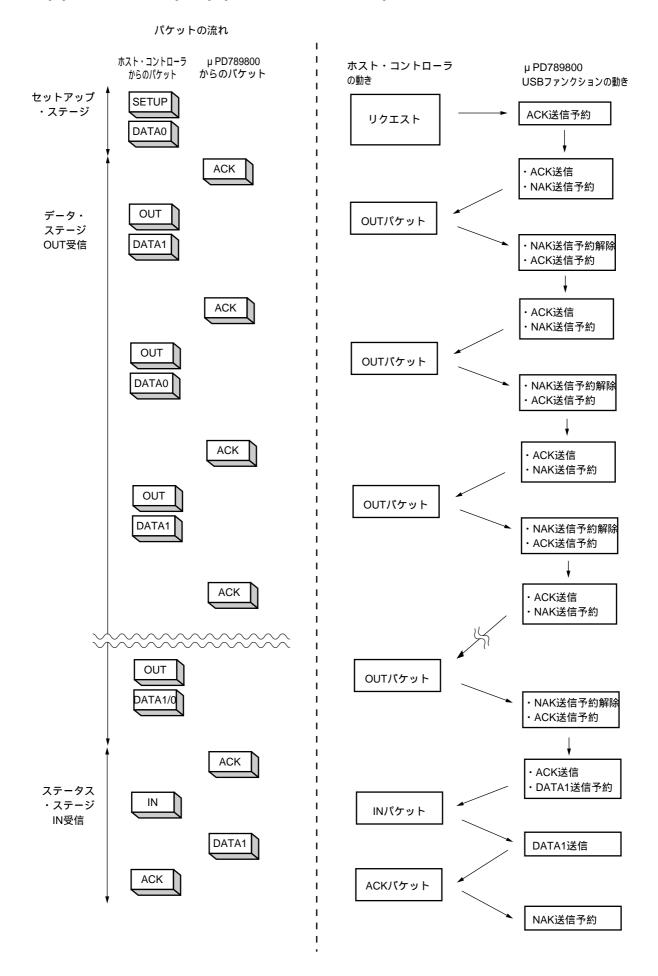

| p.100, 107, 109, | 第8章 USBファンクション                                                             |

| 111, 113-116,    | ・章構成を変更                                                                    |

| 118-122, 124,    | ・バッファ名称を受信トークン・バンク,受信データ・バンク,送信データ・バンク0, 1に表記                              |

| 129, 131, 132,   | 統一                                                                         |

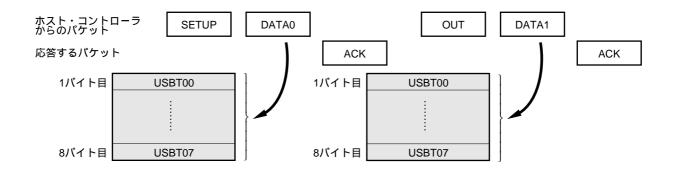

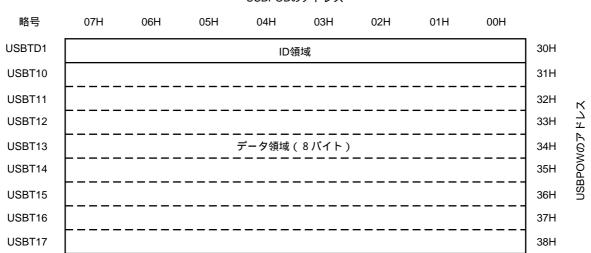

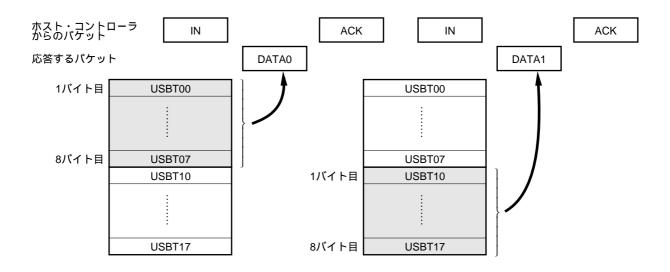

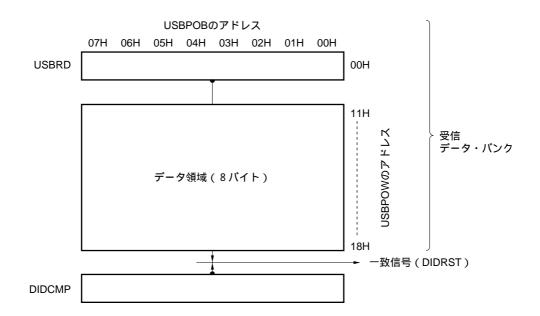

| 134, 135-144     | ・受信時と送信時のイメージ図を追加                                                          |

|                  | ・SETUP受信時のレジスタ値を追加                                                         |

|                  | ・データ・ハンドシェーク・パケット受信モード・レジスタ(URXMOD)の記述を変更                                  |

|                  | ・パケット受信ステータス・レジスタ(RXSTAT)の説明文を追加し,Read Onlyビットを変更                          |

|                  | ・トークン・パケット受信結果格納レジスタ(TRXRSL)の注釈文を追加                                        |

|                  | ・データ・パケット送信予約レジスタ(DTXRSV)に注意文を追加                                           |

|                  | ・ハンドシェーク・パケット送信予約レジスタ(HTXRSV)のビット1(DNAEN)の説明を変                             |

|                  | 更                                                                          |

|                  | ・表8 - 3 <b>送信予約の際の条件</b> のフラグ名誤記を訂正                                        |

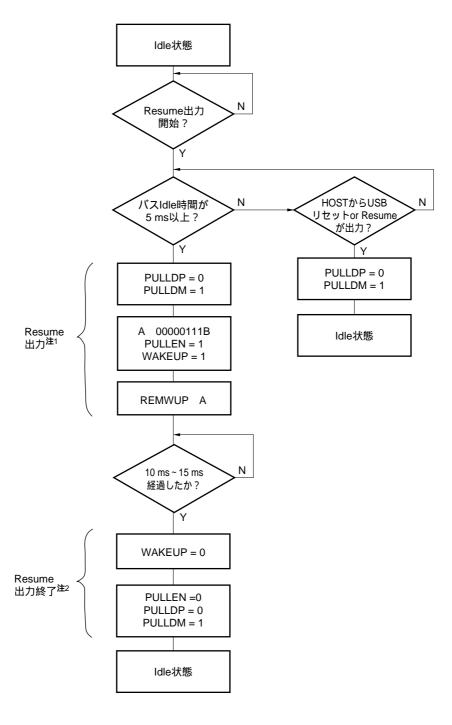

|                  | ・8. 5. 2 <b>リモート・ウエイク・アップ制御の動作</b> の内容を全面変更                                |

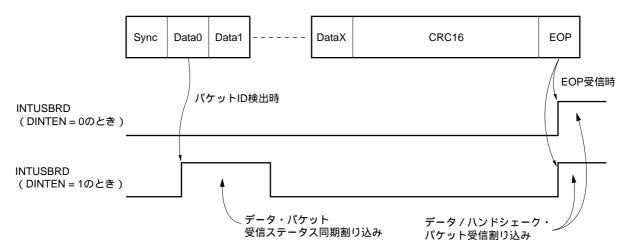

|                  | ・表8 - 4 USBファンクションからの割り込み要因一覧を追加                                           |

|                  | ・8.6 USB <b>ファンクションからの割り込み要求</b> でのフラグ名誤記を訂正                               |

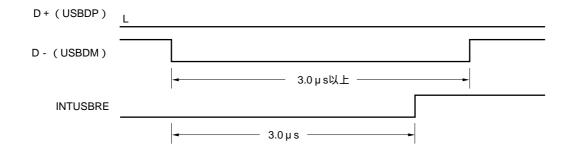

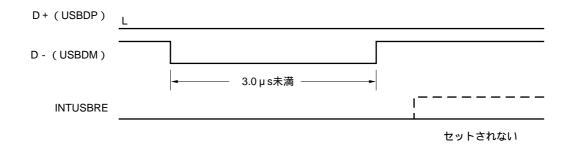

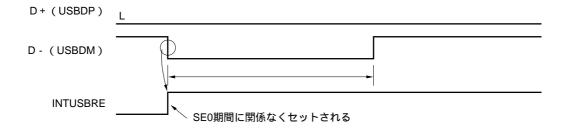

|                  | ・USBリセット / Resume検出割り込み(INTUSBRE)の説明文を追加                                   |

|                  | ・8.7 USB <b>ファンクションの制御</b> を追加                                             |

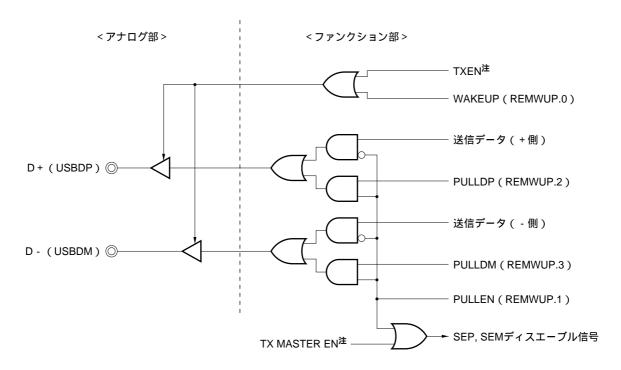

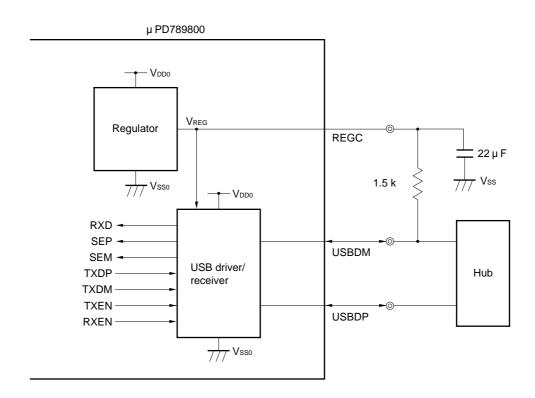

| p.167            | 図10 - 1 レギュレータ, USBドライバ/レシーバの構成図とその注意文を修正                                  |

| p.169            | 表11-1 割り込み要因一覧にウォッチドッグ・タイマ割り込みの備考文を追加                                      |

| p.172            | <b>図</b> 11 - 2 <b>割り込み要求フラグ・レジスタのフォーマット</b> に注意文を追加                       |

| p.190            | 12. 2. 2 STOP <b>モード</b> に (3) STOP <b>命令実行時の注意事項</b> を追加                  |

| p.196-204        | フラッシュ・メモリ・プログラミングに関する内容を , 14. 1 <b>フラッシュ・メモリの特徴</b> とし                    |

|                  | て全面改訂                                                                      |

| p.216-224        | <b>第</b> 16章 <b>電気的特性</b> を追加                                              |

| p.225            | <b>第</b> 17 <b>章 外形図</b> を追加                                               |

| p.226            | 第18章 半田付け推奨条件を追加                                                           |

| p.227-234        | <b>付録</b> A <b>開発ツール</b> の内容を全面改訂                                          |

|                  | 組み込み用ソフトウエアを削除,ターゲット・システム設計上の注意を追加                                         |

| p.240, 241       | <b>付録</b> C <b>改版履歴</b> に第3版での改版内容を追加                                      |

# 本版で改訂された主な箇所(2/2)

| 箇 所      | 内容                                                              |  |

|----------|-----------------------------------------------------------------|--|

|          | 修正版(U12978JJ3V1UD00)で改訂された主な箇所                                  |  |

| p.130    | p.130 <b>図</b> 8 - 21 <b>リモート・ウエイク・アップ制御の動作フロー・チャート</b> の注釈文を修正 |  |

|          | 修正版(U12978JJ3V3UD00)で改訂された主な箇所                                  |  |

| p.22, 23 | 第1章 概 説                                                         |  |

|          | ・鉛フリー製品を追加                                                      |  |

| p.226    | 第18章 半田付け推奨条件                                                   |  |

|          | ・表18 - 1 表面実装タイプの半田付け条件で,鉛フリー製品の半田付け条件を追加                       |  |

本文欄外の★印は,本版で改訂された主な箇所を示しています。

# はじめに

**対象者** このマニュアルはμ PD789800サブシリーズの機能を理解し,その応用システムや応用プログラムを設計,開発するユーザのエンジニアを対象としています。

対象製品は,次に示すサブシリーズの各製品です。

・ $\mu$  PD789800サブシリーズ:  $\mu$  PD789800, 78F9801

**目 的** このマニュアルは,次の構成に示す機能をユーザに理解していただくことを目的としています。

構 成  $\mu$  PD789800サブシリーズのマニュアルは,このマニュアルと命令編(78K/0Sシリーズ共通)の2冊に分かれています。

μ PD789800サブシリーズ ユーザーズ・マニュアル 78K/0Sシリーズ ユーザーズ・マニュアル 命令編

端子機能

割り込み

内部ブロック機能

その他の内蔵周辺機能

電気的特性

CPU機能 命令セット 命令の説明

読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコンピュータの一般知識を必要とします。

一通りの機能を理解しようとするとき

目次に従って読んでください。

レジスタ・フォーマットの見方

ビット番号を で囲んでいるものは、そのビット名称がアセンブラでは予約語に、Cコンパイラではsfrbit.hというヘッダ・ファイルで定義済みとなっているものです。

レジスタ名が分かっていてレジスタの詳細を確認するとき

付録B レジスタ索引を利用してください。

78K/0Sシリーズの命令機能の詳細を知りたいとき

別冊の78K/OS**シリーズ ユーザーズ・マニュアル 命令編(**U11047J**)**を参照してください。

$\mu$  PD789800サブシリーズの電気的特性が知りたいとき

第16章 電気的特性を参照してください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記 :  $\overline{\times \times}$  (端子,信号名称に上線)

注 : 本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数…××××または××××B

10進数...×××× 16進数...××××H

# **関連資料** 関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

### デバイスの関連資料

| 資料 名                        | 資料      | 番号      |

|-----------------------------|---------|---------|

|                             | 和文      | 英 文     |

| μPD789800サブシリーズ ユーザーズ・マニュアル | このマニュアル | U12978E |

| 78K/0Sシリーズ ユーザーズ・マニュアル 命令編  | U11047J | U11047E |

### 開発ツール (ソフトウエア) の資料 (ユーザーズ・マニュアル)

| 資 料 名                              |                               | 資料番号    |         |

|------------------------------------|-------------------------------|---------|---------|

|                                    |                               | 和文      | 英 文     |

| RA78KOS アセンブラ・パッケージ                | 操作編                           | U14876J | U14876E |

|                                    | 言語編                           | U14877J | U14877E |

|                                    | 構造化アセンブリ言語編                   | U11623J | U11623E |

| CC78K0S Cコンパイラ                     | 操作編                           | U14871J | U14871E |

|                                    | 言語編                           | U14872J | U14872E |

| SM78Kシリーズ システム・シミュレータ Ver.2.30以上   | 操作編(Windows <sup>®</sup> ベース) | U15373J | U15373E |

|                                    | 外部部品ユーザ・オープン・                 | U15802J | U15802E |

|                                    | インタフェース仕様編                    |         |         |

| ID78Kシリーズ 統合ディバッガ Ver.2.30以上       | 操作編(Windowsベース)               | U15185J | U15185E |

| プロジェクト・マネージャ Ver.3.12以上(Windowsベース | )                             | U14610J | U14610E |

### 開発ツール (ハードウエア) の資料 (ユーザーズ・マニュアル)

| 資料名                           | 資料      | 番号      |

|-------------------------------|---------|---------|

|                               | 和文      | 英 文     |

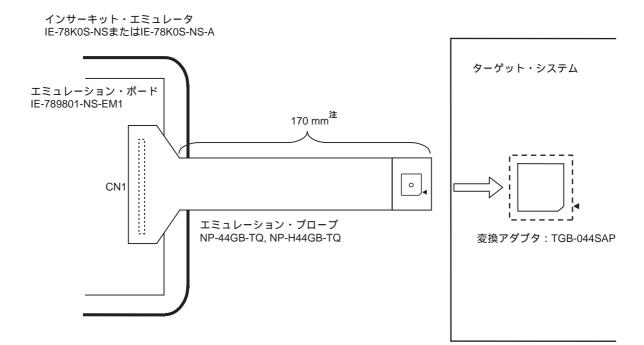

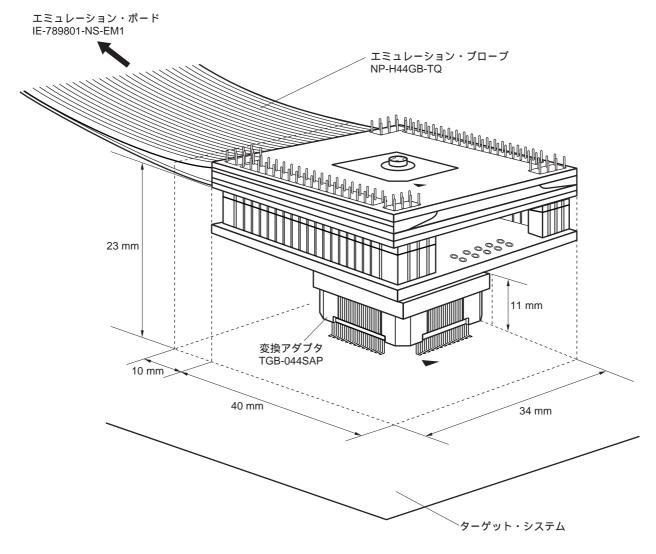

| IE-78KOS-NS インサーキット・エミュレータ    | U13549J | U13549E |

| IE-78K0S-NS-A インサーキット・エミュレータ  | U15207J | U15207E |

| IE-789801-NS-EM1 エミュレーション・ボード | U13390J | U13390E |

### フラッシュ・メモリ書き込み用の資料

| 資料名                                | 資料      | 番号      |

|------------------------------------|---------|---------|

|                                    | 和 文     | 英 文     |

| PG-FP3 フラッシュ・メモリ・プログラマ ユーザーズ・マニュアル | U13502J | U13502E |

| PG-FP4 フラッシュ・メモリ・プログラマ ユーザーズ・マニュアル | U15260J | U15260E |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

### その他の資料

| 資料 名                                                    | 資料番号    |         |

|---------------------------------------------------------|---------|---------|

|                                                         | 和 文     | 英 文     |

| SEMICONDUCTOR SELECTION GUIDE - Products and Packages - | X13769X |         |

| 半導体デバイス 実装マニュアル                                         | 注       |         |

| NEC半導体デバイスの品質水準                                         | C11531J | C11531E |

| NEC半導体デバイスの信頼性品質管理                                      | C10983J | C10983E |

| 静電気放電(ESD)破壊対策ガイド                                       | C11892J | C11892E |

| 半導体 品質 / 信頼性ハンドブック                                      | C12769J | -       |

| マイクロコンピュータ関連製品ガイド 社外メーカ編                                | U11416J | -       |

注 「半導体デバイス実装マニュアル」のホーム・ページ参照

和文:http://www.necel.com/pkg/ja/jissou/index.html 英文:http://www.necel.com/pkg/en/mount/index.html

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには,必ず最新の資料をご使用ください。

# 目 次

第1章 概 説 ... 22

1.1 特 徵 ... 22

| 1. 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>応用分野</b> 22                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 1. 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>オーダ情報</b> 22                                         |

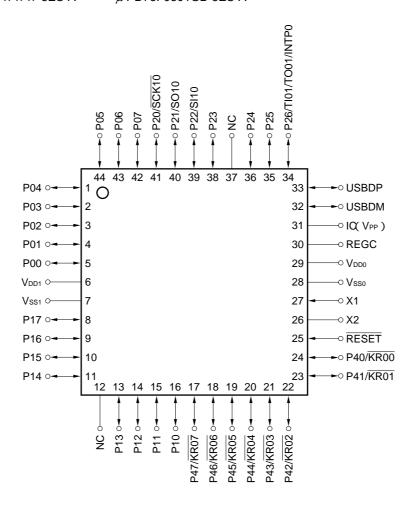

| 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>端子接続図(</b> Top View <b>)</b> 23                      |

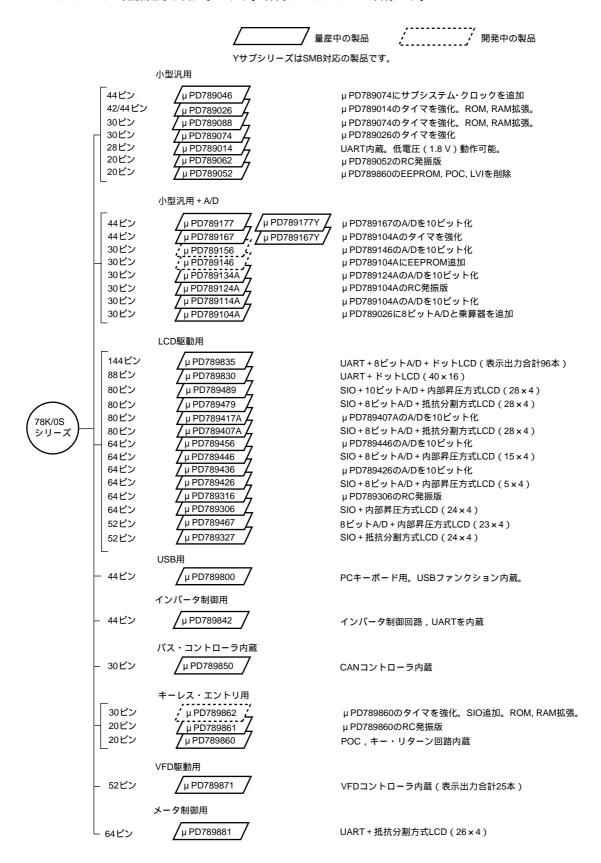

| 1. 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78K/0S <b>シリーズの展開</b> 24                                |

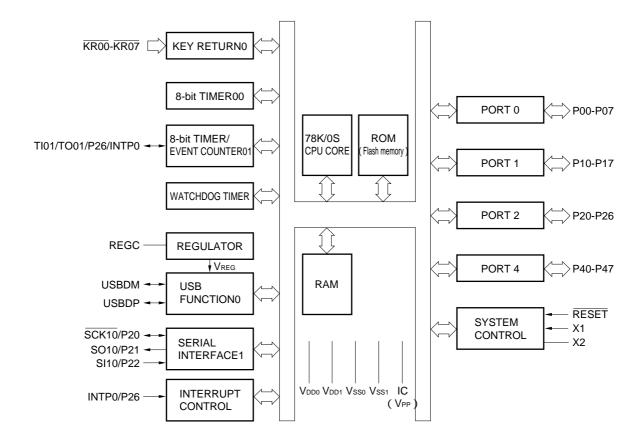

| 1. 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>プロック図</b> 27                                         |

| 1. 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 機能概要 28                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |

| 第2章                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>端子機能</b> 29                                          |

| 2. 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>端子機能一覧</b> 29                                        |

| 2. 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>端子機能の説明</b> 31                                       |

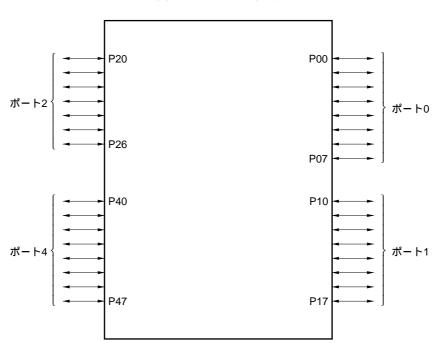

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2. 2. 1 P00-P07 (Port0) 31                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2. 2. 2 P10-P17 (Port1) 31                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2. 2. 3 P20-P26 ( Port2 ) 31                            |

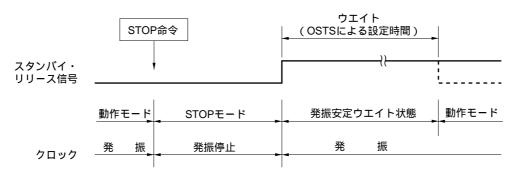

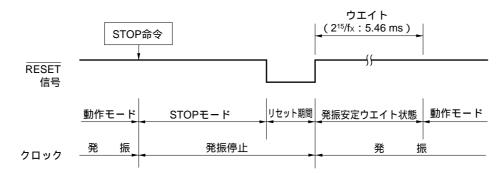

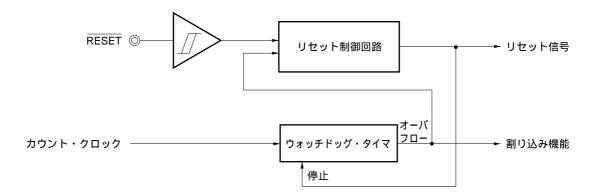

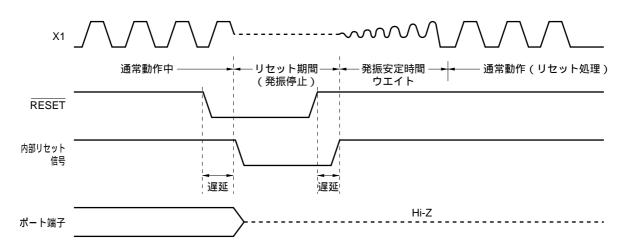

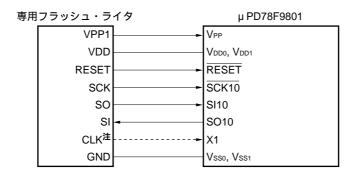

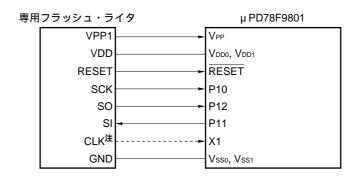

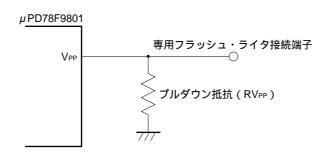

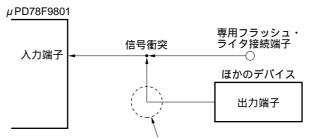

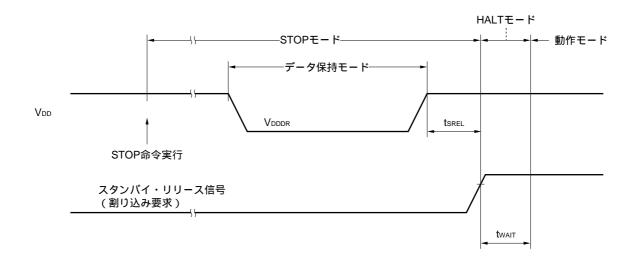

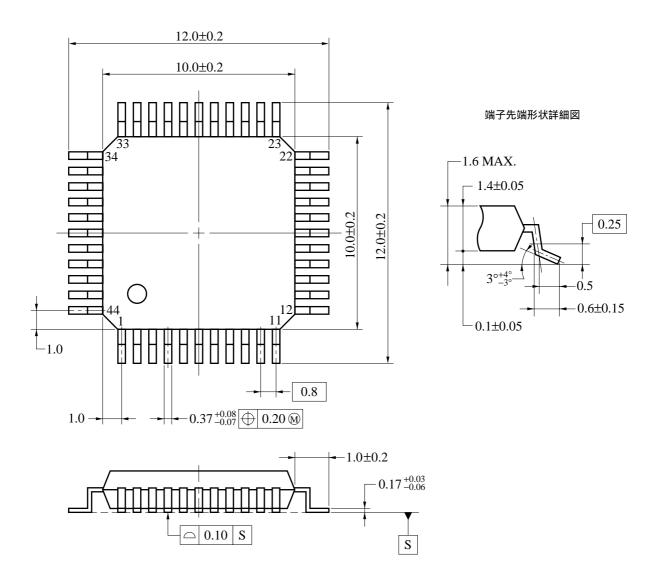

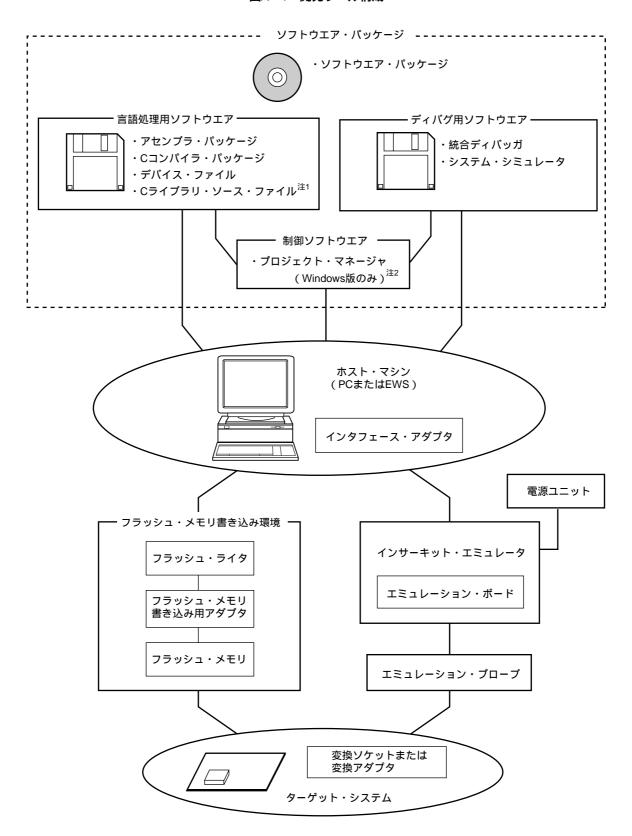

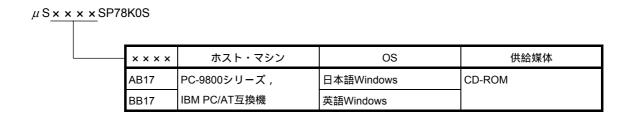

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2. 2. 4 P40-P47 (Port4) 32                              |