### カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、 詳細については必ず本文の内容をご確認ください。

# SH7144グループ、 SH7145グループ

ハードウェアマニュアル

ルネサス32ビットRISCマイクロコンピュータ SuperH<sup>™</sup> RISC engineファミリ/ SH7144シリーズ

| SH7144 | HD64F7144 |

|--------|-----------|

|        | HD6437144 |

|        | HD6417144 |

| SH7145 | HD64F7145 |

|        | HD6437145 |

|        | HD6417145 |

### 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例など全ての情報 の使用に起因する損害、第三者の知的財産権その他の権利に対する侵害に関し、弊社は責任を負い ません。

- 3. 本資料に記載の製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的、あるいはその他 軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替および外国貿易法」 その他輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 4. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例などの全ての情報は本資料発行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 5. 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに 起因する損害がお客様に生じた場合においても、弊社はその責任を負いません。

- 6. 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム 全体で十分に評価し、お客様の責任において適用可否を判断してください。弊社は、適用可否に 対する責任は負いません。

- 7. 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会ください。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 8. 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないでください。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1)生命維持装置。

- 2)人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行うもの。

- 4)その他、直接人命に影響を与えるもの。

- 9. 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件 およびその他諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品 をご使用された場合の故障および事故につきましては、弊社はその責任を負いません。

- 10.弊社は製品の品質および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が 発生したり、使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作 が生じた場合も人身事故、火災事故、社会的損害などを生じさせないよう、お客様の責任において 冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウェアおよびソフトウェ ア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システム としての安全検証をお願いいたします。

- 11.本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故につきましては、弊社はその責任を負いません。

- 12.本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固くお断りいたします。

- 13.本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業窓口までご照会ください。

### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

### 2. 電源投入時の処置

【注意】電源投入時は,製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザープアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

### 4. クロックについて

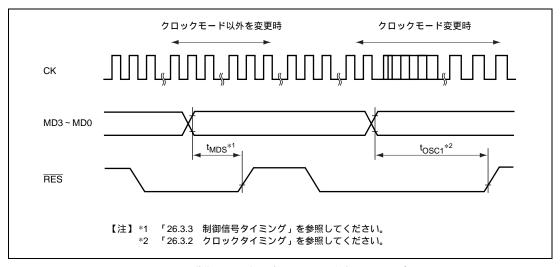

【注意】リセット時は、クロックが安定した後、リセットを解除してください。 プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

### 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品ご使用上の注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 目次

- 5. 概要

- 6. 各機能モジュールの説明

- ・CPU およびシステム制御系

- ・内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュールごとに異なりますが、一般的には、 特長、 入出力端子、 レジスタの説明、 動作説明、 使用上の注意事項、 等の節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認の上設計してください。 各章の本文中には説明に対する注意事項と、各章の最後には使用上の注意事項があります。 必ずお読みください。(使用上の注意事項は必要により記載されます。)

- 7. レジスター覧

- 8. 電気的特性

- 9. 付録

- 製品型名、外形寸法など

- 本版で改訂された箇所(改訂版のみ適用)

改定来歴は、前版の記載内容について訂正・追加された主な箇所についてまとめたものです。 改定内容のすべてについて記載したものではありませんので、詳細については、本書の本文上 でご確認ください。

10. 索引

### はじめに

SH7144 シリーズは、ルネサス テクノロジオリジナルの RISC 方式の CPU をコアにして、システム構成に必要な周辺機能を集積したシングルチップ RISC マイコンです。

- 対象者 このマニュアルは、SH7144シリーズを用いた応用システムを設計するユーザを対象としています。 このマニュアルを使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する 基本的な知識を必要とします。

- 目的 このマニュアルは、SH7144 シリーズのハードウエア機能と電気的特性をユーザに理解していただくことを目的にしています。

なお、実行命令の詳細については、「SH-1/SH-2/SH-DSP ソフトウェアマニュアル」に記載しておりますので、あわせてご覧ください。

### 読み方

- 対象製品と製品略称の表記について。

- → 本書では、下記の製品について説明をします。

| 製品分類と製品略称 |           | 基本製品型名  |                         |           |

|-----------|-----------|---------|-------------------------|-----------|

| 基         | 本分類       |         | 内蔵 ROM 分類               |           |

| SH7144    | (112 ピン版) | SH7144F | フラッシュメモリ版(ROM 容量 256KB) | HD64F7144 |

|           |           | SH7144M | マスク ROM 版(ROM 容量 256KB) | HD6437144 |

|           |           |         | ROM レス版                 | HD6417144 |

| SH7145    | (144 ピン版) | SH7145F | フラッシュメモリ版(ROM 容量 256KB) | HD64F7145 |

|           |           | SH7145M | マスク ROM 版(ROM 容量 256KB) | HD6437145 |

|           |           |         | ROM レス版                 | HD6417145 |

本書では、製品区分のために製品略称を使用しています。たとえば、112 ピン版製品を、基本分類略称の SH7144 で示し、144 ピン版製品は略称の SH7145 で示します。これらは、それぞれ内蔵 ROM によりフラッシュメモリ版とマスク ROM 版、および ROM レス版があります。フラッシュメモリ版を限定して示す場合、略称の後に Fを付け、SH7144F のように表記することがあります。マスク ROM 版、および ROM レス版を限定して示す場合は、略称の後に M を付け、SH7144M のように表記することがあります。

#### • 代表品種

→ 本書では、HD64F7144を代表品種として説明しています。したがって、本書を HD6437144、HD6417144、HD64F7145、HD6437145、HD6417145のマニュアルとして使用する場合は、相違点の指示がない場合は、そのまま HD6437144、HD64F7144、HD64F7145、HD6437145、HD6417145と置き換えてご使用ください。

相違点の指示がある場合は、指示の品種に適用される仕様としてご使用ください。

- 機能全体を理解しようとするとき。

- → 目次に従って読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

- CPU機能の詳細を理解したいとき。

- → 別冊の「SH-1/SH-2/SH-DSP ソフトウェアマニュアル」を参照してください。

- レジスタ名がわかっていて、詳細機能を知りたいとき。

- → 本書の後ろに、「索引」があります。索引からページ番号を検索してください。 「第25章 レジスタ一覧」にアドレス、ビット内容、初期化についてまとめています。

凡例 レジスタ表記 :シリアルコミュニケーションなど、同一または類似した機能が複数チャネルに存在す

る場合に、次の表記を使用します。

XXX\_N (XXX は基本レジスタ名称、N はチャネル番号)

ビット表記: 左側が上位ビット、右側が下位ビットの順に表記します。

数字の表記 : 2 進数は B'xxxx、16 進数は H'xxxx、10 進数は xxxx

信号の表記:ローアクティブの信号にはオーバーバーを付けます。xxxx

関連資料一覧 ウェブ・サイトに最新資料を掲載しています。ご入手の資料が最新版であるかを確認してください。 (http://www.renesas.com/)

• SH7144シリーズに関するユーザーズマニュアル

| 資料名                                 | 資料番号       |

|-------------------------------------|------------|

| SH7144 グループ、SH7145 グループ ハードウエアマニュアル | 本マニュアル     |

| SH-1/SH-2/SH-DSP ソフトウェアマニュアル        | RJJ09B0228 |

### • 開発ツール関連ユーザーズマニュアル

| 資料名                                           | 資料番号            |

|-----------------------------------------------|-----------------|

| C/C++ コンパイラ、アセンブラ、最適化リンケージエディタユーザーズマニュアル      | RJJ10J1885      |

| シミュレータ・デバッガ(Windows 版)ユーザーズマニュアル              | ADJ - 702 - 353 |

| High-performance Embedded Workshop ユーザーズマニュアル | RJJ10J2060      |

### アプリケーションノート

| 資料名          | 資料番号       |

|--------------|------------|

| C/C++ コンパイラ編 | RJJ05B0557 |

## 目次

|     | In The Control of the |      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.  | 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-1  |

| 1.1 | 特長                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-1  |

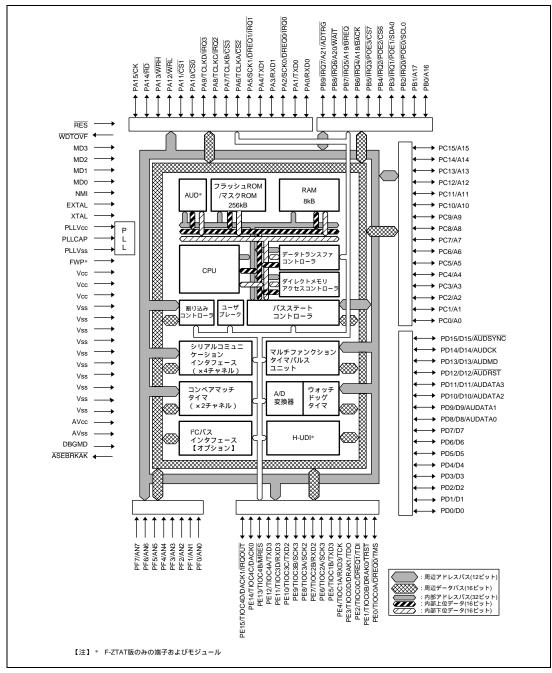

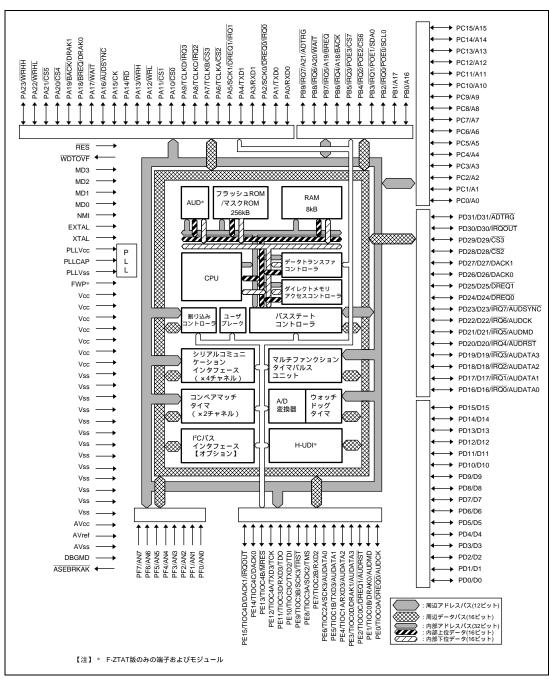

| 1.2 | 内部プロック図                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-3  |

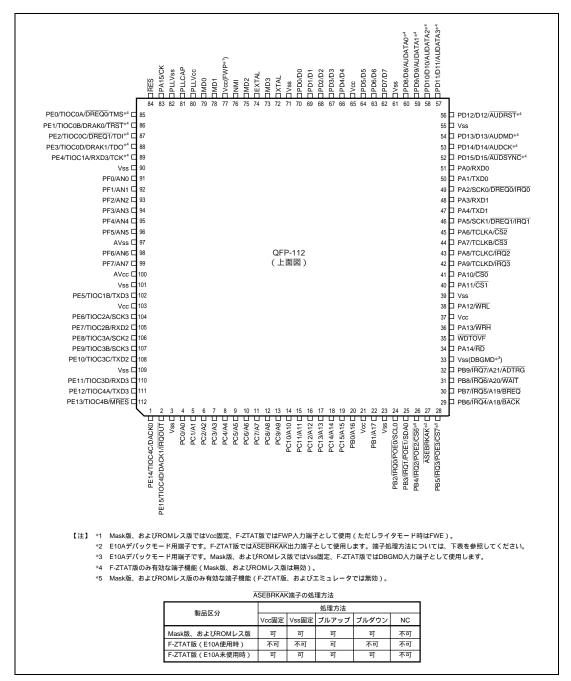

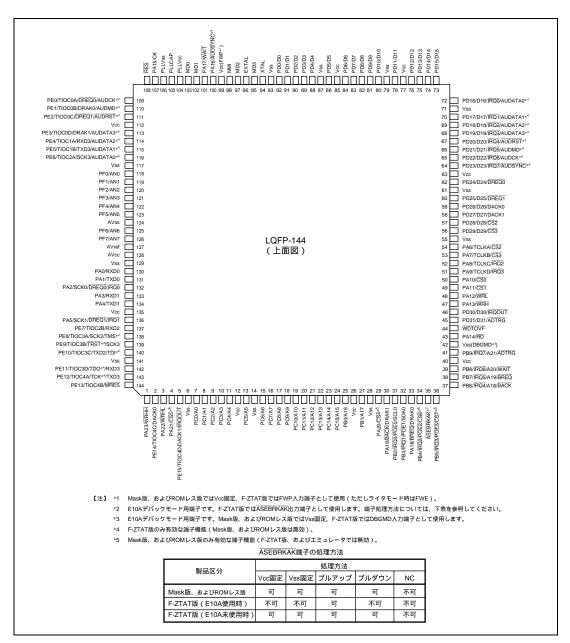

| 1.3 | ピン配置図                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-5  |

| 1.4 | 端子機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-7  |

| 2.  | CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-1  |

| 2.1 | 特長                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-1  |

| 2.2 | レジスタの構成                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1  |

| 2.2 | 2.1 汎用レジスタ (Rn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-3  |

| 2.2 | 2.2 コントロールレジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-3  |

| 2.2 | 2.3 システムレジスタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-4  |

| 2.2 | 2.4 レジスタの初期値                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-4  |

| 2.3 | データ形式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-4  |

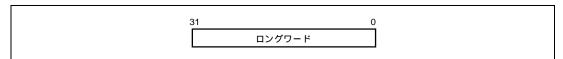

| 2.3 | 3.1 レジスタのデータ形式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-4  |

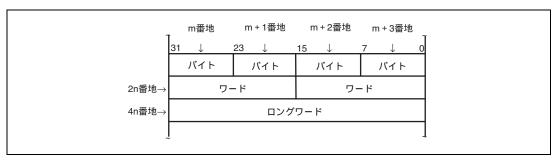

| 2.3 | 3.2 メモリ上でのデータ形式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-5  |

| 2.3 | 3.3 イミディエイトデータのデータ形式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-5  |

| 2.4 | 命令の特長                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-6  |

| 2.4 | 4.1 RISC 方式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-6  |

| 2.4 | 4.2 アドレッシングモード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-9  |

| 2.4 | 4.3 命令形式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-12 |

| 2.5 | 命令セット                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-15 |

| 2.5 | 5.1 分類順命令セット                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-15 |

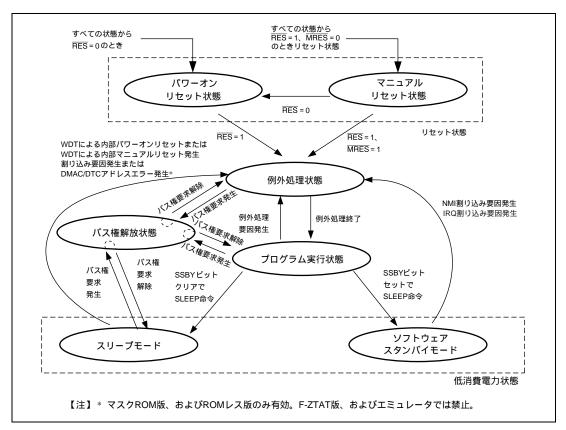

| 2.6 | 処理状態                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-25 |

| 2.0 | 6.1 状態遷移                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-25 |

| 3.  | MCU 動作モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-1  |

| 3.1 | 動作モードの選択                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-1  |

| 3.2 | 入出力端子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-2  |

| 3.3 | 各動作モードの説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-2  |

| 3.3 | 3.1 モード 0 (MCU 拡張モード 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-2  |

| 3.3 | 3.2 モード 1 (MCU 拡張モード 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-2  |

| 3.3 | 3.3 モード 2 (MCU 拡張モード 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-2  |

| 3.3 | 3.4 モード3(シングルチップモード)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-2  |

| 3.3.        | .5 クロックモード       | 3-3  |

|-------------|------------------|------|

| 3.4         | アドレスマップ          | 3-3  |

| 3.5         | 本LSIの初期状態        | 3-4  |

| 3.6         | 動作モード変更時の注意事項    | 3-4  |

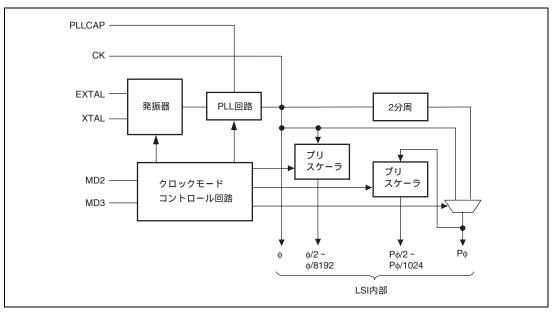

| 4. <i>1</i> | クロック発振器          | 4-1  |

| 4.1         | 発振器              | 4-2  |

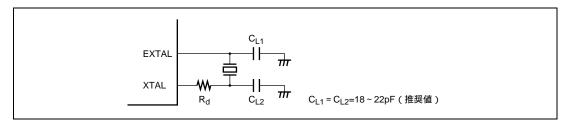

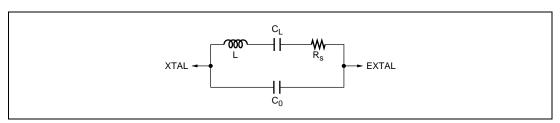

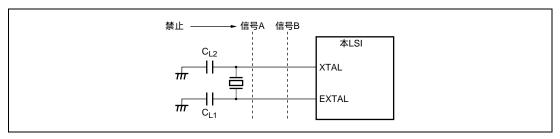

| 4.1.        | .1 水晶発振子を接続する方法  | 4-2  |

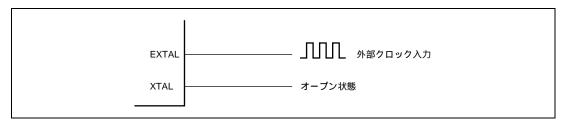

| 4.1.        | .2 外部クロックを入力する方法 | 4-3  |

| 4.2         | 発振停止検出機能         | 4-3  |

| 4.3         | 使用上の注意事項         | 4-4  |

| 4.3.        | .1 発振子に関する注意事項   | 4-4  |

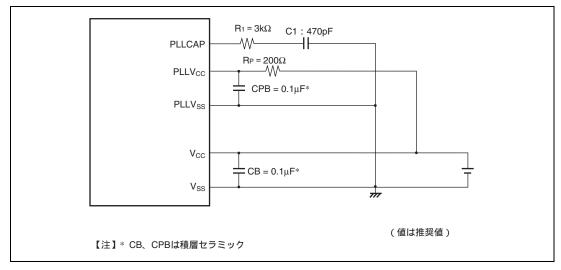

| 4.3.        | .2 ボード設計上の注意     | 4-4  |

| 5. ß        | 列外処理             | 5-1  |

| 5.1         | 概要               |      |

| 5.1.        |                  |      |

| 5.1.        |                  |      |

| 5.1.        |                  |      |

| 5.2         | リセット             |      |

| 5.2.        | リセットの種類          | 5-4  |

| 5.2.        | .2 パワーオンリセット     | 5-4  |

| 5.2.        | .3 マニュアルリセット     | 5-5  |

| 5.3         | アドレスエラー          | 5-6  |

| 5.3.        | .1 アドレスエラー発生要因   | 5-6  |

| 5.3.        | .2 アドレスエラー例外処理   | 5-6  |

| 5.4         | 割り込み             | 5-7  |

| 5.4.        | .1 割り込み要因        | 5-7  |

| 5.4.        | .2 割り込み優先順位      | 5-7  |

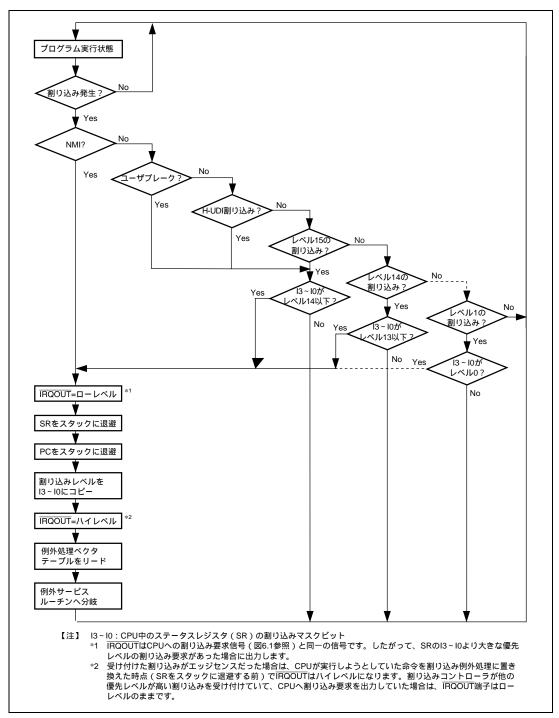

| 5.4.        | .3 割り込み例外処理      | 5-8  |