# RZ/N1D グループ、 RZ/N1S グループ、 RZ/N1L グループ

ユーザーズマニュアル アーキテクチャ・製品データ編

RZ ファミリ RZ/N シリーズ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。回路、ソフトウェアおよびこれらに関連する情報を使用する場合、お客様の責任において、お客様の機器・システムを設計ください。これらの使用に起因して生じた損害(お客様または第三者いずれに生じた損害も含みます。以下同じです。)に関し、当社は、一切その責任を負いません。

- 2. 当社製品または本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、 著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行うものではなく、また責任を負うものではありません。

- 3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を組み込んだ製品の輸出入、製造、販売、利用、配布その他の行為を行うにあたり、第三者保有の技術の利用に関するライセンスが必要となる場合、当該ライセンス取得の判断および取得はお客様の責任において行ってください。

- 5. 当社製品を、全部または一部を問わず、改造、改変、複製、リバースエンジニアリング、その他、不適切に使用しないでください。かかる改造、改変、 複製、リバースエンジニアリング等により生じた損害に関し、当社は、一切その責任を負いません。

- 6. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通制御(信号)、大規模通信機器、金融端末基幹システム、各種安全制御装置等当社製品は、データシート等により高信頼性、Harsh environment 向け製品と定義しているものを除き、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(宇宙機器と、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等)に使用されることを意図しておらず、これらの用途に使用することは想定していません。たとえ、当社が想定していない用途に当社製品を使用したことにより損害が生じても、当社は一切その責任を負いません。

- 7. あらゆる半導体製品は、外部攻撃からの安全性を 100%保証されているわけではありません。当社ハードウェア/ソフトウェア製品にはセキュリティ対策が組み込まれているものもありますが、これによって、当社は、セキュリティ脆弱性または侵害(当社製品または当社製品が使用されているシステムに対する不正アクセス・不正使用を含みますが、これに限りません。)から生じる責任を負うものではありません。当社は、当社製品または当社製品が使用されたあらゆるシステムが、不正な改変、攻撃、ウイルス、干渉、ハッキング、データの破壊または窃盗その他の不正な侵入行為(「脆弱性問題」といいます。)によって影響を受けないことを保証しません。当社は、脆弱性問題に起因しまたはこれに関連して生じた損害について、一切責任を負いません。また、法令において認められる限りにおいて、本資料および当社ハードウェア/ソフトウェア製品について、商品性および特定目的との合致に関する保証ならびに第三者の権利を侵害しないことの保証を含め、明示または黙示のいかなる保証も行いません。

- 8. 当社製品をご使用の際は、最新の製品情報(データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等)をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は、データシート等において高信頼性、Harsh environment 向け製品と定義しているものを除き、耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 10. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。当社製品および 技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定 めるところに従い必要な手続きを行ってください。

- 12. お客様が当社製品を第三者に転売等される場合には、事前に当該第三者に対して、本ご注意書き記載の諸条件を通知する責任を負うものといたします。

- 13. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 14. 本資料に記載されている内容または当社製品についてご不明な点がございましたら、当社の営業担当者までお問合せください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社が直接的、間接的に支配する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

(Rev.5.0-1 2020.10)

#### 本社所在地

〒135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

www.renesas.com

#### 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の 商標です。すべての商標および登録商標は、それぞれの所有者に帰属し ます。

#### お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄の営業お問合せ窓口に関する情報などは、弊社ウェブサイトをご覧ください。

www.renesas.com/contact/

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本ドキュメントおよびテクニカル アップデートを参照してください。

#### 1. 静電気対策

CMOS 製品の取り扱いの際は静電気防止を心がけてください。CMOS 製品は強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジンケース、導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、CMOS 製品を実装したボードについても同様の扱いをしてください。

#### 2. 電源投入時の処置

電源投入時は、製品の状態は不定です。電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

#### 3 電源オフ時における入力信号

当該製品の電源がオフ状態のときに、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、 誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源オフ時における入力信号」についての記載のある製品は、その内容を守ってください。

#### 4. 未使用端子の処理

未使用端子は、「未使用端子の処理」に従って処理してください。CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて調動作を起こす恐れがあります。

#### 5. クロックについて

リセット時は、クロックが安定した後、リセットを解除してください。プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 6. 入力端子の印加波形

入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。CMOS 製品の入力がノイズなどに起因して、 $V_L$  (Max.) から  $V_H$  (Min.) までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定の場合はもちろん、 $V_L$  (Max.) から  $V_H$  (Min.) までの領域を通過する遷移期間中にチャタリングノイズなどが入らないように使用してください。

#### 7. リザーブアドレス(予約領域)のアクセス禁止

リザーブアドレス (予約領域) のアクセスを禁止します。アドレス領域には、将来の拡張機能用に割り付けられている リザーブアドレス (予約領域) があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 8. 製品間の相違について

型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。同じグループのマイコンでも型名が違うと、フラッシュメモリ、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ幅射量などが異なる場合があります。 型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

## このマニュアルの使い方

#### 1. 目的と対象者

このマニュアルは、本マイコンのハードウェア機能と電気的特性をユーザに理解していただくためのマニュアルです。本マイコンを用いた応用システムを設計するユーザを対象にしています。このマニュアルを使用するには、電気回路、論理回路、マイクロコンピュータに関する基本的な知識が必要です。

このマニュアルは、大きく分類すると、製品の概要、CPU、システム制御機能、周辺機能、電気的特性、使用上の注意で構成されています。

本マイコンは、注意事項を十分確認の上、使用してください。注意事項は、各章の本文中、各章の最後、注意事項の章に記載しています。

改訂記録は旧版の記載内容に対して訂正または追加した主な箇所をまとめたものです。改訂内容すべてを記録したものではありません。詳細は、このマニュアルの本文でご確認ください。

RZ/N1 グループでは次のドキュメントを用意しています。

#### ■ RZ/N1 関連ドキュメント一覧

| ドキュメント名                                                                 | 資料番号                             |

|-------------------------------------------------------------------------|----------------------------------|

| RZ/N1D グループ、RZ/N1S グループ、RZ/N1L グループ データシート                              | R01DS0323JJ****                  |

| RZ/N1D グループ、RZ/N1S グループ、RZ/N1L グループ ユーザーズマニュアル<br>アーキテクチャ・製品データ編        | R01UH0750JJ****                  |

| RZ/N1D グループ、RZ/N1S グループ、RZ/N1L グループ ユーザーズマニュアル<br>システム・周辺機能 1 編         | R01UH0751JJ****<br>(本ユーザーズマニュアル) |

| RZ/N1D グループ、RZ/N1S グループ、RZ/N1L グループ ユーザーズマニュアル<br>周辺機能 2 編              | R01UH0752JJ****                  |

| RZ/N1D グループ、RZ/N1S グループ、RZ/N1L グループ ユーザーズマニュアル<br>R-IN Engine・イーサネット機能編 | R01UH0753JJ****                  |

| RZ/N1D グループ、RZ/N1S グループ、RZ/N1L グループ ユーザーズマニュアル<br>PWMTimer              | R01UH0913JJ****                  |

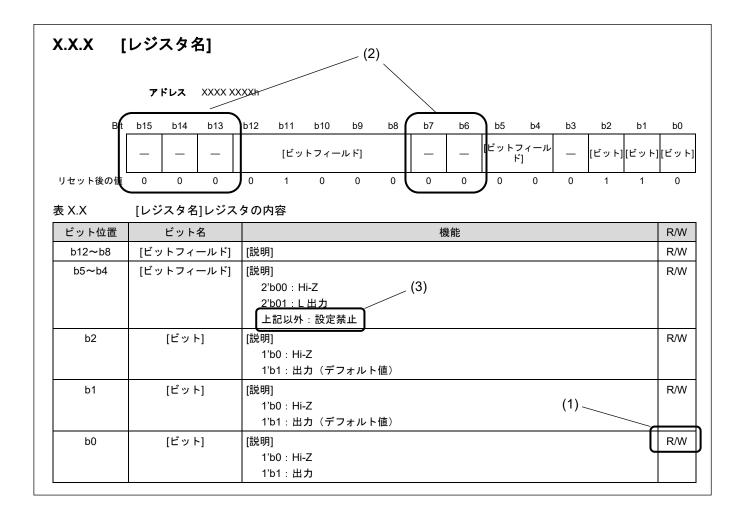

#### 2. レジスタの表記

各章において「レジスタの説明」には、ビットの並びを示すビット配置図とビットに設定する内容を説明するビット機能表があります。使用する記号、用語を以下に説明します。

(1) R/W : 読み出し/書き込みとも有効です。

R/(W) : 読み出し/書き込みとも有効ですが、書き込みには制限があります。

制限の内容については、各レジスタの説明や注記を参照ください。

R: 読み出しのみ有効です。書き込みは無効になります。

W: 書き込みのみ有効です。読み出した値は保証されません。

(2) 予約ビットです。書き込みを行う場合には、指定された値を書き込んでください。指定以外の値を書き込んだ場合の動作は保証されません。

(3) 設定禁止。設定した場合の動作は保証されません。

## 3. 略語および略称の説明

| 略語/略称 フルスペル |                                             |  |

|-------------|---------------------------------------------|--|

| AHB         | Arm Advanced High-performance Bus           |  |

| APB         | Arm Advanced Peripheral Bus                 |  |

| AXI         | Arm Advanced eXtensible Interface           |  |

| bps         | bits per second                             |  |

| CA7         | Arm Cortex-A7 module                        |  |

| CM3         | Arm Cortex-M3 module                        |  |

| CRC         | Cyclic Redundancy Check                     |  |

| DMA         | Direct Memory Access                        |  |

| DMAC        | Direct Memory Access Controller             |  |

| Hi-Z        | High Impedance                              |  |

| HSR         | High-availability Seamless Redundancy       |  |

| HW-RTOS     | Hard Ware Real Time OS                      |  |

| I/O         | Input/Output                                |  |

| INTC        | Interrupt Controller                        |  |

| LSB         | Least Significant Bit                       |  |

| MSB         | Most Significant Bit                        |  |

| NC          | Non-Connect                                 |  |

| NoC         | Network-on-Chip                             |  |

| PLL         | Phase Locked Loop                           |  |

| PWM         | Pulse Width Modulation                      |  |

| UART        | Universal Asynchronous Receiver/Transmitter |  |

| OTP         | One Time Programmable                       |  |

| PTP         | Precision Time Protocol                     |  |

| PRP         | Parallel Redundancy Protocol                |  |

| SoC         | System On Chip                              |  |

## 4. アクセスサイズの表記

アクセスサイズ:

8 ビット=バイト

16 ビット=ハーフワード

32 ビット=ワード

Arm は Arm Limited(またはその子会社)の EU およびその他地域における登録商標です。 全ての商標・登録商標は各所有者の財産です。

## 目 次

| 第1草 | 全体構造                 | 14 |

|-----|----------------------|----|

| 1.1 | デバイス概要               | 14 |

| 1.2 | 仕様の概要                | 15 |

| 1.3 | 製品ファミリ/パッケージ別機能比較    | 23 |

| 1.4 | 製品一覧                 | 24 |

| 1.5 | ブロック図                |    |

| 第2章 | アドレス空間               | 28 |

| 2.1 | メモリマップ               |    |

|     | .1.1 RZ/N1D          |    |

|     | .1.2 RZ/N1S          |    |

| 2   | .1.3 RZ/N1L          | 32 |

| 2.2 | レジスタマップサマリ           | 33 |

| 第3章 | クロック生成               | 35 |

| 3.1 | 概要                   | 35 |

| 3.2 | クロックゲーティング           | 37 |

| 3.3 | クロック選択               | 37 |

| 3.4 | クロック分周               |    |

| 3.5 | クロック周波数変更            |    |

| 3.6 | クロックオシレータ接続          |    |

|     | .6.1 メインクロックオシレータ    |    |

|     | 3.6.1.1 水晶発振子        |    |

|     | 3.6.1.2 外部クロック入力     |    |

| 3   | .6.2 RTC クロックオシレータ   |    |

|     | 3.6.2.2 RTC を使用しない場合 |    |

| 第4章 | リセット                 | 44 |

| 4.1 | 概要                   | 44 |

| 4.2 | チップレベルリセット           | 45 |

| 4   | .2.1 マスタリセット         | 45 |

| 4   | .2.2 システムリセット        | 45 |

| 4   | .2.3 JTAG リセット       | 45 |

| 4.3 | モジュールリセット            | 46 |

| 第5章 | IO マルチプレキシング         | 47 |

| 5.1 | 概要                   | 47 |

| 5.2 | レジスタマップ              | 50 |

| 5.3 | レジスタ説明               | 51 |

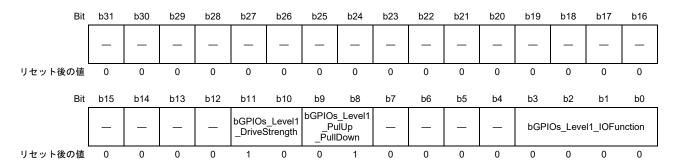

|        | 5.3.1  | rGPIOs_Level1_ConfigA_[n] — GPIO[n] RGMII マルチプレキシング Level1    |    |

|--------|--------|---------------------------------------------------------------|----|

|        |        | コンフィグレーションレジスタ(n=0~59)                                        | 51 |

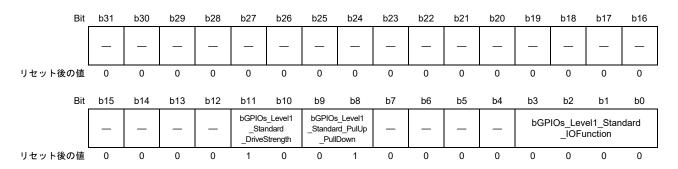

|        | 5.3.2  | rGPIOs_Level1_ConfigB_[n] – GPIO[n] Standard マルチプレキシング Level1 |    |

|        |        | コンフィグレーションレジスタ(n=60~169(最大))                                  | 52 |

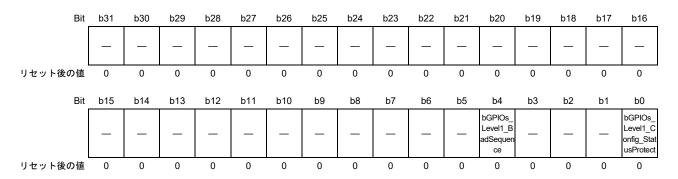

|        | 5.3.3  | rGPIOs_Level1_StatusProtect — GPIO マルチプレキシング Level1 ステータスおよび  |    |

|        |        | プロテクトレジスタ                                                     | 53 |

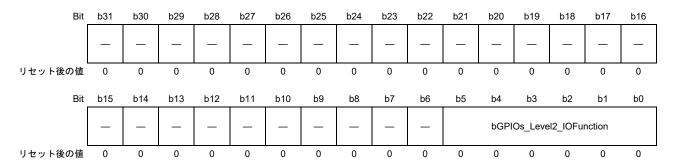

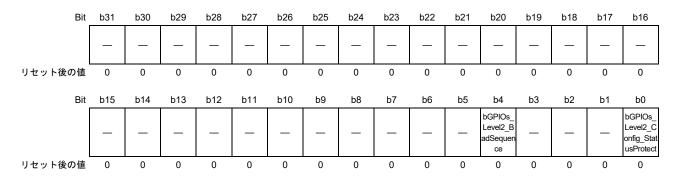

|        | 5.3.4  | rGPIOs_Level2_Config_[n]ーGPIO[n]マルチプレキシング Level2              |    |

|        |        | コンフィグレーションレジスタ(n=0~169(最大))                                   | 54 |

|        | 5.3.5  | rGPIOs_Level2_StatusProtect — GPIO マルチプレキシング Level2 ステータスおよび  |    |

|        |        | プロテクトレジスタ                                                     | 55 |

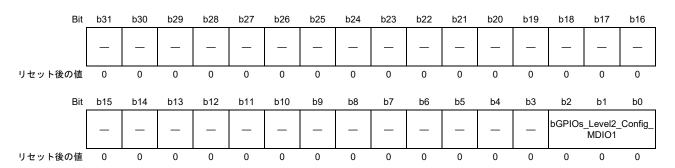

|        | 5.3.6  | rGPIOs_Level2_Config_MDIO1 ― MDIO1 インタフェースコンフィグレーション          |    |

|        |        | レジスタ                                                          | 56 |

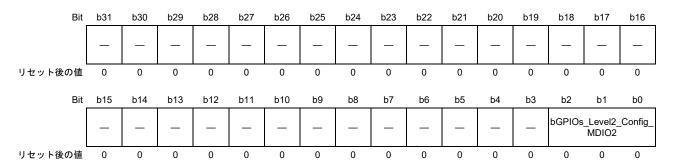

|        | 5.3.7  | rGPIOs_Level2_Config_MDIO2 ー MDIO2 インタフェースコンフィグレーション          |    |

|        |        | レジスタ                                                          | 57 |

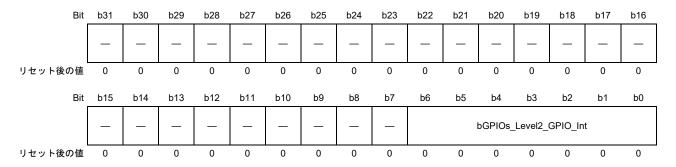

|        | 5.3.8  | rGPIOs_Level2_GPIO_Int_[n] – GPIO_Int[n]割り込みコンフィグレーションレジスタ    |    |

|        |        | (n=0~7)                                                       | 58 |

| 5.4    | 動作詞    | 设定                                                            | 59 |

|        | 5.4.1  | GPIOs Level1 コンフィグレーションレジスタのプロテクトアクセス                         | 59 |

|        | 5.4.2  | GPIOs Level2 コンフィグレーションレジスタのプロテクトアクセス                         | 60 |

|        | 5.4.3  | GPIO 割り込みラインのコンフィグレーション                                       | 61 |

| ## 0 # | ±      | 7 = / - >   u                                                 | 00 |

| 第 6 章  | -      | ステムコントロール                                                     |    |

| 6.1    |        |                                                               |    |

| 6.2    | レジ     | スタマップ                                                         | 62 |

| 6.3    | レジ     | スタ説明                                                          | 66 |

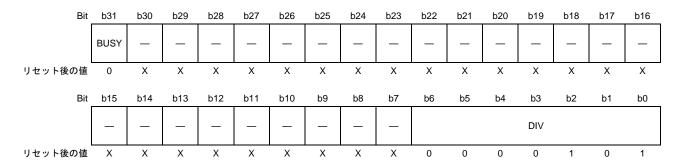

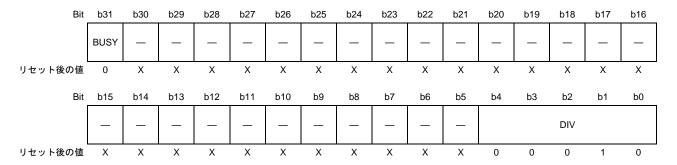

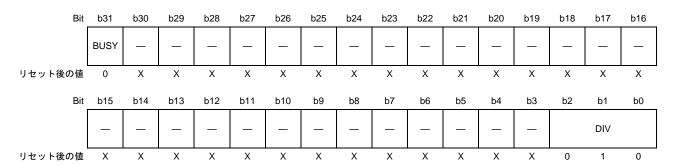

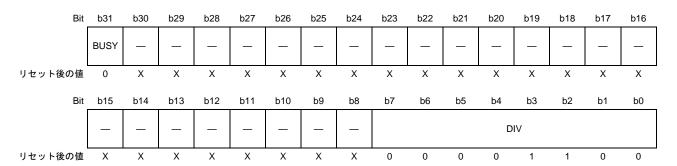

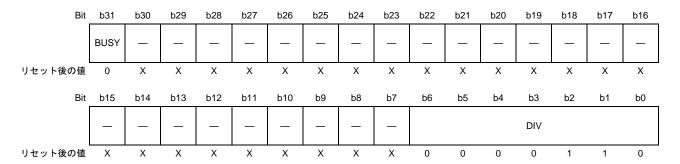

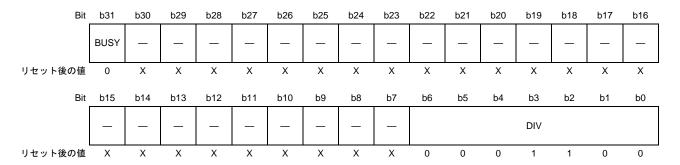

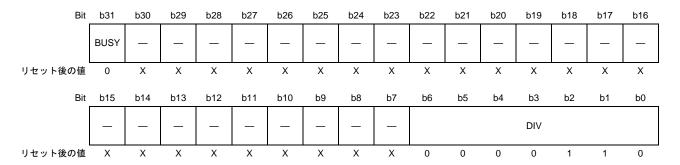

|        | 6.3.1  | PWRCTRL_SWITCHDIV — A5PSW のクロック分周器コントロール                      | 66 |

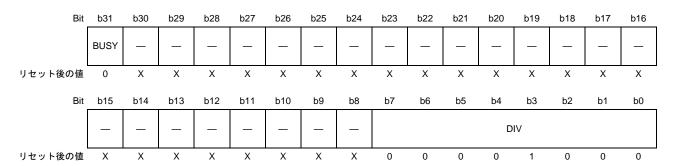

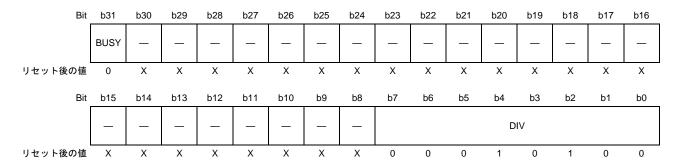

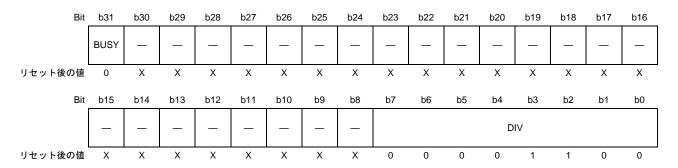

|        | 6.3.2  | PWRCTRL_OPPDIV — OPP モードのクロック分周器コントロール                        | 67 |

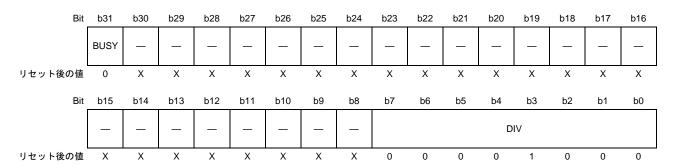

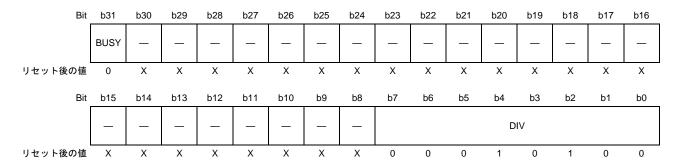

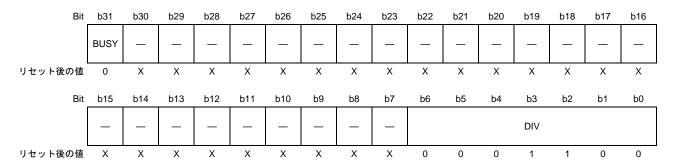

|        | 6.3.3  | PWRCTRL_CA7DIV — CA7 のクロック分周器コントロール                           | 68 |

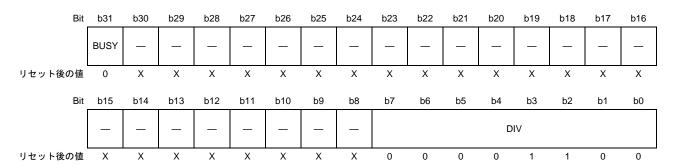

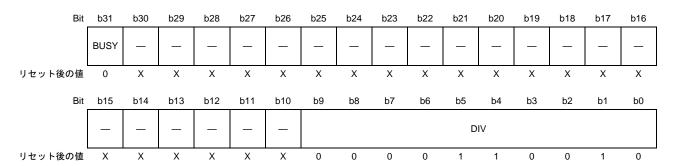

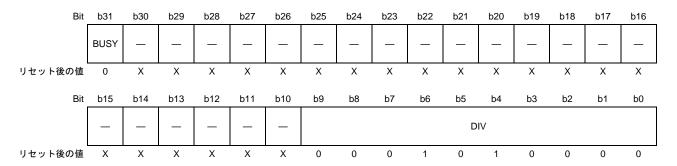

|        | 6.3.4  | PWRCTRL_PG1_PR2DIV — PG1 Program2 のクロック分周器コントロール              | 69 |

|        | 6.3.5  | PWRCTRL_PG1_PR3DIV — PG1 Program3 のクロック分周器コントロール              | 70 |

|        | 6.3.6  | PWRCTRL_PG1_PR4DIV — PG1 Program4 のクロック分周器コントロール              | 71 |

|        | 6.3.7  | PWRCTRL_PG4_PR1DIV — PG4 Program1 のクロック分周器コントロール              | 72 |

|        | 6.3.8  | PWRCTRL_QSPI1DIV — QSPI1 のクロック分周器コントロール                       | 73 |

|        | 6.3.9  | PWRCTRL_SDIO1DIV — SDIO1 のクロック分周器コントロール                       | 74 |

|        | 6.3.10 | PWRCTRL_SDIO2DIV — SDIO2 のクロック分周器コントロール                       | 75 |

|        | 6.3.11 | PWRCTRL_PG0_ADCDIV — PG0 ADC のクロック分周器コントロール                   | 76 |

|        | 6.3.12 | PWRCTRL_PG0_I2CDIV — PG0 I2C のクロック分周器コントロール                   | 77 |

|        | 6.3.13 | PWRCTRL_PG0_UARTDIV — PG0 UART のクロック分周器コントロール                 | 78 |

|        | 6.3.14 | PWRCTRL_NFLASHDIV — NAND FLASH Controller のクロック分周器コントロール      | 79 |

|        | 6.3.15 | PWRCTRL_HWRTOS_MDCDIV — HW-RTOS GMAC の MDC Clock のクロック分周器     | ÷  |

|        |        | コントロール                                                        | 80 |

|        | 6.3.16 | PWRCTRL_QSPI2DIV — QSPI2 のクロック分周器コントロール                       | 81 |

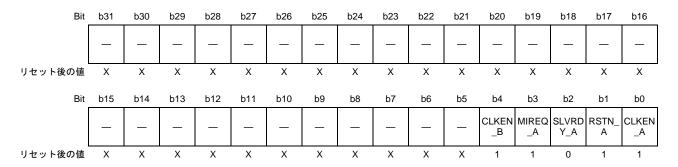

|        | 6.3.17 | PWRCTRL SDIO1 – SDIO1 のパワーマネージメントコントロール                       | 82 |

| 6.3.18 | PWRSTAT_SDIO1 – SDIO1 のパワーマネージメントステータス                  | 83   |

|--------|---------------------------------------------------------|------|

| 6.3.19 | SYSSTAT – システムステータスフラグレジスタ                              | 84   |

| 6.3.20 | PWRCTRL_USB - USB2.0 のパワーマネージメントコントロール                  | 85   |

| 6.3.21 | PWRSTAT_USB – USB2.0 のパワーマネージメントステータス                   | 86   |

| 6.3.22 | PWRCTRL_MSEBI — MSEBI のパワーマネージメントコントロール                 | 87   |

| 6.3.23 | PWRSTAT_MSEBI — MSEBI のパワーマネージメントステータス                  | 88   |

| 6.3.24 | PWRCTRL_PG0_0 - PG0 のパワーマネージメントコントロール#0                 | 89   |

| 6.3.25 | PWRSTAT_PG0 - PG0 のパワーマネージメントステータス                      | 91   |

| 6.3.26 | PWRCTRL_PG0_1 - PG0 のパワーマネージメントコントロール#1                 | 92   |

| 6.3.27 | PWRCTRL_PG1_1 – PG1 のパワーマネージメントコントロール#1                 | 93   |

| 6.3.28 | PWRCTRL_PG1_2 – PG1 のパワーマネージメントコントロール#2                 | 95   |

| 6.3.29 | PWRCTRL_DMA - DMAC1 と DMAC2 のパワーマネージメントコントロール           | 96   |

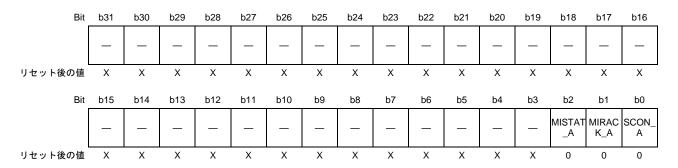

| 6.3.30 | PWRCTRL_NFLASH – NAND FLASH Controller のパワーマネージメント      |      |

|        | コントロール                                                  |      |

| 6.3.31 | PWRCTRL_QSPI1 — QSPI1 のパワーマネージメントコントロール                 |      |

| 6.3.32 | PWRSTAT_DMA - DMAC1 と DMAC2 のパワーマネージメントステータス            | 99   |

| 6.3.33 | PWRSTAT_NFLASH - NAND FLASH Controller のパワーマネージメントステータス | .100 |

| 6.3.34 | PWRSTAT_QSPI1 - QSPI1 のパワーマネージメントステータス                  | .101 |

| 6.3.35 | PWRCTRL_DDRC - DDR Memory Controller のパワーマネージメントコントロール  | .102 |

| 6.3.36 | PWRCTRL_EETH — 外部 Ethernet クロックのパワーマネージメントコントロール        | .103 |

| 6.3.37 | PWRCTRL_MAC1 – GMAC1 のパワーマネージメントコントロール                  | .104 |

| 6.3.38 | PWRCTRL_MAC2 – GMAC2 のパワーマネージメントコントロール                  | .105 |

| 6.3.39 | PWRSTAT_DDRC - DDR Memory Controller のパワーマネージメントステータス   | .106 |

| 6.3.40 | PWRSTAT_MAC1 – GMAC1 のパワーマネージメントステータス                   | .107 |

| 6.3.41 | PWRSTAT_MAC2 – GMAC2 のパワーマネージメントステータス                   |      |

| 6.3.42 | PWRCTRL_ECAT — ETHERCAT のパワーマネージメントコントロール               | .109 |

| 6.3.43 | PWRCTRL_SERCOS - SERCOSIII のパワーマネージメントコントロール            | .110 |

| 6.3.44 | PWRSTAT_ECAT — ETHERCAT のパワーマネージメントステータス                | .111 |

| 6.3.45 | PWRSTAT_SERCOS - SERCOSIII のパワーマネージメントステータス             | .112 |

| 6.3.46 | PWRCTRL_HSR – HSR のパワーマネージメントコントロール                     | .113 |

| 6.3.47 | PWRCTRL_QSPI2 – QSPI2 のパワーマネージメントコントロール                 | .114 |

| 6.3.48 | PWRSTAT_HSR – HSR のパワーマネージメントステータス                      | .115 |

| 6.3.49 | PWRSTAT_QSPI2 - QSPI2 のパワーマネージメントステータス                  | .116 |

| 6.3.50 | PWRSTAT_SWITCH – A5PSW のパワーマネージメントステータス                 | .117 |

| 6.3.51 | RSTSTAT – リセットステータスレジスタ                                 | .118 |

| 6.3.52 | USBSTAT — USBPLL のステータス情報                               | .119 |

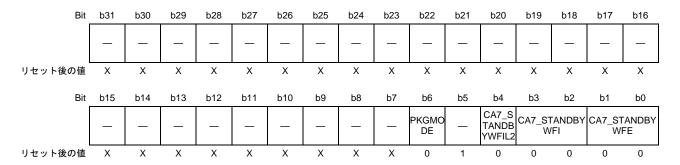

| 6.3.53 | PWRCTRL_SDIO2 – SDIO2 のパワーマネージメントコントロール                 | .120 |

| 6.3.54 | PWRSTAT_SDIO2 – SDIO2 のパワーマネージメントステータス                  | .121 |

| 6.3.55 | PWRCTRL_PG2_25MHZ — PG2 25MHz のパワーマネージメントコントロール         | .122 |

| 6.3.56 | PWRCTRL_PG1_PR2 - PG1 Program2 のパワーマネージメントコントロール        | .123 |

| 6.3.57 | PWRCTRL_PG3_48MHZ - PG3 48MHz のパワーマネージメントコントロール         | .125 |

| 6.3.58 | PWRCTRL_PG4 – PG4 のパワーマネージメントコントロール                     | .126 |

| 6.3.59 | PWRCTRL_PG1_PR3 - PG1 Program3 のパワーマネージメントコントロール        | .127 |

| 6.3. | .60 PWRCTRL_PG1_PR4 — PG1 Program4 のパワーマネージメントコントロール   | 128 |  |

|------|--------------------------------------------------------|-----|--|

| 6.3. |                                                        |     |  |

| 6.3. | .62 RSTEN — リセットイネーブルレジスタ                              | 130 |  |

| 6.3. | .63 PWRCTRL_SWITCH — A5PSW のパワーマネージメントコントロール           | 131 |  |

| 6.3. | .64 PWRCTRL_RTC – RTC のパワーマネージメントコントロール                | 132 |  |

| 6.3. | .65 PWRSTAT_RTC – RTC のパワーマネージメントステータス                 | 133 |  |

| 6.3. | .66 PWRCTRL_ROM — ROM のパワーマネージメントコントロール                | 134 |  |

| 6.3. | .67 PWRSTAT_PG1 – PG1 のパワーマネージメントステータス                 | 135 |  |

| 6.3. | .68 PWRSTAT_PG2_25MHZ — PG2 25MHz のパワーマネージメントステータス     | 137 |  |

| 6.3. | .69 PWRSTAT_PG3_48MHZ – PG3 48MHz のパワーマネージメントステータス     | 138 |  |

| 6.3. | .70 PWRSTAT_PG4 – PG4 のパワーマネージメントステータス                 | 139 |  |

| 6.3. | .71 PWRSTAT_ROM – ROM のパワーマネージメントステータス                 | 140 |  |

| 6.3. | .72 PWRCTRL_CM3 — CM3 のパワーマネージメントコントロール                | 141 |  |

| 6.3. | .73 PWRSTAT_CM3 – CM3 のパワーマネージメントステータス                 | 142 |  |

| 6.3. | .74 PWRSTAT_RINCTRL – R-IN Engine アクセサリレジスタのパワーマネージメント |     |  |

|      | ステータス                                                  | 143 |  |

| 6.3. | .75 PWRSTAT_SWITCHCTRL — イーサネットアクセサリレジスタの              |     |  |

|      | パワーマネージメントステータス                                        | 144 |  |

| 6.3. | .76  PWRCTRL_RINCTRL — R-IN Engine アクセサリレジスタの          |     |  |

|      | パワーマネージメントコントロール                                       | 145 |  |

| 6.3. | .77 PWRCTRL_SWITCHCTRL — イーサネットアクセサリレジスタの              |     |  |

|      | パワーマネージメントコントロール                                       | 146 |  |

| 6.3. | .78 PWRCTRL_HWRTOS — HW-RTOS のパワーマネージメントコントロール         | 147 |  |

| 6.3. | .79 RSTCTRL — リセットコントロールレジスタ                           | 148 |  |

| 6.3. | .80 CFG_USB — USB モードコンフィグレーションレジスタ                    | 149 |  |

| 6.3. | .81 OPMODE – システムとブートのコンフィグレーションレジスタ                   | 150 |  |

| 6.3. | .82 CFG_SDIO[m] — SDIO[m]コンフィグレーションレジスタ(m=1 もしくは 2)    | 151 |  |

| 6.3. | .83 DBGCON — デバッグコントロールレジスタ                            | 152 |  |

| 6.3. | .84 CFG_GPIOT_PTEN_xx — GPIO トリガイネーブルレジスタ              | 153 |  |

| 6.3. | .85 CFG_GPIOT_TSRC — GPIO トリガソースセレクトレジスタ               | 154 |  |

| 6.3. | .86 CFG_DMAMUX — DMAC1 と DMAC2 のマルチプレクサレジスタ            | 155 |  |

| 6.3. | .87 VERSION — プロダクトバージョンレジスタ                           | 158 |  |

| 6.3. | .88 BOOTADDR – Cortex-A7 プロセッサ 1 ブートアドレスコンフィグレーション     |     |  |

|      | レジスタ                                                   | 158 |  |

|      |                                                        |     |  |

| 第7章  | 動作モード                                                  | 159 |  |

| 7.1  | 概要                                                     | 159 |  |

| 7.2  | ブートモード仕様(RZ/N1D および RZ/N1S)                            | 160 |  |

| 7.2. | .1 共通の特徴                                               | 160 |  |

| 7.2. | .2 QSPI ブートの特徴                                         | 160 |  |

| 7.2. | .3 NAND ブートの特徴                                         | 161 |  |

| 7.2. | .4 USB ブートの特徴                                          | 162 |  |

| 7.3  | 標準のブートシーケンス                                            | 163 |  |

| 7.3.1    | 概要                                 | 163 |

|----------|------------------------------------|-----|

| 7.3.2    | 外部端子によるコンフィグレーション                  | 163 |

| 7.3.3    | CPU ブート                            | 164 |

| 7.3.4    | RZ/N1D および RZ/N1S のブート             | 165 |

| 7.3.5    | RZ/N1L のブート                        | 165 |

| 7.4 SP   | PKG フォーマット(RZ/N1D および RZ/N1S)      | 166 |

| 7.4.1    | 概要                                 | 166 |

| 7.4.2    | 実装の詳細                              | 166 |

| 7.5 RZ   | /N1 初期化シーケンス                       | 169 |

| 7.5.1    | 標準の初期化シーケンス                        | 169 |

| 7.5.2    | USBPLL の設定                         | 169 |

| 7.5.3    | Cortex-M3 の活性化                     | 169 |

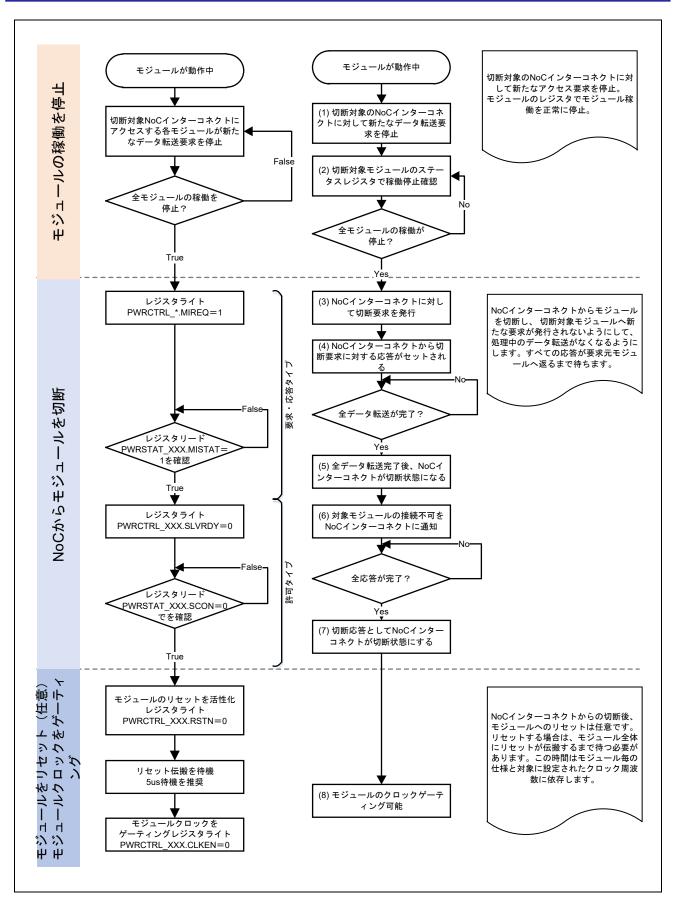

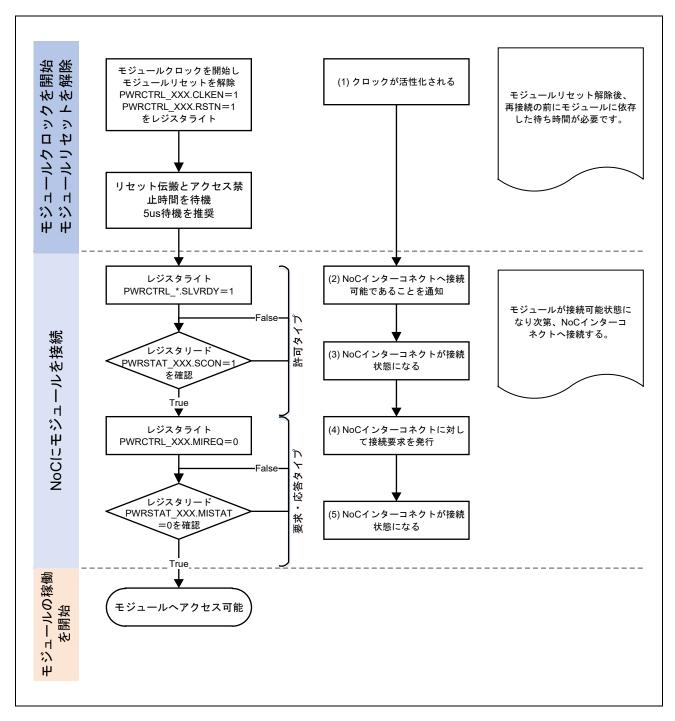

| 7.5.4    | 一般的な NoC のプログラミングシーケンス             | 170 |

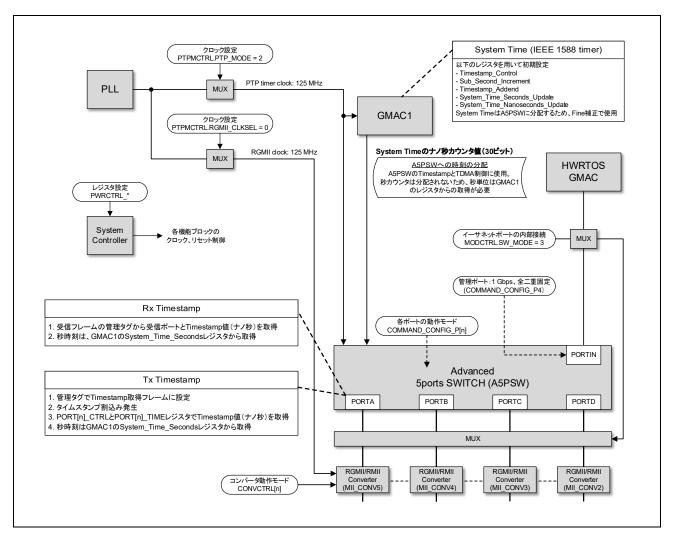

| 第8章 E    | Ethernet インタフェースモード                | 175 |

| 8.1 概    | 要                                  | 175 |

| 8.2 サ7   | ポートするモード                           | 177 |

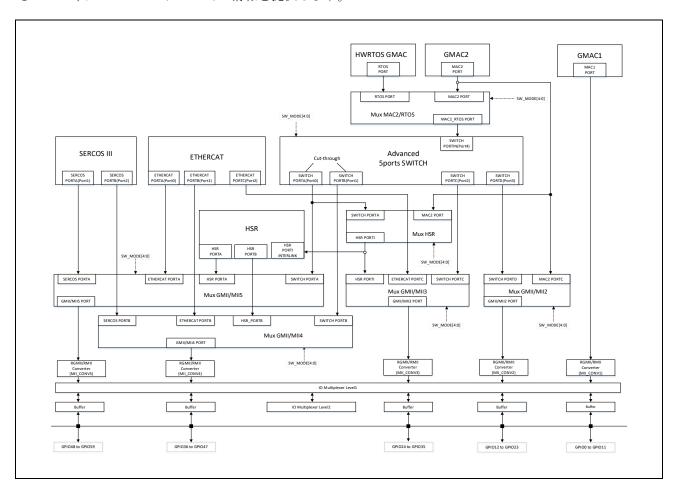

| 8.2.1    | イーサネットポートの内部接続                     | 181 |

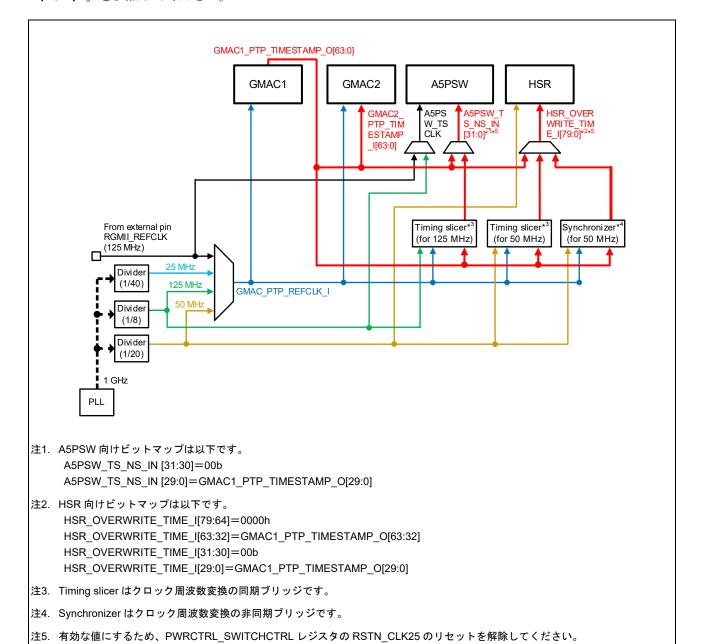

| 8.2.2    | PTP 用クロックの選択                       | 182 |

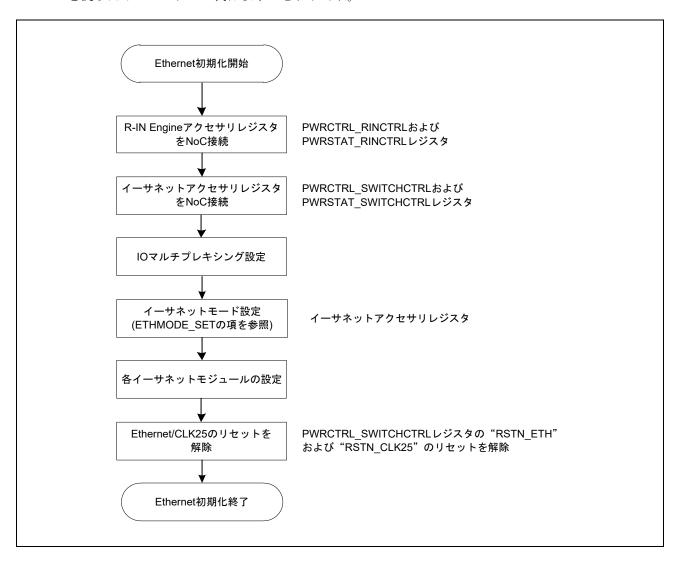

| 8.3 操作   | 作手順                                | 185 |

| 8.3.1    | 初期化                                | 185 |

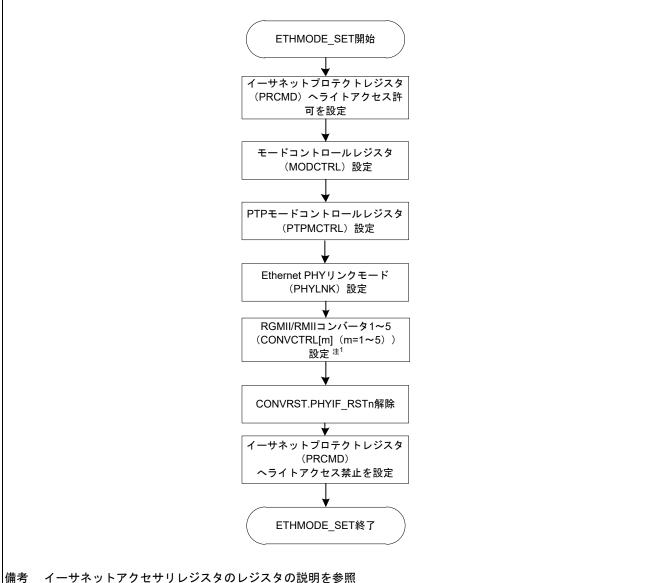

| 8.3.2    | ETHMODE_SET                        | 186 |

| 8.4 使月   | 用上の注意事項                            | 187 |

| 8.4.1    | 制限                                 | 187 |

| 8        | 3.4.1.1 サポートされる Ethernet 信号        | 187 |

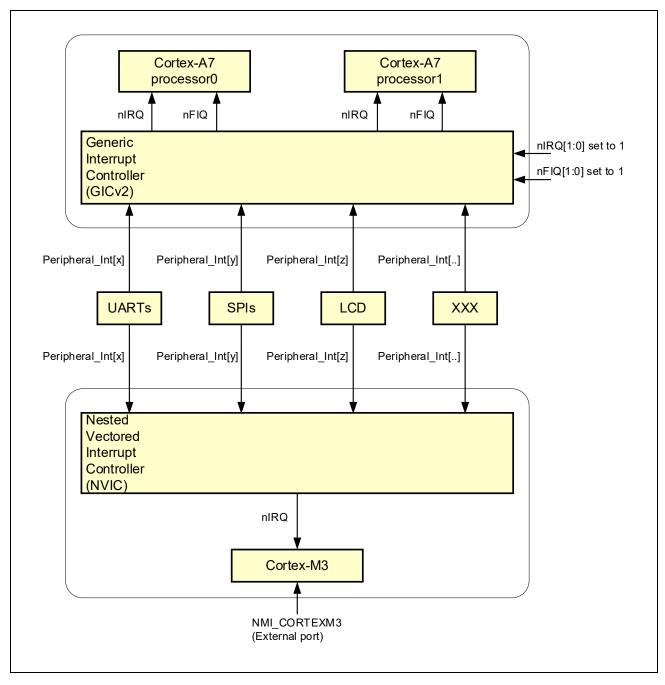

| 第9章 害    | 剽り込み                               | 188 |

| 9.1 概要   | 要                                  | 188 |

| 9.1.1    | Cortex-A7 GICv2                    | 188 |

| 9.1.2    | Cortex-M3 NVIC                     | 188 |

| 9.2 動作   | 作                                  | 189 |

| 9.2.1    | IRQ の同期化                           | 189 |

| 9.2.2    | ノンマスカブル割り込み                        | 189 |

| 9.2.3    | Cortex-A7 と Cortex-M3 の割り込みマネージメント | 190 |

| 9.2.4    | 割り込み割り当てとベクタ番号                     | 191 |

| 第 10 章 ( | 0                                  | 195 |

| 10.1 端-  | 子機能                                | 195 |

| 10.2 未信  | 使用端子の処理                            | 201 |

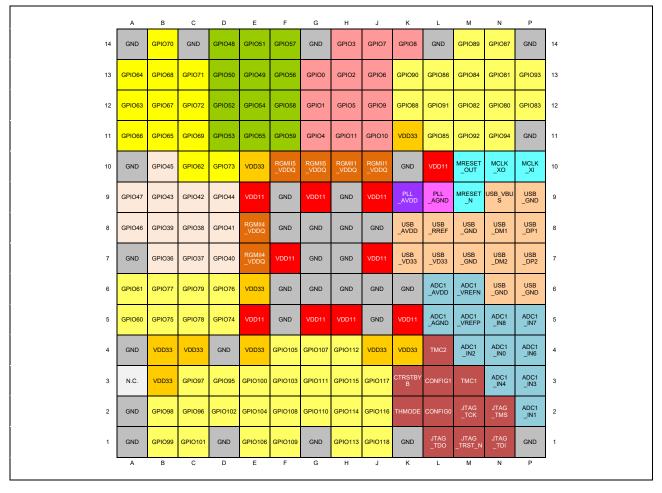

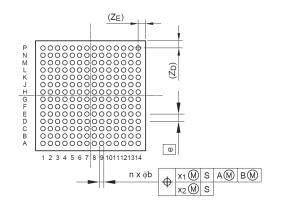

| 10.3 端-  | 子配置図                               | 202 |

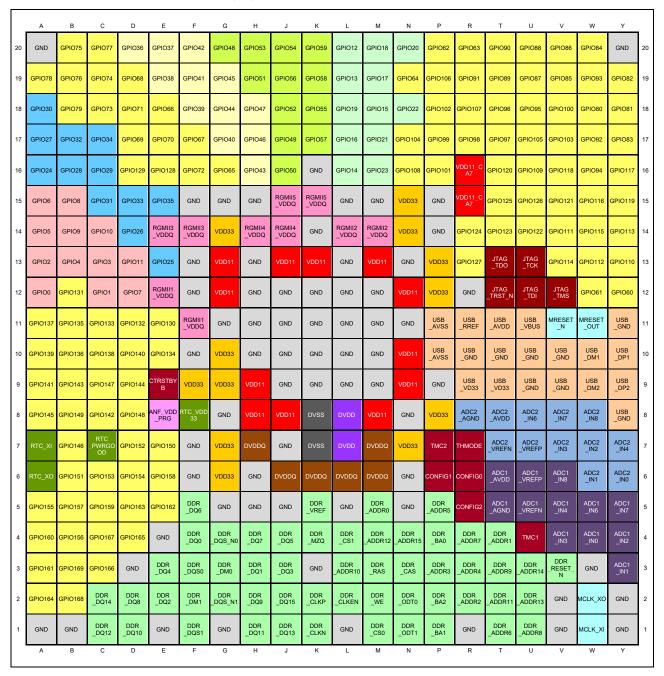

| 10.3.1   | l RZ/N1D BGA-400 パッケージ             | 202 |

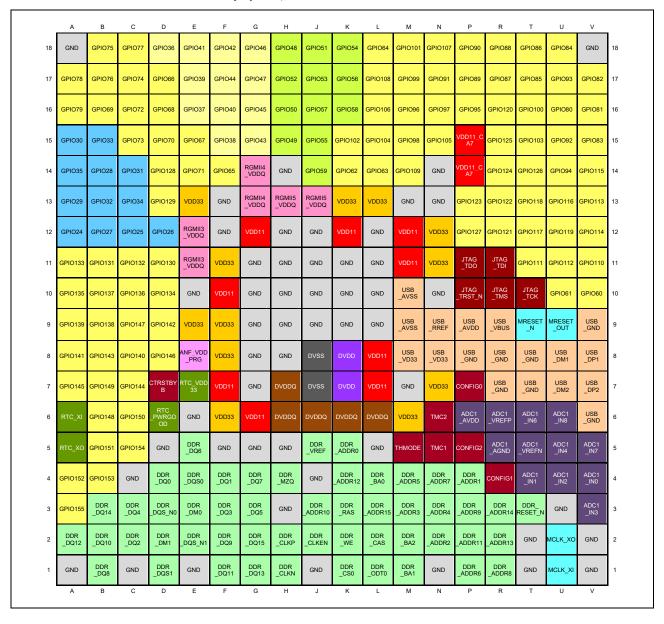

| 10.3.2   | 2 RZ/N1D BGA-324 パッケージ             | 203 |

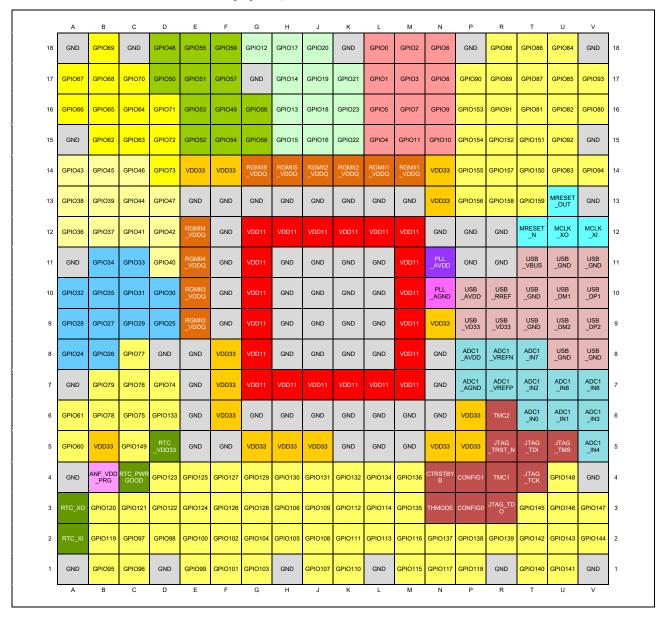

| 10.3.3 RZ/N1S BGA-324 パッケージ       | 204 |

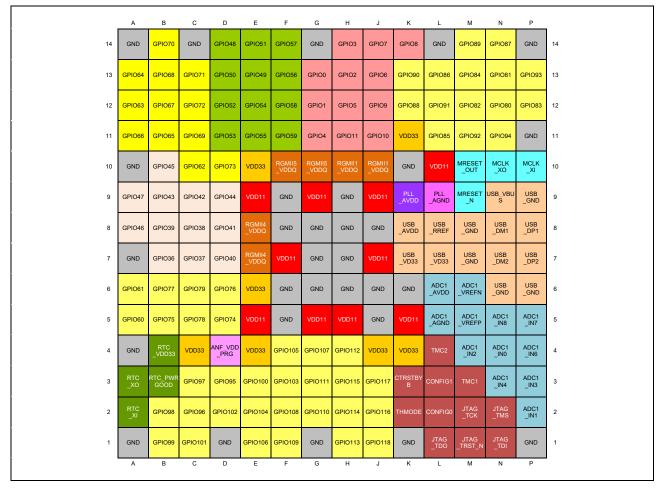

|-----------------------------------|-----|

| 10.3.4 RZ/N1S BGA-196 パッケージ       | 205 |

| 10.3.5 RZ/N1L BGA-196 パッケージ       | 206 |

| 第 11 章 電気的特性                      | 207 |

| 11.1 絶対最大定格                       | 207 |

| 11.2 推奨動作条件                       | 208 |

| 11.3 DC 特性                        | 209 |

| 11.3.1 電流                         |     |

| 11.3.2 デジタル IO                    |     |

| 11.3.3 DDR3/DDR2 SDRAM インタフェース    | 210 |

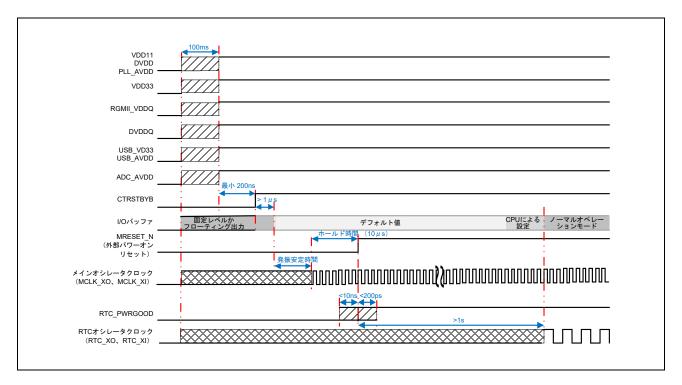

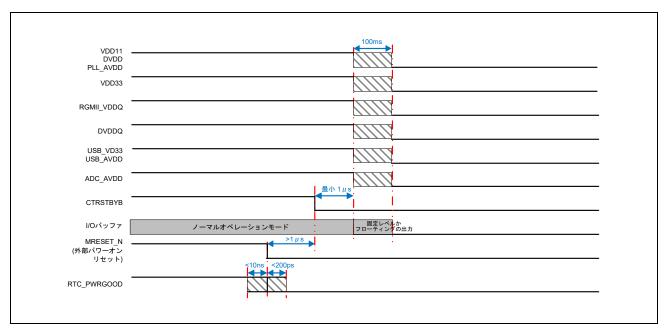

| 11.4 電源投入/切断シーケンス                 | 211 |

| 11.4.1 電源投入                       | 211 |

| 11.4.2 電源切断                       | 211 |

| 11.5 AC タイミング特性                   | 212 |

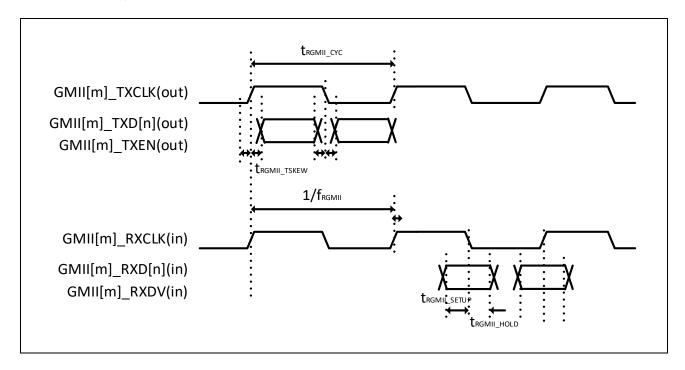

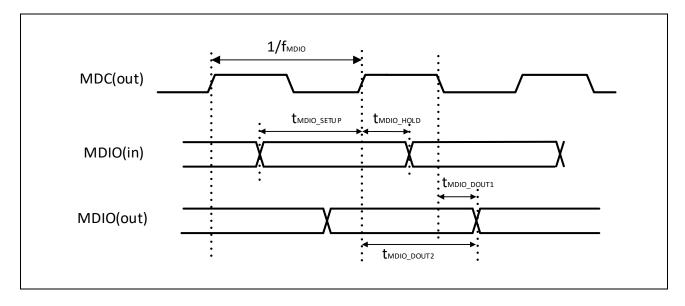

| 11.5.1 Ethernet MAC インタフェースタイミング  | 212 |

| 11.5.1.1 RGMII                    |     |

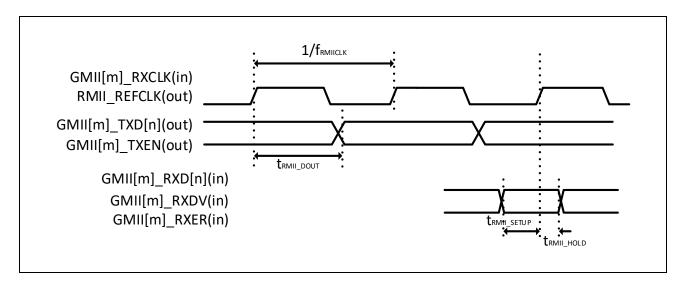

| 11.5.1.2 RMII                     |     |

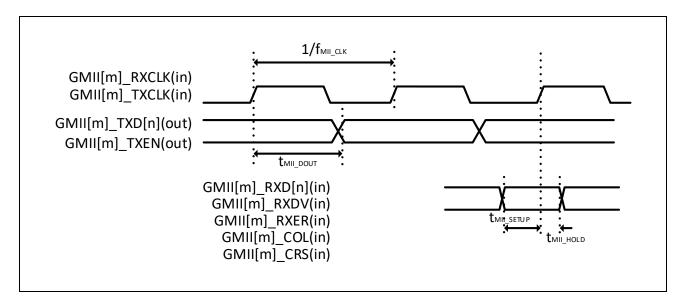

| 11.5.1.3 MII                      |     |

| 11.5.2 メモリインタフェースタイミング            |     |

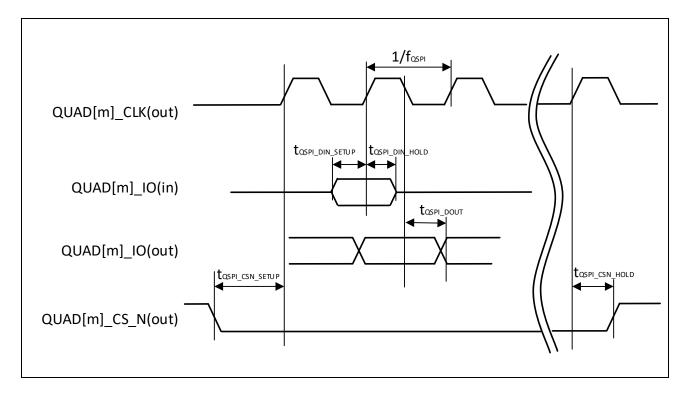

| 11.5.2.1 QSPI Flash タイミング         |     |

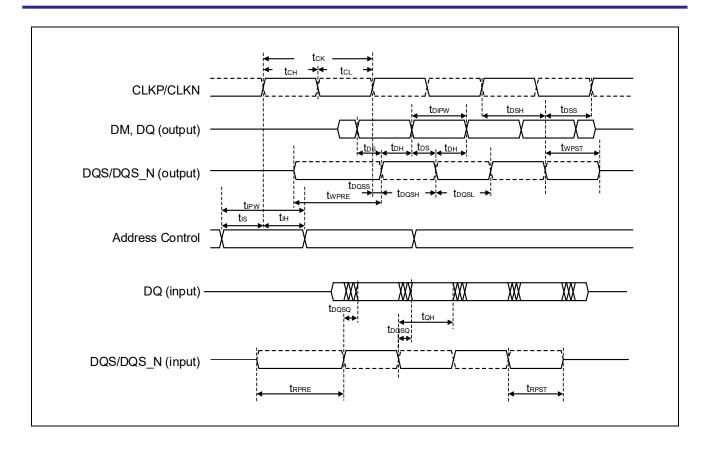

| 11.5.2.2 DDR3/DDR2 インタフェース        |     |

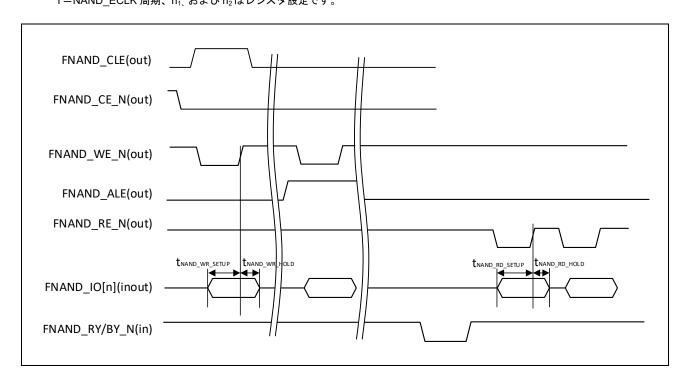

| 11.5.2.3 NAND Flash インタフェース       |     |

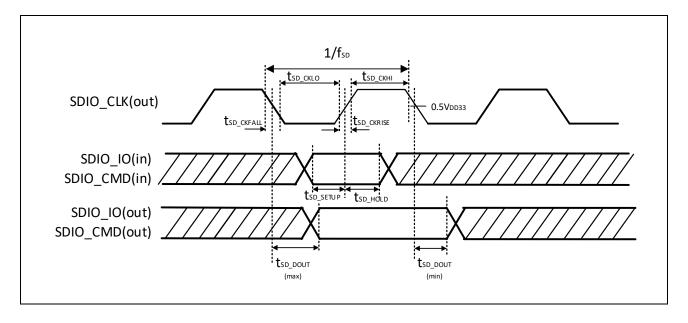

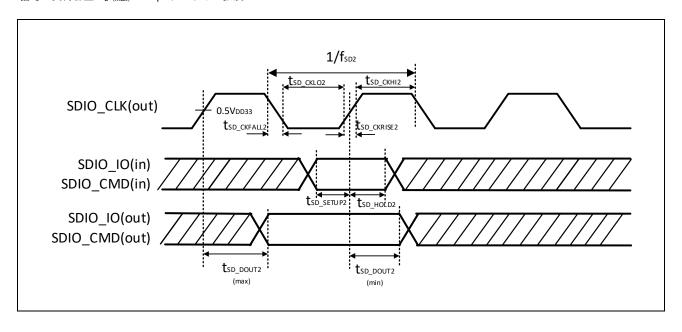

| 11.5.2.4 SD/eMMC/SDIO インタフェース     |     |

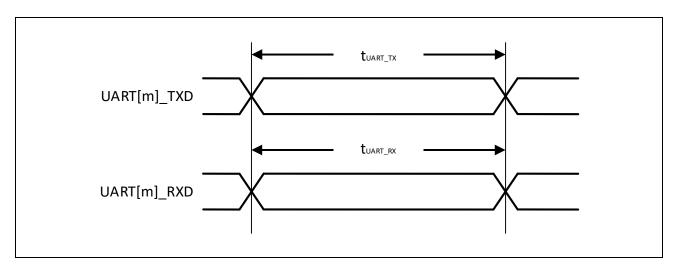

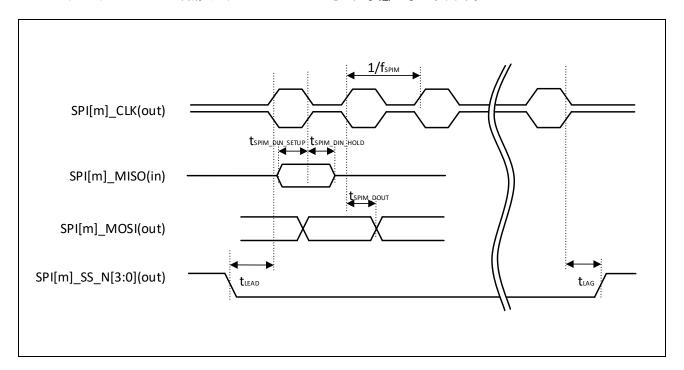

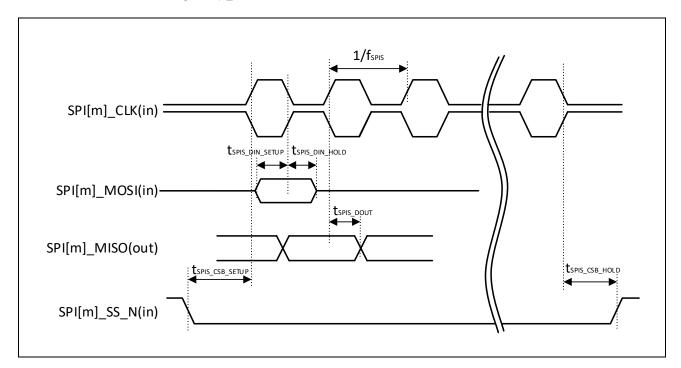

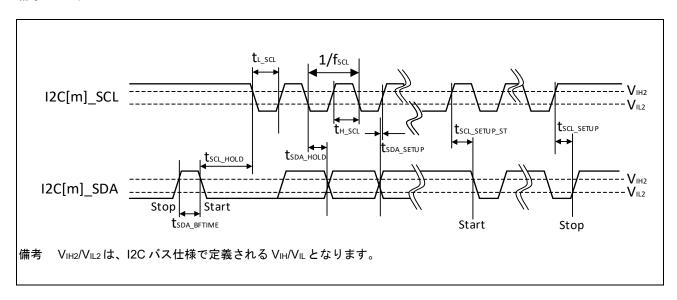

| 11.5.3 シリアルインタフェースタイミング           |     |

| 11.5.3.1 UART<br>11.5.3.2 SPI マスタ |     |

| 11.5.3.3 SPI スレーブ                 |     |

| 11.5.3.4 I2C                      |     |

| 11.5.3.5 CAN                      |     |

| 11.5.3.6 JTAG/SWD                 |     |

| 11.5.4 LCD インタフェースタイミング           |     |

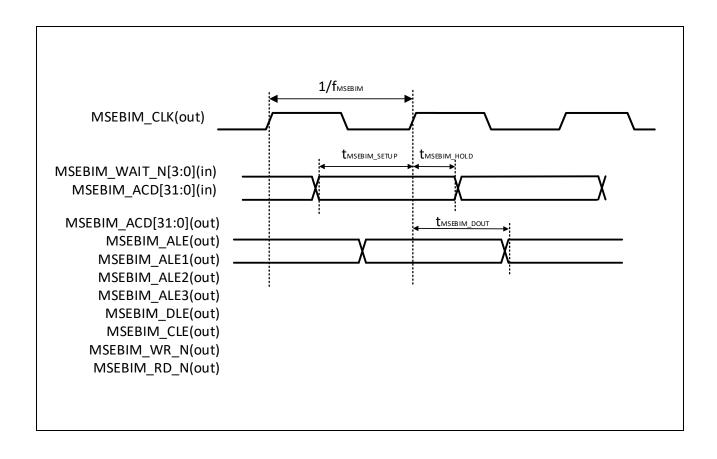

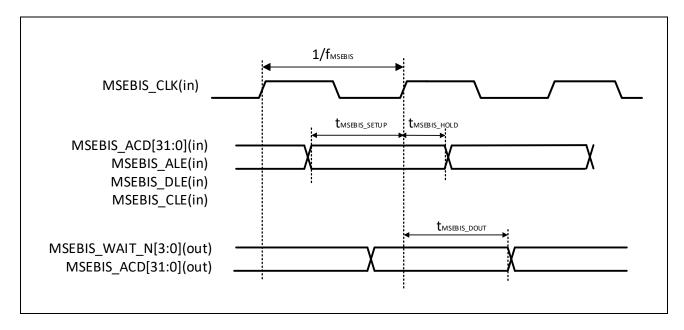

| 11.5.5 MSEBI インタフェースタイミング         | 230 |

| 11.6 ADC 特性                       | 232 |

| 11.7 RTC オシレータ特性                  | 232 |

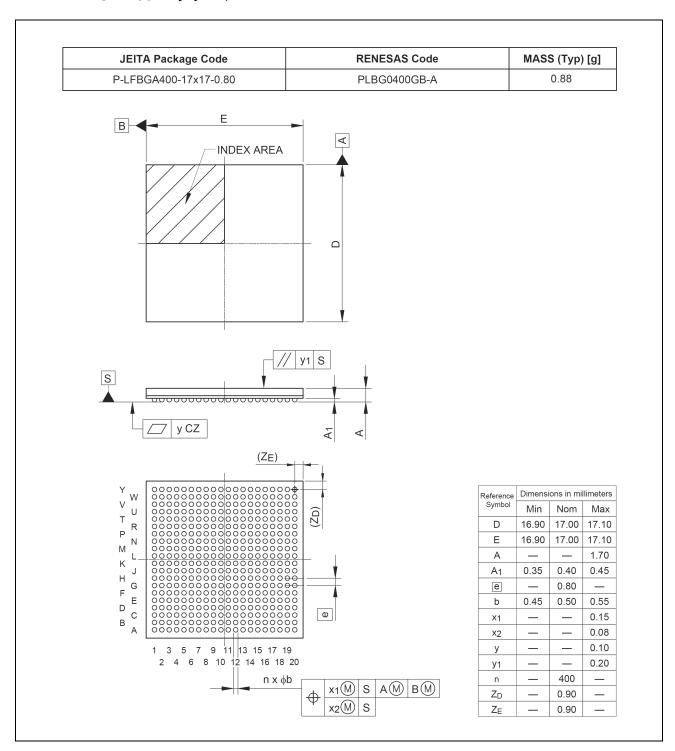

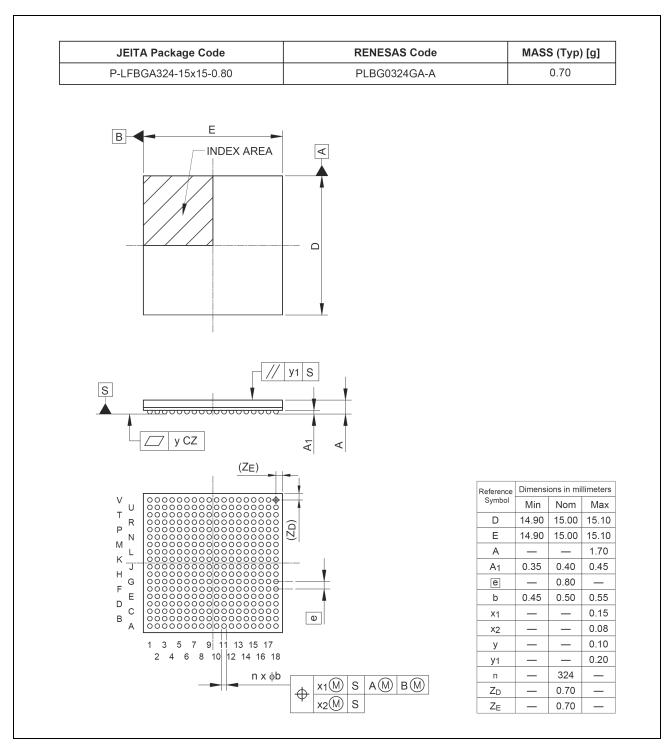

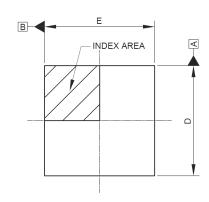

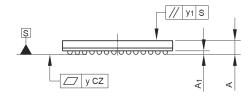

| 第 12 章 機械的特性                      | 233 |

| 12.1 パッケージ情報                      | 233 |

| 12.1.1 BGA-400 パッケージ              | 233 |

| 12.1.2 BGA-324 パッケージ              | 234 |

| 12.1.3 BGA-196 パッケージ              | 235 |

| 付録 A | 端子割り当て           | . 236 |

|------|------------------|-------|

| 付録 B | IO マルチプレクシング割り当て | . 245 |

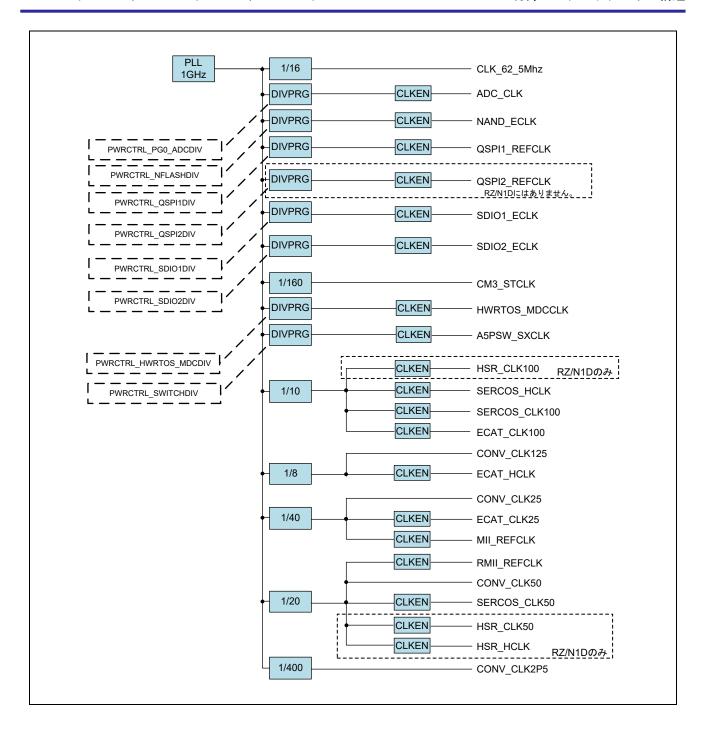

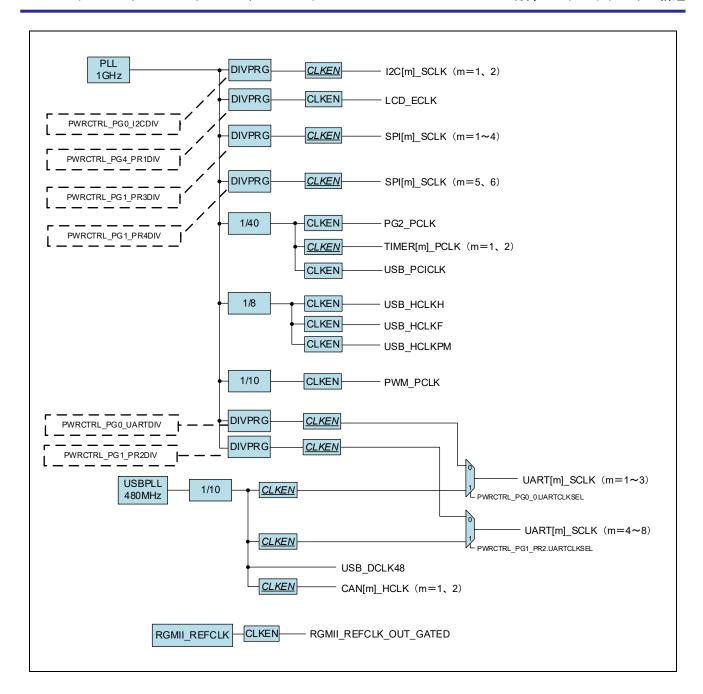

| 付録 C | クロックツリー構造        | . 249 |

## 第1章 全体構造

### 1.1 デバイス概要

#### ■ 32 ビット Arm® Cortex®-A7 MPCore 内蔵

- 最大 500MHz

- シングルコアもしくはデュアルコア

- FPU、VFPv4-D16

- MMU

- L1 キャッシュ:コア毎に 16K バイト(命令)/ 16K バイト(データ)

- L2 キャッシュ:最大 256K バイト

#### ■ 32 ビット Arm® Cortex®-M3 プロセッサ内蔵

- 最大 125MHz

- Memory Protection Unit (MPU) をサポート

#### ■ 低消費電力機能

- クロックゲーティング管理

- クロック周波数変更

#### ■ 内蔵 SRAM

• 最大 6M バイト (ECC 付き)

#### ■ データ転送

● 2 ユニットの各 8ch DMAC

#### ■ メモリインタフェース

- 最大 2ch の Quad SPI/XIP

- 高度な ECC 管理機能を備えた NAND Flash

- 16 ビット幅 DDR インタフェース (DDR2-500/DDR3-1000)

- 最大 2ch の SD/SDIO/eMMC

#### ■ IO マルチプレキシングコントローラ

• 周辺機能の I/O 位置を複数の端子の中から選択可

#### ■ クロックオシレータ

- ◆外部クロック/オシレータ 入力周波数:40MHz

- 32kHz の RTC

#### ■ セキュリティ機能(オプション)

• セキュアブート/JTAG ロック/64 ビットのチップ ID

#### ■ 周辺機能

- CPU リソース

- メールボックス

- 2ユニットのタイマ (16bit×6ch, 32bit×2ch)

- PWMTimer (16bit×16ch)

- CPU 毎に1ユニットのウォッチドッグ

- セマフォ

- 汎用インタフェース

- 1ch の USB2.0 ホスト

- 1ch の USB2.0 ホストもしくはファンクション

- 8ch O UART

- 6ch の SPI (4ch のマスタ / 2ch のスレーブ)

- 2ch Ø I<sup>2</sup>C

- 2ch O CAN

- 最大 2 ユニットの 12 ビット ADC (最大 1MSPS)

- MSEBI (外部バスインタフェース)

- その他機能

- LCD コントローラ

- GPIOピン(最大 170)

#### ■ R-IN Engine

- Arm<sup>®</sup> Cortex<sup>®</sup>-M3 CPU

- ハードウェア RTOS アクセラレータ (HW-RTOS)

- ハードウェア Ethernet アクセラレータ

#### ■ 高度なリアルタイム Ethernet 機能

- Sercos<sup>®注1</sup>III スレーブコントローラ

- EtherCAT®注23 ポートスレーブコントローラ

- Advanced 5 (4+1) Port Switch (A5PSW)

- QoS と IEEE1588 対応で 5 ポートをスイッチ ▶ 最大 5 のギガビットのポート

- IEC62439-3 Ed2.0-2012 準拠の PRP (オプション)

- IEC62439-3 Ed2.0-2012 準拠の HSR (オプション)

- 最大 2 つの独立した GMAC、IEEE1588 準拠

- MII/RMII/RGMII の最大 5 の外部ポート

注1. Sercos は、Sercos International e.V.の登録商標です。

注2. EtherCAT は、ドイツ Beckhoff Automation GmbH によりライセンスされた特許取得済み技術であり登録商標です。

## 1.2 仕様の概要

表 1.1 仕様の概要 (1/8)

| 分類      | モジュール/機能       | 説明                                                                                                                                                                                                                                                                                                        |

|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU     | Arm Cortex-A7  | <ul> <li>Arm 社の 32 ビット CPU Cortex-A7 (リビジョン r0p5)</li> <li>デュアルコアもしくはシングルコア</li> <li>最大動作周波数: 500MHz</li> <li>クロック周波数変更</li> <li>L1 キャッシュ: コア単位に 16K バイト (命令) / 16K バイト (データ)</li> <li>L2 キャッシュ: 最大 256K バイト</li> <li>FPU、VFPv4-D16</li> <li>MMU</li> <li>ハードウェアコヒーレントキャッシュ</li> <li>リトルエンディアン</li> </ul> |

|         | Arm Cortex-M3  | <ul> <li>Arm 社の 32 ビット CPU Cortex-M3 (リビジョン r2p1)</li> <li>最大動作周波数: 125MHz</li> <li>Memory Protection Unit (MPU)</li> <li>リトルエンディアン</li> </ul>                                                                                                                                                            |

| メモリ     | オンチップ 2MB SRAM | <ul> <li>容量: 2M バイト (1M バイト+1M バイト)</li> <li>512K バイト単位に分割されたアクセスポート</li> <li>SEC-DED (シングルエラー訂正、ダブルエラー検出)</li> </ul>                                                                                                                                                                                     |

|         | オンチップ 4MB SRAM | <ul> <li>容量:4M バイト</li> <li>1M バイト単位に分割されたアクセスポート</li> <li>SEC-DED (シングルエラー訂正、ダブルエラー検出)</li> </ul>                                                                                                                                                                                                        |

| ウォッチドッグ |                | <ul> <li>リロードレジスタ付きのフリーランニングの12ビットデクリメントカウンタ</li> <li>出力をシステムリセット、あるいは割り込みとして使用可能</li> <li>デバッガ(ブレークポイント実行など)によるCPU停止中のウォッチドッグ停止制御</li> </ul>                                                                                                                                                             |

| 動作モード   |                | ● 3 つのブートモード(CA7)<br>— NAND Flash<br>— QSPI Flash<br>— USB DFU                                                                                                                                                                                                                                            |

| クロック    | クロック発生回路       | <ul> <li>入力 40MHz クロックをオシレータまたはクリスタルから選択可能</li> <li>システムクロック:最大 125MHz</li> <li>Cortex-A7 クロック:システムクロックの 1/2/4 倍</li> <li>DDR メモリクロック: 250MHz/500MHz</li> </ul>                                                                                                                                           |

| RTC     |                | <ul> <li>● 24 時間モードの日付クロック</li> <li>● カレンダー</li> <li>● アラーム機能</li> <li>● クリスタル 32kHz</li> <li>● RTC バックアップモード用独立電源供給</li> </ul>                                                                                                                                                                           |

| リセット    |                | <ul><li>● マスタリセット入力</li><li>● 内部システムリセット(ソフトウェア、ウォッチドッグ)</li></ul>                                                                                                                                                                                                                                        |

表 1.1 仕様の概要 (2/8)

| 分類                | モジュール/機能                                                            | 説明                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| データ転送             | ダイレクトメモリ<br>アクセスコントローラ<br>(Direct Memory Access<br>Controller:DMAC) | <ul> <li>● 2 ユニット:         <ul> <li>DMAC1:8 チャネル、16 リクエストソース</li> <li>DMAC2:8 チャネル、16 リクエストソース</li> </ul> </li> <li>● メモリからメモリ、メモリから周辺機能、周辺機能からメモリの転送</li> <li>● 転送幅:         <ul> <li>8、16、32、64 ビット</li> </ul> </li> <li>プログラマブルな DMA バーストサイズ</li> </ul>                                                                                                                                          |

| メールボックス           |                                                                     | ● 3 ユニットのプログラマブルなメールボックス                                                                                                                                                                                                                                                                                                                                                                            |

|                   |                                                                     | メールボックス毎の 7 つの 32 ビットデータレジスタ<br>                                                                                                                                                                                                                                                                                                                                                                    |

| セマフォ              |                                                                     | ● 内部共有リソースのハードウェアロックメカニズム                                                                                                                                                                                                                                                                                                                                                                           |

| パラレルバス<br>インタフェース | 外部バスインタフェース<br>(Medium Speed<br>External Bus Interface:<br>MSEBI)   | <ul> <li>マスタおよびスレーブモード         <ul> <li>8、16、32 ビットから選択可能なデータバス幅</li> </ul> </li> <li>アドレス/データ/制御データをデータバス上にマルチプレクス</li> <li>バーストモード</li> <li>DMA サポート         <ul> <li>マスタモード: 4DMA チャネル接続(外部リクエスト受信可能)</li> <li>スレーブモード: 外部リクエスト送信可能</li> </ul> </li> <li>最大 4 チップセレクト</li> <li>2 バイト~4G バイトのプログラマブルなアドレス機能</li> <li>プログラマブルなセットアップ/ホールド時間</li> <li>外部ウエイトリクエスト</li> </ul>                        |

| I/O ポート           | IO マルチプレキシング                                                        | <ul><li>周辺機能の I/O 位置が選択可能</li><li>出力ドライブ強度の選択</li><li>オンチップのプルアップ/プルダウン抵抗の選択</li></ul>                                                                                                                                                                                                                                                                                                              |

| メモリ<br>インタフェース    | DDR2/3 コントローラ                                                       | <ul> <li>DDR2-500/DDR3-1000</li> <li>メモリデータパスサイズ:16 ビット、8 ビット、8 + ECC ビット</li> <li>最大2 チップセレクトおよび 2ODT</li> <li>最大2G バイトアドレスをサポート</li> <li>ECC SEC/DED ソフトウェア設定可能(有効/無効)</li> <li>終端抵抗(ODT:On-Die Termination)設定</li> <li>出カインピーダンスおよびスルーレート設定</li> <li>DDR2/DDR3 低電力制御マネージメント(ソフトウェアによる)</li> <li>ポートアドレス保護チェック</li> <li>ポートアドレス保護チェック</li> <li>ポート単位の最大16アドレス保護領域</li> </ul>                      |

|                   | NAND Flash<br>コントローラ                                                | <ul> <li>● 8 ビットバス幅の NAND インタフェース</li> <li>● 非同期モードサポート</li> <li>● 4 チップセレクト</li> <li>● ライトプロテクション</li> <li>● プログラマブルなアドレスサイクル (0/1/2/3/4/5)</li> <li>● 内蔵 DMA</li> <li>● 256B、512B、2KB、1KB、4KB、8KB、16KBページをサポート</li> <li>● BCH ECC (エラー検出およびデータ訂正)</li> <li>- ECC データブロックサイズ: 256 バイト、512 バイト、1024 バイト</li> <li>- ECC 訂正機能: 2、4、8、16、24、32 ビットエラー</li> <li>● Bad Block Management (BBM)</li> </ul> |

表 1.1 仕様の概要 (3/8)

| 分類          | モジュール/機能        | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| メモリインタフェース  | Quad SPI (QSPI) | <ul> <li>● 最大 2 ユニット</li> <li>● Single、Dual もしくは Quad の I/O 命令をサポート</li> <li>● リード高速化モード(NoCMD モード)をサポート</li> <li>● リマップアドレスによるダイレクトアクセス</li> <li>● プログラマブルなデバイスサイズ</li> <li>● 最大 4 チップセレクト</li> <li>● 1/2/3/4 バイトアドレス指定をサポート</li> <li>● プログラマブルなページサイズをサポート(デフォルト 256 バイト)</li> <li>● プログラマブルなデバイスブロック毎のバイト数</li> <li>● プログラマブルなライトプロテクト領域</li> <li>● 送受信 FIFO: 16 バイト</li> <li>● 送受信 FIFO へのダイレクトアクセス(レガシーモード)</li> <li>■ コントロールレジスタセットによる任意の FLASH コマンド実行</li> <li>● ダイレクトアクセス時のバーストライト対応</li> </ul> |

|             | SD/SDIO/eMMC    | <ul> <li>● 最大 2 ユニット</li> <li>● SD/SDIO カードインタフェース         <ul> <li>1 ビットもしくは 4 ビットモードでのデータ転送</li> <li>デフォルトモードもしくはハイスピードモードでのデータ転送</li> </ul> </li> <li>● eMMC インタフェース                  <ul> <li>1 ビット、4 ビットもしくは 8 ビットモードでのデータ転送</li> <li>● 転送速度</li> <li>デフォルトモード:最大 25MHz</li> <li>ハイスピードモード:最大 50MHz</li> </ul> </li> <li>● PIO/SDMA/ADMA2 転送のサポート</li> </ul>                                                                                                                                       |

| ネットワークエレメント | R-IN Engine     | ● ITRON ライクのシステムコール - イベント、セマフォ、およびメールボックスといったエレメント用の 30 種類のシステムコール ● タスクスケジューラ - ハードウェア ISR: 128 の割り込みから最大 32 個を選択可能 - コンテキスト要素数: 64 - セマフォ識別子数: 128 - イベント識別子数: 64 - メールボックス識別子数: 64 - メールボックス要素数: 192 - コンテキスト優先度レベル数: 16 ● ハードウェアファンクションマネージャ ● 内蔵 DMA コントローラ ● バッファアロケータ ● ヘッダのエンコード/デコード ● 専用ギガビットイーサネット MAC(MACDMAC 内蔵)                                                                                                                                                                          |

表 1.1 仕様の概要 (4/8)

| 分類          | モジュール/機能                                        | 説明       |

|-------------|-------------------------------------------------|----------|

| ネットワークエレメント | アドバンスト5ポートスイッチ(Advanced 5 Port<br>Switch:A5PSW) | ● 動作モード: |

表 1.1 仕様の概要 (5/8)

| 分類     | モジュール/機能         | 説明                                                                  |

|--------|------------------|---------------------------------------------------------------------|

| ネットワーク | HSR スイッチ         | ● HSR 機能(IEC 62439-3 edition 2.0- 2012)                             |

| エレメント  |                  | – DANH                                                              |

|        |                  | – 冗長ボックス(Red Box)                                                   |

|        |                  | │<br>│ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □                          |

|        |                  | <br>  _ 重複した受信フレームのフィルタリング                                          |

|        |                  | - 冗長ヘッダの生成と検出                                                       |

|        |                  | - 受信フレーム追跡テーブル                                                      |

|        |                  | ● 100Mbps 全二重イーサネット                                                 |

|        |                  | ● 動的フレームバッファ割り当て(page manager)                                      |

|        |                  | ● 128 プロキシノード (VDANs) をサポート                                         |

|        |                  | ● リンクローカルプロトコルをサポート                                                 |

|        |                  | <ul><li>● 重複検出メモリ</li></ul>                                         |

|        |                  | ● MAC アドレスフィルタリング                                                   |

|        |                  | ● 1 つの VLAN タグをサポート                                                 |

|        |                  | ● ポート単位(集約なし)のポート統計                                                 |

|        |                  | ● 144K バイトフレームバッファ                                                  |

|        |                  | • IEEE 1588-2008                                                    |

|        |                  | <ul><li>● フラッディング制御を備えたイーサネットマルチキャスト</li></ul>                      |

|        |                  | ● 拡張フレーム長:最大 2000 バイト (ジャンボフレーム未対応)                                 |

|        |                  | ● HSR ループで最小 16 ノードをサポート                                            |

|        |                  | ● 重複検出滞留時間設定                                                        |

|        | EtherCAT スレーブ    | ● 最大 3 ポート                                                          |

|        | コントローラ           | ● 自動 TX シフト                                                         |

|        |                  | ● 拡張リンク検出                                                           |

|        |                  | ● 8 つの FMMU (Fieldbus Memory Management Unit)                       |

|        |                  | • 8 つの SyncManager                                                  |

|        |                  | ● 64 ビット分散クロック                                                      |

|        |                  | ● グローバル IRQ へのマッピング                                                 |

|        |                  | • Read/Write オフセット                                                  |

|        |                  | ● ライトプロテクション                                                        |

|        |                  | • AL Status Code レジスタ                                               |

|        |                  | ● 拡張ウォッチドッグ                                                         |

|        |                  | ● AL Event Mask レジスタ                                                |

|        |                  | • ウォッチドッグカウンタ                                                       |

|        |                  | ● SyncManager イベントタイム                                               |

|        |                  | ● EPU エラーカウンタ<br>● ロストリンクカウンタ                                       |

|        |                  | ● ロストリングガウンダ<br>● 外部 EEPROM 用の I2C interface                        |

|        | Canacill 7 ! = = |                                                                     |

|        | SercosIII スレーブ   | ● 2ポート                                                              |

|        |                  | ● シリアルインタフェースは 100Mbaud<br>● 自動送信のテレグラム処理および同期テレグラムおよびデータテレグラムのモニ   |

|        |                  | ■ 自動送信のテレクラム処理およい同期テレクラムおよのテータテレクラムのモー<br>タリング                      |

|        |                  | ● マルチプレクサ経由で Sercos プロトコルと標準イーサネットプロトコル間の機能切り替え                     |

|        |                  | ● 受信データストリームモニタによりフレームタイプ検出し、SercosIII フレームタ                        |

|        |                  | イプ検出時に動作開始<br>■ ニレグニノタノプ (MST/MDT + L / J+ AT) に其づいて SPAM の 3 出力データ |

|        |                  | ● テレグラムタイプ(MST/MDT もしくは AT)に基づいて SRAM の入出力データ<br>転送のハンドリング          |

表 1.1 仕様の概要 (6/8)

| 分類     | モジュール/機能       | 説明                                                                         |

|--------|----------------|----------------------------------------------------------------------------|

| ネットワーク | 独立した GMAC      | • 2ユニットの MAC (GMAC1、GMAC2)                                                 |

| エレメント  |                | ● 以下の標準規格に準拠                                                               |

|        |                | – IEEE 1588-2008 v2 standard(高精度ネットワーククロック同期)                              |

|        |                | - IEEE 1588-2008 v2 は Power IEEE C37.238 profile に準拠                       |

|        |                | - IEEE 802.3-az-2010 (Energy Efficient Ethernet (EEE) )                    |

|        |                | ● 10/100/1000Mbps データ転送速度をサポート                                             |

|        |                | ● 半二重および全二重動作の両方をサポート                                                      |

|        |                | ● 標準および最大 16K バイト(16K バイトー1)のジャンボイーサネットフレーム                                |

|        |                | をサポートするためのプログラマブルなフレーム長                                                    |

|        |                | ● アドレスフィルタブロック用 17 個の MAC アドレスレジスタ                                         |

|        |                | ● 多種のフレキシブルなアドレスフィルタリングモードに対応                                              |

|        |                | ● 送受信エンジン用独立チャネルネイティブ DMA                                                  |

|        |                | ● 拡張 IEEE 1588-2002 & 2008 イーサネットフレームタイムスタンプをサポート                          |

|        |                | Pulse-Per-Second (PPS) 出力信号のフレキシブル制御 (GMAC1 のみ)     CDC 生まれたびます。    A 数数数字 |

|        |                | ● CRC 生成およびチェック機能設定<br>  ● RMON 統計サポート(L2 層のみ)                             |

|        |                | Station Management ブロック、MDIO インタフェース                                       |

| サブシステム | USB2.0 ホスト     | ● 1つの専用ポートと1つの共用ポート(ホストもしくはファンクション)                                        |

| エレメント  | (USBh)         | ● 転送速度                                                                     |

| エレバント  | (0 = =,        | - High speed (HS) : 480Mbps (USB2.0)                                       |

|        |                | - Full speed (FS) : 12Mbps (USB1.1)                                        |

|        |                | - Full speed (F3) : 12Mbps (USB1.1)  - Low speed (LS) : 1.5Mbps (USB1.1)   |

|        |                | USB Plug Detect (UPD)                                                      |

|        |                | ● 出力ポート電力切り替えマネージメント                                                       |

|        |                | ● アプリケーションからの過電流表示                                                         |

|        |                | ● 内蔵 DMA                                                                   |

|        |                | ● 送受信 FIFO                                                                 |

|        | USB2.0 ファンクション | ● 1 つの共用ポート(ホストもしくはファンクション)                                                |

|        | (USBf)         | ● サポート                                                                     |

|        |                | - High speed (HS) : 480Mbps (USB2.0)                                       |

|        |                | - Full speed (FS) : 12Mbps (USB1.1)                                        |

|        |                | VBUS 経由でホストの接続を検出する USB Plug Detect (UPD)                                  |

|        |                | • 16 の物理 Endpoint                                                          |

|        |                | ● 内蔵 DMA                                                                   |

|        |                | ● Endpoint バッファ                                                            |

|        | UART 1, 2, 3   | ● 16550 UART 準拠                                                            |

|        |                | ● 分離した 16×8(16×8 ビット幅)の送信および 16×8 の受信 FIFO                                 |

|        |                | ● RS485 および MODBUS®拡張機能                                                    |

|        |                | ● 最大 5.2Mbaud のボーレート生成                                                     |

|        |                | ● ラインブレークの生成および検出                                                          |

|        |                | ● プログラマブルなハードウェアフロー制御                                                      |

|        |                | ● 16750 に準拠した自動フロー制御モード                                                    |

|        |                | • TXD、RXD、CTS_N、RTS_N、DTR_N、DSR_N、DCD_N、RI_Nのサポート                          |

|        | LIADTA E 6 7 0 | ● UART 1、2、3 と同機能に加えて以下の機能が使用可能                                            |

|        | UART 4、5、6、7、8 | UARTI、2、3 と同僚能に加えて以下の機能が使用可能                                               |

表 1.1 仕様の概要 (7/8)

| 分類              | モジュール/機能             | 説明                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| サブシステム<br>エレメント | SPI 1、2、3、4<br>(マスタ) | <ul> <li>送信および受信 FIFO (16×16)</li> <li>プログラマブルな RXD サンプリング機能</li> <li>プログラマブルなフレームデータサイズ (4~16 ビット)</li> <li>4 チップセレクト</li> <li>DMA コントローラインタフェース</li> </ul>                                                                                                                                                                                                        |

|                 | SPI 5、6<br>(スレーブ)    | <ul> <li>送信および受信 FIFO (16×16)</li> <li>プログラマブルなフレームデータサイズ (4~16 ビット)</li> <li>DMA コントローラインタフェース</li> </ul>                                                                                                                                                                                                                                                          |

|                 | I <sup>2</sup> C 1、2 | <ul> <li>2種類のスピードモード         <ul> <li>標準モード (0~100Kbps)</li> <li>ファストモード (400Kbps 以下)</li> </ul> </li> <li>分離された 8×8 送信および 8×8 受信 FIFO</li> <li>マスタもしくはスレーブの I2C 動作</li> <li>7 もしくは 10 ビットのアドレス指定</li> <li>7 もしくは 10 ビットの結合されたフォーマットの転送</li> <li>バルク転送モード</li> <li>プログラマブルな SDA ホールド時間 (t<sub>HD; DAT</sub>)</li> </ul>                                             |

|                 | CAN 1、2              | <ul> <li>11 ビットと 29 ビット ID の両方をサポート</li> <li>125Kbps~1Mbps のビットレートをサポート</li> <li>アクセプタンスフィルタリング</li> <li>ソフトウェアドリブンのビットレート検出(ホットプラグインサポート)</li> <li>シングルショット送信オプション、listen-only モード、自己メッセージ受信</li> <li>ビット位置情報付きのアービトレーションロスト割り込み</li> <li>Read/write エラーカウンタ</li> <li>ラストエラーレジスタ</li> <li>プログラマブルなエラー限界警告</li> <li>同期フレームの周期的送信</li> <li>プログラマブルなタイムベース</li> </ul> |

|                 | 汎用タイマ(TIMER)         | <ul> <li>● 2 ユニットでそれぞれ以下をサポート         <ul> <li>6 つのプログラマブルな 16 ビットタイマ</li> <li>2 つのプログラマブルな 32 ビットタイマ</li> </ul> </li> <li>● 2 つのタイムベースから選択可能なプリスケーラ</li> <li>● 自動リロードモードもしくはシングルショットモード</li> <li>● DMA 接続(32 ビットタイマのみ)</li> </ul>                                                                                                                                  |

|                 | PWMTimer             | <ul> <li>◆ キャプチャおよびクロック用の6本の入力         <ul> <li>バウンスフィルタ</li> <li>40本の外部入力</li> </ul> </li> <li>◆ 16本のコンペアマッチ出力         <ul> <li>20本の外部出力</li> </ul> </li> <li>◆ 16個の16ビットカウンタ</li> <li>キャプチャおよびコンペア機能</li> <li>32ビットカスケードカウンタ</li> <li>2 つの10ビットプリスケーラクロック</li> <li>他のカウンタとの同期動作</li> </ul>                                                                        |

表 1.1 仕様の概要 (8/8)

| 分類        | モジュール/機能             | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC       | ADC                  | <ul> <li>最大 2 ユニット</li> <li>12 ビット分解能</li> <li>0.0625MSPS~1MSPS のサンプリングレート</li> <li>アナログ入力         <ul> <li>8 チャネル: (5 チャネル+サンプル&amp;ホールドを備えた 3 チャネル)</li> </ul> </li> <li>チャネル毎に個々のトリガー</li> <li>DNL、±1.0LSB (Max.) [VAIN=0.0V~AVDD および f<sub>CLK</sub>=20MHz 時]</li> <li>INL、±4.0LSB (Max.) [VAIN=0.0V~AVDD および f<sub>CLK</sub>=20MHz 時]</li> <li>パワーダウンモード</li> <li>2 段階の優先度</li> <li>同一優先度レベルで同時に変換要求発生時のラウンドロビン管理</li> <li>DMA 接続</li> <li>仮想チャネル機能</li> </ul>             |

| マルチメディア   | LCD コントローラ<br>(LCDC) | <ul> <li>プログラマブルな LCD パネル解像度</li> <li>1ポートの TFT LCD パネルインタフェース         <ul> <li>18 ビットデジタル (6 ビット/color)</li> <li>24 ビットデジタル (8 ビット/color)</li> </ul> </li> <li>プログラマブルなフレームバッファ bits per pixel (bpp)         <ul> <li>カラーパレットでマップされた 1、2、4、8bpp の 18 ビット LCD ピクセル</li> <li>16、18bpp の 18 ビット LCD ピクセル</li> <li>24bpp の 24 ビット LCD ピクセル</li> </ul> </li> <li>ハードウェア点滅のサポート</li> <li>LCD パネルの LED バックライト輝度制御用の PWM モジュール</li> <li>電源投入および切断シーケンスのサポート</li> <li>内蔵 DMA</li> </ul> |

| セキュリティ    |                      | <ul> <li>セキュアブートによるプログラムの署名検証</li> <li>JTAG 接続によるデバッグ無効化</li> <li>Coretex-A7 から読み出し可能なチップ固有の 64 ビット ID</li> </ul>                                                                                                                                                                                                                                                                                                                                                               |

| デバッグインタフ: | ェース                  | <ul> <li>JTAG デバッガに結合された ETM</li> <li>Cortex-A7 および Cortex-M3 コアで共有されたトレースバッファ (32KB)</li> <li>Arm JTAG</li> <li>Arm SWD</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

| 電源電圧      |                      | <ul> <li>コア電圧: 1.15V±0.05V</li> <li>IO 電圧: 3.3V±0.3V</li> <li>DDR IO 電圧: 1.8V±0.1V、1.5V±0.075V</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |

| 動作温度      |                      | ジャンクション温度: -40°C~+110°C                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| パッケージ     |                      | <ul> <li>RZ/N1D         <ul> <li>400LFBGA、17×17mm、0.8mm ピッチ</li> <li>324LFBGA、15×15mm、0.8mm ピッチ</li> </ul> </li> <li>RZ/N1S         <ul> <li>324LFBGA、15×15mm、0.8mm ピッチ</li> <li>196LFBGA、12×12mm、0.8mm ピッチ</li> </ul> </li> <li>RZ/N1L         <ul> <li>196LFBGA、12×12mm、0.8mm ピッチ</li> </ul> </li> </ul>                                                                                                                                                                      |

## 1.3 製品ファミリ/パッケージ別機能比較

表 1.2 ルネサス CPU サブシステム

| ハードウェア機能                    |                                |            | RZ/            | N1D                  | RZ/I                | N1S        | RZ/N1L                 |  |  |

|-----------------------------|--------------------------------|------------|----------------|----------------------|---------------------|------------|------------------------|--|--|

|                             | パッケージ                          | ジタイプ:      | 400BGA         | 324BGA               | 324BGA              | 196BGA     | 196BGA                 |  |  |

| Processor Unit              | Arm Cortex-A7                  |            | デュ             | アル                   | シン                  | グル         | _                      |  |  |

| Arm Cortex-M3               |                                |            | 使用可能           |                      |                     |            |                        |  |  |

| Memory Unit                 | 2 MB with ECC                  |            |                |                      | 使用可能                |            |                        |  |  |

|                             | 4 MB with ECC                  |            | _              | _                    |                     | 使用可能       |                        |  |  |

|                             | DDR メモリコン                      | ノトローラ      | 使用可            | 可能 <sup>注 1</sup>    |                     | _          |                        |  |  |

|                             | Quad SPI                       |            | 10             | ch                   | 2ch                 | 1ch        | l <sup>注 2</sup>       |  |  |

|                             | SDIO/SD/eMM0                   | )          |                |                      | 2ch                 |            |                        |  |  |

|                             | NAND Flash                     |            |                |                      | 使用可能                |            |                        |  |  |

| Networking                  | R-IN Engine & I                | HWRTOS     |                |                      | 使用可能 <sup>注 5</sup> |            |                        |  |  |

| elements                    | Ethernet ポート                   | 数          | 5 ポート          | 3 ポート <sup>注 3</sup> | 5 ポート               | 3 ポー       | - ト <sup>注 3</sup>     |  |  |

|                             | 独立した GMAC                      |            | 最大 2           | 使用不可注4               | 最大 2                | 最大         | 1 注 4                  |  |  |

|                             | EtherCAT Slave                 | Controller |                |                      | 使用可能注6 注7           |            |                        |  |  |

|                             | SercosIII Slave                | Controller |                |                      | 使用可能注6 注7           |            |                        |  |  |

|                             | Advanced 5port                 | Switch     | 5 ポート<br>(4+1) | 4 ポート<br>(3+1)       | 5 ポート<br>(4+1)      | 3 ポ<br>(2+ | ート<br>1) <sup>注7</sup> |  |  |

|                             |                                | PRP        | オプション          | _                    | 使用可能                | -          | _                      |  |  |

|                             | HSR Switch 注 5                 | 注 6        | オプション          |                      | _                   |            |                        |  |  |

| Peripheral Group            | ADC                            |            | 2ユニット          |                      | 1 ユニット              |            |                        |  |  |

|                             | RTC                            |            |                | ·<br>使用              | 可能                  |            | 使用不可                   |  |  |

|                             | DMAC                           |            | 2ch            |                      |                     |            |                        |  |  |

|                             | UART                           |            | 8ch            |                      |                     |            |                        |  |  |

|                             | I <sup>2</sup> C               |            | 2ch            |                      |                     |            |                        |  |  |

|                             | Parallel bus Master & Slave 注8 |            |                | スレーブのみ               |                     |            |                        |  |  |

|                             | USB Host & Fu                  | nction     |                |                      |                     |            |                        |  |  |

|                             | Mailbox                        |            |                | 使用可能                 |                     |            |                        |  |  |

|                             | Watchdog for C                 | A7         | 使用可            | 使用可能、2 使用可能、1        |                     |            | 使用不可                   |  |  |

|                             | Watchdog for C                 | M3         |                |                      |                     |            |                        |  |  |

|                             | SPI マスタ                        |            | 4ch            |                      |                     |            |                        |  |  |

|                             | SPI スレーブ                       |            | 2ch            |                      |                     |            |                        |  |  |

|                             | CAN                            |            |                | 2ch                  |                     |            |                        |  |  |

|                             | LCDC                           |            | 使用可能使用不可       |                      |                     |            |                        |  |  |

|                             | Semaphore                      |            | 使用可能           |                      |                     |            |                        |  |  |

|                             | Timer block                    |            | 2ユニット          |                      |                     |            |                        |  |  |

|                             | PWMTimer                       |            |                |                      | 使用可能                |            |                        |  |  |

| GPIO 端子数 <sup>注 9</sup>     |                                |            | 170            | 132                  | 160                 | 95         | 95                     |  |  |

| セキュリティ機能<br><sup>注 10</sup> |                                |            |                | オプシ                  | ション                 |            | _                      |  |  |

- 注1. RZ/N1D-324 はチップセレクトおよび ODT が 1 つとなります。

- 注2. RZ/N1S-196 および RZ/N1L はチップセレクトが 2 つのみとなります。

- 注3. 使用できないポートの詳細については Ethernet インタフェースモードの制限の章を参照ください。

- 注4. GMAC2 は RZ/N1D-324、RZ/N1S-196、および RZ/N1L において A5PSW 経由で使用できます。

- 注5. HW-RTOS と HSR は同時に使用できません。

- 注6. SERCOSIII、ETHERCAT、および HSR 機能は同時に使用できません。

- 注7. A5PSW、SERCOSIII、および ETHERCAT 機能は RZ/N1S-196 および RZ/N1L において同時に使用できません。

- 注8. RZ/N1D-324 は 32 ビットモードを使用できません。RZ/N1S-196 および RZ/N1L は 8 ビットモードかつ 2 外部ウエイトリクエストのみ使用できます。RZ/N1S-196 のマスタは ALE シリアルモードのみ使用できます。

- 注9. 周辺機能の信号と共用されています。

- 注10. オプションのセキュリティ機能に関する情報は、弊社営業窓口にお問い合わせください。

## 1.4 製品一覧

表 1.3 製品一覧

| 名称     | P/N           | パッケージ  | メイン CPU        | PRP/HSR | セキュリティ |

|--------|---------------|--------|----------------|---------|--------|

| RZ/N1D | R9A06G032VGBG | 400BGA | デュアル Cortex-A7 | _       | _      |

|        | R9A06G032EGBG |        |                |         | 使用可能   |

|        | R9A06G032VGBA | 324BGA |                |         | _      |

|        | R9A06G032EGBA |        |                |         | 使用可能   |

|        | R9A06G032NGBG | 400BGA |                | PRP/HSR | _      |

|        | R9A06G032PGBG |        |                |         | 使用可能   |

| RZ/N1S | R9A06G033VGBA | 196BGA | シングル Cortex-A7 | _       | _      |

|        | R9A06G033EGBA |        |                |         | 使用可能   |

|        | R9A06G033NGBG | 324BGA |                | PRP     | _      |

|        | R9A06G033PGBG |        |                |         | 使用可能   |

| RZ/N1L | R9A06G034VGBA | 196BGA | Cortex-M3      | _       | _      |

## 1.5 ブロック図

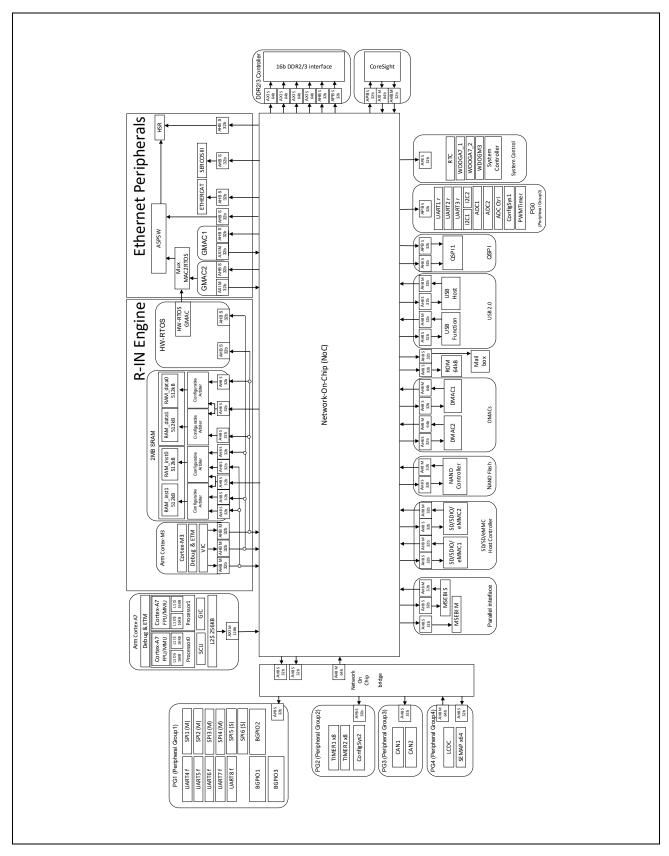

図 1.1 RZ/N1D デュアル Cortex-A7 & Cortex-M3

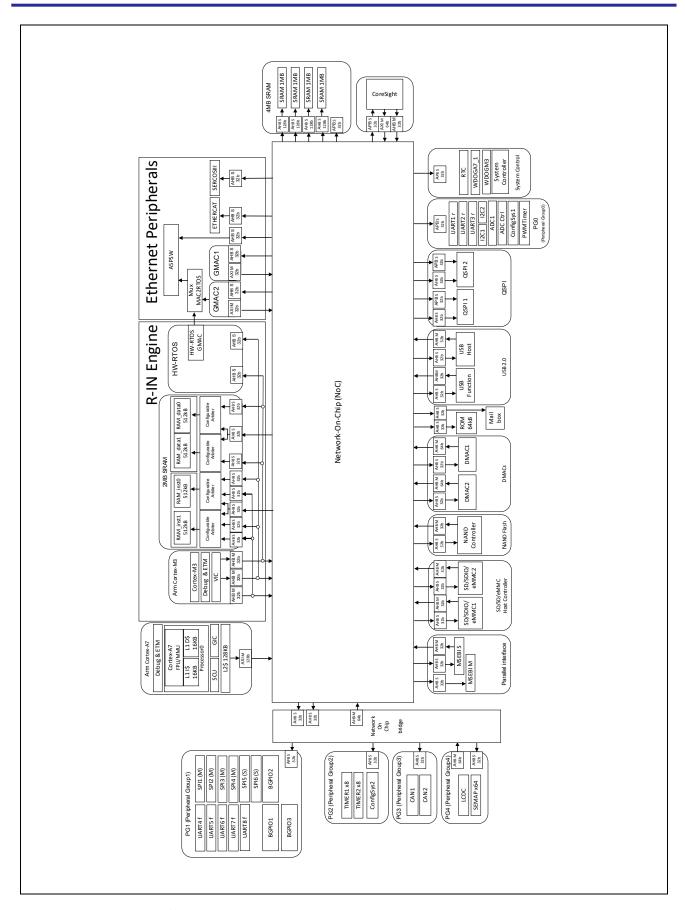

図 1.2 RZ/N1S シングル Cortex-A7 & Cortex-M3

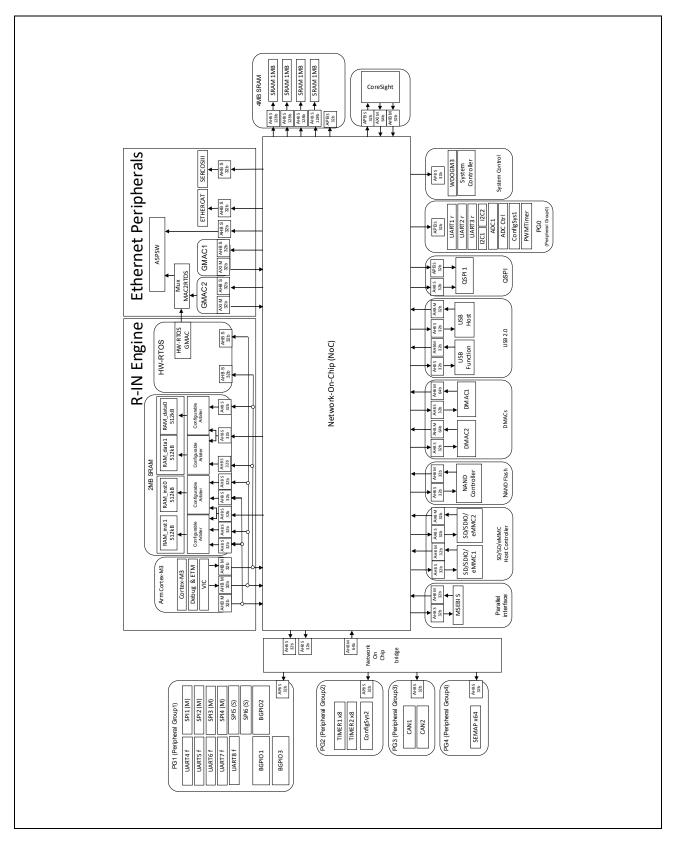

図 1.3 RZ/N1L Cortex-M3

## 第2章 アドレス空間

#### 2.1 メモリマップ

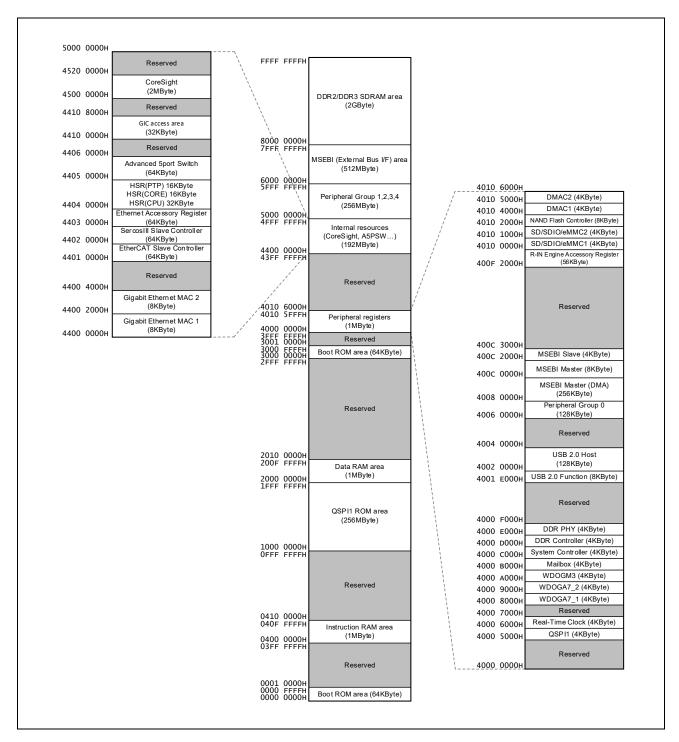

#### 2.1.1 RZ/N1D

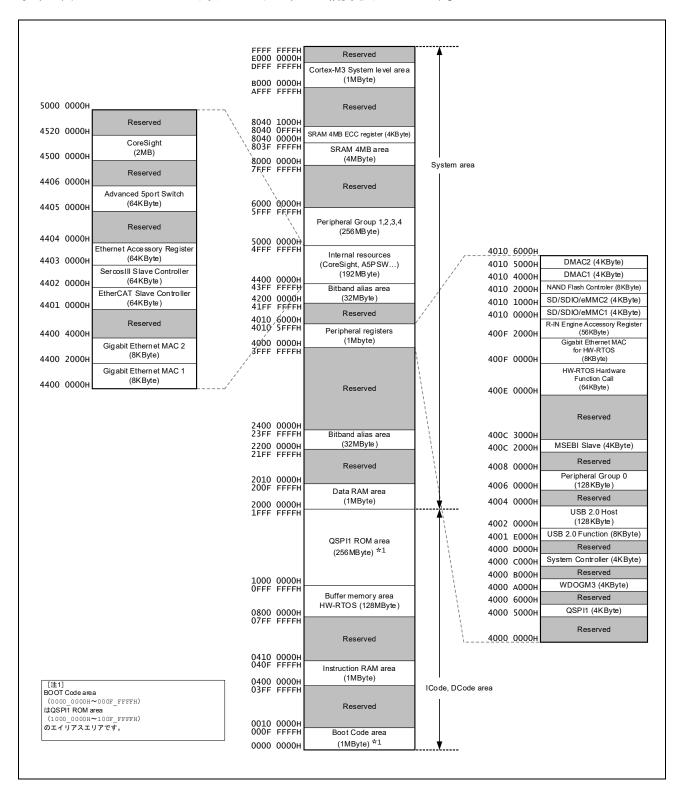

以下の図は Arm Cortex-A7 から見たメモリマップの概要を示しています。

図 2.1 RZ/N1D (Cortex-A7) のメモリマップ

以下の図は Arm Cortex-M3 から見たメモリマップの概要を示しています。

図 2.2 RZ/N1D (Cortex-M3) のメモリマップ

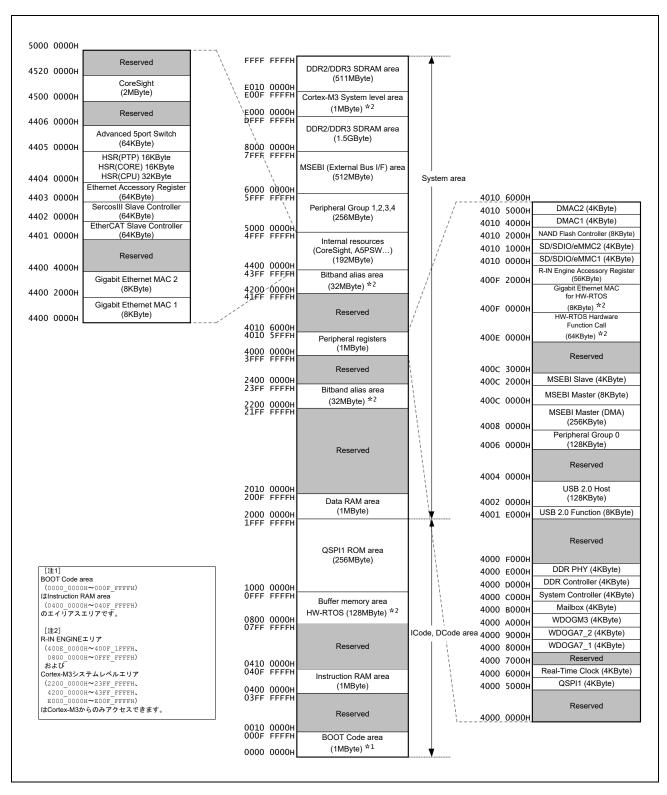

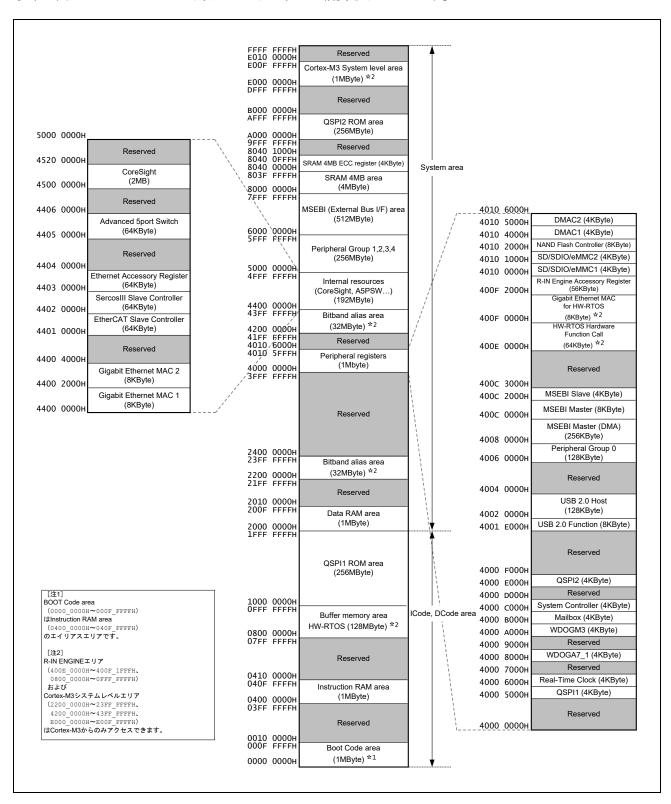

#### 2.1.2 RZ/N1S

以下の図は Arm Cortex-A7 から見たメモリマップの概要を示しています。

図 2.3 RZ/N1S (Cortex-A7) のメモリマップ

以下の図は Arm Cortex-M3 から見たメモリマップの概要を示しています。

図 2.4 RZ/N1S (Cortex-M3) のメモリマップ

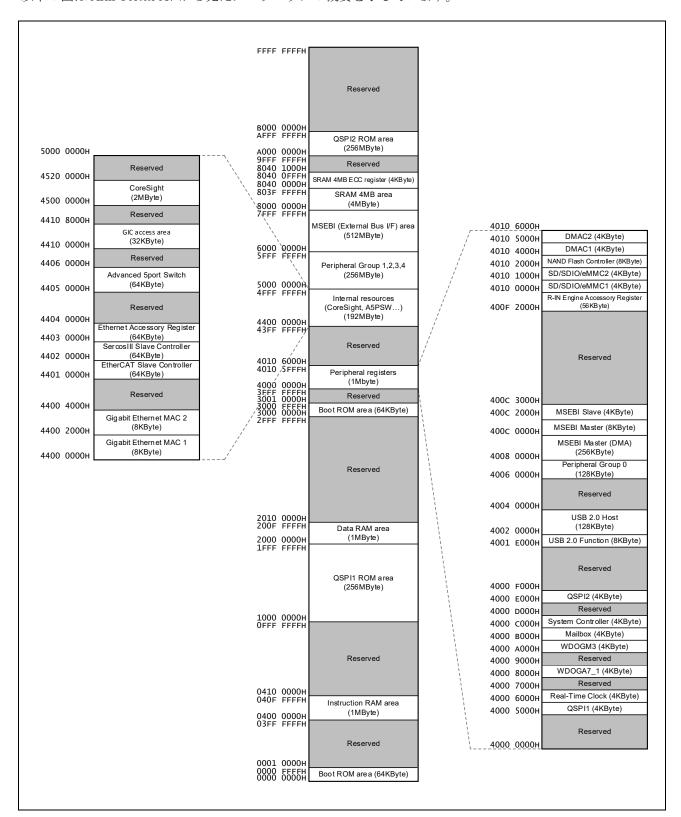

#### 2.1.3 RZ/N1L

以下の図は Arm Cortex-M3 から見たメモリマップの概要を示しています。

図 2.5 RZ/N1L のメモリマップ

## 2.2 レジスタマップサマリ

以下のレジスタマップはすべての RZ/N1 グループ内の周辺機能のベースアドレスをカバーしています。 『〇』マークがないモジュールにはアクセスしないでください。

#### 表 2.1 レジスタマップ(1/2)

| 開始アドレス    | 周辺機能                                                                   | RZ/N1D-400 | RZ/N1D-324 | RZ/N1S-324 | RZ/N1S-196 | RZ/N1L |

|-----------|------------------------------------------------------------------------|------------|------------|------------|------------|--------|

| 4000_5000 | Quad SPI Controller1 (QSPI1)                                           | 0          | 0          | 0          | 0          | 0      |

| 4000_6000 | Real-Time Clock (RTC)                                                  | 0          | 0          | 0          | 0          | ×      |

| 4000_8000 | Watchdog for CA7 processor0 (WDOGA7_1)                                 | 0          | 0          | 0          | 0          | ×      |

| 4000_9000 | Watchdog for CA7 processor1 (WDOGA7_2)                                 | 0          | 0          | ×          | ×          | ×      |

| 4000_A000 | Watchdog for CM3 (WDOGCM3)                                             | 0          | 0          | 0          | 0          | 0      |

| 4000_B000 | Mailbox (IPCM)                                                         | 0          | 0          | 0          | 0          | ×      |

| 4000_C000 | System Controller                                                      | 0          | 0          | 0          | 0          | 0      |

| 4000_D000 | DDR2/3 Controller                                                      | 0          | 0          | _          | _          | _      |

| 4000_E000 | DDR2/3 PHY                                                             | 0          | 0          | _          | _          | _      |

|           | Quad SPI Controller2 (QSPI2)                                           |            | _          | 0          | ×          | ×      |

| 4001_E000 | USB 2.0 HS Function Controller (USBf) / EPC                            | 0          | 0          | 0          | 0          | 0      |

| 4001_F000 | USB 2.0 HS Function Controller (USBf) / AHB-EPC Bridge                 | 0          | 0          | 0          | 0          | 0      |

| 4002_0000 | USB 2.0 HS Host Controller (USBh) / OHCl Operation                     | 0          | 0          | 0          | 0          | 0      |

| 4002_1000 | USB 2.0 HS Host Controller (USBh) / EHCl Operation                     | 0          | 0          | 0          | 0          | 0      |

| 4003_0000 | USB 2.0 HS Host Controller (USBh) / AHB PCI Bridge (PCI Config. Space) | 0          | 0          | 0          | 0          | 0      |

| 4003_0000 | USB 2.0 HS Host Controller (USBh) / OHCl (PCl Config. Space)           | 0          | 0          | 0          | 0          | 0      |

| 4003_0100 | USB 2.0 HS Host Controller (USBh) / EHCl (PCl Config. Space)           | 0          | 0          | 0          | 0          | 0      |

| 4003_0800 | USB 2.0 HS Host Controller (USBh) / AHB PCI Bridge (PCI Com. Space)    |            | 0          | 0          | 0          | 0      |

| 4006_0000 | UART1                                                                  |            | 0          | 0          | 0          | 0      |

| 4006_1000 | UART2                                                                  | 0          | 0          | 0          | 0          | 0      |

| 4006_2000 | UART3                                                                  | 0          | 0          | 0          | 0          | 0      |

| 4006_3000 | I2C1                                                                   |            | 0          | 0          | 0          | 0      |

| 4006_4000 | I2C2                                                                   |            | 0          | 0          | 0          | 0      |

| 4006_5000 | ADC Controller / 12bit A/D Converters                                  | 0          | 0          | 0          | 0          | 0      |

| 4006_7000 | ConfigSys1                                                             | 0          | 0          | 0          | 0          | 0      |

| 4006_8000 | PWMTimer                                                               | 0          | 0          | 0          | 0          | 0      |

| 4008_0000 | MSEBI / Master (MSEBIM) From DMA                                       | 0          | 0          | 0          | 0          | ×      |

| 400C_0000 | MSEBI / Master (MSEBIM) From CPU                                       | 0          | 0          | 0          | 0          | ×      |

| 400C_1000 | MSEBI / Slave (MSEBIS) From MSEBI                                      |            | 0          | 0          | 0          | 0      |

| 400C_2000 | MSEBI / Slave (MSEBIS) From CPU                                        |            | 0          | 0          | 0          | 0      |

| 400E_0000 | HW-RTOS Hardware Function Call                                         |            | 0          | 0          | 0          | 0      |

| 400F_0000 | Gigabit Ethernet MAC for HW-RTOS (HW-RTOS GMAC)                        |            | 0          | 0          | 0          | 0      |

| 400F_2000 | R-IN Engine Accessory Register                                         |            | 0          | 0          | 0          | 0      |

| 4010_0000 | SD/SDIO/eMMC Controller1 (SDIO1)                                       |            | 0          | 0          | 0          | 0      |

| 4010_1000 | SD/SDIO/eMMC Controller2 (SDIO2)                                       | 0          | 0          | 0          | 0          | 0      |

| 4010_2000 | NAND Flash Controller                                                  | 0          | 0          | 0          | 0          | 0      |

| 4010_4000 | DMAC1                                                                  | 0          | 0          | 0          | 0          | 0      |

| 4010_5000 | DMAC2                                                                  | 0          | 0          | 0          | 0          | 0      |

表 2.1 レジスタマップ (2/2)

| 開始アドレス    | 周辺機能                                   | RZ/N1D-400 | RZ/N1D-324 | RZ/N1S-324 | RZ/N1S-196 | RZ/N1L |

|-----------|----------------------------------------|------------|------------|------------|------------|--------|

| 4400_0000 | Gigabit Ethernet MAC1 (GMAC1)          | 0          | ×          | 0          | 0          | 0      |

| 4400_2000 | Gigabit Ethernet MAC2 (GMAC2)          | 0          | 0          | 0          | 0          | 0      |

| 4401_0000 | EtherCAT Slave Controller (ETHERCAT)   | 0          | 0          | 0          | 0          | 0      |

| 4402_0000 | SercosIII Slave Controller (SERCOSIII) | 0          | 0          | 0          | 0          | 0      |

| 4403_0000 | Ethernet Accessory Register            | 0          | 0          | 0          | 0          | 0      |

| 4404_0000 | HSR Switch / CPU                       | 注 1        | _          | _          | _          | _      |

| 4404_8000 | HSR Switch / CORE                      | 注 1        | _          | _          | _          | _      |

| 4404_C000 | HSR Switch / PTP                       | 注 1        | _          | _          | _          | _      |

| 4405_0000 | Advanced 5port Switch (A5PSW)          | 0          | 0          | 0          | 0          | 0      |

| 5000_0000 | UART4                                  | 0          | 0          | 0          | 0          | 0      |

| 5000_1000 | UART5                                  | 0          | 0          | 0          | 0          | 0      |

| 5000_2000 | UART6                                  | 0          | 0          | 0          | 0          | 0      |

| 5000_3000 | UART7                                  | 0          | 0          | 0          | 0          | 0      |

| 5000_4000 | UART8                                  | 0          | 0          | 0          | 0          | 0      |

| 5000_5000 | SPI1 (Master)                          |            | 0          | 0          | 0          | 0      |

| 5000_6000 | SPI2 (Master)                          |            | 0          | 0          | 0          | 0      |

| 5000_7000 | SPI3 (Master)                          |            | 0          | 0          | 0          | 0      |

| 5000_8000 | SPI4 (Master)                          |            | 0          | 0          | 0          | 0      |

| 5000_9000 | SPI5 (Slave)                           | 0          | 0          | 0          | 0          | 0      |

| 5000_A000 | SPI6 (Slave)                           | 0          | 0          | 0          | 0          | 0      |

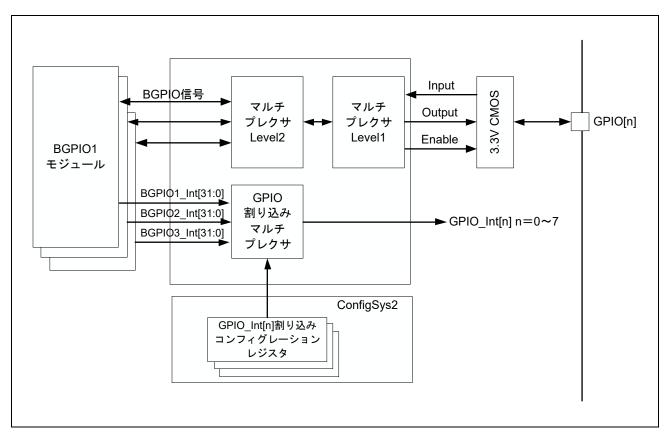

| 5000_B000 | BGPIO1                                 | 0          | 0          | 0          | 0          | 0      |

| 5000_C000 | BGPIO2                                 | 0          | 0          | 0          | 0          | 0      |

| 5000_D000 | BGPIO3                                 | 0          | 0          | 0          | ×          | ×      |

| 5100_0000 | ConfigSys2                             | 0          | 0          | 0          | 0          | 0      |

| 5100_1000 | Timer Block1 (TIMER1)                  | 0          | 0          | 0          | 0          | 0      |

| 5100_2000 | Timer Block2 (TIMER2)                  | 0          | 0          | 0          | 0          | 0      |

| 5210_4000 | CAN1                                   |            | 0          | 0          | 0          | 0      |

| 5210_5000 | CAN2                                   | 0          | 0          | 0          | 0          | 0      |

| 5300_0000 | Semaphore (SEMAP)                      |            | 0          | 0          | 0          | 0      |

| 5300_4000 | LCD Controller (LCDC)                  | 0          | 0          | 0          | ×          | ×      |

注1. HSR はオプションです。

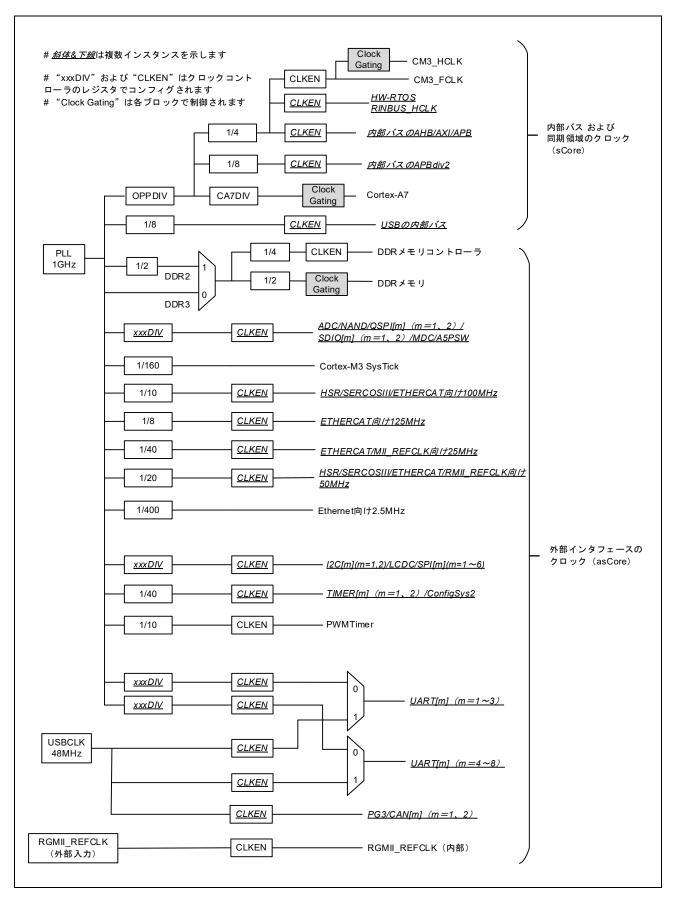

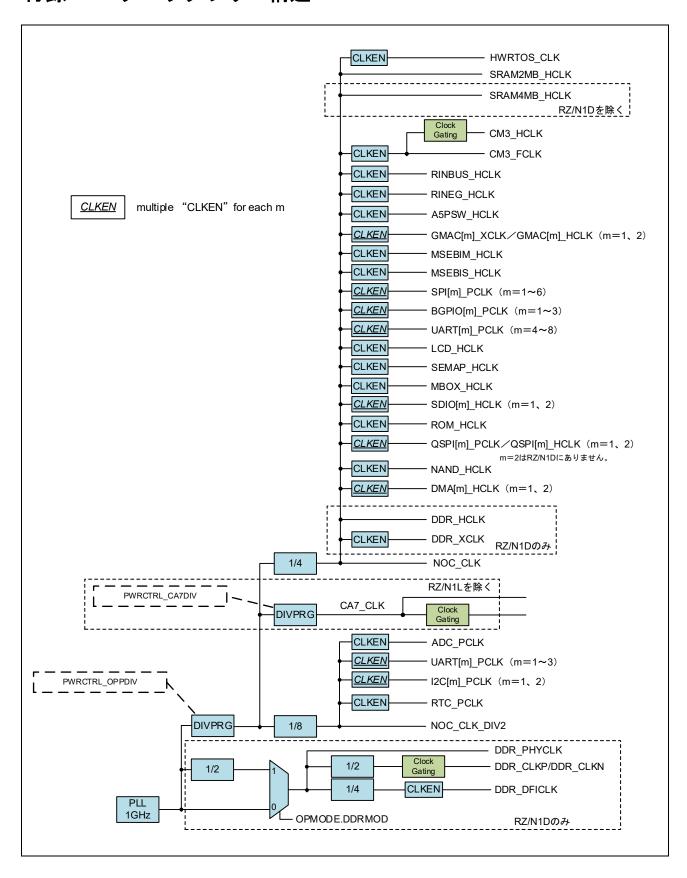

## 第3章 クロック生成

## 3.1 概要

RZ/N1 は 3 つのクロックソースと 1 つの RGMII のリファレンスクロック入力と 1 つの RMII/MII のリファレンスクロック出力を持っています。

システムコントローラはクロックコントローラ向けのレジスタを含んでいます。これによりパワーマネージメントソフトウェアはクロックゲーティング、クロック選択そしてクロック分周機能のコントロールをすることが可能です。

表 3.1 クロック生成仕様

| 項目                     | 仕様                                                                 |

|------------------------|--------------------------------------------------------------------|

| メインクロックオシレータ           | 共振周波数:40MHz                                                        |

|                        | 外部クロック入力周波数:40MHz                                                  |

|                        | このシステムのメインクロックソース。外部クロック入力モードも使用可能です。                              |

| RTC クロックオシレータ          | 共振周波数:32.768kHz                                                    |

|                        | RTC のクロックソース。RTC 専用パワードメインに属しています。                                 |

| JTAG(JTAG_TCK)のため      | 入力周波数:10MHz(最大)                                                    |

| のクロック入力                | CoreSight®と JTAG コントローラのためのクロック。                                   |

| PLL                    | 入力クロックソース:メインクロックオシレータ                                             |

|                        | 出カクロック周波数:1000MHz                                                  |

|                        | このシステムのメイン PLL。                                                    |

| USBPLL                 | 入力クロックソース:メインクロックオシレータ                                             |

|                        | 出カクロック周波数: 480MHz                                                  |

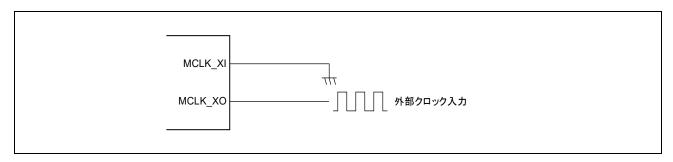

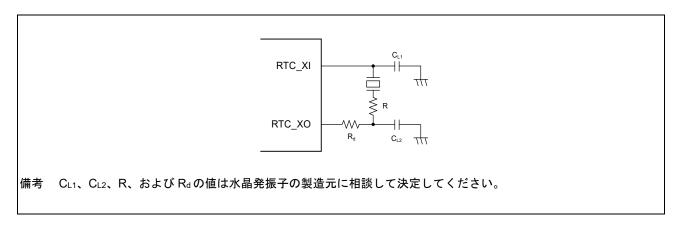

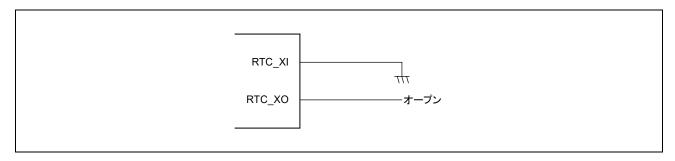

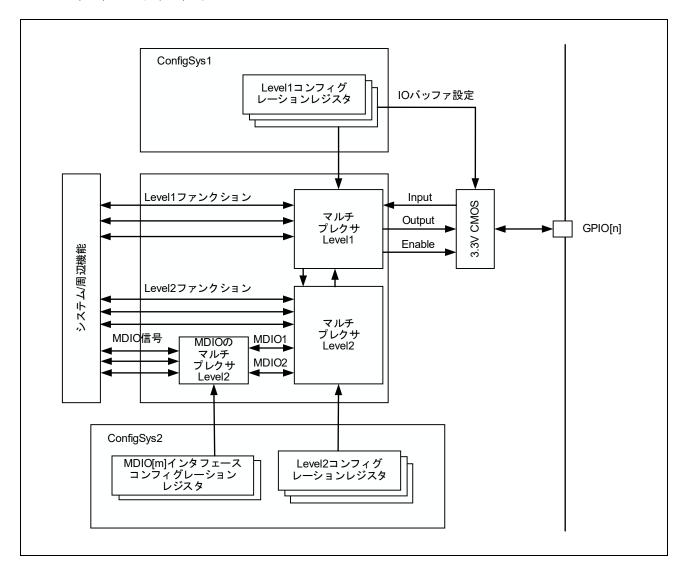

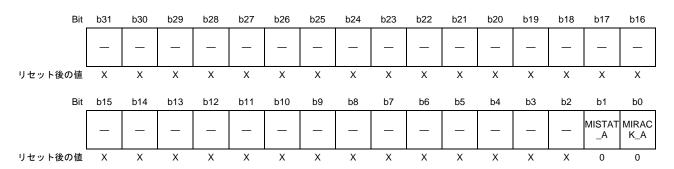

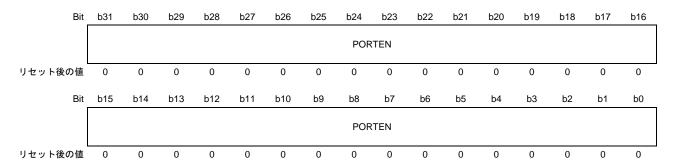

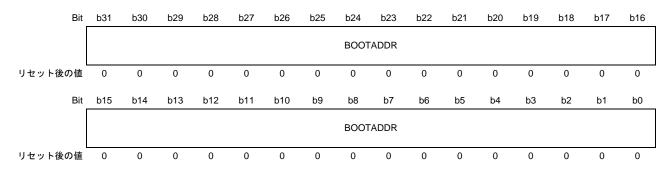

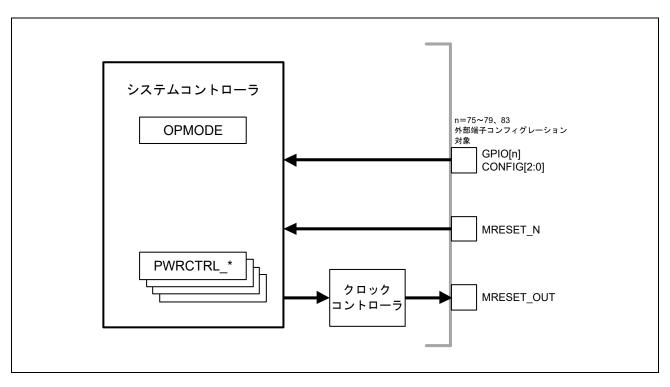

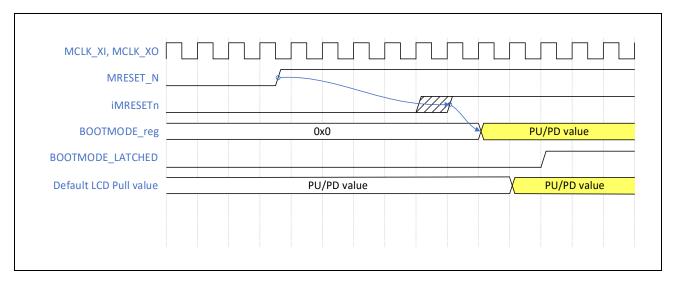

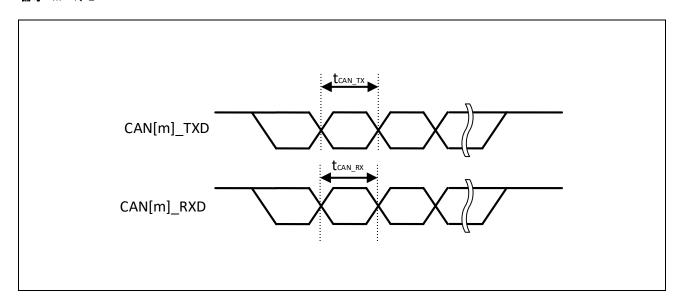

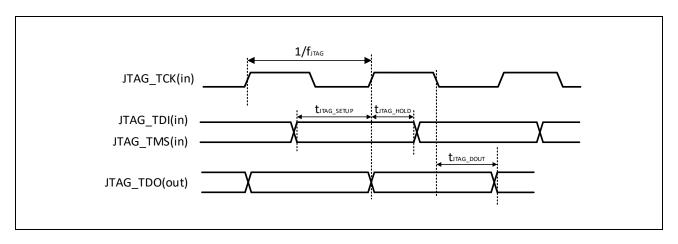

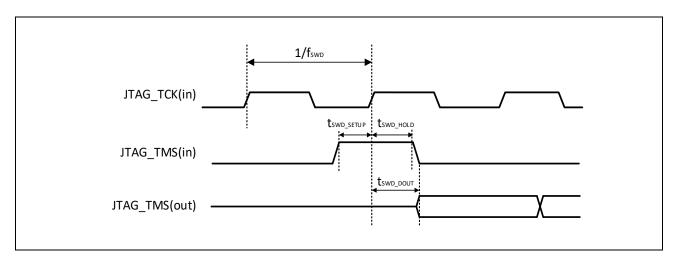

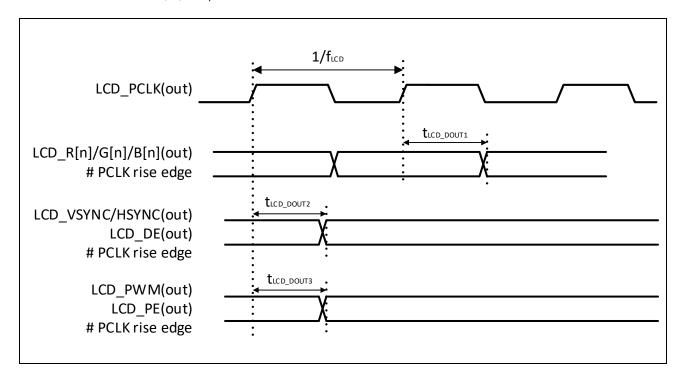

|                        | USBPHY の PLL。480MHz の 1/10 の 48MHz がシステムに供給されます。デフォルトはパワーダウンモードです。 |