# **RL78/I1B**

ユーザーズマニュアル ハードウェア編

16 ビット・シングルチップ・マイクロコントローラ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

## ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。回路、ソフトウェアおよびこれらに関連する情報を使用する場合、お客様の責任において、お客様の機器・システムを設計ください。これらの使用に起因して生じた損害(お客様または第三者いずれに生じた損害も含みます。以下同じです。)に関し、当社は、一切その責任を負いません。

- 2. 当社製品または本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、 著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行うものではなく、また責任を負うものではあり ません。

- 3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を組み込んだ製品の輸出入、製造、販売、利用、配布その他の行為を行うにあたり、第三者保有の技術の利用に関するライセンスが必要となる場合、当該ライセンス取得の判断および取得はお客様の責任において行ってください。

- 5. 当社製品を、全部または一部を問わず、改造、改変、複製、リバースエンジニアリング、その他、不適切に使用しないでください。かかる改造、改変、 複製、リバースエンジニアリング等により生じた損害に関し、当社は、一切その責任を負いません。

- 6. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通制御(信号)、大規模通信機器、金融端末基幹システム、各種安全制御装置等

当社製品は、データシート等により高信頼性、Harsh environment 向け製品と定義しているものを除き、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(宇宙機器と、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等)に使用されることを意図しておらず、これらの用途に使用することは想定していません。たとえ、当社が想定していない用途に当社製品を使用したことにより損害が生じても、当社は一切その責任を負いません。

- 7. あらゆる半導体製品は、外部攻撃からの安全性を 100%保証されているわけではありません。当社ハードウェア/ソフトウェア製品にはセキュリティ 対策が組み込まれているものもありますが、これによって、当社は、セキュリティ脆弱性または侵害(当社製品または当社製品が使用されているシステムに対する不正アクセス・不正使用を含みますが、これに限りません。)から生じる責任を負うものではありません。当社は、当社製品または当社製品が使用されたあらゆるシステムが、不正な改変、攻撃、ウイルス、干渉、ハッキング、データの破壊または窃盗その他の不正な侵入行為(「脆弱性問題」といいます。)によって影響を受けないことを保証しません。当社は、脆弱性問題に起因しまたはこれに関連して生じた損害について、一切責任を負いません。また、法令において認められる限りにおいて、本資料および当社ハードウェア/ソフトウェア製品について、商品性および特定目的との合致に関する保証ならびに第三者の権利を侵害しないことの保証を含め、明示または黙示のいかなる保証も行いません。

- 8. 当社製品をご使用の際は、最新の製品情報(データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等)をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は、データシート等において高信頼性、Harsh environment 向け製品と定義しているものを除き、耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 10. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。当社製品および技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定めるところに従い必要な手続きを行ってください。

- 12. お客様が当社製品を第三者に転売等される場合には、事前に当該第三者に対して、本ご注意書き記載の諸条件を通知する責任を負うものといたします。

- 13. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 14. 本資料に記載されている内容または当社製品についてご不明な点がございましたら、当社の営業担当者までお問合せください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社が直接的、間接的に 支配する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

(Rev.5.0-1 2020.10)

## 本社所在地

〒 135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

www.renesas.com

# 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の 商標です。すべての商標および登録商標は、それぞれの所有者に帰属し ます。

## お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄の営業お問合せ窓口 に関する情報などは、弊社ウェブサイトをご覧ください。

www.renesas.com/contact/

## 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本ドキュメントおよびテクニカルアップデートを参照してください。

#### 1. 静電気対策

CMOS 製品の取り扱いの際は静電気防止を心がけてください。CMOS 製品は強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジンケース、導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、CMOS 製品を実装したボードについても同様の扱いをしてください。

#### 2. 電源投入時の処置

電源投入時は、製品の状態は不定です。電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

#### 3. 電源オフ時における入力信号

当該製品の電源がオフ状態のときに、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源オフ時における入力信号」についての記載のある製品は、その内容を守ってください。

#### 4. 未使用端子の処理

未使用端子は、「未使用端子の処理」に従って処理してください。CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。

#### 5. クロックについて

リセット時は、クロックが安定した後、リセットを解除してください。プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 6. 入力端子の印加波形

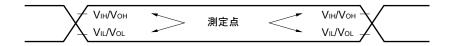

入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。CMOS 製品の入力がノイズなどに起因して、 $V_{\rm IL}$  (Max.) から  $V_{\rm IH}$  (Min.) までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定の場合はもちろん、 $V_{\rm IL}$  (Max.) から  $V_{\rm IH}$  (Min.) までの領域を通過する遷移期間中にチャタリングノイズなどが入らないように使用してください。

#### 7. リザーブアドレス (予約領域) のアクセス禁止

リザーブアドレス (予約領域) のアクセスを禁止します。アドレス領域には、将来の拡張機能用に割り付けられている リザーブアドレス (予約領域) があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 8. 製品間の相違について

型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。同じグループのマイコンでも型名が違うと、フラッシュメモリ、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ幅射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

# このマニュアルの使い方

- 対 象 者 このマニュアルはRL78/I1Bの機能を理解し、その応用システムや応用プログラムを設計、開発するユーザのエンジニアを対象としています。

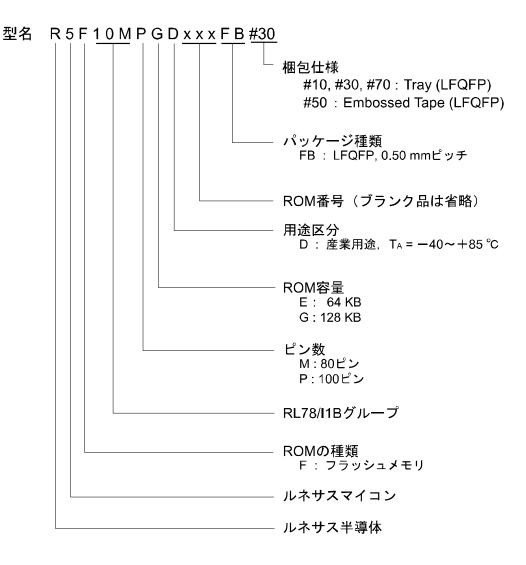

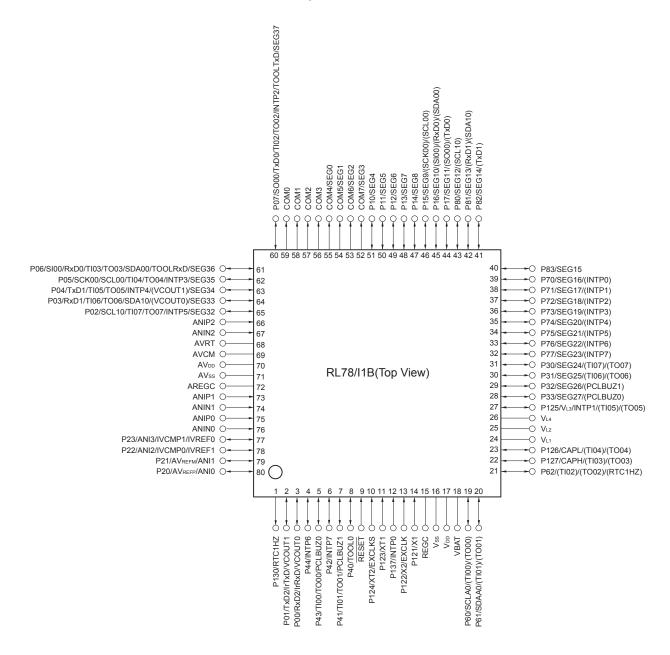

- 80ピン製品: R5F10MME, R5F10MMG

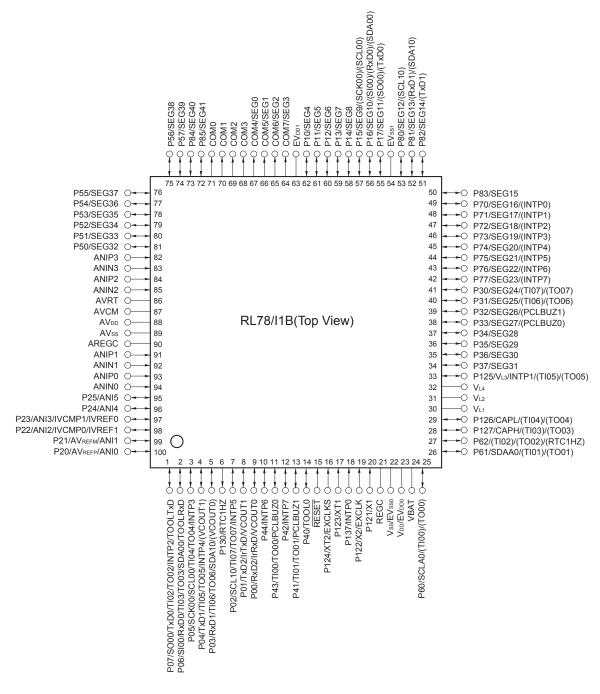

- 100ピン製品: R5F10MPE, R5F10MPG

- 目 的 このマニュアルは、次の構成に示す機能をユーザに理解していただくことを目的としています。

- 構 成 RL78/I1Bのマニュアルは、このマニュアルと命令編(RL78ファミリ共通)の2冊に分かれています。

RL78/l1B ユーザーズ・マニュアル ハードウェア編

- ●端子機能

- ●内部ブロック機能

- ●割り込み

- ●その他の内蔵周辺機能

- ●電気的特性

RL78ファミリ ユーザーズ・マニュアル ソフトウェア編

- ●CPU機能

- ●命令セット

- ●命令の説明

- 読 み 方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコントローラの一般知識を必要とします。

- □一通りの機能を理解しようとするとき

- →目次に従って読んでください。

本文欄外の★印は、本版で改訂された主な箇所を示しています。

この"★"をPDF上でコピーして「検索する文字列」に指定することによって、改版箇所を容易に 検索できます。

- □レジスタ・フォーマットの見方

- →ビット番号を口で囲んでいるものは、そのビット名称がアセンブラでは予約語に、コンパイラでは#pragma sfr指令で、sfr変数として定義されているものです。

- □RL78/I1Bマイクロコントローラの命令機能の詳細を知りたいとき

- →別冊のRL78ファミリ ユーザーズ・マニュアル ソフトウエア編 (R01US0015J) を参照して ください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記 : ××× (端子, 信号名称に上線)

注:本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数···××××または××××B

10進数…×××× 16進数…××××H

### 関連資料

関連資料は暫定版の場合がありますが、この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

### デバイスの関連資料

| 資料名                          | 資料番号   |      |        |       |

|------------------------------|--------|------|--------|-------|

|                              | 和      | 文    | 英      | 文     |

| RL78/l1B ユーザーズ・マニュアル ハードウェア編 | このマニ   | ュアル  | R01UH0 | 0407E |

| RL78ファミリ ユーザーズ・マニュアル ソフトウェア編 | R01US0 | 015J | R01US0 | 0015E |

## フラッシュ・メモリ書き込み用の資料(ユーザーズマニュアル)

| 資 料 名 |                                                          | 資料番号       |            |  |

|-------|----------------------------------------------------------|------------|------------|--|

|       |                                                          | 和 文        | 英 文        |  |

| PG-FF | 25 フラッシュメモリプログラマ ユーザーズマニュアル                              | _          | _          |  |

|       | RL78, 78K, V850, RX100, RX200, RX600 (RX64x除く), R8C, SH編 | R20UT2923J | R20UT2923E |  |

|       | 共通編                                                      | R20UT2922J | R20UT2922E |  |

|       | セットアップマニュアル                                              | R20UT0930J | R20UT0930E |  |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには、必ず最新の資料をご使用ください。

#### その他の資料

| 資 料 名                    | 資料番号       |            |  |

|--------------------------|------------|------------|--|

|                          | 和 文        | 英 文        |  |

| ルネサス マイクロコンピュータ RL78ファミリ | R01CP0003J | R01CP0003E |  |

| 半導体パッケージ 実装マニュアル         | 注          |            |  |

| 信頼性ハンドブック                | R51ZZ0001J | R51ZZ0001E |  |

注 「半導体パッケージ実装マニュアル」のホーム・ページ参照

和文:http://japan.renesas.com/products/package/index.jsp 英文:http://www.renesas.com/products/package/index.jsp

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには、必ず最新の資料をご使用ください。

すべての商標および登録商標は、それぞれの所有者に帰属します。

EEPROMは、ルネサス エレクトロニクス株式会社の登録商標です。

SuperFlashは、米国Silicon Storage Technology, Inc.の米国、日本などの国における登録商標です。

注意:本製品はSilicon Storage Technology, Inc.からライセンスを受けたSuperFlash®を使用しています。

# 目次

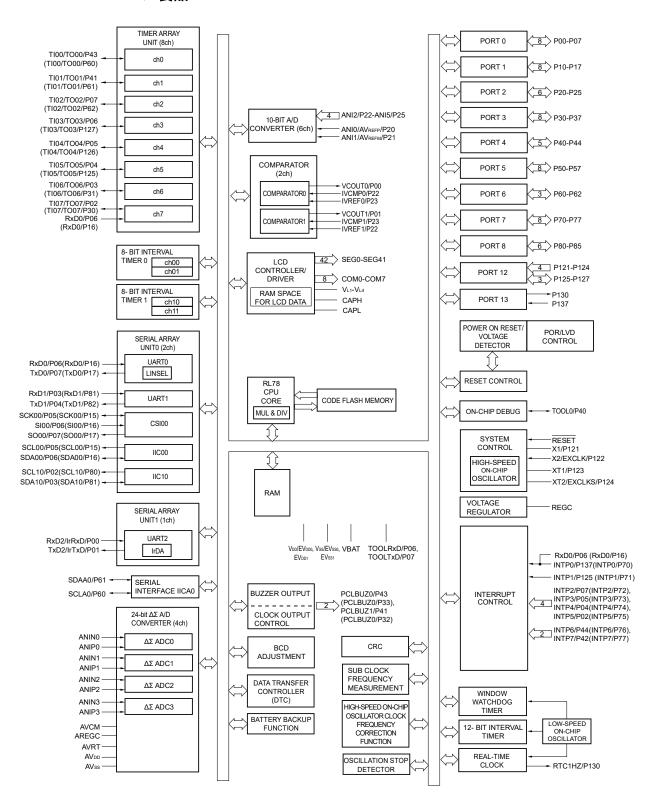

| 第1章  | 概           | 説                                       | 1  |

|------|-------------|-----------------------------------------|----|

| 1. 1 | 特           | 徵                                       | 1  |

| 1. 2 |             | <b>5</b>                                |    |

| 1. 3 |             | s続図(Top View)                           |    |

| •    |             | 80ピン製品                                  |    |

|      |             | 100ピン製品                                 |    |

| 1. 4 |             | .称                                      |    |

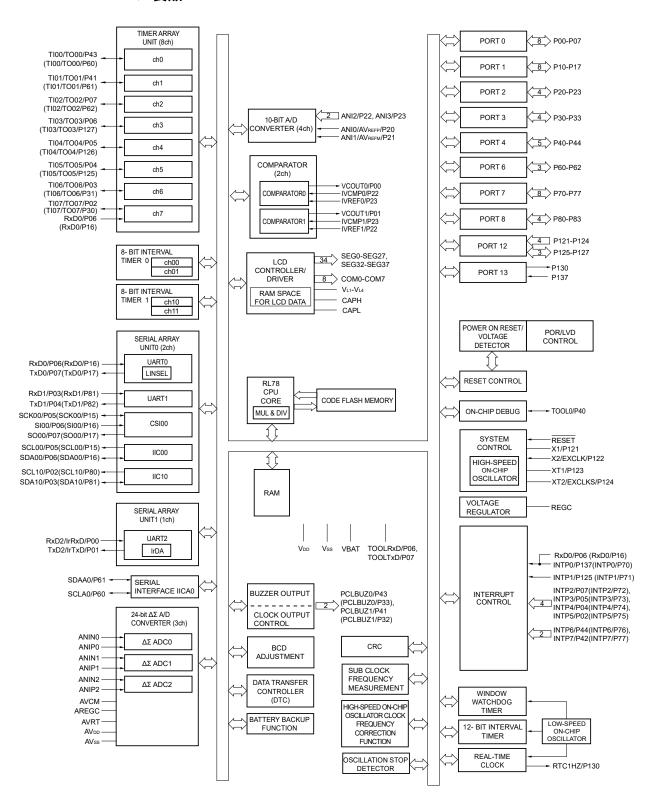

| 1. 5 |             | ・・・<br>! ク図                             |    |

|      |             | ・<br>80ピン製品                             |    |

|      |             | 100ピン製品                                 |    |

| 1. 6 |             | 要                                       |    |

|      |             |                                         |    |

| 第2章  | 端子機         | 卷能                                      | 12 |

|      |             |                                         |    |

| 2. 1 |             | 機能                                      |    |

|      |             | 80ピン製品                                  |    |

|      |             | 100ピン製品                                 |    |

| 2. 2 |             | · 以外の機能                                 |    |

|      | 2. 2. 1     | X11/3/14 / 12 44 / X/10                 |    |

|      |             | 機能説明                                    |    |

| 2. 3 |             | 引端子の処理                                  |    |

| 2. 4 | <b>ふ子</b> フ | 『ロック図                                   | 25 |

| 第3章  | CPU         | アーキテクチャ                                 | 39 |

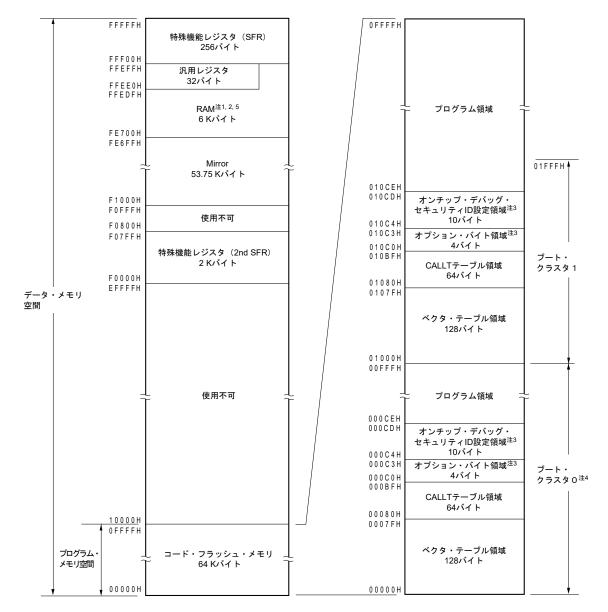

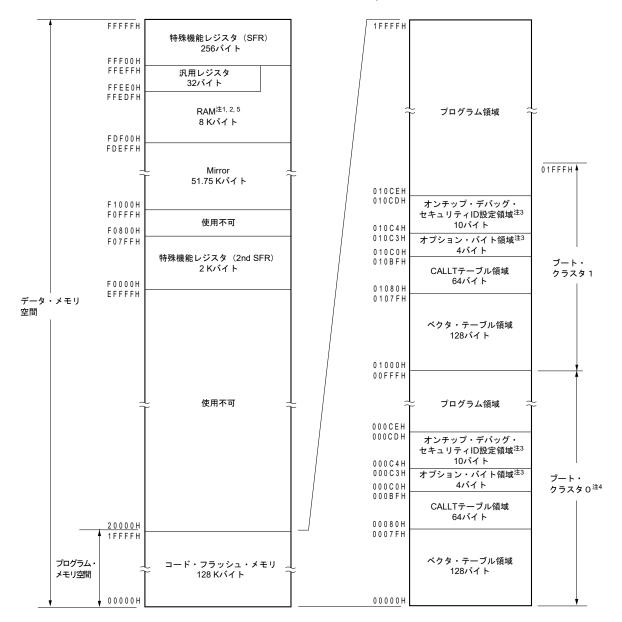

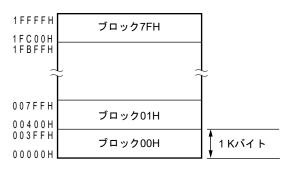

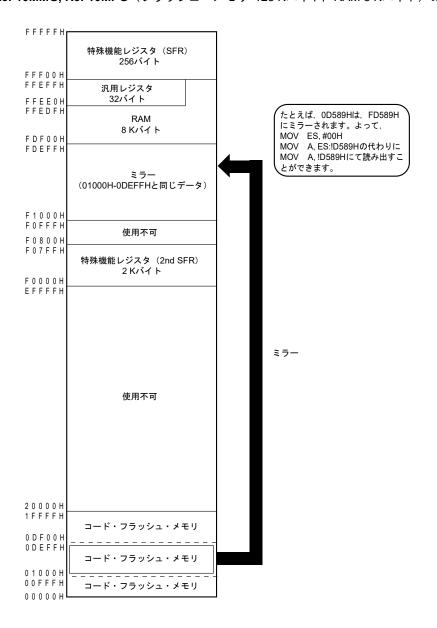

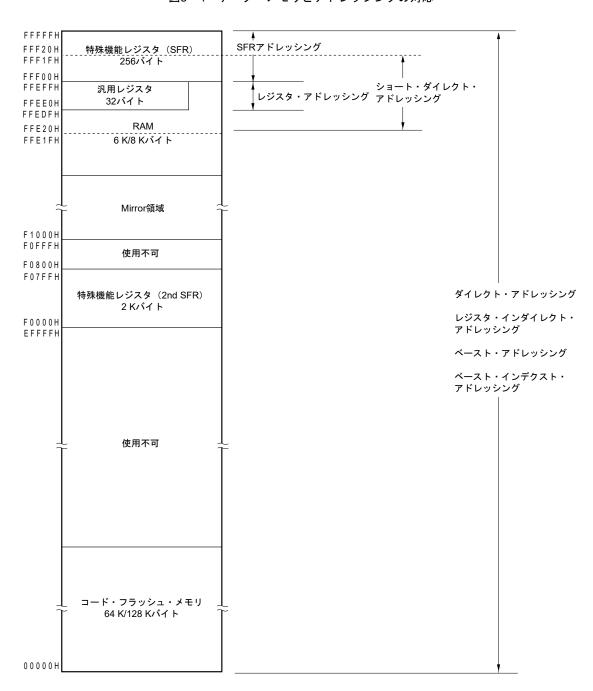

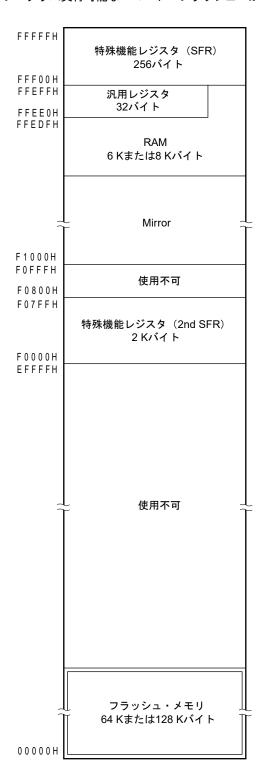

| 3 1  | メモリ         | 空間                                      | 30 |

| 5. 1 |             | 大部プログラム・メモリ空間                           |    |

|      |             | ミラー領域                                   |    |

|      | 3. 1. 3     |                                         |    |

|      | 3. 1. 4     |                                         |    |

|      | 3. 1. 5     | •                                       |    |

|      |             | データ・メモリ・アドレッシング                         |    |

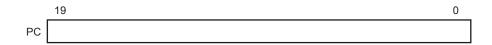

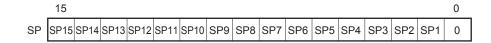

| 3. 2 |             | · · · · · · · · · · · · · · · · · · ·   |    |

| V    |             | 制御レジスタ                                  |    |

|      |             | 汎用レジスタ                                  |    |

|      | 3. 2. 3     |                                         |    |

|      | 3. 2. 4     | 特殊機能レジスタ(SFR:Special Function Register) |    |

|      | 3. 2. 5     | •                                       |    |

| 3. 3 | 命令ア         | 'ドレスのアドレッシング                            |    |

|      |             | レラティブ・アドレッシング                           |    |

|      |             | イミーディエト・アドレッシング                         |    |

|      |             | テーブル・インダイレクト・アドレッシング                    |    |

|      |             | レジスタ・ダイレクト・アドレッシング                      |    |

| 3. 4 | 処理ラ         | <sup>:</sup> ータ・アドレスに対するアドレッシング         | 73 |

|      | 3. 4. 1     | インプライド・アドレッシング                          | 73 |

|      | 3. 4. 2 レジスタ・アドレッシング                           | 73  |

|------|------------------------------------------------|-----|

|      | 3.4.3 ダイレクト・アドレッシング                            | 74  |

|      | 3.4.4 ショート・ダイレクト・アドレッシング                       | 75  |

|      | 3. 4. 5 SFRアドレッシング                             |     |

|      | 3.4.6 レジスタ・インダイレクト・アドレッシング                     |     |

|      | 3. 4. 7 ベースト・アドレッシング                           |     |

|      | 3. 4. 8 ベースト・インデクスト・アドレッシング                    |     |

|      | 3. 4. 9 スタック・アドレッシング                           |     |

|      |                                                |     |

| 第4章  | ポート機能                                          | 85  |

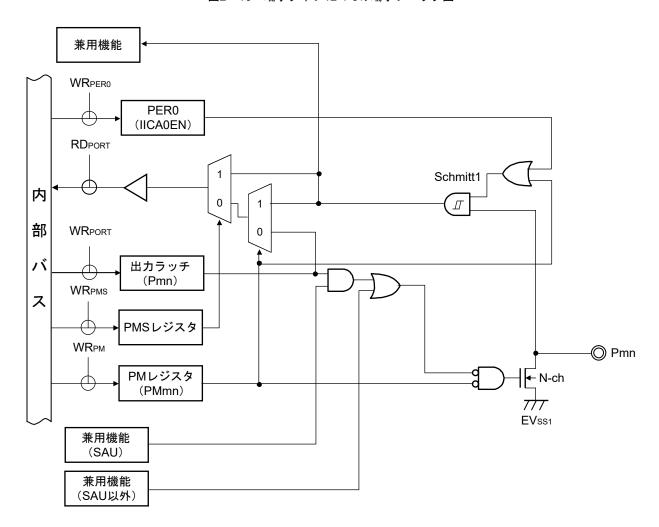

| 4. 1 | ポートの機能                                         | 85  |

| 4. 2 | ポートの構成                                         | 85  |

|      | 4. 2. 1 ポート0                                   | 86  |

|      | 4. 2. 2 ポート1                                   | 86  |

|      | 4. 2. 3 ポート2                                   | 87  |

|      | 4. 2. 4 ポート3                                   | 88  |

|      | 4. 2. 5 ポート4                                   | 88  |

|      | 4. 2. 6 ポート5                                   | 88  |

|      | 4. 2. 7 ポート6                                   | 88  |

|      | 4. 2. 8 ポート7                                   | 89  |

|      | 4. 2. 9 ポート8                                   |     |

|      | 4. 2. 10 ポート12                                 |     |

|      | 4. 2. 11 ポート13                                 |     |

| 4. 3 | ポート機能を制御するレジスタ                                 |     |

|      | 4. 3. 1 ポート・モード・レジスタ(PMxx)                     |     |

|      | 4.3.2 ポート・レジスタ (Pxx)                           |     |

|      | 4. 3. 3 プルアップ抵抗オプション・レジスタ(PUxx)                |     |

|      | 4.3.4 ポート入力モード・レジスタ(PIMxx)                     |     |

|      | 4.3.5 ポート出力モード・レジスタ(POMxx)                     |     |

|      | 4. 3. 6 A/Dポート・コンフィギュレーション・レジスタ(ADPC)          |     |

|      | 4.3.7 グローバル・デジタル・インプット・ディスエーブル・レジスタ(GDIDIS)    |     |

|      | 4.3.8 周辺I/Oリダイレクション・レジスタ(PIOR)                 |     |

|      | 4. 3. 9 LCDポート・ファンクション・レジスタ0-5 (PFSEG0-PFSEG5) |     |

|      | 4.3.10 LCD入力切り替え制御レジスタ (ISCLCD)                |     |

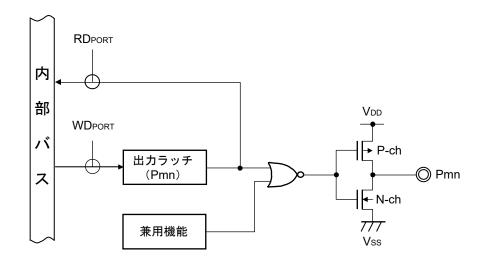

| 4. 4 | ポート機能の動作                                       |     |

|      | 4. 4. 1 入出力ポートへの書き込み                           |     |

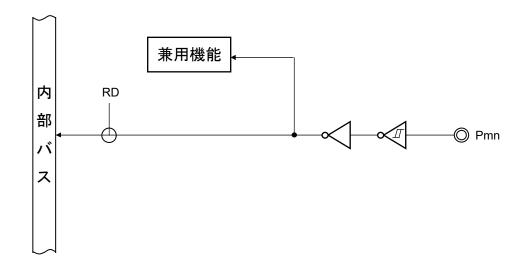

|      | 4.4.2 入出力ポートからの読み出し                            |     |

|      | 4. 4. 3 入出力ポートでの演算                             |     |

|      | 4.4.4 異電位(1.8 V系, 2.5 V系, 3 V系)外部デバイスとの接続方法    |     |

|      | 4.4.5 入出力バッファによる異電位(1.8 V系, 2.5 V系, 3 V系)対応    |     |

| 4. 5 | 兼用機能使用時のレジスタの設定                                |     |

|      | 4. 5. 1 兼用機能使用時の基本的な考え方                        |     |

|      | 4.5.2 出力機能を使用しない兼用機能のレジスタ設定                    |     |

|      | 4. 5. 3 使用するポート機能および兼用機能のレジスタ設定例               |     |

|      | 4. 5. 4 SEGxx端子兼用ポートの動作                        |     |

|      | 4. 5. 5 VL3, CAPL, CAPH端子兼用ポートの動作              |     |

| 4. 6 | ポート機能使用時の注意事項                                  |     |

|      | 4.6.1 ポート・レジスタn (Pn) に対する1ビット・メモリ操作命令に関する注意事項  | 123 |

|             | 4. 6. 2 端子設定に関する注意事項                          | 124   |

|-------------|-----------------------------------------------|-------|

| 第5章         | クロック発生回路                                      | 125   |

| カリキ         | / ロ / / 元工回路                                  | . 123 |

| 5. 1        | クロック発生回路の機能                                   | 125   |

| 5. 2        | クロック発生回路の構成                                   | 127   |

| 5. 3        | クロック発生回路を制御するレジスタ                             | 129   |

|             | 5. 3. 1 クロック動作モード制御レジスタ(CMC)                  | 129   |

|             | 5. 3. 2 システム・クロック制御レジスタ(CKC)                  | 132   |

|             | 5.3.3 クロック動作ステータス制御レジスタ(CSC)                  | 134   |

|             | 5. 3. 4 発振安定時間カウンタ状態レジスタ(OSTC)                | 135   |

|             | 5. 3. 5 発振安定時間選択レジスタ(OSTS)                    | 137   |

|             | 5.3.6 周辺イネーブル・レジスタ0,1 (PER0, PER1)            | 139   |

|             | 5. 3. 7 サブシステム・クロック供給モード制御レジスタ(OSMC)          | 142   |

|             | 5. 3. 8 高速オンチップ・オシレータ周波数選択レジスタ(HOCODIV)       | 144   |

|             | 5. 3. 9 周辺クロック制御レジスタ(PCKC)                    | 145   |

| 5. 4        | システム・クロック発振回路                                 | 146   |

|             | 5. 4. 1 X1発振回路                                | 146   |

|             | 5. 4. 2 XT1発振回路                               | 146   |

|             | 5. 4. 3 高速オンチップ・オシレータ                         | 150   |

|             | 5. 4. 4 低速オンチップ・オシレータ                         | 150   |

| 5. 5        | クロック発生回路の動作                                   | 151   |

| 5. 6        | クロックの制御                                       | 153   |

|             | 5. 6. 1 高速オンチップ・オシレータの設定例                     |       |

|             | 5. 6. 2 X1発振回路の設定例                            | 154   |

|             | 5. 6. 3 XT1発振回路の設定例                           | 156   |

|             | 5. 6. 4 CPUクロック状態移行図                          | 157   |

|             | 5. 6. 5 CPUクロックの移行前の条件と移行後の処理                 |       |

|             | 5.6.6 CPUクロックの切り替えとシステム・クロックの切り替えに要する時間       | 165   |

|             | 5. 6. 7 クロック発振停止前の条件                          | 166   |

| 5. 7        | 発振子と発振回路定数                                    | 167   |

| <del></del> |                                               |       |

| 第6草         | 高速オンチップ・オシレータ・クロック周波数補正機能                     | .171  |

| 6. 1        | 高速オンチップ・オシレータ・クロック周波数補正機能                     | 171   |

| -           | レジスタ説明                                        |       |

| V           | 6. 2. 1 高速オンチップ・オシレータ・クロック周波数補正制御レジスタ(HOCOFC) |       |

| 6. 3        |                                               |       |

|             | 6. 3. 1 動作概要                                  |       |

|             | 6. 3. 2 動作手順                                  |       |

| 6. 4        |                                               |       |

|             | 6. 4. 1 SFRアクセス                               |       |

|             | 6. 4. 2 スタンバイ時動作                              |       |

|             | 6.4.3 高速オンチップ・オシレータ周波数選択レジスタ(HOCODIV)の変更について  |       |

| 第7章         | タイマ・アレイ・ユニット                                  | .178  |

| • •         |                                               | _     |

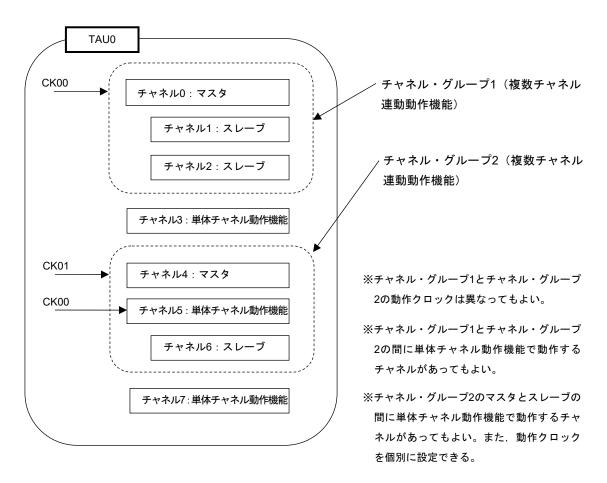

| 7. 1        | タイマ・アレイ・ユニットの機能                               |       |

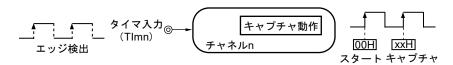

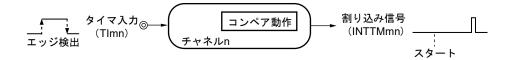

|             | 7. 1. 1 単独チャネル動作機能                            | 179   |

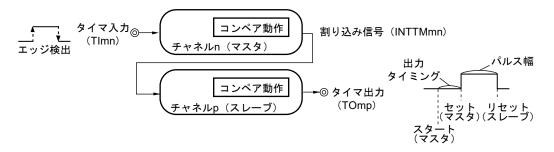

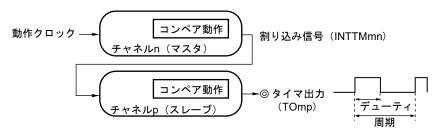

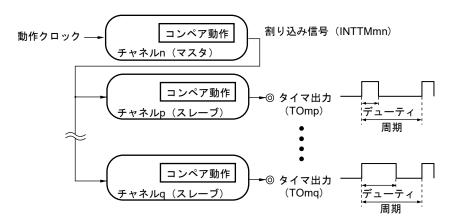

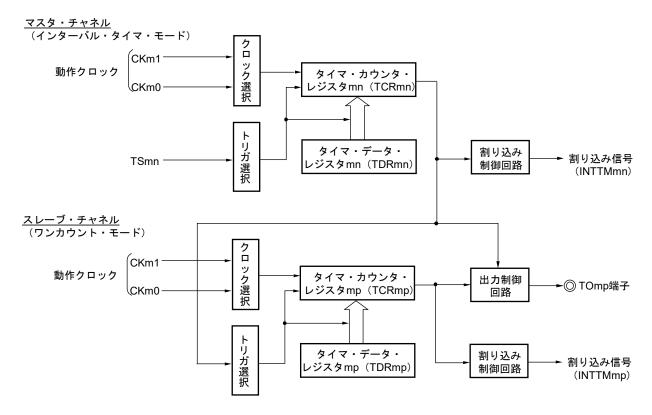

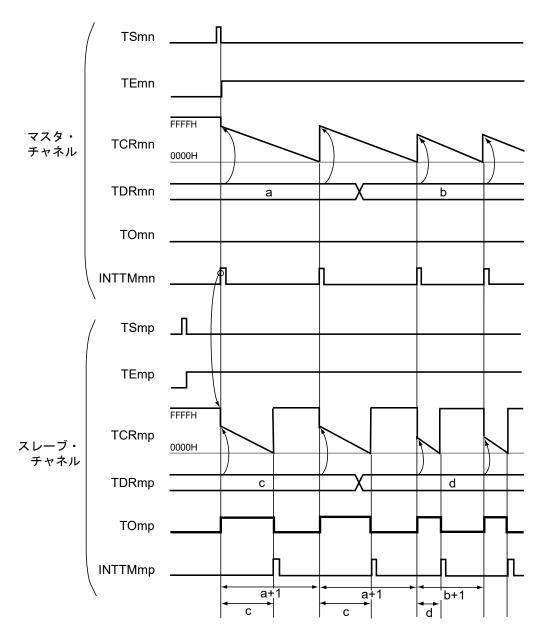

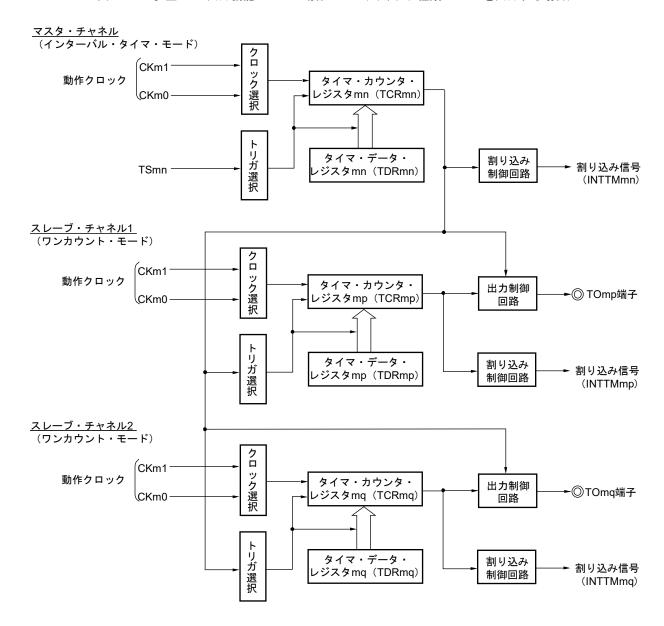

|      | 7. 1. 2 複数チャネル連動動作機能                 | 180 |

|------|--------------------------------------|-----|

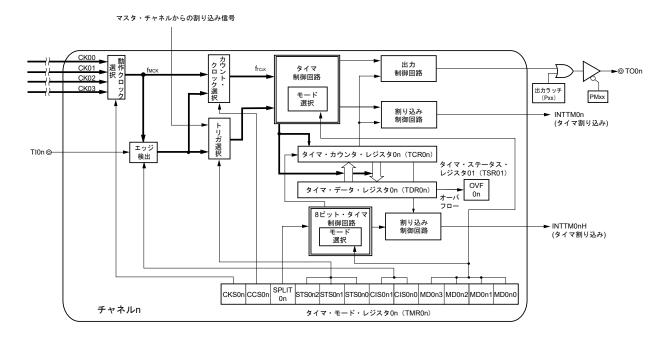

|      | 7.1.3 8ビット・タイマ動作機能(チャネル1,3のみ)        | 181 |

|      | 7. 1. 4 LIN-bus対応機能(チャネル7のみ)         | 182 |

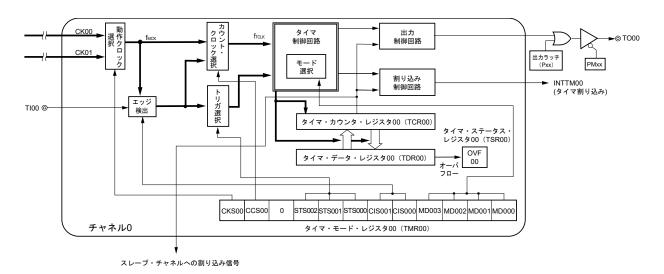

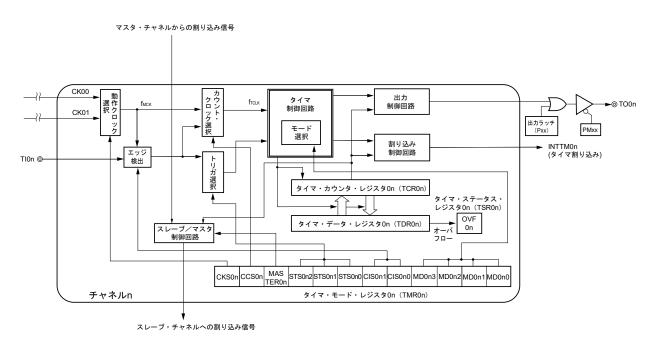

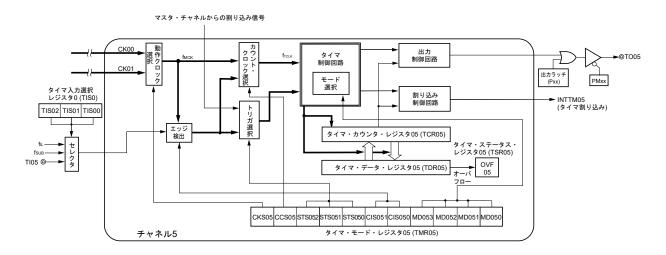

| 7. 2 | タイマ・アレイ・ユニットの構成                      | 183 |

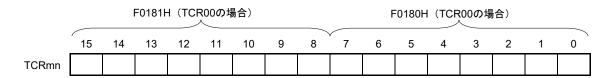

|      | 7. 2. 1 タイマ・カウンタ・レジスタmn(TCRmn)       | 187 |

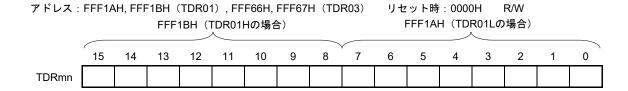

|      | 7.2.2 タイマ・データ・レジスタmn (TDRmn)         | 189 |

| 7. 3 | タイマ・アレイ・ユニットを制御するレジスタ                | 190 |

|      | 7.3.1 周辺イネーブル・レジスタ0(PERO)            |     |

|      | 7.3.2 タイマ・クロック選択レジスタm(TPSm)          |     |

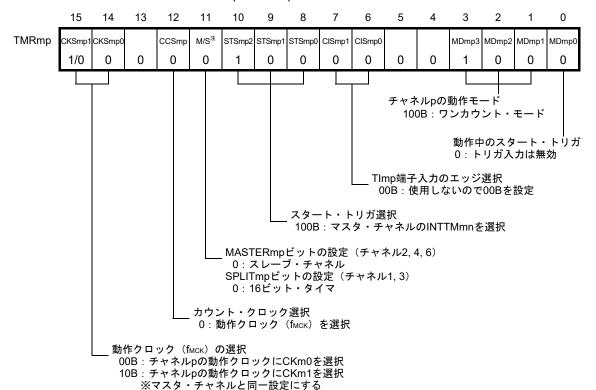

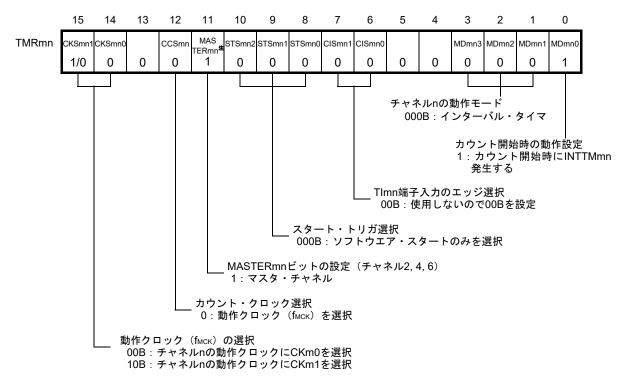

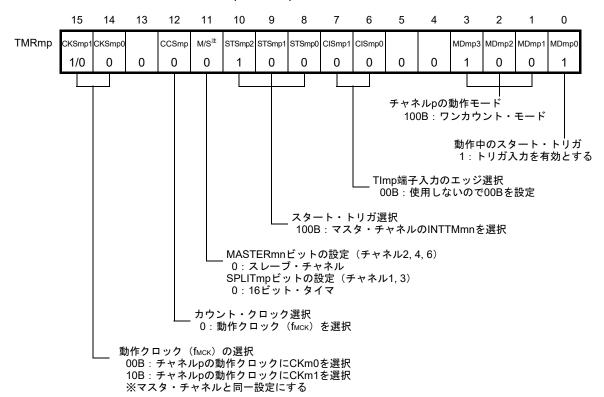

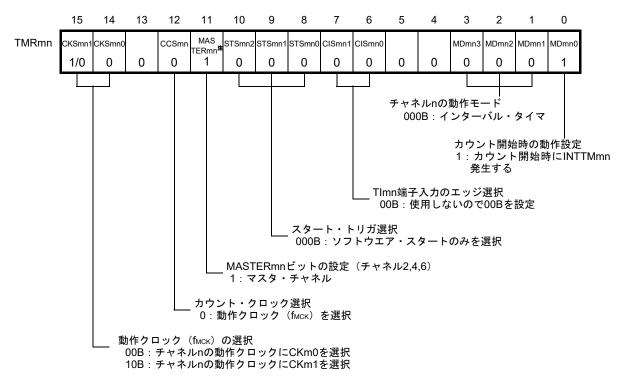

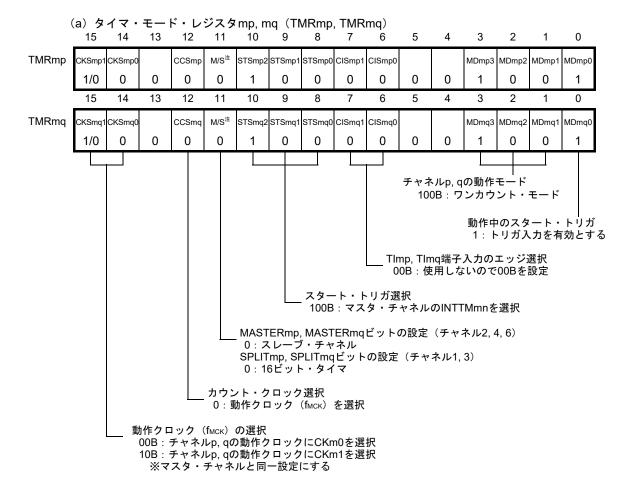

|      | 7.3.3 タイマ・モード・レジスタmn (TMRmn)         |     |

|      | 7.3.4 タイマ・ステータス・レジスタmn (TSRmn)       |     |

|      | 7.3.5 タイマ・チャネル許可ステータス・レジスタm(TEm)     |     |

|      | 7.3.6 タイマ・チャネル開始レジスタm (TSm)          |     |

|      | 7.3.7 タイマ・チャネル停止レジスタm(TTm)           |     |

|      | 7.3.8 タイマ入力選択レジスタ0 (TISO)            |     |

|      | 7.3.9 タイマ出力許可レジスタm(TOEm)             |     |

|      | 7. 3. 10 タイマ出力レジスタm(TOm)             |     |

|      | 7. 3. 11 タイマ出力レベル・レジスタm(TOLm)        |     |

|      | 7. 3. 12 タイマ出力モード・レジスタm(TOMm)        |     |

|      | 7.3.13 入力切り替え制御レジスタ (ISC)            |     |

|      | 7. 3. 14 ノイズ・フィルタ許可レジスタ1(NFEN1)      |     |

|      | 7. 3. 15 タイマ入出力端子のポート機能を制御するレジスタ     |     |

| 7 1  | 7.3.13 メイマス山ガ端子のホート仮能を制御するレンスメ       |     |

| 7.4  | 7.4.1 複数チャネル連動動作機能の基本ルール             |     |

|      | 7.4.2 8ビット・タイマ動作機能の基本ルール (チャネル1,3のみ) |     |

| 7. 5 | 7.4.2 ocッド・ダイマ動作機能の基本ルール(テャネル1,300分) |     |

| 7.5  | 7. 5. 1 カウント・クロック(fтcLK)             |     |

|      | 7.5.1 カウンド・クロック (ITCLK)              |     |

|      |                                      |     |

| 7.0  |                                      |     |

| 7. 6 | チャネル出力(TOmn端子)の制御                    |     |

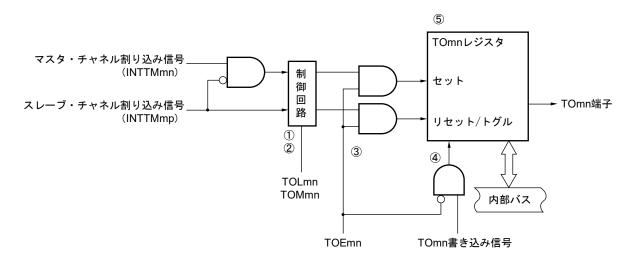

|      | 7. 6. 1 TOmn端子の出力回路の構成               |     |

|      | 7. 6. 2 TOmn端子の出力設定                  |     |

|      | 7.6.3 チャネル出力操作時の注意事項                 |     |

|      | 7. 6. 4 TOmnビットの一括操作                 |     |

|      | 7.6.5 カウント動作開始時のタイマ割り込みとTOmn端子出力について |     |

| 7. 7 | タイマ入力(TImn)の制御                       |     |

|      | 7. 7. 1 Tlmnの入力回路構成                  |     |

|      | 7.7.2 ノイズ・フィルタ                       |     |

|      | 7.7.3 チャネル入力操作時の注意事項                 |     |

| 7. 8 | タイマ・アレイ・ユニットの単独チャネル動作機能              |     |

|      | 7.8.1 インターバル・タイマ/方形波出力としての動作         |     |

|      | 7.8.2 外部イベント・カウンタとしての動作              |     |

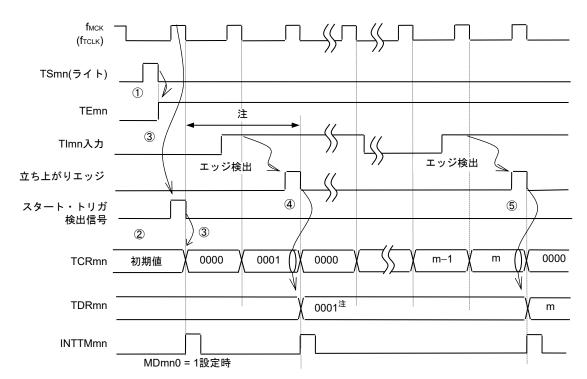

|      | 7.8.3 入力パルス間隔測定としての動作                |     |

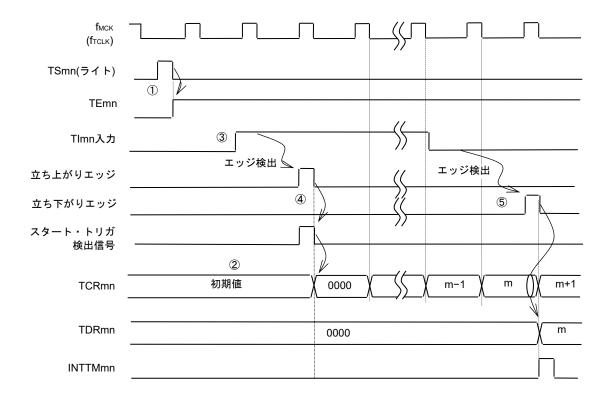

|      | 7.8.4 入力信号のハイ/ロウ・レベル幅測定としての動作        |     |

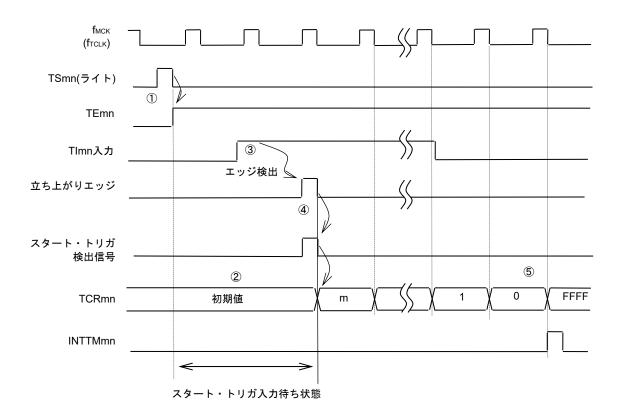

|      | 7.8.5 ディレイ・カウンタとしての動作                |     |

| 7. 9 | タイマ・アレイ・ユニットの複数チャネル連動動作機能            |     |

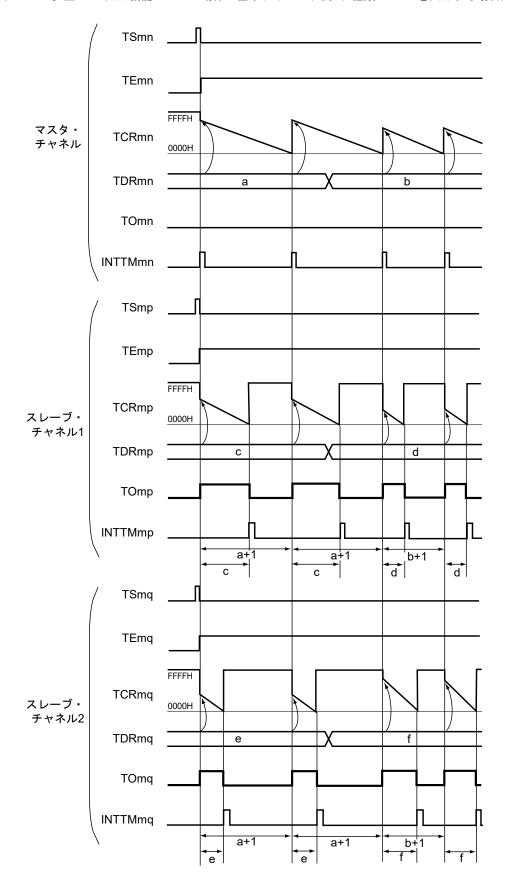

|      | 7. 9. 1 ワンショット・パルス出力機能としての動作         |     |

|      | 7. 9. 2 PWM機能としての動作                  |     |

|      | 7.9.3 多重PWM出力機能としての動作                | 271 |

| 7. 10 | ) タイマ・アレイ・ユニット使用時の注意事項                | 279 |

|-------|---------------------------------------|-----|

|       | 7. 10. 1 タイマ出力使用時の注意事項                | 279 |

|       |                                       |     |

| 第8草   | リアルタイム・クロック2                          | 280 |

| 8. 1  | リアルタイム・クロック2の機能                       | 280 |

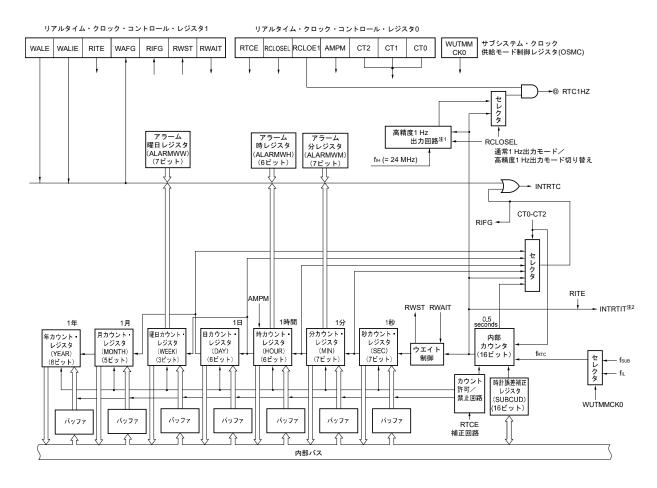

| 8. 2  | リアルタイム・クロック2の構成                       |     |

| 8. 3  |                                       |     |

|       | 8. 3. 1 周辺イネーブル・レジスタ0 (PER0)          |     |

|       | 8. 3. 2 周辺イネーブル・レジスタ1(PER1)           |     |

|       | 8.3.3 サブシステム・クロック供給モード制御レジスタ(OSMC)    |     |

|       | 8.3.4 パワー・オン・リセット・ステータス・レジスタ(PORSR)   | 287 |

|       | 8.3.5 リアルタイム・クロック・コントロール・レジスタ0(RTCC0) | 288 |

|       | 8.3.6 リアルタイム・クロック・コントロール・レジスタ1(RTCC1) | 290 |

|       | 8.3.7 秒カウント・レジスタ(SEC)                 | 293 |

|       | 8.3.8 分カウント・レジスタ(MIN)                 | 293 |

|       | 8.3.9 時カウント・レジスタ(HOUR)                | 294 |

|       | 8. 3. 10 日カウント・レジスタ(DAY)              | 296 |

|       | 8. 3. 11 曜日カウント・レジスタ(WEEK)            | 297 |

|       | 8.3.12 月カウント・レジスタ(MONTH)              | 298 |

|       | 8. 3. 13 年カウント・レジスタ(YEAR)             | 298 |

|       | 8. 3. 14 時計誤差補正レジスタ(SUBCUD)           | 299 |

|       | 8. 3. 15 アラーム分レジスタ(ALARMWM)           | 302 |

|       | 8. 3. 16 アラーム時レジスタ(ALARMWH)           | 302 |

|       | 8. 3. 17 アラーム曜日レジスタ(ALARMWW)          | 303 |

| 8. 4  | リアルタイム・クロック2の動作                       | 304 |

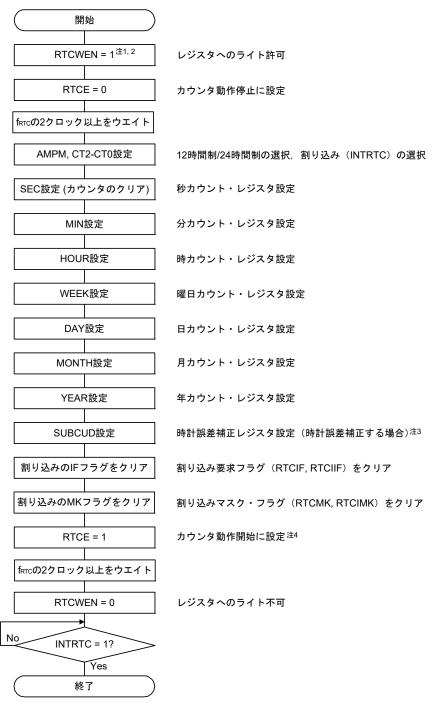

|       | 8. 4. 1 リアルタイム・クロック2の動作開始             | 304 |

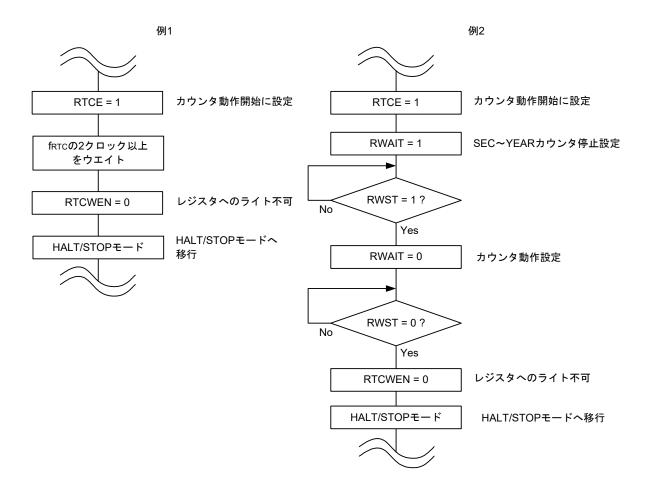

|       | 8. 4. 2 動作開始後のHALT/STOPモードへの移行        | 305 |

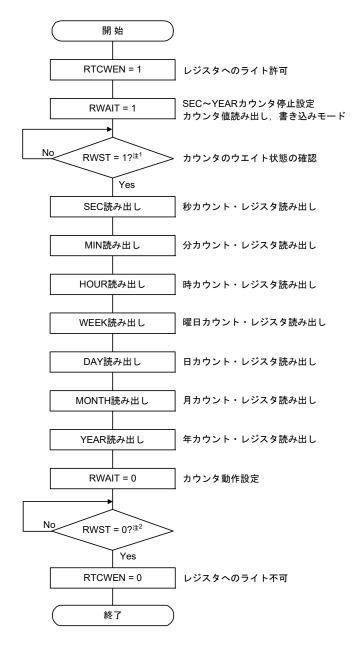

|       | 8. 4. 3 リアルタイム・クロック2のカウンタ読み出し         |     |

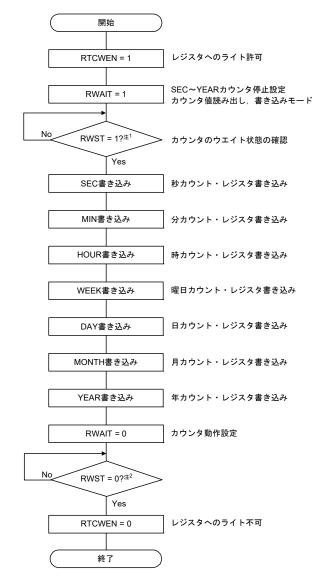

|       | 8. 4. 4 リアルタイム・クロック2のカウンタ書き込み         |     |

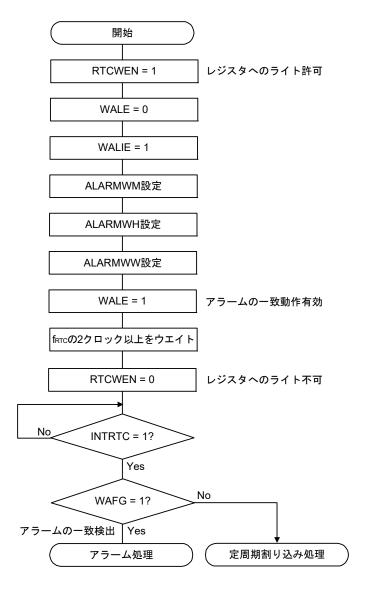

|       | 8. 4. 5 リアルタイム・クロック2のアラーム設定           |     |

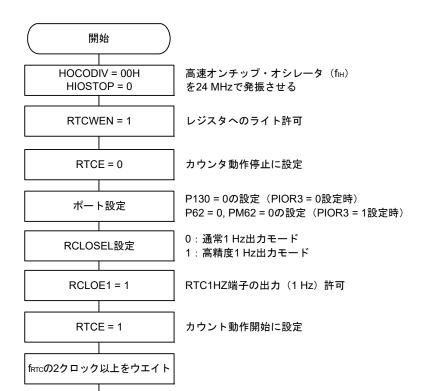

|       | 8. 4. 6 リアルタイム・クロック2の1 Hz出力           |     |

|       | 8. 4. 7 時計誤差補正レジスタの設定手順               |     |

|       | 8. 4. 8 リアルタイム・クロック2の時計誤差補正例          |     |

|       | 8. 4. 9 高精度1 Hz出力について                 | 314 |

| 第9章   | サブシステム・クロック周波数測定回路                    | 315 |

| 9. 1  | サブシステム・クロック周波数測定回路                    | 315 |

|       | サブシステム・クロック周波数測定回路の構成                 |     |

|       | サブシステム・クロック周波数測定回路を制御するレジスタ           |     |

|       | 9. 3. 1 周辺イネーブル・レジスタ1(PER1)           | 317 |

|       | 9.3.2 サブシステム・クロック供給モード制御レジスタ(OSMC)    | 318 |

|       | 9.3.3 周波数測定カウント・レジスタL(FMCRL)          |     |

|       | 9.3.4 周波数測定カウント・レジスタH (FMCRH)         | 320 |

|       | 9.3.5 周波数測定コントロール・レジスタ(FMCTL)         | 321 |

| 9. 4  | サブシステム・クロック周波数測定回路の動作                 | 322 |

|       | 9.4.1 基準クロックによるサブシステム・クロック周波数測定回路の設定  | 322 |

|       | 9.4.2 サブシステム・クロック周波数測定回路の動作タイミング      | 323 |

| 第10章 12ビット・インターバル・タイマ                  | 324              |

|----------------------------------------|------------------|

| 10. 1 12ビット・インターバル・タイマの機能              | 324              |

| 10. 2 12ビット・インターバル・タイマの構成              | 324              |

| 10.3 12ビット・インターバル・タイマを制御するレジスタ         | 325              |

| 10. 3. 1 周辺イネーブル・レジスタ1(PER1)           | 325              |

| 10. 3. 2 サブシステム・クロック供給モード制御レジスタ(C      | OSMC)326         |

| 10. 3. 3 12ビット・インターバル・タイマ・コントロール・      | レジスタ(ITMC)327    |

| 10.4 12ビット・インターバル・タイマの動作               | 328              |

| 10. 4. 1 12ビット・インターバル・タイマの動作タイミング.     | 328              |

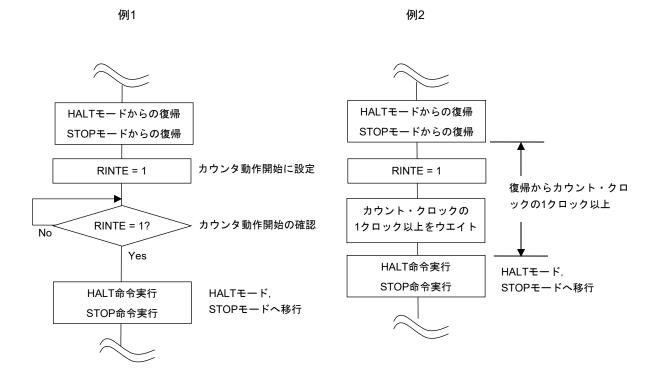

| 10. 4. 2 HALT/STOP モードから復帰後にカウンタ動作開始 l | し,再度HALT/STOPモード |

| への移行                                   | 329              |

| 第11章 8ビット・インターバル・タイマ                   | 330              |

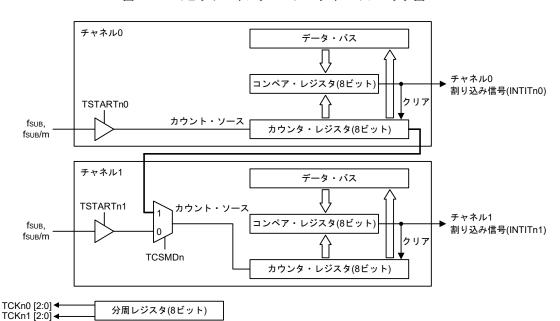

| 11. 1 概要                               | 330              |

| 11. 2 入出力端子                            | 331              |

| 11. 3 レジスタの説明                          |                  |

| 11. 3. 1 8ビット・インターバル・タイマ・カウンタ・レジス      |                  |

| (n = 0, 1, i = 0, 1)                   |                  |

| 11.3.2 8ビット・インターバル・タイマ・カウンタ・レジス        |                  |

| (n = 0, 1)                             | 332              |

| 11. 3. 3 8ビット・インターバル・タイマ・コンペア・レジス      |                  |

| (n = 0, 1, i = 0, 1)                   | 333              |

| 11. 3. 4 8ビット・インターバル・タイマ・コンペア・レジス      | タn(TRTCMPn)      |

| (n = 0, 1)                             |                  |

| 11.3.5 8ビット・インターバル・タイマ制御レジスタn (TR      |                  |

| 11.3.6 8ビット・インターバル・タイマ分周レジスタn(TR       |                  |

| 11. 4 動作説明                             |                  |

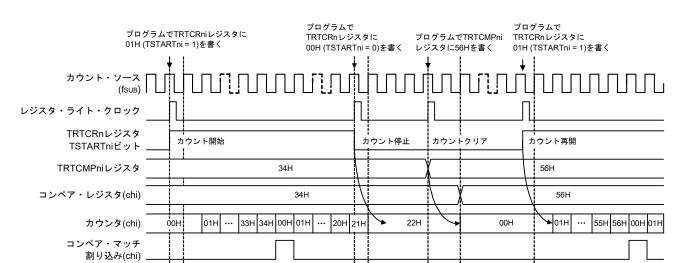

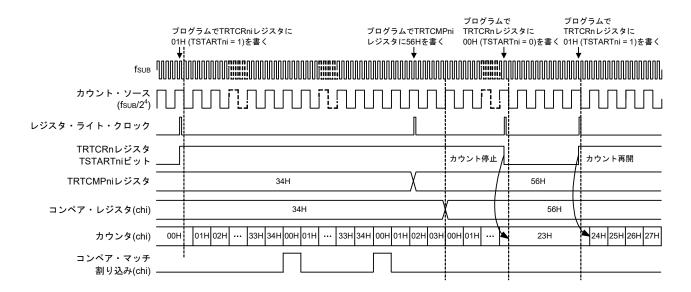

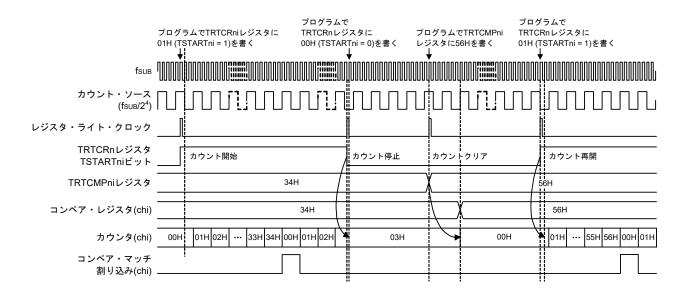

| 11. 4. 1 カウンタ・モード                      |                  |

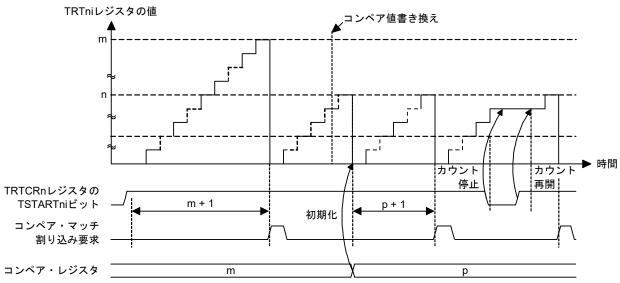

| 11. 4. 2 タイマ動作                         |                  |

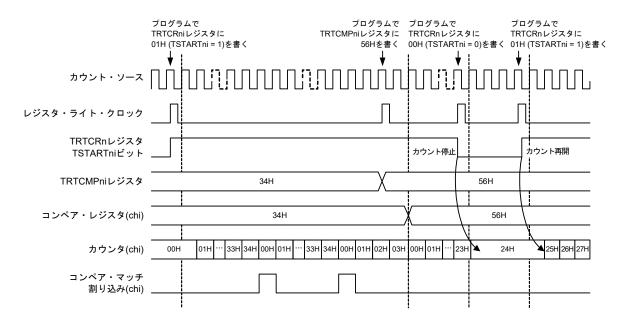

| 11. 4. 3 開始/停止タイミング                    |                  |

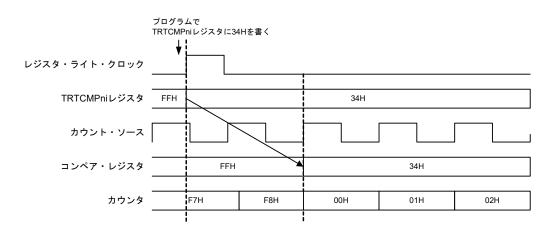

| 11. 4. 4 コンペア・レジスタ値の反映タイミング            |                  |

| 11.5 8ビット・インターバル・タイマの注意事項              |                  |

| 11. 5. 1 動作モードおよびクロック設定変更について          |                  |

| 11. 5. 2 コンペア・レジスタへのアクセスについて           |                  |

| 11.5.3 8ビット・インターバル・タイマ設定手順について         | 343              |

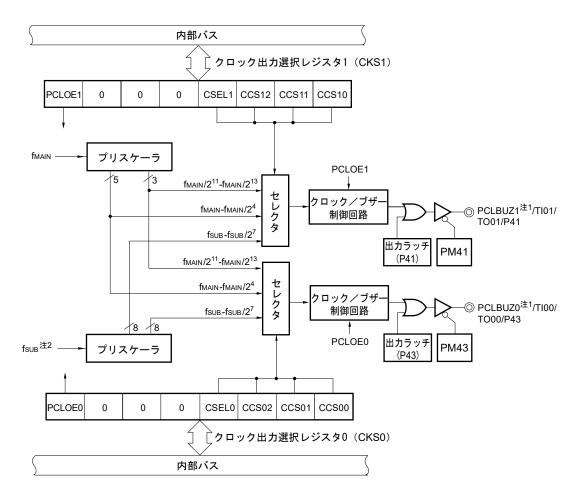

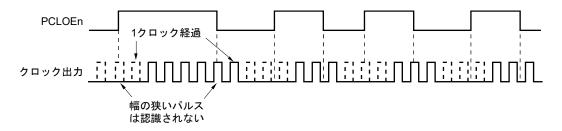

| 第12章 クロック出力/ブザー出力制御回路                  | 344              |

| 12. 1 クロック出力/ブザー出力制御回路の機能              |                  |

| 12. 2 クロック出力/ブザー出力制御回路の構成              |                  |

| 12.3 クロック出力/ブザー出力制御回路を制御するレジスタ         |                  |

| 12. 3. 1 クロック出力選択レジスタn(CKSn)           |                  |

| 12.3.2 クロック出力/ブザー出力端子のポート機能を制御す        |                  |

| 12. 4 クロック出力/ブザー出力制御回路の動作              |                  |

| 12. 4. 1 出力端子の動作                       |                  |

| 12.5 クロック出力/ブザー出力制御回路の注意事項             | 349              |

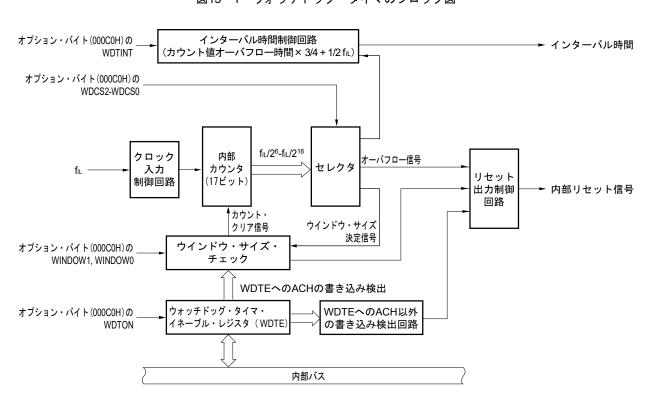

| 第13章  | ウォッ       | チドッグ・タイマ                         | 350 |

|-------|-----------|----------------------------------|-----|

| 13. 1 | ウォッラ      | チドッグ・タイマの機能                      | 350 |

| 13. 2 |           | Fドッグ・タイマの構成                      |     |

|       |           | チドッグ・タイマを制御するレジスタ                |     |

| .0.0  |           | ウォッチドッグ・タイマ・イネーブル・レジスタ(WDTE)     |     |

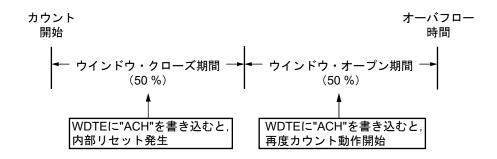

| 13 4  |           | Fドッグ・タイマの動作                      |     |

| 10. 1 |           | ウォッチドッグ・タイマの動作制御                 |     |

|       |           | ウォッチドッグ・タイマのオーバフロー時間の設定          |     |

|       |           | ウォッチドッグ・タイマのウインドウ・オープン期間の設定      |     |

|       |           | ウォッチドッグ・タイマのインターバル割り込みの設定        |     |

|       |           |                                  |     |

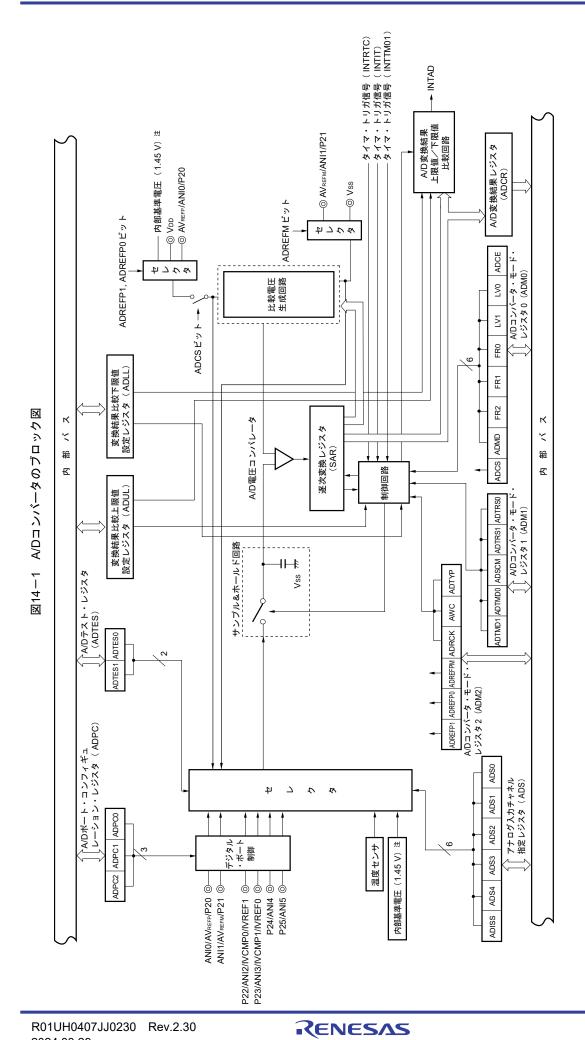

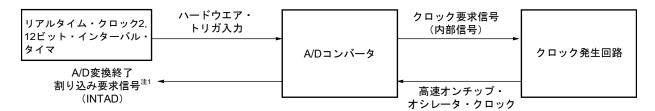

| 第14章  | A/D⊐:     | ノバータ                             | 358 |

|       |           | バータの機能                           |     |

|       |           | バータの構成                           |     |

| 14. 3 |           | バータを制御するレジスタ                     |     |

|       |           | 周辺イネーブル・レジスタ0(PERO)              |     |

|       |           | A/Dコンバータ・モード・レジスタ0 (ADM0)        |     |

|       |           | A/Dコンバータ・モード・レジスタ1 (ADM1)        |     |

|       |           | A/Dコンバータ・モード・レジスタ2 (ADM2)        |     |

|       |           | 10ビットA/D変換結果レジスタ(ADCR)           |     |

|       |           | 8ビットA/D変換結果レジスタ(ADCRH)           |     |

|       |           | アナログ入力チャネル指定レジスタ(ADS)            |     |

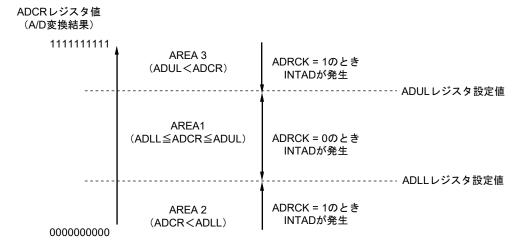

|       | 14. 3. 8  | 変換結果比較上限値設定レジスタ(ADUL)            |     |

|       | 14. 3. 9  | 変換結果比較下限値設定レジスタ(ADLL)            |     |

|       |           | A/Dテスト・レジスタ(ADTES)               |     |

|       |           | アナログ入力端子のポート機能を制御するレジスタ          |     |

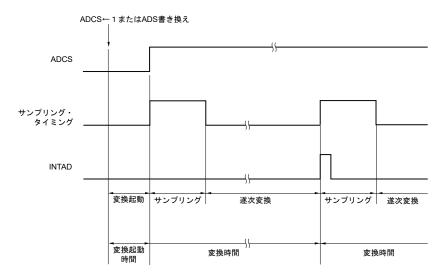

|       |           | バータの変換動作                         |     |

|       | _         | Eと変換結果                           |     |

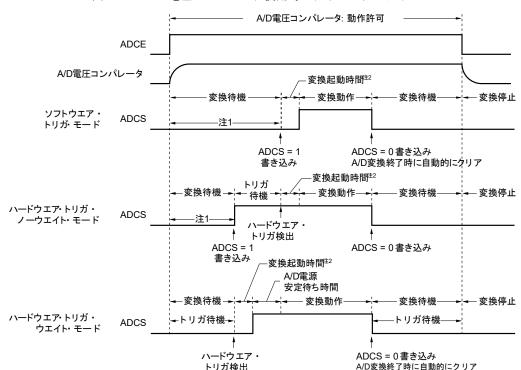

| 14. 6 |           | バータの動作モード                        |     |

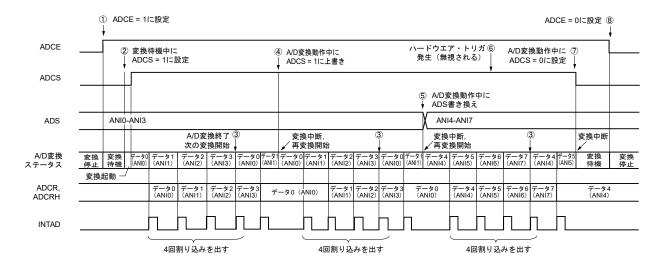

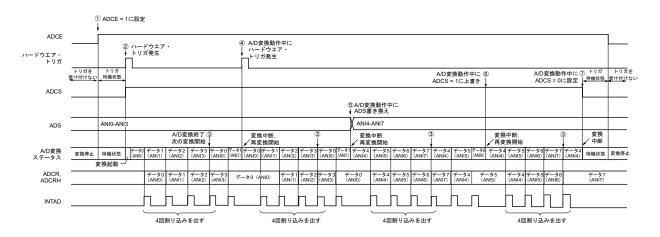

|       |           | ソフトウエア・トリガ・モード(セレクト・モード、連続変換モード) | 384 |

|       | 14. 6. 2  | ソフトウエア・トリガ・モード                   |     |

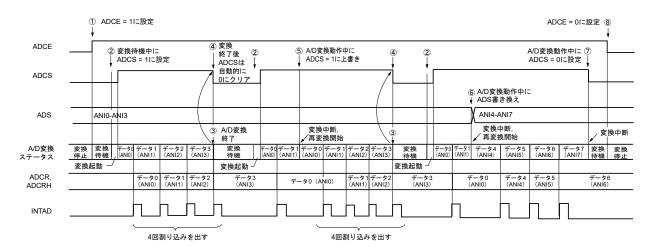

|       |           | (セレクト・モード, ワンショット変換モード)          |     |

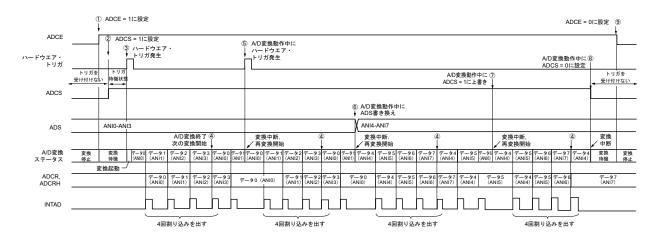

|       |           | ソフトウエア・トリガ・モード(スキャン・モード、連続変換モード) | 386 |

|       | 14. 6. 4  | ソフトウエア・トリガ・モード                   |     |

|       |           | (スキャン・モード, ワンショット変換モード)          | 387 |

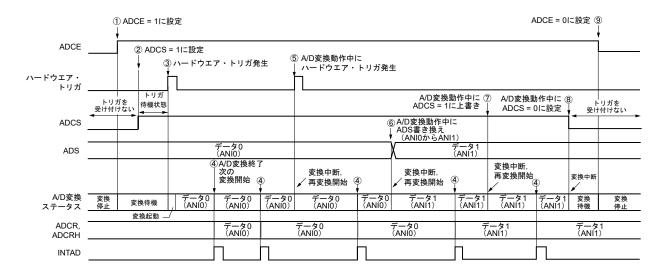

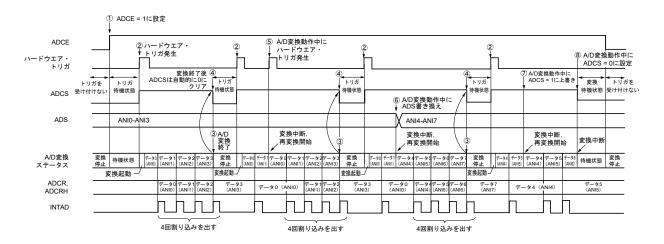

|       | 14. 6. 5  | ハードウエア・トリガ・ノーウエイト・モード            |     |

|       |           | (セレクト・モード,連続変換モード)               | 388 |

|       | 14. 6. 6  | ハードウエア・トリガ・ノーウエイト・モード            |     |

|       |           | (セレクト・モード,ワンショット変換モード)           | 389 |

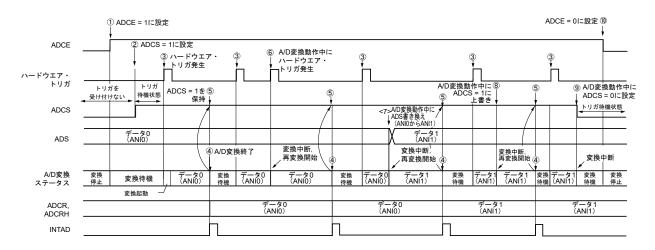

|       | 14. 6. 7  | ハードウエア・トリガ・ノーウエイト・モード            |     |

|       |           | (スキャン・モード,連続変換モード)               | 390 |

|       | 14. 6. 8  | ハードウエア・トリガ・ノーウエイト・モード            |     |

|       |           | (スキャン・モード, ワンショット変換モード)          | 391 |

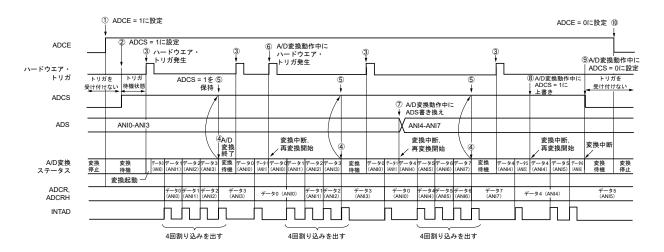

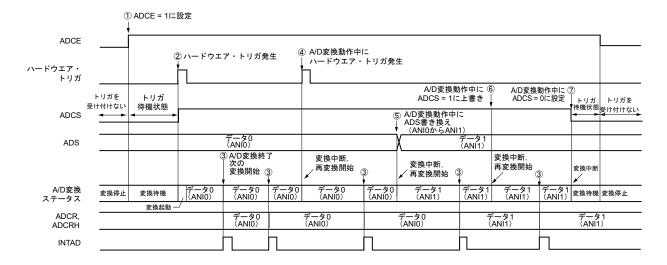

|       | 14. 6. 9  | ハードウエア・トリガ・ウエイト・モード              |     |

|       |           | (セレクト・モード,連続変換モード)               | 392 |

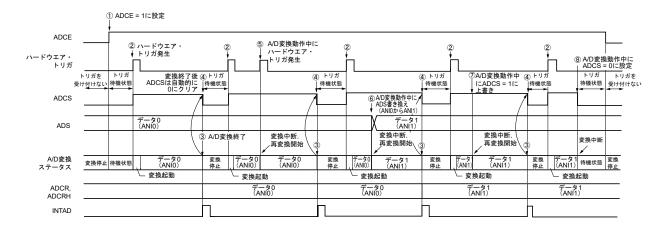

|       | 14. 6. 10 | ハードウエア・トリガ・ウエイト・モード              |     |

|       |           | (セレクト・モード, ワンショット変換モード)          | 393 |

|       | 14. 6. 11 | ハードウエア・トリガ・ウエイト・モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|-------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|       |           | (スキャン・モード,連続変換モード)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 394   |

|       | 14. 6. 12 | ハードウエア・トリガ・ウエイト・モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|       |           | (スキャン・モード, ワンショット変換モード)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 395   |

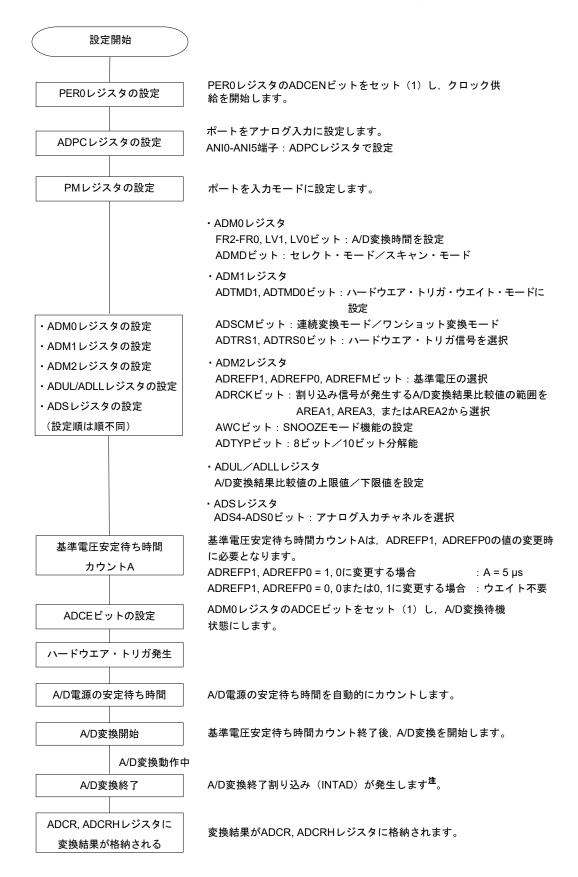

| 14. 7 | A/Dコン     | ·バータの設定フロー・チャート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 396   |

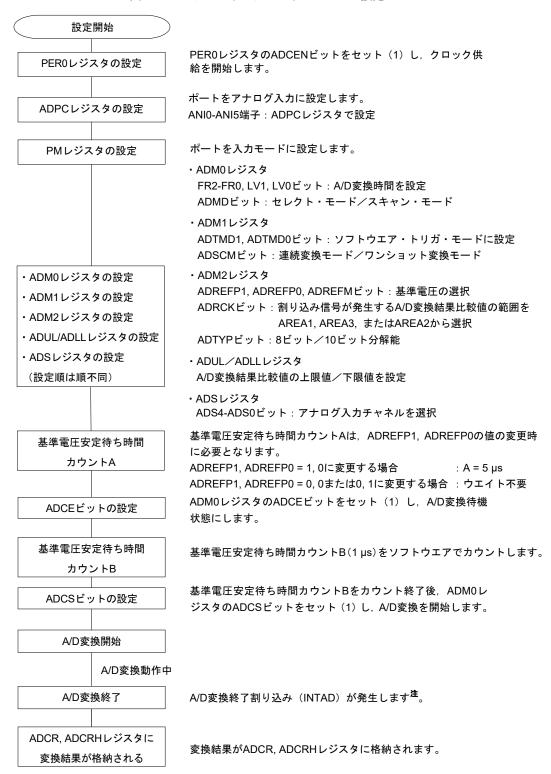

|       | 14. 7. 1  | ソフトウエア・トリガ・モード設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 396   |

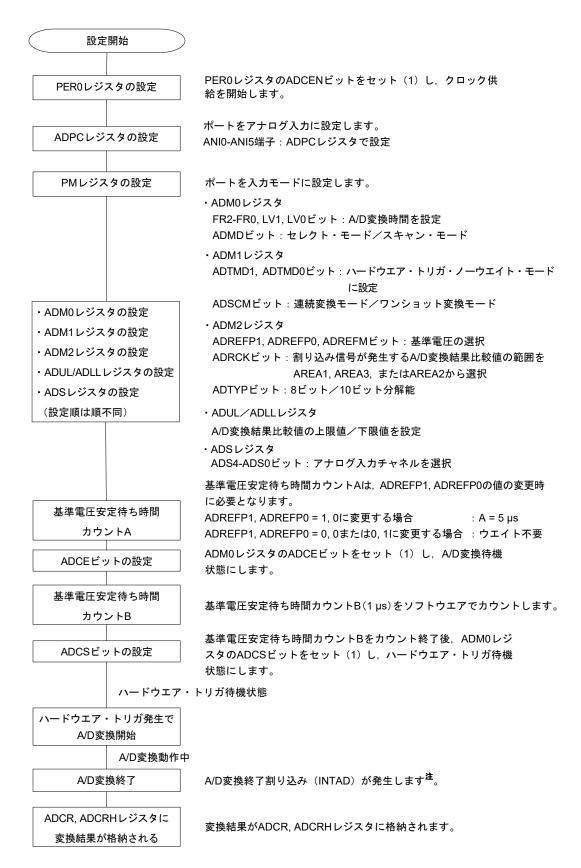

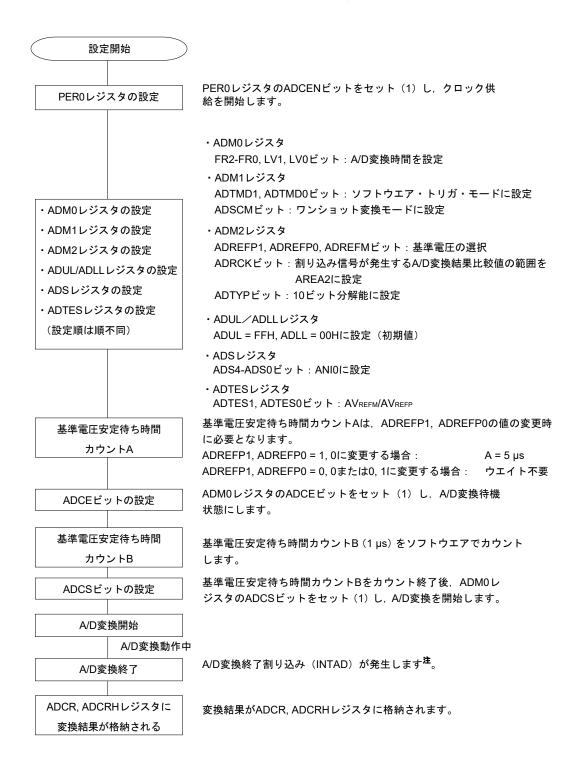

|       | 14. 7. 2  | ハードウエア・トリガ・ノーウエイト・モード設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 397   |

|       | 14. 7. 3  | ハードウエア・トリガ・ウエイト・モード設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 398   |

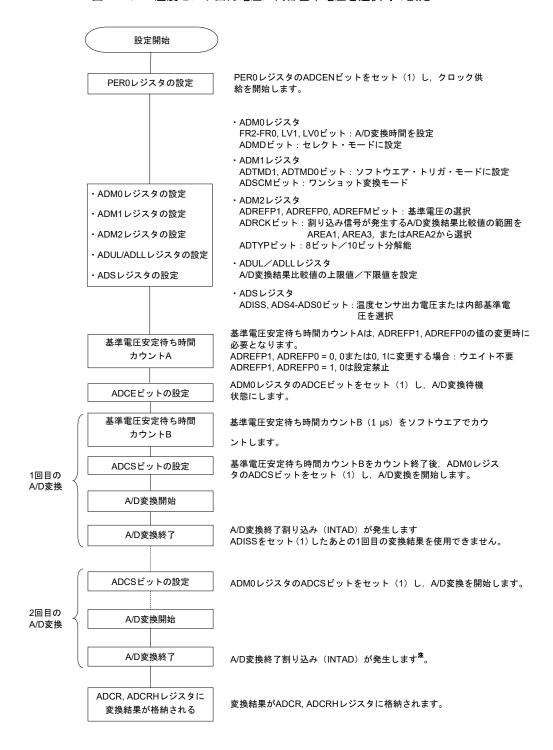

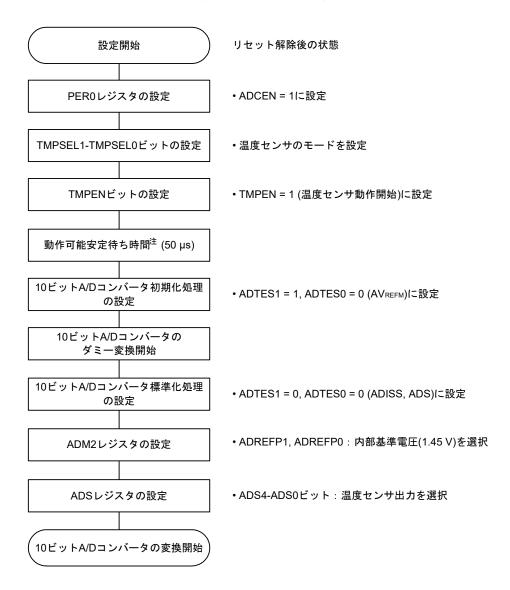

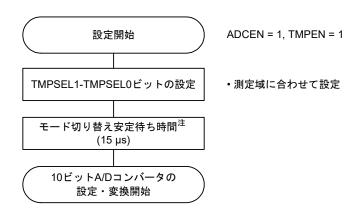

|       | 14. 7. 4  | 温度センサ出力電圧/内部基準電圧を選択時の設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|       |           | (例 ソフトウエア・トリガ・モード、ワンショット変換モード時)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 399   |

|       | 14. 7. 5  | テスト・モード設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 400   |

| 14. 8 | SNOOZ     | ′Eモード機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 401   |

| 14. 9 | A/Dコン     | ·バータ特性表の読み方                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 405   |

| 14. 1 | 0 A/D⊐    | ンバータの注意事項                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 408   |

|       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| 第15章  | 温度セ       | ンサ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 412   |

|       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

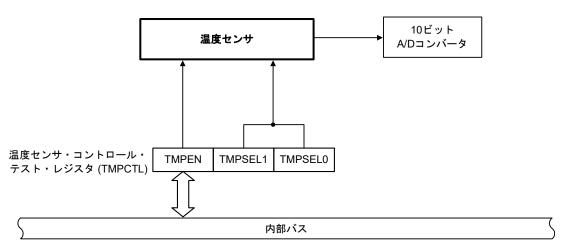

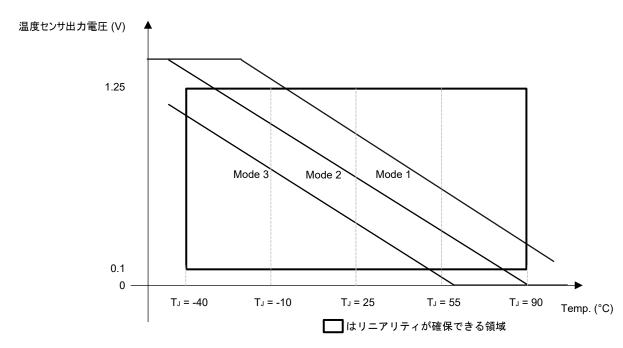

| 15. 1 | 温度セニ      | ンサの機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 412   |

| 15. 2 | レジス?      | タの説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 413   |

|       | 15. 2. 1  | 温度センサ・コントロール・テスト・レジスタ(TMPCTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 413   |

| 15. 3 |           | 頁                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

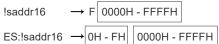

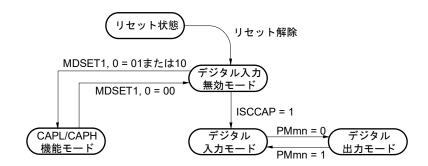

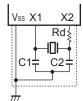

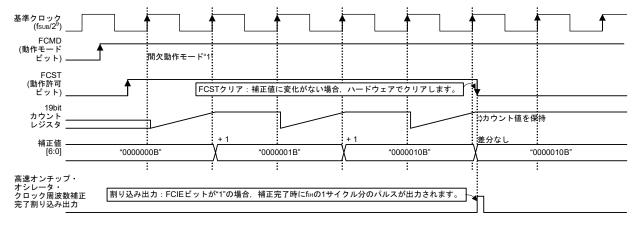

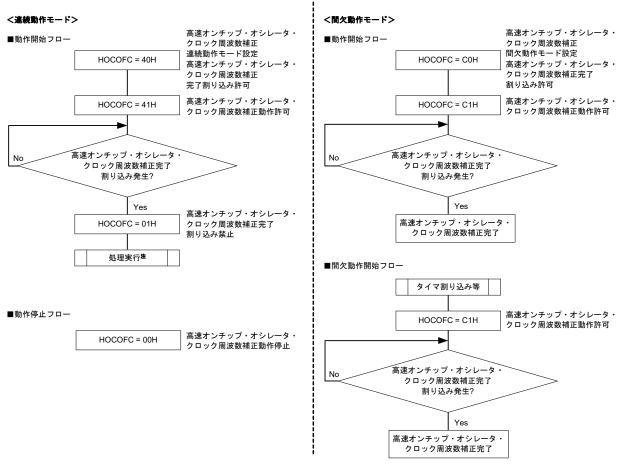

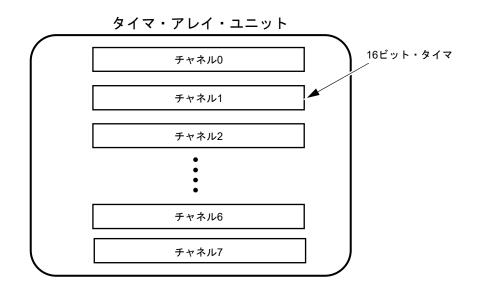

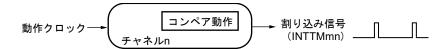

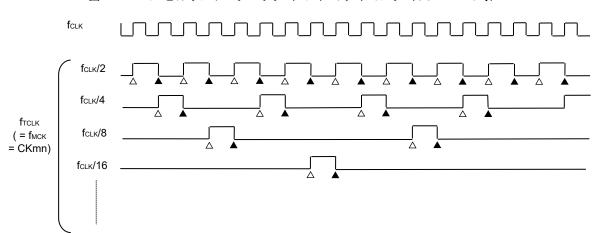

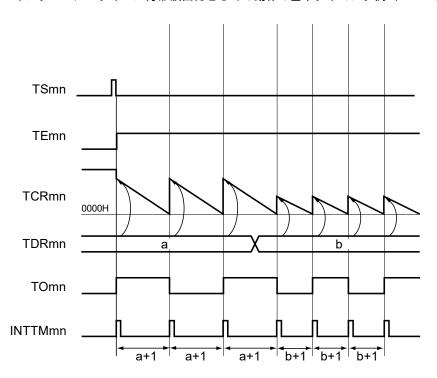

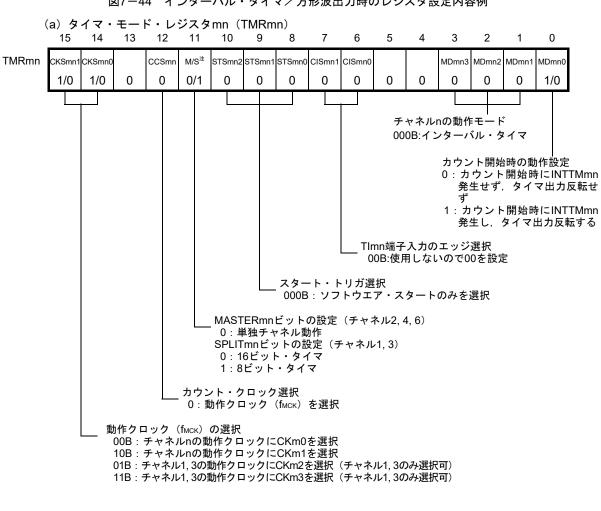

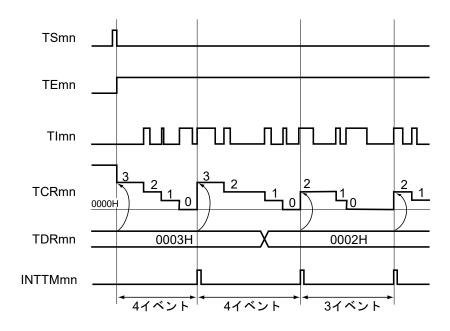

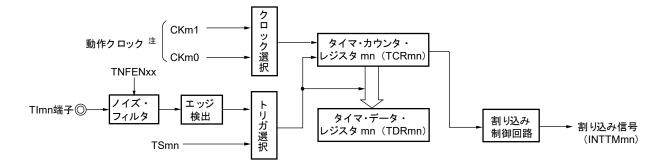

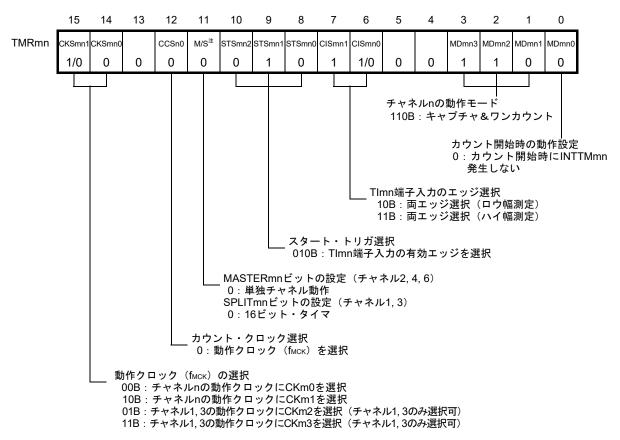

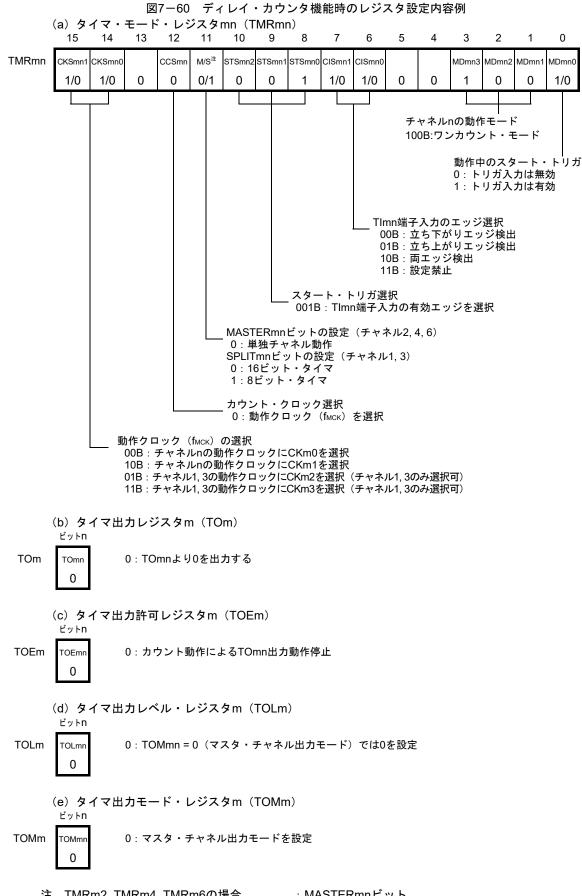

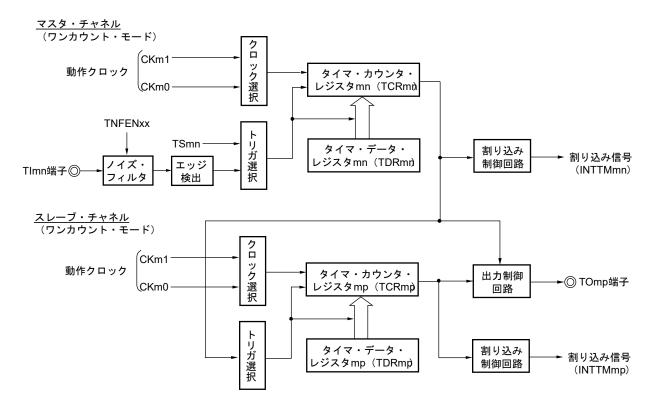

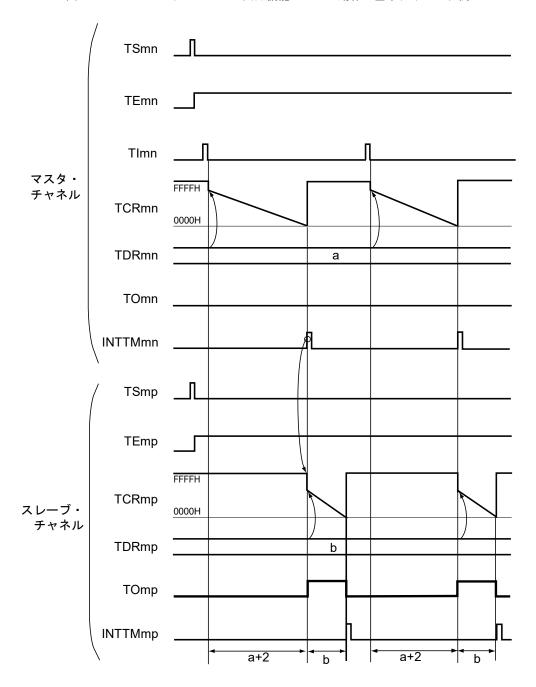

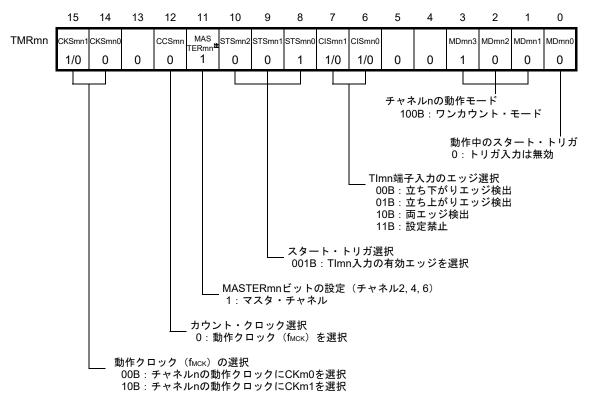

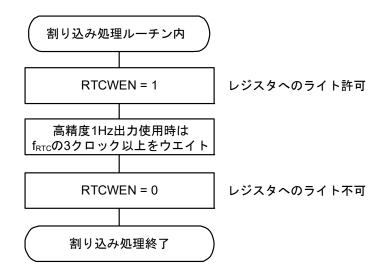

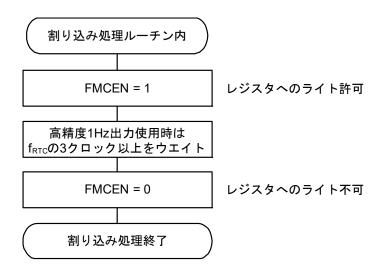

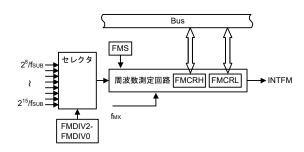

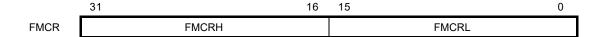

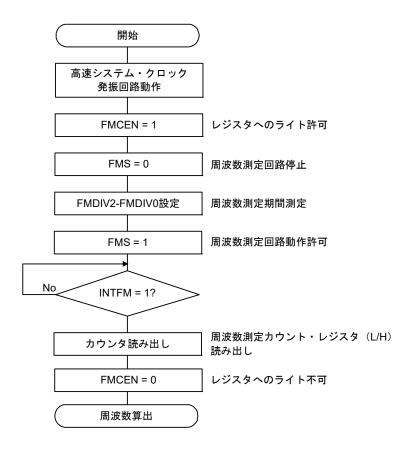

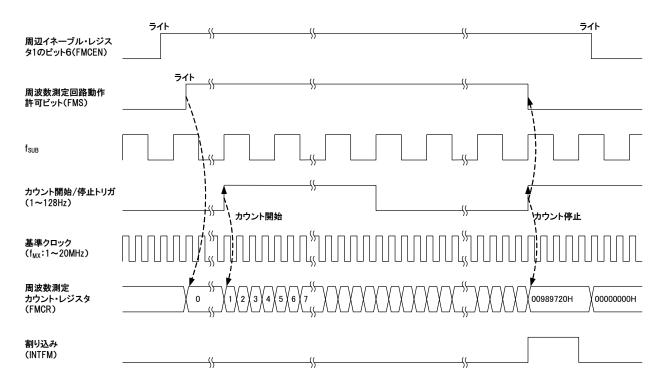

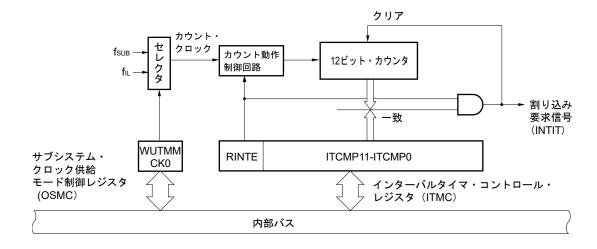

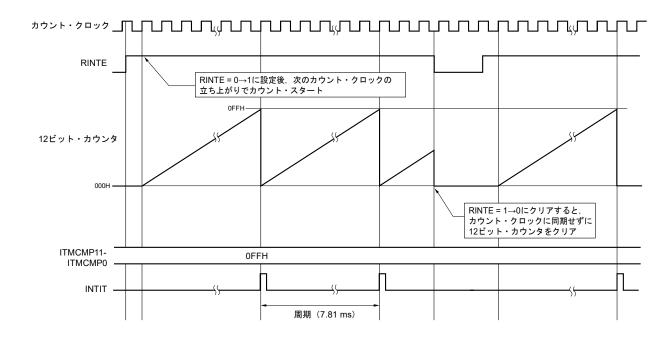

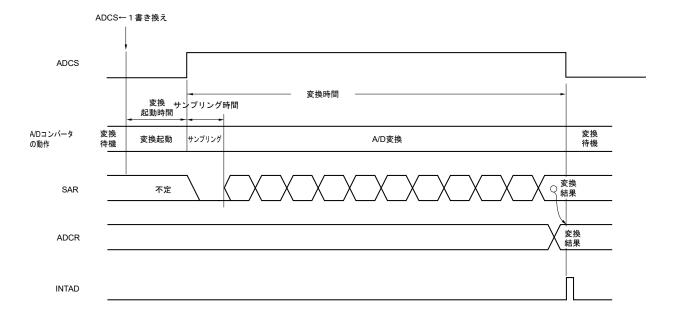

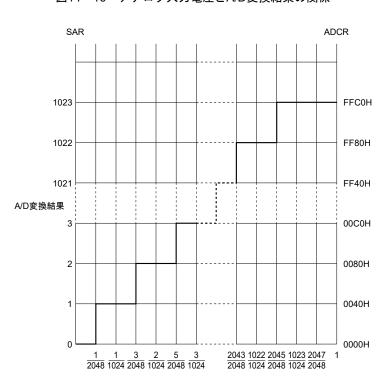

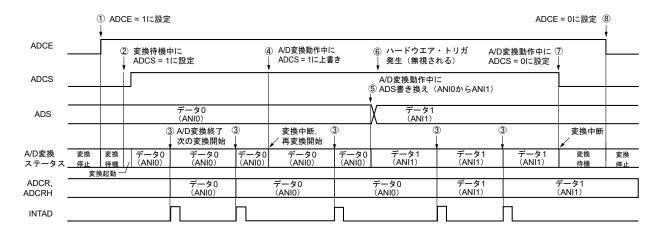

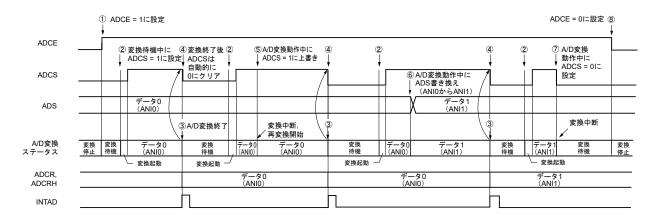

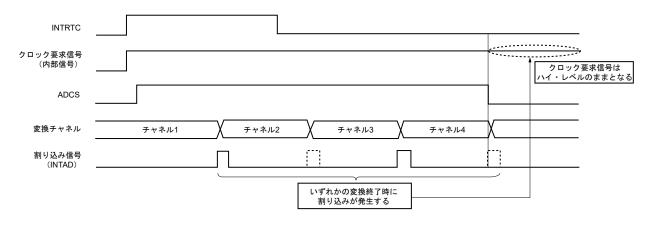

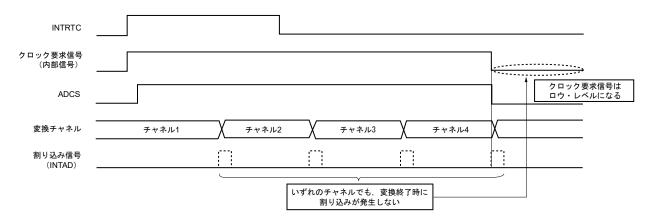

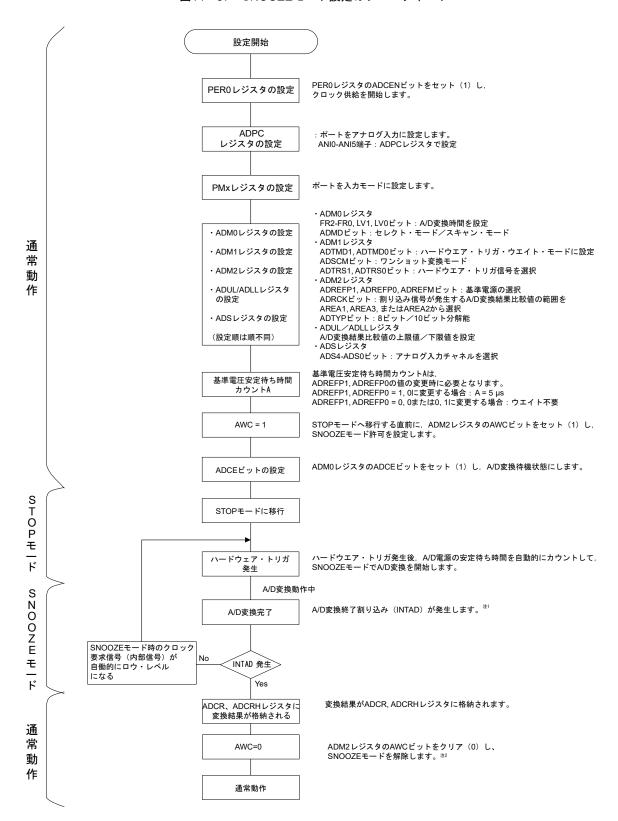

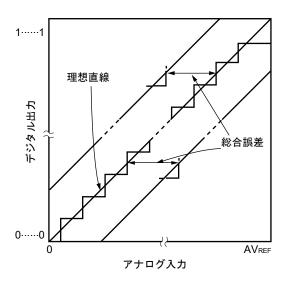

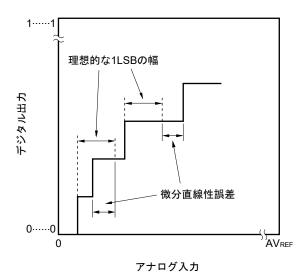

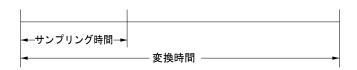

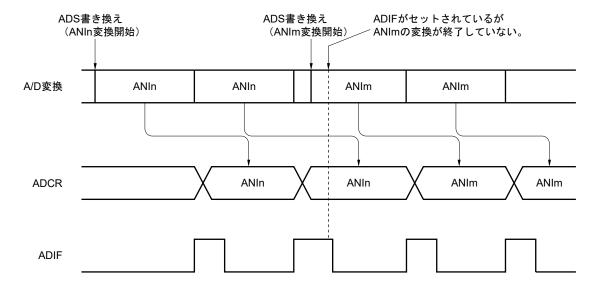

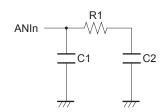

|       | 15. 3. 1  | A/Dコンバータ・モード・レジスタ0(ADM0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 414   |