# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

# ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# R8C/11グループ

ハードウェアマニュアル ルネサス16ビットシングルチップマイクロコンピュータ M16Cファミリ/R8C/Tinyシリーズ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサスエレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサスエレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

#### **−** 安全設計に関するお願い ·

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、 誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果とし て、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した 冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

# 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様が用途に応じた適切なルネサス テクノロジ製品をご購入いただく ための参考資料であり、本資料中に記載の技術情報についてルネサス テクノロジが 所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサステクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報 は本資料発行時点のものであり、ルネサス テクノロジは、予告なしに、本資料に 記載した製品または仕様を変更することがあります。ルネサス テクノロジ半導体製品のご購入に当たりましては、事前にルネサス テクノロジ、ルネサス販売または特 約店へ最新の情報をご確認頂きますとともに、ルネサス テクノロジホームページ (http://www.renesas.com) などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料 の記述誤りに起因する損害がお客様に生じた場合には、ルネサス テクノロジはその 責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサス テクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサステクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサステクノロジ、ルネサス販売または特約店までご照会ください。

# このマニュアルの使い方

# 1. 対象

このマニュアルはR8C/11グループのハードウェアマニュアルです。

このマニュアルを使用する上で、電気回路、論理回路、およびマイクロコンピュータの基本的な知識が必 要です。

# 2. レジスタ図の見方

レジスタ図で使用する記号、用語を説明します。

**\***1

: 用途に応じて"0"または"1"にしてください。 : "0"にしてください。 空白

: "1" にしてください。 1

: 何も配置されてないビットです。

\*2

RW:読むとビットの状態が読めます。書くと有効データになります。 :読むとビットの状態が読めます。書いた値は無効になります。 WO:書くと有効データになります。ビットの状態は読めません。

: 何も配置されていないビットです。

\*3

## ・予約ビット

予約ビットです。指定された値にしてください。

\* 4

#### ・何も配置されていない

該当ビットには何も配置されていません。将来、周辺展開により新しい機能を持つ可能性があります ので、書く場合は"0"を書いてください。

# ・設定しないでください

設定した場合の動作は保証されません。

#### ・動作モードによって機能が異なる

周辺機能のモードによってビットの機能が変わります。各モードのレジスタ図を参照してください。

# 3. M16Cファミリ関連ドキュメント

M16Cファミリでは次のドキュメントを用意しています。

| ドキュメントの種類                | 記載内容                           |  |

|--------------------------|--------------------------------|--|

| ショートシート                  | ハードウェアの概要                      |  |

| データシート                   | ハードウェアの概要と電気的特性                |  |

| ハードウェアマニュアル              | ハードウェアの仕様(ピン配置、メモリマップ、周辺機能の仕様、 |  |

|                          | 電気的特性、タイミング)                   |  |

| ソフトウェアマニュアル              | 命令 (アセンブリ言語) の動作の詳細            |  |

| アプリケーションノート              | 周辺機能の応用例                       |  |

|                          | 参考プログラム                        |  |

|                          | M16Cファミリ入門用基本機能説明              |  |

|                          | アセンブリ言語、C言語によるプログラムの作成方法       |  |

| RENESAS TECHNICAL UPDATE | 製品の仕様、ドキュメント等に関する速報            |  |

注1. 最新版を使用してください。最新版はルネサステクノロジホームページに掲載されています。

# 目次

| 番地  | 也別ページ早見表                           | B-1 |

|-----|------------------------------------|-----|

| 1.  | 概要                                 | 1   |

| 1.1 | 応用                                 | 1   |

| 1.2 | 性能概要                               | 2   |

| 1.3 | ブロック図                              | 3   |

| 1.4 | 製品一覧                               | 4   |

| 1.5 | ピン接続図                              | 5   |

| 1.6 | 端子の機能説明                            | 6   |

| 2.  | 中央演算処理装置(CPU)                      | 7   |

| 2.1 | データレジスタ(R0、R1、R2、R3)               | 7   |

| 2.2 | アドレスレジスタ(A0、A1)                    | 7   |

| 2.3 | フレームベースレジスタ(FB)                    | 8   |

| 2.4 | 割り込みテーブルレジスタ(INTB)                 | 8   |

| 2.5 | プログラムカウンタ(PC)                      | 8   |

| 2.6 | ユーザスタックポインタ(USP)、割り込みスタックポインタ(ISP) | 8   |

| 2.7 | スタティックベースレジスタ(SB)                  | 8   |

| 2.8 | フラグレジスタ(FLG)                       | 8   |

| 2   | 2.8.1 キャリフラグ(Cフラグ)                 | 8   |

| 2   | 2.8.2 デバッグフラグ(Dフラグ)                | 8   |

| 2   | 2.8.3 ゼロフラグ(Zフラグ)                  | 8   |

| 2   | 2.8.4 サインフラグ(Sフラグ)                 | 8   |

| 2   | 2.8.5 レジスタバンク指定フラグ(Bフラグ)           | 8   |

| 2   | 2.8.6 オーバフローフラグ(Oフラグ)              | 8   |

| 2   | 2.8.7 割り込み許可フラグ(Iフラグ)              | 8   |

| 2   | 2.8.8 スタックポインタ指定フラグ(Uフラグ)          | 8   |

| 2   | 2.8.9 プロセッサ割り込み優先レベル(IPL)          | 8   |

| 2   | 2.8.10 予約領域                        | 8   |

| 3. メモリ                                              | 9  |

|-----------------------------------------------------|----|

| 4. SFR                                              | 10 |

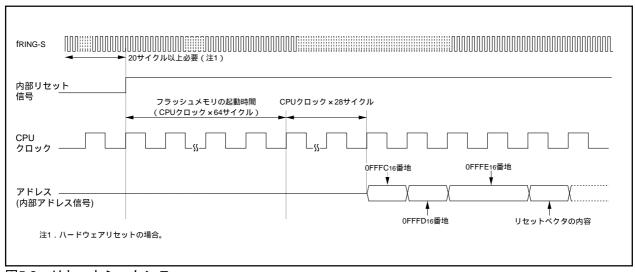

| 5. リセット                                             |    |

|                                                     |    |

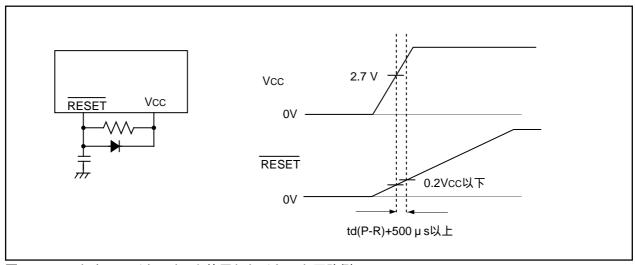

| 5.1 ハードウェアリセット                                      |    |

| 5.1.1 ハードウェアリセット1                                   |    |

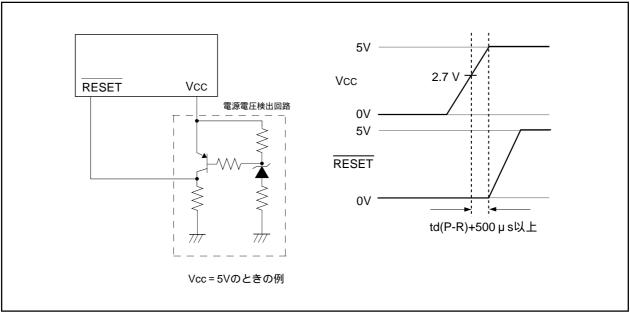

| 5.1.2 ハードウェアリセット2                                   |    |

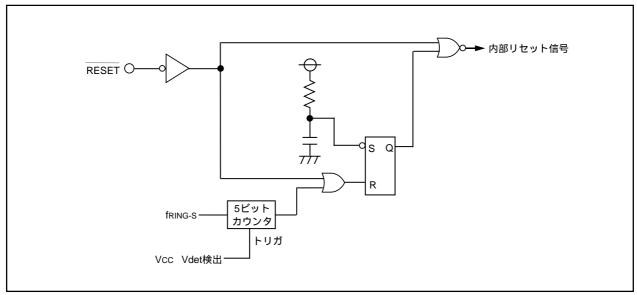

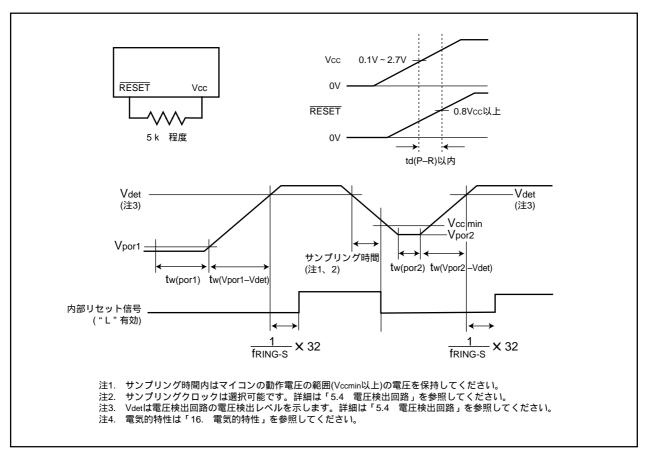

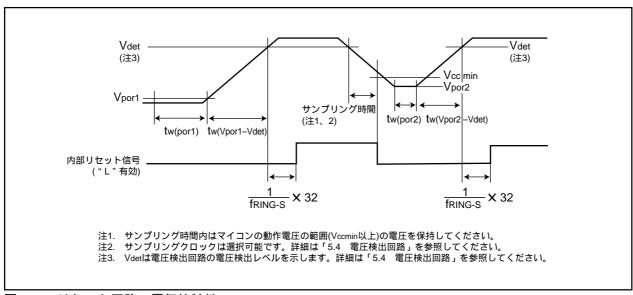

| 5.1.3 パワーオンリセット機能                                   |    |

| 5.2 ソフトウェアリセット                                      |    |

| 5.3 ウォッチドッグタイマリセット                                  |    |

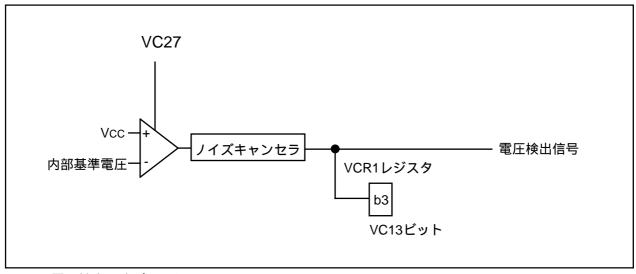

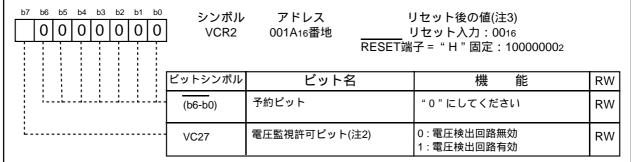

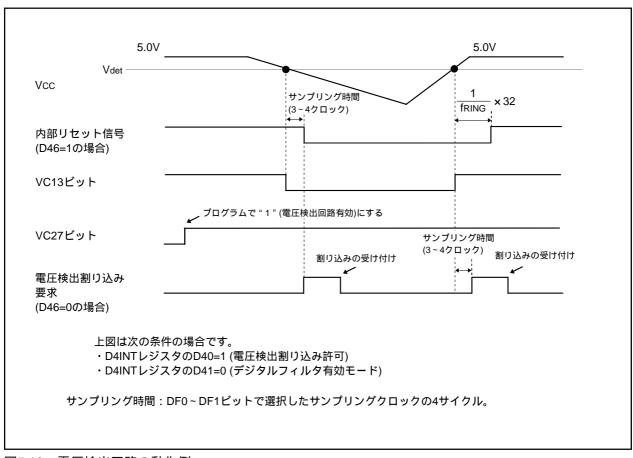

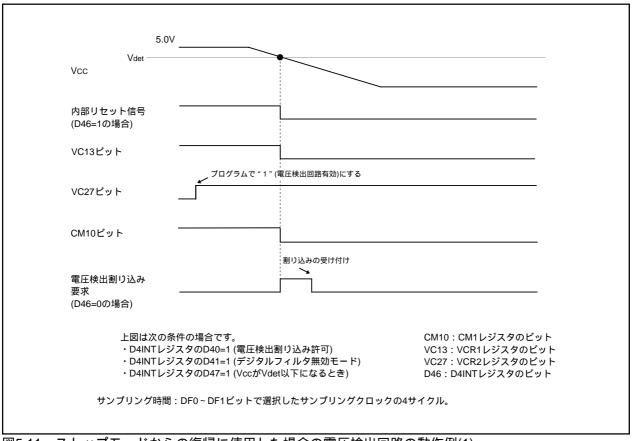

| 5.4 電圧検出回路                                          |    |

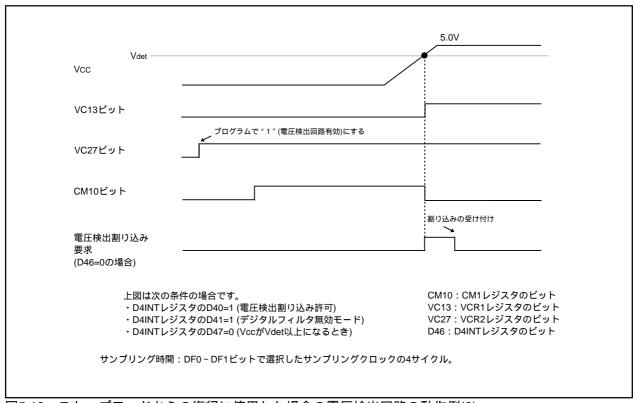

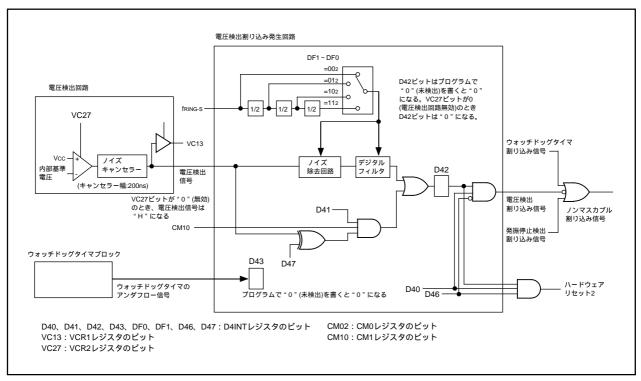

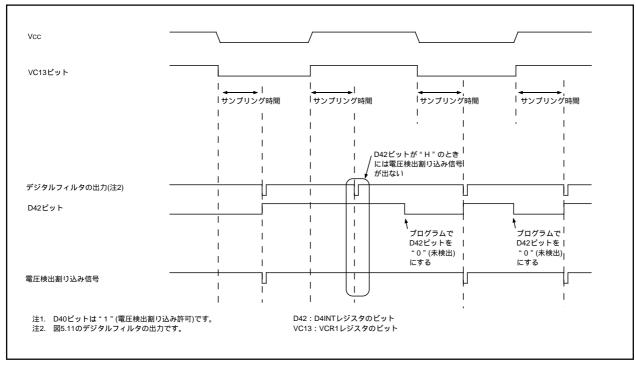

| 5.4.1 電圧検出割り込み                                      |    |

| 5.4.2 電圧検出割り込みによるストップモードからの復帰                       | 28 |

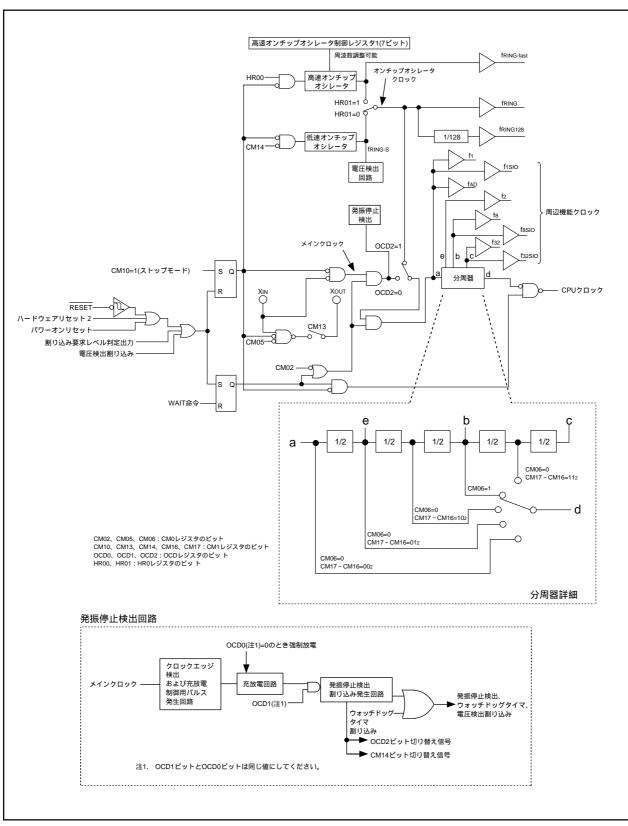

| 6. クロック発生回路                                         | 29 |

| 6.1 メインクロック                                         | 34 |

| 6.2 オンチップオシレータクロック                                  | 35 |

| 6.2.1 低速オンチップオシレータクロック                              | 35 |

| 6.2.2 高速オンチップオシレータクロック                              | 35 |

| 6.3 CPUクロックと周辺機能クロック                                | 36 |

| 6.3.1 CPUクロック                                       | 36 |

| 6.3.2 周辺機能クロック(f1、f2、f8、f32、fAD、f1SIO、f8SIO、f32SIO) | 36 |

| 6.3.3 fring, fring128                               |    |

| 6.3.3 fring-fast                                    | 36 |

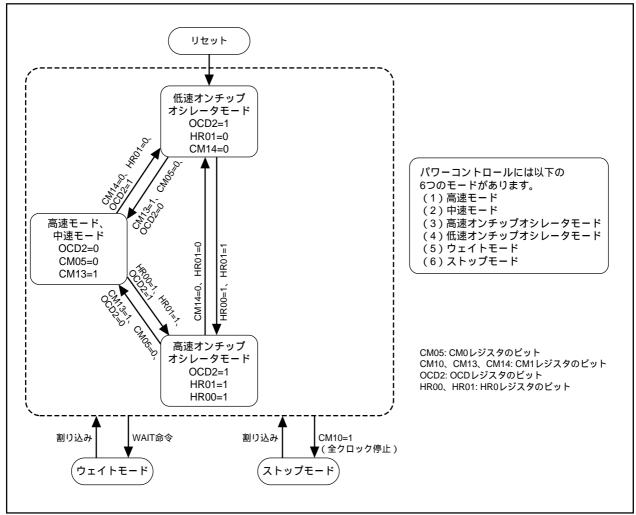

| 6.4 パワーコントロール                                       | 37 |

| 6.4.1 通常動作モード                                       | 37 |

| 6.4.2 ウェイトモード                                       |    |

| 6.4.3 ストップモード                                       | 40 |

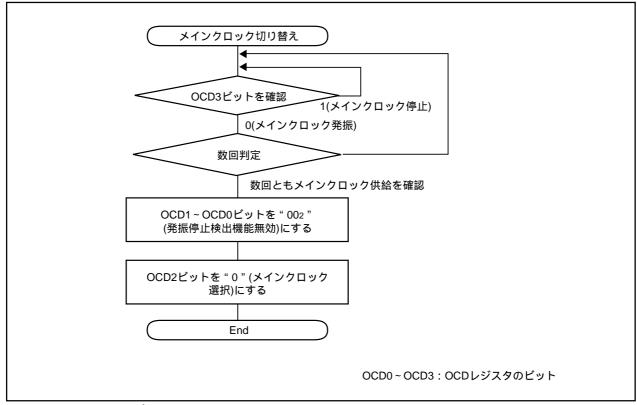

| 6.5 発振停止検出機能                                        |    |

| 6.5.1 発振停止検出機能の使用方法                                 |    |

| 7. プロテクト                                            |    |

|                                                     |    |

| 8. プロセッサモード                                         | 45 |

| 0.4 プロセッサエードの種類                                     | 45 |

| 9. バフ   | ス制御                    | 46 |

|---------|------------------------|----|

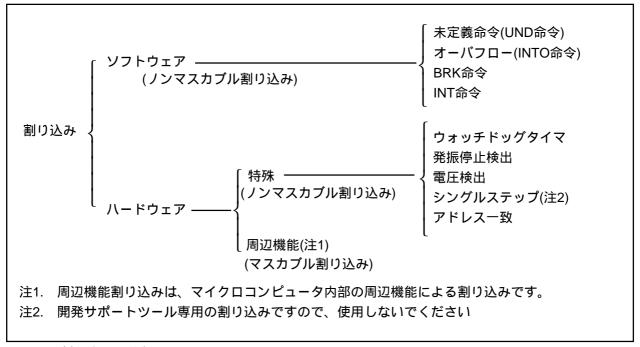

| 10. 割   | り込み                    | 47 |

| 10.1 割  | り込みの概要                 | 47 |

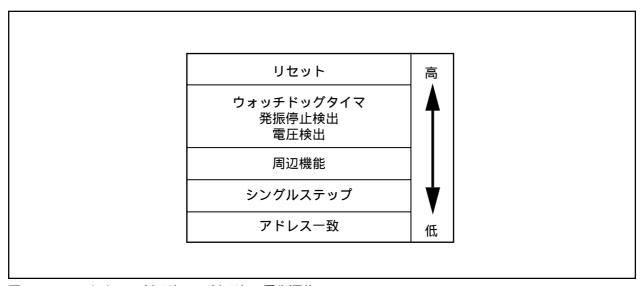

| 10.1.1  | 割り込みの分類                | 47 |

| 10.1.2  | ソフトウェア割り込み             | 48 |

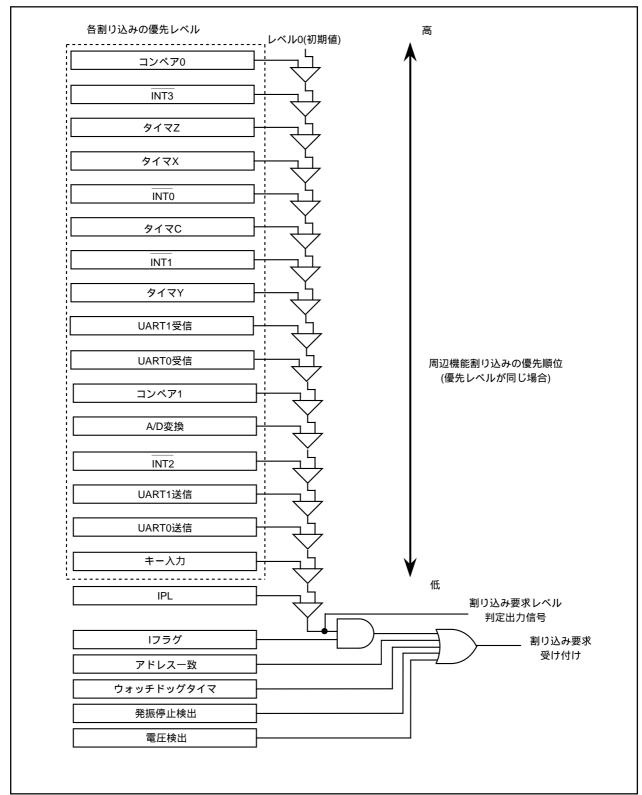

| 10.1.3  | ハードウェア割り込み             | 49 |

| 10.1.4  | 割り込みと割り込みベクタ           | 50 |

| 10.1.5  | 割り込み制御                 | 52 |

| 10.2 IN | _<br>T割り込み             | 60 |

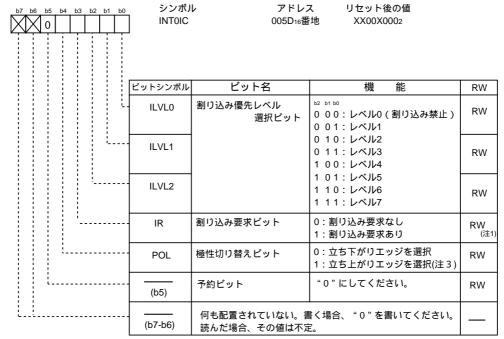

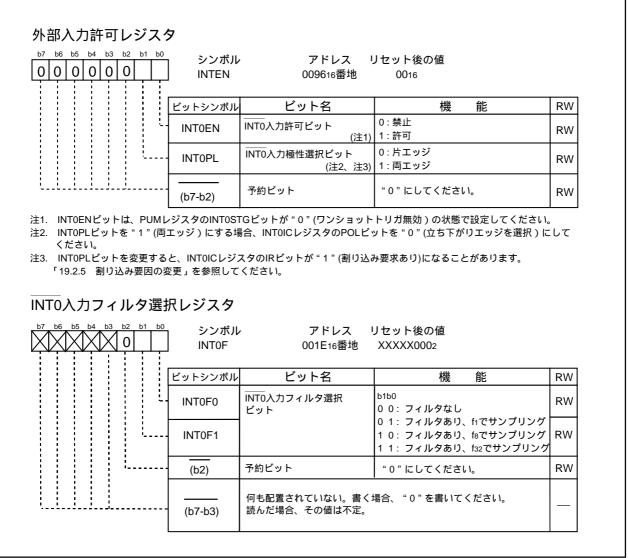

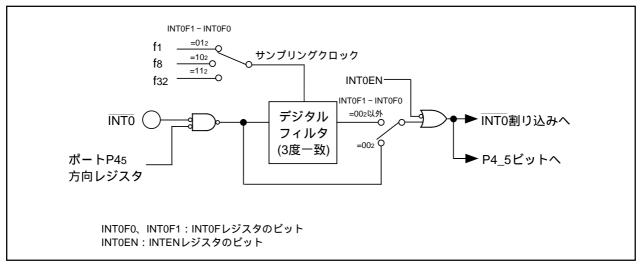

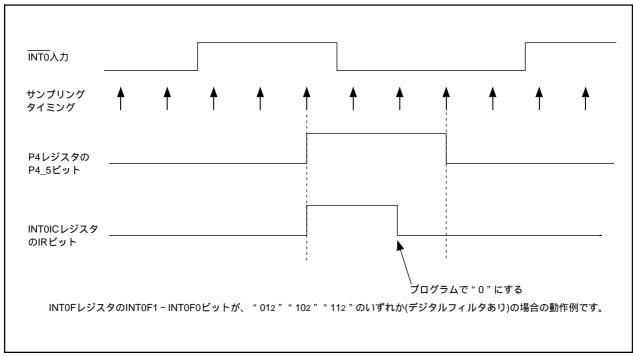

| 10.2.1  | <br>INT0割り込み           | 60 |

| 10.2.2  | <br>INT0入力フィルタ         | 61 |

| 10.2.3  | <br>INT1割り込み、INT2割り込み  | 62 |

| 10.2.4  | <br>INT3割り込み           | 63 |

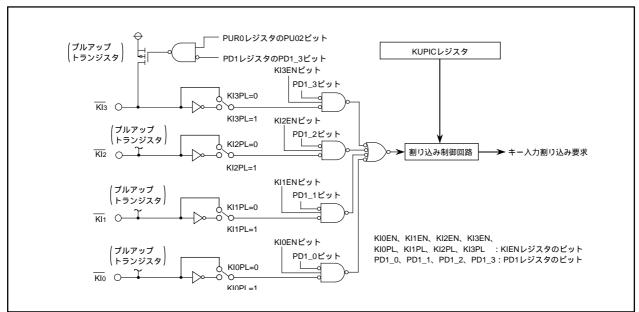

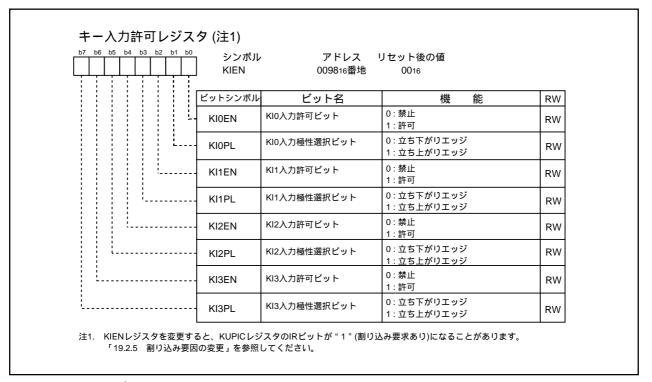

| 10.3 +  | 一入力割り込み                | 65 |

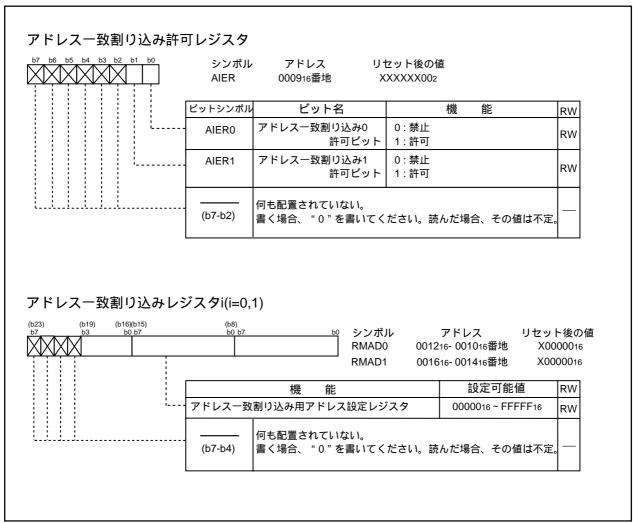

| 10.4 ア  | ドレス一致割り込み              | 66 |

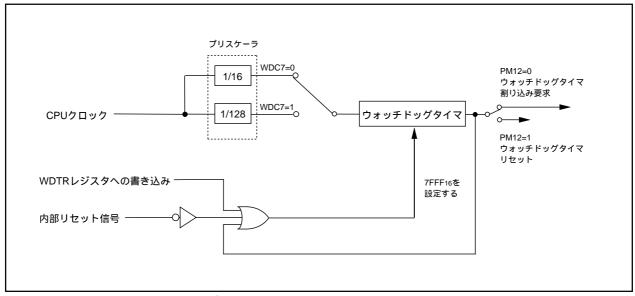

| 11. ウ   | ォッチドッグタイマ              | 68 |

| 12. タ   | イマ                     | 70 |

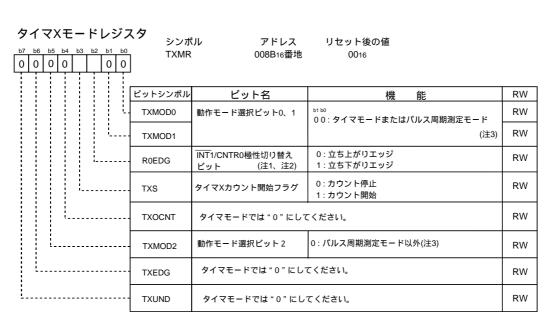

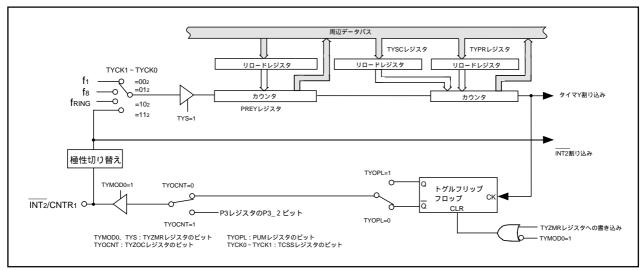

| 12.1 タ  | イマX                    | 71 |

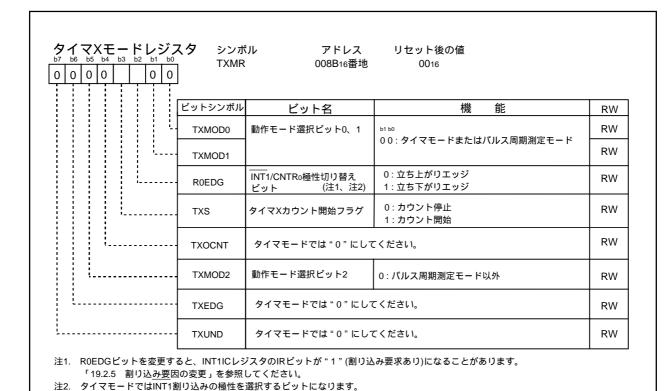

| 12.1.1  | タイマモード                 | 73 |

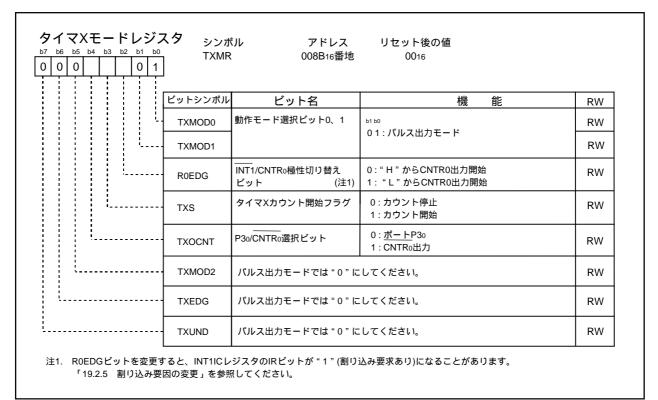

| 12.1.2  | パルス出力モード               | 74 |

| 12.1.3  | イベントカウンタモード            | 75 |

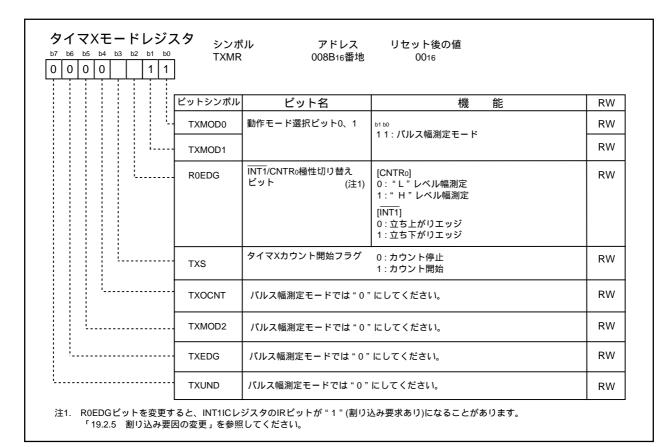

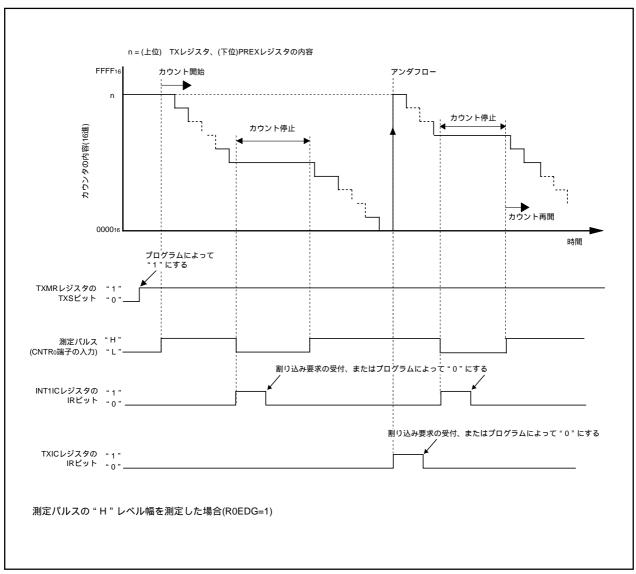

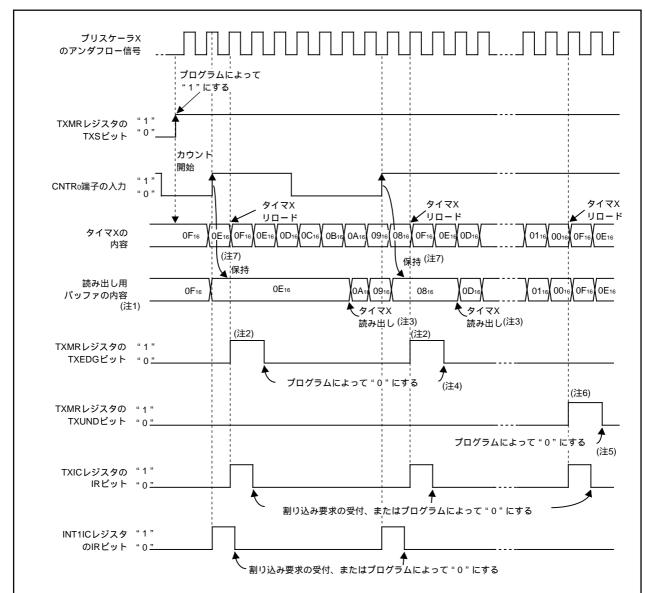

| 12.1.4  | パルス幅測定モード              | 76 |

| 12.1.5  | パルス周期測定モード             | 78 |

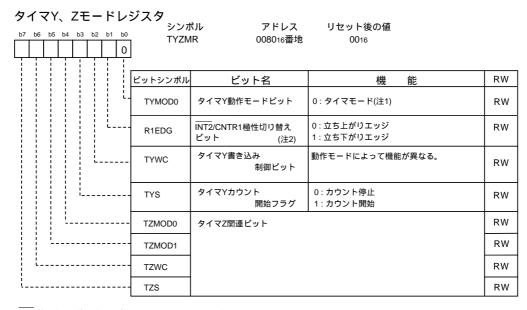

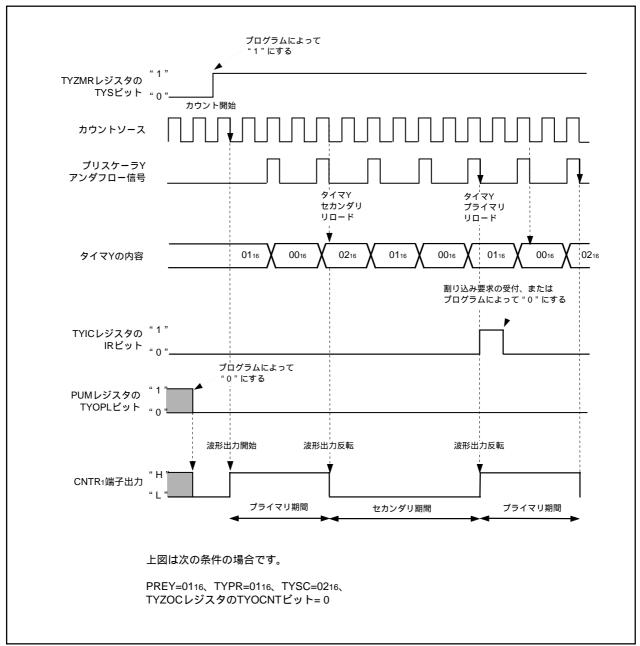

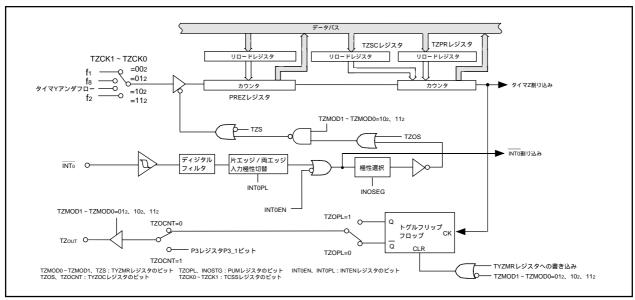

| 12.2 タ  | 1 7 Y                  | 80 |

| 12.2.1  | タイマモード                 | 83 |

| 12.2.2  | プログラマブル波形発生モード         | 85 |

| 12.3 タ  | イマZ                    | 88 |

| 12.3.1  | タイマモード                 | 91 |

| 12.3.2  | プログラマブル波形発生モード         | 93 |

| 12.3.3  | プログラマブルワンショット発生モード     | 95 |

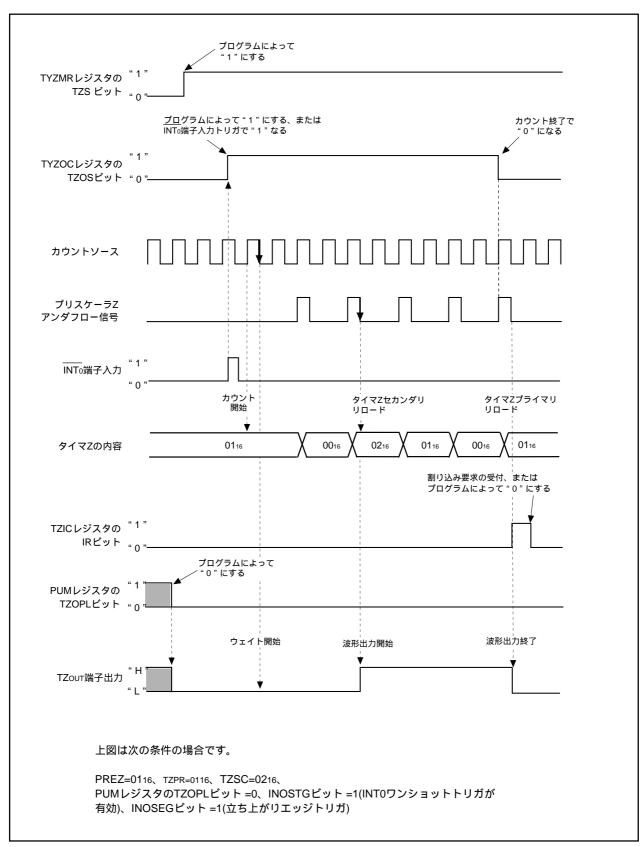

| 12.3.4  | プログラマブルウェイトワンショット発生モード | 98 |

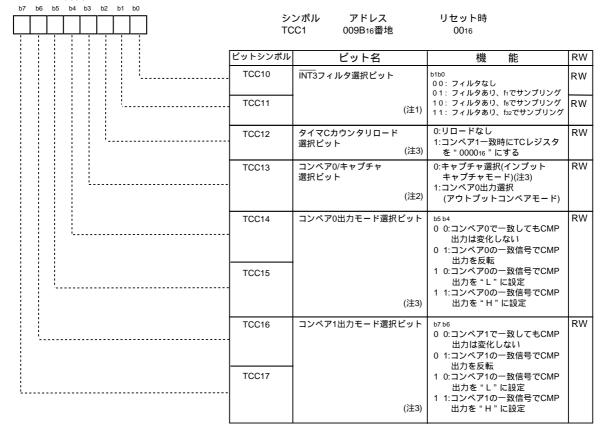

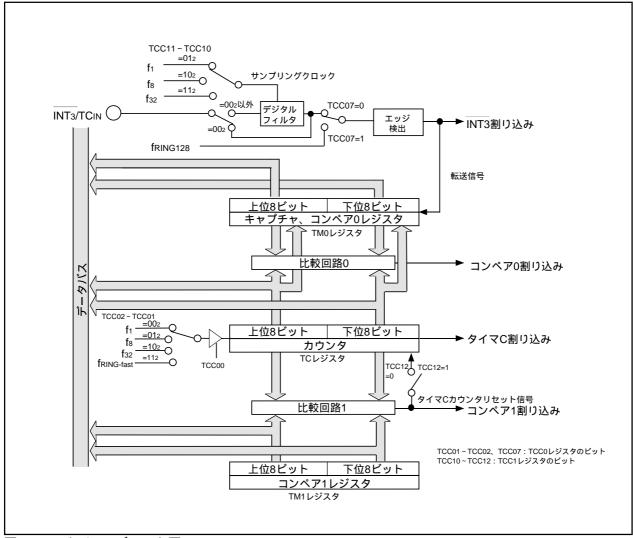

| 12.4 | タイマC                                          | 101 |

|------|-----------------------------------------------|-----|

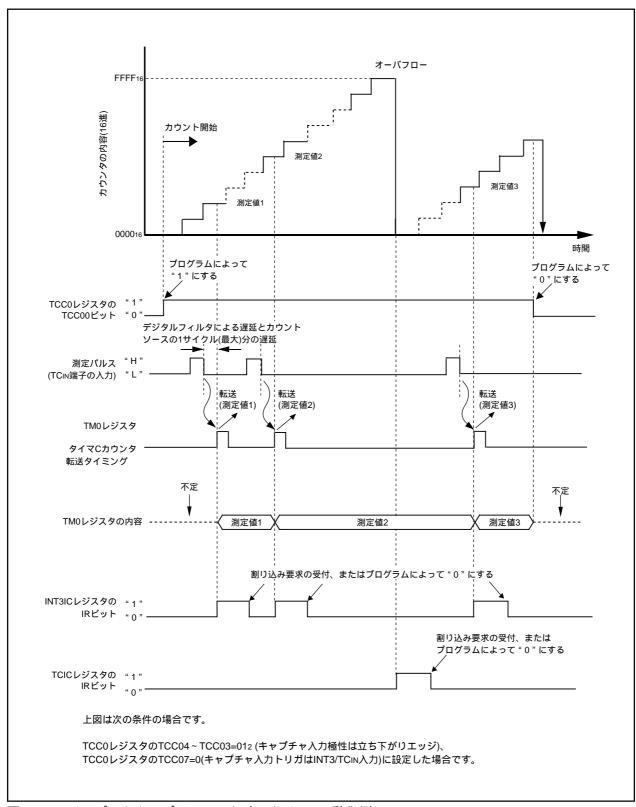

| 12.  | .4.1 インプットキャプチャモード                            | 105 |

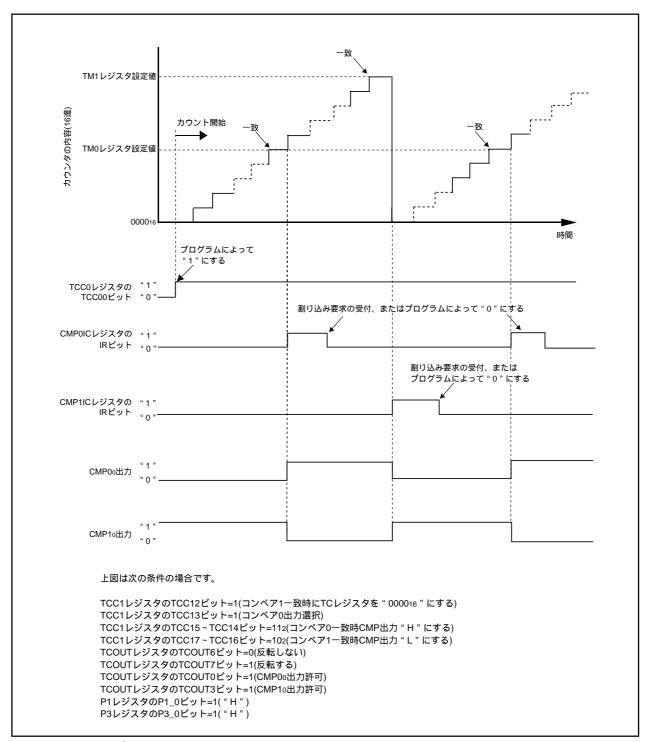

| 12.  | .4.2 アウトプットコンペアモード                            | 107 |

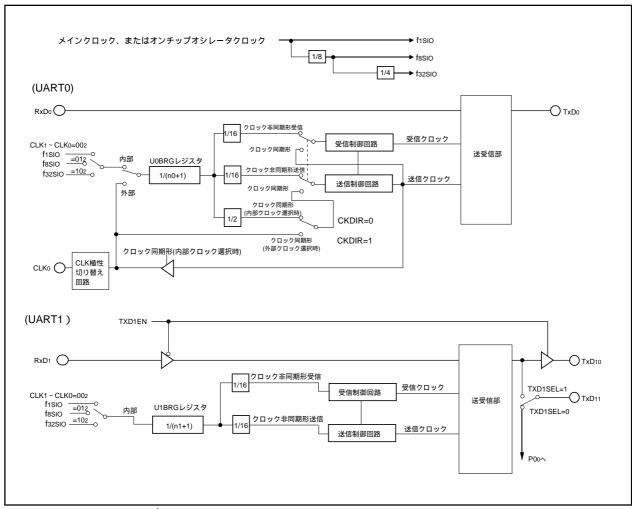

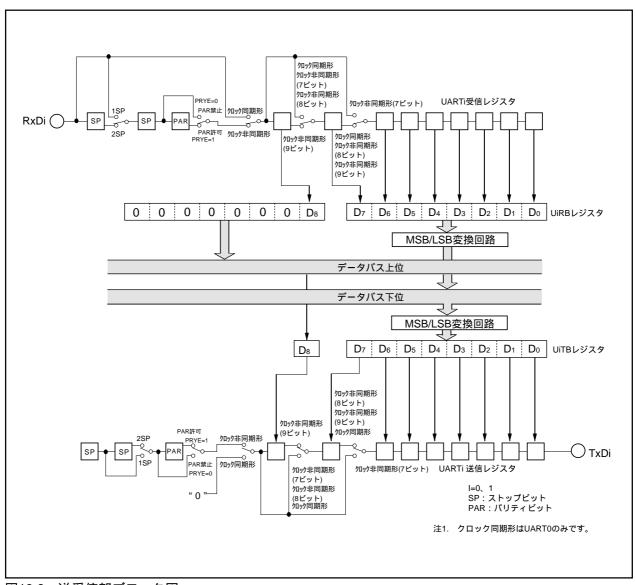

| 13.  | シリアルインタフェース                                   | 109 |

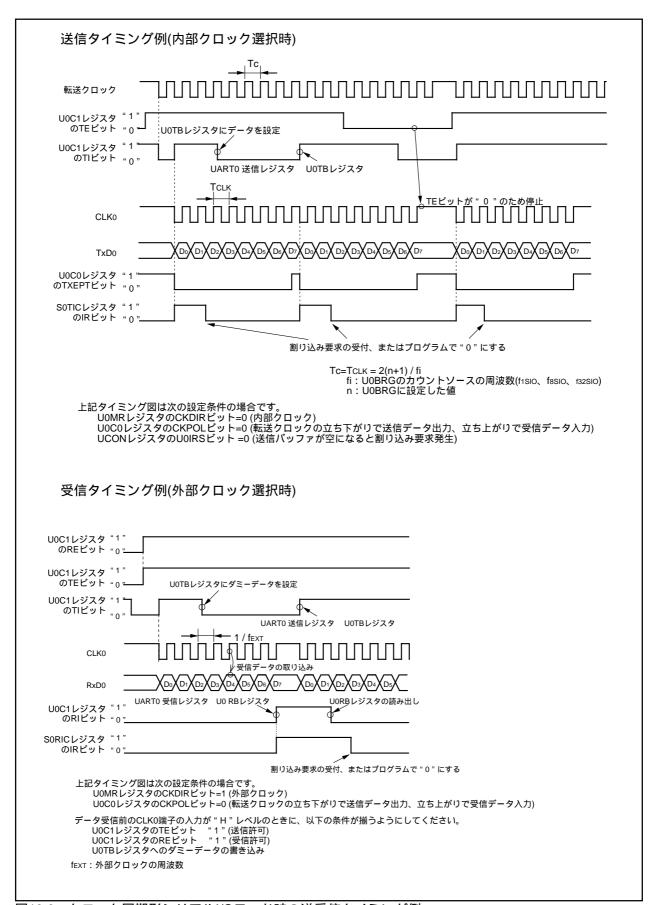

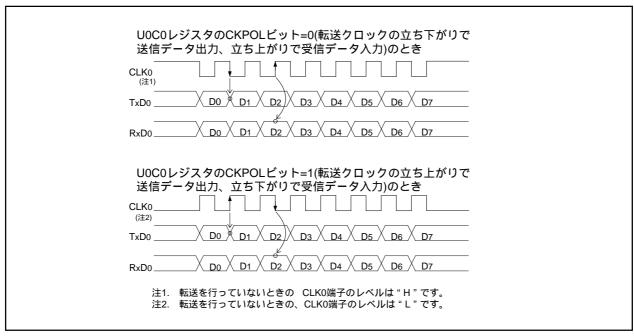

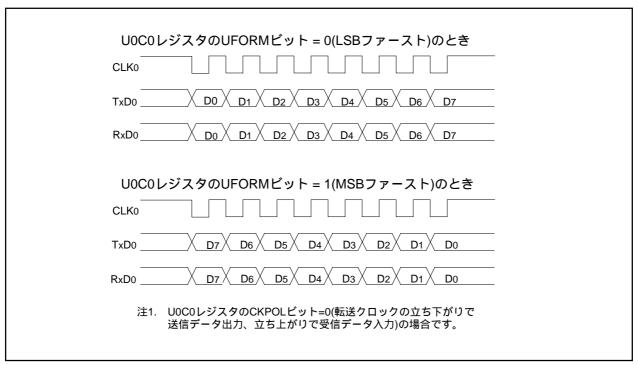

| 13.1 | クロック同期形シリアルI/Oモード                             | 114 |

| 13.  | 1.1 極性選択機能                                    | 117 |

| 13.  | .1.2 LSBファースト、MSBファースト選択                      | 117 |

| 13.  | 1.3 連続受信モード                                   | 118 |

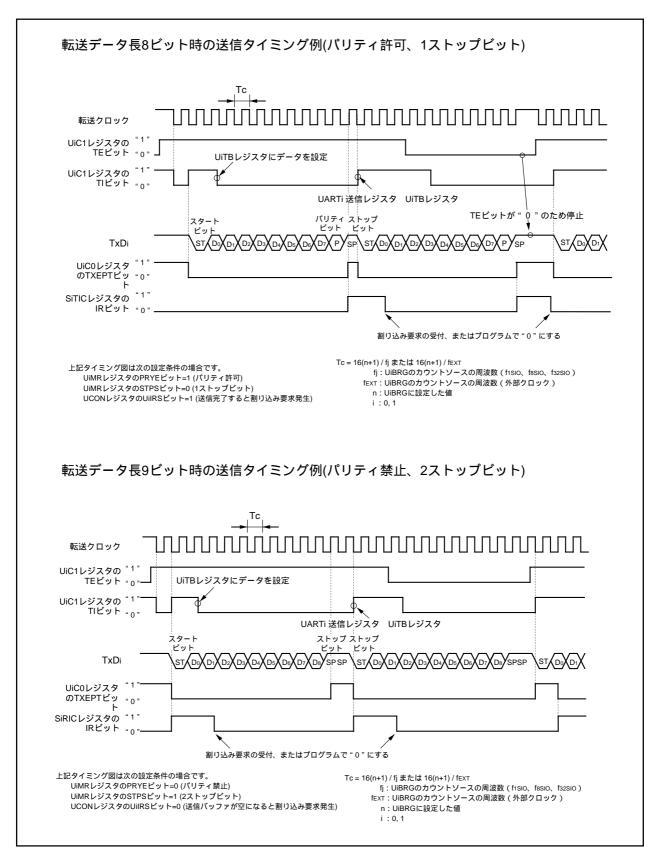

| 13.2 | クロック非同期形シリアルI/O(UART)モード                      | 119 |

| 13.  | .2.1 TxD10/RxD1選択機能(UART1)                    | 122 |

| 13.  | .2.2 TxD11選択機能(UART1)                         | 122 |

| 13.  | .2.3 ビットレート                                   | 123 |

| 14.  | A/Dコンバータ                                      | 124 |

| 14.1 | 単発モード                                         | 128 |

| 14.2 | 繰り返しモード                                       | 130 |

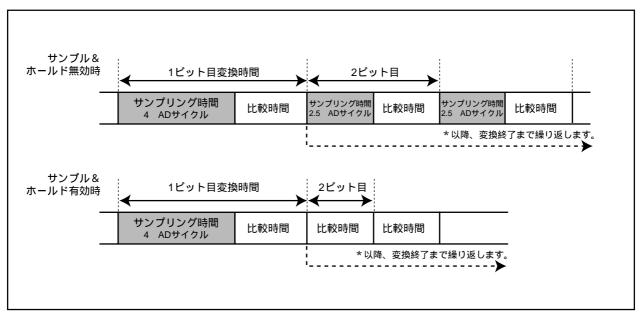

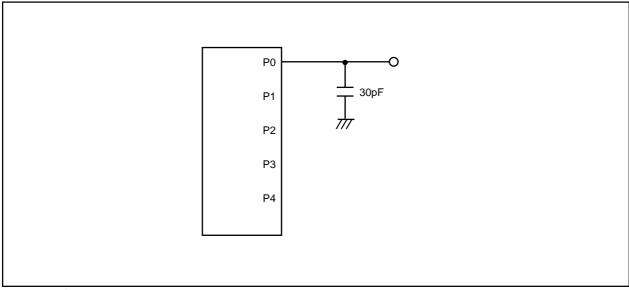

| 14.3 | サンプル&ホールド                                     | 132 |

| 14.4 | A/D変換サイクル数                                    | 132 |

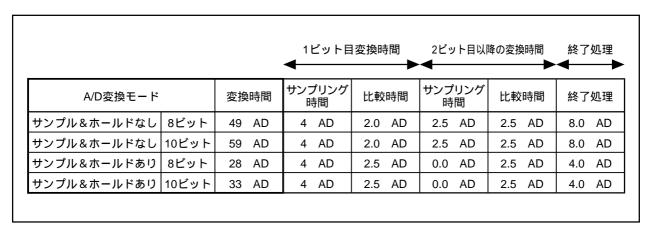

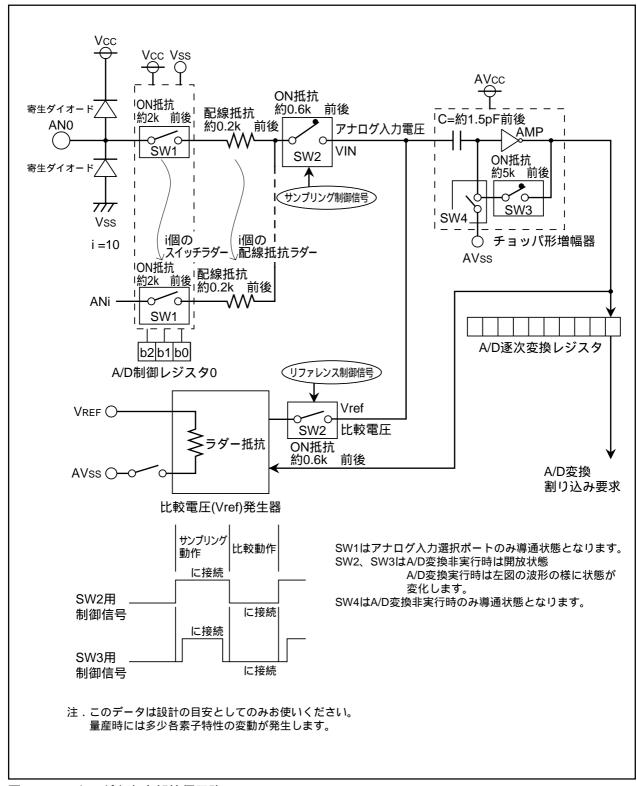

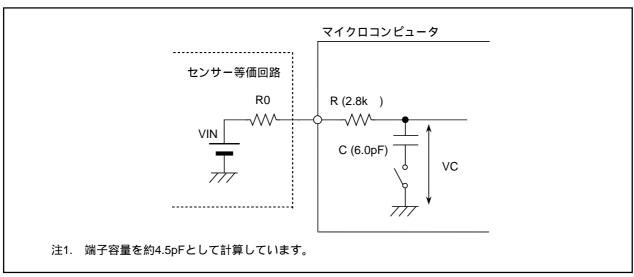

| 14.5 | アナログ入力内部等価回路                                  | 133 |

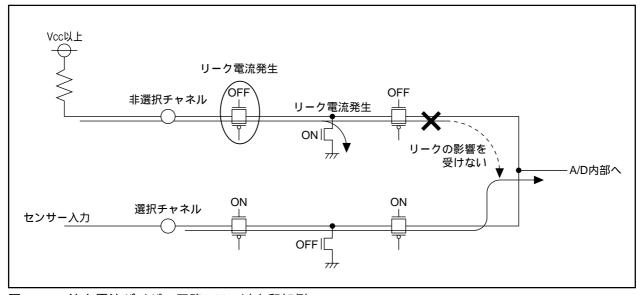

| 14.6 | 注入電流バイパス回路                                    | 134 |

| 14.7 | A/D変換時のセンサーの出力インピーダンス                         | 135 |

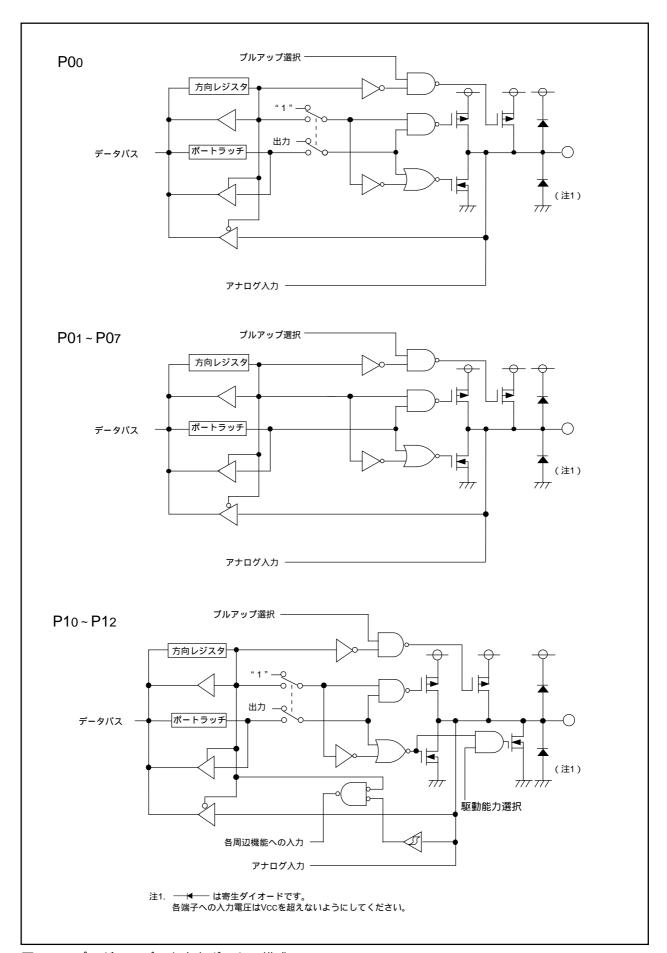

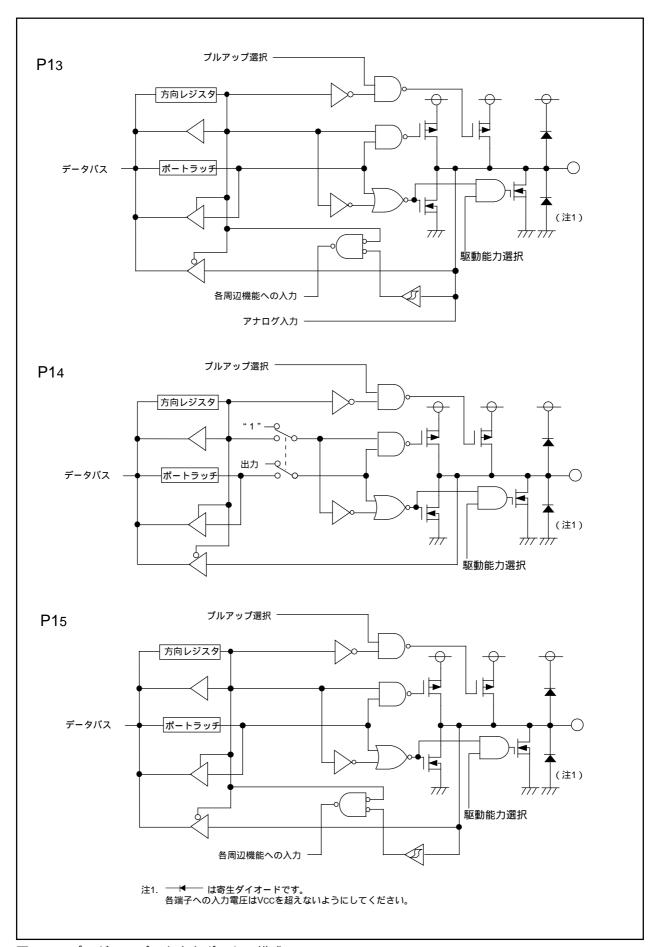

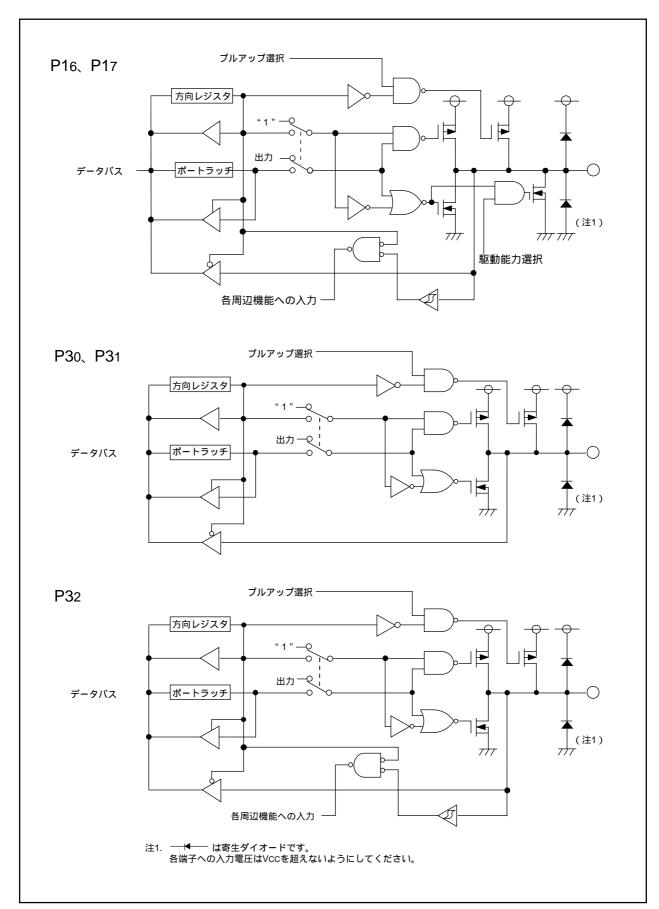

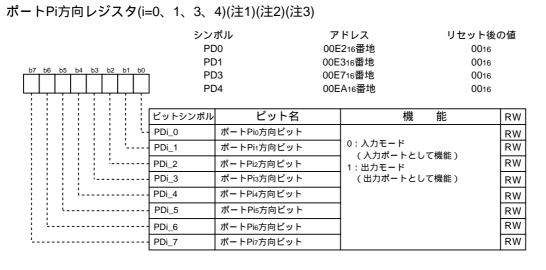

| 15.  | プログラマブル入出力ポート                                 | 136 |

| 15.1 | 機能説明                                          | 136 |

| 15.  | .1.1 ポートPi方向レジスタ(PDiレジスタ i=0、1、3、4)           | 136 |

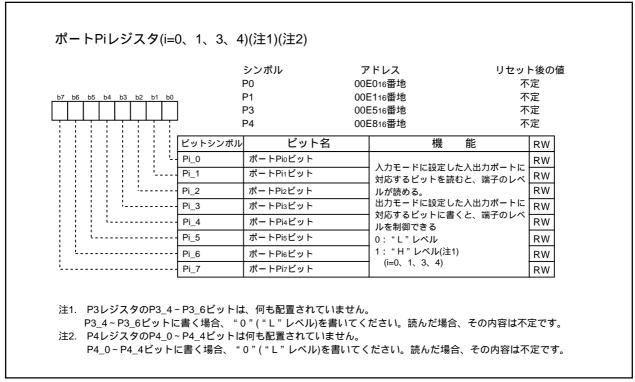

| 15.  | .1.2 ポートPiレジスタ(Piレジスタ i=0、1、3、4)              | 136 |

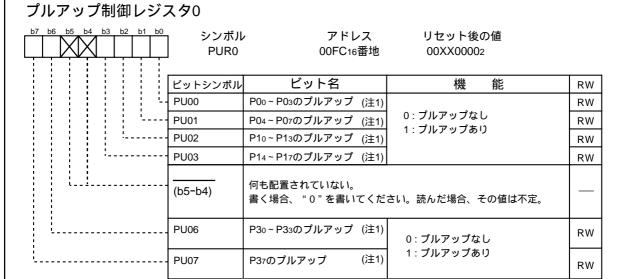

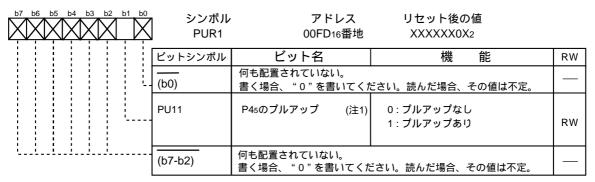

| 15.  | .1.3 プルアップ制御レジスタ0、プルアップ制御レジスタ1(PUR0、PUR1レジスタ) | 136 |

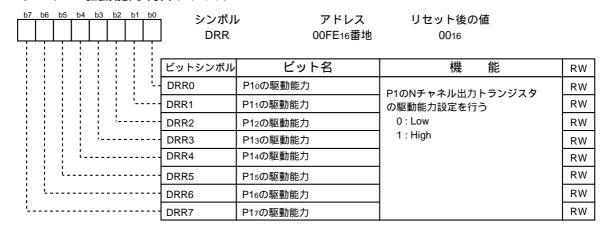

| 15.  | 1.4 ポートP1駆動能力制御レジスタ(DRRレジスタ)                  | 136 |

| 15.2 | ポートの設定                                        | 144 |

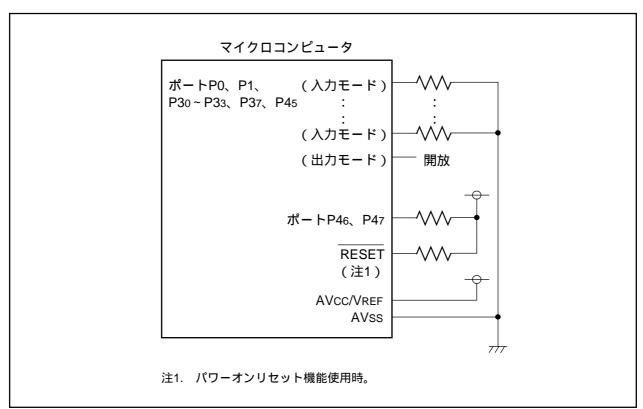

| 15.3 | 未使用端子の処理                                      | 150 |

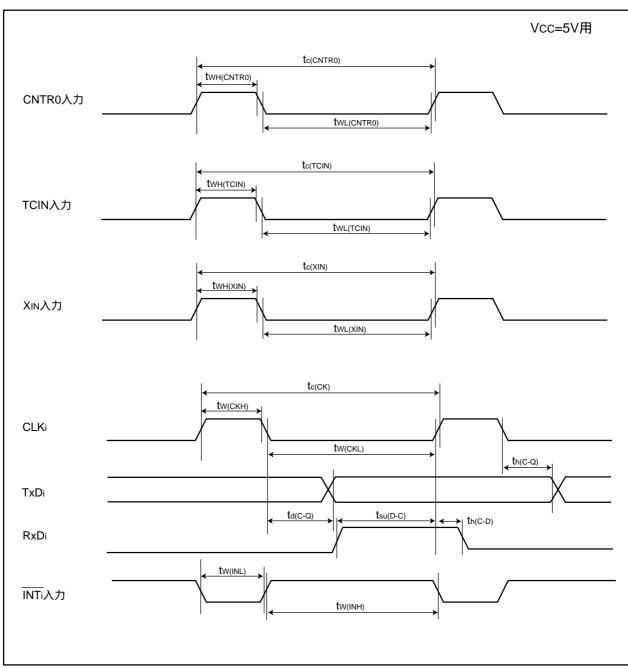

| 16.  | 電気的特性                                         | 151 |

|      | フラッシュメモリ版                                     |     |

| 17.1 | 概要                                            | 163 |

| 17.2 | メモリ配置                                         | 164 |

| 17 2 | フラッシュメモリ書き換え替止機能                              | 165 |

| 17.3.1 IDコードチェック機能     | 165 |

|------------------------|-----|

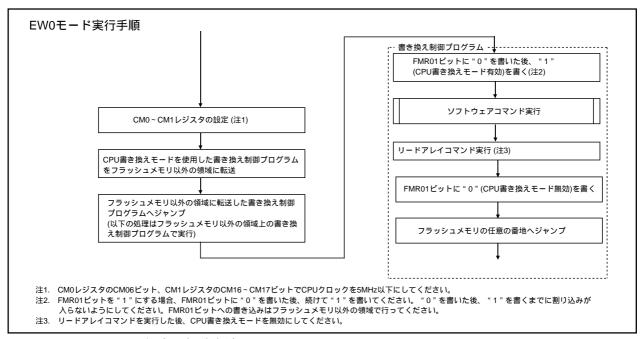

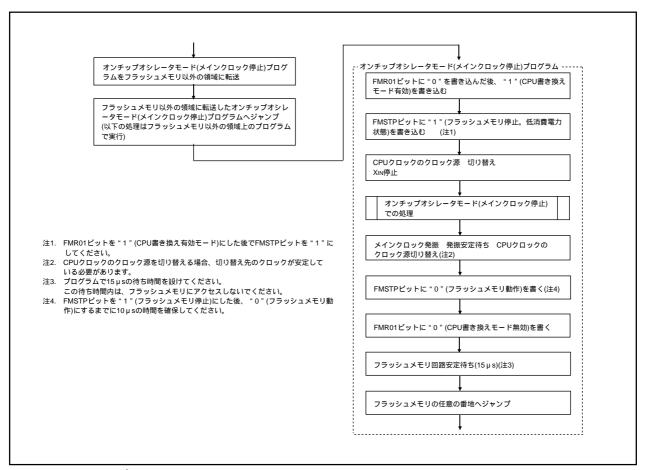

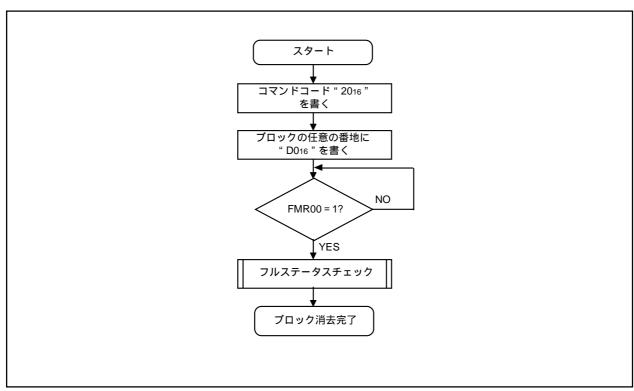

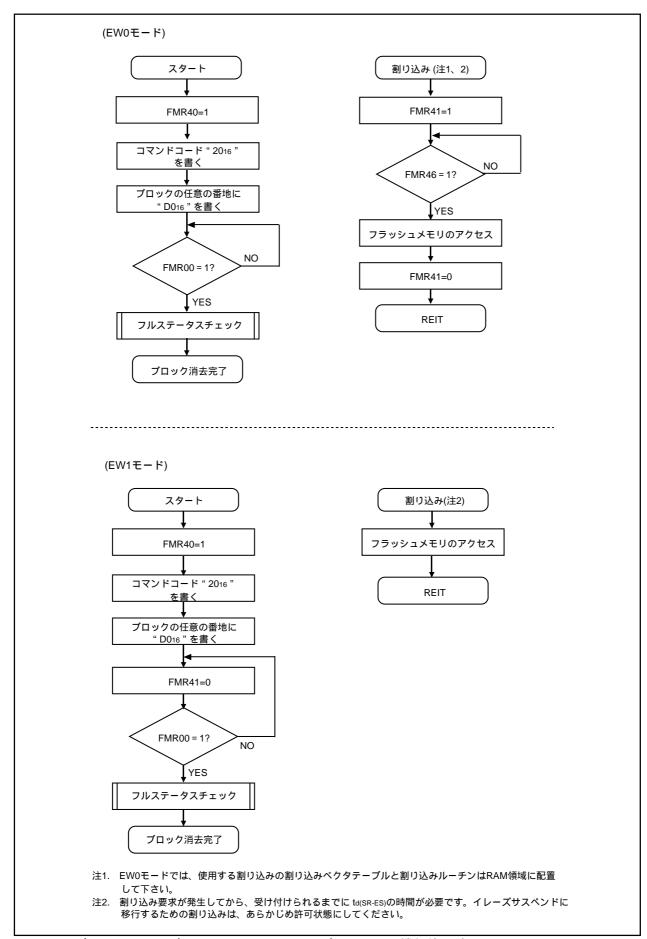

| 17.4 CPU書き換えモード        | 167 |

| 17.4.1 EW0モード          | 168 |

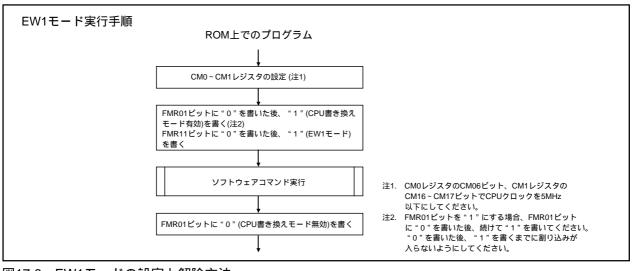

| 17.4.2 EW1モード          | 168 |

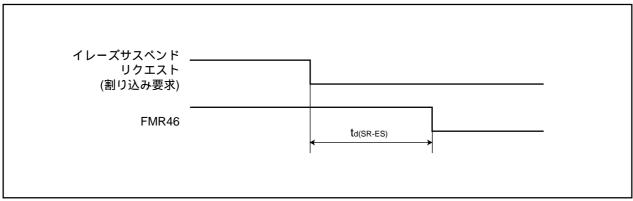

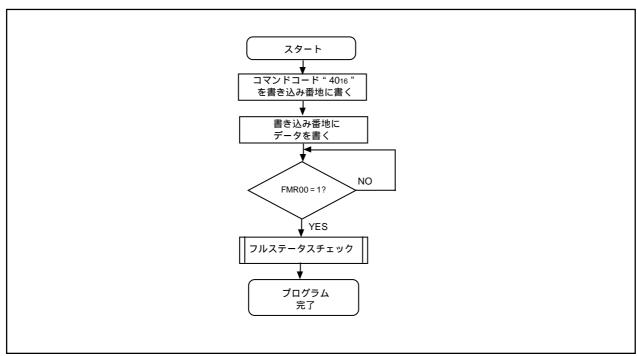

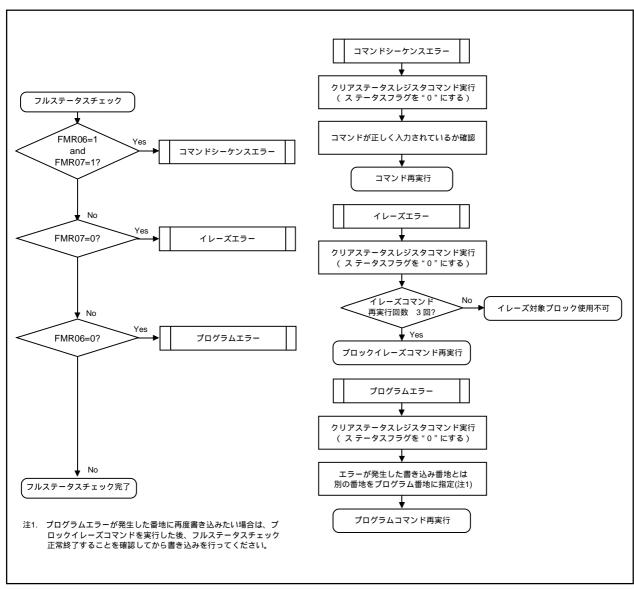

| 17.4.3 ソフトウェアコマンド      | 174 |

| 17.4.4. ステータスレジスタ      | 178 |

| 17.4.5 フルステータスチェック     | 179 |

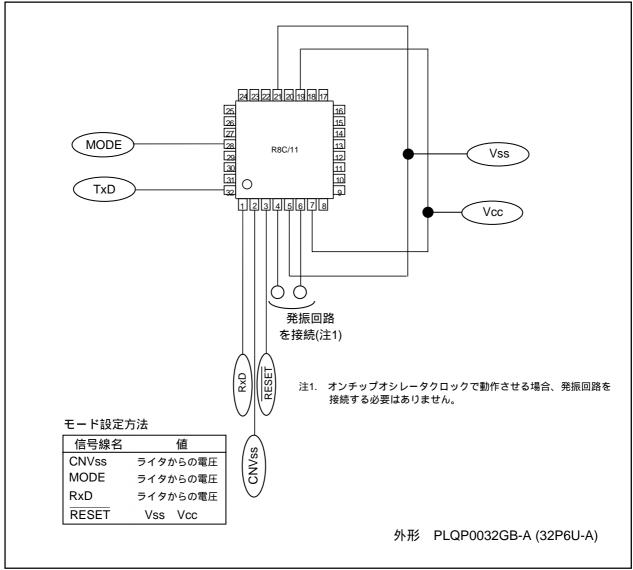

| 17.5 標準シリアル入出力モード      | 181 |

| 17.5.1 IDコードチェック機能     | 181 |

| 18. オンチップデバッガ          | 185 |

| 18.1 アドレス一致割り込み        | 185 |

| 18.2 シングルステップ割り込み      | 185 |

| 18.3 UART1             | 185 |

| 18.4 BRK命令             | 185 |

| 19. 使用上の注意事項           | 186 |

| 19.1 ストップモード、ウェイトモード   | 186 |

| 19.1.1 ストップモード         | 186 |

| 19.1.2 ウェイトモード         | 186 |

| 19.2 割り込み              | 187 |

| 19.2.1 00000₁6番地の読み出し  | 187 |

| 19.2.2 SPの設定           | 187 |

| 19.2.3 外部割り込み、キー入力割り込み | 187 |

| 19.2.4 ウォッチドッグタイマ割り込み  | 187 |

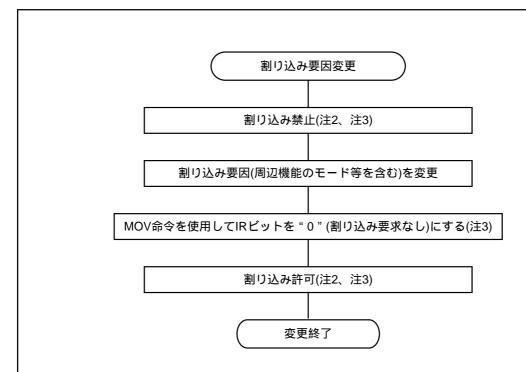

| 19.2.5 割り込み要因の変更       | 188 |

| 19.2.6 割り込み制御レジスタの変更   | 189 |

| 19.3 クロック発生回路          | 190 |

| 19.3.1 発振停止検出機能        | 190 |

| 19.3.2 発振回路定数          | 190 |

| 19.4 タイマ               | 191 |

| 19.4.1 タイマX、タイマY、タイマ Z | 191 |

| 19.4.2 タイマX            | 191 |

| 19.4.3 タイマY            | 191 |

| 19.4.4 タイマZ            | 191 |

| 19.4.5 タイマC            | 191 |

| 19.5 | シリアルインタフェース                       | 192   |

|------|-----------------------------------|-------|

| 19.6 | A/Dコンバータ                          | 193   |

| 19.7 | フラッシュメモリ                          | 194   |

| 19.  | 7.1 CPU書き換えモード                    | 194   |

| 19.8 | ノイズに関する注意事項                       | 196   |

| 20.  | オンチップデバッガの注意事項                    | 197   |

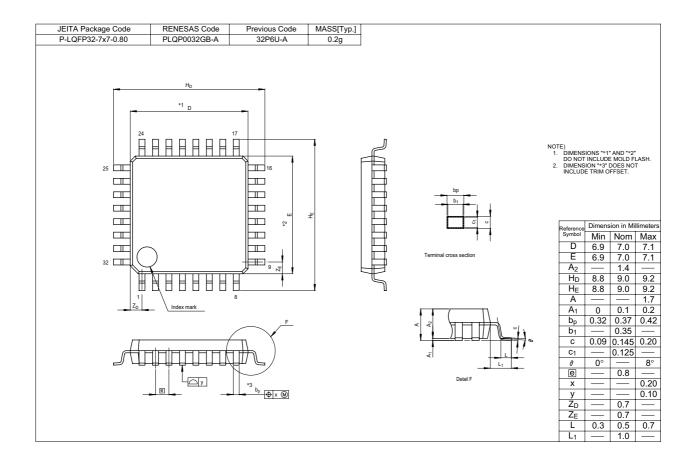

| 付録   | 1. 外形寸法図                          | 198   |

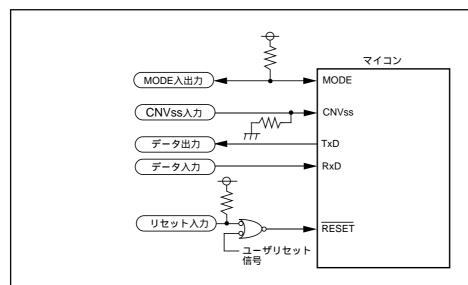

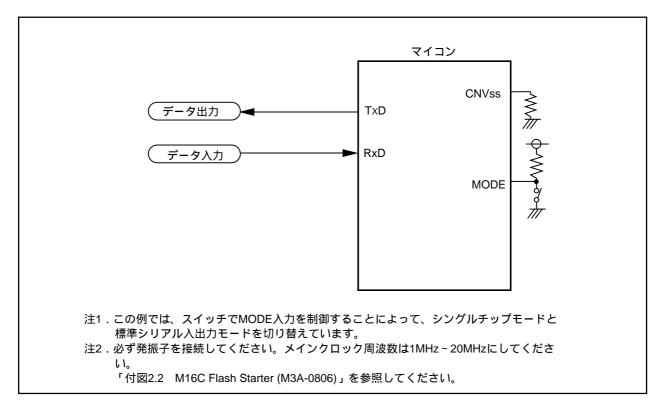

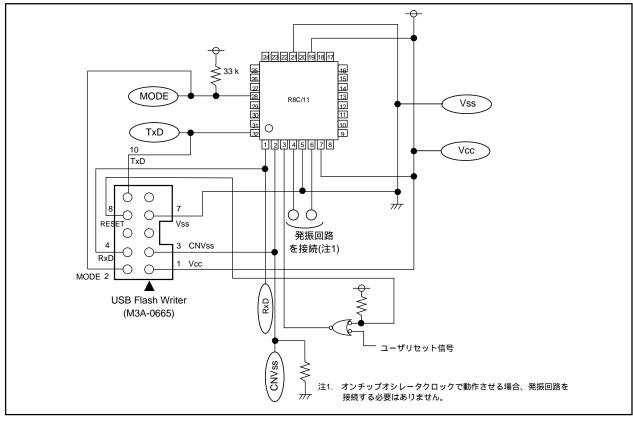

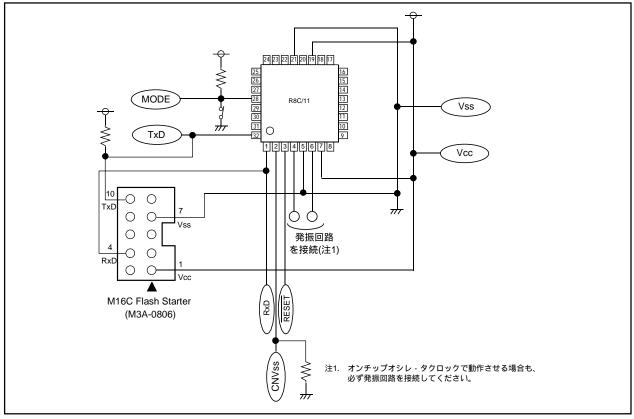

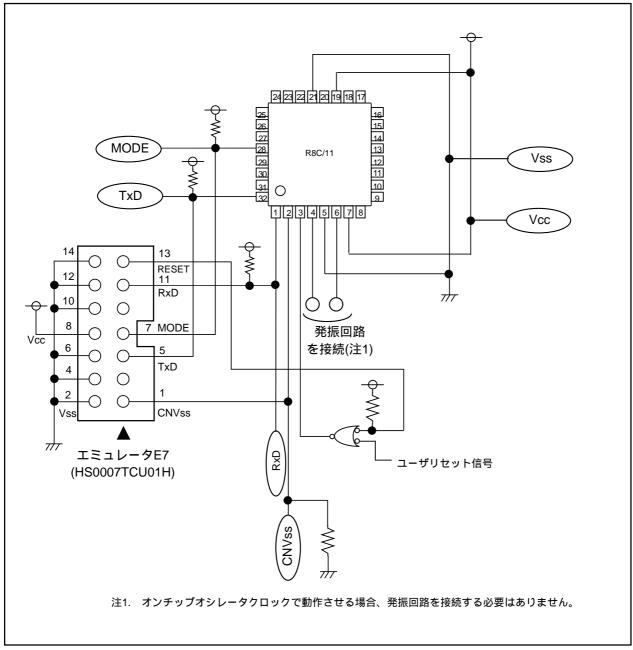

| 付録   | 2. シリアルライタとオンチップデバッギングエミュレータとの接続例 | _ 199 |

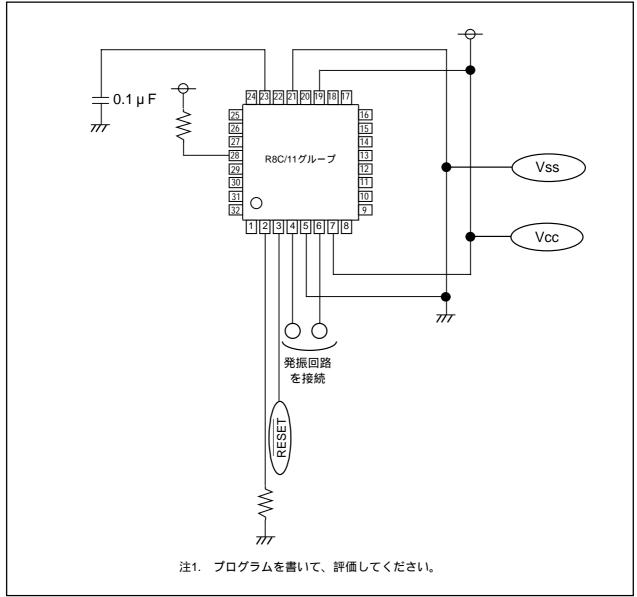

| 付録:  | 3. 発振評価回路例                        | 201   |

| SFR  | レジスタ索引                            | 202   |

# 番地別ページ早見表

| 番地               | レジスタ                            | シンボル                                    | 掲載ページ |

|------------------|---------------------------------|-----------------------------------------|-------|

| 000016           |                                 |                                         |       |

| 000116           |                                 |                                         |       |

| 000216           |                                 |                                         |       |

| 000316           |                                 |                                         |       |

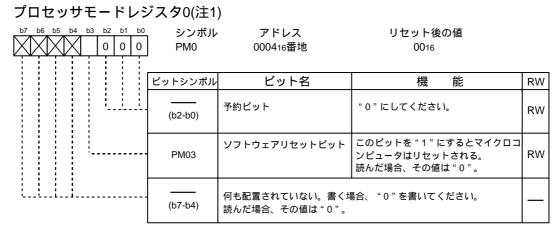

| 000416           | プロセッサモードレジスタ0                   | PM0                                     | 45    |

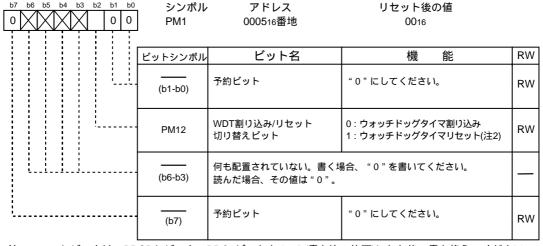

| 000516           | プロセッサモードレジスタ1                   | PM1                                     | 45    |

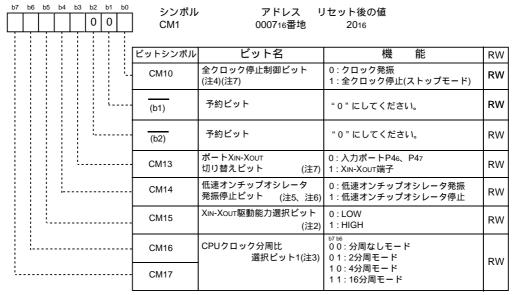

| 000616           | システムクロック制御レジスタ0                 | CM0                                     | 31    |

| 000716           | システムクロック制御レジスタ1                 | CM1                                     | 31    |

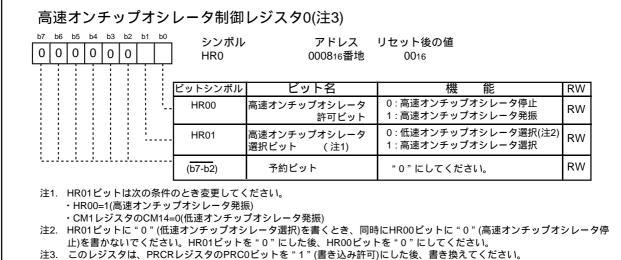

| 000816           | 高速オンチップオシレータ制御レジスタ0             | HR0                                     | 33    |

| 000916           | アドレスー致割り込み許可レジスタ                | AIER                                    | 67    |

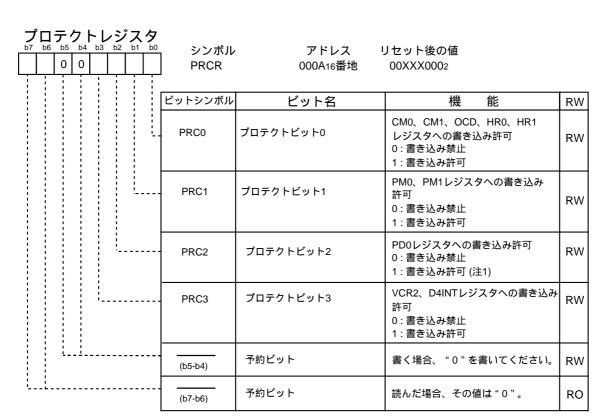

| 000A16           | プロテクトレジスタ                       | PRCR                                    | 44    |

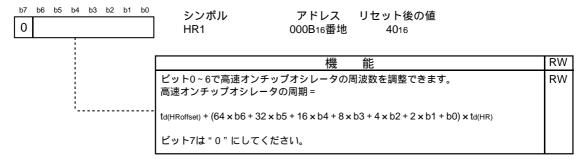

| 000B16           | 高速オンチップオシレータ制御レジスタ1             | HR1                                     | 33    |

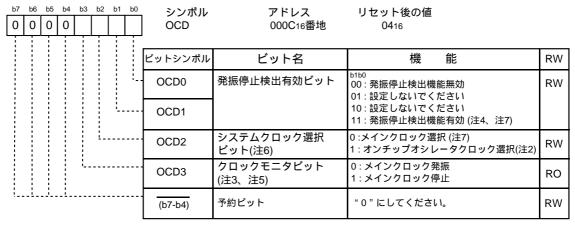

| 000C16           | 発振停止検出レジスタ                      | OCD                                     | 32    |

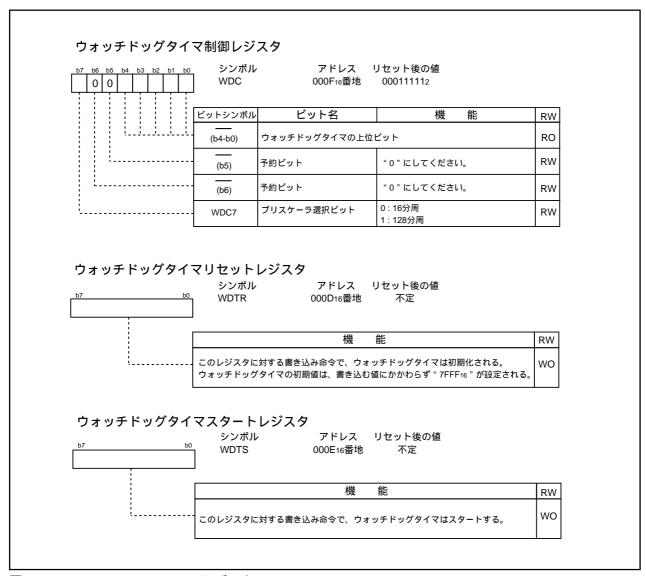

| 000D16           | ウォッチドッグタイマリセットレジスタ              | WDTR                                    | 69    |

| 000E16           | ウォッチドッグタイマスタートレジスタ              | WDTS                                    | 69    |

| 000E16           | ウォッチドッグタイマ制御レジスタ                | WDC                                     | 69    |

| 001016           | 2 3 2 3 1 2 2 2 1 Chapter 2 2 C |                                         |       |

| 001116           | <br> アドレスー致割り込みレジスタ0            | RMAD0                                   | 67    |

| 001216           |                                 | 111111111111111111111111111111111111111 | 0,    |

| 001316           |                                 |                                         |       |

| 001416           |                                 |                                         |       |

| 001516           | <br> アドレスー致割り込みレジスタ1            | RMAD1                                   | 67    |

| 001616           | TOX SERVE                       | TOWNE                                   | 0,    |

| 001716           |                                 |                                         |       |

| 001716           |                                 |                                         |       |

| 001916           | 電圧検出レジスタ1                       | VCR1                                    | 22    |

| 001A16           | 電圧検出レジスタ2                       | VCR2                                    | 22    |

| 001R16           | 電圧1人出レンハッ2                      | VOILE                                   |       |

| 001C16           |                                 |                                         |       |

| 001D16           |                                 |                                         |       |

| 001E16           | INTO入力フィルタ選択レジスタ                | INT0F                                   | 60    |

| 001F16           | 電圧検出割り込みレジスタ                    | D4INT                                   | 23    |

| 002016           | モエバ出品 りたの レンバン                  | DHIN                                    | 20    |

| 002016           |                                 |                                         |       |

| 002116           |                                 |                                         |       |

| 002316           |                                 |                                         |       |

| 002416           |                                 |                                         |       |

| 002516           |                                 |                                         |       |

| 002616           |                                 |                                         |       |

| 002716           |                                 |                                         |       |

| 002716           |                                 |                                         |       |

| 002916           |                                 |                                         |       |

| 002316<br>002A16 |                                 |                                         |       |

| 002A16           |                                 |                                         |       |

| 002B16           |                                 |                                         |       |

| 002D16           |                                 |                                         |       |

| 002E16           |                                 |                                         |       |

| UUZL 10          |                                 |                                         | 1     |

| 番地     | レジスタ              | シンボル   | 掲載ページ |

|--------|-------------------|--------|-------|

| 003016 |                   |        |       |

| 003116 |                   |        |       |

| 003216 |                   |        |       |

| 003316 |                   |        |       |

| 003416 |                   |        |       |

| 003516 |                   |        |       |

| 003616 |                   |        |       |

| 003716 |                   |        |       |

| 003816 |                   |        |       |

| 003916 |                   |        |       |

| 003A16 |                   |        |       |

| 003B16 |                   |        |       |

| 003C16 |                   |        |       |

| 003D16 |                   |        |       |

| 003E16 |                   |        |       |

| 003F16 |                   |        |       |

| 004016 |                   |        |       |

| 004116 |                   |        |       |

| 004216 |                   |        |       |

| 004316 |                   |        |       |

| 004416 |                   |        |       |

| 004516 |                   |        |       |

| 004616 |                   |        |       |

| 004716 |                   |        |       |

| 004816 |                   |        |       |

| 004916 |                   |        |       |

| 004A16 |                   |        |       |

| 004B16 |                   |        |       |

| 004C16 |                   |        |       |

| 004D16 | キー入力割り込み制御レジスタ    | KUPIC  | 53    |

| 004E16 | AD変換割り込み制御レジスタ    | ADIC   | 53    |

| 004F16 |                   |        |       |

| 005016 | コンペア1割り込み制御レジスタ   | CMP1IC | 53    |

| 005116 | UART0送信割り込み制御レジスタ | S0TIC  | 53    |

| 005216 | UART0受信割り込み制御レジスタ | S0RIC  | 53    |

| 005316 | UART1送信割り込み制御レジスタ | S1TIC  | 53    |

| 005416 | UART1受信割り込み制御レジスタ | S1RIC  | 53    |

| 005516 | INT2割り込み制御レジスタ    | INT2IC | 53    |

| 005616 | タイマX割り込み制御レジスタ    | TXIC   | 53    |

| 005716 | タイマY割り込み制御レジスタ    | TYIC   | 53    |

| 005816 | タイマZ割り込み制御レジスタ    | TZIC   | 53    |

| 005916 | INT1割り込み制御レジスタ    | INT1IC | 53    |

| 005A16 | INT3割り込み制御レジスタ    | INT3IC | 53    |

| 005B16 | タイマC割り込み制御レジスタ    | TCIC   | 53    |

| 005C16 | コンペア0割り込み制御レジスタ   | CMP0IC | 53    |

| 005D16 | INTO割り込み制御レジスタ    | INT0IC | 53    |

| 005E16 |                   |        |       |

| 005F16 |                   |        |       |

空欄はすべて予約領域です。

# 番地別ページ早見表

| 番地     | レジスタ             | シンボル  | 掲載ページ |

|--------|------------------|-------|-------|

| 006016 |                  |       |       |

| 006116 |                  |       |       |

| 006216 |                  |       |       |

| 006316 |                  |       |       |

| 006416 |                  |       |       |

| 006516 |                  |       |       |

| 006616 |                  |       |       |

| 006716 |                  |       |       |

| 006816 |                  |       |       |

| 006916 |                  |       |       |

| 006A16 |                  |       |       |

| 006B16 |                  |       |       |

| 006C16 |                  |       |       |

| 006D16 |                  |       |       |

| 006E16 |                  |       |       |

| 006F16 |                  |       |       |

| 007016 |                  |       |       |

| 007116 |                  |       |       |

| 007216 |                  |       |       |

| 007316 |                  |       |       |

| 007416 |                  |       |       |

| 007516 |                  |       |       |

| 007616 |                  |       |       |

| 007716 |                  |       |       |

| 007816 |                  |       |       |

| 007916 |                  |       |       |

| 007A16 |                  |       |       |

| 007B16 |                  |       |       |

| 007C16 |                  |       |       |

| 007D16 |                  |       |       |

| 007E16 |                  |       |       |

| 007F16 |                  |       |       |

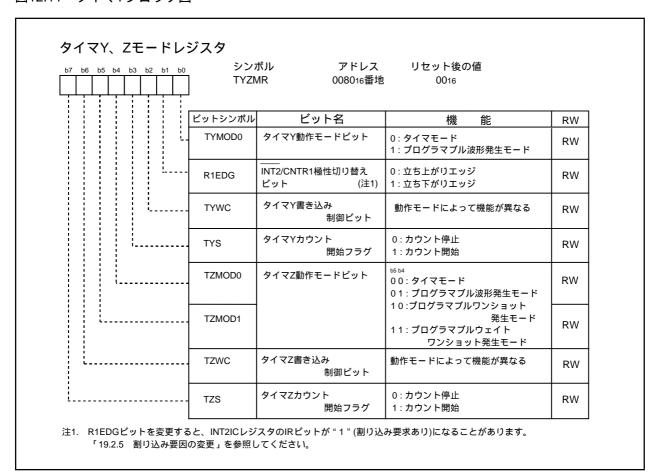

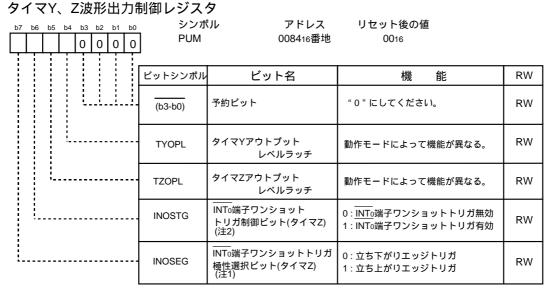

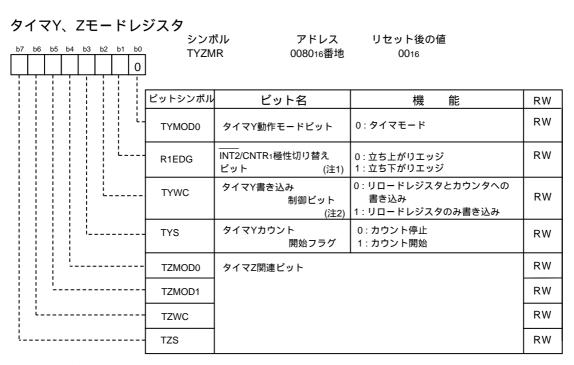

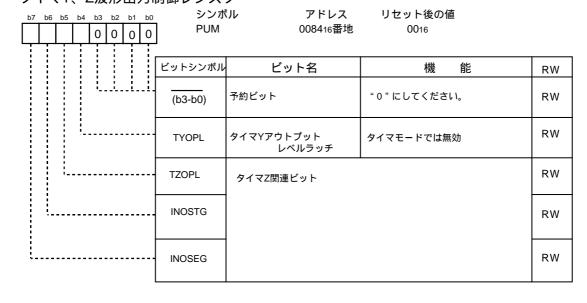

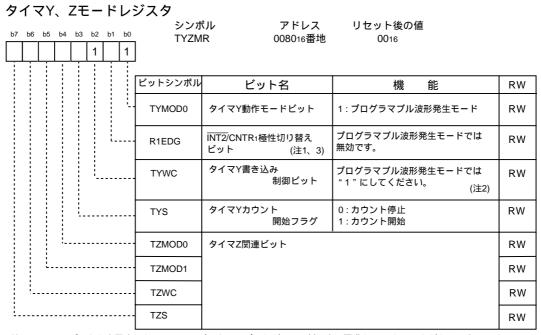

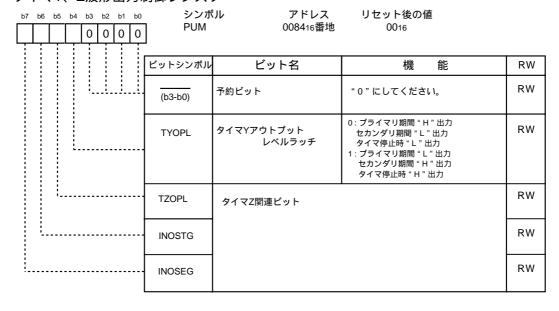

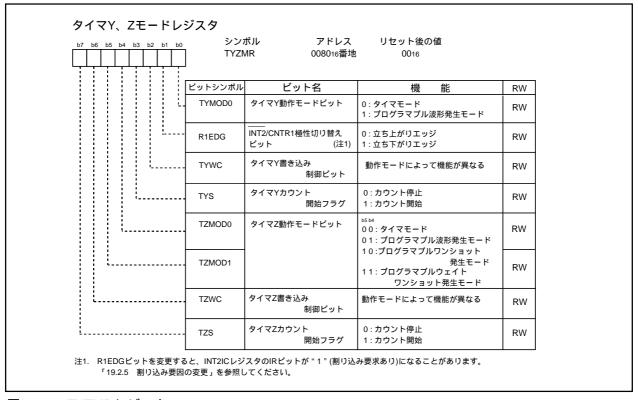

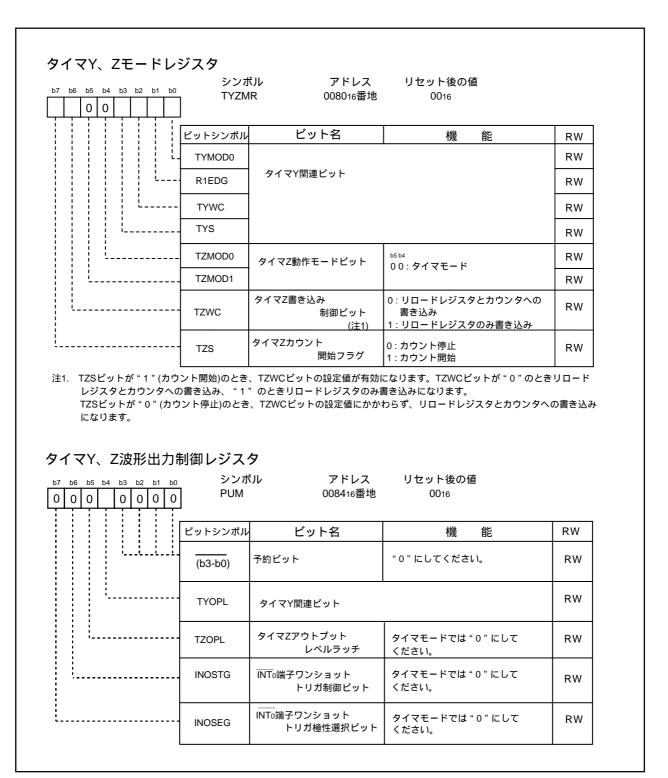

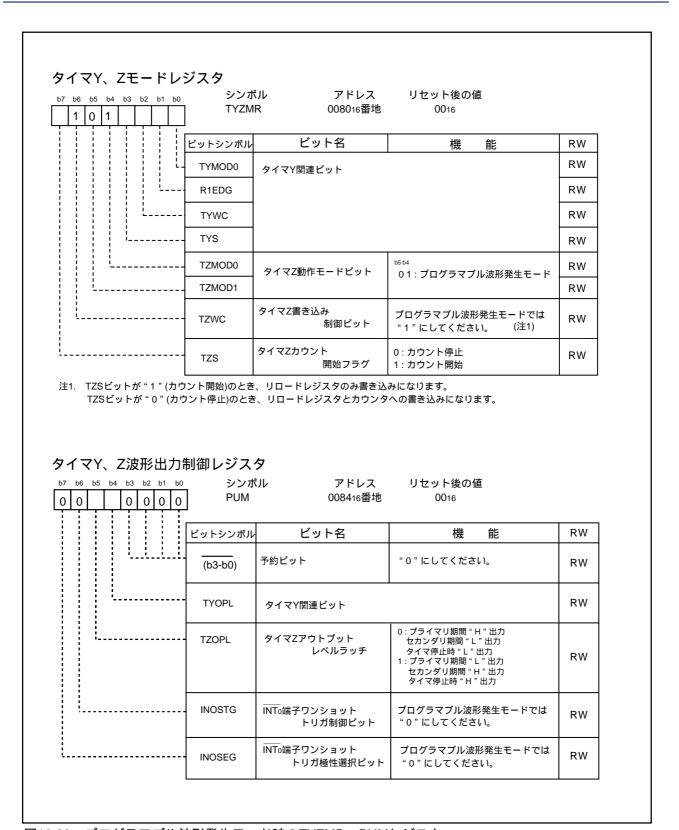

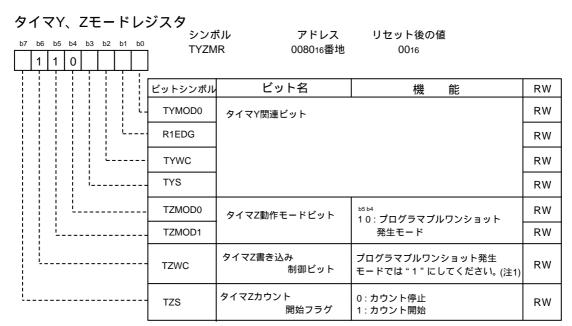

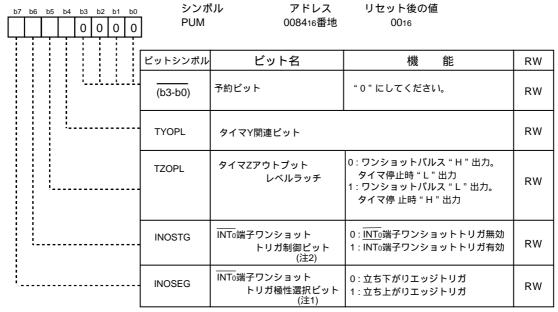

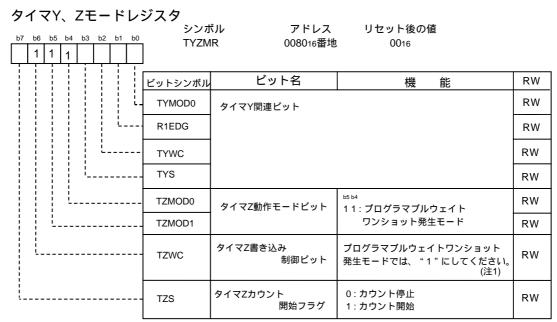

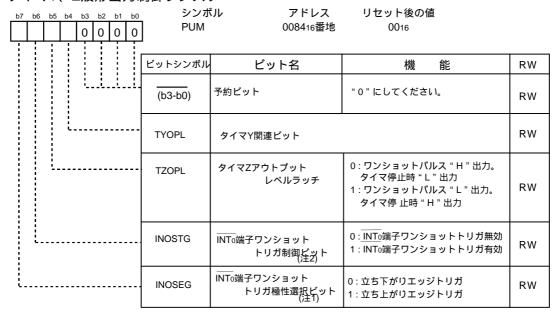

| 008016 | タイマY、Zモードレジスタ    | TYZMR | 80/88 |

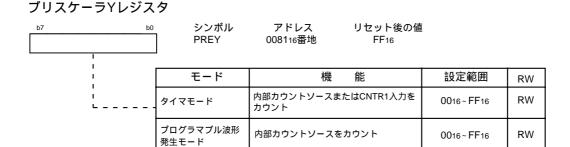

| 008116 | プリスケーラYレジスタ      | PREY  | 81    |

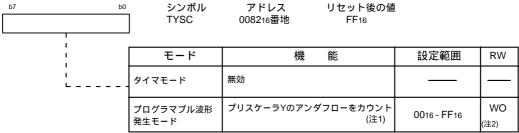

| 008216 | タイマYセカンダリレジスタ    | TYSC  | 81    |

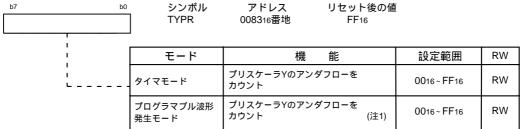

| 008316 | タイマYプライマリレジスタ    | TYPR  | 81    |

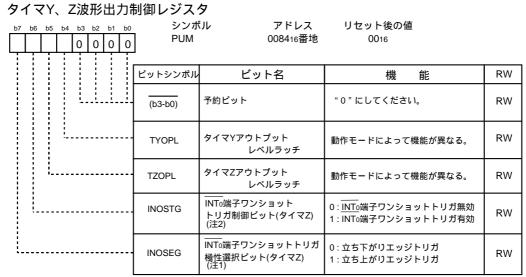

| 008416 | タイマY、Z波形出力制御レジスタ | PUM   | 82/90 |

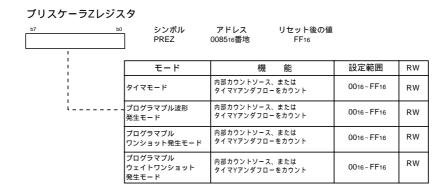

| 008516 | プリスケーラZレジスタ      | PREZ  | 89    |

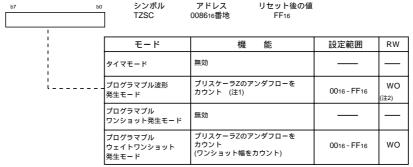

| 008616 | タイマZセカンダリレジスタ    | TZSC  | 89    |

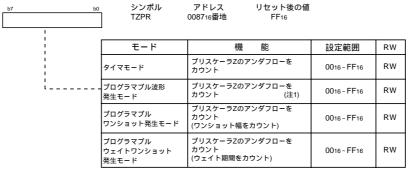

| 008716 | タイマZプライマリレジスタ    | TZPR  | 89    |

| 008816 |                  |       |       |

| 008916 |                  |       |       |

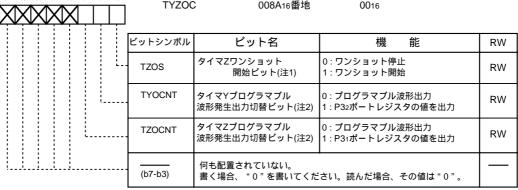

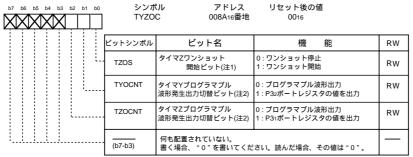

| 008A16 | タイマY、Z出力制御レジスタ   | TYZOC | 81/89 |

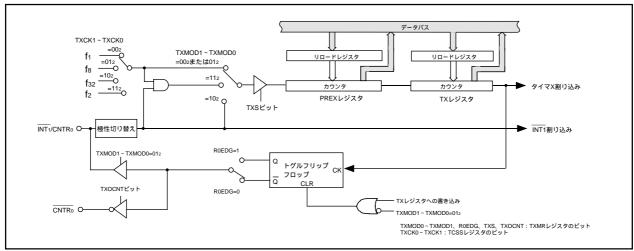

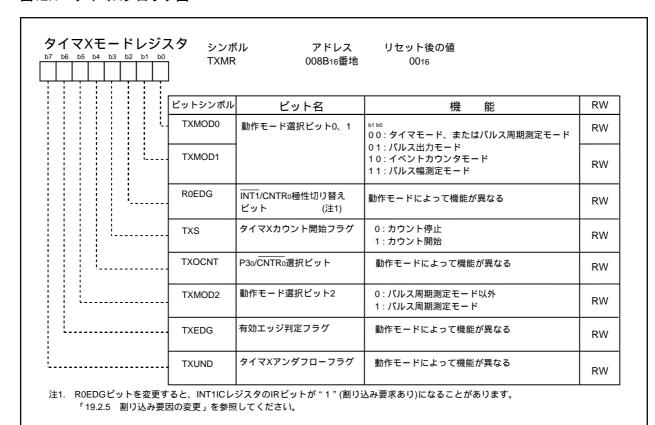

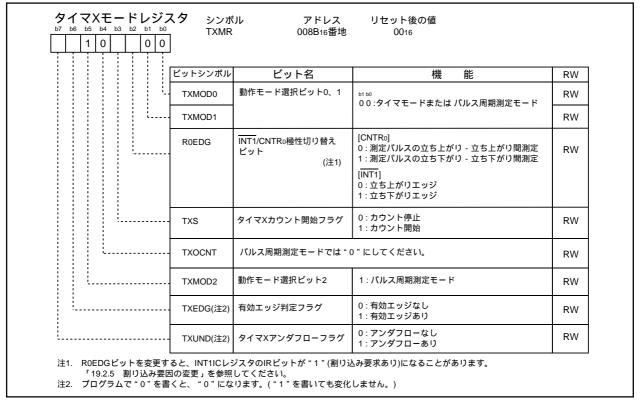

| 008B16 | タイマXモードレジスタ      | TXMR  | 71    |

| 008C16 | プリスケーラXレジスタ      | PREX  | 72    |

| 008D16 | タイマXレジスタ         | TX    | 72    |

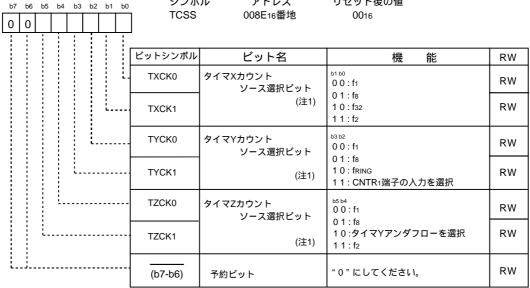

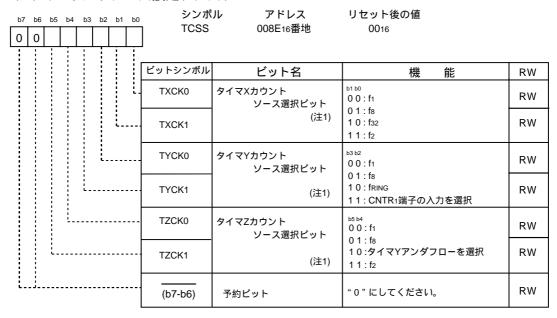

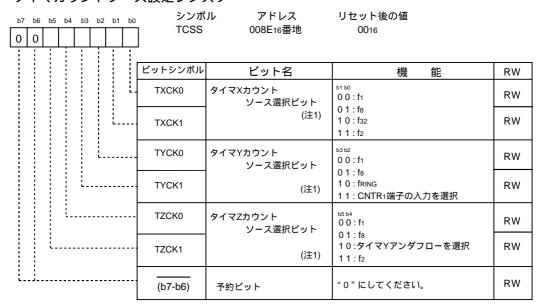

| 008E16 | タイマカウントソース設定レジスタ | TCSS  | 82/90 |

| 008F16 |                  |       |       |

| 番地                 | レジスタ            | シンボル  | 掲載ページ |

|--------------------|-----------------|-------|-------|

| 009016             | タイマCレジスタ        | TC    | 103   |

| 009116             |                 |       |       |

| 009216             |                 |       |       |

| 009316             |                 |       |       |

| 009416             |                 |       |       |

| 009516             |                 |       |       |

| 009616             | 外部入力許可レジスタ      | INTEN | 60    |

| 009716             |                 |       |       |

| 009816             | キー入力許可レジスタ      | KIEN  | 65    |

| 009916             |                 |       |       |

| 009A16             | タイマC制御レジスタ0     | TCC0  | 103   |

| 009B16             | タイマC制御レジスタ1     | TCC1  | 104   |

| 009C <sub>16</sub> | キャプチャ、コンペア0レジスタ | TM0   | 103   |

| 009E16<br>009F16   | コンペア1レジスタ       | TM1   | 103   |

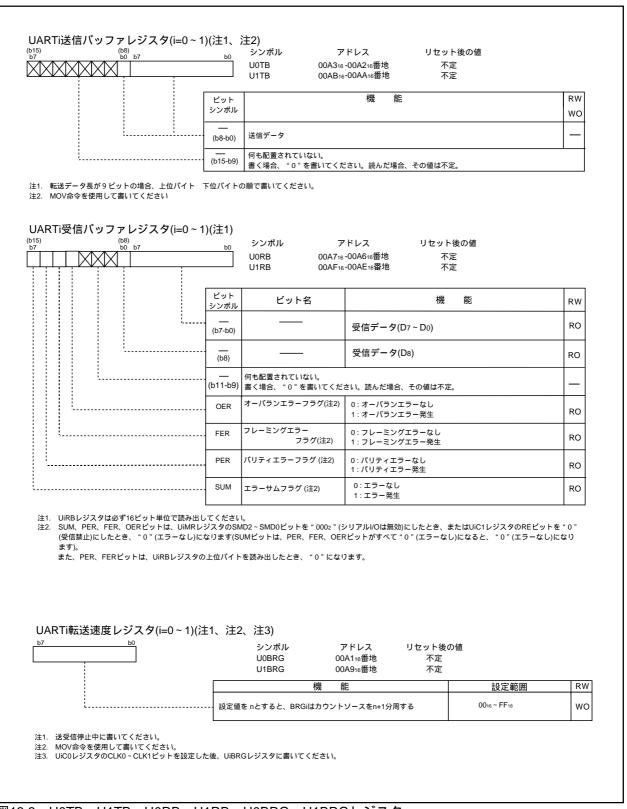

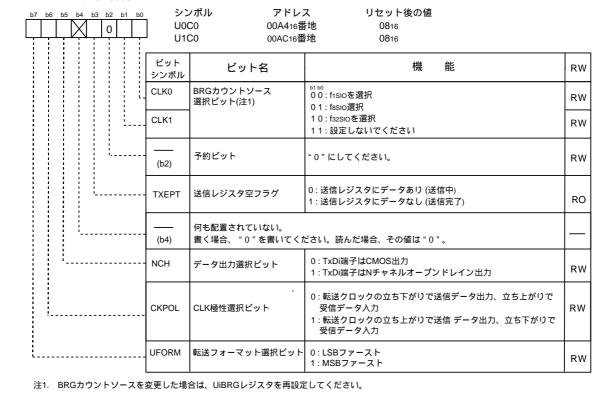

| 00A016             | UART0送受信モードレジスタ | U0MR  | 112   |

| 00A016             | UART0転送速度レジスタ   | U0BRG | 111   |

| 00A216             |                 |       |       |

| 00A316             | UART0送信バッファレジスタ | U0TB  | 111   |

| 00A416             | UARTO送受信制御レジスタ0 | U0C0  | 112   |

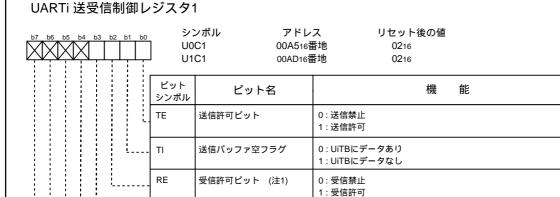

| 00A516             | UART0送受信制御レジスタ1 | U0C1  | 113   |

| 00A616             |                 |       |       |

| 00A716             | UART0受信バッファレジスタ | U0RB  | 111   |

| 00A816             | UART1送受信モードレジスタ | U1MR  | 112   |

| 00A916             | UART1転送速度レジスタ   | U1BRG | 111   |

| 00AA16             | UART1送信バッファレジスタ | U1TB  | 111   |

| 00AB16             | UARTI区はバックテレクスタ | OTIB  | '''   |

| 00AC16             | UART1送受信制御レジスタ0 | U1C0  | 112   |

| 00AD16             | UART1送受信制御レジスタ1 | U1C1  | 113   |

| 00AE16             | UART1受信バッファレジスタ | U1RB  | 111   |

| 00AF16             | UARTI又自ハリントレンスタ | OIKB  | '''   |

| 00B016             | UART送受信制御レジスタ2  | UCON  | 113   |

| 00B116             |                 |       |       |

| 00B216             |                 |       |       |

| 00B316             |                 |       |       |

| 00B416             |                 |       |       |

| 00B516             |                 |       |       |

| 00B616             |                 |       |       |

| 00B716             |                 |       |       |

| 00B816             |                 |       |       |

| 00B916             |                 |       |       |

| 00BA16             |                 |       |       |

| 00BB16             |                 |       |       |

| 00BC16             |                 |       |       |

| 00BD16             |                 |       |       |

| 00BE16             |                 |       |       |

| 00BF16             |                 |       |       |

空欄はすべて予約領域です。

# 番地別ページ早見表

| 番地               | レジスタ        | シンボル   | 掲載<br>ページ |

|------------------|-------------|--------|-----------|

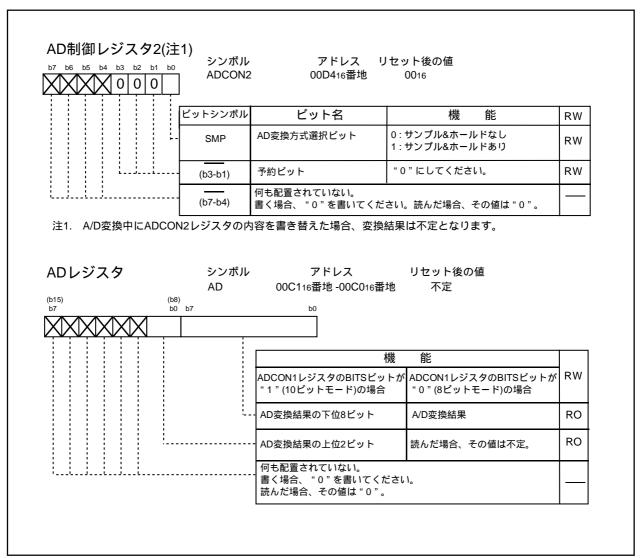

| 00C016<br>00C116 | ADレジスタ      | AD     | 127       |

| 00C216           |             |        |           |

| 00C316           |             |        |           |

| 00C416           |             |        |           |

| 00C516           |             |        |           |

| 00C616           |             |        |           |

| 00C716           |             |        |           |

| 00C816           |             |        |           |

| 00C916           |             |        |           |

| 00CA16           |             |        |           |

| 00CB16           |             |        |           |

| 00CC16           |             |        |           |

| 00CD16           |             |        |           |

| 00CE16           |             |        |           |

| 00CF16           |             |        |           |

| 00D016           |             |        |           |

| 00D116           |             |        |           |

| 00D216           |             |        |           |

| 00D316           |             |        |           |

| 00D416           | AD制御レジスタ2   | ADCON2 | 127       |

| 00D516           |             |        |           |

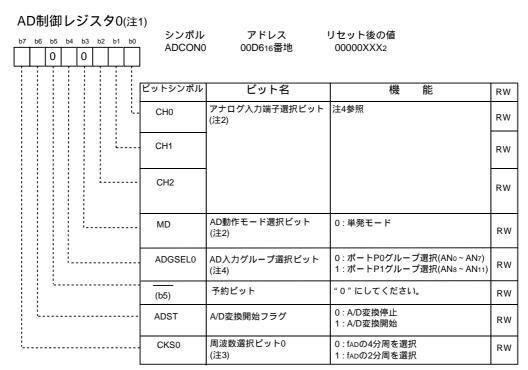

| 00D616           | AD制御レジスタ0   | ADCON0 | 126       |

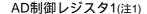

| 00D716           | AD制御レジスタ1   | ADCON1 | 126       |

| 00D816           |             |        |           |

| 00D916           |             |        |           |

| 00DA16           |             |        |           |

| 00DB16           |             |        |           |

| 00DC16           |             |        |           |

| 00DD16           |             |        |           |

| 00DE16           |             |        |           |

| 00DF16           |             |        |           |

| 00E016           | ポートP0レジスタ   | P0     | 142       |

| 00E116           | ポートP1レジスタ   | P1     | 142       |

| 00E216           |             | PD0    | 142       |

| 00E316           | ポートP1方向レジスタ | PD1    | 142       |

| 00E416           |             |        |           |

| 00E516           | ポートP3レジスタ   | P3     | 142       |

| 00E616           |             |        |           |

| 00E716           | ポートP3方向レジスタ | PD3    | 142       |

| 00E816           | ポートP4レジスタ   | P4     | 142       |

| 00E916           |             |        |           |

| 00EA16           | ポートP4方向レジスタ | PD4    | 142       |

| 00EB16           |             |        |           |

| 00EC16           |             |        |           |

| 00ED16           |             |        |           |

| 00EE16           |             |        |           |

| 00EF16           |             |        |           |

| 番地                 | レジスタ            | シンボル  | 掲載           |

|--------------------|-----------------|-------|--------------|

| 00F016             |                 |       |              |

| 00F116             |                 |       |              |

| 00F216             |                 |       |              |

| 00F316             |                 |       |              |

| 00F416             |                 |       |              |

| 00F516             |                 |       |              |

| 00F616             |                 |       |              |

| 00F716             |                 |       |              |

| 00F816             |                 |       |              |

| 00F916             |                 |       |              |

| 00FA16             |                 |       |              |

| 00FB16             |                 |       |              |

| 00FC16             | プルアップ制御レジスタ0    | PUR0  | 143          |

| 00FD16             | プルアップ制御レジスタ1    | PUR1  | 143          |

| 00FE16             | ポートP1駆動能力制御レジスタ | DRR   | 143          |

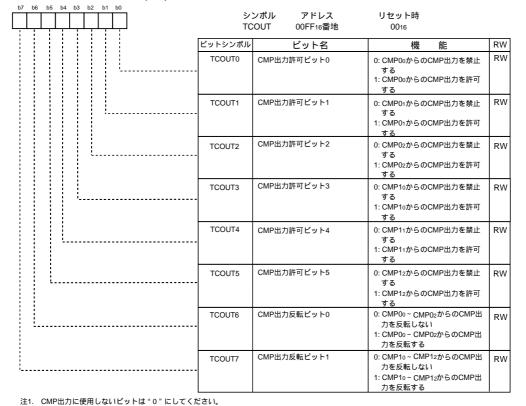

| 00FF16             | タイマC出力制御レジスタ    | TCOUT | 104          |

| ¥                  |                 |       | <del>*</del> |

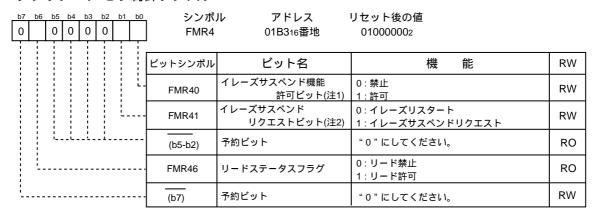

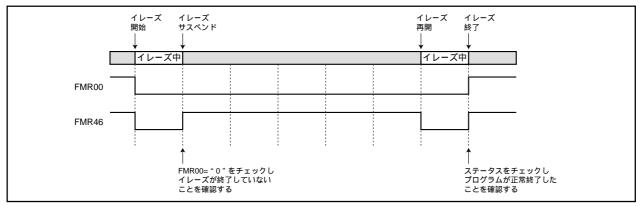

| 01B316             | フラッシュメモリ制御レジスタ4 | FMR4  | 171          |

| 01B416             |                 |       |              |

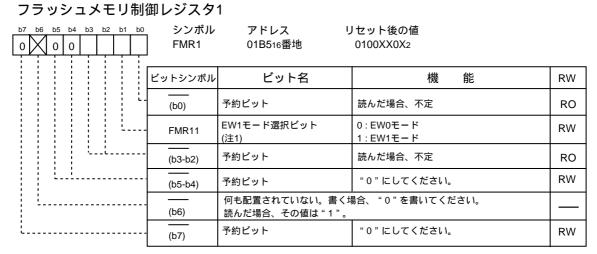

| 01B516             | フラッシュメモリ制御レジスタ1 | FMR1  | 171          |

| 01B616             |                 |       |              |

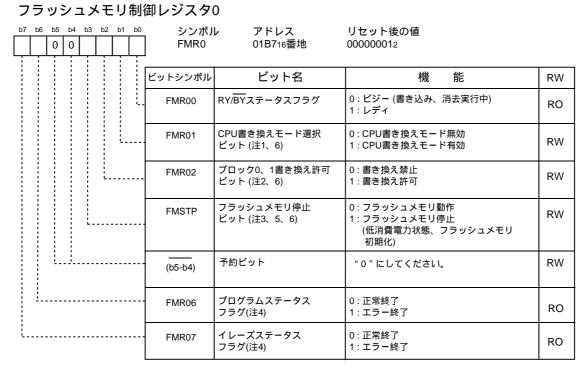

| 01B7 <sub>16</sub> | フラッシュメモリ制御レジスタ0 | FMR0  | 170          |

空欄はすべて予約領域です。

# R8C/11グループ

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

RJJ09B0040-0230 Rev.2.30 2006.2.13

# 1. 概要

本マイコンは高性能シリコンゲートCMOSプロセスを採用し、R8C/Tinyシリーズ CPUコアを搭載したシングルチップマイクロコンピュータで、32ピンプラスチックモールドLQFPに収められています。このシングルチップマイクロコンピュータは、高機能命令を持ちながら高い命令効率を持ち、1Mバイトのアドレス空間と、命令を高速に実行する能力を備えています。

# 1.1 応用

家電、事務機器、住設機器(センサー、セキュリティ)、産業一般、オーディオ、他

# 1.2 性能概要

表1.1に本マイコンの性能概要を示します。

# 表1.1 性能概要

|           |              | 性能                                   |

|-----------|--------------|--------------------------------------|

| CPU       | 基本命令数        | 89命令                                 |

|           | 最短命令実行時間     | 50ns (f(XIN)=20MHz, Vcc=3.0 ~ 5.5V)  |

|           |              | 100ns (f(XIN)=10MHz, Vcc=2.7 ~ 5.5V) |

|           | 動作モード        | シングルチップ                              |

|           | アドレス空間       | 1Mバイト                                |

|           | メモリ容量        | 表1.2を参照してください。                       |

| 周辺機能      | 割り込み         | 内部:11要因、外部:5要因、ソフトウェア:4要因、           |

|           |              | 割り込み優先レベル:7レベル                       |

|           | ウォッチドッグタイマ   | 15ビット×1チャネル (プリスケーラ付)                |

|           | タイマ          | タイマX:8ビット×1チャネル、タイマY:8ビット×           |

|           |              | 1チャネル、タイマZ:8ビット×1チャネル                |

|           |              | (各タイマ:8ビットプリスケーラ付)                   |

|           |              | タイマC:16ビット×1チャネル                     |

|           |              | インプットキャプチャ回路、アウトプットコンペア              |

|           |              | 回路                                   |

|           | シリアルインタフェース  | 1チャネル                                |

|           | (シリアルI/O)    | クロック同期形シリアルI/O、クロック非同期形シリアルI/O       |

|           | ,            | 1チャネル                                |

|           |              | クロック非同期形シリアルI/O                      |

|           | A/Dコンバータ     | 10ビットA/Dコンバータ:1回路、12チャネル             |

|           | クロック発生回路     | 2回路                                  |

|           |              | ・メインクロック発振回路 (帰還抵抗内蔵)                |

|           |              | ・オンチップオシレータ (高速、低速)                  |

|           |              | 高速オンチップオシレータは周波数調整機能付き               |

|           | 発振停止検出機能     | メインクロック発振停止検出機能                      |

|           | 電圧検出回路       | 内蔵                                   |

|           | パワーオンリセット回路  | 内蔵                                   |

|           | ポート          | 入出力:22本 (LED駆動用ポート含む)、入力:2本          |

|           |              | (LED駆動用入出力ポート:8本)                    |

| 電気的特性     | 電源電圧         | Vcc=3.0 ~ 5.5V (f(XIN)=20MHz)        |

|           |              | Vcc=2.7 ~ 5.5V (f(XIN)=10MHz)        |

|           | 消費電流         | 標準 9mA (Vcc=5V、f(XIN)=20MHz、高速モード)   |

|           |              | 標準 5mA (Vcc=3V、f(XIN)=10MHz、高速モード)   |

|           |              | 標準 35 μ A (Vcc=3V、ウェイトモード、周辺クロック停止)  |

|           |              | 標準 0.7 μ A (Vcc=3V、ストップモード)          |

| フラッシュメモリ版 | プログラム、イレーズ電圧 | Vcc=2.7 ~ 5.5V                       |

|           | プログラム、イレーズ回数 | 100回                                 |

| 動作周囲温度    |              | -20 ~ 85                             |

|           |              | -40 ~85 (Dバージョン)                     |

| パッケージ     |              | 32ピンプラスチックモールドLQFP                   |

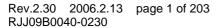

# 1.3 ブロック図

図1.1に本マイコンのブロック図を示します。

図1.1 ブロック図

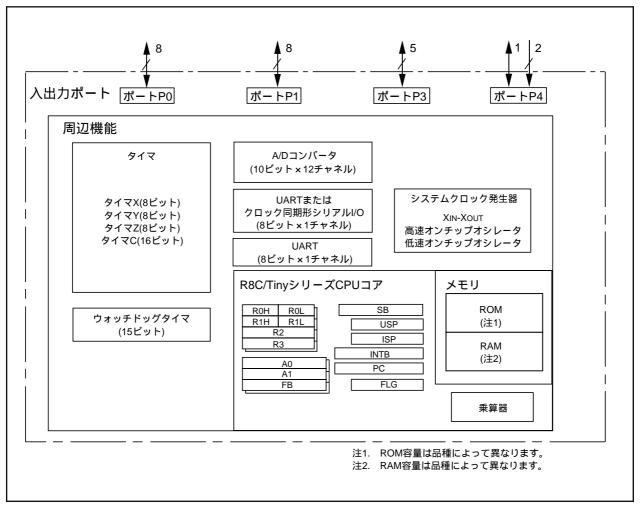

# 1.4 製品一覧

表1.2に製品一覧表を示します。

表1.2 製品一覧表

2006年2月現在

| 型名          | ROM容量  | RAM容量  | パッケージ        | 備         | 考 |

|-------------|--------|--------|--------------|-----------|---|

| R5F21112FP  | 8Kバイト  | 512バイト | PLQP0032GB-A | フラッシュメモリ版 |   |

| R5F21113FP  | 12Kバイト | 768バイト | PLQP0032GB-A |           |   |

| R5F21114FP  | 16Kバイト | 1Kバイト  | PLQP0032GB-A |           |   |

| R5F21112DFP | 8Kバイト  | 512バイト | PLQP0032GB-A | Dバージョン    |   |

| R5F21113DFP | 12Kバイト | 768バイト | PLQP0032GB-A |           |   |

| R5F21114DFP | 16Kバイト | 1Kバイト  | PLQP0032GB-A |           |   |

図1.2 型名とメモリサイズ・パッケージ

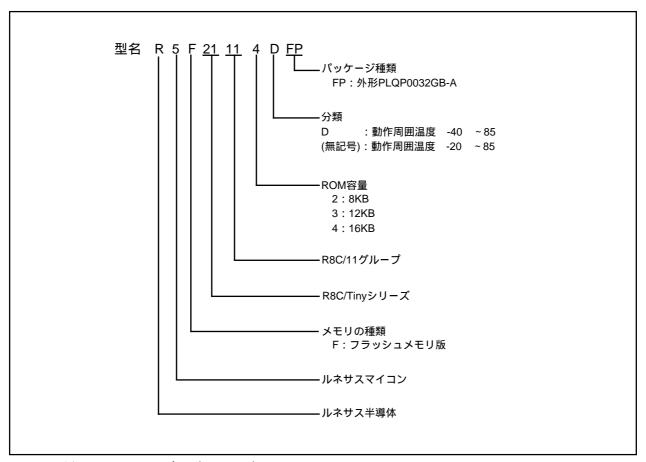

# 1.5 ピン接続図

図1.3にピン接続図(上面図)を示します。

図1.3 ピン接続図(上面図)

# 1.6 端子の機能説明

表1.3に本マイコンの端子の機能説明を示します。

表1.3 端子の機能説明

| 分類         | 端子名                                 | 入出力 | 機能                               |

|------------|-------------------------------------|-----|----------------------------------|

| 電源入力       | Vcc                                 | 入力  | Vccには、2.7V~5.5Vを入力してください。        |

|            | Vss                                 |     | Vssには、OVを入力してください。               |

| IVcc       | IVcc                                | 出力  | 内部電源を安定化させるための端子です。              |

|            |                                     |     | コンデンサ(0.1 μ F)を介してVssに接続してください。  |

|            |                                     |     | Vccに接続しないでください。                  |

| アナログ電源入力   | AVcc                                | 入力  | A/Dコンバータの電源入力です。AVccはVccに接続して    |

|            | AVss                                |     | ください。AVssはVssに接続してください。AVccとAVss |

|            |                                     |     | 間にはコンデンサを接続してください。               |

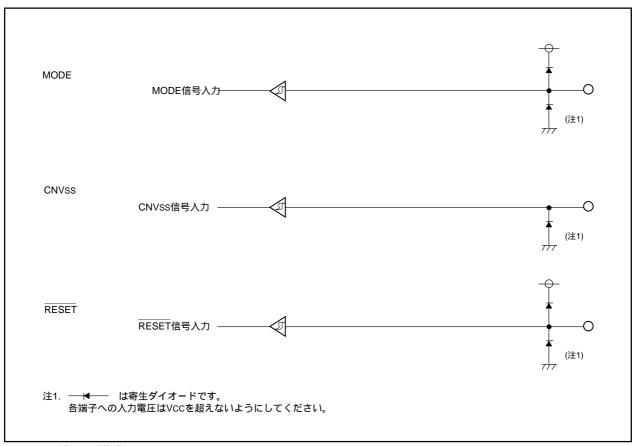

| リセット入力     | RESET                               | 入力  | │この端子に" L "を入力すると、マイクロコンピュータ│    |

|            |                                     |     | はリセット状態になります。                    |

| CNVss      | CNVss                               | 入力  | 抵抗を介してVssに接続してください。(注1)          |

| MODE       | MODE                                | 入力  | 抵抗を介してVccに接続してください。              |

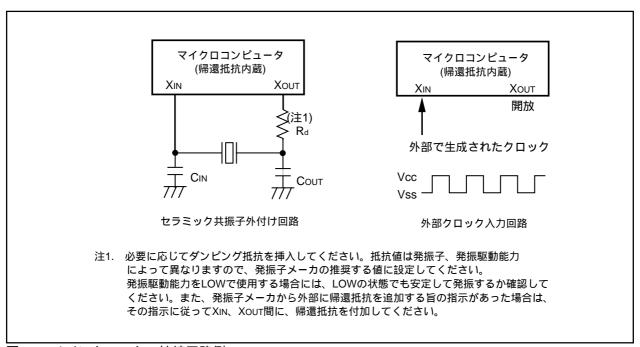

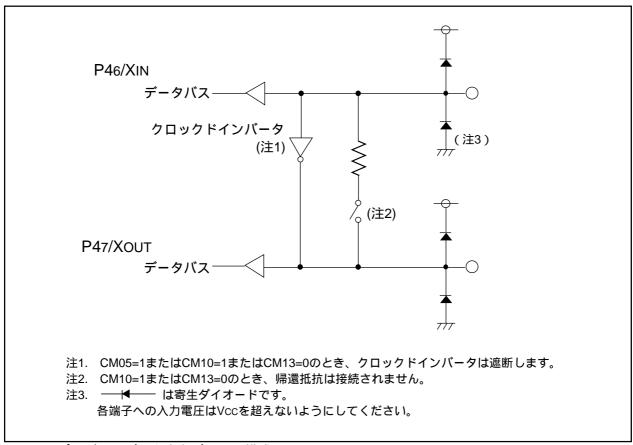

| メインクロック入力  | XIN                                 | 入力  | メインクロック発振回路の入出力です。XINとXOUT       |

|            |                                     |     | <b>」の間にはセラミック共振子、または水晶発振子を接</b>  |

| メインクロック出力  | Xout                                | 出力  | 続してください。外部で生成したクロックを入力す          |

|            |                                     |     | る場合は、XINからクロックを入力し、XOUTは開放に      |

|            |                                     |     | してください。                          |

| INT割り込み入力  | INT <sub>0</sub> ~ INT <sub>3</sub> | 入力  | INT割り込みの入力です。                    |

| キー入力割り込み入力 | KI <sub>0</sub> ~ KI <sub>3</sub>   | 入力  | キー入力割り込みの入力です。                   |

| タイマX       | CNTR <sub>0</sub>                   | 入出力 | タイマXの入出力です。                      |

|            | CNTR <sub>0</sub>                   | 出力  | タイマXの出力です。                       |

| タイマY       | CNTR <sub>1</sub>                   | 入出力 | タイマYの入出力です。                      |

| タイマZ       | TZout                               | 出力  | タイマZの出力です。                       |

| タイマC       | TCIN                                | 入力  | タイマCの入力です。                       |

|            | CMP00 ~ CMP02,<br>CMP10 ~ CMP12     | 出力  | タイマCの出力です。                       |

| シリアル       | CLK <sub>0</sub>                    | 入出力 | 転送クロック入出力です。                     |

| インターフェース   | RxD0、RxD1                           | 入力  | シリアルデータ入力です。                     |

|            | TxD0、TxD10、                         | 出力  | シリアルデータ出力です。                     |

|            | TxD11                               |     |                                  |

| 基準電圧入力     | VREF                                | 入力  | A/Dコンバータの基準電圧入力です。VREFはVccに接     |

|            |                                     |     | 続してください。                         |

| A/Dコンバータ   | AN0 ~ AN11                          | 入力  | A/Dコンバータのアナログ入力です。               |

| 入出力ポート     | P00 ~ P07、                          | 入出力 | CMOSの8ビット入出力ポートです。入出力を選択す        |

|            | P10 ~ P17、                          |     | るための方向レジスタを持ち、1端子ごとに入力ポー         |

|            | P30 ~ P33, P37,                     |     | ト、または出力ポートにできます。                 |

|            | P45                                 |     | 入力ポートは、プログラムでプルアップ抵抗の有無          |

|            |                                     |     | を選択できます。                         |

|            |                                     |     | ポートP10~P17はLED駆動ポートとして使用できます。    |

| 入力ポート      | P46、P47                             | 入力  | 入力専用ポートです。                       |

|            |                                     |     | <u>'</u>                         |

注1.接続する参考抵抗値は「19.8 ノイズに関する注意事項」を参照してください。

# 2. 中央演算処理装置(CPU)

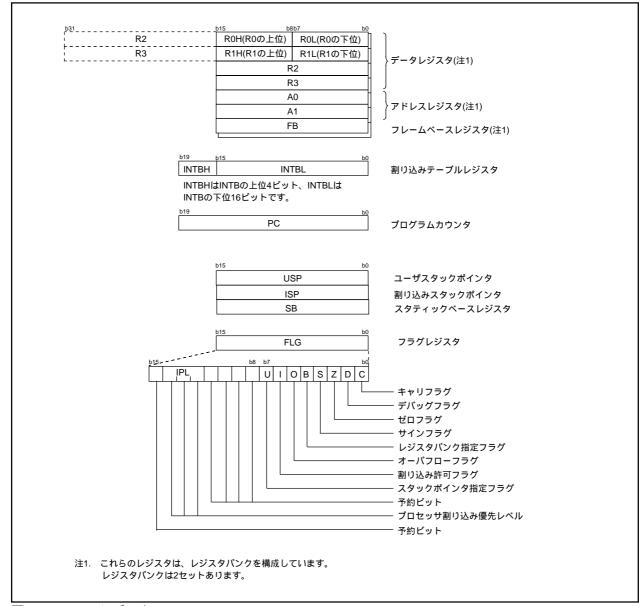

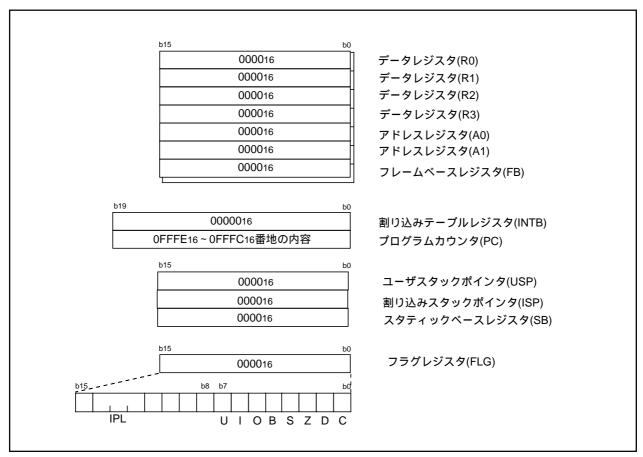

図2.1にCPUのレジスタを示します。CPUには13個のレジスタがあります。これらのうち、R0、R1、R2、R3、A0、A1、FBはレジスタバンクを構成しています。レジスタバンクは2セットあります。

図2.1 CPUのレジスタ

# 2.1 データレジスタ(R0、R1、R2、R3)

R0は16ビットで構成されており、主に転送や算術、論理演算に使用します。R1~R3はR0と同様です。 R0は、上位(R0H)と下位(R0L)を別々に8ビットのデータレジスタとして使用できます。R1H、R1LはR0H、 R0Lと同様です。R2とR0を組合せて32ビットのデータレジスタ(R2R0)として使用できます。R3R1はR2R0 と同様です。

# 2.2 アドレスレジスタ(AO、A1)

A0は16ビットで構成されており、アドレスレジスタ間接アドレッシング、アドレスレジスタ相対アドレッシングに使用します。また、転送や算術、論理演算に使用します。A1はA0と同様です。

A1とA0を組合せて32ビットのアドレスレジスタ(A1A0)として使用できます。

# 2.3 フレームベースレジスタ(FB)

FBは16ビットで構成されており、FB相対アドレッシングに使用します。

2.4 割り込みテーブルレジスタ(INTB)

INTBは20ビットで構成されており、可変割り込みベクタテーブルの先頭番地を示します。

2.5 プログラムカウンタ(PC)

PCは20ビットで構成されており、次に実行する命令の番地を示します。

2.6 ユーザスタックポインタ(USP)、割り込みスタックポインタ(ISP)

スタックポインタ(SP)は、USPとISPの2種類あり、共に16ビットで構成されています。 USPとISPはFLGのUフラグで切り替えられます。

2.7 スタティックベースレジスタ(SB)

SBは16ビットで構成されており、SB相対アドレッシングに使用します。

2.8 フラグレジスタ(FLG)

FLGは11ビットで構成されており、CPUの状態を示します。

2.8.1 キャリフラグ(Cフラグ)

算術論理ユニットで発生したキャリ、ボロー、シフトアウトしたビット等を保持します。

2.8.2 デバッグフラグ(Dフラグ)

Dフラグはデバッグ専用です。"0"にしてください。

2.8.3 ゼロフラグ(Zフラグ)

演算の結果が0のとき"1"になり、それ以外のとき"0"になります。

2.8.4 サインフラグ(Sフラグ)

演算の結果が負のとき"1"になり、それ以外のとき"0"になります。

2.8.5 レジスタバンク指定フラグ(Bフラグ)

Bフラグが"0"の場合、レジスタバンク0が指定され、"1"の場合、レジスタバンク1が指定されます。

2.8.6 オーバフローフラグ(Oフラグ)

演算の結果がオーバフローしたときに"1"になります。それ以外では"0"になります。

2.8.7 割り込み許可フラグ(Iフラグ)

マスカブル割り込みを許可するフラグです。

Iフラグが"0"の場合、マスカブル割り込みは禁止され、"1"の場合、許可されます。 割り込み要求を受け付けると、Iフラグは"0"になります。

2.8.8 スタックポインタ指定フラグ(Uフラグ)

Uフラグが "0" の場合、ISPが指定され、 "1" の場合、USPが指定されます。

ハードウェア割り込み要求を受け付けたとき、またはソフトウェア割り込み番号 $0 \sim 31$ のINT命令を実行したとき、Uフラグは"0"になります。

2.8.9 プロセッサ割り込み優先レベル(IPL)

IPLは3ビットで構成されており、レベル0~7までの8段階のプロセッサ割り込み優先レベルを指定します。 要求があった割り込みの優先レベルが、IPLより大きい場合、その割り込み要求は許可されます。

2.8.10 予約ビット

書く場合、"0"を書いてください。読んだ場合、その値は不定。

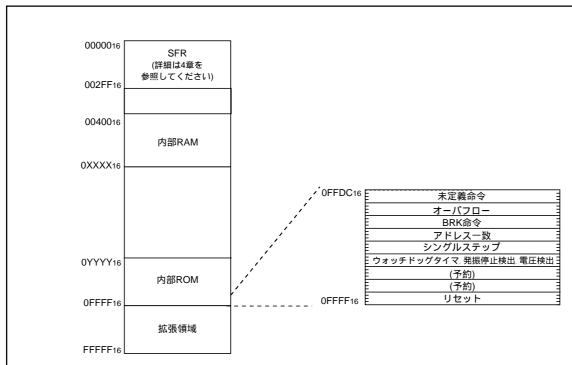

R8C/11グループ 3. メモリ

# 3. メモリ

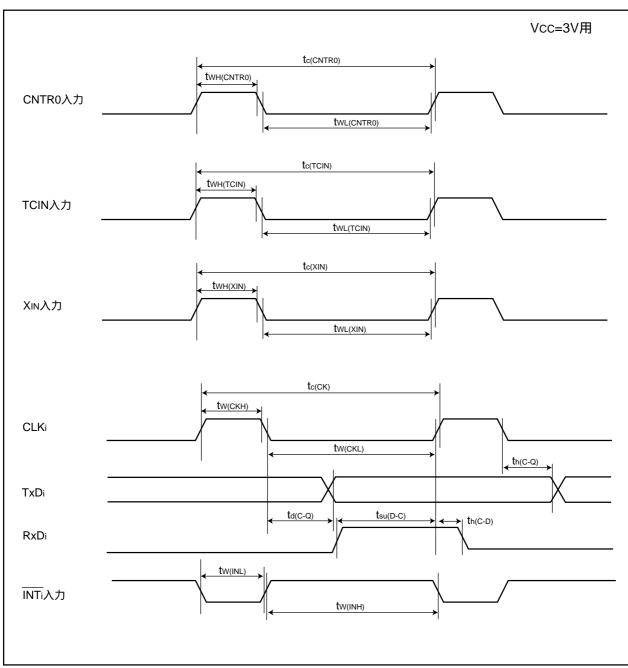

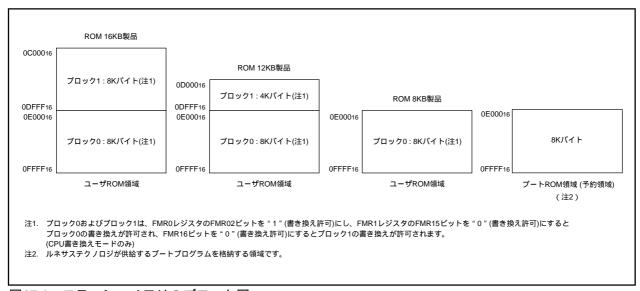

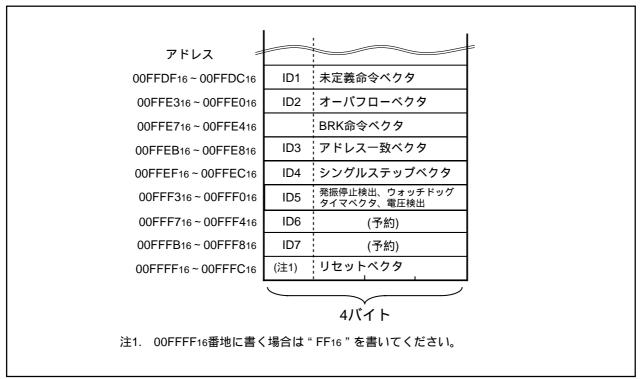

図3.1にメモリ配置を示します。アドレス空間は0000016番地からFFFFF16番地までの1Mバイトあります。 内部ROMは0FFFF16番地から下位方向に配置されます。例えば16Kバイトの内部ROMは、0C00016番地から 0FFFF16番地に配置されます。

固定割り込みベクタテーブルはOFFDC16番地からOFFFF16番地に配置されます。ここに割り込みルーチンの 先頭番地を格納します。

内部RAMは0040016番地から上位方向に配置されます。例えば1Kバイトの内部RAMは、0040016番地から007FF16番地に配置されます。内部RAMはデータ格納以外に、サブルーチン呼び出しや、割り込み時のスタックとしても使用します。

SFRは、0000016番地から002FF16番地に配置されています。ここには、周辺機能の制御レジスタが配置されています。SFRのうち何も配置されていない領域はすべて予約領域のため、ユーザは使用できません。

注1. 空欄は予約領域です。アクセスしないでください。

| TII 67                 | 内部     | ROM       | 内部RAM  |           |

|------------------------|--------|-----------|--------|-----------|

| 型名                     | 容量     | 0YYYY16番地 | 容量     | 0XXXX16番地 |

| R5F21114FP、R5F21114DFP | 16Kバイト | 0C00016   | 1Kバイト  | 007FF16   |

| R5F21113FP、R5F21113DFP | 12Kバイト | 0D00016   | 768バイト | 006FF16   |

| R5F21112FP、R5F21112DFP | 8Kバイト  | 0E00016   | 512バイト | 005FF16   |

図3.1 メモリ配置図

R8C/11グループ 4. SFR

# 4. SFR

SFR(Special Function Register)は、周辺機能の制御レジスタです。表4.1~表4.4にSFR一覧を示します。

表4.1 SFR一覧(1)(注1)

| 衣4.1                                                                                                                                                                                                       | SFR一頁(1)(注1)                             |       |                                                  |                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|--------------------------------------------------|----------------|

| 番地                                                                                                                                                                                                         | レジスタ                                     |       | シンボル                                             | リセット後の値        |

| 000016                                                                                                                                                                                                     | - · ·                                    |       |                                                  |                |

| 000116                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 000216                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 000316                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 000416                                                                                                                                                                                                     | ブロセッサモードレジスタ0                            |       | PM0                                              | 0016           |

| 000516                                                                                                                                                                                                     | プロセッサモードレジスタ1                            |       | PM1                                              | 0016           |

| 000616                                                                                                                                                                                                     | システムクロック制御レジスタ0                          |       | CM0                                              | 011010002      |

| 000716                                                                                                                                                                                                     | システムクロック制御レジスタ 1                         |       | CM1                                              | 001000002      |

| 000816                                                                                                                                                                                                     | 高速オンチップオシレータ制御レジスタ0                      |       | HR0                                              | 0016           |

| 000916                                                                                                                                                                                                     | アドレス一致割り込み許可レジスタ                         |       | AIER                                             | XXXXXX002      |

| 000A16                                                                                                                                                                                                     | プロテクトレジスタ                                |       | PRCR                                             | 00XXX0002      |

| 000B16                                                                                                                                                                                                     | 高速オンチップオシレータ制御レジスタ1                      |       | HR1                                              | 4016           |

| 000C16                                                                                                                                                                                                     | 発振停止検出レジスタ                               |       | OCD                                              | 000001002      |

| 000D16                                                                                                                                                                                                     | ウォッチドッグタイマリセットレジスタ<br>ウォッチドッグタイマスタートレジスタ |       | WDTR                                             | XX16           |

| 000E16                                                                                                                                                                                                     |                                          |       | WDTS                                             | XX16           |

| 000F16                                                                                                                                                                                                     | ウォッチドッグタイマ制御レジスタ                         |       | WDC<br>RMAD0                                     | 000111112      |

| 001016                                                                                                                                                                                                     | アドレス一致割り込みレジスタ0                          |       | RIVIADO                                          | 0016           |

| 001116                                                                                                                                                                                                     |                                          |       |                                                  | 0016<br>V016   |

| 0012 <sub>16</sub><br>0013 <sub>16</sub>                                                                                                                                                                   |                                          |       | <del>                                     </del> | X016           |

| 001316                                                                                                                                                                                                     | アドレス一致割り込みレジスタ1                          |       | RMAD1                                            | 0016           |

| 001416                                                                                                                                                                                                     | ノーレス 以削り心のレンスプー                          |       | LINIADI                                          | 0016           |

| 001516                                                                                                                                                                                                     |                                          |       |                                                  | X016           |

| 001016                                                                                                                                                                                                     |                                          |       | +                                                | ΛΟΙΟ           |

| 001716                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 001916                                                                                                                                                                                                     | 電圧検出レジスタ1                                | (注2)  | VCR1                                             | 000010002      |

| 001A16                                                                                                                                                                                                     | 電圧検出レジスタ2                                | (注2)  | VCR2                                             | 0016(注3)       |

|                                                                                                                                                                                                            |                                          | (/=-/ |                                                  | 100000002 (注4) |

| 001B <sub>16</sub>                                                                                                                                                                                         |                                          |       |                                                  | (i= )          |

| 001C16                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 001D16                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 001E16                                                                                                                                                                                                     | INT0入力フィルタ選択レジスタ                         |       | INT0F                                            | XXXXX0002      |

| 001F16                                                                                                                                                                                                     | 電圧検出割り込みレジスタ                             | (注2)  | D4INT                                            | 0016 (注3)      |

|                                                                                                                                                                                                            |                                          |       |                                                  | 010000012 (注4) |

| 002016                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 002116                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 002216                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 002316                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 002416                                                                                                                                                                                                     |                                          |       | 1                                                |                |

|                                                                                                                                                                                                            |                                          |       |                                                  |                |

| 002516                                                                                                                                                                                                     |                                          |       |                                                  |                |

| 002516<br>002616                                                                                                                                                                                           |                                          |       |                                                  |                |

| 002516<br>002616<br>002716                                                                                                                                                                                 |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816                                                                                                                                                                       |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916                                                                                                                                                             |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16                                                                                                                                                   |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16                                                                                                                                         |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16                                                                                                                               |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002D16                                                                                                                     |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002D16<br>002E16                                                                                                           |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002D16<br>002E16<br>002F16                                                                                                 |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002D16<br>002E16<br>002F16<br>003016                                                                                       |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002C16<br>002E16<br>002F16<br>003016<br>003116                                                                             |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002D16<br>002E16<br>002F16<br>003016                                                                                       |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002D16<br>002E16<br>002F16<br>003016<br>003116<br>003316                                                                   |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002C16<br>002D16<br>002F16<br>002F16<br>003116<br>003116                                                                   |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002916<br>002016<br>002C16<br>002C16<br>002C16<br>002C16<br>003016<br>003116<br>003216<br>003316<br>003316                                               |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002216<br>002D16<br>002D16<br>002E16<br>002F16<br>003016<br>003116<br>003316<br>003416                                                                   |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002D16<br>002D16<br>002E16<br>002E16<br>003016<br>003116<br>003116<br>003316<br>003416<br>003516                                               |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002918<br>002A16<br>002B16<br>002C16<br>002C16<br>002E16<br>003C16<br>003116<br>00316<br>00316<br>003516<br>003516<br>003616                                       |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002D16<br>002E16<br>002F16<br>003116<br>003116<br>00316<br>00316<br>00316<br>00316<br>00316<br>003516<br>003616                      |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002A16<br>002B16<br>002C16<br>002D16<br>002E16<br>00316<br>00316<br>00316<br>003316<br>003516<br>003616<br>003716                                        |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002916<br>002D16<br>002D16<br>002E16<br>002E16<br>00316<br>00316<br>00316<br>00316<br>003516<br>003516<br>003616<br>003616<br>003716<br>003816<br>003916 |                                          |       |                                                  |                |

| 002516<br>002616<br>002716<br>002816<br>002916<br>002916<br>002D16<br>002D16<br>002E16<br>002E16<br>00316<br>00316<br>00316<br>003516<br>003616<br>003716<br>003816<br>003816                              |                                          |       |                                                  |                |

| 002516 002616 002716 002816 002916 0022816 0022816 0022816 0022816 0022816 0022816 0022816 002516 0032816 00316 003316 003416 003516 003616 003716 003816 003816 003816 003816 003816 003816 003816        |                                          |       |                                                  |                |

X:不定です。

注1. 空欄は予約領域です。アクセスしないでください。 注2. ソフトウェアリセット、ウォッチドッグタイマリセットでは変化しません。 注3. リセット入力の場合。 注4. RESET端子が"H"固定の場合。

R8C/11グループ 4. SFR

# 表4.2 SFR一覧(2)(注1)

| ٠. ١٠٠             | O. K. 92(2)(/11)  |         |                 |

|--------------------|-------------------|---------|-----------------|

| 番地                 | レジスタ              | シンボル    | リセット後の値         |

| 004016             |                   |         | 7 - 7 - 12 - 12 |

| 004116             |                   |         |                 |

| 004216             |                   |         |                 |

| 004316             |                   |         |                 |

| 004416             |                   |         |                 |

| 004516             |                   |         |                 |

| 004616             |                   |         |                 |

| 004716             |                   |         |                 |

| 004816             |                   |         |                 |

| 004916             |                   |         |                 |

| 004A16             |                   |         |                 |

| 004A16             |                   |         |                 |

| 004C16             |                   |         |                 |

| 004C16             | ナートも割り込みものしていると   | KUDIC   | VVVVV0000       |

| 004E16             | キ・入力割り込み制御レジスタ    | KUPIC   | XXXXX0002       |

| 004E16             | AD変換割り込み制御レジスタ    | ADIC    | XXXXX0002       |

| 004F16             | ー >               | OMPAIO  | V/V/V/0000      |

|                    | コンペア1割り込み制御レジスタ   | CMP1IC  | XXXXX0002       |

| 005116             | UARTO送信割り込み制御レジスタ | SOTIC   | XXXXX0002       |

| 005216             | UART0受信割り込み制御レジスタ | SORIC   | XXXXX0002       |

| 005316             | UART1送信割り込み制御レジスタ | S1TIC   | XXXXX0002       |

| 005416             | UART1受信割り込み制御レジスタ | S1RIC   | XXXXX0002       |

| 005516             | INT2割り込み制御レジスタ    | INT2IC  | XXXXX0002       |

| 005616             | タイマX割り込み制御レジスタ    | TXIC    | XXXXX0002       |

| 005716             | タイマY割り込み制御レジスタ    | TYIC    | XXXXX0002       |

| 005816             | タイマZ割り込み制御レジスタ    | TZIC    | XXXXX0002       |

| 005916             | INT1割り込み制御レジスタ    | INT1IC  | XXXXX0002       |

| 005A16             | INT3割り込み制御レジスタ    | INT3IC  | XXXXX0002       |

| 005B16             | タイマC割り込み制御レジスタ    | TCIC    | XXXXX0002       |

| 005C16             | コンペア0割り込み制御レジスタ   | CMP0IC  | XXXXX0002       |

| 005D16             | INTO割り込み制御レジスタ    | INTOIC  | XX00X0002       |

| 005E16             |                   | IIVIOIO | XX00X0002       |

| 005F16             |                   |         |                 |

| 006016             |                   |         |                 |

|                    |                   |         |                 |

| 0061 <sub>16</sub> |                   |         |                 |

|                    |                   |         |                 |

| 006316             |                   |         |                 |

| 006416             |                   |         |                 |

| 006516             |                   |         |                 |

| 006616             |                   |         |                 |

| 006716             |                   |         |                 |

| 006816             |                   |         |                 |

| 006916             |                   |         |                 |

| 006A16             |                   |         |                 |

| 006B <sub>16</sub> |                   |         |                 |

| 006C16             |                   |         |                 |

| 006D16             |                   |         |                 |

| 006E16             |                   |         |                 |

| 006F16             |                   |         |                 |

| 007016             |                   |         |                 |

| 007116             |                   |         |                 |

| 007216             |                   |         |                 |

| 007316             |                   |         |                 |

| 007416             |                   |         |                 |

| 007516             |                   |         |                 |

| 007616             |                   |         |                 |

| 007716             |                   |         |                 |

| 007716             |                   |         |                 |

|                    |                   |         |                 |

| 007916             |                   |         |                 |

| 007A16             |                   |         |                 |

|                    |                   |         |                 |

| 007B16             |                   |         |                 |

| 007C16             |                   |         |                 |

| 007C16             |                   |         |                 |

| 007C16             |                   |         |                 |

注1. 空欄は予約領域です。アクセスしないでください。

X:不定です。

R8C/11グループ 4. SFR

#### SFR一覧(3)(注1) 表4.3

| 147.0                                                                                                      |                              |       |              |

|------------------------------------------------------------------------------------------------------------|------------------------------|-------|--------------|

| 番地                                                                                                         | レジスタ                         | シンボル  | リセット後の値      |

| 008016                                                                                                     | タイマY、Zモードレジスタ                | TYZMR | 0016         |

| 008116                                                                                                     | プリスケーラYレジスタ                  | PREY  | FF16         |

| 008216                                                                                                     | タイマYセカンダリレジスタ                | TYSC  | FF16         |

| 008316                                                                                                     | タイマYプライマリレジスタ                | TYPR  | FF16         |

| 008316                                                                                                     | タイマY、Z波形出力制御レジスタ             | PUM   | 0016         |

| 008516                                                                                                     |                              | PREZ  |              |

|                                                                                                            | プリスケーラZレジスタ<br>タイマZセカンダリレジスタ | TZSC  | FF16<br>FF16 |

| 008616                                                                                                     |                              |       |              |

| 008716                                                                                                     | タイマZブライマリレジスタ                | TZPR  | FF16         |

| 008816                                                                                                     |                              |       |              |

| 008916                                                                                                     |                              |       |              |

| 008A16                                                                                                     | タイマY、Z出力制御レジスタ               | TYZOC | 0016         |

| 008B <sub>16</sub>                                                                                         | タイマXモードレジスタ                  | TXMR  | 0016         |

| 008C16                                                                                                     | ブリスケーラXレジスタ                  | PREX  | FF16         |

| 008D <sub>16</sub>                                                                                         | タイマXレジスタ                     | TX    | FF16         |

| 008E16                                                                                                     | タイマカウントソース設定レジスタ             | TCSS  | 0016         |

| 008F16                                                                                                     |                              |       |              |

| 009016                                                                                                     | タイマCレジスタ                     | TC    | 0016         |

| 009116                                                                                                     |                              |       | 0016         |

| 009216                                                                                                     |                              |       |              |

| 009316                                                                                                     |                              |       |              |

| 009416                                                                                                     |                              |       |              |

| 009516                                                                                                     |                              |       |              |

| 009616                                                                                                     | 外部入力許可レジスタ                   | INTEN | 0016         |

| 009016                                                                                                     | TIMES WORL DESCRIPTION       |       | 33.0         |

| 009716                                                                                                     | <br> キー入力許可レジスタ              | KIEN  | 0016         |

| 009916                                                                                                     | 十一八万計・リレンスク                  | RILIN | 0010         |

| 009916<br>009A16                                                                                           | <br> タイマC制御レジスタ0             | TCC0  | 0016         |

|                                                                                                            | タイマC制御レジスタ1                  | TCC1  | 0016         |

| 009B16                                                                                                     |                              |       |              |

| 009C16                                                                                                     | キャブチャ、コンペア0レジスタ              | TMO   | 0016         |

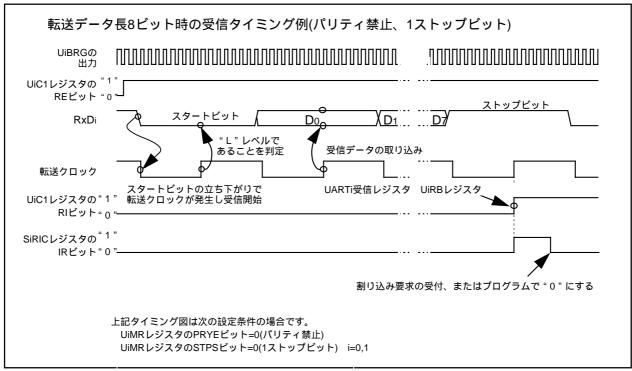

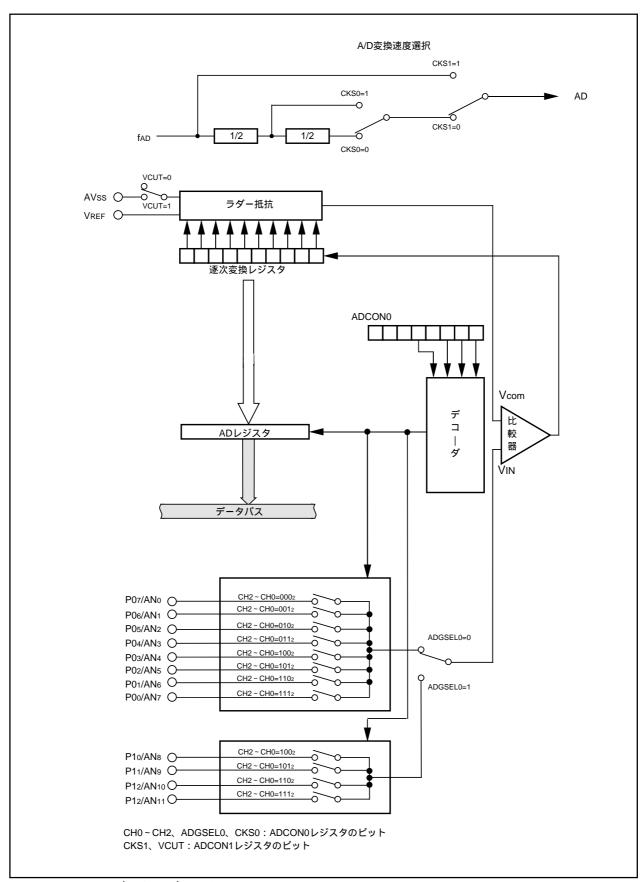

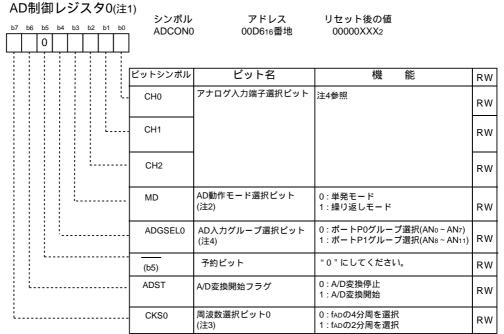

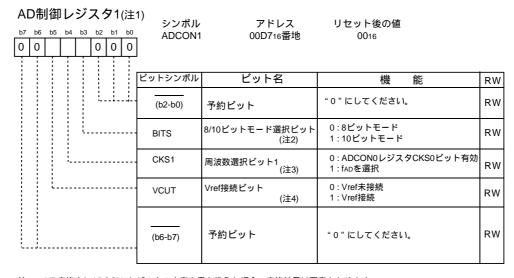

| 009D16                                                                                                     |                              |       | 0016 (注2)    |