# CA91L862A (QSpan II™) User Manual

Final Manual July 24, 2024

# **Revision History**

### Final Manual, July 24, 2024

Removed obsolete part numbers from Ordering Information.

### Final Manual, May 16, 2013

This version was updated to include general improvements.

### 8091862.MA001.08, Final Manual, November 2009

This version of the document was rebranded as IDT. It does not include any technical changes.

### 8091862.MA001.07, Final Manual, January 2007

- Corrected the description of the BS field in the PBTI0\_CTL, PBTI1\_CTL, QBSI0 AT, and QBSI1 AT registers (see "Register Map" on page 195).

- Updated the Ordering Information section to indicate a reduction in the variety of QSpan II parts available to customers (see "Ordering Information" on page 405).

8091862.MA001.06, Final Manual, September 2000

8091862.MA001.05, Final Manual, September 2000

8091862.MA001.04, Preliminary Manual, December 1999

8091862.MA001.03, Preliminary Manual, September 1999

8091862.MA001.02, Preliminary Manual, September 1999

8091862.MA001.01, Preliminary Manual, August 1999

# **Contents**

| Cha | pter 1 | : General Information                             | 23 |

|-----|--------|---------------------------------------------------|----|

| 1.1 | What   | is the QSpan II                                   | 24 |

|     | 1.1.1  | QSpan II Features                                 | 25 |

|     | 1.1.2  | QSpan II verses QSpan                             | 26 |

| 1.2 | Docui  | ment Conventions                                  | 27 |

|     | 1.2.1  | Signals                                           | 27 |

|     | 1.2.2  | Bit Ordering                                      | 27 |

|     | 1.2.3  | Numeric Conventions                               | 27 |

|     | 1.2.4  | Topographic Conventions                           | 27 |

|     | 1.2.5  | Symbols                                           | 28 |

|     | 1.2.6  | Document Status                                   | 28 |

| 1.3 | Relate | ed Documentation                                  | 28 |

| Cha | nton 2 | : Functional Overview                             | 20 |

| 2.1 | _      | riew                                              |    |

| 2.1 |        | DBus Slave Channel                                |    |

| 2.2 | `      | CI Target Channel                                 |    |

| 2.3 |        | DMA Channel                                       |    |

| 2.4 |        | DMA Channel                                       |    |

| 2.6 |        | egister Channel                                   |    |

| 2.7 |        | nterrupt Channel                                  |    |

| 2.7 |        | EPROM Channel                                     |    |

|     |        |                                                   |    |

| Cha | pter 3 | : The QBus Slave Channel                          | 33 |

| 3.1 | Overv  | riew                                              | 33 |

| 3.2 | QBus   | Slave Channel Architecture                        | 34 |

|     | 3.2.1  | QBus Slave Module                                 | 35 |

|     |        | 3.2.1.1 QBus Data Parity Generation and Detection | 35 |

|     | 3.2.2  | Qx-FIFO and Qr-FIFO                               | 36 |

|     | 3.2.3  | PCI Master Module                                 | 36 |

| 3.3 | Chanr  | nel Description                                   | 36 |

| 3.4 | Addre  | ess Phase                                         | 37 |

|     | 3.4.1  | Transaction Decoding and QBus Slave Images         | 37         |

|-----|--------|----------------------------------------------------|------------|

|     |        | 3.4.1.1 MPC860 Cycles                              | 39         |

|     |        | 3.4.1.2 MC68360 Cycles                             | 39         |

|     |        | 3.4.1.3 M68040 Cycles                              | 39         |

|     | 3.4.2  | PCI Bus Request                                    | 40         |

|     | 3.4.3  | Address Translation                                | 40         |

|     | 3.4.4  | Address Phase on the PCI Bus                       | 43         |

| 3.5 | Data I | hase                                               | 44         |

|     | 3.5.1  | Endian Mapping                                     | 44         |

|     | 3.5.2  | Data Path                                          | 46         |

|     |        | 3.5.2.1 Writes                                     | 46         |

|     |        | 3.5.2.2 Read Transactions — Burst and Single Cycle | 48         |

|     |        | 3.5.2.3 Prefetched Reads                           | 48         |

|     |        | 3.5.2.4 Delayed Reads and PCI Transaction Ordering | 49         |

|     | 3.5.3  | PCI Target Channel Reads                           | 50         |

|     | 3.5.4  | Parity Monitoring by PCI Master Module             | 50         |

| 3.6 | Termi  | nation Phase                                       | 51         |

|     | 3.6.1  | Posted Write Termination                           |            |

| 3.7 | PCI M  | aster Retry Counter                                | 54         |

| Cha | pter 4 | The PCI Target Channel                             | <b>5</b> 5 |

| 4.1 | _      | ew                                                 |            |

| 4.2 |        | arget Channel Architecture                         |            |

|     | 4.2.1  | PCI Target Module                                  |            |

|     | 4.2.2  | Px-FIFO and Pr-FIFO                                |            |

|     | 4.2.3  | QBus Master Module                                 |            |

|     |        | 4.2.3.1 QBus Data Parity Generation and Detection  |            |

| 4.3 | Chann  | el Description                                     |            |

| 4.4 |        | ss Phase                                           |            |

|     | 4.4.1  | Transaction Decoding                               |            |

|     | 4.4.2  | Address Translation                                |            |

|     | 4.4.3  | Transaction Codes on the QBus                      |            |

|     | 4.4.4  | PCI BIOS Memory Allocation                         |            |

|     |        | 4.4.4.1 Block Size and PCI Address Space           |            |

|     |        | 4.4.4.2 Base Address                               |            |

| 4.5 | Data I | hase                                               |            |

|     | 4.5.1  | Endian Mapping                                     |            |

|     |        | 4.5.1.1 Write Cycle Mapping for PCI Target Channel |            |

|     |        | 4.5.1.2 Read Cycle Mapping for PCI Target Channel  |            |

|     | 4.5.2  | Data Path                                          |            |

|     |        | 4.5.2.1 Posted Writes                              |            |

|     |        | 4.5.2.2 Delayed Writes                             |            |

|     |        | =                                                  |            |

|            |        | 4.5.2.3 Single Read Transactions             | 74  |

|------------|--------|----------------------------------------------|-----|

|            |        | 4.5.2.4 Prefetched Read Transactions         | 74  |

|            | 4.5.3  | Parity Monitoring by PCI Target Module       | 75  |

| 4.6        | Reads  | s and PCI Transaction Ordering               | 75  |

|            | 4.6.1  | Transaction Ordering Disable Option          |     |

| 4.7        | QBus   | Arbitration and Sampling                     | 76  |

|            | 4.7.1  | MC68360 Bus Arbitration                      | 76  |

|            | 4.7.2  | MPC860 Bus Arbitration                       | 77  |

|            | 4.7.3  | M68040 Bus Arbitration                       | 78  |

| 4.8        | Termi  | inations                                     | 78  |

|            | 4.8.1  | QBus Master Module Terminations              | 78  |

|            | 4.8.2  | MC68360 Cycle Terminations                   | 78  |

|            | 4.8.3  | MPC860 Cycle Terminations                    | 79  |

|            | 4.8.4  | M68040 Cycle Terminations                    | 79  |

|            | 4.8.5  | Terminations driven by the PCI Target Module | 80  |

|            |        | 4.8.5.1 Target-Disconnect                    | 80  |

|            |        | 4.8.5.2 Target-Retry                         | 81  |

|            |        | 4.8.5.3 Target-Abort                         | 81  |

|            | 4.8.6  | Terminations of Posted Writes                | 82  |

| Cha        | nter 5 | : The IDMA Channel                           | 83  |

| 5.1        | •      | /iew                                         |     |

| 5.2        |        | Read Transactions                            |     |

|            | 5.2.1  | Data Path                                    |     |

| 5.3        | PCI W  | Vrite Transactions                           |     |

|            | 5.3.1  | Data Path                                    |     |

| 5.4        | TC[3:  | 0] Encoding with MPC860 IDMA                 |     |

| 5.5        | _      | A Status Tracking                            |     |

| 5.6        |        | A Errors, Resets, and Interrupts             |     |

| 5.7        |        | A Endian Issues                              |     |

|            |        |                                              | 0.3 |

|            | _      | : The DMA Channel                            |     |

| 6.1        |        | view                                         |     |

| 6.2        |        | Registers                                    |     |

|            | 6.2.1  | Burst Cycles                                 |     |

|            | 6.2.2  | DMA Cycles on QBus                           |     |

| 6.3        |        | t Mode DMA Operation                         |     |

|            | 6.3.1  | Initiating a Direct Mode Transfer            |     |

| <i>(</i> ) | 6.3.2  | Terminating a Direct Mode Transfer           |     |

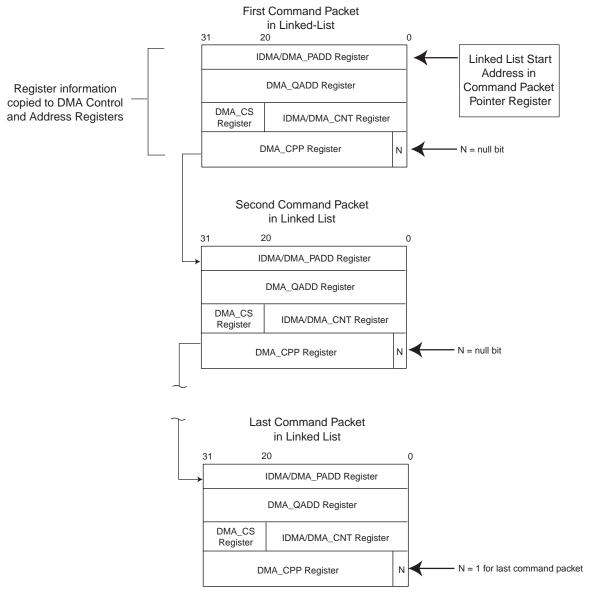

| 6.4        |        | d List Mode DMA Operation.                   |     |

|            | 6.4.1  | Initiating a Linked List Mode DMA Operation  |     |

|            | 6.4.2  | Terminating a Linked List Mode DMA Operation | 102 |

| Chaj | pter 7: The Register Channel                                             | 103 |

|------|--------------------------------------------------------------------------|-----|

| 7.1  | Overview                                                                 | 103 |

| 7.2  | Register Access Fairness                                                 | 104 |

| 7.3  | Register Access from the PCI Bus                                         | 105 |

| 7.4  | Register Access from the QBus                                            | 107 |

|      | 7.4.1 Examples of QBus Register Accesses                                 | 108 |

|      | 7.4.2 PCI Configuration Cycles Generated from the QBus                   | 108 |

|      | 7.4.3 Address Phase of PCI Configuration Cycles                          | 109 |

|      | 7.4.3.1 Data Phase of PCI Configuration Cycles                           | 110 |

|      | 7.4.4 Interrupt Acknowledge Cycle                                        | 110 |

| 7.5  | Register Access Synchronization                                          | 111 |

| 7.6  | Mailbox Registers                                                        | 112 |

| Cha  | pter 8: The Interrupt Channel                                            | 113 |

| 8.1  | Overview                                                                 |     |

| 8.2  | Hardware-Triggered Interrupts                                            | 114 |

| 8.3  | Software-Triggered Interrupts                                            |     |

|      | 8.3.1 Interrupt Generation due to PCI Configuration Register Status Bits |     |

| 8.4  | Interrupt Acknowledge Cycle                                              |     |

| 8.5  | Disabling PCI Interrupts                                                 | 119 |

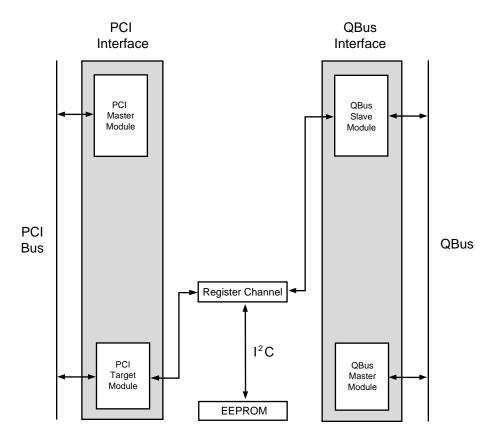

| Chai | pter 9: The EEPROM Channel                                               | 121 |

| 9.1  | Overview                                                                 |     |

| 9.2  | EEPROM Configuration and Plug and Play Compatibility                     |     |

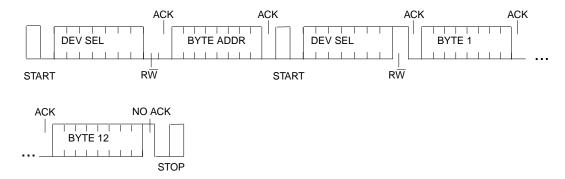

| 9.3  | EEPROM I <sup>2</sup> C Protocol                                         |     |

| 9.4  | Mapping of EEPROM Bits to QSpan II Registers                             |     |

| 9.5  | Programming the EEPROM from the QBus or PCI Bus                          |     |

|      | 9.5.1 Writing to the EEPROM                                              |     |

|      | 9.5.2 Reading from the EEPROM                                            |     |

| 9.6  | EEPROM Access.                                                           |     |

| 9.7  | Vital Product Data Support                                               |     |

|      | 9.7.1 Reading VPD Data                                                   |     |

|      | 9.7.2 Writing VPD Data.                                                  | 129 |

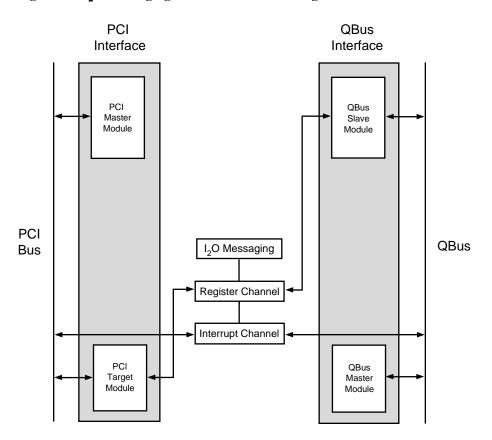

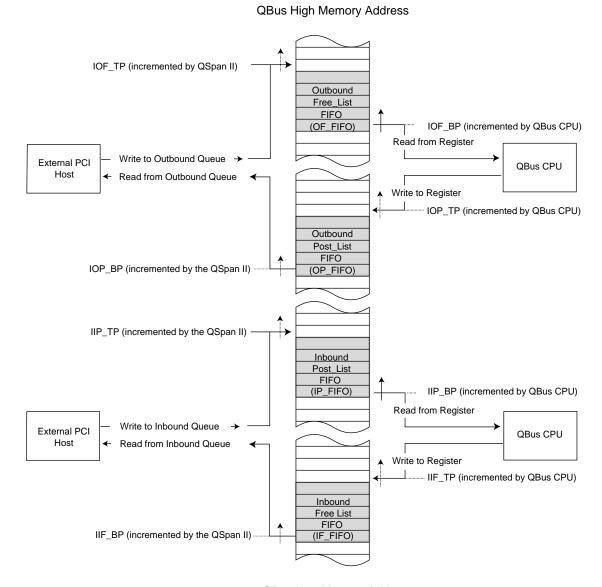

| Chai | pter 10: I <sub>2</sub> O Messaging Unit                                 | 131 |

| 10.1 | Overview                                                                 |     |

| 10.2 | Inbound Messaging                                                        |     |

| 10.3 | Outbound Messaging                                                       |     |

| 10.4 | I <sub>2</sub> O Operation                                               |     |

| 10.5 | Summary of I <sub>2</sub> O Operations                                   |     |

|      | 10.5.1 Initialization                                                    |     |

|      | 10.5.1.1 Inbound I <sub>2</sub> O Message                                |     |

|      | 10.5.1.2 I <sub>2</sub> O Outbound Message                               |     |

| 10.6 | I <sub>2</sub> O Interrupts                   | 137 |

|------|-----------------------------------------------|-----|

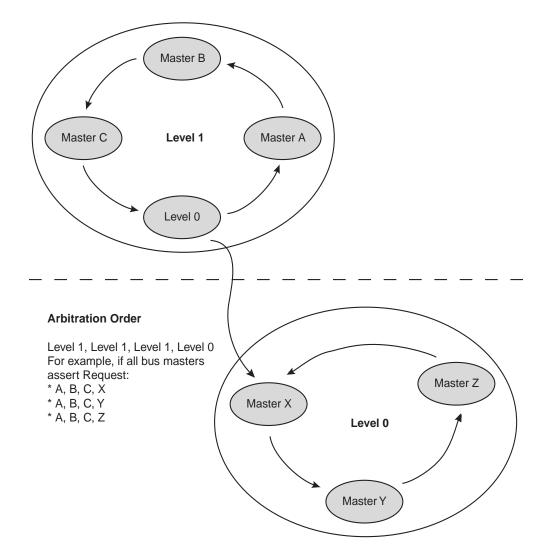

| Cha  | pter 11: PCI Bus Arbiter                      | 139 |

| 11.1 | Overview                                      | 139 |

| 11.2 | Arbitration Scheme                            | 140 |

| 11.3 | Bus Parking                                   | 142 |

| Cha  | pter 12: CompactPCI Hot Swap Friendly Support | 143 |

| 12.1 | Overview                                      |     |

| 12.2 | Hot Swapping with the QSpan II                | 144 |

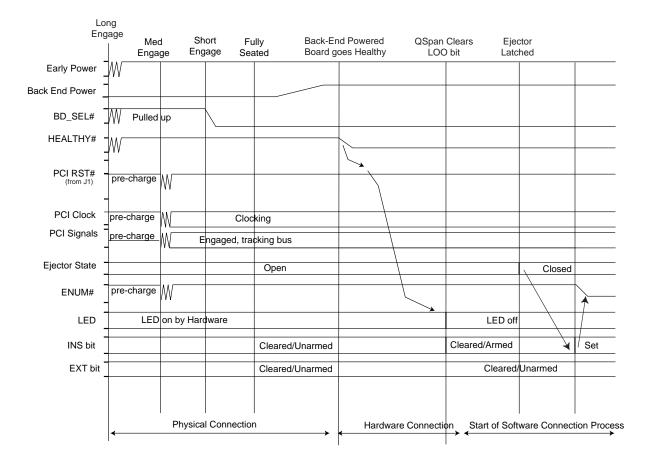

| 12.3 | CompactPCI Hot Swap Card Insertion            | 145 |

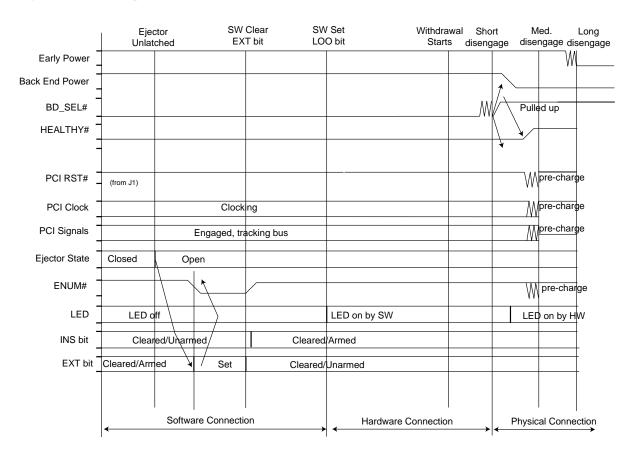

| 12.4 | CompactPCI Hot Swap Card Extraction.          | 147 |

| Cha  | pter 13: PCI Power Management Event Support   | 151 |

| 13.1 | Overview                                      |     |

| 13.2 | Power Management Event (PME#) Support         | 151 |

| Cha  | pter 14: Reset Options                        | 153 |

| 14.1 | Types of Resets                               |     |

|      | 14.1.1 PCI Transactions during QBus Reset     |     |

|      | 14.1.2 IDMA Reset                             | 154 |

|      | 14.1.3 Clocking and Resets                    | 154 |

| 14.2 | Configuration Options at Reset                | 155 |

|      | 14.2.1 PCI Bus Master Reset Option            | 155 |

|      | 14.2.2 QBus Master and Slave Modes            | 156 |

|      | 14.2.3 EEPROM Loading                         | 156 |

|      | 14.2.4 PCI Register Access Option             |     |

|      | 14.2.5 PCI Bus Arbitration Option             | 156 |

| Cha  | pter 15: Hardware Implementation Issues       | 157 |

| 15.1 | Test Mode Pins                                | 157 |

| 15.2 | JTAG Support                                  | 158 |

| 15.3 | Decoupling Capacitors                         | 158 |

| Cha  | pter 16: Signals                              | 159 |

| 16.1 | Terminology                                   | 159 |

| 16.2 | Overview                                      | 160 |

| 16.3 | MC68360 Signals: QUICC                        | 161 |

| 16.4 | MPC860 Signals: PowerQUICC                    | 165 |

| 16.5 | M68040 Signals                                | 169 |

| 16.6 | PCI Bus Signals                               | 172 |

| 16.7 | Hot Swap Signals                              | 174 |

| 16.8 | Miscellaneous Signals                         | 175 |

| 16.9 | JTAG Signals                                  | 176 |

| Chap | oter 17 | ': Signals and DC Characteristics         | 77         |

|------|---------|-------------------------------------------|------------|

| 17.1 | Termin  | ology                                     | 177        |

| 17.2 | Packag  | ring and Voltage Level Support            | 178        |

| 17.3 | Signals | s and DC Characteristics                  | 178        |

| 17.4 |         |                                           |            |

| Appe | endix A | A: Registers                              | 93         |

| A.1  |         | ew                                        |            |

| A.2  | Termin  | ology                                     | 194        |

| A.3  |         | er Map                                    |            |

| A.4  | Registe | ers                                       | 200        |

| Appe | endix l | B: Timing                                 | 299        |

| B.1  |         | ew                                        |            |

| B.2  | Timing  | Parameters                                | 300        |

| B.3  | Wait S  | tate Insertion — QBus Slave Module        | 314        |

| B.4  | Timing  | Diagrams                                  | 315        |

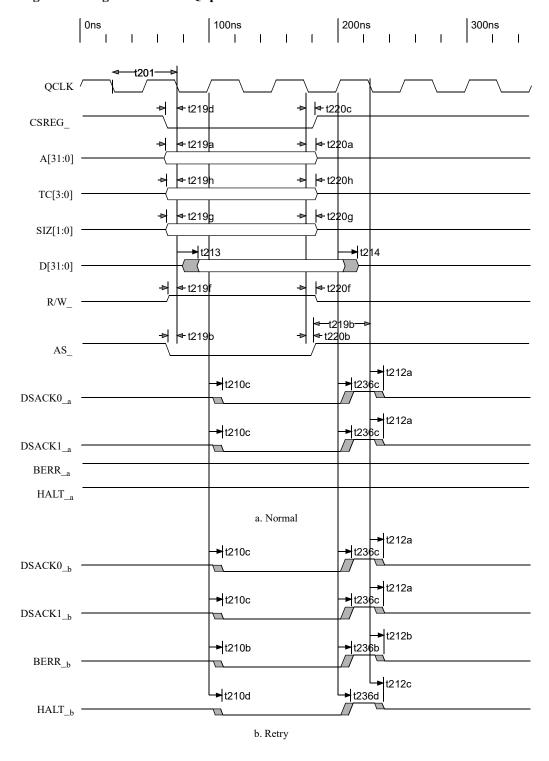

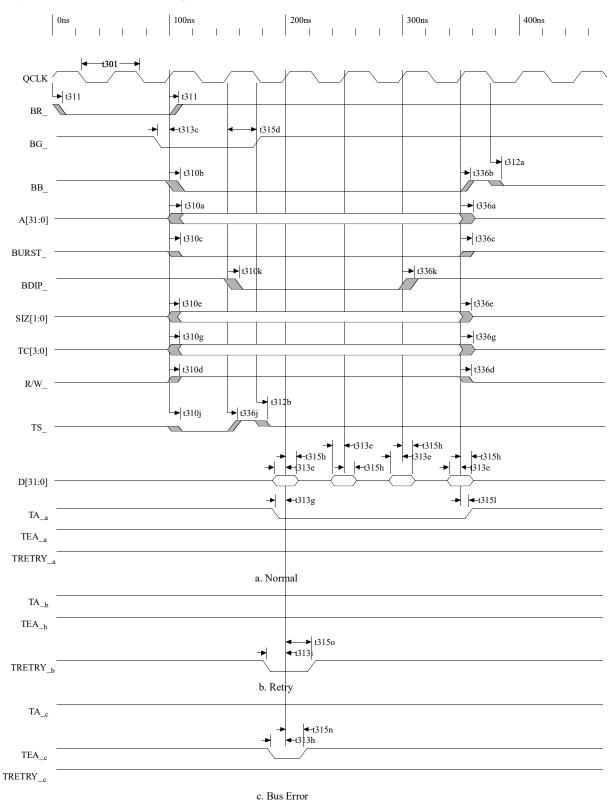

|      | B.4.1   | QBus Interface — MC68360                  |            |

|      | B.4.2   | QBus Master Cycles — MC68360              | 315        |

|      |         | B.4.2.1 QBus Slave Cycles — MC68360       | 318        |

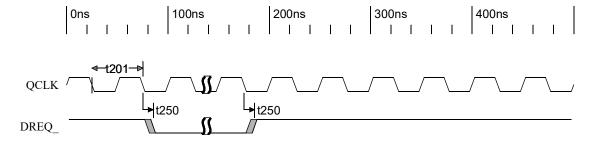

|      |         | B.4.2.2 QBus IDMA Cycles — MC68360        | 322        |

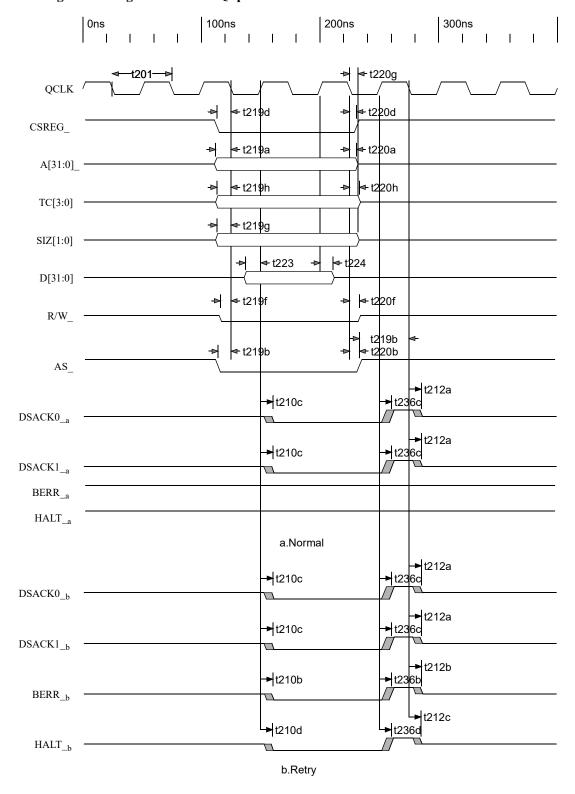

|      | B.4.3   | QBus Interface — MPC860                   | 330        |

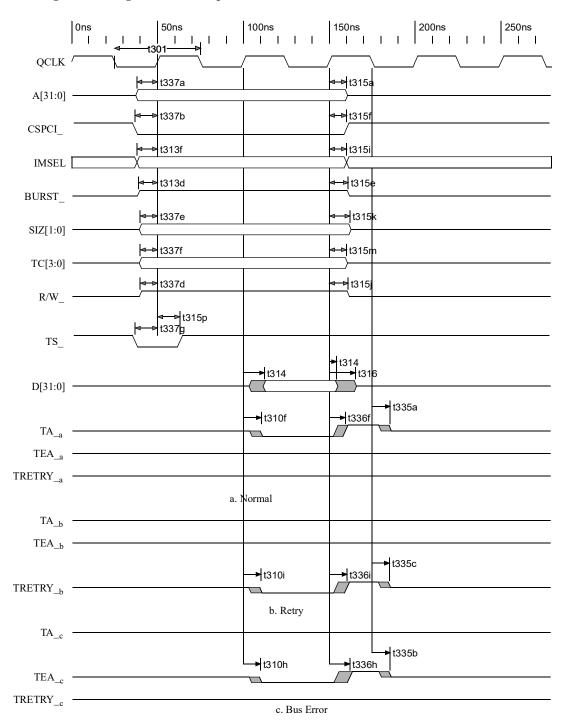

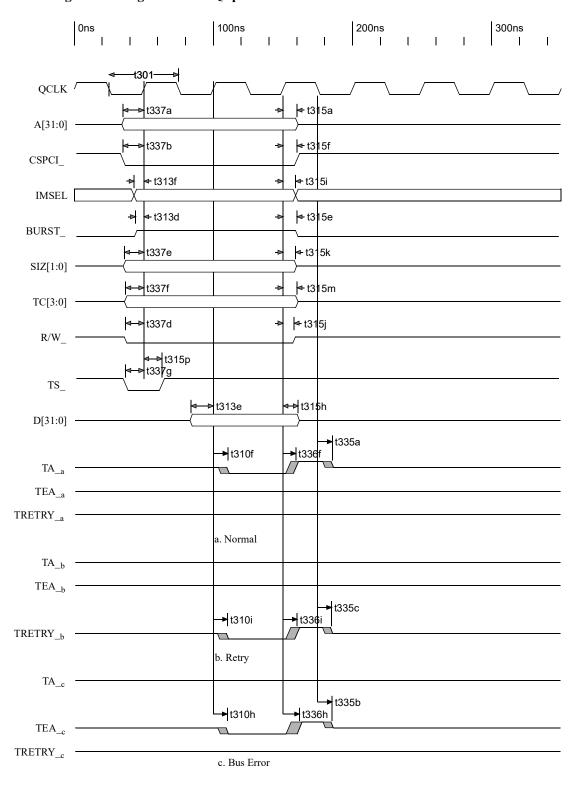

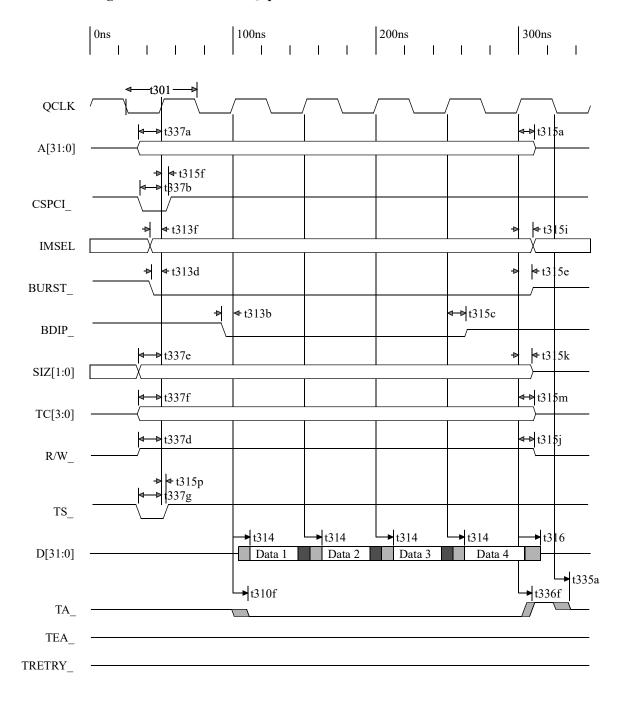

|      |         | B.4.3.1 QBus Master Cycles — MPC860       | 330        |

|      |         | B.4.3.2 QBus Slave Cycle — MPC860         | 335        |

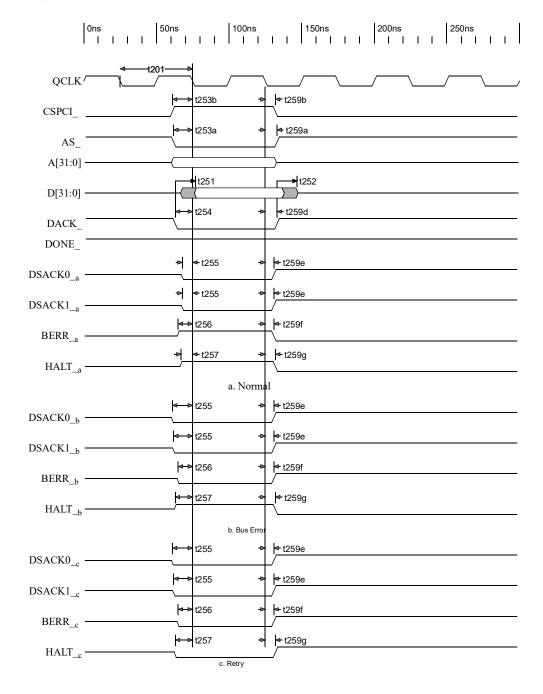

|      |         | B.4.3.3 QBus IDMA Cycles — MPC860         | 341        |

|      | B.4.4   | QBus Interface — M68040                   | 345        |

|      |         | B.4.4.1 QBus Master Cycles — M68040       | 346        |

|      |         | B.4.4.2 QBus Slave Cycles — M68040        | 349        |

|      | B.4.5   | Interrupts and Resets                     | 355        |

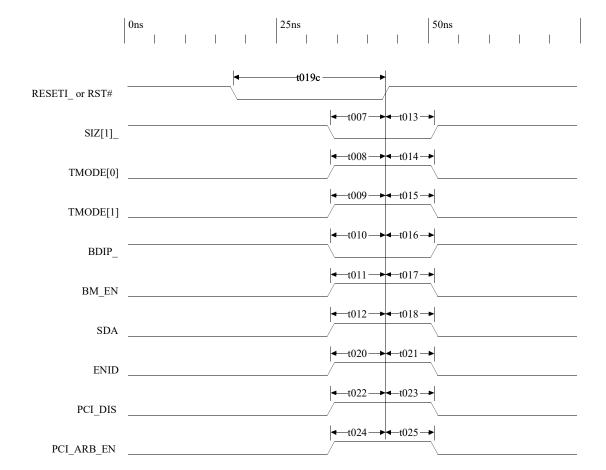

|      | B.4.6   | Reset Options                             | 357        |

| Appe | endix ( | C: Typical Applications                   | <b>5</b> 9 |

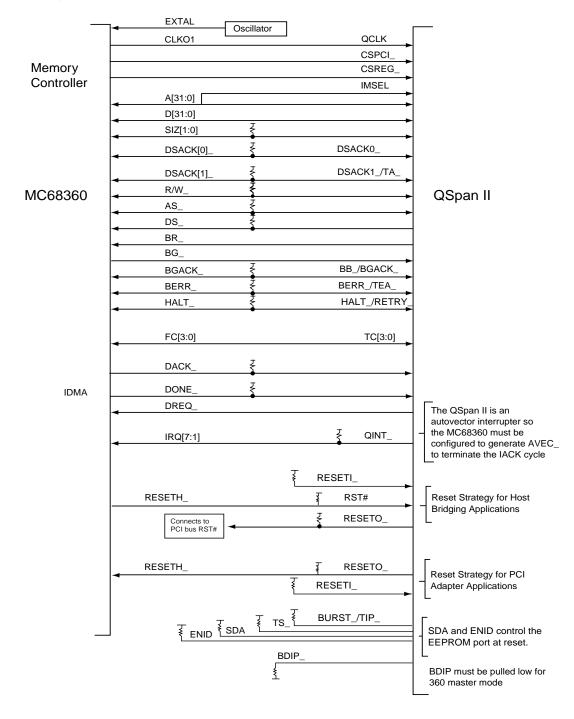

| C.1  | MC683   | 360 Interface                             | 359        |

|      | C.1.1   | Hardware Interface                        | 359        |

|      |         | C.1.1.1 Clocking                          | 359        |

|      |         | C.1.1.2 Resets                            | 360        |

|      |         | C.1.1.3 Memory Controller                 | 361        |

|      |         | C.1.1.4 QBus Direct Connects              | 362        |

|      |         | C.1.1.5 Interrupts.                       | 362        |

|      |         | C.1.1.6 PCI Signals                       |            |

|      |         | C.1.1.7 EEPROM Interface.                 | 362        |

|      |         | C.1.1.8 Reset Options                     | 363        |

|      |         | C.1.1.9 Unused Inputs Requiring Pull-Ups. | 363        |

|            |         | C.1.1.10 No Connects                     | 363 |

|------------|---------|------------------------------------------|-----|

|            |         | C.1.1.11 JTAG Signals                    | 363 |

|            |         | C.1.1.12 Address Multiplexing for DRAM   | 364 |

|            | C.1.2   | Software Issues                          |     |

|            | C.1.3   | MC68360 Slave Mode Interface             |     |

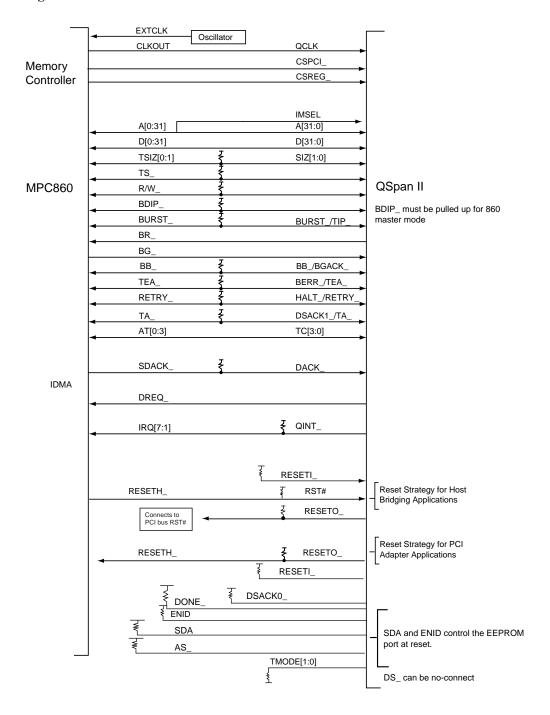

| C.2        | MPC86   | 60 Interface                             | 365 |

|            | C.2.1   | Hardware Interface                       | 366 |

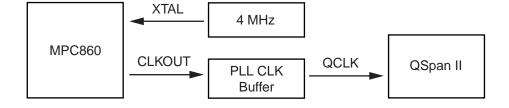

|            |         | C.2.1.1 Clocking                         | 366 |

|            |         | C.2.1.2 Resets                           | 367 |

|            |         | C.2.1.3 Memory Controller                | 368 |

|            |         | C.2.1.4 QBus Direct Connects             | 368 |

|            |         | C.2.1.5 Interrupts                       | 369 |

|            |         | C.2.1.6 PCI Signals                      | 369 |

|            |         | C.2.1.7 EEPROM Interface                 | 369 |

|            |         | C.2.1.8 Reset Options                    | 369 |

|            |         | C.2.1.9 Unused Inputs Requiring Pull-Ups | 370 |

|            |         | C.2.1.10 No Connects                     |     |

|            |         | C.2.1.11 JTAG Signals                    | 370 |

|            |         | C.2.1.12 Bused Signals                   | 370 |

|            |         | C.2.1.13 Address Multiplexing for DRAM   | 370 |

|            |         | C.2.1.14 Software Issues                 |     |

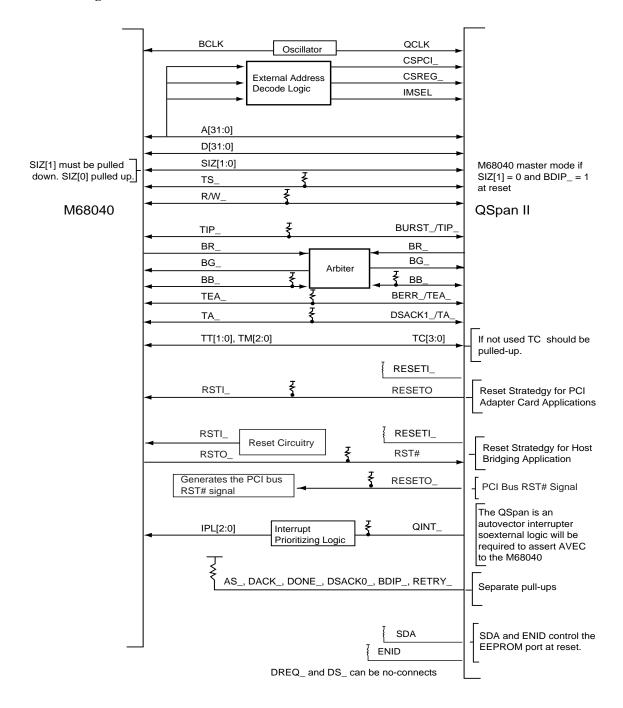

| C.3        | M6804   | O Interface                              | 372 |

|            | C.3.1   | Hardware Interface                       | 373 |

|            |         | C.3.1.1 Clocking                         | 373 |

|            |         | C.3.1.2 Resets                           | 373 |

|            |         | C.3.1.3 Address Decoder                  | 374 |

|            |         | C.3.1.4 QBus Direct Connects             | 374 |

|            |         | C.3.1.5 Interrupts                       |     |

|            |         | C.3.1.6 PCI Signals                      | 375 |

|            |         | C.3.1.7 EEPROM Interface                 | 375 |

|            |         | C.3.1.8 Reset Options                    |     |

|            |         | C.3.1.9 Unused Inputs Requiring Pull-Ups | 376 |

|            |         | C.3.1.10 No Connects                     | 376 |

|            |         | C.3.1.11 JTAG Signals                    | 376 |

| Anne       | endiv l | D: Software Initialization               | 377 |

| D.1        |         | laneous Control Register Configuration   |     |

| D.1        |         | Slave Channel Initialization             |     |

| D.3        | -       | er Access from the PCI Bus               |     |

| D.3<br>D.4 | _       | arget Channel Initialization             |     |

| D.4<br>D.5 |         | Logging of Posted Transactions           |     |

| D.5        |         | /DMA Channel Initialization              | 384 |

| D.7        | Interrupt Initialization                        | 384 |

|------------|-------------------------------------------------|-----|

| D.8        | Generation of PCI Configuration and IACK Cycles | 385 |

| D.9        | EEPROM and VPD Initialization                   | 386 |

| D.10       | I <sub>2</sub> O Messaging Unit Initialization  | 386 |

| D.11       | PCI Expansion ROM Implementation                |     |

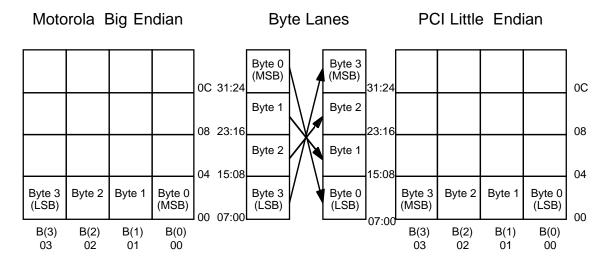

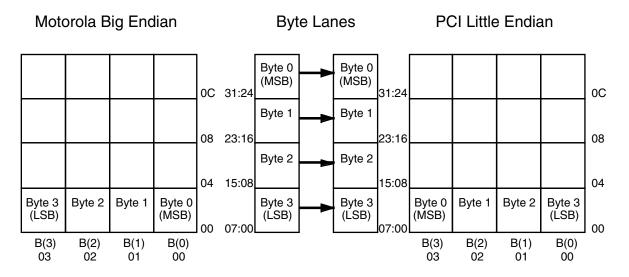

| App        | endix E: Endian Mapping                         | 389 |

| E.1        | Overview                                        |     |

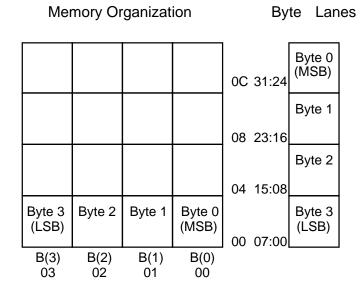

| E.2        | Big-Endian System                               | 390 |

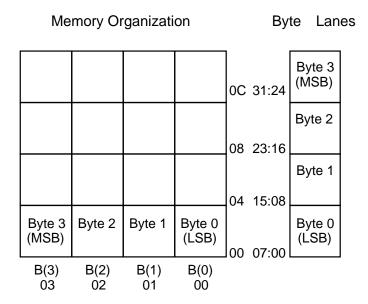

| E.3        | Little-Endian System                            |     |

| E.4        | Endian Mapping Methods                          |     |

|            | E.4.1 Address Invariance                        |     |

|            | E.4.2 Data Invariance                           |     |

|            | E.4.3 Combined Method                           |     |

| Chai       | pter 18: Operating and Storage Conditions       | 395 |

| 18.1       | Power Dissipation                               |     |

| 18.2       | Operating Conditions.                           |     |

| 18.3       | Thermal Characteristics                         |     |

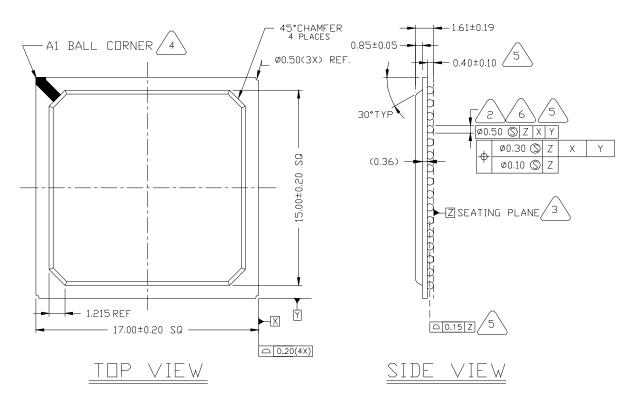

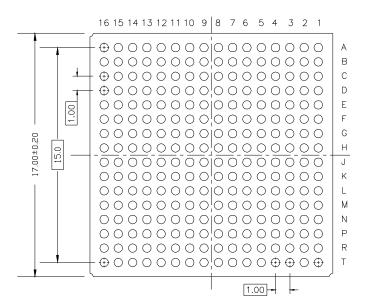

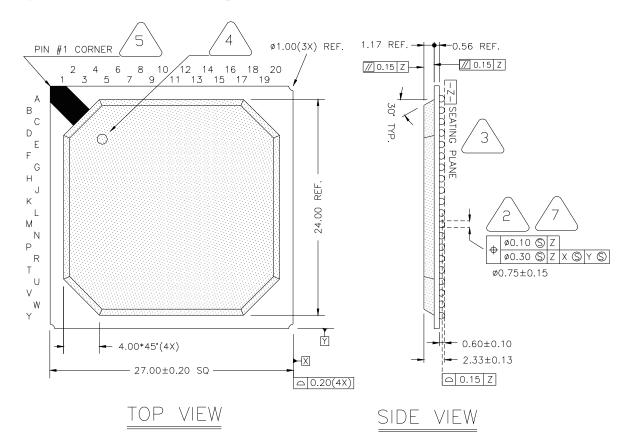

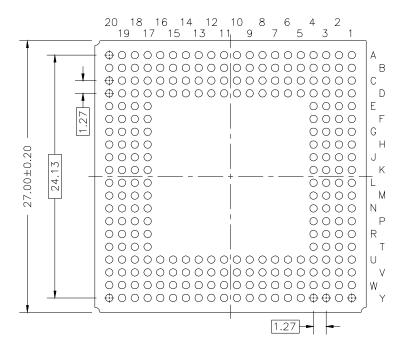

| Ann        | endix F: Mechanical Information                 | 300 |

| App<br>F.1 |                                                 |     |

| Г.1        | Mechanical Information                          |     |

|            |                                                 |     |

|            | F.1.1.1 PBGA Notes — 17 mm                      |     |

|            | F.1.2 256 PBGA — 27 mm                          |     |

|            |                                                 |     |

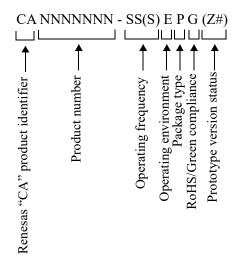

|            | endix G: Ordering Information                   |     |

| G.1        | Ordering Information                            |     |

| G.2        | Part Numbering Information                      | 406 |

| Glos       | ssary                                           | 409 |

| In da      |                                                 | 411 |

# **List of Figures**

| Figure 1:  | QSpan II Bridging PCI and Processor Buses            | 24  |

|------------|------------------------------------------------------|-----|

| Figure 2:  | QSpan II Functional Diagram                          | 30  |

| Figure 3:  | QBus Slave Channel — Functional Diagram              | 34  |

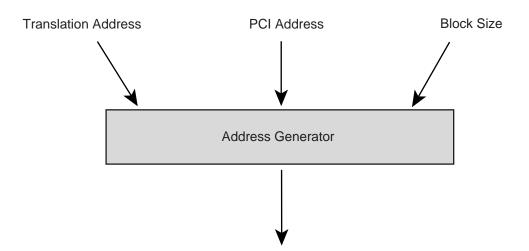

| Figure 4:  | Address Generator for QBus Slave Channel Transfers   | 41  |

| Figure 5:  | PCI Target Channel — Functional Diagram              | 56  |

| Figure 6:  | Address Generator for PCI Target Channel Transfers   | 63  |

| Figure 7:  | IDMA Channel — Functional Diagram                    | 84  |

| Figure 8:  | DMA Channel — Functional Diagram                     | 94  |

| Figure 9:  | Linked List DMA Operation                            | 99  |

| Figure 10: | Register Channel — Functional Diagram                | 104 |

| Figure 11: | QSpan II Control and Status Registers                | 105 |

| Figure 12: | QCSR Access from the QBus                            | 107 |

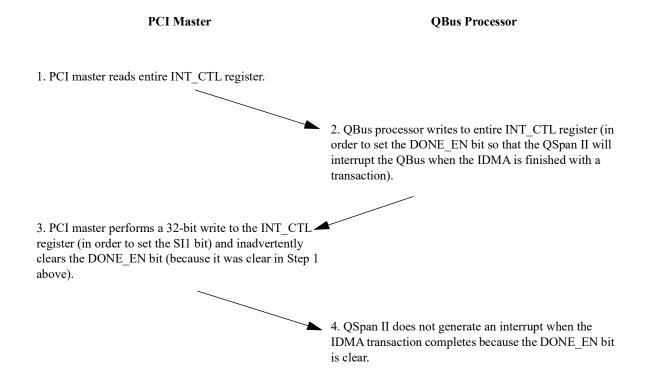

| Figure 13: | Example of a Register-Access Synchronization Problem | 111 |

| Figure 14: | Interrupt Channel — Functional Diagram               | 114 |

| Figure 15: | EEPROM Channel — Functional Diagram                  | 122 |

| Figure 16: | Sequential Read from EEPROM                          | 123 |

| Figure 17: | I <sub>2</sub> O Messaging Unit — Functional Diagram | 132 |

| Figure 18: | I <sub>2</sub> O Implementation                      | 133 |

| Figure 19: | PCI Bus Arbiter — Functional Diagram                 | 140 |

| Figure 20: | PCI Bus Arbiter — Arbitration Scheme                 | 141 |

| Figure 21: | CompactPCI Hot Swap — Functional Diagram             | 144 |

| Figure 22: | Hot Swap Card Insertion                              | 147 |

| Figure 23: | Hot Swap Card Extraction                             | 149 |

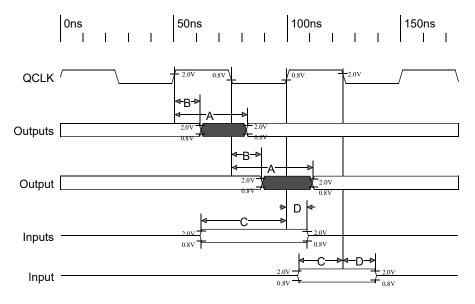

| Figure 24: | Reference Voltages for AC Timing Specification       | 300 |

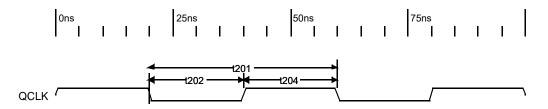

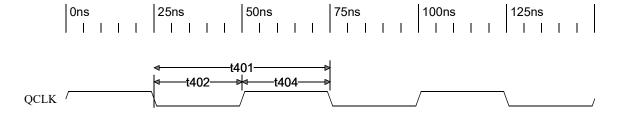

| Figure 25: | QCLK Input Timing — MC68360 CLKO1                    | 315 |

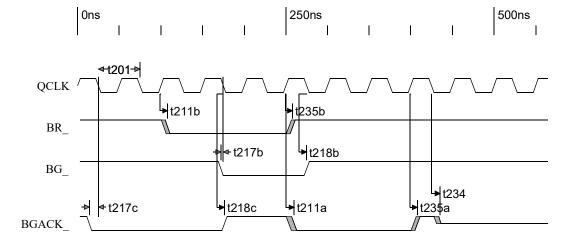

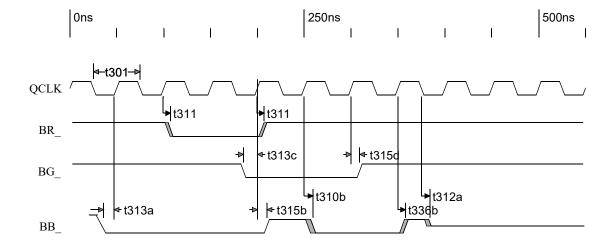

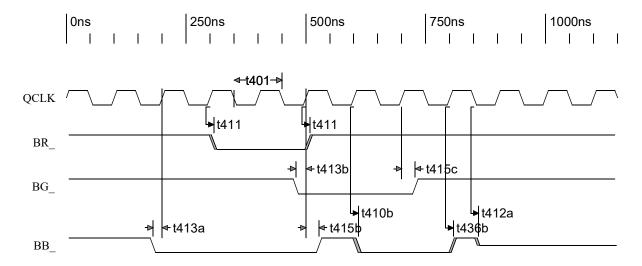

| Figure 26: | QBus Arbitration — MC68360                           | 315 |

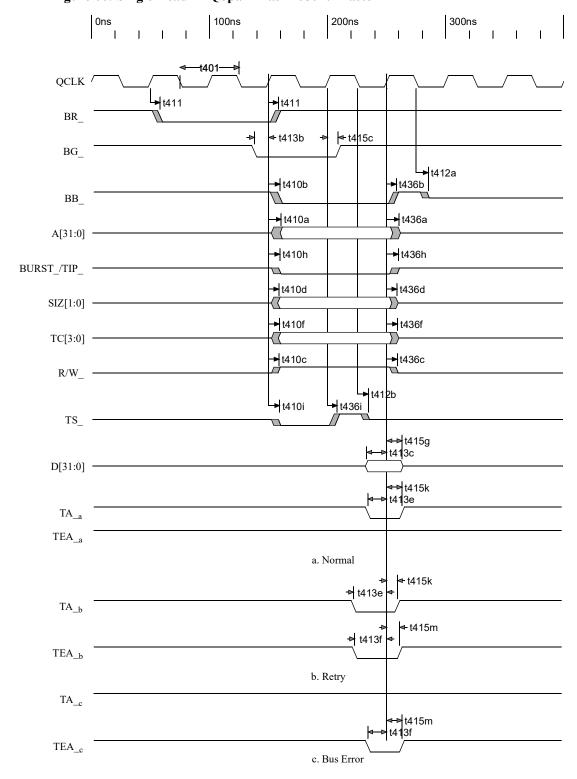

| Figure 27: | Single Read — QSpan II as MC68360 Master             | 316 |

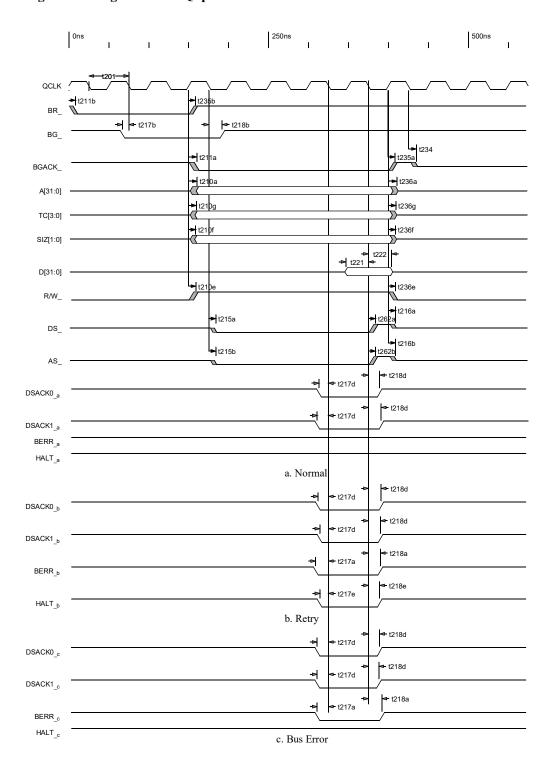

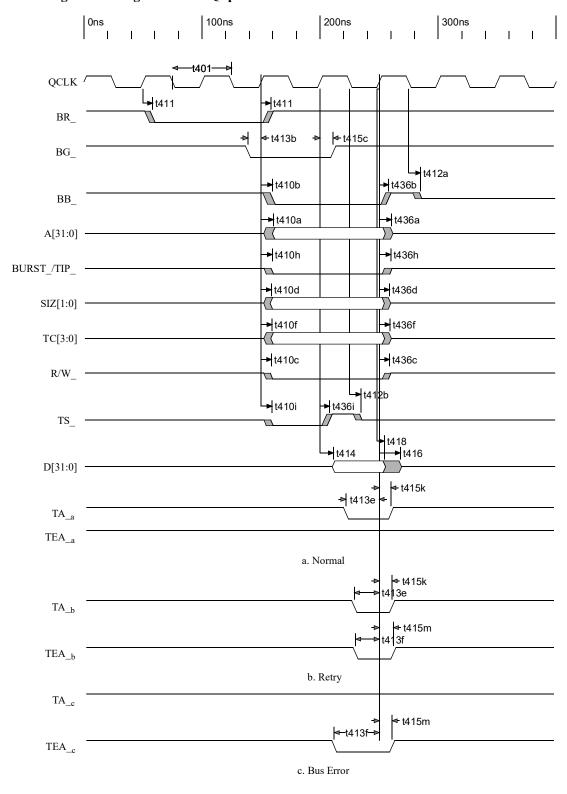

| Figure 28: | Single Write — QSpan II as MC68360 Master            | 317 |

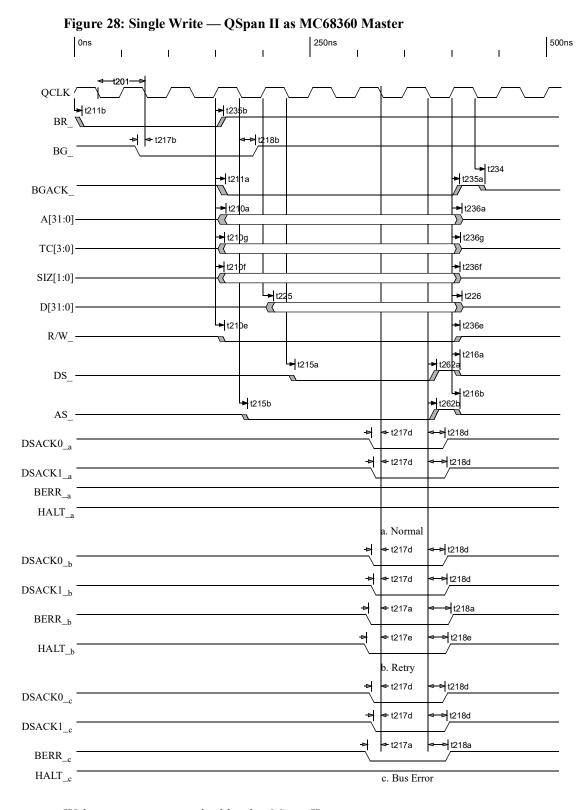

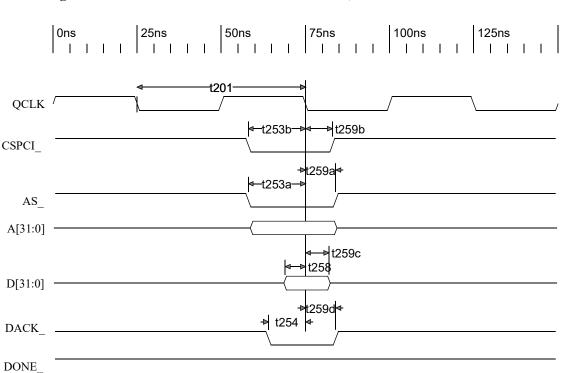

| Figure 29: | Delayed Single Read — QSpan II as MC68360 Slave      | 318 |

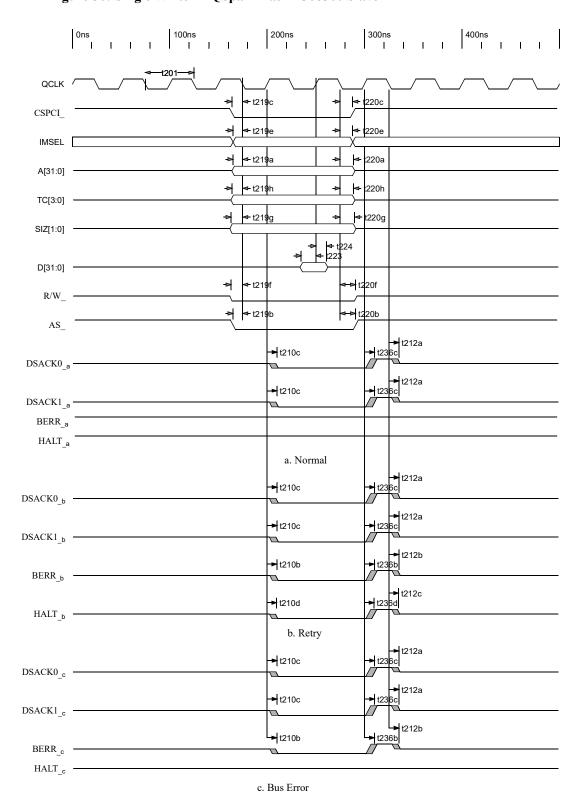

| Figure 30: | Single Write — QSpan II as MC68360 Slave             | 319 |

| Figure 31: | Register Read — QSpan II as MC68360 Slave                  | 320 |

|------------|------------------------------------------------------------|-----|

| Figure 32: | Register Write — QSpan II as MC68360 Slave                 | 321 |

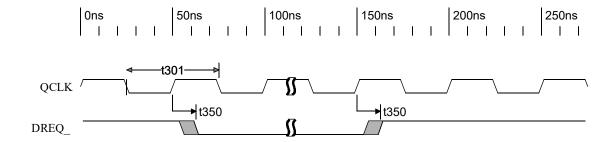

| Figure 33: | MC68360 DREQ_ Timing                                       | 322 |

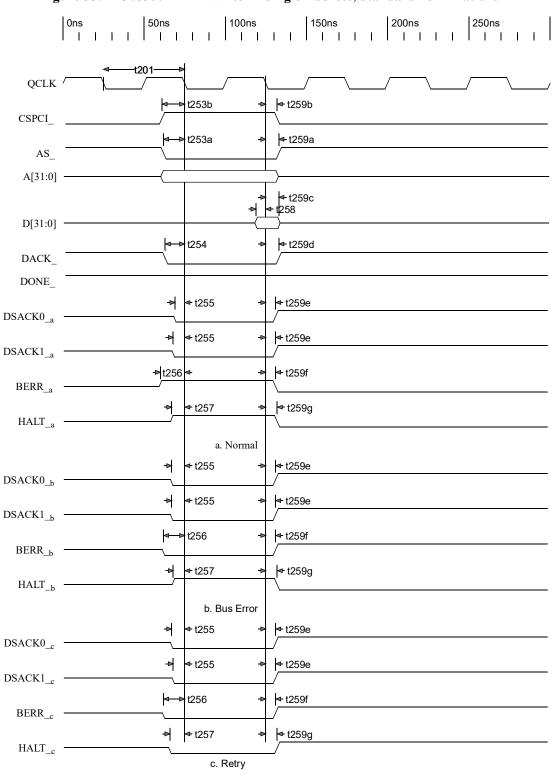

| Figure 34: | MC68360 IDMA Read — Single Address, Standard Terminations  | 323 |

| Figure 35: | MC68360 IDMA Write — Single Address, Standard Terminations | 324 |

| Figure 36: | MC68360 IDMA Read — Single Address, Fast Termination       | 325 |

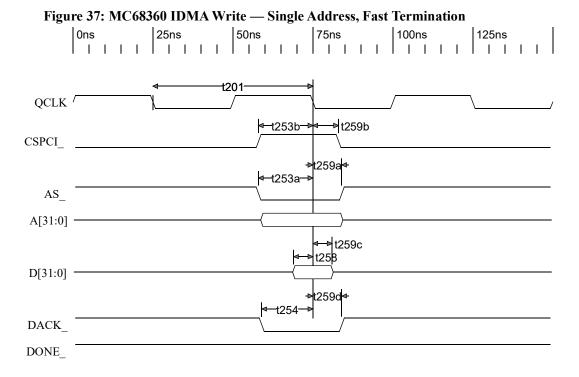

| Figure 37: | MC68360 IDMA Write — Single Address, Fast Termination      | 325 |

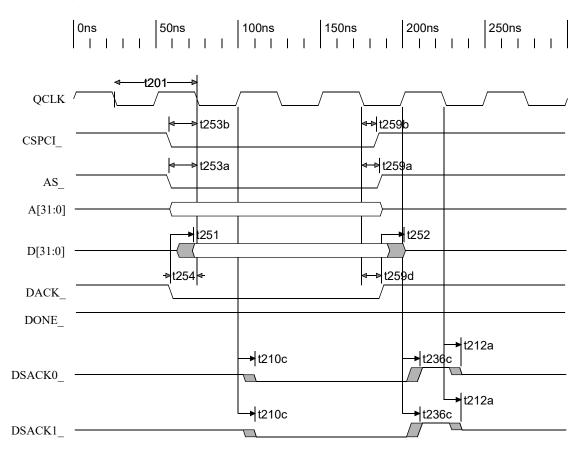

| Figure 38: | MC68360 IDMA Read — Dual Address, Standard Termination     | 326 |

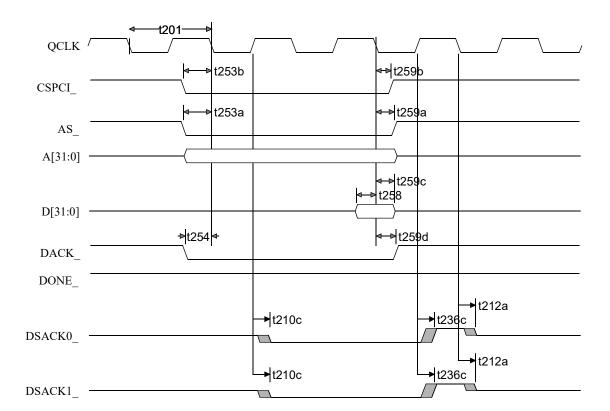

| Figure 39: | MC68360 IDMA Write — Dual Address, Standard Termination    | 327 |

| Figure 40: | MC68360 IDMA Read — Dual Address, Fast Termination         | 328 |

| Figure 41: | MC68360 IDMA Read — Dual Address, Fast Termination         | 329 |

| Figure 42: | QBus Arbitration — MPC860                                  | 330 |

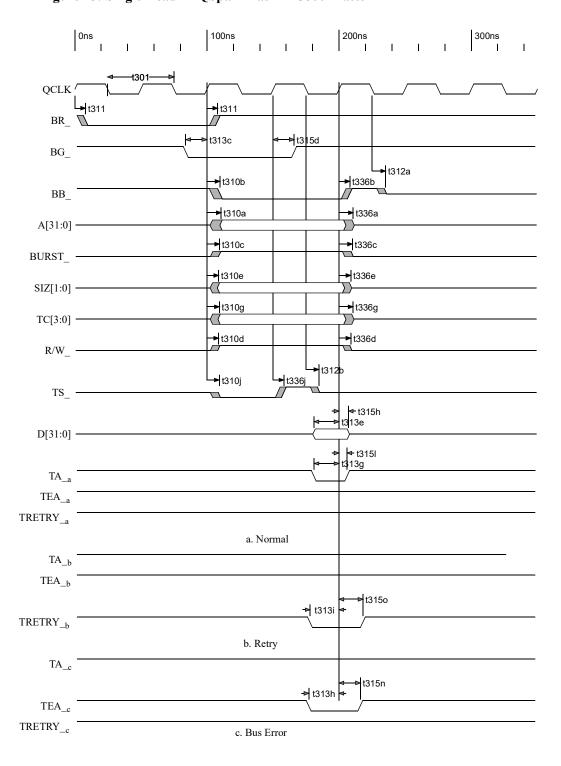

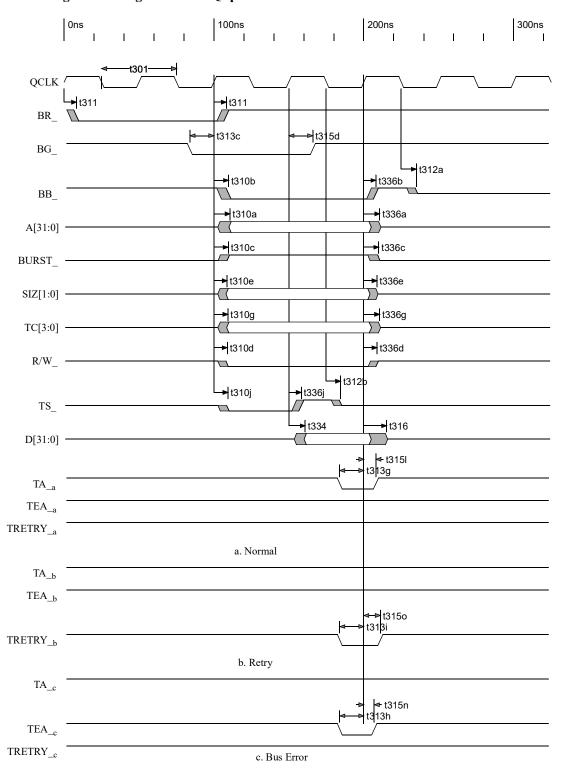

| Figure 43: | Single Read — QSpan II as MPC860 Master                    | 331 |

| Figure 44: | Single Write — QSpan II as MPC860 Master                   | 332 |

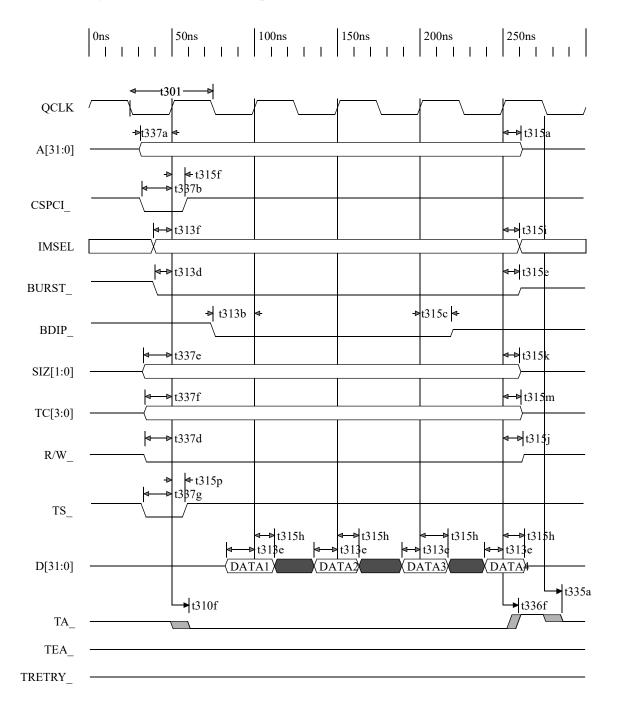

| Figure 45: | Burst Read — QSpan II as MPC860 Master                     |     |

| Figure 46: | Aligned Burst Write — QSpan II as MPC860 Master            | 334 |

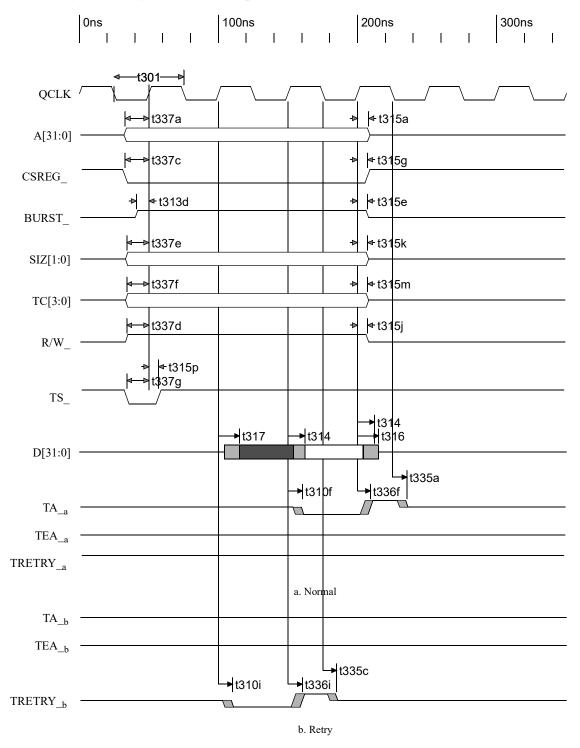

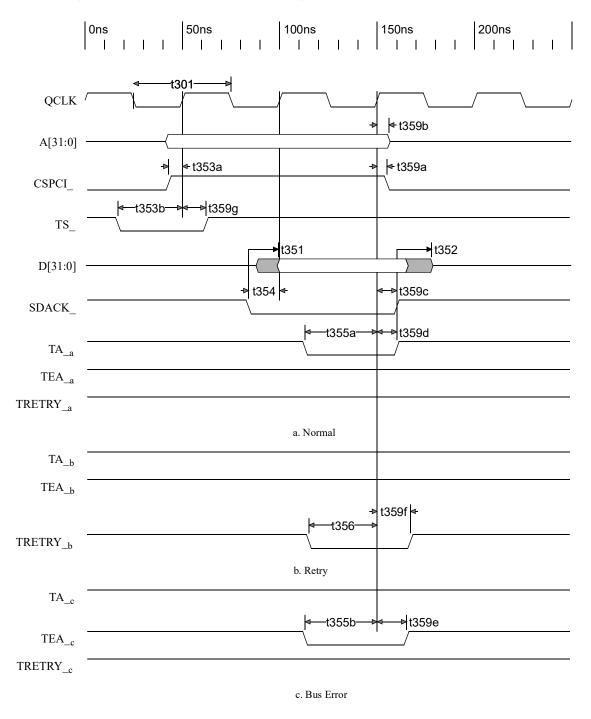

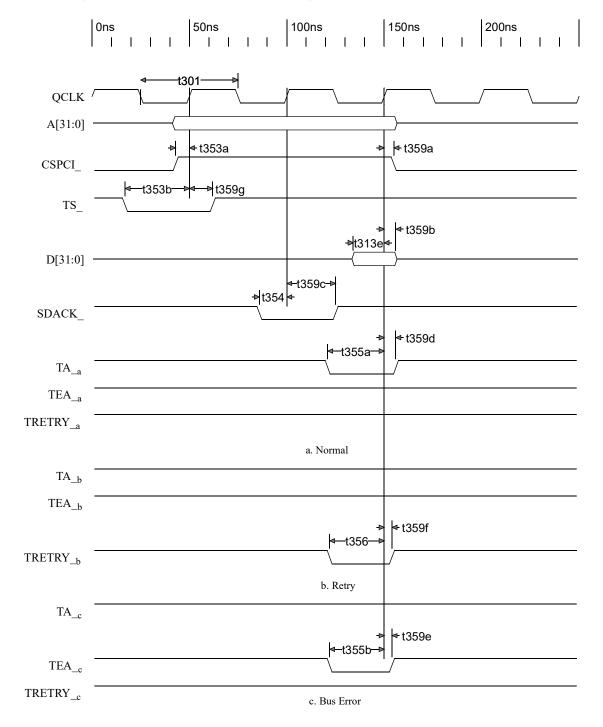

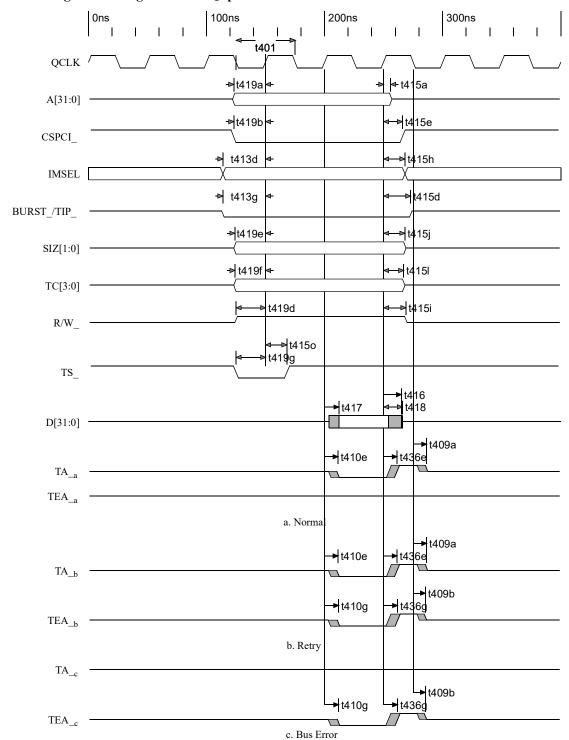

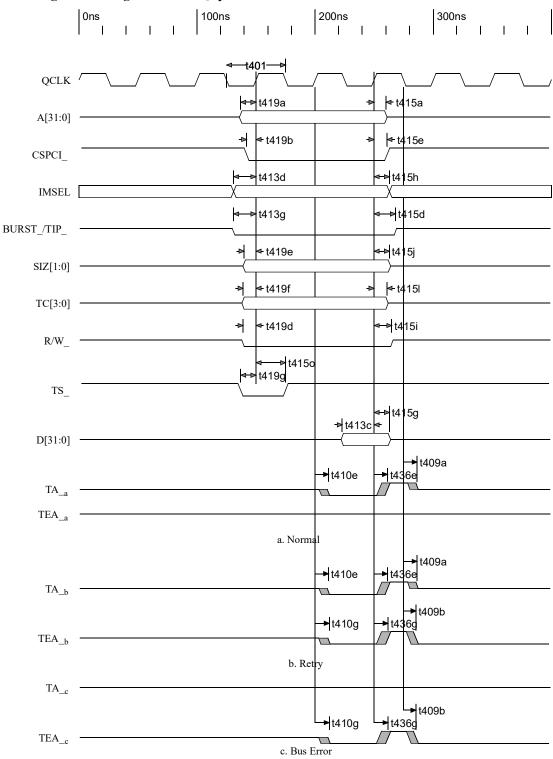

| Figure 47: | Single Read — QSpan II as MPC860 Slave                     | 335 |

| Figure 48: | Single Write — QSpan II as MPC860 Slave                    | 336 |

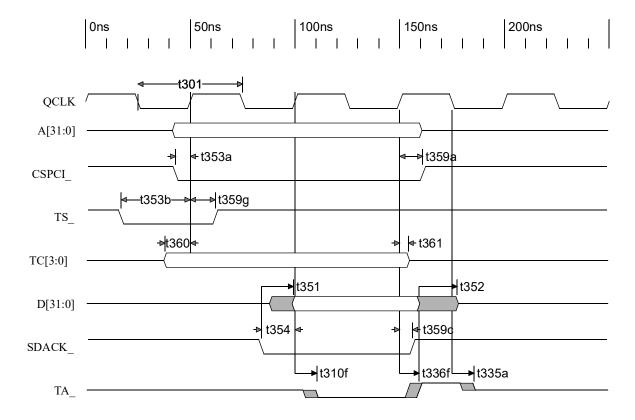

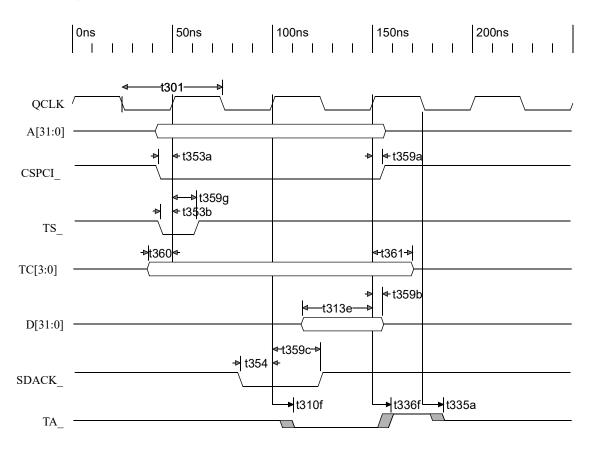

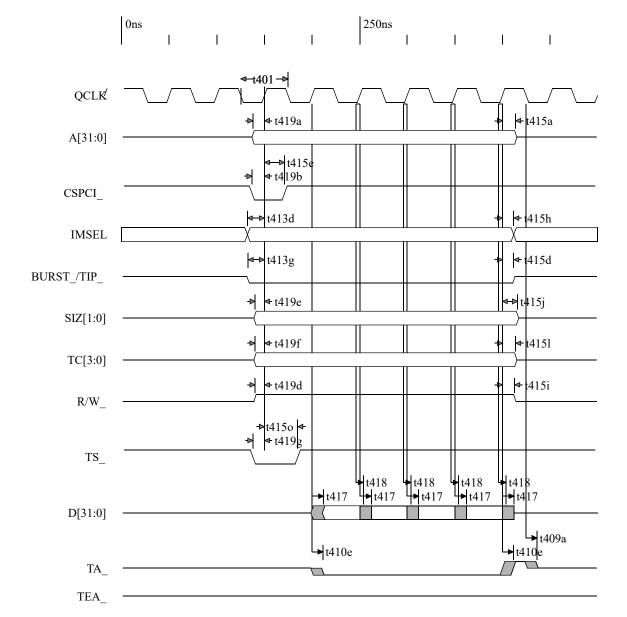

| Figure 49: | Burst Read — QSpan II as MPC860 Slave                      | 337 |

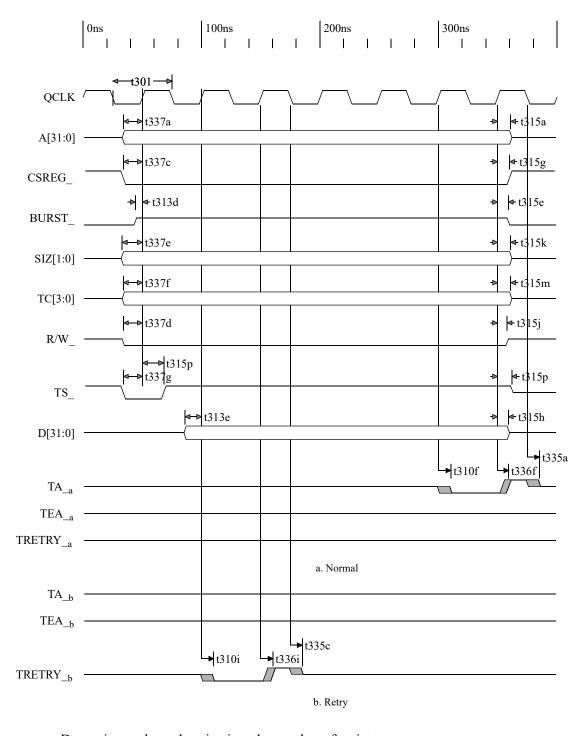

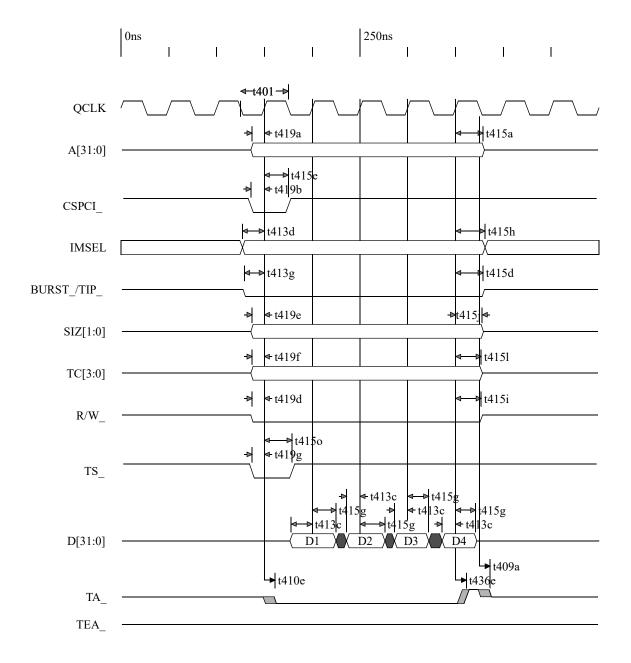

| Figure 50: | Burst Write — QSpan II as MPC860 Slave                     | 338 |

| Figure 51: | Register Read — QSpan II as MPC860 Slave                   | 339 |

| Figure 52: | Register Write — QSpan II as MPC860 Slave                  | 340 |

| Figure 53: | MPC860 DREQ_ Timing                                        | 341 |

| Figure 54: | MPC860 IDMA Read — Single Address                          | 342 |

| Figure 55: | MPC860 IDMA Write — Single Address                         | 343 |

| Figure 56: | MPC860 IDMA Read — Dual Address                            | 344 |

| Figure 57: | MPC860 IDMA Write — Dual Address                           | 345 |

| Figure 58: | QCLK Input Timing — M68040 BCLK                            | 345 |

| Figure 59: | QBus Arbitration — M68040                                  | 346 |

| Figure 60: | Single Read — QSpan II as M68040 Master                    | 347 |

| Figure 61: | Single Write — QSpan II as M68040 Master                   | 348 |

| Figure 62: | Single Read — QSpan II as M68040 Slave                     | 349 |

| Figure 63: | Single Write — QSpan II as M68040 Slave                    | 350 |

| Figure 64: | Delayed Burst Read — QSpan II as M68040 Slave              | 351 |

| Figure 65: | Posted Burst Write — QSpan II as M68040 Slave              | 352 |

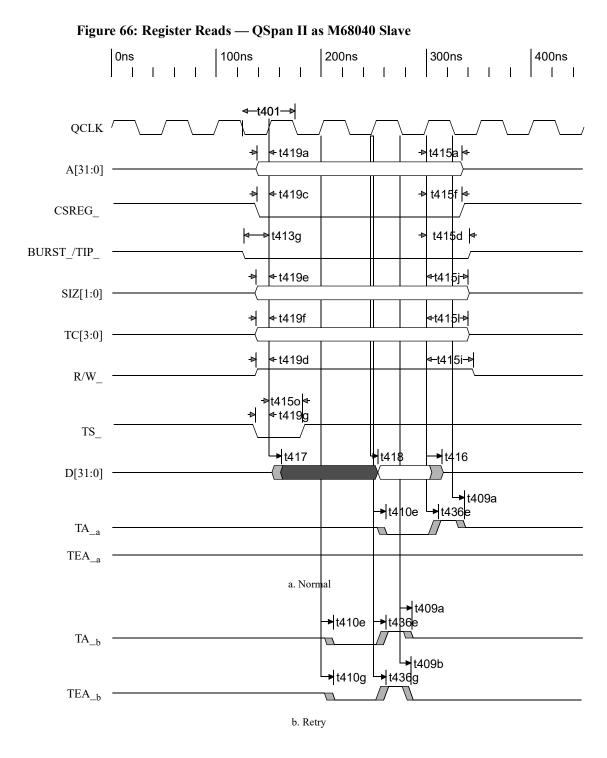

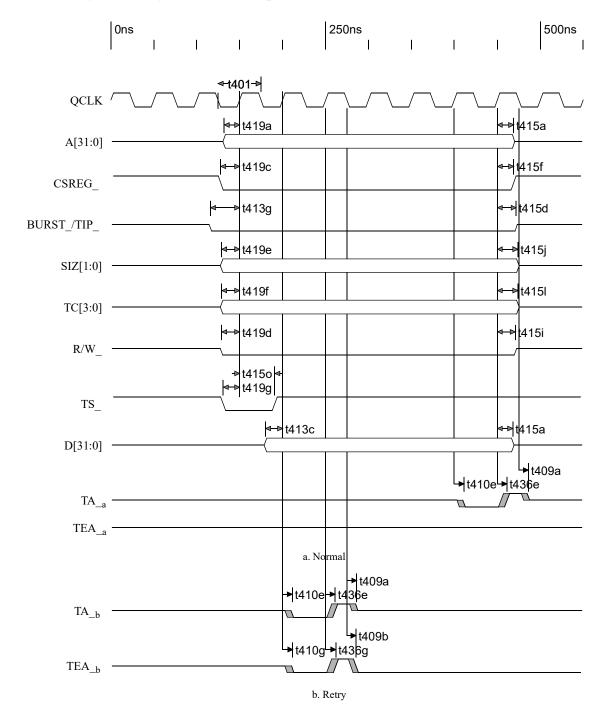

| Figure 66: | Register Reads — QSpan II as M68040 Slave                  |     |

| Figure 67: | Register Write — QSpan II as M68040 Slave                  | 354 |

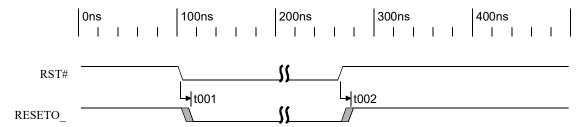

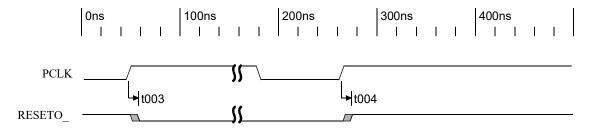

| Figure 68: | Reset from PCI Interface — RST# related to RESETO          | 355 |

| Figure 69: | Software Reset                                             | 355 |

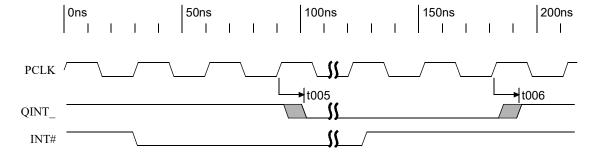

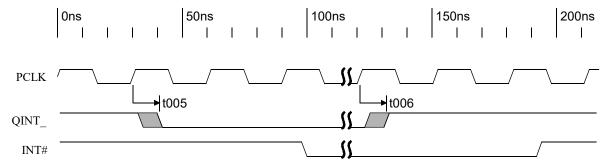

| Figure 70: | INT# Interrupt to QINT_ Interrupt               | 355   |

|------------|-------------------------------------------------|-------|

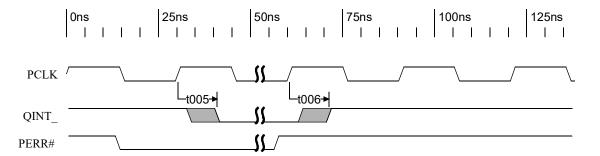

| Figure 71: | PERR# Interrupt                                 | 355   |

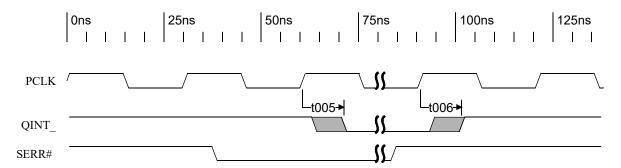

| Figure 72: | SERR# Interrupt                                 | 356   |

| Figure 73: | QINT_ Interrupt to INT# Interrupt               | 356   |

| Figure 74: | Reset Options                                   | 357   |

| Figure 75: | MC68360 Interface                               | 360   |

| Figure 76: | MPC860 Interface                                | 365   |

| Figure 77: | MPC860/QSpan II Clocking Scheme Example         | 366   |

| Figure 78: | Example Code for Executing an MPC860 Delay Loop | 367   |

| Figure 79: | M68040 Interface                                | 372   |

| Figure 80: | Big-Endian System                               | 390   |

| Figure 81: | Little-Endian System                            | . 391 |

| Figure 82: | Address Invariant Mapping                       | 392   |

| Figure 83: | Data Invariant Mapping                          | 393   |

| Figure 84: | 256 PBGA, 17 mm — Top and Side Views            | 400   |

| Figure 85: | 256 PBGA, 17 mm — Bottom View                   | 401   |

| Figure 86: | 256 PBGA, 27 mm — Top and Side Views            | 402   |

| Figure 87. | 256 PRGA 27 mm — Bottom View                    | 403   |

16

# **List of Tables**

| Table 1:  | QSpan II New Features and Functional Enhancements               | 26 |

|-----------|-----------------------------------------------------------------|----|

| Table 2:  | Reset Options for QBus Slave Modes                              | 35 |

| Table 3:  | Address Fields for QBus Slave Image                             | 38 |

| Table 4:  | Control Fields for QBus Slave Image                             | 38 |

| Table 5:  | Translation of QBus Address to PCI Address                      | 42 |

| Table 6:  | Command Type Encoding for Transfer Type                         | 43 |

| Table 7:  | Translation from QBus Transaction to PCI Transaction Type       | 44 |

| Table 8:  | Little-Endian QBus Slave Channel Cycle Mapping                  | 45 |

| Table 9:  | Big-Endian QBus Slave Channel Cycle Mapping                     | 46 |

| Table 10: | Translation of Cycle Termination from PCI Bus to QBus           | 51 |

| Table 11: | MC68360 Cycle Terminations of QBus Slave Module                 | 52 |

| Table 12: | MPC860 Cycle Terminations of QBus Slave Module                  | 52 |

| Table 13: | M68040 Cycle Terminations of QBus Slave Module                  | 52 |

| Table 14: | QBus Slave Channel Error Responses                              | 53 |

| Table 15: | Reset Options for QBus Master and Slave Modes                   | 57 |

| Table 16: | Address Fields for PCI Target Image                             | 59 |

| Table 17: | Control Fields for PCI Target Image                             | 60 |

| Table 18: | Translation of PCI Bus Address to QBus Address                  | 64 |

| Table 19: | Little-Endian PCI Target Write Cycle Mapping — 32-Bit QBus Port | 67 |

| Table 20: | Big-Endian PCI Target Write Cycle Mapping — 32-Bit QBus Port    | 67 |

| Table 21: | Little-Endian PCI Target Read Cycle Mapping — 32-Bit QBus Port  | 69 |

| Table 22: | Big-Endian PCI Target Read Cycle Mapping — 32-Bit QBus Port     | 69 |

| Table 23: | Little-Endian PCI Target Read Cycle Mapping — 16-Bit QBus Port  | 70 |

| Table 24: | Big-Endian PCI Target Read Cycle Mapping — 16-Bit QBus Port     | 70 |

| Table 25: | Little-Endian PCI Target Read Cycle Mapping — 8-Bit QBus Port   | 71 |

| Table 26: | Big-Endian PCI Target Read Cycle Mapping — 8-Bit QBus Port      | 71 |

| Table 28: | MPC860 Cycle Terminations of QBus Master Module.                | 79 |

| Table 29: | M68040 Cycle Terminations of QBus Master Module                 | 79 |

| Table 27: | MC68360 Cycle Terminations of QBus Master Module                | 79 |

| Table 30: | Translation of Cycle Termination from QBus to PCI Bus           | 82 |

| Table 32: | IDMA Interrupt Source, Enabling, Mapping, Status and Clear bits   | 90  |

|-----------|-------------------------------------------------------------------|-----|

| Table 31: | QSpan II's Response to IDMA Errors                                | 90  |

| Table 34: | 16-Bit Big-Endian IDMA Cycle Mapping                              | 92  |

| Table 35: | 32-Bit Little-Endian IDMA Cycle Mapping                           | 92  |

| Table 36: | 32-Bit Big-Endian IDMA Cycle Mapping                              | 92  |

| Table 33: | 16-Bit Little Endian IDMA Cycle Mapping                           | 92  |

| Table 37: | PCI Memory Cycle Access to bits 15-08 of the PCI_CLASS register   | 106 |

| Table 38: | Big-Endian QBus Access to bits 15-08 of the PCI_CLASS register    | 108 |

| Table 39: | Little-Endian QBus Access to bits 15–08 of the PCI_CLASS register | 108 |

| Table 40: | PCI AD[31:16] lines asserted as a function of DEV_NUM field       | 110 |

| Table 41: | Mapping of Hardware-Initiated Interrupts                          | 115 |

| Table 42: | Interrupt Source, Enabling, Mapping, Status and Clear bits        | 116 |

| Table 43: | Software Interrupt Mapping, Status and Source bits                | 118 |

| Table 44: | Destination of EEPROM Bits Read                                   | 125 |

| Table 45: | Insertion Sequence                                                | 146 |

| Table 46: | Extraction Sequence                                               | 148 |

| Table 47: | Hardware Reset Mechanisms                                         | 153 |

| Table 48: | Reset Options for QBus Master and Slave Modes                     | 156 |

| Table 49: | Test Mode Operation                                               | 157 |

| Table 50: | QBus Signal Names Compared to Motorola Signals                    | 160 |

| Table 51: | MC68360/MPC860 Encoding for the SIZ[1:0] Signal                   | 168 |

| Table 52: | M68040 Encoding for the SIZ[1:0] Signal                           | 172 |

| Table 53: | Non-PCI DC Electrical Characteristics ( $V_{DD} \pm 5\%$ )        | 178 |

| Table 54: | 3.3V PCI I/O Signaling AC/DC Characteristics ( $V_{DD} \pm 5\%$ ) | 179 |

| Table 55: | 5V PCI I/O Signaling AC/DC Electrical Characteristics             | 180 |

| Table 56: | Pin List for QSpan II Signals                                     | 181 |

| Table 57: | PCI Bus Address/Data Pins                                         | 185 |

| Table 58: | QBus Address Pins                                                 | 186 |

| Table 59: | QBus Data Pins                                                    | 187 |

| Table 60: | External Request and Grant Pins                                   | 187 |

| Table 61: | Pin Assignments for Power (V <sub>DD</sub> )                      | 188 |

| Table 62: | Voltage Required to be Applied to VH                              | 188 |

| Table 63: | Pin Assignments for Ground (V <sub>SS</sub> )                     | 189 |

| Table 64: | No-connect Pin Assignments                                        | 189 |

| Table 65: | Pinout of 17x17 mm Package                                        | 190 |

| Table 66: | Pinout of 27x27 mm Package                                        | 191 |

| Table 67: | Register Map                                                      | 195 |

| Table 68: | I2O Memory Map — Lower 4K                                         | 199 |

| Table 69: | PCI Configuration Space ID Register                               | 200 |

| Table 70:  | PCI Configuration Space Control and Status Register    | . 201 |

|------------|--------------------------------------------------------|-------|

| Table 71:  | PCI Configuration Class Register                       | . 204 |

| Table 72:  | PCI Configuration Miscellaneous 0 Register             | . 205 |

| Table 73:  | PCI Configuration Base Address for Memory Register     | . 206 |

| Table 74:  | I20 Base Address Register                              | . 207 |

| Table 75:  | PCI Configuration Base Address for Target 0 Register   | . 208 |

| Table 76:  | PCI Address Lines Compared as a Function of Block Size | . 209 |

| Table 77:  | PCI Configuration Base Address for Target 1 Register   | . 210 |

| Table 78:  | PCI Address Lines Compared as a Function of Block Size | . 211 |

| Table 79:  | PCI Configuration Subsystem ID Register                | . 212 |

| Table 80:  | PCI Configuration Expansion ROM Base Address Register  | . 213 |

| Table 81:  | Writable BA bits as a function of Block Size           | . 214 |

| Table 82:  | PCI Capabilities Pointer Register                      | . 215 |

| Table 83:  | PCI Configuration Miscellaneous 1 Register             | . 216 |

| Table 84:  | PCI Power Management Capabilities Register             | . 217 |

| Table 85:  | PCI Power Management Control and Status Register       | . 218 |

| Table 86:  | CompactPCI Hot Swap Register                           | . 219 |

| Table 87:  | PCI Vital Product Data Register                        | . 220 |

| Table 88:  | PCI VPD Data Register                                  | . 221 |

| Table 89:  | PCI Bus Target Image 0 Control Register                | . 222 |

| Table 90:  | PCI Bus Target Image 0 Address Register                | . 224 |

| Table 91:  | PCI Address Lines Compared as a Function of Block Size | . 225 |

| Table 92:  | PCI Bus Target Image 1 Control Register                | . 226 |

| Table 93:  | PCI Bus Target Image 1 Address Register                | . 228 |

| Table 94:  | PCI Address Lines Compared as a Function of Block Size | . 229 |

| Table 95:  | PCI Bus Expansion ROM Control Register                 | . 230 |

| Table 96:  | PCI Address Lines Compared as a Function of Block Size | . 231 |

| Table 97:  | PCI Bus Error Log Control and Status Register          | . 232 |

| Table 98:  | PCI Bus Address Error Log Register                     | . 234 |

| Table 99:  | PCI Bus Data Error Log Register                        | . 235 |

| Table 100: | I2O Control and Status Register                        | . 236 |

| Table 101: | I2O Inbound Free_List Top Pointer Register             | . 238 |

| Table 102: | I2O Inbound Free_List Bottom Pointer Register          | . 239 |

| Table 103: | I2O Inbound Post_List Top Pointer Register             | . 240 |

| Table 104: | I2O Inbound Post_List Bottom Pointer Register          | . 241 |

| Table 105: | I2O Outbound Free_List Top Pointer Register            | . 242 |

| Table 106: | I2O Outbound Free_List Bottom Pointer Register         | . 243 |

| Table 107: | I2O Outbound Post_List Top Pointer Register            | . 244 |

| Table 108: | I2O Outbound Post, List Bottom Pointer Register        | 245   |

| Table 109: | IDMA Control and Status Register                            | 246 |

|------------|-------------------------------------------------------------|-----|

| Table 110: | IDMA/DMA PCI Address Register                               | 249 |

|            | IDMA/DMA Transfer Count Register                            |     |

| Table 112: | DMA QBus Address Register                                   | 251 |

| Table 113: | DMA Control and Status Register                             | 252 |

| Table 114: | DMA Command Packet Pointer Register                         | 255 |

| Table 115: | Configuration Address Register                              | 256 |

| Table 116: | PCI AD[31:16] lines asserted as a function of DEV_NUM field | 257 |

| Table 117: | Configuration Data Register                                 | 258 |

| Table 118: | IACK Cycle Generator Register                               | 259 |

| Table 119: | Interrupt Status Register                                   | 260 |

| Table 120: | Interrupt Control Register                                  | 263 |

| Table 121: | Interrupt Direction Register                                | 266 |

| Table 122: | Interrupt Control Register 2                                | 269 |

| Table 123: | Mailbox 0 Register                                          | 270 |

| Table 124: | Mailbox 1 Register                                          | 271 |

| Table 125: | Mailbox 2 Register                                          | 272 |

| Table 126: | Mailbox 3 Register                                          | 273 |

| Table 127: | Miscellaneous Control and Status Register                   | 274 |

| Table 128: | Master/Slave Mode — MSTSLV field                            | 276 |

| Table 129: | EEPROM Control and Status Register                          | 277 |

| Table 130: | Miscellaneous Control 2 Register                            | 278 |

| Table 131: | PCI Bus Arbiter Control Register                            | 281 |

| Table 132: | Parked PCI Master                                           | 282 |

| Table 133: | QBus Slave Image 0 Control Register                         | 283 |

| Table 134: | QSpan II Response to a Single-Read Cycle Access             | 284 |

| Table 135: | QSpan II Response to a Burst-Read Cycle Access              | 284 |

| Table 136: | QSpan II Response to a Single-Write Cycle Access            | 284 |

| Table 137: | QSpan II Response to a Burst-Write Cycle Access             | 284 |

| Table 138: | QBus Slave Image 0 Address Translation Register             | 285 |

| Table 139: | Address Lines Translated as a Function of Block Size        | 286 |

| Table 140: | QBus Slave Image 1 Control Register                         | 287 |

| Table 141: | QSpan II Response to a Single-Read Cycle Access             | 288 |

| Table 142: | QSpan II Response to a Burst-Read Cycle Access              | 288 |

| Table 143: | QSpan II Response to a Single-Write Cycle Access            | 288 |

| Table 144: | QSpan II Response to a Burst-Write Cycle Access             | 288 |

| Table 145: | QBus Slave Image 1 Address Translation Register             | 289 |

| Table 146: | QBus Address Lines Compared as a function of Block Size     | 290 |

| Table 147: | QBus Error Log Control and Status Register                  | 291 |

| Table 148: | QBus Address Error Log                                     | 292 |

|------------|------------------------------------------------------------|-----|

| Table 149: | QBus Data Error Log                                        | 293 |

| Table 150: | I20 Outbound Post_List Interrupt Status Register           | 294 |

| Table 151: | I20 Outbound Post_List Interrupt Mask Register             | 295 |

| Table 152: | I2O Inbound Queue Register                                 | 296 |

| Table 153: | I2O Outbound Queue Register                                | 297 |

| Table 154: | Timing Parameters for MC68360 Interface                    | 301 |

| Table 155: | Timing Parameters for MPC860 Interface                     | 306 |

| Table 156: | Timing Parameters for M68040 Interface                     | 310 |

| Table 157: | Timing Parameters for Interrupts and Resets                | 313 |

| Table 158: | Timing Parameters for Reset Options                        | 313 |

| Table 159: | Direction of QBus Signals During MC68360 IDMA Cycles       | 322 |

| Table 160: | Direction of QBus Signals During MPC860 IDMA Cycles        | 341 |

| Table 161: | Summary of the QSpan II's Miscellaneous Control Register   | 378 |

| Table 162: | Summary of the QSpan II's Miscellaneous Control Register 2 | 379 |

| Table 163: | PCI Arbiter Control Register Summary                       | 380 |

| Table 164: | QBus Slave Channel Programming Summary                     | 380 |

| Table 165: | Register Access                                            | 381 |

| Table 166: | PCI Target Image Programming Summary                       | 381 |

| Table 167: | QBus Error Logging Programming Summary                     | 383 |

| Table 168: | PCI Bus Error Logging Programming Summary                  | 383 |

| Table 169: | IDMA/DMA Channel Programming Summary                       | 384 |

| Table 170: | PCI Configuration and IACK Cycle Programming Summary       | 385 |

| Table 171: | PCI Expansion ROM programming                              | 387 |

| Table 172: | Power Dissipation                                          | 395 |

| Table 173: | 3.3 Volt Absolute Maximum Ratings                          | 396 |

| Table 174: | 3.3 Volt Recommended Operating Conditions                  | 396 |

| Table 175: | Junction to Ambient Characteristics                        | 397 |

| Table 176: | 256 PBGA — 17 mm Packaging Features                        | 399 |

| Table 177: | 256 PBGA — 27 mm Packaging Features                        | 401 |

| Table 178: | Ordering Information                                       | 405 |

|            |                                                            |     |

# **Chapter 1:** General Information

This chapter describes the main functions and features of the QSpan II. It also discusses general document elements and technical support information. The following topics are discussed:

- "What is the QSpan II" on page 24

- "Document Conventions" on page 27

- "Motorola MPC860 (PowerQUICC) User's Manual" on page 28

- "Related Documentation" on page 28

# 1.1 What is the QSpan II

The QSpan II<sup>TM</sup> chip is a member of Renesas' family of PCI bus-bridging devices. QSpan II enables board designers to bring PCI-based embedded products to market faster, for less cost, and with high performance.

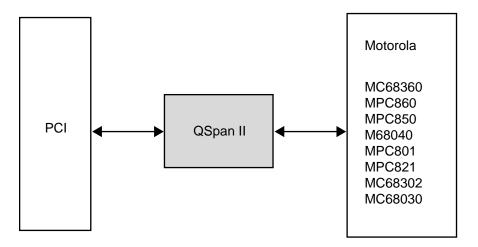

Developed as part of an ongoing strategic relationship with Motorola®, QSpan II is designed to gluelessly bridge the MC68360 (QUICC<sup>TM</sup>), the MPC860 (PowerQUICC<sup>TM</sup>), other MPCxxx devices, and the M68040/M68060 to PCI (see Figure 1). With additional glue logic, QSpan II can also be connected to lower-end communications controllers and processors, such as the MC68302 and MC68030.

Figure 1: QSpan II Bridging PCI and Processor Buses

## 1.1.1 QSpan II Features

QSpan II has the following features:

- A direct-connect interface to the PCI bus for Motorola's MC68360 and MPC860 communications controllers, and the M68040 Host processor.

- QSpan compatible

- Support for up to 50 MHz MPC8xx bus frequencies (industrial temperature range: -40°C to 85°C)

- Available in two, low thermal resistance packages: 17 mm x 17 mm PBGA; and 27 mm x 27 mm PBGA. Both packages have 3.3V power requirements and are 5V tolerant

- 32-bit PCI interface

- Integrated PCI bus arbiter

- Flexible, high performance DMA engine which operates in both Direct and Scatter/ Gather mode

- Five FIFO buffers for multiple transactions in both directions

- Accepts and generates burst reads and writes on the PCI bus

- MPC860 UPM-compliant burst reads and writes as processor bus master

- Separate channel supports MC68360 and MPC860 IDMA

- Flexible address space mapping and translation between the PCI and processor buses

- Programmable endian-byte ordering

- Serial EEPROM interface for Plug and Play compatibility

- Support for PCI and processor bus operation at different clock frequencies

- IEEE 1149.1 JTAG boundary scan support

- CompactPCI Hot Swap Friendly support

- Support for Vital Product Data and Power Management

- I<sub>2</sub>O Messaging Unit

- Mailbox registers for user-designed message passing

# 1.1.2 QSpan II verses QSpan

The following table summarizes the main QSpan II features that were unavailable in the QSpan device.

**Table 1: QSpan II New Features and Functional Enhancements**

| Description                                                                                           | See                                                          |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Features                                                                                              |                                                              |

| DMA Channel                                                                                           | "The DMA Channel"<br>on page 93                              |

| Vital Product Data (PCI Local Bus Specification 2.2 compatible)                                       | "Vital Product Data<br>Support" on page 128                  |

| I <sub>2</sub> O Messaging Unit                                                                       | "I <sub>2</sub> O Messaging Unit"<br>on page 131             |

| Integrated PCI Bus Arbiter                                                                            | "PCI Bus Arbiter" on<br>page 139                             |

| CompactPCI Hot Swap Friendly                                                                          | "CompactPCI Hot<br>Swap Friendly<br>Support" on page 143     |

| PCI Bus Power Management (PCI Bus Power Management Interface Specification 1.1 compatible)            | "PCI Power<br>Management Event<br>Support" on page 151       |

| Functional Enhancements                                                                               |                                                              |

| Support for QBus Data Parity Generation and Detection                                                 | "QBus Data Parity<br>Generation and<br>Detection" on page 35 |

| Performance Improvement for QBus Posted Write Transfers                                               | "Writes" on page 46                                          |

| Support for prefetching through the QBus Slave Channel                                                | "Prefetched Reads"<br>on page 48                             |

| Option to Keep Bus Busy (BB_) asserted on Back-to-Back Transfers on the QBus during PCI target cycles | "Bursting on the QBus" on page 73                            |

| Option to use a different prefetch count in the PCI Target Channel based on the Target Image          | "Prefetched Read<br>Transactions" on<br>page 74              |

| MPC860 UPM-compliant burst reads and writes as processor bus master                                   | "Burst Cycles" on page 96                                    |

# 1.2 **Document Conventions**

## 1.2.1 Signals

Signals are either active high or active low. Active low signals are defined as true (asserted) when they are at a logic low. Similarly, active high signals are defined as true at a logic high. Signals are considered asserted when active and negated when inactive, irrespective of voltage levels. For voltage levels, the use of 0 indicates a low voltage while a 1 indicates a high voltage.

The following signal conventions are used:

- SIGNAL#: Active low signals on the PCI bus interface.

- SIGNAL : Active low signals on the Host processor bus interface.

## 1.2.2 Bit Ordering

This document adopts the convention that the most significant bit is always the largest number (also referred to as *Little-Endian* bit ordering). For example, the PCI address/data bus consists of AD[31:0], where AD[31] is the most significant bit and AD[0] is the least-significant bit of the field.

### 1.2.3 Numeric Conventions

The following numeric conventions are used:

- Hexadecimal numbers are denoted by the prefix  $\partial x$ . For example, 0x004.

- Binary numbers are denoted by the suffix b. For example, 010b.

### **1.2.4** Topographic Conventions

The following typographic conventions are used:

- *Italic* type is used for the following purposes:

- **Book titles**: For example, *PCI Local Bus Specification (Revision 2.2)*.

- **Important terms**: For example, when a device is granted access to the PCI bus it is called the bus *master*.

- **Undefined values**: For example, the device supports two or three ports depending on the setting of the PCI Dx register.

- Courier type is used to represent a file name or text that appears on a computer display. For example, "run loadext. exe by typing it at a command prompt."

#### 1.2.5 **Symbols**

This symbol directs the reader to useful information or suggestions.

This symbol alerts the reader to procedures or operating levels which may result in misuse or damage to the product.

This symbol alerts the reader to an initialization process that must be performed as a minimum to access the required channel or interface.

#### 1.2.6 **Document Status**

Renesas technical documentation is classified as either Advance, Preliminary, or Final. These classifications are briefly explained:

- Advance: The Advance manual contains information that is subject to change. The Advance manual exists until device prototypes are available. This type of manual can be downloaded from our website.

- **Preliminary**: The Preliminary manual contains information about a device that is near production-ready, and is revised on an "as needed" basis. The Preliminary manual exists until the device is released to production. This type of manual can be downloaded from our website.

- **Formal**: The Formal manual contains information about a customer-ready device. This type of manual can be downloaded from our website.

#### 1.3 **Related Documentation**

Before you read this manual, you should be familiar with the following:

- PCI Local Bus Specification (Revision 2.2)

- CompactPCI Hot Swap Specification (Revision 1.0)

- CompactPCI Specification (Revision 2.1)

- PCI Bus Power Management Interface Specification, (Revision 1.1)

- *Intelligent I/O Architecture Specification (Revision 1.5)*

- OSpan II/MPC860 CompactPCI Evaluation Board Manual (6091862 MA001)

- *OSpan II Software Development Kit Manual (6091862 MA002)*

- Motorola M68040 User's Manual

- Motorola MC68360 User's Manual

- Motorola MPC860 (PowerQUICC) User's Manual

28 July 24, 2024

# **Chapter 2:** Functional Overview

This chapter briefly discusses the main functional components (also referred to as channels) of the QSpan II. Please see the following chapters for a detailed explanation of each component:

- Chapter 3: "The QBus Slave Channel" on page 33

- Chapter 4: "The PCI Target Channel" on page 55

- Chapter 5: "The IDMA Channel" on page 83

- Chapter 6: "The DMA Channel" on page 93

- Chapter 7: "The Register Channel" on page 103

- Chapter 8: "The Interrupt Channel" on page 113

- Chapter 9: "The EEPROM Channel" on page 121

- Chapter 10: "I<sub>2</sub>O Messaging Unit" on page 131

- Chapter 11: "PCI Bus Arbiter" on page 139

- Chapter 12: "CompactPCI Hot Swap Friendly Support" on page 143

- Chapter 13: "PCI Power Management Event Support" on page 151

- Chapter 14: "Reset Options" on page 153

- Chapter 15: "Hardware Implementation Issues" on page 157

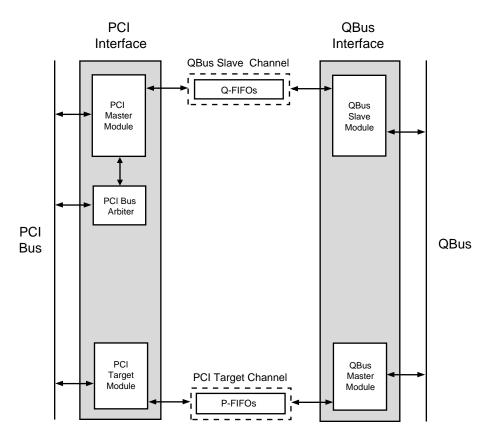

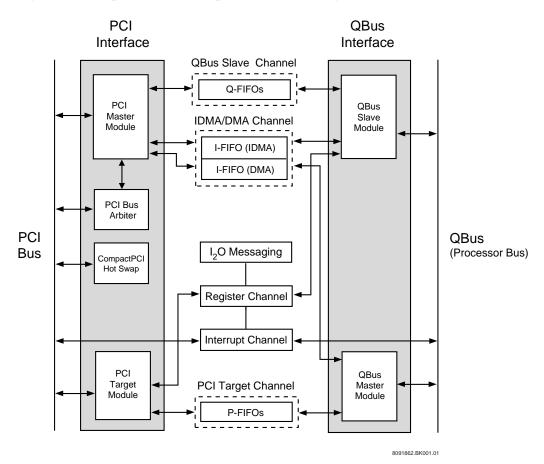

### 2.1 Overview

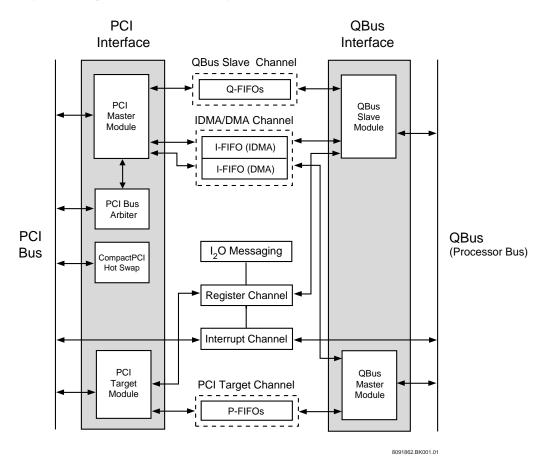

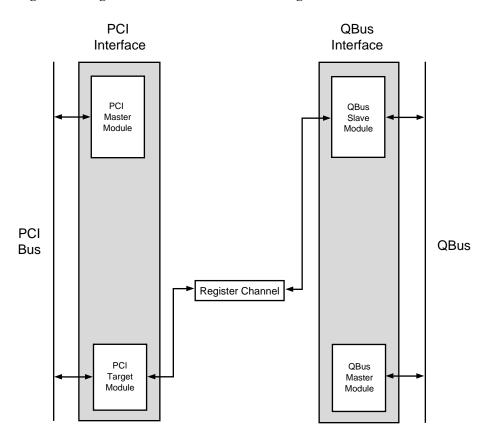

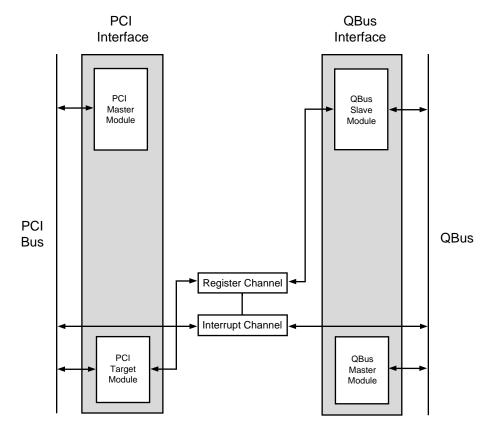

QSpan II has two interfaces: a PCI Bus Interface and a QBus Interface (see Figure 2). The PCI Interface connects the QSpan II to the PCI bus. The QBus Interface connects the QSpan II to the processor bus. Both interfaces support master and slave transactions. The QBus Interface can be directly connected to an MC68360 (QUICC) bus, an MPC860 (PowerQUICC) bus, or an M68040 bus. The QBus Interface can also be connected to other buses with glue logic.

Each interface has two functional modules: a Master Module and a Slave/Target Module. These modules are connected to QSpan II's functional channels.

Figure 2: QSpan II Functional Diagram

# **2.2** The QBus Slave Channel

The QBus Slave Channel transfers data between the QBus and the PCI bus (see Figure 2). It supports posted writes, prefetched reads, and delayed single reads and writes. Write transactions from the QBus to the PCI bus can be posted or delayed. Posted writes are queued in the Qx-FIFO with immediate data acknowledgment on the QBus. QSpan II then completes the write on the PCI bus. For delayed reads, the data is prefetched on the PCI bus and stored in the Qr-FIFO. Subsequent reads retrieve the data from the Qr-FIFO. Delayed transactions — both reads and writes — require data acknowledgment on the PCI bus before data acknowledgment is provided on the QBus.

PCI Memory and I/O spaces are accessible through two Slave images associated with the QBus Slave Channel. Configuration space is accessible through the CON\_DATA register (see Table 117 on page 258). The QBus Slave images are selected using a pair of chip-select signals on the QSpan II (for information, see Chapter 3: "The QBus Slave Channel" on page 33).

# 2.3 The PCI Target Channel

The PCI Target Channel transfers data between the PCI bus and the QBus (see Figure 2). It supports posted writes — to ensure zero-wait state bursting — prefetched reads, and delayed single reads and writes. The 256-byte Px-FIFO supports the queuing of long PCI burst writes.

Delayed reads and writes must complete on the QBus before data acknowledgment occurs on the PCI bus. Reads are executed as delayed transactions, but the QSpan II can be configured to prefetch read data. Prefetched reads are queued in a 256-byte Pr-FIFO.

QSpan II provides two programmable Target images on the PCI bus. These images can be mapped anywhere in Memory or I/O space (for information, see Chapter 4: "The PCI Target Channel" on page 55).

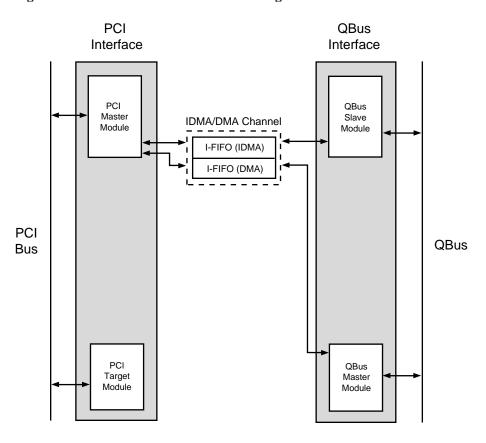

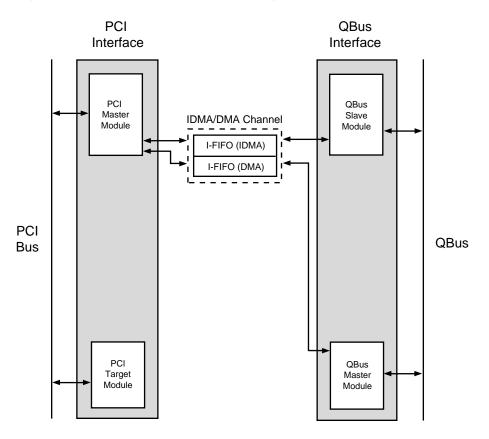

## **2.4** The IDMA Channel

QSpan II can operate as an IDMA peripheral for data transfer between the QBus and the PCI bus (see Figure 2). For transfers going to or from PCI, software can perform bulk data movement using the QSpan II's IDMA Channel. The IDMA Channel supports single- and dual-address cycles, and fast-termination. A separate set of IDMA handshake signals are provided on the QBus. The IDMA Channel can be used by external QBus masters to read data from or write data to a PCI target in one direction at a time. The IDMA Channel contains a 256-byte I-FIFO and a set of IDMA registers (for information, see Chapter 5: "The IDMA Channel" on page 83).

## 2.5 The DMA Channel

QSpan II has a DMA Channel for high performance data transfer between the QBus and the PCI bus (see Figure 2). The DMA controller uses the existing IDMA registers — as well as a few additional registers — and shares the 256-byte I-FIFO with the IDMA Channel. Because of the shared FIFO, the QSpan II cannot use its IDMA and DMA Channels at the same time.

The DMA Channel operates in two modes: Direct Mode and Linked List Mode. In Direct Mode, the DMA registers are programmed directly by an external master. In Linked List Mode, the DMA registers are loaded from PCI bus memory or QBus memory by the QSpan II (for information, see Chapter 6: "The DMA Channel" on page 93).

# **2.6** The Register Channel

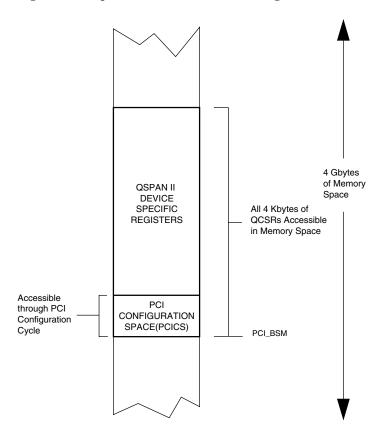

QSpan II provides 4 Kbytes of Control and Status Registers (QCSRs) to program PCI settings, as well as the QSpan II's device specific parameters (see Figure 2). QCSR space is accessible from the PCI bus and the QBus.

An internal arbitration mechanism grants access to the QCSRs. The access mechanisms for the QCSRs, including the arbitration protocol, differ depending on whether the registers are accessed from the PCI bus or the QBus.

PCI Configuration cycles can be generated from the QBus by accessing QSpan II registers. The cycles proceed as delayed transfers (for information, see Chapter 7: "The Register Channel" on page 103).

# 2.7 The Interrupt Channel

QSpan II can generate interrupts based on hardware or software events (see Figure 2). Two bidirectional interrupt pins are provided: one on the PCI Interface; the other on the QBus Interface. Interrupt registers track the status of errors. They also allow users to enable, clear, and map errors. Interrupts can be generated using one of the four available software interrupt sources (for information, see Chapter 8: "The Interrupt Channel" on page 113).

QSpan II also contains four mailbox registers which can be used for message passing (for information, see "Mailbox Registers" on page 112). These mailbox registers can generate an interrupt when data is written to them.

### 2.8 The EEPROM Channel

Some of QSpan II's registers can be programmed by data in an EEPROM at system reset. This allows board designers to set identifiers for their cards on the PCI bus at reset. The identifiers enable the PCI Bus Expansion ROM Control Register (PBROM\_CTL) and set various address and image parameters. If the QSpan II is configured with an EEPROM, the QSpan II can boot-up as a Plug and Play compatible device; local processor initialization is also possible.

QSpan II supports reads from and writes to the EEPROM. The EEPROM device is not included with the QSpan II (for more information, see Chapter 9: "The EEPROM Channel" on page 121).

# **Chapter 3:** The QBus Slave Channel

This chapter describes the QSpan II's QBus Slave Channel. The following topics are discussed:

- "QBus Slave Channel Architecture" on page 34

- "Channel Description" on page 36

- "Address Phase" on page 37

- "Data Phase" on page 44

- "Termination Phase" on page 51

- "PCI Master Retry Counter" on page 54

# 3.1 Overview

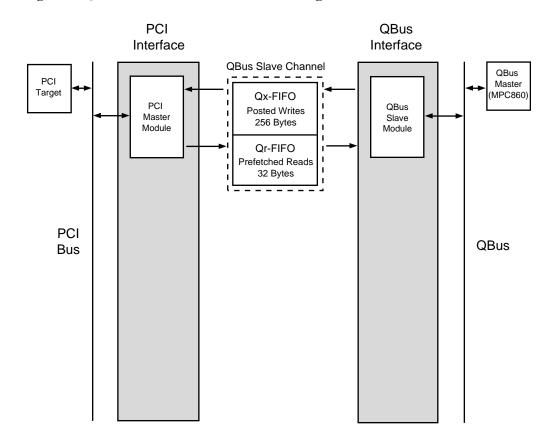

The QBus direct-connects to an MC68360 (QUICC) bus, an MPC860 (PowerQUICC) bus, or an M68040 bus (see Figure 3). The QBus can also be direct-connected to a combination of buses, such as an MC68360 bus and an MPC860 bus. A QBus master uses the QBus Slave Channel or IDMA/DMA Channel to access a PCI target.

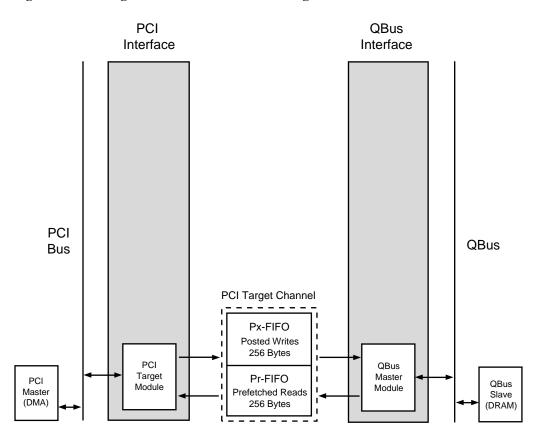

Figure 3: QBus Slave Channel — Functional Diagram

# 3.2 QBus Slave Channel Architecture

Figure 3 shows the QBus Slave Channel in relation to the QBus and the PCI bus. The QBus is shown with an MPC860 processor; the PCI bus is shown with a single PCI device. The arrows represent data flow. The QBus Slave Channel has the following components:

- QBus Slave Module

- Qx-FIFO

- Qr-FIFO

34

PCI Master Module

The QBus Slave Module and PCI Master Module are shared between the QBus Slave Channel and the IDMA/DMA Channel. These components are discussed in the following sections.

### 3.2.1 QBus Slave Module

The QBus Slave Module is a non-multiplexed 32-bit address, 32-bit data interface. The QBus Slave Module accepts MC68360 cycles, and either MPC860 or M68040 cycles. The QBus Slave Module's mode is set by the SIZ[1] signal at reset. This reset option is summarized in Table 2 (for more information, see Chapter 14: "Reset Options" on page 153). The MSTSLV[1:0] field in the Miscellaneous and Control Status register (MISC\_CTL) indicates the slave (and master) mode of the QBus (see Table 127 on page 274). The connections required for interfacing the QSpan II to an MC68360, MPC860, and/or M68040 are described in Appendix C: "Typical Applications" on page 359.

**Table 2: Reset Options for QBus Slave Modes**

| Reset sampling of SIZ[1] | Slave Mode         |

|--------------------------|--------------------|

| 0                        | MC68360 and M68040 |

| 1                        | MC68360 and MPC860 |

### 3.2.1.1 QBus Data Parity Generation and Detection

The QBus Slave Module (QSM) supports the generation and detection of QBus data parity. The use of QBus data parity is optional. Data parity is valid on the same clock cycle as the QBus data. QSpan II supports Odd and Even parity, and is controlled by QBUS\_PAR in the MISC\_CTL2 register (see Table 130 on page 278). Even parity is the default setting, which is the same as the PCI bus. The detection of a QBus data parity error does not affect the operation of the QSpan II. The PCI bus parity generation and detection is independent of the QBus data parity generation and detection.

Four pins are used for the QBus Data Parity signals: DP[3:0]. When parity is set to Even, the number of 1s on the QBus Data lines (D[7:0]) and DP[0] equal an even number. Similarly, for Odd parity, the number of 1s on D[7:0] and DP[0] equal an odd number. The following list shows which data parity signals DP[3:0] are used for which data lines:

- DP[0] contains the parity for data lines D[7:0]

- DP[1] contains the parity for data lines D[15:8]

- DP[2] contains the parity for data lines D[23:16]

- DP[3] contains the parity for data lines D[31:24]

The QBus Slave Module generates the data parity when it completes a slave read cycle. If it detects a parity error during a slave write cycle, it sets the QBus Data Parity Error Status bit (QDPE\_S) in the Interrupt Status (INT\_STAT) register (see Table 119 on page 260). QSpan II can generate an external interrupt (INT# or QINT\_) depending on the setting of QBus Data Parity Error Interrupt Enable (QDPE\_EN) bit and QBus Data Parity Error Interrupt Direction (QDPE\_DIR) bit in INT\_EN and INT\_DIR registers, respectively. Writing a 1 to the QDPE\_S bit negates the interrupt and clears the status bit

When the QBus Slave Module detects a parity error it sets the QDPE\_S bit but continues the transfer as if there were no parity error. For example, if a write is directed to the QSpan II with a data parity error, the QBus Slave Module terminates the cycle normally and passes it onto the QSpan II's PCI interface. QSpan II's PCI master generates the write cycle with the correct parity for the data on the PCI bus.

QSpan II only checks data parity on valid bytes of data. If a single byte transfer is completed on the QBus, only the valid byte on the data bus is checked (for example, D[31:24]).

### 3.2.2 Qx-FIFO and Qr-FIFO

The Qx-FIFO is a 256-byte buffer for posted writes from the QBus to the PCI bus. The Qx-FIFO supports sixty-four 32-bit entries. The Qx-FIFO accepts data from an external QBus master while transferring data to a PCI target (for information, see "Writes" on page 46).

The Qx-FIFO is on the data path for single delayed writes. A delayed write must be completed before the following write can be posted.

The Qr-FIFO is a 32-byte buffer which stores data read from PCI Targets.

### 3.2.3 PCI Master Module

The PCI Master Module is a 32 bit/33MHz PCI 2.2 Specification compliant master interface. PCI signals supported by the QSpan II are outlined in "PCI Bus Signals" on page 172.

QSpan II masters the PCI bus through its PCI Master Module. The PCI Master Module is available to the QBus Slave Channel (access from a remote QBus master) and the IDMA/DMA Channel.

# 3.3 Channel Description

The operation of the QBus Slave Channel is described in the following sections by tracing the path of a transaction from the QBus to the PCI bus. This is completed by dividing a transaction into three phases:

- Address Phase: This section describes transaction decoding and how address information from the QBus is passed to a corresponding address space on the PCI bus.

- Data Phase: This section describes endian mapping and byte-lane translation through the QBus Slave Channel. This section also describes the methods that data is buffered in the QBus Slave Channel depending on the programming of the QBus Slave images.

- Termination Phase: This section discusses how terminations from a PCI target are

communicated to the master on the QBus. It also describes how the QSpan II PCI

Master Module handles terminations (for example, retries or Target-Aborts). We

also describe the terminations the QSpan II issues as a QBus slave device.

# 3.4 Address Phase

# 3.4.1 Transaction Decoding and QBus Slave Images

QSpan II accepts a transaction through its QBus Slave Module when one of its chip selects is asserted along with the Address Strobe (AS\_) or Transaction Start signal (TS\_). The chip selects, CSREG\_ and CSPCI\_, do not need to be detected asserted on the same clock edge as TS\_ for QBus Slave Channel accesses. This allows for wait states to be inserted to perform address decoding. However, the IDMA Channel requires that CSPCI\_ be detected asserted on the same clock edge as TS\_ for dual-address IDMA transfers.

Single address IDMA transfers do not require CSPCI\_ to be asserted.

If CSREG\_ is asserted, then the transaction is decoded as a QSpan II register access (if the address 0x504 is a PCI Configuration cycle, see Chapter 7: "The Register Channel" on page 103). In order to access the PCI bus, the QBus master (or address decoder circuitry) asserts the PCI chip-select pin (CSPCI\_) and the QBus Slave Module claims the cycle for the QBus Slave Channel. One of the two QBus Slave Images is selected during this transaction. The QBus Slave Image is qualified by the Image Select Signal (IMSEL).

The type of PCI cycle generated by the QSpan II depends on the following:

- which OBus Slave Image is selected

- the type of transaction initiated by the external QBus master

The level of IMSEL determines which of the two QBus Slave Images is used. If IMSEL is 0, QBus Slave Image 0 is selected (see Table 133 on page 283 and Table 138 on page 285); if IMSEL is 1, QBus Slave Image 1 is selected (see Table 140 on page 287 and Table 145 on page 289). The levels of BURST\_ and R/W\_ determine whether the QSpan II will generate a single PCI cycle or a burst, a PCI read or a write, respectively. There is some interaction between images and hardware signals, as described in Tables 133 to 145.

A Slave Image is a set of parameters which are encoded in QSpan II registers. A Slave Image controls transfers between the QBus and the PCI bus. Similar Target Images are provided in the PCI Target Channel. Two QBus Slave images of equal capability are provided so that designers can quickly access — on the basis of hardware rather than software — PCI addresses from the QBus, or access addresses in different ways. The two Slave Images are completely independent from one another.

For example, the designer can set-up QBus Slave Image 0 to access a hard-disk using 128 Mbytes of memory in PCI memory space. The designer can simultaneously have QBus Slave Image 1 available to access a different device, with its own memory size. The designer can access the first device with posted writes — Posted Write Enable (PWEN) bit set to 1 — and the other with delayed writes — PWEN set to 0. For a third type of access, it would be necessary to share one of the Slave Images.

The following tables summarize the QBus Slave Image control and address fields.

Table 3: Address Fields for QBus Slave Image

| Field                         | Abbreviation and<br>Register Page                     | Description                                                       |

|-------------------------------|-------------------------------------------------------|-------------------------------------------------------------------|

| Block Size                    | BS (Table 138 on page 285 and Table 145 on page 289)  | Amount of PCI memory accessible from QBus                         |

| PCI Address Space             | PAS (Table 133 on page 283 and Table 140 on page 287) | Mapping to PCI memory space or I/O space                          |

| Translation Address           | TA (Table 138 on page 285 and Table 145 on page 289)  | Address bits that are substituted to generate the PCI bus address |

| Enable Address<br>Translation | EN (Table 138 on page 285 and Table 145 on page 289)  | Enables address translation using TA field                        |

**Table 4: Control Fields for QBus Slave Image**

| Field         | Abbreviation and Register Page                            | Description              |

|---------------|-----------------------------------------------------------|--------------------------|

| Posted Write  | PWEN (Table 133 on page 283 and<br>Table 140 on page 287) | Posted write enable bit  |

| Prefetch Read | PREN (Table 133 on page 283 and<br>Table 140 on page 287) | Prefetch read enable bit |

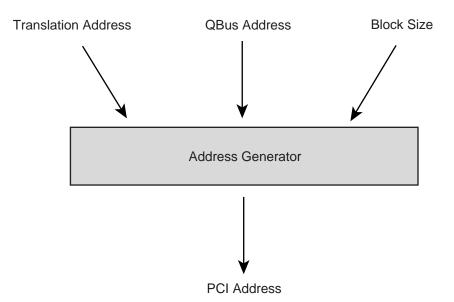

The QBus Slave Channel allows a QBus master to access a range of addresses in PCI Memory or I/O space. The PCI address space bit (PAS) of the selected image determines whether the current transfer is directed towards PCI Memory or I/O space. The range of addresses that can be accessed through a Slave Image is controlled by the block size (BS) field. Up to 2 Gbytes of PCI Memory or I/O space can be accessed from the QBus in one Slave Image if address translation is required. The use of the Block Size, PCI Address Space, Translation Address and Enable Address Translation fields is discussed in "Address Translation" on page 40, and "Address Phase on the PCI Bus" on page 43.

The QBus Slave Image Control registers specify how writes are processed (see Table 133 on page 283 and Table 140 on page 287). If the PWEN bit is 1, the QSpan II will perform posted writes when the specific QBus Slave Image is accessed with a single write. Otherwise writes are handled as single delayed transactions. If the PREN bit is 1, the QSpan II will perform a burst read on the PCI bus when the MPC860 or MC68360 performs a single 32-bit read on the QBus. Otherwise, the QSpan II will handle this as a single delayed read transaction.

QBus Slave Image 0 can also be programmed from an external EEPROM (for information, see "Mapping of EEPROM Bits to QSpan II Registers" on page 124.

38 July 24, 2024

### **3.4.1.1** MPC860 Cycles