# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル (暫定

# NU85E

32 ビット・マイクロプロセッサ・コア ハードウエア編

NU85E NU85EA

**資料番号** A14874JJ3V0UM00 (第 3 版 ) **発行年月** December 2001 NS CP(N)

# [メ モ]

## 目次要約

第1章 概 説 ... 20

**第2章 端子機能** ... 28

第3章 CPU ... 55

**第4章 BCU** ... 79

第5章 BBR ... 123

第6章 STBC ... 140

第7章 DMAC ... 154

第8章 INTC ... 210

第9章 テスト機能 ... 235

第10章 NB85E901 ... 240

付録 A ROM/RAM アクセス・タイミング ... 252

付録 B 総合索引 ... 254

付録 C 改版履歴 ... 260

## CMOSデバイスの一般的注意事項:

## 静電気対策 (MOS全般)

#### 注意 MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、NECが出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

## 未使用入力の処理 (CMOS特有)

## 注意 CMOSデバイスの入力レベルは固定してください。

バイポーラやNMOSのデバイスと異なり、CMOSデバイスの入力に何も接続しない状態で動作させると、ノイズなどに起因する中間レベル入力が生じ、内部で貫通電流が流れて誤動作を引き起こす恐れがあります。プルアップかプルダウンによって入力レベルを固定してください。また、未使用端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してV∞またはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については,その内容を守ってください。

## 初期化以前の状態 (MOS全般)

#### 注意 電源投入時, MOSデバイスの初期状態は不定です。

分子レベルのイオン注入量等で特性が決定するため、初期状態は製造工程の管理外です。電源投入時の端子の出力状態や入出力設定、レジスタ内容などは保証しておりません。ただし、リセット動作やモード設定で定義している項目については、これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

本製品が外国為替および外国貿易管理法の規定による規制貨物等 (または役務) に該当するか否かは , ユーザ (仕様を決定した者) が判定してください。

- 本資料は,この製品の企画段階で作成していますので,予告なしに内容を変更することがあります。 また本資料で扱う製品の製品化を中止することがあります。

- 文書による当社の承諾なしに本資料の転載複製を禁じます。

- 本資料に記載された製品の使用もしくは本資料に記載の情報の使用に際して,当社は当社もしくは第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。上記使用に 起因する第三者所有の権利にかかわる問題が発生した場合,当社はその責を負うものではありませんの でご了承ください。

- 本資料に記載された回路,ソフトウエア,及びこれらに付随する情報は,半導体製品の動作例,応用例を説明するためのものです。従って,これら回路・ソフトウエア・情報をお客様の機器に使用される場合には,お客様の責任において機器設計をしてください。これらの使用に起因するお客様もしくは第三者の損害に対して,当社は一切その責を負いません。

- 当社は品質,信頼性の向上に努めていますが,半導体製品はある確率で故障が発生します。当社半導体製品の故障により結果として,人身事故,火災事故,社会的な損害等を生じさせない冗長設計,延焼対策設計,誤動作防止設計等安全設計に十分ご注意願います。

- 当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定して頂く「特定水準」に分類しております。また,各品質水準は以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認の上ご使用願います。

標準水準:コンピュータ, OA機器, 通信機器, 計測機器, AV機器, 家電, 工作機械, パーソナル機器, 産業用ロボット

特別水準:輸送機器(自動車,列車,船舶等),交通用信号機器,防災/防犯装置,各種安全装置, 生命維持を直接の目的としない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート / データ・ブック等の資料で,特に品質水準の表示がない場合は標準水準製品であることを表します。当社製品を上記の「標準水準」の用途以外でご使用をお考えのお客様は,必ず事前に当社販売窓口までご相談頂きますようお願い致します。

M5 98.8

## 本版で改訂された主な箇所

| 箇 所        | 内 容                                                      |

|------------|----------------------------------------------------------|

| p.33       | 2. 2. 2 (3) VAPREQ 記述を追加                                 |

| p.36       | 2. 2. 2(17)VMLAST, VSLAST 記述を追加                          |

| p.36       | 2. 2. 2(18)VMAHLD, VSAHLD 記述を追加                          |

| p.37       | 2. 2. 2 (20) VBDC 記述を追加                                  |

| p.37       | 2. 2. 2 (21) VBDV 記述を追加                                  |

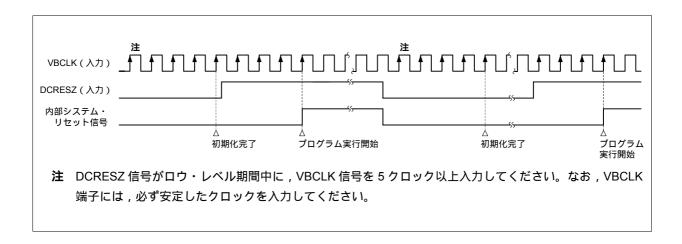

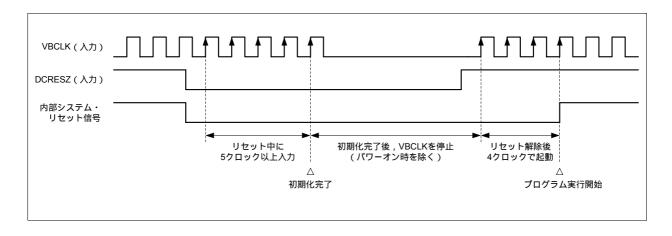

| p.37, 38   | <b>2.2.3(1) DCRESZ</b> 記述を追加,図 2 - 2 を追加                 |

| p.50, 51   | 2.3 未使用端子の処理 注を追加                                        |

| p.54       | <b>表 2 - 10 各動作モードでの端子状態</b> DBO12-DBO5 のリセット時の状態を<br>修正 |

| p.139      | 5.5 <b>注意事項</b> 追加                                       |

| p.143, 144 | <b>6.2.1 パワー・セーブ・コントロール・レジスタ (PSC)</b> 備考 4, 5 を追加       |

| p.147      | 表 6-3 割り込み処理ルーチン内でソフトウエア STOP モードに設定したあ                  |

|            | との動作 備考を追加                                               |

| p.150      | 6.6(1)(b)ソフトウエア STOP モード解除時 <4>と備考を追加                    |

| p.152      | 6.6(2)(b)ハードウエア STOP モード解除時 備考を追加                        |

| p.162      | 図 7 - 6 DMA アドレシング・コントロール・レジスタ 0-3(DADC0-DADC3)          |

|            | 注意を追加                                                    |

| p.164      | 図 7 - 7 DMA チャネル・コントロール・レジスタ 0-3(DCHC0-DCHC3)            |

|            | 注意,記述を追加                                                 |

| p.177      | 7. 8. 5 DMARQn 信号によるシングル転送時の 1 回転送 記述を追加                 |

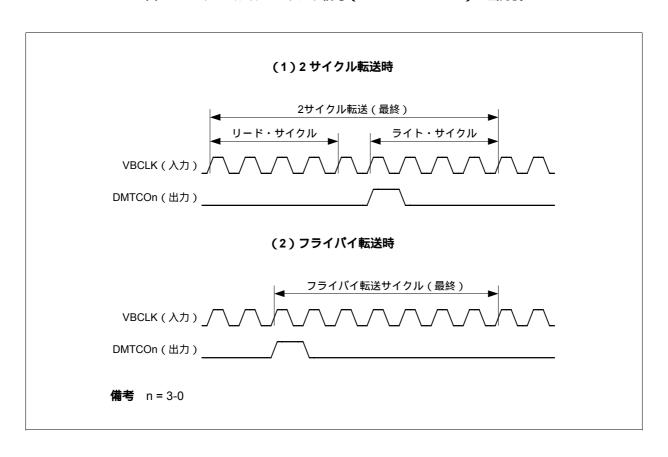

| p.178      | <b>図 7 - 24 2 サイクル転送例</b> 追加                             |

| p.179      | <b>7.9.2 フライバイ転送</b> 記述を追加                               |

| p.179      | 図 7 - 25 フライバイ転送例 (メモリ I/O) 追加                           |

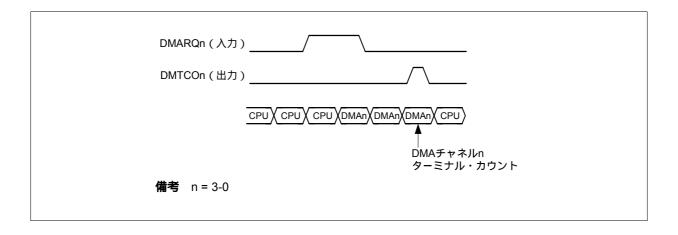

| p.181      | <b>図7-27 ターミナル・カウント信号 (DMTCO3-DMTCO0) の出力例</b> 追加        |

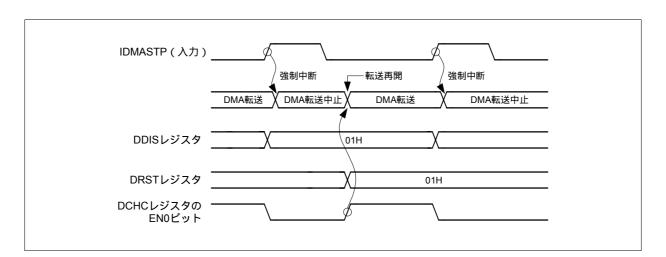

| p.183      | <b>図 7 - 29 DMA 転送の強制終了例</b> 備考を修正                       |

| p.208      | 7. 15 (3) DMA <b>転送に関する各種時間</b> 記述を修正,追加                 |

| p.209      | 7. 15 (4) DMA 転送中の CPU アクセス 記述を追加                        |

| p.209      | 7. 15 (6) DMARQn 信号の保持 , (7) VMLOCK 信号 追加                |

| p.214      | 8. 2 ノンマスカブル割り込み(NMI) 注意 1 を修正,注意 2 を追加                  |

| p.237      | 図 9 - 1 周辺マクロ接続例 修正                                      |

| p.238      | 9.4(2)テスト・モード用端子 NPB 周辺が接続されている場合を削除,修正                  |

| p.260, 261 | 付録 C 改版履歴 追加                                             |

本文欄外の 印は,本版で改訂された主な箇所を示しています。

巻末にアンケート・コーナを設けております。このドキュメントに対するご意見を お気軽にお寄せください。

## はじめに

- 対象者 このマニュアルは CBIC の CPU コアである NU85E, NU85EA のハードウエア機能を理解し,それを 用いた応用システムを設計するユーザを対象とします。

- **的** このマニュアルは,次の構成に示す NU85E, NU85EA の持つハードウエア機能をユーザに理解していただくことを目的としています。

- 構 成 このマニュアルは, NU85E, NU85EAのハードウエア機能について記述しています。アーキテクチャ, 命令機能などの詳細については「V850E1 ユーザーズ・マニュアル アーキテクチャ編」を参照してください。

各マニュアルは,大きく分けて次の内容で構成されています。

NU85E ユーザーズ・マニュアル ハードウエア編 (このマニュアル)

- 概 説

- CPU 機能

- 周辺 I/O 機能

- テスト機能

V850E1 ユーザーズ・マニュアル アーキテクチャ編

- レジスタ・セット

- 命令形式と命令セット

- 割り込みと例外

- パイプラインの動作

- **読み方** このマニュアルの読者には、電気、論理回路、マイクロコンピュータに関する一般知識を必要とします。

- 一通り NU85E, NU85EA のハードウエア機能を理解しようとするとき →目次に従ってお読みください。

機能名などが分かっていて、その詳細を確認するとき

→付録 B 総合索引を参照してください。

命令機能の詳細を知りたいとき

→別冊の V850E1 ユーザーズ・マニュアル アーキテクチャ編 (U14559J) を参照してください。

なお,このマニュアルでは NU85E を代表として説明しています。NU85EA を使用する場合は,「NU85E」を「NU85EA」に読み替えてお使いください。

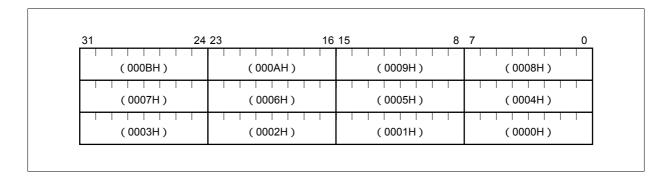

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記: xxxZ(端子,信号名称のあとにZ)

注:本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2 進数 ... xxxx または xxxxB

10 進数 ... xxxx 16 進数 ... xxxxH

2のべき数を示す接頭語(アドレス空間,メモリ容量):

K(キロ) ...  $2^{10} = 1024$ M(メガ) ...  $2^{20} = 1024^2$ G(ギガ) ...  $2^{30} = 1024^3$

データ・タイプ : ワード ... 32 ビット

ハーフワード ... 16 ビット

バイト ... 8 ビット

関連資料 関連資料は暫定版の場合がありますが、この資料では「暫定」の表示をしておりません。あらかじめ ご了承ください。

● V850E1 ユーザーズ・マニュアル アーキテクチャ編 (U14559J)

• メモリ・コントローラ ユーザーズ・マニュアル NU85E, NU85ET 編 (A15019J)

• 命令キャッシュ, データ・キャッシュ ユーザーズ・マニュアル NU85E, NU85ET 編

(A15241J)

● CB-10 ファミリ VX タイプ 設計マニュアル NU85E, NU85ET 編 (A15401J)

● CB-10 ファミリ VX タイプ コア・ライブラリ 設計マニュアル CPU コア , ペリフェラル編

(A15133J)

なお , 上記関連資料は予告なしに内容を変更することがあります。設計などには必ず最新の資料をご使用ください。

## 目 次

## 第1章 概 説 ... 20

- 1.1 概 要 ... 20

- 1.2 応用システム例 ... 21

- 1.3 特 徵 ... 22

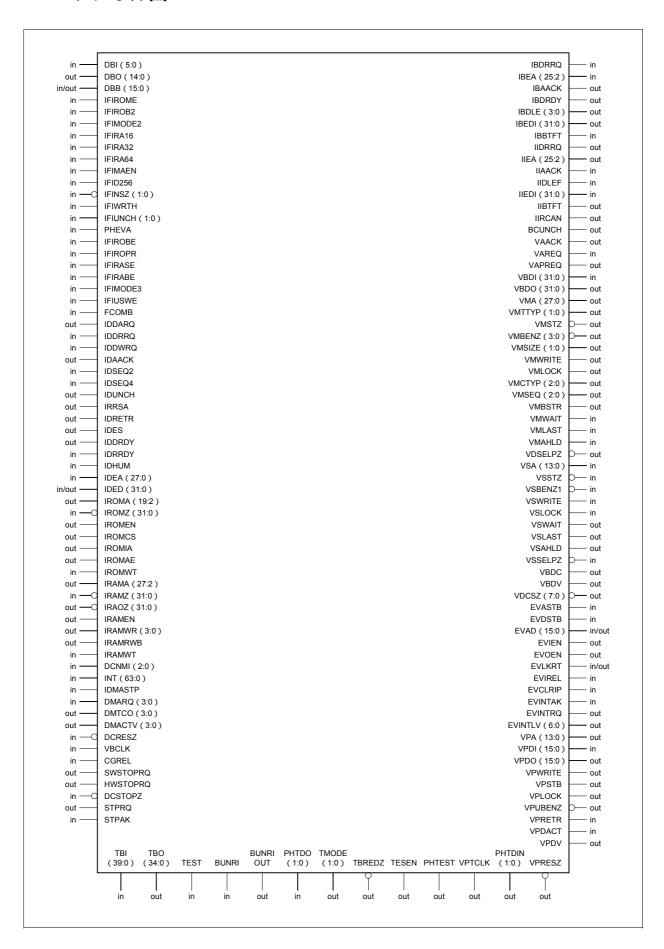

- 1.4 シンボル図 ... 24

- 1.5 機能プロック構成 ... 25

- 1.5.1 内部ブロック図 ... 25

- 1.5.2 内部ユニット ... 26

- 1.6 NU85E と NB85E の機能上の主な違い ... 27

## **第2章 端子機能** ... 28

- 2.1 端子機能一覧 ... 28

- 2.2 端子機能の説明 ... 32

- 2. 2. 1 NPB 用端子 ... 32

- 2. 2. 2 VSB 用端子 ... 33

- 2.2.3 システム制御用端子 ... 37

- 2.2.4 DMAC 用端子 ... 39

- 2.2.5 INTC 用端子 ... 40

- 2.2.6 VFB用端子 ... 40

- 2.2.7 VDB 用端子 ... 40

- 2.2.8 命令キャッシュ用端子 ... 41

- 2.2.9 データ・キャッシュ用端子 ... 43

- 2. 2. 10 RCU 用端子 ... 44

- 2.2.11 周辺エバチップ・モード用端子 ... 45

- 2.2.12 動作モード設定用端子 ... 46

- 2.2.13 テスト・モード用端子 ... 48

- 2.3 未使用端子の処理 ... 50

- 2.4 端子状態 ... 52

## 第3章 CPU ... 55

- 3.1 特 徵 ... 55

- 3.2 レジスタ ... 56

- 3.2.1 プログラム・レジスタ ... 57

- 3.2.2 システム・レジスタ ... 59

- 3.3 アドレス空間 ... 62

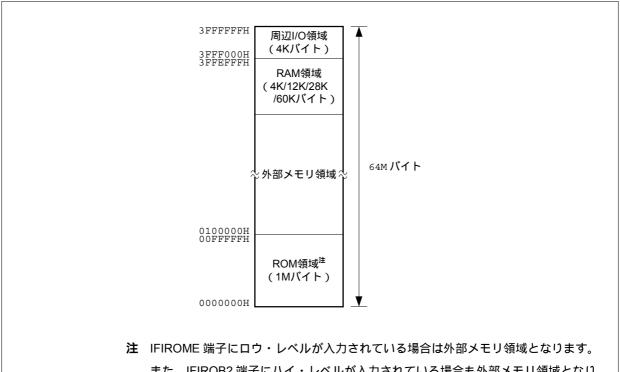

- 3.3.1 プログラム領域 ... 63

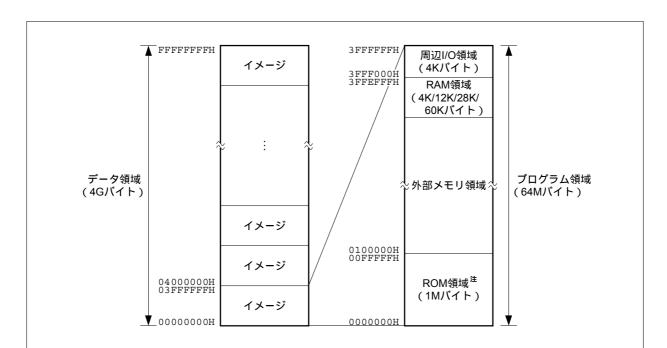

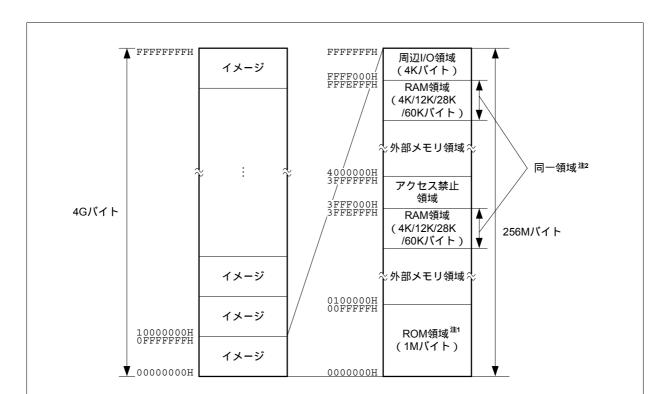

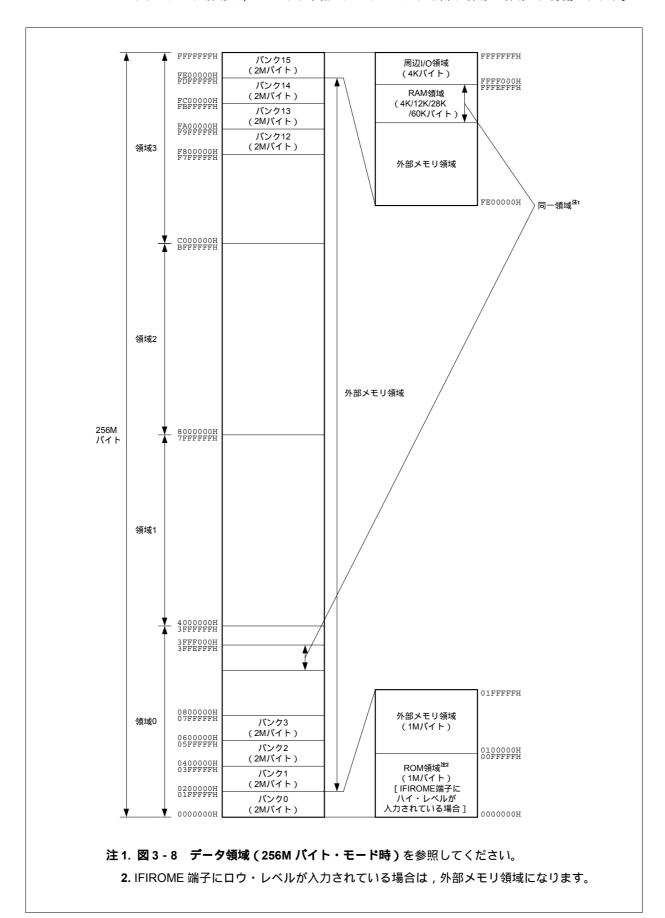

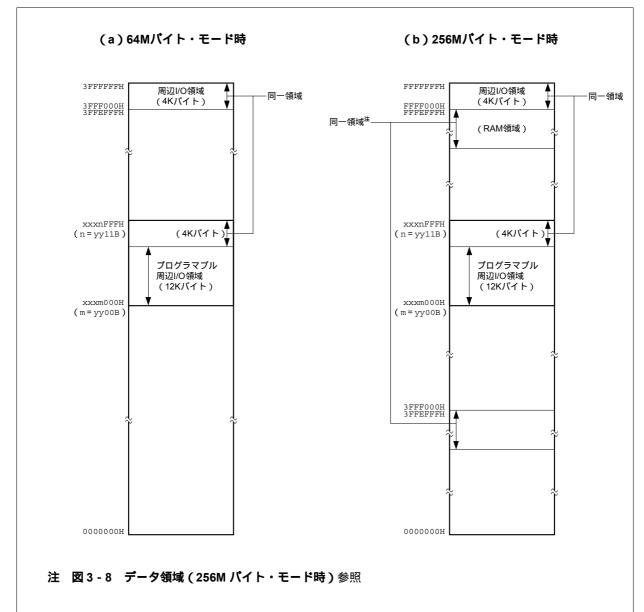

- 3.3.2 データ領域 ... 64

- 3.4 領 域 ... 66

- 3.4.1 ROM 領域 ... 66

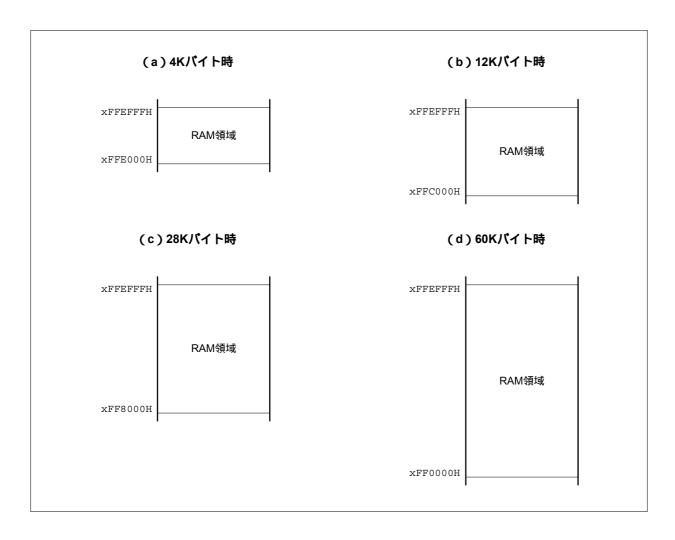

- 3.4.2 RAM 領域 ... 68

- 3.4.3 周辺 I/O 領域 ... 70

- 3.4.4 外部メモリ領域 ... 71

- 3.5 周辺 I/O レジスタ ... 71

- 3.5.1 NU85E 制御用レジスタ ... 72

- 3.5.2 メモリ・コントローラ (MEMC)制御用レジスタ ... 76

- 3.5.3 命令キャッシュ制御用レジスタ ... 77

- 3.5.4 データ・キャッシュ制御用レジスタ ... 77

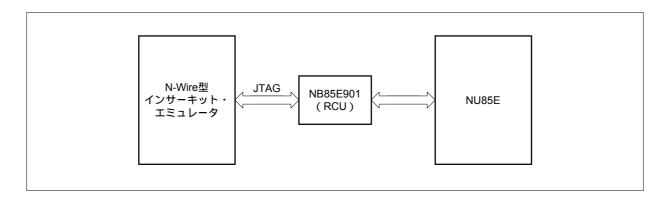

- 3.6 RCU インタフェース ... 78

- 3.6.1 概 要 ... 78

- 3.6.2 オンチップ・ディバグ ... 78

## **第4章 BCU** ... 79

- 4.1 特 徵 ... 79

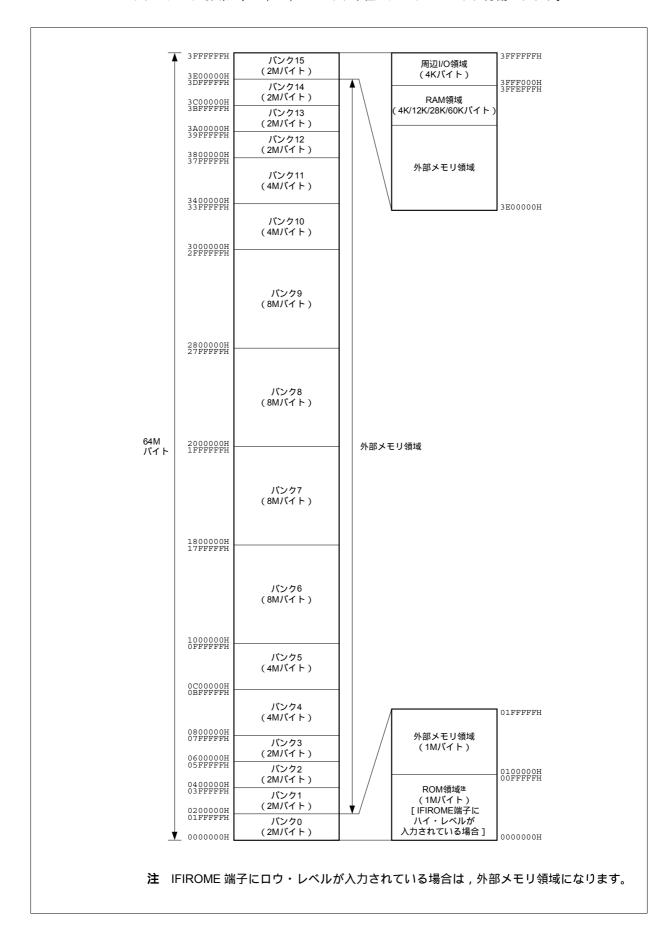

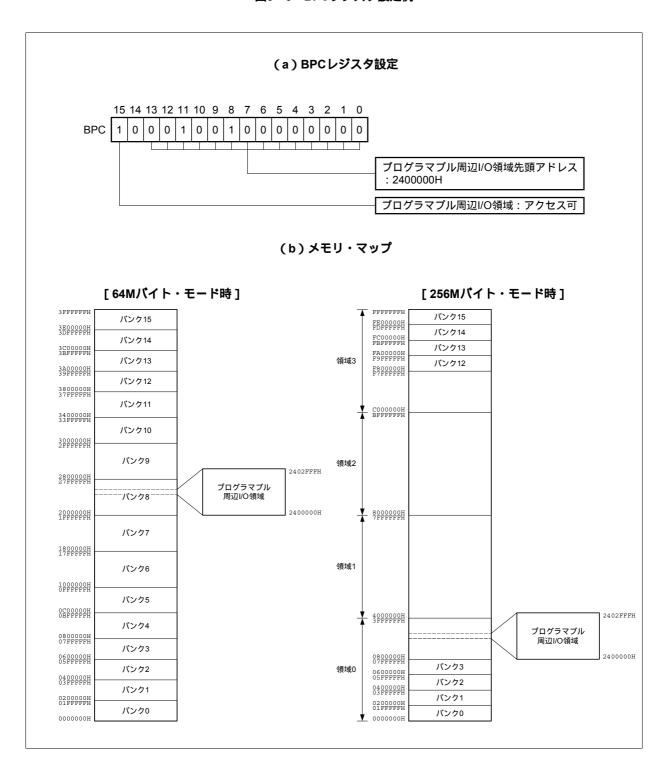

- **4.2 メモリ・バンク** ... 79

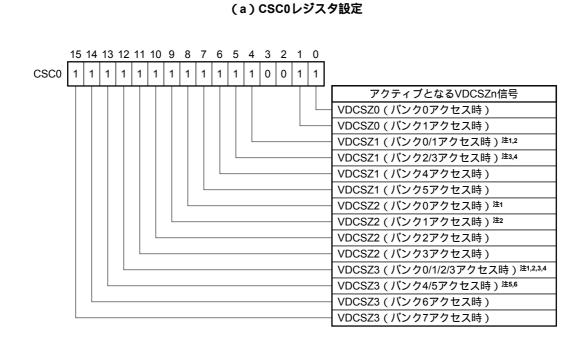

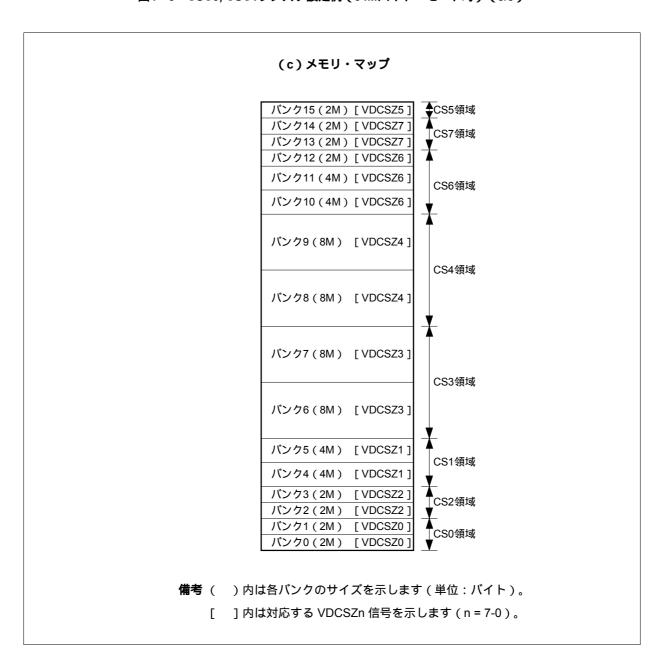

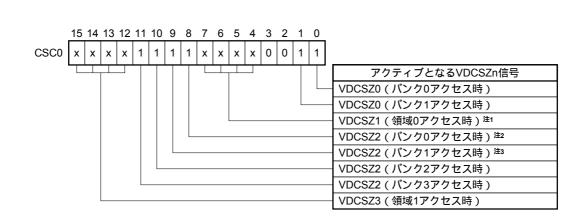

- 4.3 プログラマブル・チップ・セレクト機能 ... 82

- 4.4 プログラマブル周辺 I/O 領域選択機能 ... 88

- 4.5 バス・サイズ設定機能 ... 91

- 4.6 エンディアン設定機能 ... 92

- 4.6.1 エンディアン・コンフィギュレーション・レジスタ (BEC) ... 92

- 4.6.2 NEC 製開発ツールにおけるビッグ・エンディアン形式の使用制限 ... 93

- 4.7 キャッシュ・コンフィギュレーション ... 95

- **4.8 BCU 関連レジスタ設定例** ... 96

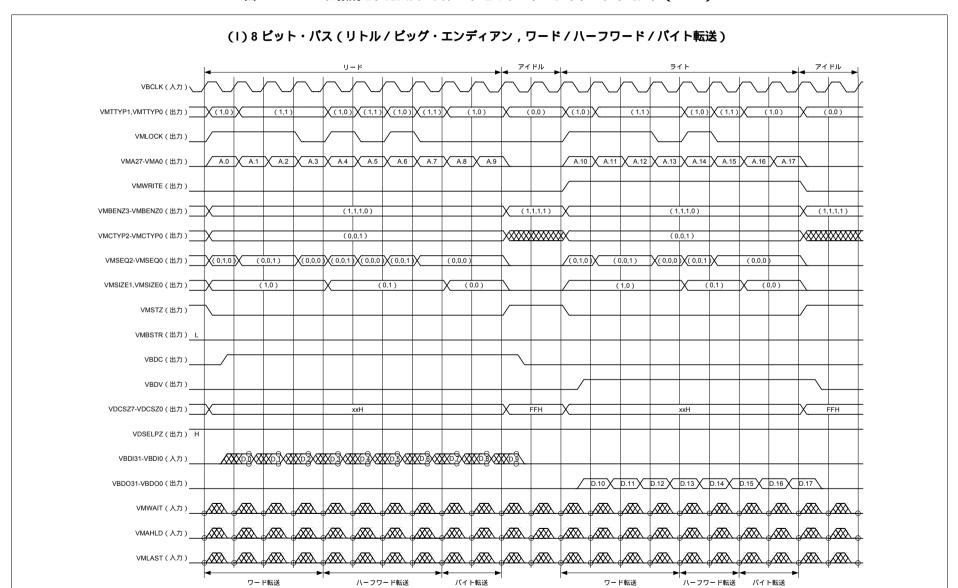

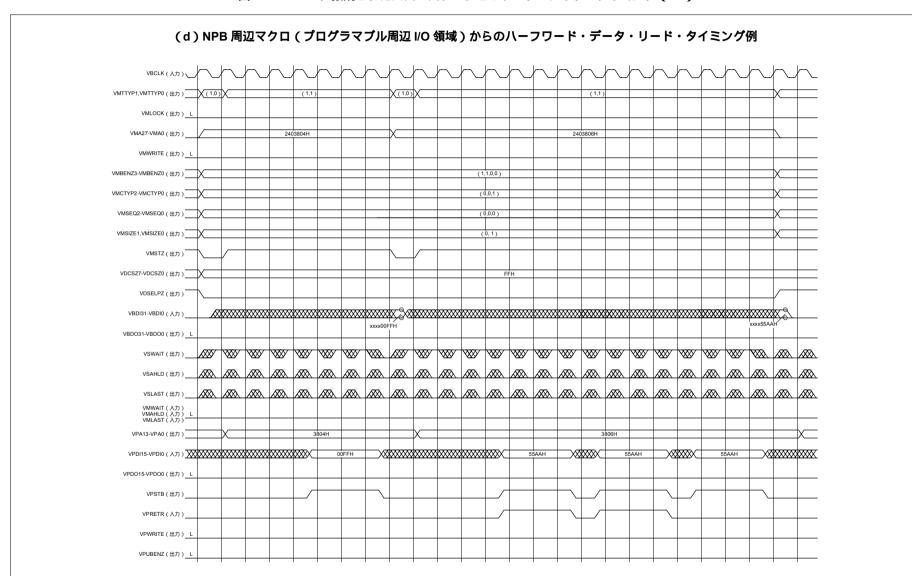

- 4.9 VSB によるデータ転送 ... 99

- 4.9.1 データ転送例 ... 99

- 4.9.2 バス・マスタが出力する制御信号 ... 100

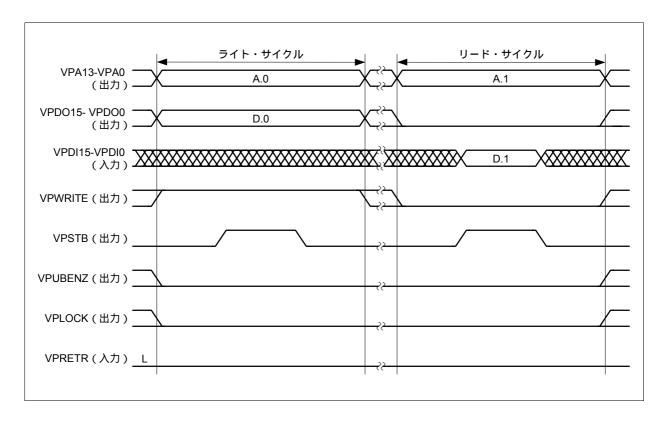

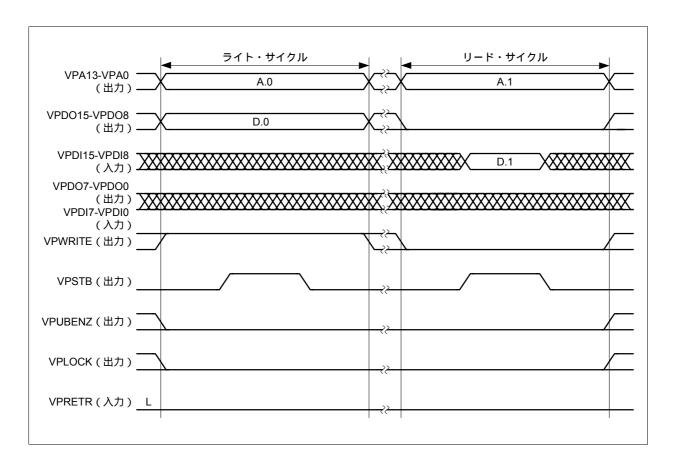

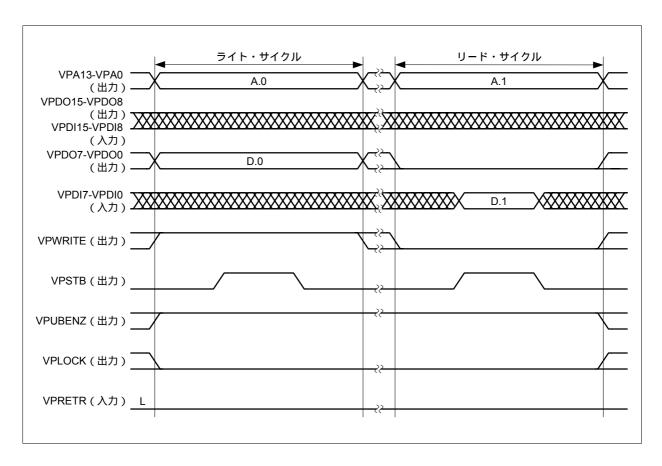

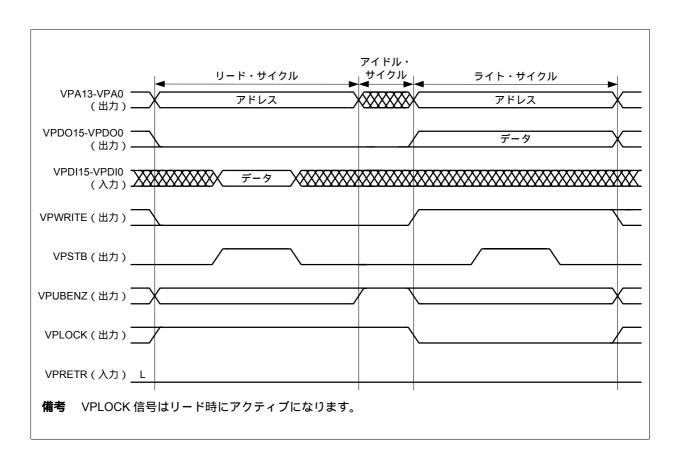

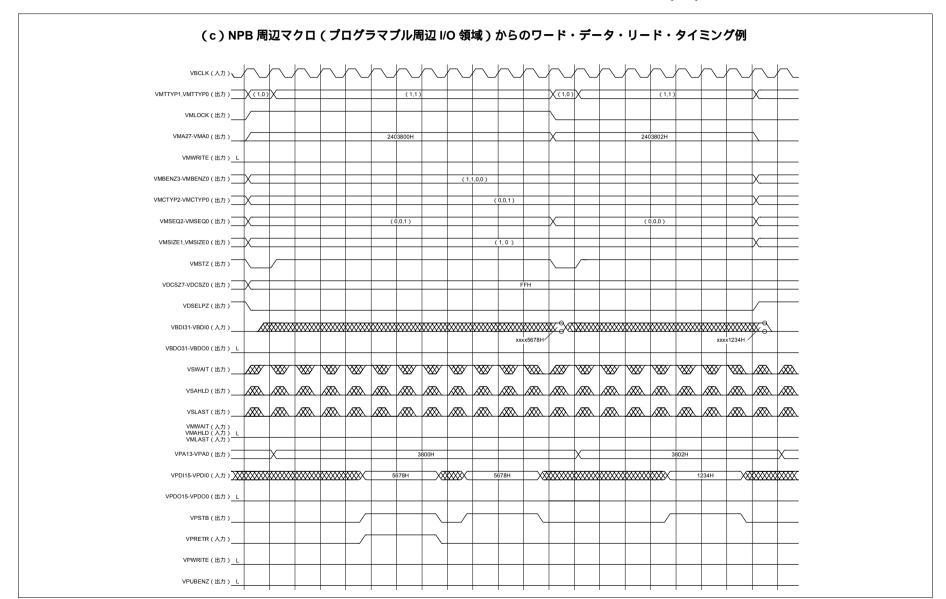

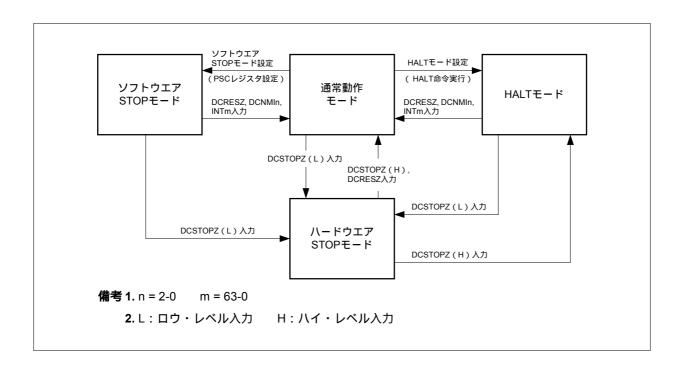

- 4.9.3 リード/ライト・タイミング ... 103

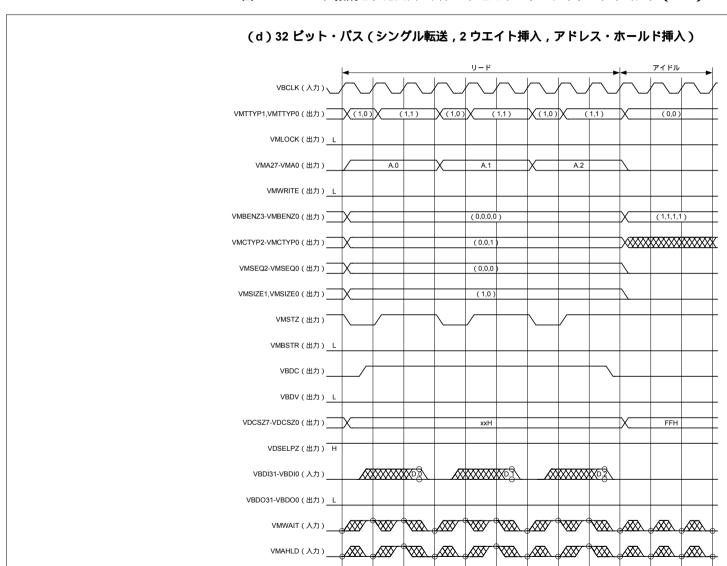

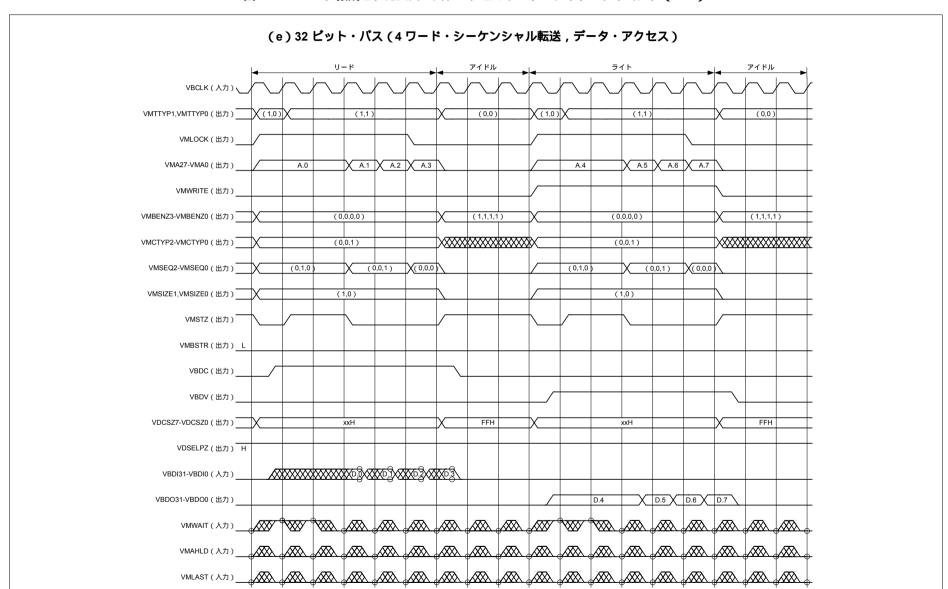

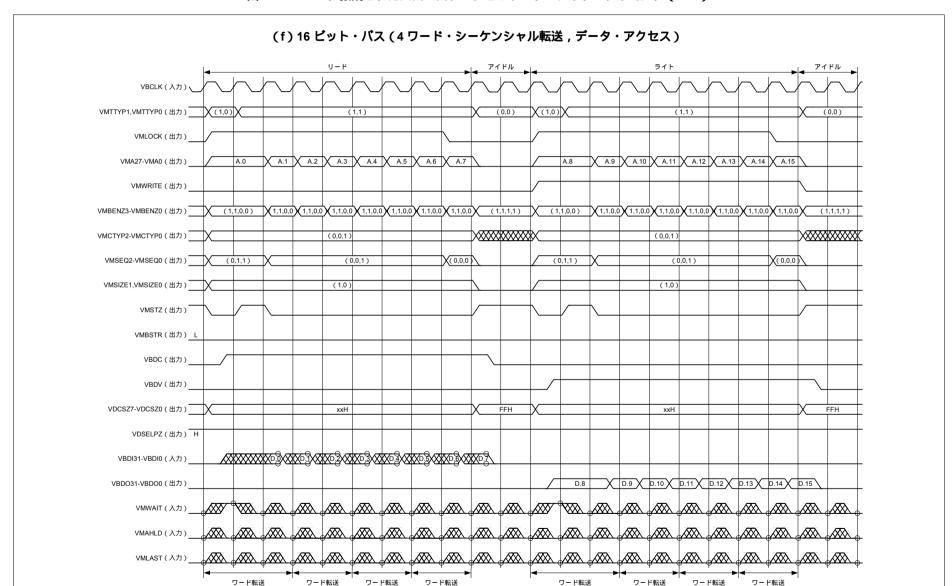

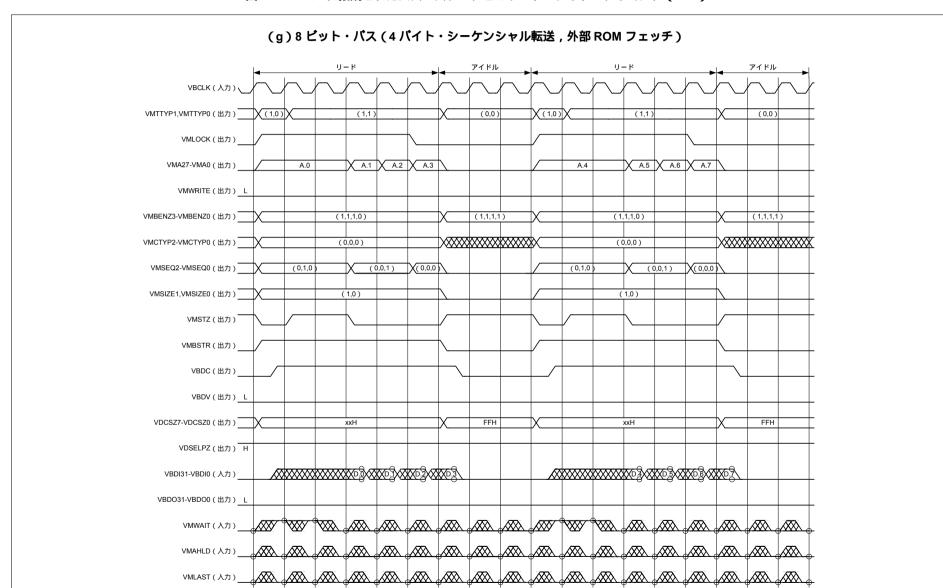

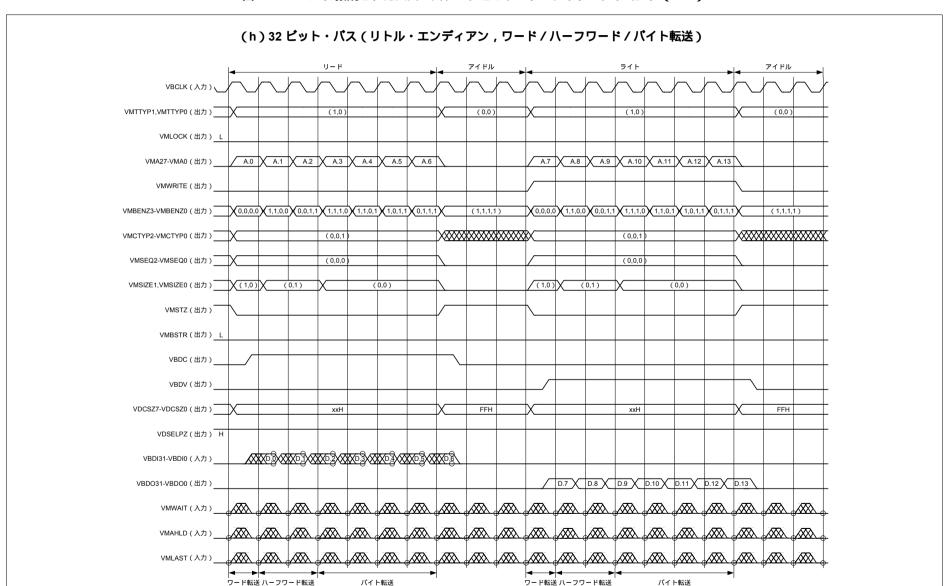

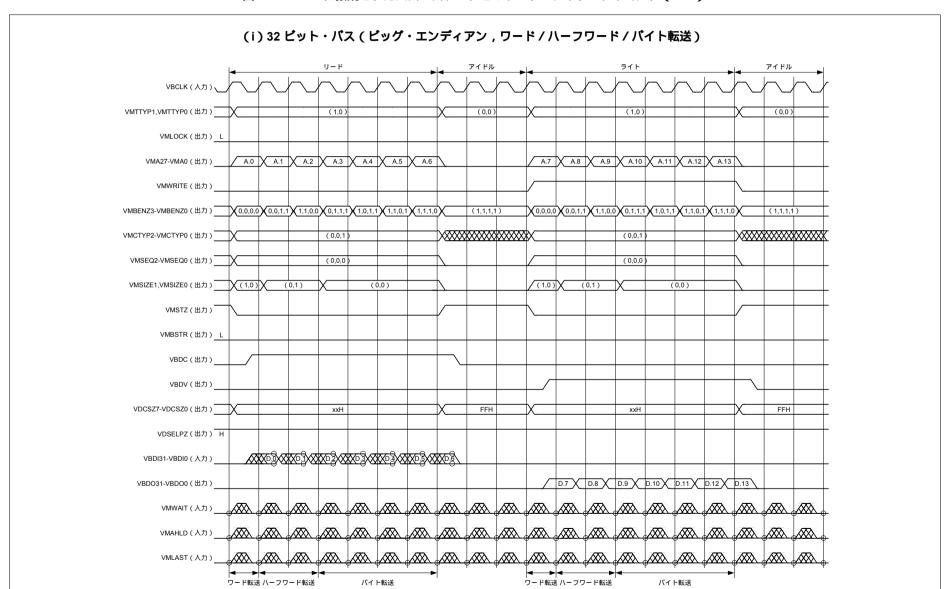

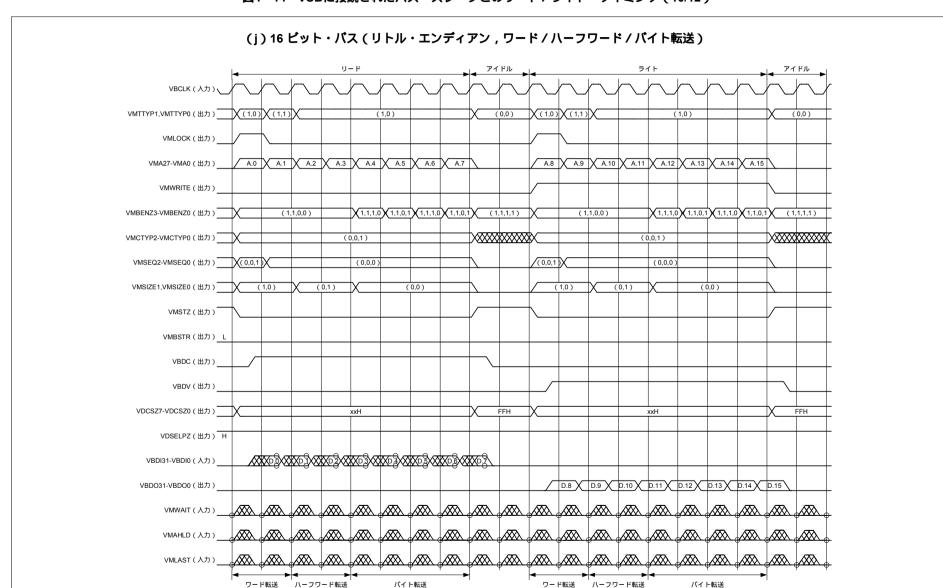

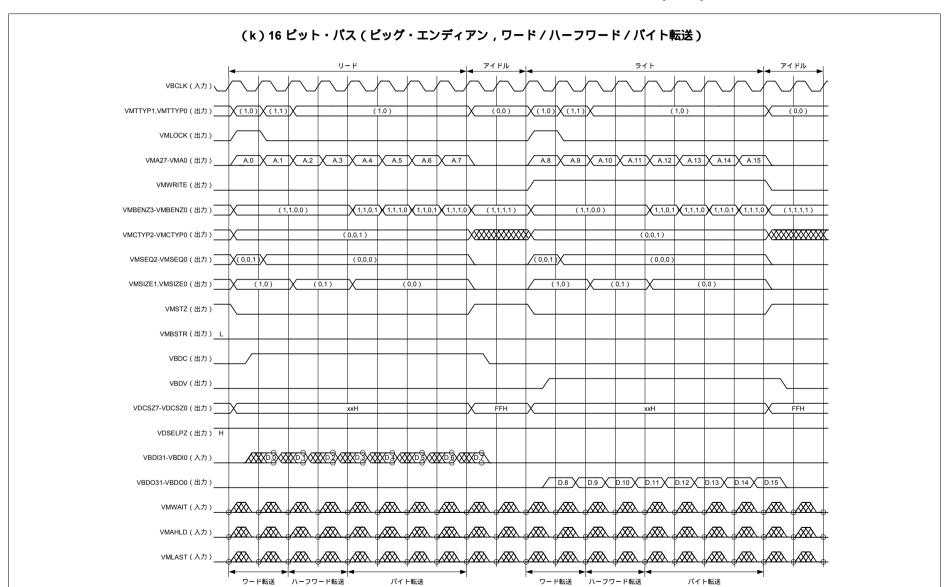

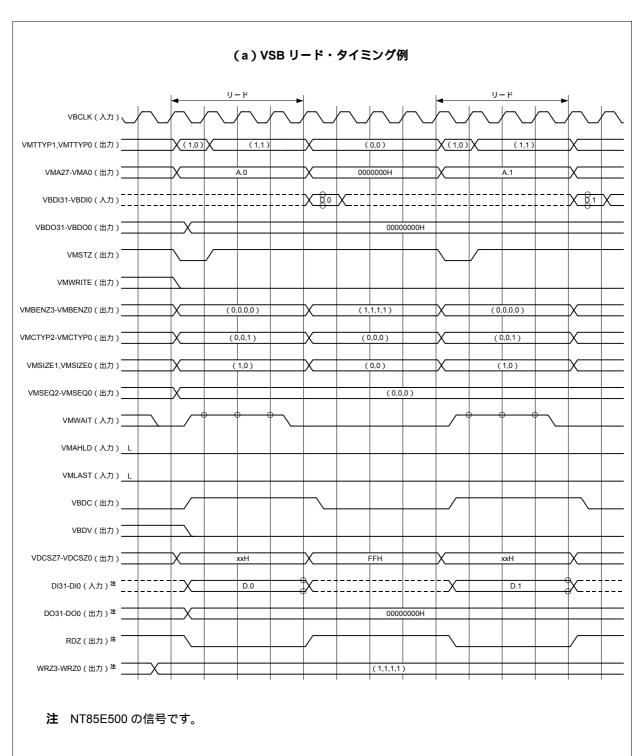

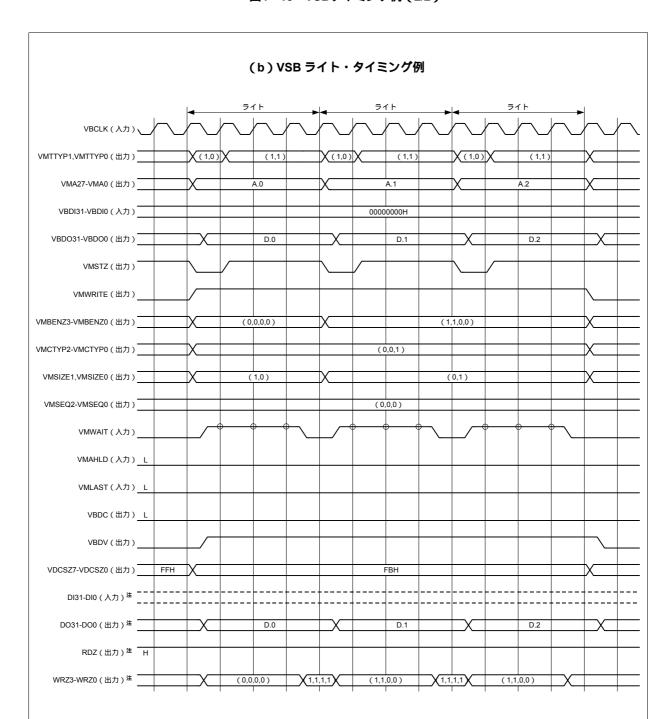

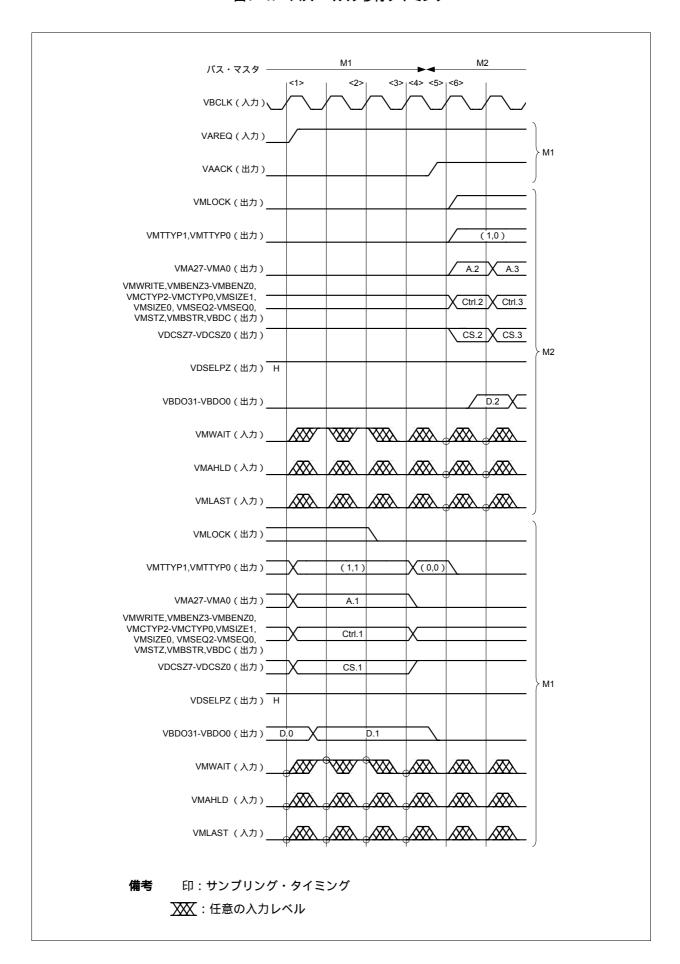

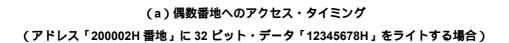

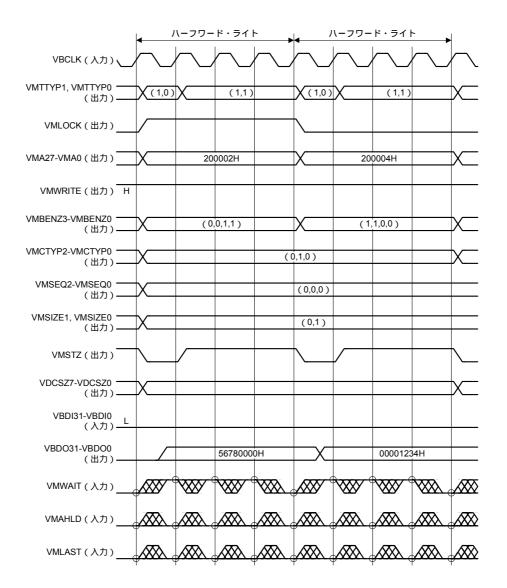

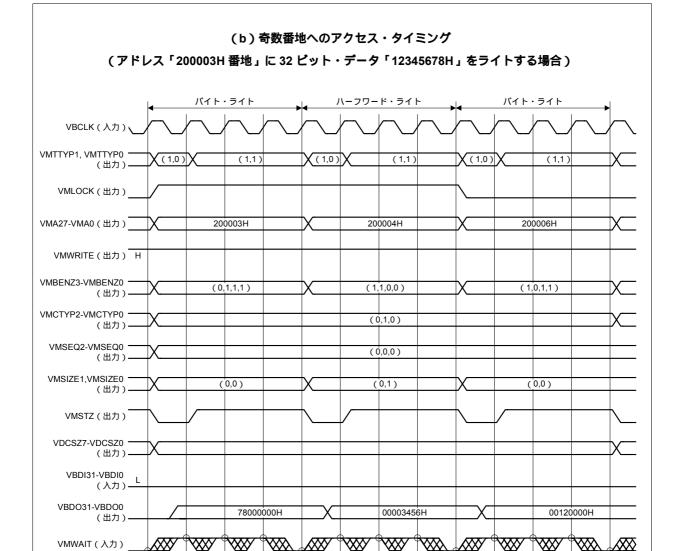

- 4.9.4 VSB リード/ライト・タイミング例 ... 116

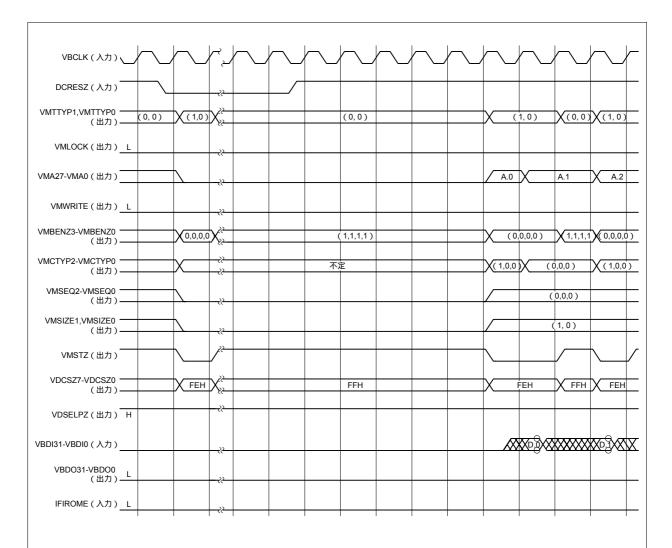

- 4.9.5 リセット・タイミング ... 118

- 4.9.6 バス・マスタ移行タイミング ... 119

- 4.9.7 ミス・アライン・アクセス・タイミング ... 121

## **第5章 BBR** ... 123

- 5.1 プログラマブル周辺 I/O 領域 ... 125

- 5.2 ウエイト挿入機能 ... 128

- 5.3 リトライ機能 ... 130

- 5.4 NPB リード/ライト・タイミング ... 130

- 5.5 注意事項 ... 139

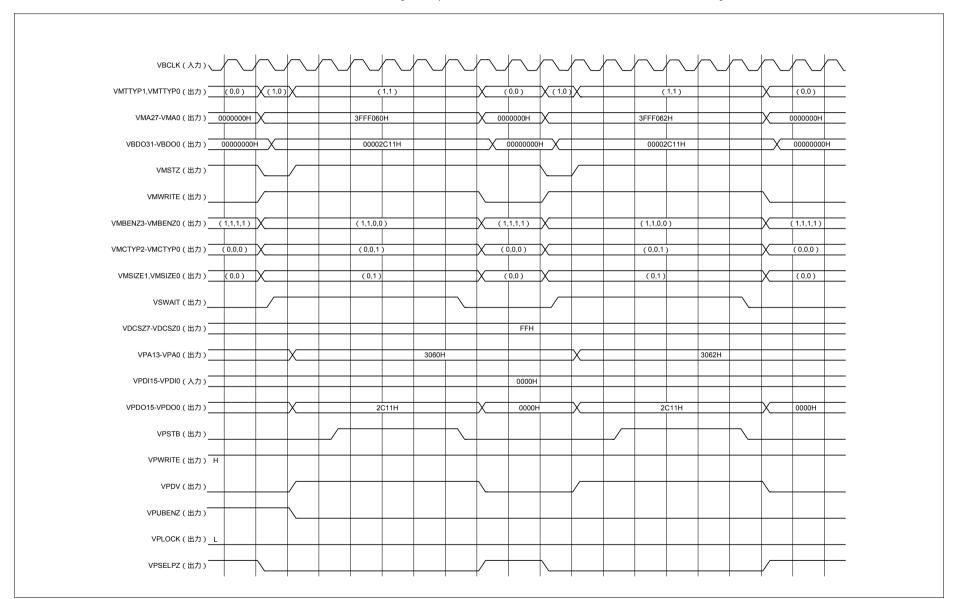

## 第6章 STBC ... 140

- 6.1 パワー・セーブ機能 ... 140

- 6.2 制御レジスタ ... 141

- 6.2.1 パワー・セーブ・コントロール・レジスタ (PSC) ... 141

- 6.2.2 コマンド・レジスタ (PRCMD) ... 144

- **6.3 HALT モード** ... 145

- 6.4 ソフトウエア STOP モード ... 146

- **6.5 ハードウエア STOP モード** ... 148

- 6.6 ソフトウエア / ハードウエア STOP モードでのクロック制御 ... 149

## 第7章 DMAC ... 154

- 7.1 特 徵 ... 154

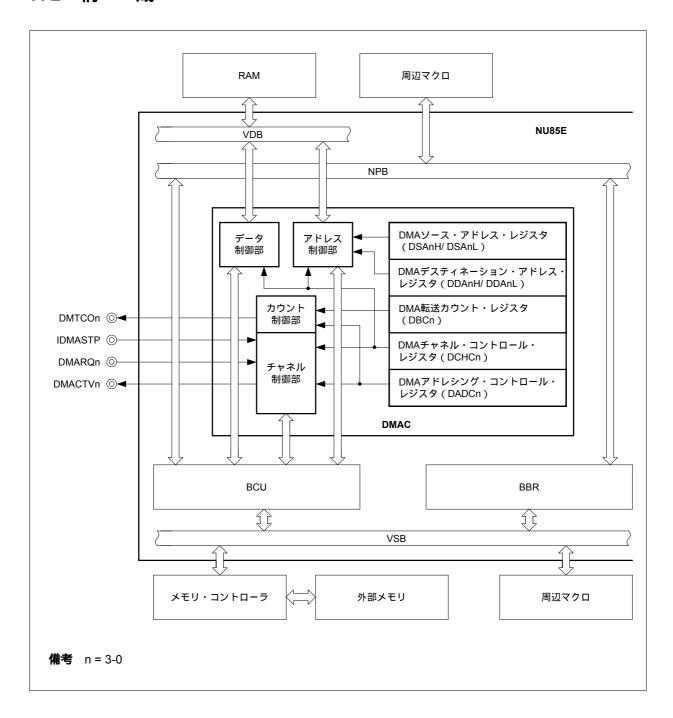

- 7.2 構 成... 155

- 7.3 転送対象 ... 156

- 7.4 DMA チャネルの優先順位 ... 156

- 7.5 制御レジスタ ... 157

- 7.5.1 DMA ソース・アドレス・レジスタ 0-3 (DSA0-DSA3) ... 157

- 7. 5. 2 DMA デスティネーション・アドレス・レジスタ 0-3 (DDA0-DDA3) ... 159

- 7.5.3 DMA 転送カウント・レジスタ 0-3 (DBC0-DBC3) ... 161

- 7. 5. 4 DMA アドレシング・コントロール・レジスタ 0-3 (DADC0-DADC3) ... 162

- 7. 5. 5 DMA チャネル・コントロール・レジスタ 0-3 (DCHC0-DCHC3) ... 164

- 7.5.6 DMA ディスエーブル・ステータス・レジスタ (DDIS) ... 165

- 7.5.7 DMA リスタート・レジスタ (DRST) ... 166

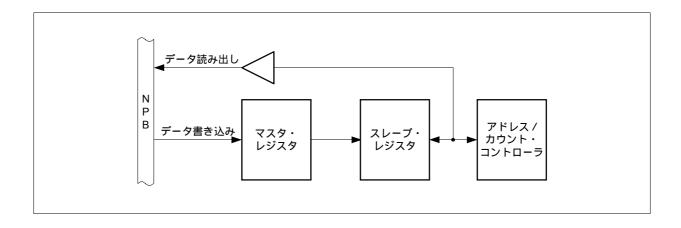

- 7.6 ネクスト・アドレス設定機能 ... 167

- 7.7 DMA パス・ステート ... 168

- 7.7.1 バス・ステートの種類 ... 168

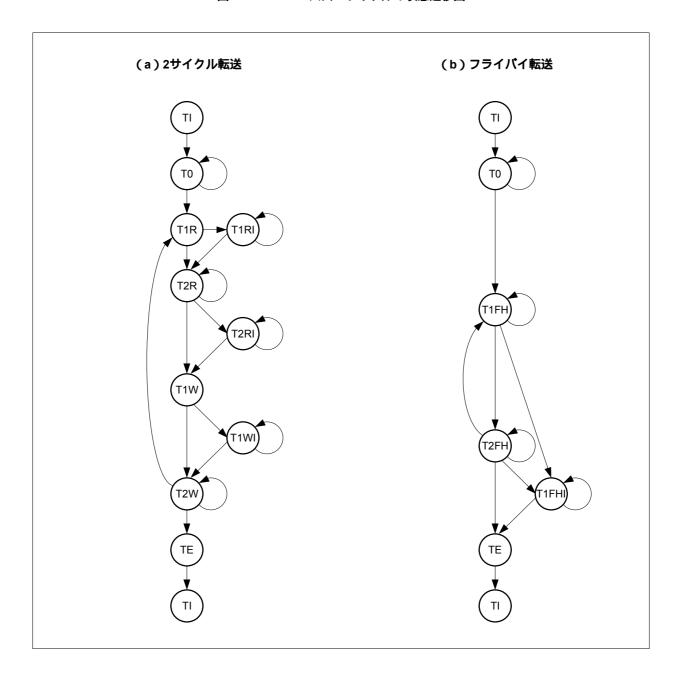

- 7.7.2 DMAC バス・サイクルの状態遷移 ... 170

- 7.8 転送モード ... 171

- 7.8.1 シングル転送モード ... 171

- 7.8.2 シングルステップ転送モード ... 173

- 7.8.3 ライン転送モード ... 174

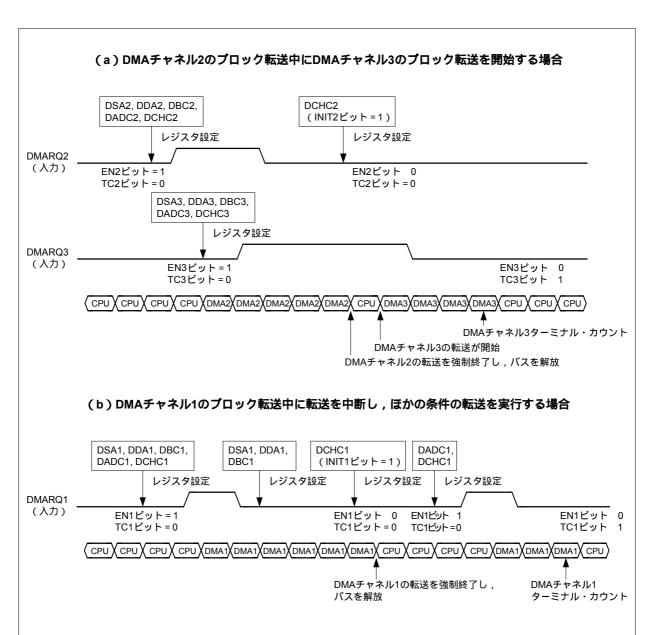

- 7.8.4 ブロック転送モード ... 176

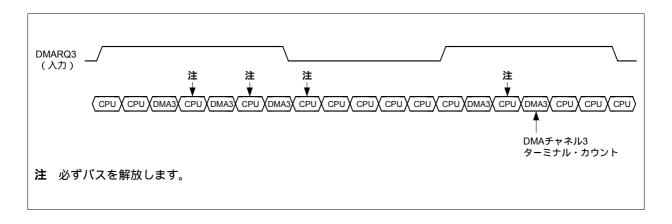

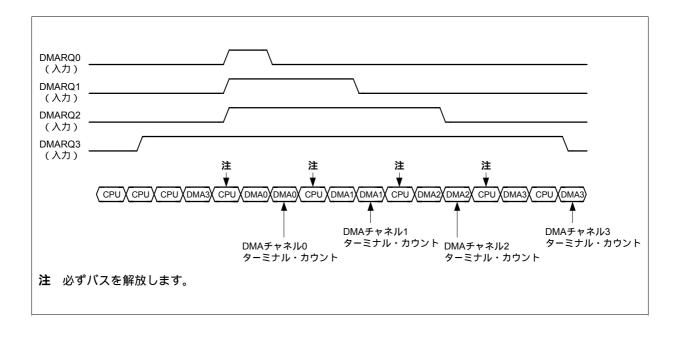

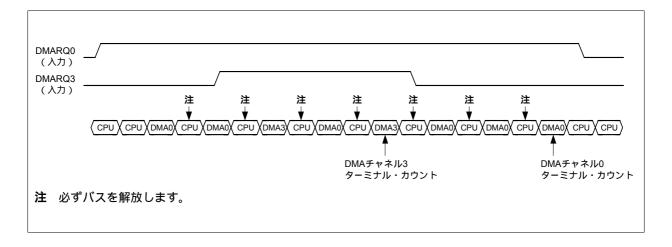

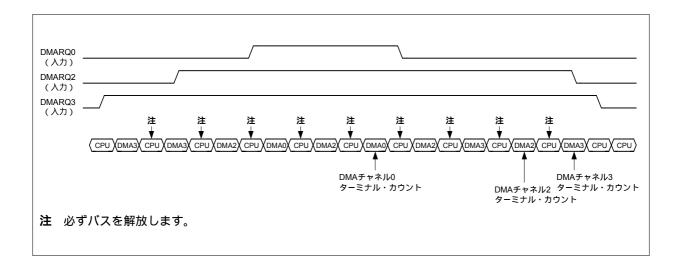

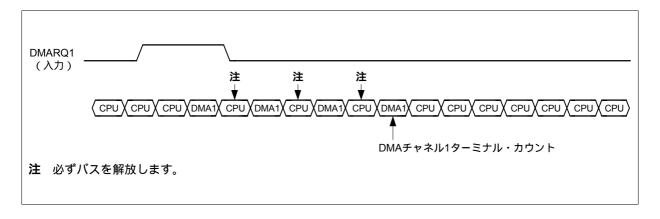

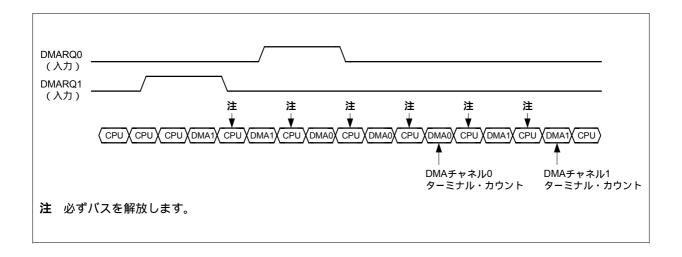

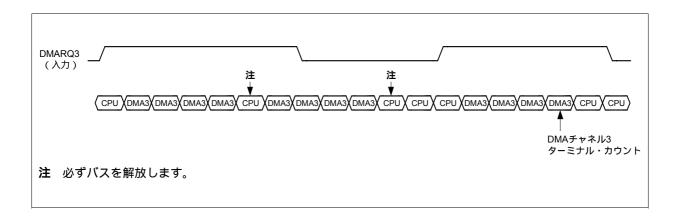

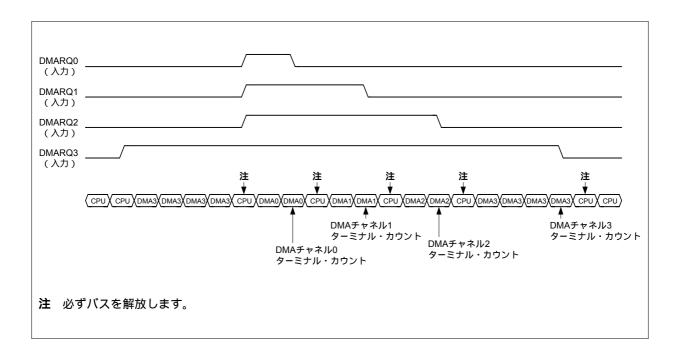

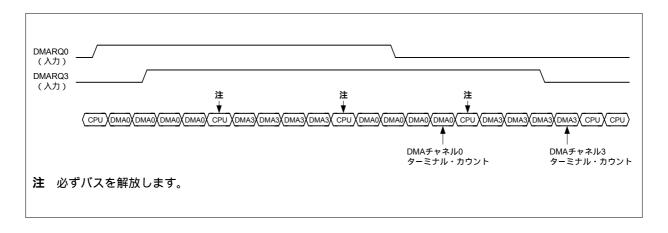

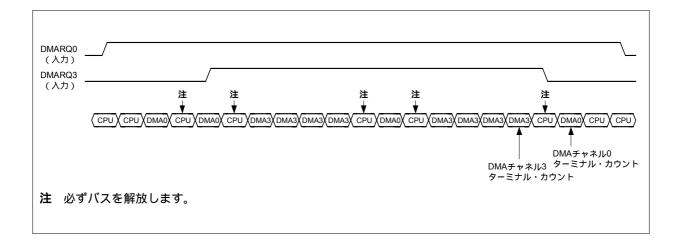

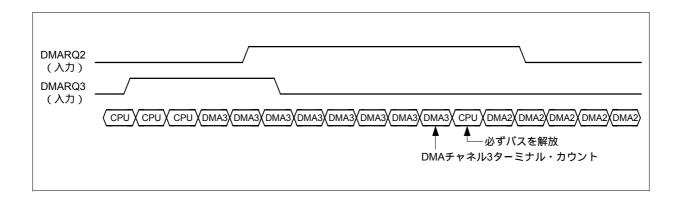

- 7.8.5 DMARQn 信号によるシングル転送時の 1 回転送 ... 177

- 7.9 転送タイプ ... 178

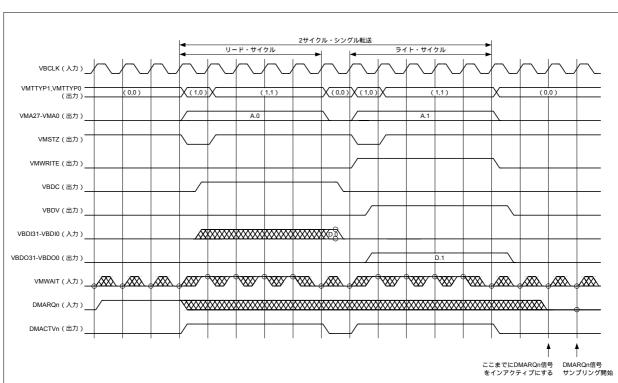

- 7.9.1 2サイクル転送 ... 178

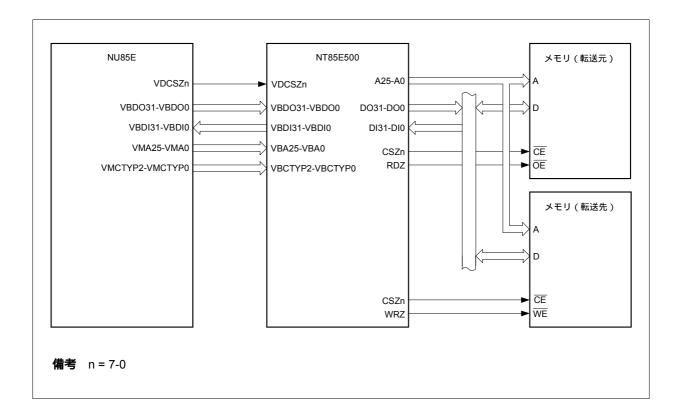

- 7.9.2 フライバイ転送 ... 179

- 7. 10 DMA 転送起動要因 ... 180

- 7. 11 DMA 転送完了時のターミナル・カウント出力 ... 181

- 7.12 強制中断 ... 182

- 7.13 強制終了 ... 183

- 7. 14 DMA 転送タイミング例 ... 184

- 7.15 注意事項 ... 208

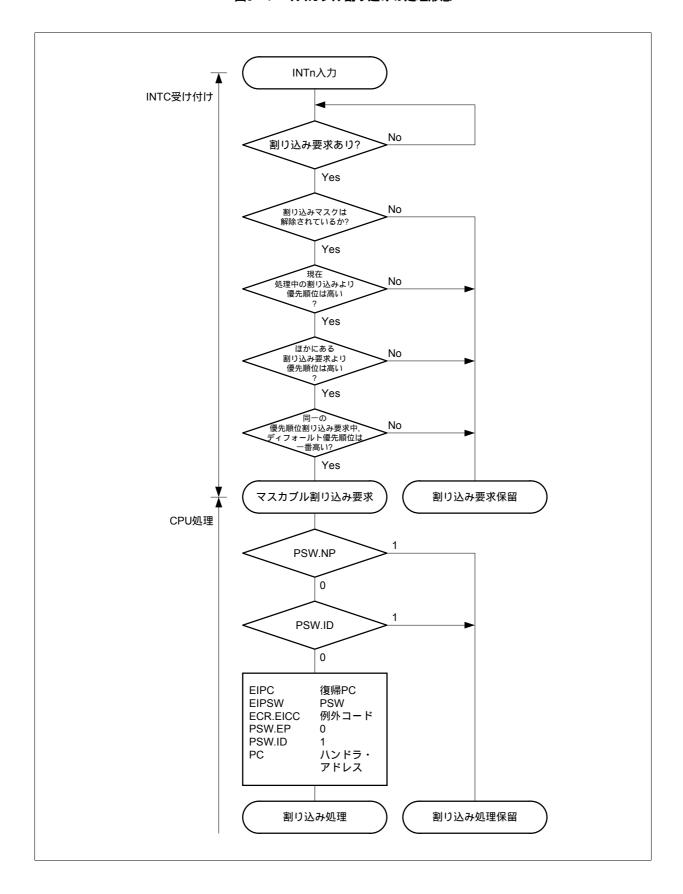

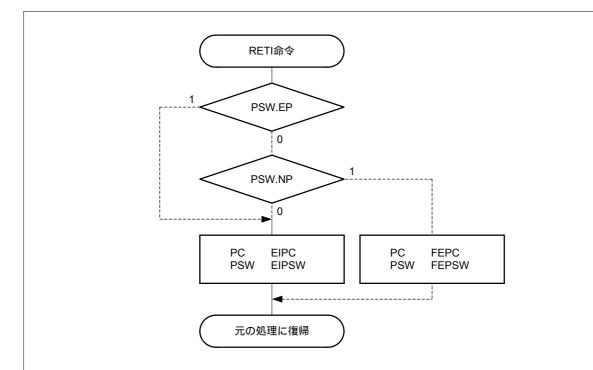

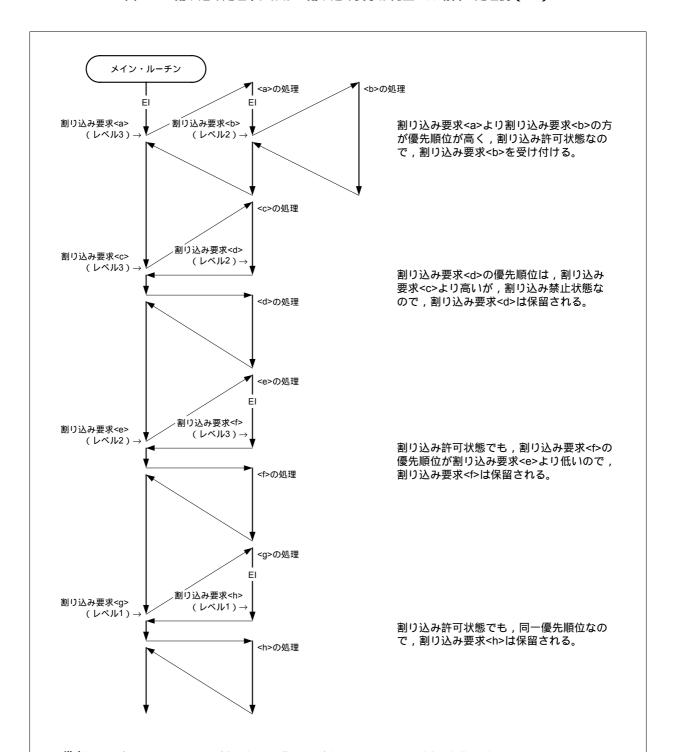

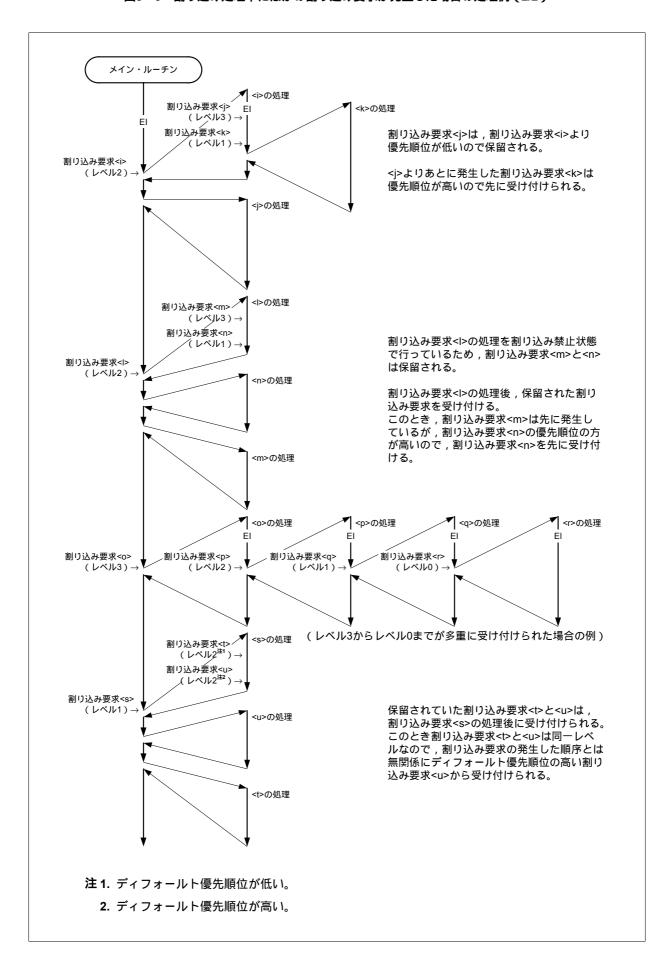

## 第8章 INTC ... 210

- 8.1 特 徵 ... 211

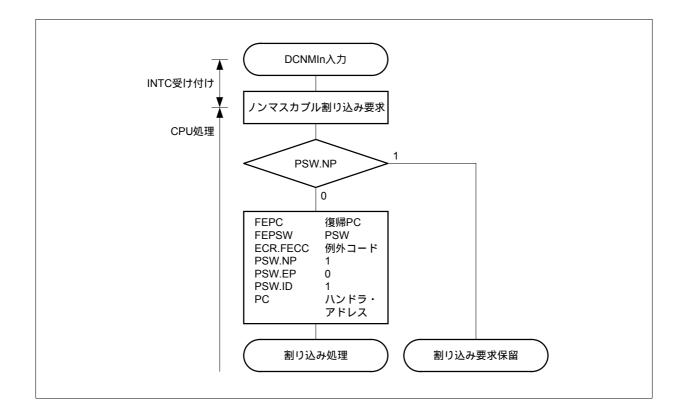

- 8.2 ノンマスカブル割り込み(NMI) ... 214

- 8.2.1 動作...217

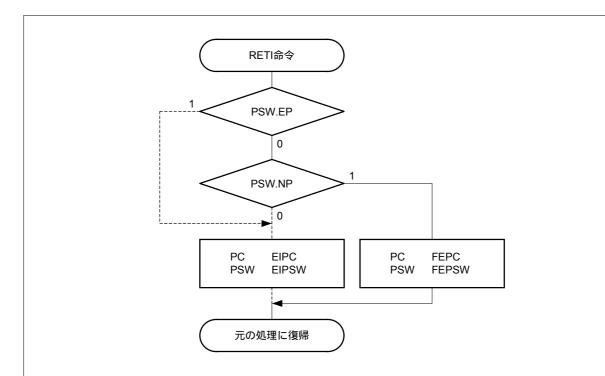

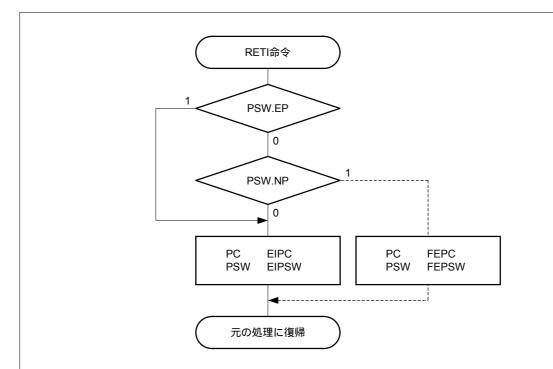

- 8.2.2 復 帰 ... 218

- 8.3 マスカブル割り込み ... 219

- 8.3.1 動 作 ... 219

- 8.3.2 復 帰 ... 221

- 8.3.3 マスカブル割り込みの優先順位 ... 222

- 8.3.4 制御レジスタ ... 226

- 8.3.5 マスカブル割り込みステータス・フラグ(ID) ... 229

- 8.4 ソフトウエア例外 ... 230

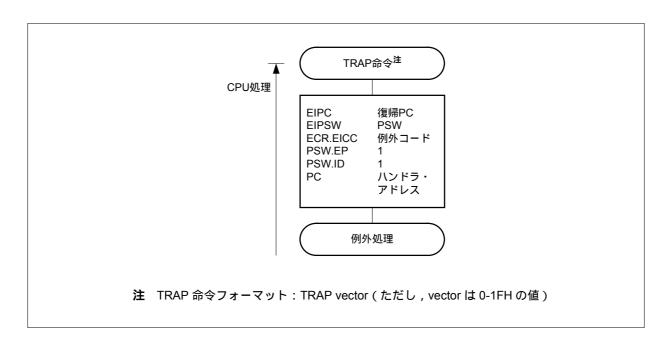

- 8.4.1 動作...230

- 8.4.2 復 帰 ... 231

- 8.5 例外トラップ ... 232

- 8.5.1 不正命令コード ... 232

- 8.5.2 動 作 ... 233

- 8.5.3 復 帰 ... 233

- 8.6 割り込み応答時間 ... 234

- 8.7 割り込みが受け付けられない期間 ... 234

## 第9章 テスト機能 ... 235

- 9.1 テスト用端子 ... 235

- 9.1.1 テスト・バス端子(TBI39-TBI0, TBO34-TBO0) ... 235

- 9.1.2 BUNRI, TEST 端子 ... 235

- 9.1.3 BUNRIOUT 端子 ... 236

- 9.2 テスト・インタフェース信号一覧 ... 236

- 9.3 テスト・モード時の周辺マクロ接続例 ... 237

- 9.4 テスト・モード時の各端子の処理 ... 238

## 第10章 NB85E901 ... 240

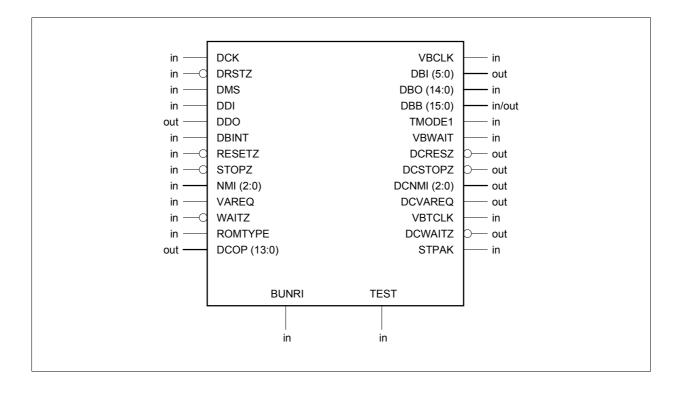

- 10.1 シンボル図 ... 240

- 10.2 端子機能 ... 241

- 10.2.1 端子機能一覧 ... 241

- 10.2.2 端子機能の説明 ... 242

- 10.2.3 未使用端子の処理 ... 244

- 10.2.4 端子状態 ... 245

- 10.3 ディバグ機能 ... 247

- **10.4 NU85E 接続例** ... 248

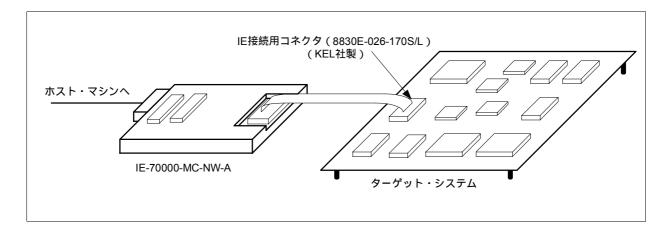

- 10.5 N-Wire 型 IE の接続 ... 249

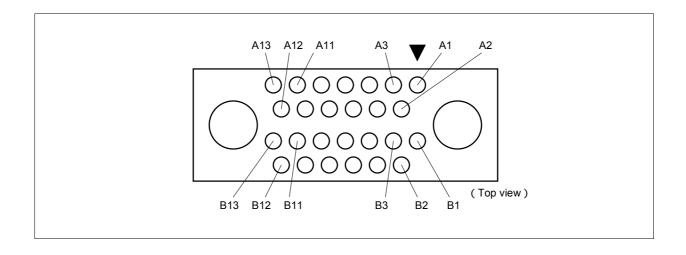

- 10.5.1 IE 接続コネクタ (ターゲット・システム側) ... 249

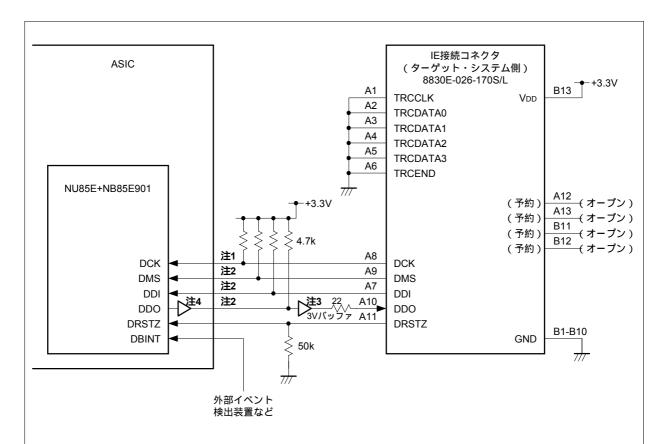

- 10.5.2 NU85E に NB85E901 を接続した場合の推奨回路例 ... 251

## 付録 A ROM/RAM アクセス・タイミング ... 252

## 付録 B 総合索引 ... 254

- B. 1 50 音で始まる語句の索引 ... 254

- **B.2** アルファベットで始まる語句の索引 ... 256

## 付録 C 改版履歴 ... 260

# 図の目次 (1/4)

| 図番号    | タイトル , ページ                                         |

|--------|----------------------------------------------------|

| 2 - 1  | DCRESZ 信号の受け付け 38                                  |

| 2 - 2  | システム・リセットにより VBCLK の発振を停止させる場合 38                  |

|        |                                                    |

| 3 - 1  | CPU レジスター覧 56                                      |

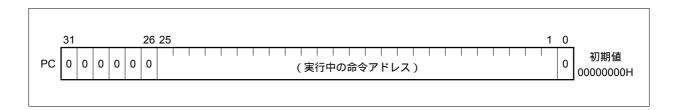

| 3 - 2  | プログラム・カウンタ(PC) 58                                  |

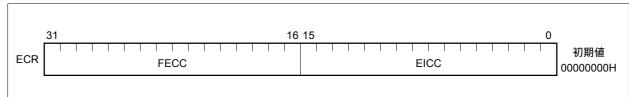

| 3 - 3  | 割り込み要因レジスタ(ECR) 60                                 |

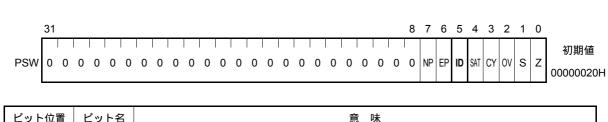

| 3 - 4  | プログラム・ステータス・ワード (PSW ) 61                          |

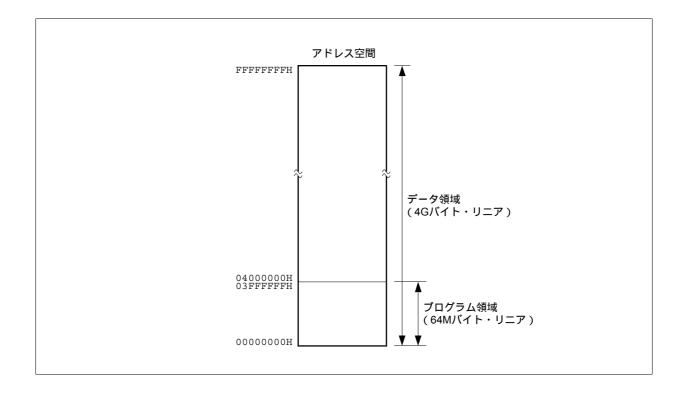

| 3 - 5  | アドレス空間 62                                          |

| 3 - 6  | プログラム領域 63                                         |

| 3 - 7  | データ領域(64M バイト・モード時) 64                             |

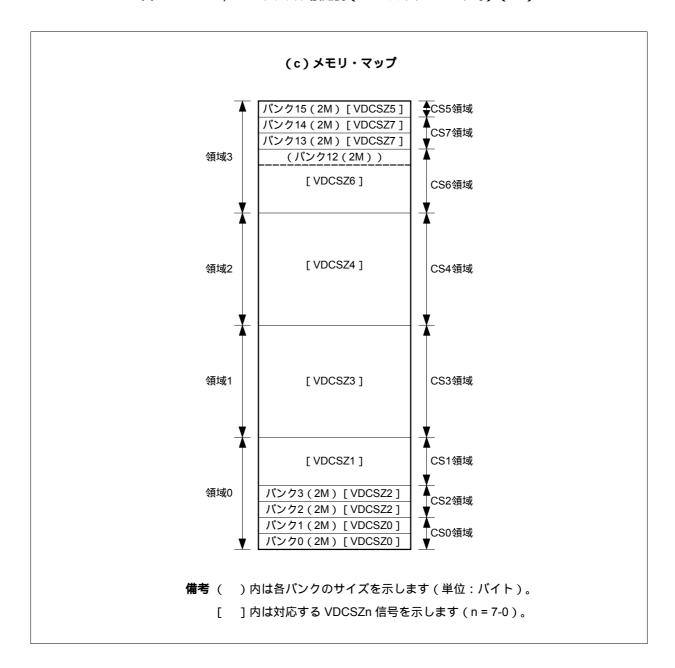

| 3 - 8  | データ領域(256M バイト・モード時) 65                            |

| 3 - 9  | ROM 領域 66                                          |

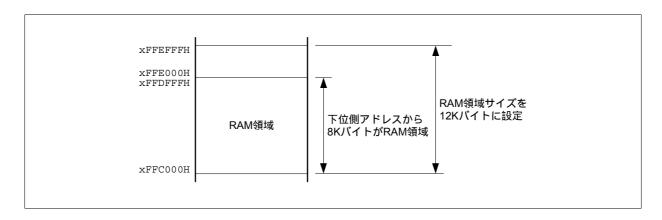

| 3 - 10 | RAM 領域 68                                          |

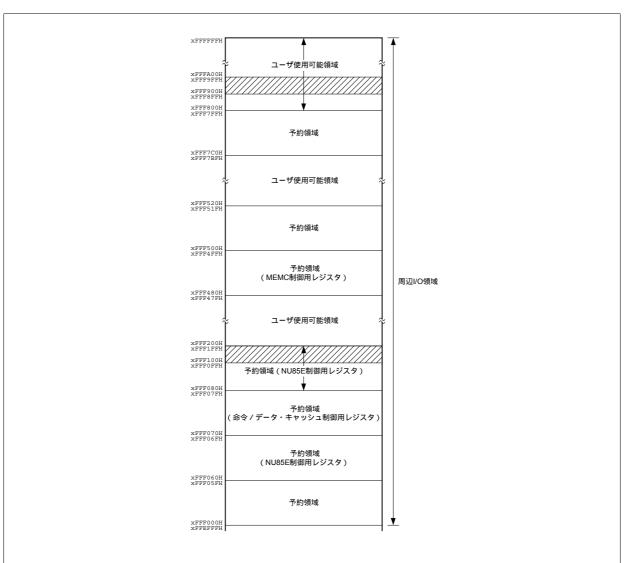

| 3 - 11 | 周辺 I/O 領域 70                                       |

| 3 - 12 | RCU を介した NU85E と N-Wire 型インサーキット・エミュレータの接続概略図 … 78 |

|        |                                                    |

| 4 - 1  | チップ領域セレクト制御レジスタ 0 ( CSC0 ) 82                      |

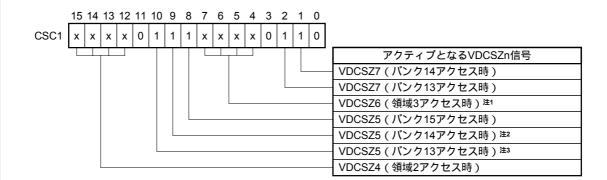

| 4 - 2  | チップ領域セレクト制御レジスタ 1(CSC1) 83                         |

| 4 - 3  | CSC0, CSC1 レジスタ設定例(64M バイト・モード時) 84                |

| 4 - 4  | CSC0, CSC1 レジスタ設定例(256M バイト・モード時) 87               |

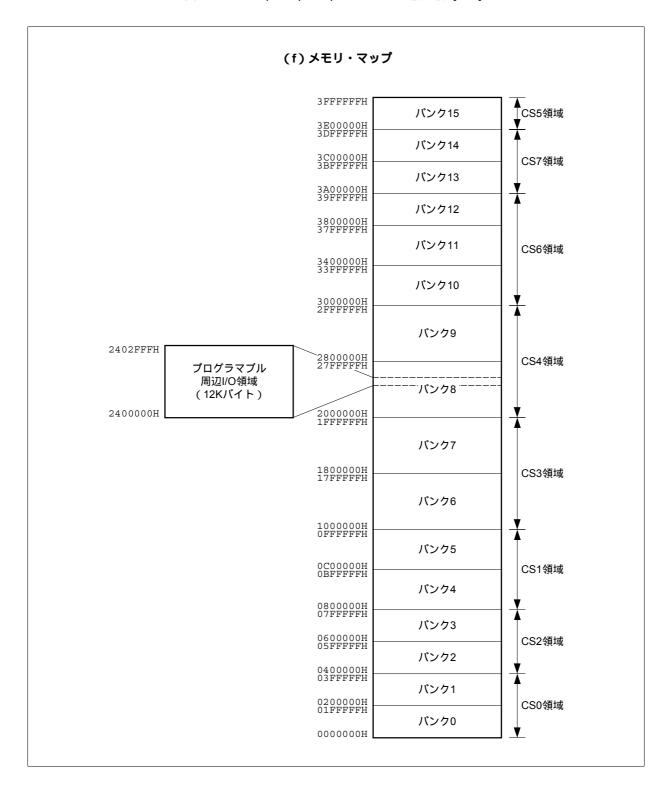

| 4 - 5  | 周辺 I/O 領域とプログラマブル周辺 I/O 領域 89                      |

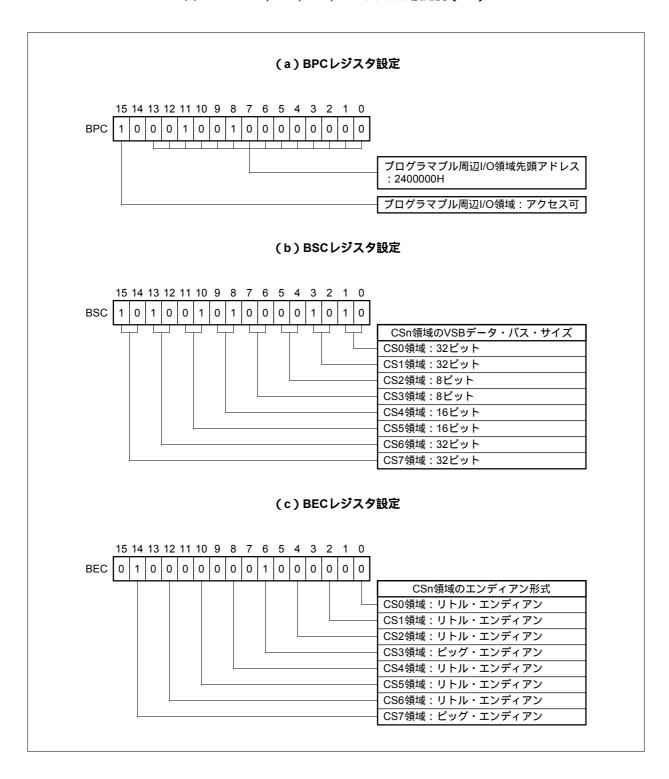

| 4 - 6  | 周辺 I/O 領域セレクト制御レジスタ(BPC) 90                        |

| 4 - 7  | バス・サイズ・コンフィギュレーション・レジスタ (BSC) 91                   |

| 4 - 8  | エンディアン・コンフィギュレーション・レジスタ(BEC) 92                    |

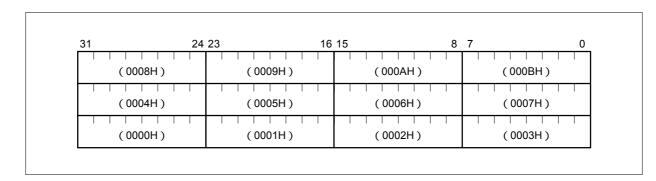

| 4 - 9  | ワード・データのリトル・エンディアン形式例 93                           |

| 4 - 10 | ワード・データのビッグ・エンディアン形式例 93                           |

| 4 - 11 | キャッシュ・コンフィギュレーション・レジスタ(BHC) 95                     |

| 4 - 12 | BPC, BSC, BEC, BHC レジスタ設定例 96                      |

| 4 - 13 | VSB によるデータ転送例 99                                   |

| 4 - 14 | VSB に接続されたバス・スレーブとのリード / ライト・タイミング 104             |

| 4 - 15 | VSB タイミング例 116                                     |

| 4 - 16 | リセット・タイミング 118                                     |

| 4 - 17 | バス・マスタ移行タイミング 120                                  |

| 4 - 18 | ミス・アライン・アクセス・タイミング 121                             |

|        |                                                    |

| 5 - 1  | NPB 接続の概略図 123                                     |

| 5 - 2  | NU85E と周辺マクロの接続例 124                               |

| 5 - 3  | 周辺 I/O 領域とプログラマブル周辺 I/O 領域 125                     |

| 5 - 4  | 国辺 I/O 領域セレクト制御レジスタ(BPC) 126                       |

# 図の目次(2/4)

| 図番号    | タイトル , ページ                                         |

|--------|----------------------------------------------------|

| 5 - 5  | BPC レジスタ設定例 127                                    |

| 5 - 6  | NPB ストローブ・ウエイト・コントロール・レジスタ(VSWC) 128               |

| 5 - 7  | リトライ機能 130                                         |

| 5 - 8  | ハーフワード・アクセス・タイミング 131                              |

| 5 - 9  | 奇数アドレスに対するバイト・アクセス・タイミング 131                       |

| 5 - 10 | 偶数アドレスに対するバイト・アクセス・タイミング 132                       |

| 5 - 11 | リード・モディファイ・ライト・タイミング 132                           |

| 5 - 12 | リトライ・タイミング(ライト) 133                                |

| 5 - 13 | リトライ・タイミング(リード) 133                                |

| 5 - 14 | NPB に接続されたバス・スレーブとのリード / ライト・タイミング 134             |

| 5 - 15 | NPB ライト・タイミング(CSC0, CSC1 レジスタへのデータ・ライト・タイミング例) 138 |

| 6 - 1  | パワー・セーブ機能状態遷移図 140                                 |

| 6 - 2  | パワー・セーブ・コントロール・レジスタ(PSC) 142                       |

| 6 - 3  | コマンド・レジスタ ( PRCMD ) 144                            |

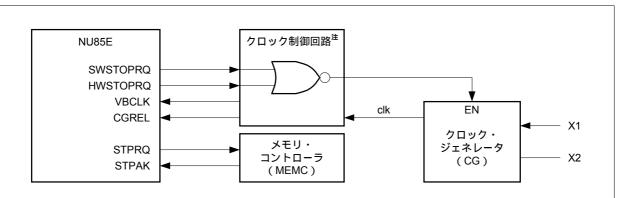

| 6 - 4  | NU85E とクロック制御回路の接続 149                             |

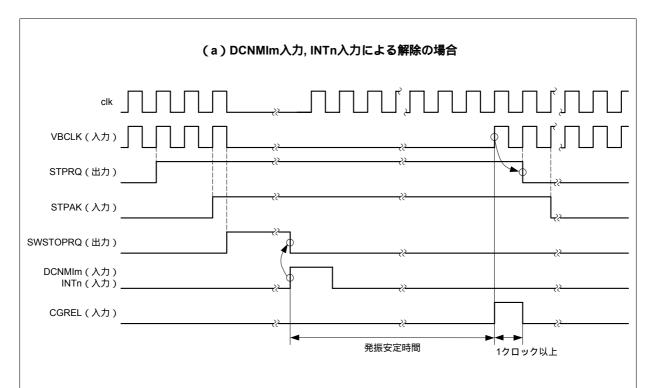

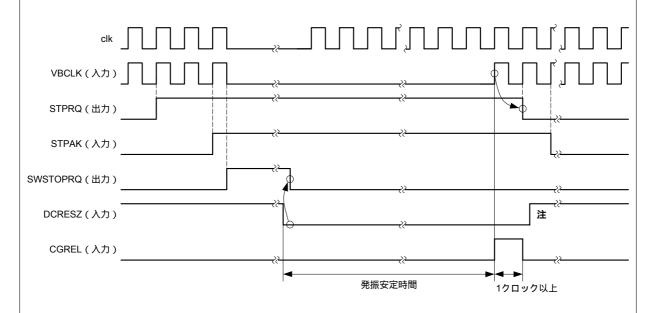

| 6 - 5  | ソフトウエア STOP モード設定 / 解除タイミング例 151                   |

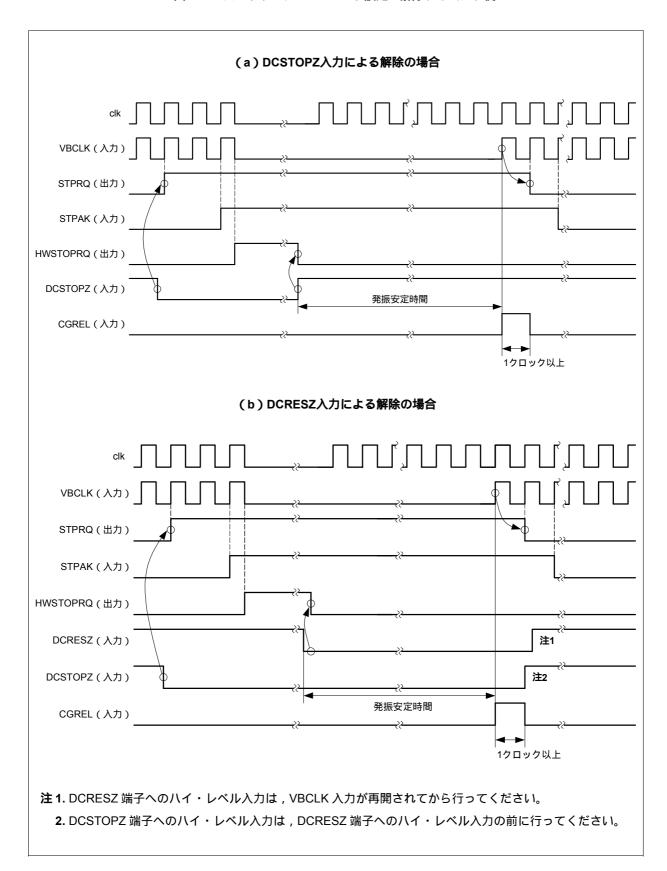

| 6 - 6  | ハードウエア STOP モード設定 / 解除タイミング例 153                   |

|        |                                                    |

| 7 - 1  | DMA ソース・アドレス・レジスタ 0H-3H(DSA0H-DSA3H) 157           |

| 7 - 2  | DMA ソース・アドレス・レジスタ 0L-3L ( DSA0L-DSA3L ) 158        |

| 7 - 3  | DMA デスティネーション・アドレス・レジスタ 0H-3H ( DDA0H-DDA3H ) 159  |

| 7 - 4  | DMA デスティネーション・アドレス・レジスタ 0L-3L(DDA0L-DDA3L) 160     |

| 7 - 5  | DMA 転送カウント・レジスタ 0-3(DBC0-DBC3) 161                 |

| 7 - 6  | DMA アドレシング・コントロール・レジスタ 0-3 ( DADC0-DADC3 ) 162     |

| 7 - 7  | DMA チャネル・コントロール・レジスタ 0-3(DCHC0-DCHC3) 164          |

| 7 - 8  | DMA ディスエーブル・ステータス・レジスタ(DDIS) 165                   |

| 7 - 9  | DMA リスタート・レジスタ ( DRST ) 166                        |

| 7 - 10 | バッファ・レジスタの構成 167                                   |

| 7 - 11 | DMAC バス・サイクルの状態遷移図 170                             |

| 7 - 12 | シングル転送例 1 171                                      |

| 7 - 13 | シングル転送例 2 171                                      |

| 7 - 14 | シングル転送例 3 172                                      |

| 7 - 15 | シングル転送例 4 172                                      |

| 7 - 16 | シングルステップ転送例 1 173                                  |

| 7 - 17 |                                                    |

| 7 - 18 | ライン転送例 1 174                                       |

|        | ライン転送例 2 174                                       |

| 7 - 20 | ライン転送例 3 175                                       |

## 図の目次(3/4)

#### 図番号

## タイトル,ページ

- 7-21 ライン転送例 4 ... 175

- 7-22 ブロック転送例 ... 176

- 7 23 DMARQn 信号によるシングル転送時の 1 回転送 ... 177

- 7-24 2 サイクル転送例 ... 178

- 7-25 フライバイ転送例 (メモリ I/O) ... 179

- 7-26 ターミナル・カウント信号 (DMTCO3-DMTCO0) タイミング例 ... 181

- 7 27 ターミナル・カウント信号 (DMTCO3-DMTCO0) の出力例 ... 181

- 7 28 DMA 転送の強制中断例 ... 182

- 7-29 DMA 転送の強制終了例 ... 183

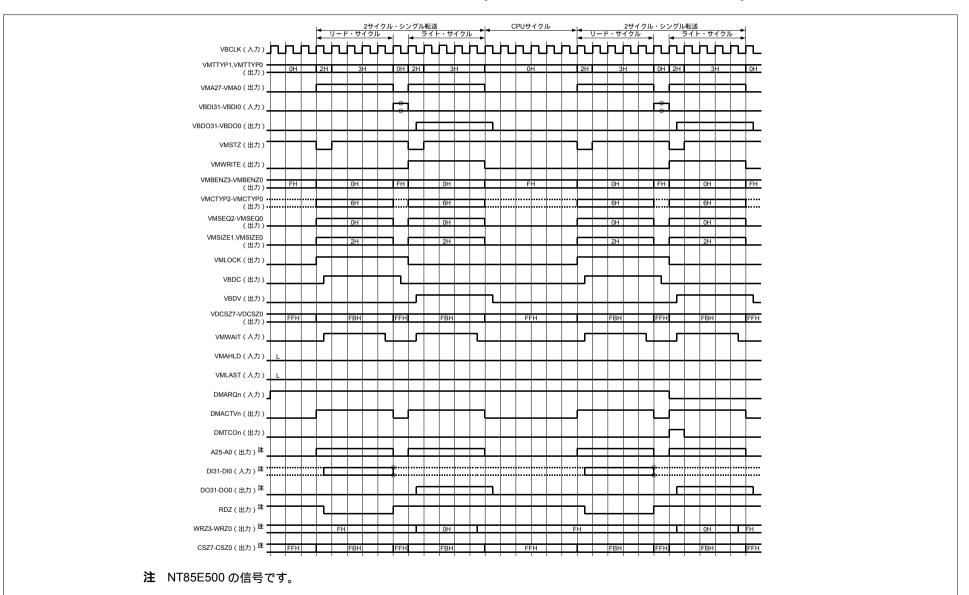

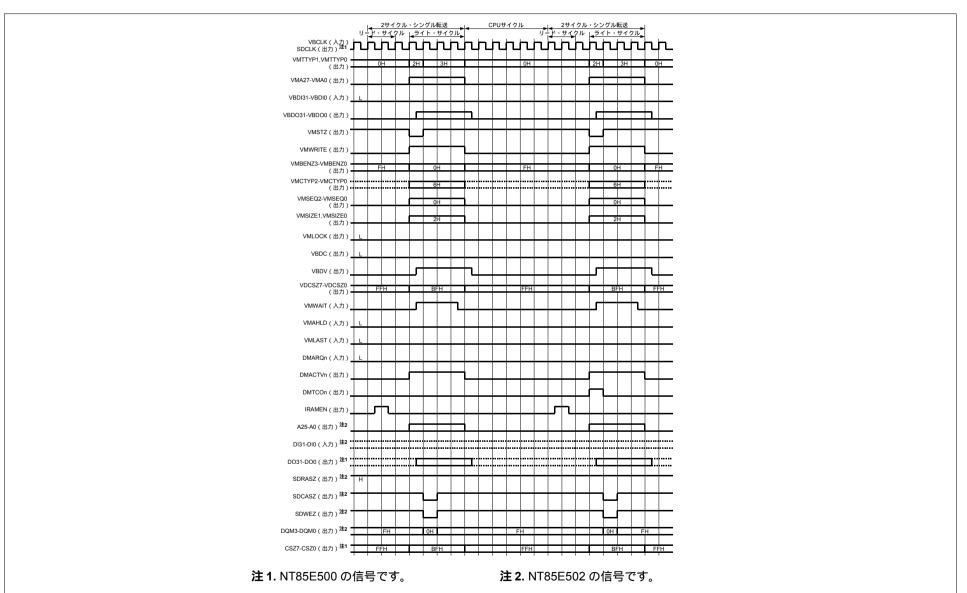

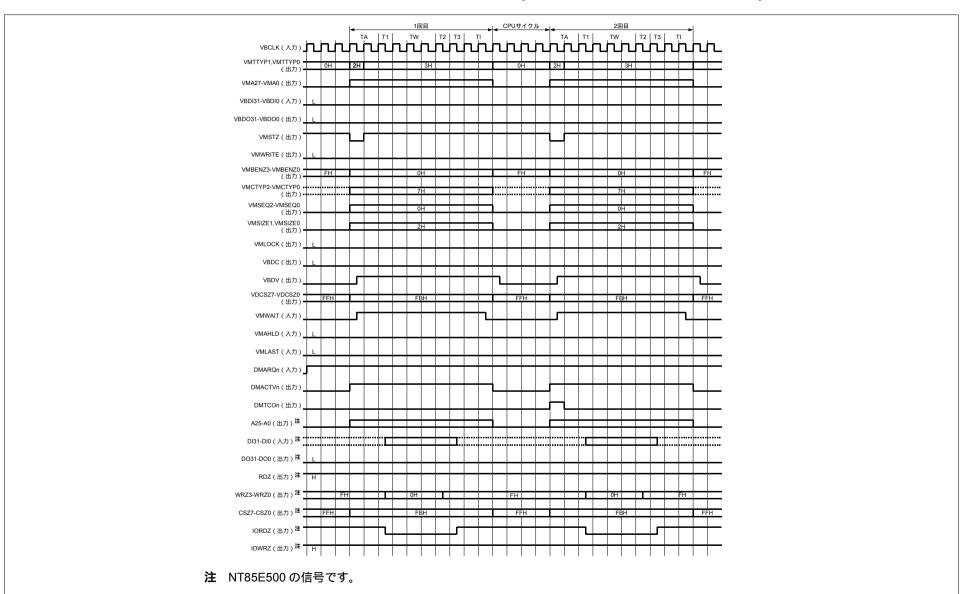

- 7 30 2 サイクル・シングル転送タイミング例(NT85E500 に接続した外部 SRAM↔外部 SRAM) ... 185

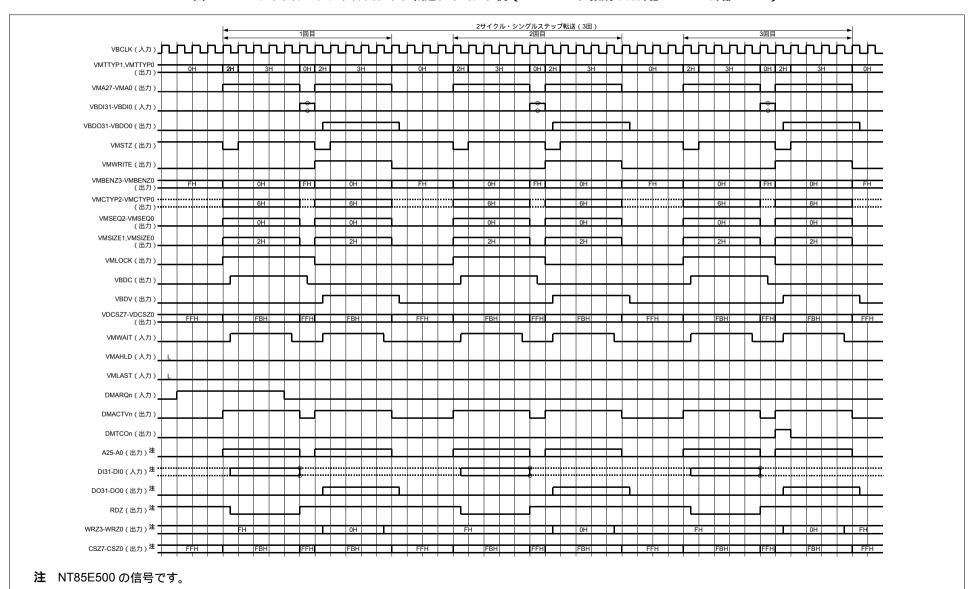

- 7 31 2 サイクル・シングルステップ転送タイミング例(NT85E500 に接続した外部 SRAM↔外部 SRAM) ... 187

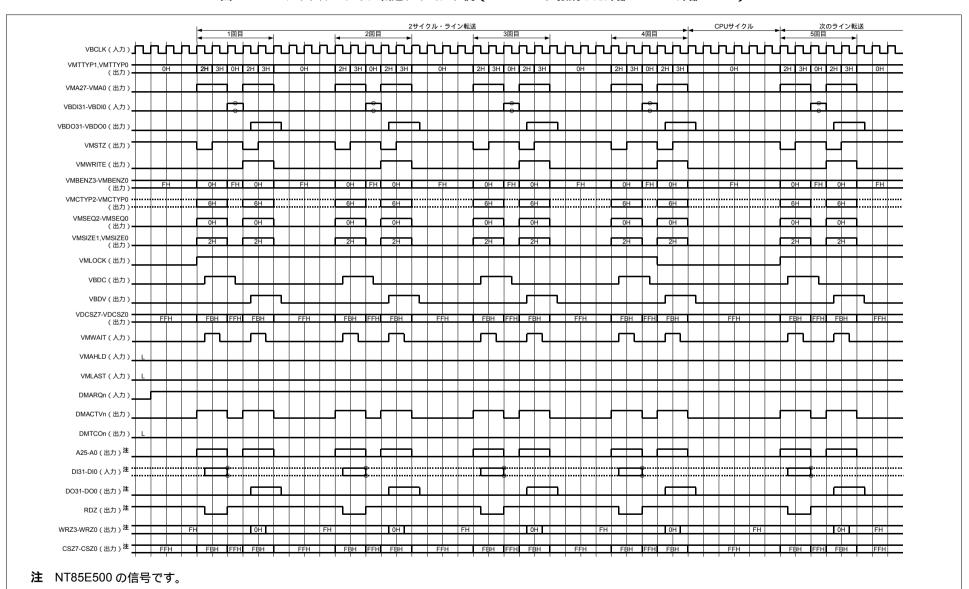

- 7 32 2 サイクル・ライン転送タイミング例(NT85E500 に接続した外部 SRAM↔外部 SRAM) ... 189

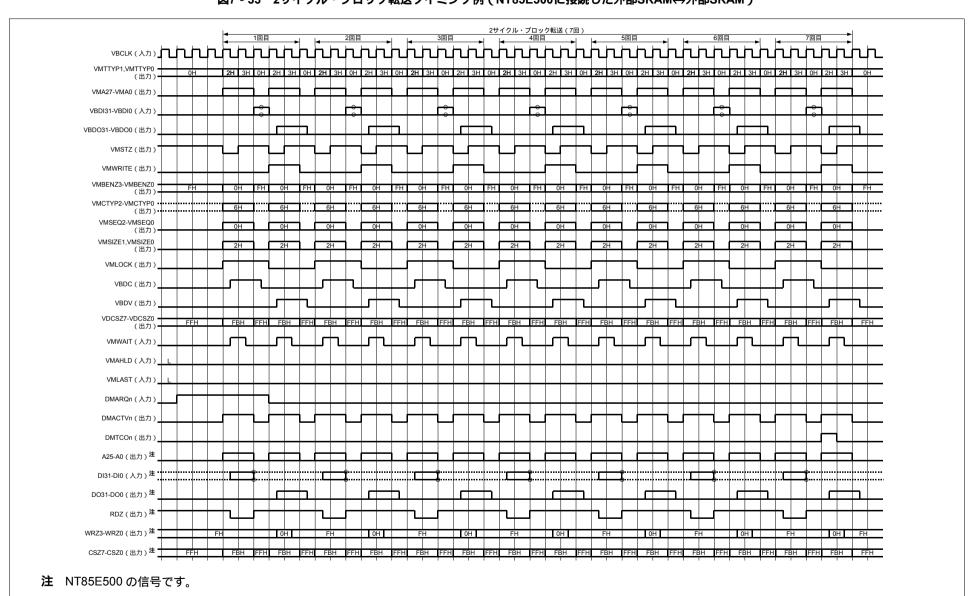

- 7-33 2 サイクル・ブロック転送タイミング例(NT85E500 に接続した外部 SRAM↔外部 SRAM) ... 191

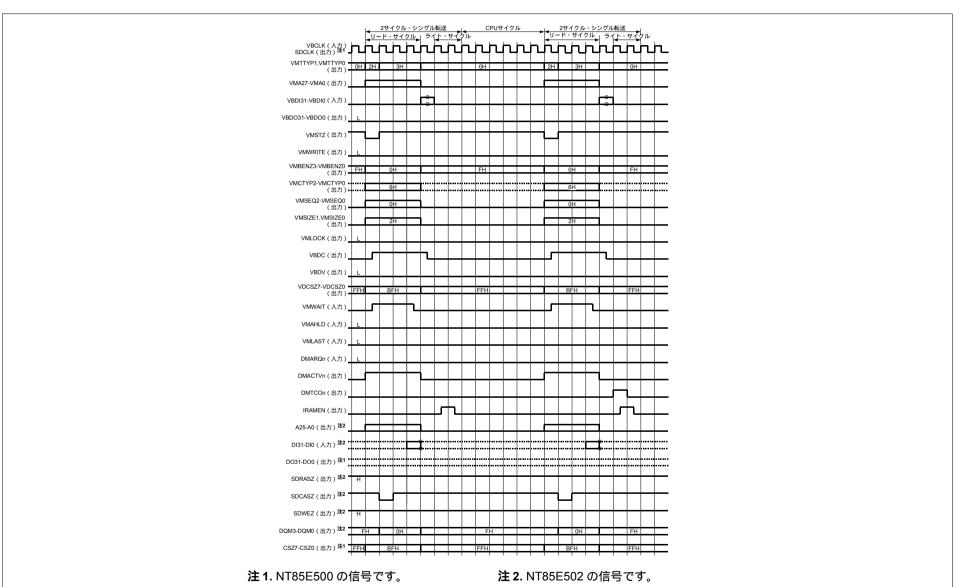

- 7 34 2 サイクル・シングル転送タイミング例 (VDB に接続した RAM→NT85E502 に接続した SDRAM) ... 193

- 7 35 2 サイクル・シングル転送タイミング例(NT85E502 に接続した SDRAM→VDB に接続した RAM) ... 195

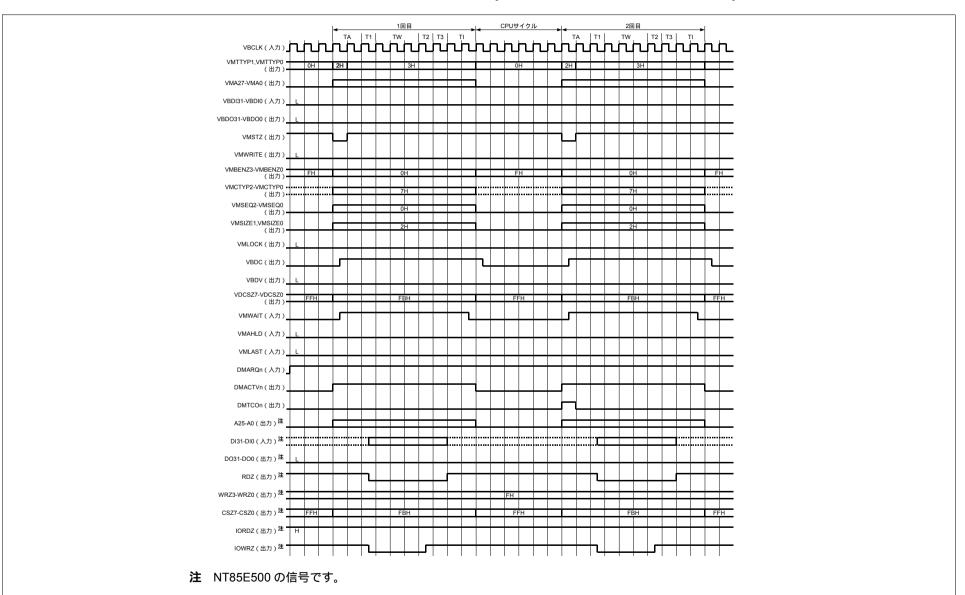

- 7 36 フライバイ・シングル転送タイミング例(NT85E500 に接続した外部 SRAM→外部 I/O) ... 197

- 7 37 フライバイ・シングルステップ転送タイミング例(NT85E500 に接続した外部 SRAM→外部 I/O) ... 199

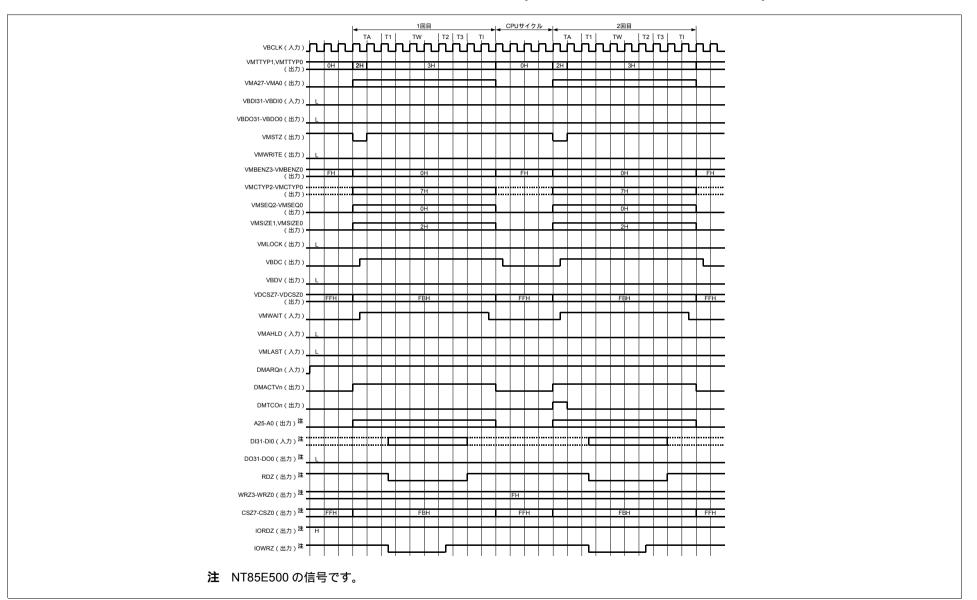

- 7 38 フライバイ・シングルステップ転送タイミング例(NT85E500 に接続した外部 I/O→外部 SRAM) ... 201

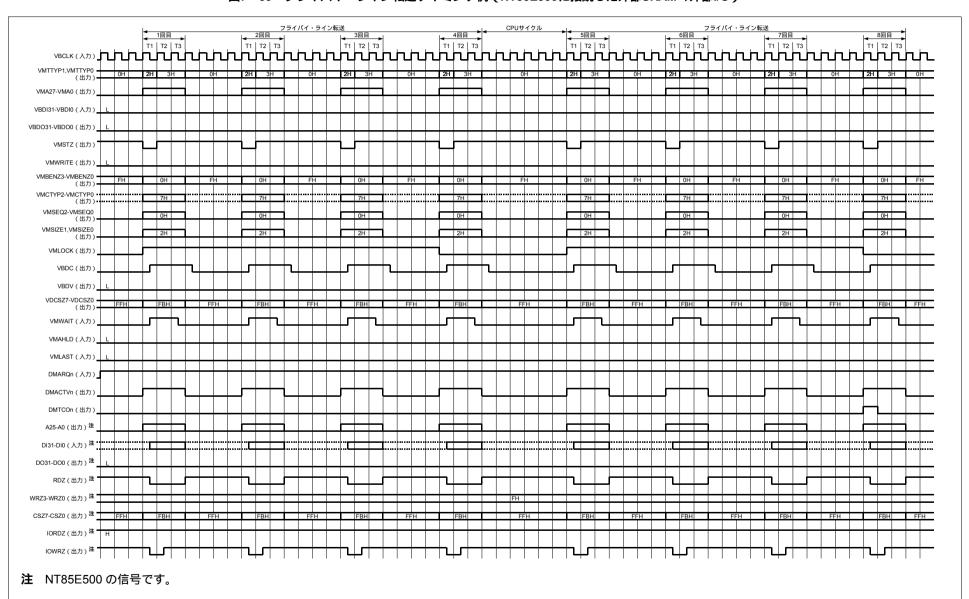

- 7 39 フライバイ・ライン転送タイミング例(NT85E500に接続した外部 SRAM→外部 I/O) ... 203

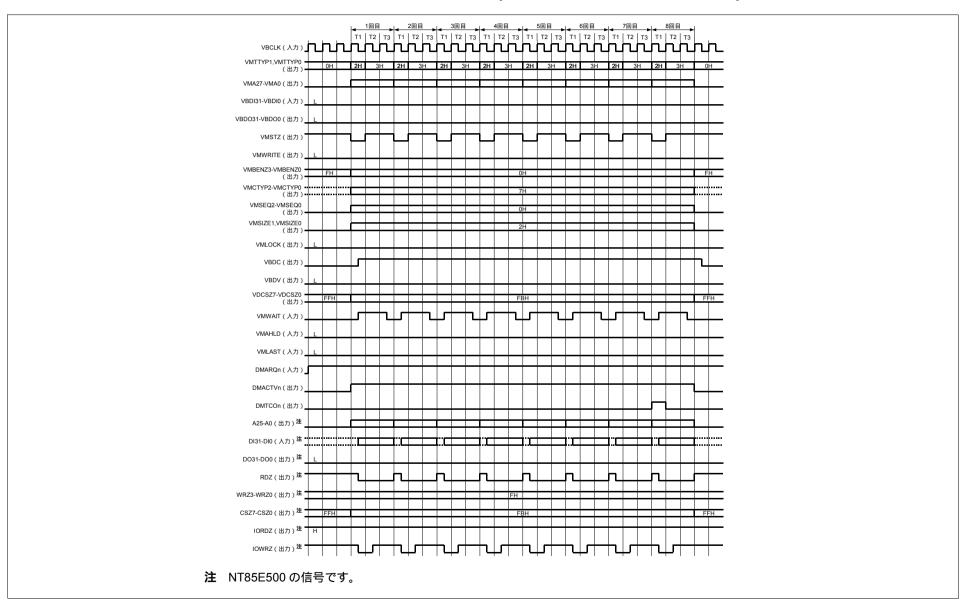

- 7 40 フライバイ・ブロック転送タイミング例(NT85E500 に接続した外部 SRAM→外部 I/O) ... 205

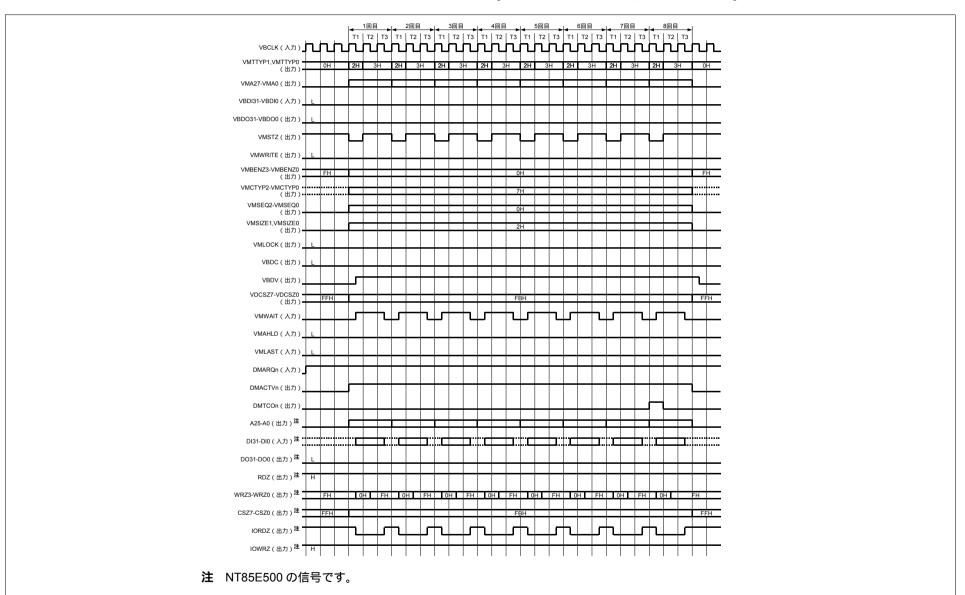

- 7 41 フライバイ・ブロック転送タイミング例(NT85E500 に接続した外部 I/O→外部 SRAM) ... 207

- 8-1 ノンマスカブル割り込み要求の受け付け動作 ... 215

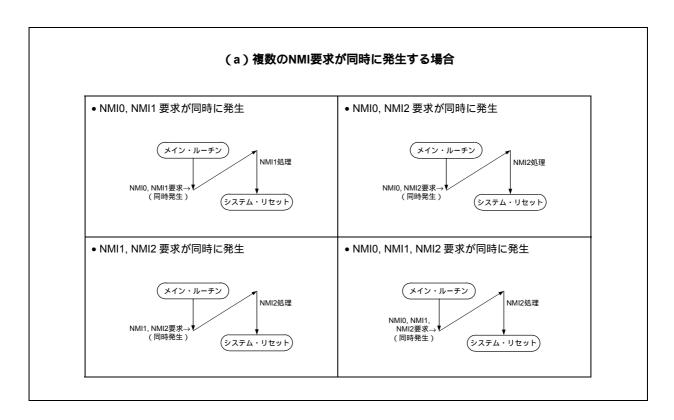

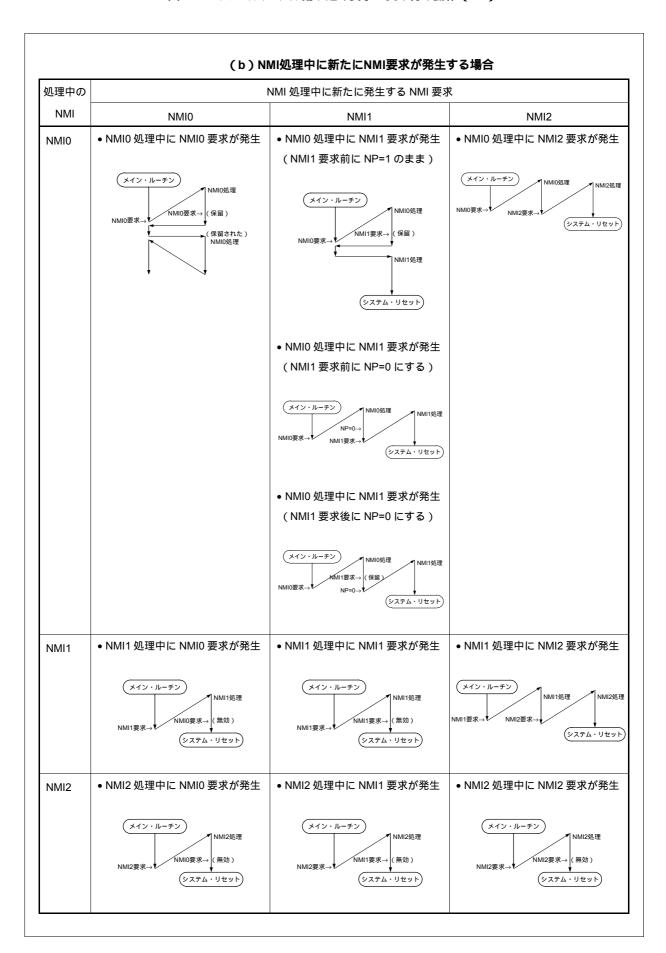

- 8-2 ノンマスカブル割り込みの処理形態 ... 217

- 8-3 RETI 命令の処理形態 ... 218

- 8-4 マスカブル割り込みの処理形態 ... 220

- 8-5 RETI 命令の処理形態 ... 221

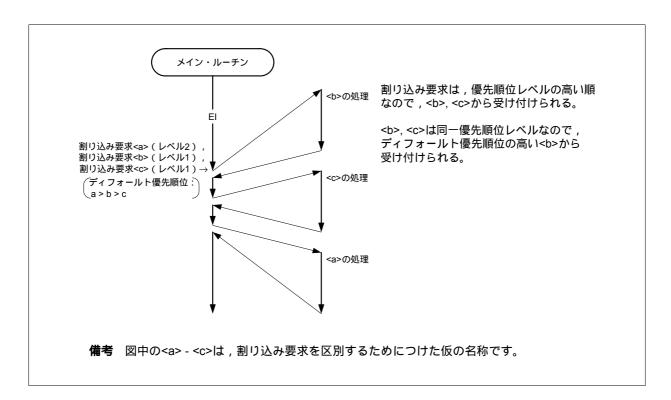

- 8-6 割り込み処理中にほかの割り込み要求が発生した場合の処理例 ... 223

# 図の目次(4/4)

| 図番号    | タイトル , ページ                         |

|--------|------------------------------------|

| 8 - 7  | 同時発生した割り込み要求の処理例 225               |

| 8 - 8  | 割り込み制御レジスタ 0-63 (PIC0-PIC63) 226   |

| 8 - 9  | 割り込みマスク・レジスタ 0-3(IMR0-IMR3) 227    |

| 8 - 10 | インサービス・プライオリティ・レジスタ(ISPR) 228      |

| 8 - 11 | プログラム・ステータス・ワード (PSW) 229          |

| 8 - 12 | ソフトウエア例外の処理形態 230                  |

| 8 - 13 | RETI 命令の処理形態 231                   |

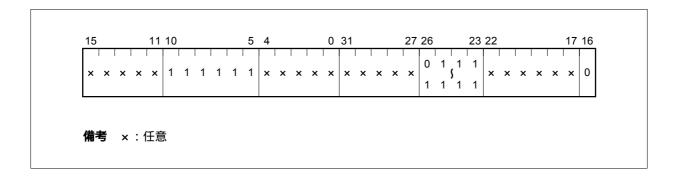

| 8 - 14 | 不正命令コード 232                        |

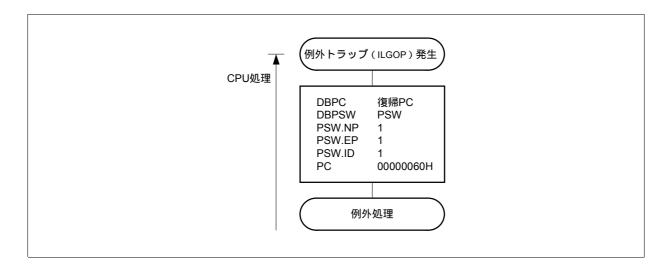

| 8 - 15 | 例外トラップの処理形態 233                    |

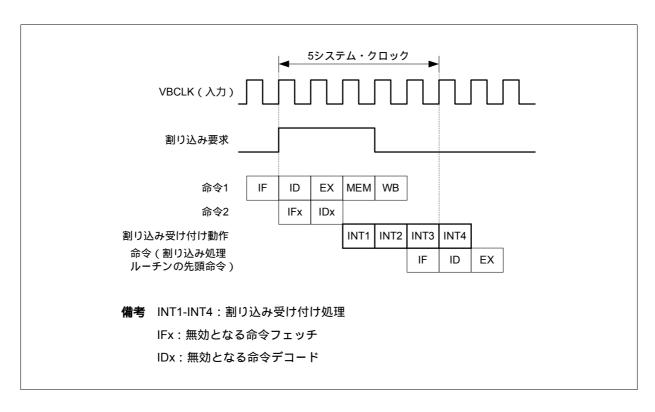

| 8 - 16 | 割り込み要求受け付け時のパイプライン動作例(概略) 234      |

|        |                                    |

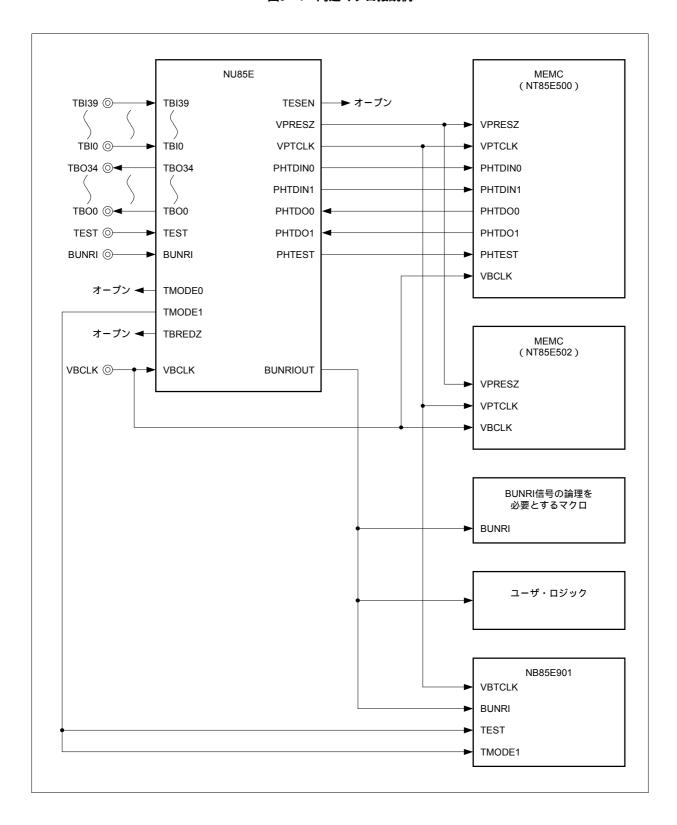

| 9 - 1  | 周辺マクロ接続例 237                       |

|        |                                    |

| 10 - 1 | NB85E901 と NU85E の接続例 248          |

| 10 - 2 | N-Wire 型 IE の接続 249                |

| 10 - 3 | IE 接続コネクタ(ターゲット・システム側)のピン配置図 … 249 |

| 10 - 4 | IE 接続推奨回路例(NU85E + NB85E901) 251   |

|        |                                    |

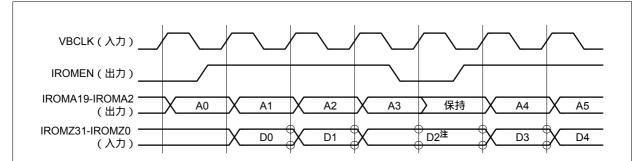

| A - 1  | ROM アクセス・タイミング 252                 |

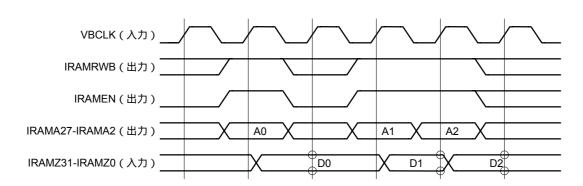

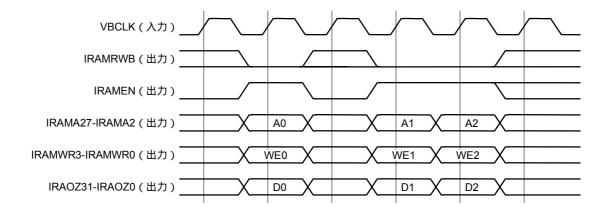

| A - 2  | RAM アクセス・タイミング 253                 |

|        |                                    |

# 表の目次(1/2)

| 表番号    | タイトル , ページ                                   |

|--------|----------------------------------------------|

| 2 - 1  | VMTTYP1, VMTTYP0 信号 33                       |

| 2 - 2  | VMBENZ3-VMBENZ0, VSBENZ1 信号 34               |

| 2 - 3  | VMSIZE1, VMSIZE0 信号 34                       |

| 2 - 4  | VMCTYP2-VMCTYP0 信号 35                        |

| 2 - 5  | VMSEQ2-VMSEQ0 信号 35                          |

| 2 - 6  | IRAMWR3-IRAMWR0 信号 41                        |

| 2 - 7  | IDDRRQ, IDDWRQ, IDSEQ4, IDSEQ2 信号 43         |

| 2 - 8  | IFIRA64, IFIRA32, IFIRA16 信号 46              |

| 2 - 9  | IFINSZ1, IFINSZ0 信号 47                       |

| 2 - 10 | 各動作モードでの端子状態 52                              |

|        |                                              |

| 3 - 1  | プログラム・レジスター覧 57                              |

| 3 - 2  | システム・レジスター覧 59                               |

| 3 - 3  | 割り込み / 例外テーブル 67                             |

| 3 - 4  | RAM 領域サイズの設定 68                              |

|        |                                              |

| 4 - 1  | VMTTYP1, VMTTYP0 信号 100                      |

| 4 - 2  | VMCTYP2-VMCTYP0 信号 100                       |

| 4 - 3  | VMBENZ3-VMBENZ0 信号 101                       |

| 4 - 4  | VMSIZE1, VMSIZE0 信号 101                      |

| 4 - 5  | VMSEQ2-VMSEQ0 信号 101                         |

| 4 - 6  | VMWAIT, VMAHLD, VMLAST 信号 102                |

| 4 - 7  | VBDC, VBDV 信号 102                            |

| 5 - 1  | 各動作周波数におけるセットアップ・ウエイト幅 , VPSTB ウエイト幅の設定値 129 |

| 0 4    |                                              |

|        | 割り込み要求による HALT モード解除後の動作 145                 |

|        | 割り込み要求によるソフトウエア STOP モード解除後の動作 146           |

|        | 割り込み処理ルーチン内でソフトウエア STOP モードに設定したあとの動作 147    |

| 6 - 4  | ハードウエア STOP モード解除後の状態 148                    |

| 7 - 1  | 転送の種類と転送対象の関係 156                            |

| 7 - 2  | ウエイト機能と転送対象の関係 156                           |

|        |                                              |

| 8 - 1  | 割り込み / 例外一覧 211                              |

|        |                                              |

| 0 _ 1  | テスト・モードの設定一瞥 235                             |

# 表の目次 (2/2)

## 表番号

タイトル , ページ

- 10-1 各動作モードでの端子状態 ... 245

- 10 2 IE 接続コネクタ(ターゲット・システム側)ピン機能 ... 250

## 第1章 概 説

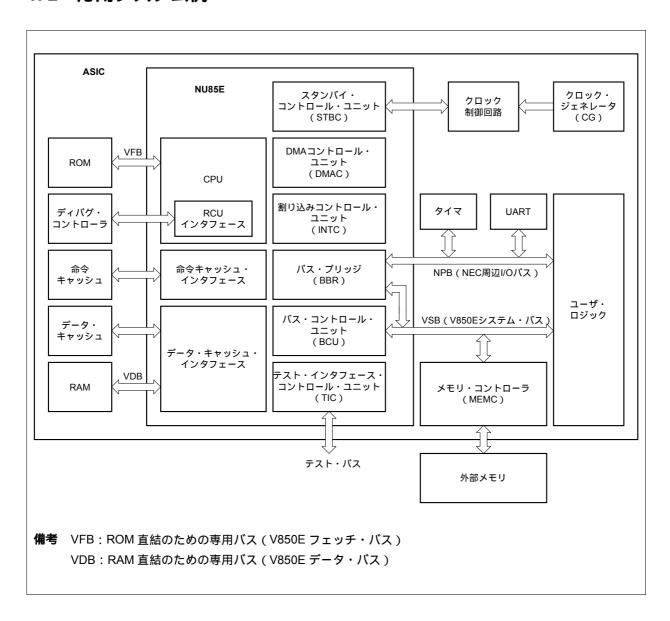

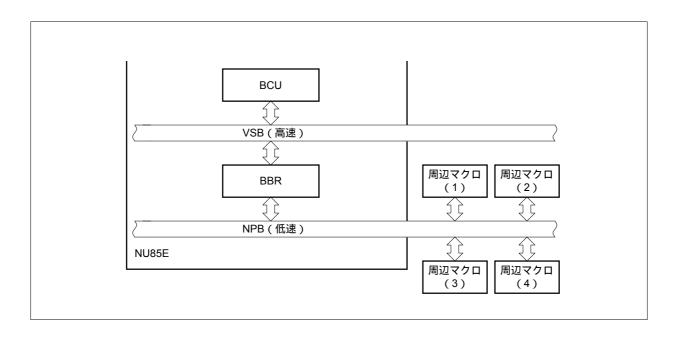

NU85E ファミリは,32/16 ビット RISC タイプの CPU「V850E1」と周辺 I/O を内蔵し,ASIC への組み込みを目的とした CPU コア群です。V850E1 は,RISC アーキテクチャをベースとし,5 段パイプラインの制御によりほとんどの命令を1クロックで実行します。また,NU85E ファミリは,高速な周辺 I/O と低速な周辺 I/O への接続を目的とした2種類の外部バス・インタフェースと ROM,RAM,命令キャッシュ,データ・キャッシュとのインタフェース機能を内蔵しています。本製品「NU85E」は,DMA コントローラ,割り込みコントローラなどの周辺 I/O を内蔵した CPU コアです。

## 1.1 概 要

#### (1) 「V850E1」CPU

5 段パイプライン方式を採用した RISC 型 CPU「V850E1」を搭載しています。2 バイト長の基本命令, 高級言語対応命令などにより, C コンパイラでのオブジェクト・コード効率を高めており, プログラム・ サイズのコンパクト化を実現します。

また,乗算処理の高速化のために,32 ビット×32 ビット演算が可能な高速ハードウエア乗算器を内蔵しています。

### (2) パス・インタフェース

周辺マクロ,ユーザ・ロジックなどの接続を目的とした次の2種類のバス・インタフェースを備えています。

- V850E システム・バス ( VSB )

- NEC 周辺 I/O バス (NPB)

VSB は , バス・マスタとして動作するマクロ ( DMAC, DSP など ) やメモリ・コントローラ ( MEMC ) などのシステム・クロックに同期して動作する高速なマクロへの接続を目的としたバスです。

NPB は,タイマやアシンクロナス・シリアル・インタフェース (UART) などのシステム・クロックに非同期で動作する比較的低速な周辺マクロへの接続を目的としたバスです。

また, ROM の直結が可能な V850E フェッチ・バス (VFB) と RAM の直結が可能な V850E データ・バス (VDB) も備えています。

さらに,命令キャッシュ,データ・キャッシュ,RCU(ラン・コントロール・ユニット)に対しては,専用のインタフェースを内蔵しているため,各マクロの直結が可能です。

#### (3) 内蔵周辺 I/O

DMA 転送を制御する DMA コントロール・ユニット(DMAC),割り込み要求を制御する割り込みコントロール・ユニット(INTC),パワー・セーブ機能を制御するスタンバイ・コントロール・ユニット (STBC)を内蔵しています。

## 1.2 応用システム例

注意 このユーザーズ・マニュアルでは, NU85Eに接続するメモリに関して次のように表記を統一しています。

● RAM : NU85E 直結の RAM (VDB に接続)● ROM : NU85E 直結の ROM (VFB に接続)

● 外部メモリ:メモリ・コントローラ (MEMC)を介して接続される RAM/ROM (VSB 経由で接続)

## 1.3 特 徵

• 命令数 83

• 汎用レジスタ 32 ビット×32 本

● 命令セット V850 CPU 上位互換

符号付き乗算(32 ビット×32 ビット→64 ビット)

飽和演算命令(オーバフロー/アンダフロー検出機能付き)

32 ビット・シフト命令:1クロック

ビット操作命令

ロング/ショート形式を持つロード/ストア命令

符号付きロード命令

● メモリ空間 プログラム領域:64M バイト・リニア

データ領域:4G バイト・リニア

メモリ・バンク分割機能: 2M, 4M, 8M バイト/バンク

• 外部バス・インタフェース

VSB ( V850E システム・バス )

- ・アドレス / データ分離バス (28 ビット・アドレス<sup>注</sup> / 32 ビット・データ・バス)

- ・データ入出力分離バス

- ・32/16/8 ビット・バス・サイジング機能

- ・バス・ホールド機能

- ・外部ウエイト機能

- ・エンディアン切り替え機能

NPB (NEC 周辺 I/O バス)

- ・アドレス / データ分離バス (14 ビット・アドレス / 16 ビット・データ・バス)

- ・データ入出力分離バス

- ・プログラマブル・ウエイト機能

- ・リトライ機能

注 バス・スレーブとして機能する場合は 14 ビット・アドレス・バス

• 割り込み/例外制御機能

ノンマスカブル割り込み:3要因

マスカブル割り込み:64 要因

例外:1要因

8 レベルの優先順位指定可能(マスカブル割り込み)

● DMA 制御機能 4 チャネル構成

転送単位:8ビット,16ビット,32ビット

最大転送回数:65536(2<sup>16</sup>)回

転送タイプ:フライバイ(1サイクル)転送,2サイクル転送

転送モード:シングル転送,シングルステップ転送,ライン転送,ブロック転送

ターミナル・カウント出力信号 (DMTCO3-DMTCO0)

• パワー・セーブ機能 HALT モード

ソフトウエア STOP モード ハードウエア STOP モード

● RCU <sup>注</sup>インタフェース機能

注 RCU (Run Control Unit): JTAG での通信やディバグ処理の実行を行う制御ユニット

## 1.4 シンボル図

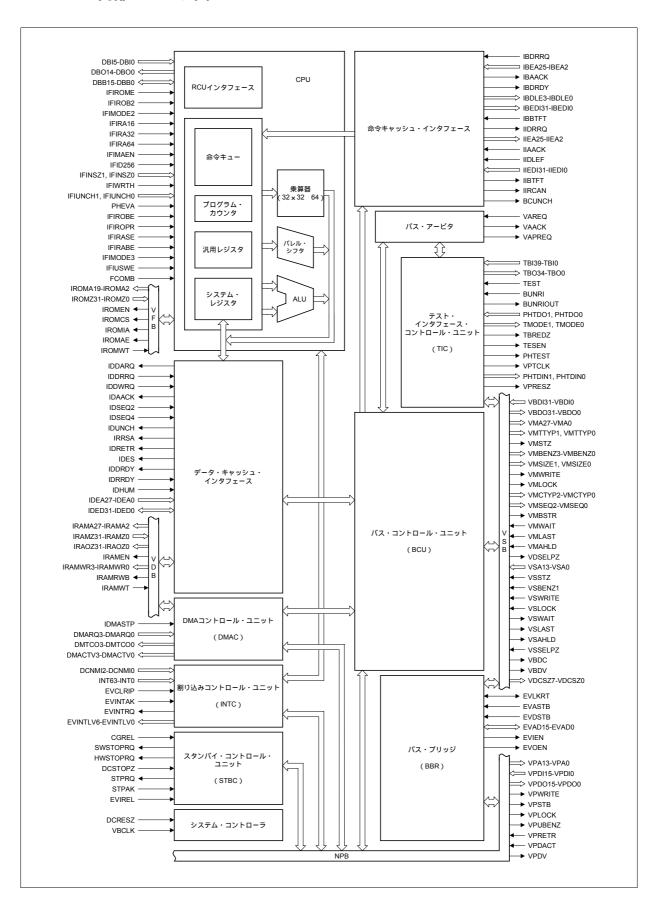

## 1.5 機能プロック構成

## 1.5.1 内部プロック図

## 1.5.2 内部ユニット

#### (1) CPU

アドレス計算,算術論理演算,データ転送などのほとんどの命令処理を 5 段パイプライン制御により 1 クロックで実行します。

32 ビット×32 ビット乗算の高速処理が可能なハードウエア乗算器,バレル・シフタなどの専用ハードウエアを内蔵し,複雑な命令処理の高速化を図っています。

また, RCU との接続を行うための RCU インタフェースを内蔵しています(第3章 CPU 参照)。

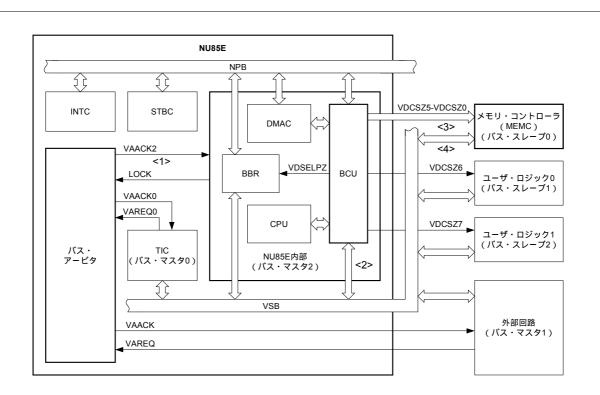

### (2) BCU

VSB 上のバス・マスタとして動作し、内蔵のバス・ブリッジ(BBR)、テスト・インタフェース・コントロール・ユニット(TIC)や、VSB に接続されたメモリ・コントローラ(MEMC)などの周辺マクロ (バス・スレーブ)を制御するバス・コントロール・ユニットです(第4章 BCU参照)。

#### (3) BBR

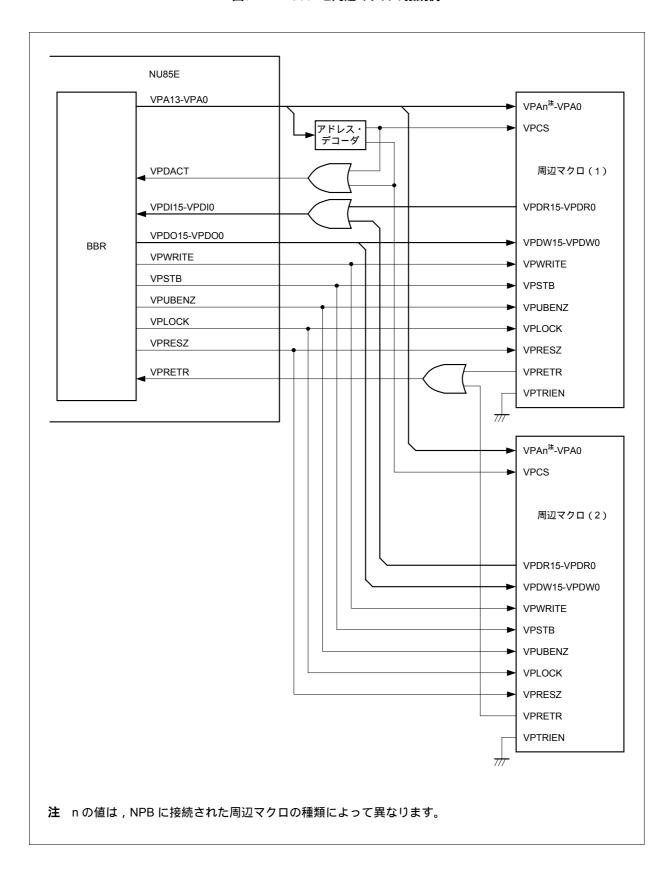

VSB 用の信号を NPB 用の信号に変換するバス・ブリッジです。

NPBに接続された周辺マクロに対して、ウエイト挿入機能、リトライ機能の設定を行います(第5章 BBR 参照)。

#### (4) STBC

パワー・セーブ機能(HALT モード,ソフトウエア STOP モード,ハードウエア STOP モード)実行時 に外部クロック・ジェネレータ(CG)を制御するスタンバイ・コントロール・ユニットです(**第6章** STBC 参照)。

### (5) DMAC

DMARQ3-DMARQ0 端子,またはソフトウエア・トリガによる DMA 転送要求に基づいて,メモリ $\leftrightarrow$ 周 辺マクロ間またはメモリ $\leftrightarrow$ メモリ間でのデータ転送を制御する 4 チャネルの DMA コントロール・ユニットです(第7章 DMAC 参照)。

### (6) INTC

各種割り込み要求を処理する割り込みコントロール・ユニットです(第8章 INTC 参照)。

## (7) TIC

テスト機能制御に使用するテスト・インタフェース・コントロール・ユニットです。テスト・モードに 設定されると,テスト用制御信号が有効になります(**第9章 テスト機能**参照)。

### (8) バス・アービタ

複数のバス・マスタからのバス制御要求を受けて、バス使用権の調停を行います。

# 1.6 NU85E と NB85E の機能上の主な違い

| 項目                    |                                       | NU85E                           | NB85E                           |  |

|-----------------------|---------------------------------------|---------------------------------|---------------------------------|--|

| VSB 用データ・バス(n = 31-0) |                                       | VBDIn (入力), VBDOn (出力)          | VBDn (入出力)                      |  |

| VSB 用マスタ / スレープ制御端子   |                                       | VMA27-VMA0(出力)                  | VBA27-VBA0(入出力)                 |  |

|                       |                                       | VSA13-VSA0(入力)                  |                                 |  |

|                       |                                       | VMTTYP1, VMTTYP0(出力)            | VBTTYP1, VBTTYP0 (入出力)          |  |

|                       |                                       | VMSTZ (出力)                      | VBSTZ (入出力)                     |  |

|                       |                                       | VSSTZ(入力)                       |                                 |  |

|                       |                                       | VMBENZ3-VMBENZ0(出力)             | VBBENZ3-VBBENZ0 (入出力)           |  |

|                       |                                       | VSBENZ1(入力)                     |                                 |  |

|                       |                                       | VMSIZE1, VMSIZE0 ( 出力 )         | VBSIZE1, VBSIZE0(入出力)           |  |

|                       |                                       | VMWRITE ( 出力 )                  | VBWRITE (入出力)                   |  |

|                       |                                       | VSWRITE (入力)                    |                                 |  |

|                       |                                       | VMLOCK ( 出力 )                   | VBLOCK (入出力)                    |  |

|                       |                                       | VSLOCK(入力)                      |                                 |  |

|                       |                                       | VMCTYP2-VMCTYP0(出力)             | VBCTYP2-VBCTYP0(入出力)            |  |

|                       |                                       | VMSEQ2-VMSEQ0(出力)               | VBSEQ2-VBSEQ0(入出力)              |  |

|                       |                                       | VMBSTR (出力)                     | VBBSTR (入出力)                    |  |

|                       |                                       | VMWAIT (入力)                     | VBWAIT(入出力)                     |  |

|                       |                                       | VSWAIT (出力)                     |                                 |  |

|                       |                                       | VMLAST(入力)                      | VBLAST (入出力)                    |  |

|                       |                                       | VSLAST (出力)                     |                                 |  |

|                       |                                       | VMAHLD(入力)                      | VBAHLD (入出力)                    |  |

|                       |                                       | VSAHLD (出力)                     |                                 |  |

|                       |                                       | VDSELPZ (出力)                    | VDSELPZ (入出力)                   |  |

|                       |                                       | VSSELPZ(入力)                     |                                 |  |

|                       |                                       | VDCSZ7-VDCSZ0(出力)               | VDCSZ7-VDCSZ0(入出力)              |  |

| NPB 用データ              | ・バス(n = 15-0)                         | VPDIn (入力), VPDOn (出力)          | VPDn (入出力)                      |  |

| NPB 用データと             | 出力バス制御出力端子                            | VPDV                            | (なし)                            |  |

| VSB 用データと             | 出力バス制御出力端子                            | VBDV                            | (なし)                            |  |

| バス使用権要求               | ····································· | VAPREQ                          | (なし)                            |  |

| テスト・モート               | ・ステータス出力端子                            | BUNRIOUT                        | (なし)                            |  |

| 入出力                   | VBDn ( n = 31-0 )                     | VBDIn, VBDOn                    | VBDn                            |  |

| タイミング                 | VxTTYPn ( n = 1, 0 )                  | VMTTYPn                         | VBTTYPn                         |  |

|                       | VxWAIT, VxLAST,                       | VMWAIT, VMLAST, VMAHLD, VSWAIT, | VBWAIT, VBLAST, VBAHLD          |  |

|                       | VxAHLD                                | VSLAST, VSAHLD                  |                                 |  |

| リセット時,                | VxA27-VxA0, VxSIZE1,                  | ロウ・レベル出力                        | 不定                              |  |

| アイドル時の                | VxSIZE0, VxSEQ2-                      | ( VMA27-VMA0, VMSIZE1, VMSIZE0, | ( VBA27-VBA0, VBSIZE1, VBSIZE0, |  |

| 端子状態                  | VxSEQ0, VBD31-VBD0                    | VMSEQ2-VMSEQ0, VBDO31-VBDO0)    | VBSEQ2-VBSEQ0, VBD31-VBD0)      |  |

# 第2章 端子機能

## 2.1 端子機能一覧

(1/4)

| 端子名     |                           | 入出力 | 機能                              |

|---------|---------------------------|-----|---------------------------------|

| NPB 用端子 | VPA13-VPA0                | 出力  | NPB に接続された周辺マクロへのアドレス出力         |

|         | VPDI15-VPDI0 <sup>注</sup> | 入力  | NPB に接続された周辺マクロからのデータ入力         |

|         | VPDO15-VPDO0              | 出力  | NPB に接続された周辺マクロへのデータ出力          |

|         | VPWRITE                   | 出力  | ライト・アクセス・ストローブ出力                |

|         | VPSTB                     | 出力  | データ・ストローブ出力                     |

|         | VPLOCK                    | 出力  | バス・ロック出力                        |

|         | VPUBENZ                   | 出力  | 上位バイト・イネーブル出力                   |

|         | VPRETR <sup>注</sup>       | 入力  | NPB に接続された周辺マクロからのリトライ要求入力      |

|         | VPDACT                    | 入力  | 外部アドレス・デコーダからのアクティブ・レベル入力       |

|         | VPDV                      | 出力  | データ出力(VPDO15-VPDO0)制御出力         |

| VSB 用端子 | VAREQ                     | 入力  | 外部バス・マスタからのバス使用権要求入力            |

|         | VAACK                     | 出力  | バス使用権アクノリッジ出力                   |

|         | VAPREQ                    | 出力  | 内部バス・マスタ(CPU, DMAC)からのバス使用権要求出力 |

|         | VBDI31-VBDI0              | 入力  | VSB に接続されたマクロからのデータ入力           |

|         | VBDO31-VBDO0              | 出力  | VSB に接続されたマクロへのデータ出力            |

|         | VMA27-VMA0                | 出力  | VSB に接続されたマクロへのアドレス出力           |

|         | VMTTYP1, VMTTYP0          | 出力  | バス転送タイプ出力                       |

|         | VMSTZ                     | 出力  | 転送スタート出力                        |

|         | VMBENZ3-VMBENZ0           | 出力  | バイト・イネーブル出力                     |

|         | VMSIZE1, VMSIZE0          | 出力  | 転送サイズ出力                         |

|         | VMWRITE                   | 出力  | リード / ライト・ステータス出力               |

|         | VMLOCK                    | 出力  | バス・ロック出力                        |

|         | VMCTYP2-VMCTYP0           | 出力  | バス・サイクル・ステータス出力                 |

|         | VMSEQ2-VMSEQ0             | 出力  | シーケンシャル・ステータス出力                 |

|         | VMBSTR                    | 出力  | バースト・リード・ステータス出力                |

|         | VMWAIT                    | 入力  | ウエイト・レスポンス入力                    |

|         | VMLAST                    | 入力  | ラスト・レスポンス入力                     |

|         | VMAHLD                    | 入力  | アドレス・ホールド・レスポンス入力               |

|         | VDSELPZ                   | 出力  | 周辺 I/O 領域アクセス・ステータス出力           |

|         | VSA13-VSA0                | 入力  | VSB に接続されたマクロからのアドレス入力          |

|         | VSSTZ                     | 入力  | 転送スタート入力                        |

|         | VSBENZ1                   | 入力  | バイト・イネーブル入力                     |

|         | VSWRITE                   | 入力  | リード / ライト・ステータス入力               |

注 内部にバス・ホルダが接続されています。

(2/4)

| لْا<br>لا | 端子名             | 入出力 | 機能                                  |

|-----------|-----------------|-----|-------------------------------------|

| VSB 用端子   | VSLOCK          | 入力  | バス・ロック入力                            |

|           | VSWAIT          | 出力  | ウエイト・レスポンス出力                        |

|           | VSLAST          | 出力  | ラスト・レスポンス出力                         |

|           | VSAHLD          | 出力  | アドレス・ホールド・レスポンス出力                   |

|           | VSSELPZ         | 入力  | 周辺 I/O 領域アクセス・ステータス入力               |

|           | VBDC            | 出力  | データ入力(VBDI31-VBDI0)制御出力             |

|           | VBDV            | 出力  | データ出力(VBDO31-VBDO0)制御出力             |

|           | VDCSZ7-VDCSZ0   | 出力  | チップ・セレクト出力                          |

| システム      | DCRESZ          | 入力  | システム・リセット入力                         |

| 制御用端子     | VBCLK           | 入力  | 内部システム・クロック入力                       |

|           | CGREL           | 入力  | クロック・ジェネレータ・リリース入力                  |

|           | SWSTOPRQ        | 出力  | クロック・ジェネレータへのソフトウエア STOP モード要求出力    |

|           | HWSTOPRQ        | 出力  | クロック・ジェネレータへのハードウエア STOP モード要求出力    |

|           | DCSTOPZ         | 入力  | ハードウエア STOP モード要求入力                 |

|           | STPRQ           | 出力  | MEMC へのハードウエア / ソフトウエア STOP モード要求出力 |

|           | STPAK           | 入力  | MEMC の STPRQ 入力に対するアクノリッジ入力         |

| DMAC 用端子  | IDMASTP         | 入力  | DMA 転送終了入力                          |

|           | DMARQ3-DMARQ0   | 入力  | DMA 転送要求入力                          |

|           | DMTCO3-DMTCO0   | 出力  | ターミナル・カウント(DMA 転送完了)出力              |

|           | DMACTV3-DMACTV0 | 出力  | DMA アクノリッジ出力                        |

| INTC 用端子  | DCNMI2-DCNMI0   | 入力  | ノンマスカブル割り込み要求(NMI)入力                |

|           | INT63-INT0      | 入力  | マスカブル割り込み要求入力                       |

| VFB 用端子   | IROMA19-IROMA2  | 出力  | ROM 用アドレス出力                         |

|           | IROMZ31-IROMZ0  | 入力  | ROM 用データ入力                          |

|           | IROMEN          | 出力  | ROM 用アクセス・イネーブル出力                   |

|           | IROMWT          | 入力  | ROM 用ウエイト入力                         |

|           | IROMCS          | 出力  | NEC の予約端子(オープンにしてください)              |

|           | IROMIA          | 出力  |                                     |

|           | IROMAE          | 出力  |                                     |

| VDB 用端子   | IRAMA27-IRAMA2  | 出力  | RAM 用アドレス出力                         |

|           | IRAMZ31-IRAMZ0  | 入力  | RAM 用データ入力                          |

|           | IRAOZ31-IRAOZ0  | 出力  | RAM 用データ出力                          |

|           | IRAMEN          | 出力  | RAM 用アクセス・イネーブル出力                   |

|           | IRAMWR3-IRAMWR0 | 出力  | RAM 用ライト・イネーブル出力                    |

|           | IRAMRWB         | 出力  | RAM 用リード / ライト・ステータス出力              |

|           | IRAMWT          | 入力  | RAM 用ウエイト入力                         |

| 命令キャッシュ用  | IBDRRQ          | 入力  | 命令キャッシュからのフェッチ要求入力                  |

| 端子        | IBEA25-IBEA2    | 入力  | 命令キャッシュからのフェッチ・アドレス入力               |

|           | IBAACK          | 出力  | 命令キャッシュへのアドレス・アクノリッジ出力              |

|           | IBDRDY          | 出力  | 命令キャッシュへのデータ・レディ出力                  |

(3/4)

| 端子名      |                            | 入出力 | 機 能                            |

|----------|----------------------------|-----|--------------------------------|

| 命令キャッシュ用 | IBDLE3-IBDLE0              | 出力  | 命令キャッシュへのデータ・ラッチ・イネーブル出力       |

| 端子       | IBEDI31-IBEDI0             | 出力  | 命令キャッシュへのデータ出力                 |

|          | IIDRRQ                     | 出力  | 命令キャッシュへのフェッチ要求出力              |

|          | IIEA25-IIEA2               | 出力  | 命令キャッシュへのフェッチ・アドレス出力           |

|          | IIAACK                     | 入力  | 命令キャッシュからのアドレス・アクノリッジ入力        |

|          | IIDLEF                     | 入力  | 命令キャッシュからのデータ・ラッチ・イネーブル入力      |

|          | IIEDI31-IIEDI0             | 入力  | 命令キャッシュからのデータ入力                |

|          | IIBTFT                     | 出力  | 命令キャッシュへのブランチ・ターゲット・フェッチ・ステータス |

|          |                            |     | 出力                             |

|          | IIRCAN                     | 出力  | 命令キャッシュへのコード・キャンセル・ステータス出力     |

|          | BCUNCH                     | 出力  | 命令キャッシュへのアンキャッシュ・ステータス出力       |

|          | IBBTFT                     | 入力  | NEC の予約端子(ロウ・レベルを入力してください)     |

| データ・     | IDDARQ                     | 出力  | データ・キャッシュへのリード / ライト・アクセス要求出力  |

| キャッシュ用端子 | IDAACK                     | 出力  | アクノリッジ出力                       |

|          | IDDRRQ                     | 入力  | BCU への VSB リード・オペレーション要求入力     |

|          | IDDWRQ                     | 入力  | BCU への VSB ライト・オペレーション要求入力     |

|          | IDSEQ4                     | 入力  | リード/ライト動作タイプ設定入力               |

|          | IDSEQ2                     | 入力  | リード/ライト動作タイプ設定入力               |

|          | IRRSA                      | 出力  | VDB ホールド・ステータス出力               |

|          | IDRETR                     | 出力  | リード・リトライ要求出力                   |

|          | IDUNCH                     | 出力  | アンキャッシュ・ステータス出力                |

|          | IDDRDY                     | 出力  | リード・データ・レディ出力                  |

|          | IDRRDY                     | 入力  | データ・キャッシュからのリード・データ・レディ入力      |

|          | IDHUM                      | 入力  | ヒット・アンダ・ミスヒット・リード入力            |

|          | IDEA27-IDEA0               | 入力  | アドレス入力                         |

|          | IDED31-IDED0 <sup>注1</sup> | 入出力 | データ入出力                         |

|          | IDES                       | 出力  | NEC の予約端子 <sup>注2</sup>        |

| RCU 用端子  | DBI5-DBI0                  | 入力  | ディバグ制御入力                       |

|          | DBO14-DBO0                 | 出力  | ディバグ制御出力                       |

|          | DBB15-DBB0 <sup>注1</sup>   | 入出力 | ディバグ制御入出力                      |

| 周辺エバチップ・ | EVASTB                     | 入力  | アドレス・ストロープ入力                   |

| モード用端子   | EVDSTB                     | 入力  | データ・ストローブ入力                    |

|          | EVAD15-EVAD0 <sup>注1</sup> | 入出力 | アドレス / データ入出力                  |

|          | EVIEN                      | 出力  | EVADn 入力イネーブル出力(n = 15-0)      |

|          | EVOEN                      | 出力  | EVADn 出力イネーブル出力(n = 15-0)      |

|          | EVLKRT <sup>注1</sup>       | 入出力 | ロック/リトライ入出力                    |

|          | EVIREL                     | 入力  | スタンバイ・リリース入力                   |

## 注1. 内部にバス・ホルダが接続されています。

2. データ・キャッシュを使用するときは,必ずデータ・キャッシュの IDES 端子に接続してください。未使用時はオープンにしてください。

(4/4)

| 端子名      |                             | 入出力 | 機能                               |

|----------|-----------------------------|-----|----------------------------------|

| 周辺エバチップ・ | EVCLRIP                     | 入力  | ISPR クリア入力                       |

| モード用端子   | EVINTAK                     | 入力  | 割り込みアクノリッジ入力                     |

|          | EVINTRQ                     | 出力  | 割り込み要求出力                         |

|          | EVINTLV6-EVINTLV0           | 出力  | 割り込みベクタ出力                        |

| 動作モード設定用 | IFIROME                     | 入力  | ROM マッピング・イネーブル入力                |

| 端子       | IFIROB2                     | 入力  | ROM 領域の配置設定入力                    |

|          | IFIRA64                     | 入力  | RAM 領域サイズ選択入力                    |

|          | IFIRA32                     | 入力  | RAM 領域サイズ選択入力                    |

|          | IFIRA16                     | 入力  | RAM 領域サイズ選択入力                    |

|          | IFIMAEN                     | 入力  | ミス・アライン・アクセス設定入力                 |

|          | IFID256                     | 入力  | データ領域設定入力                        |

|          | IFINSZ1, IFINSZ0            | 入力  | VSB データ・バス・サイズ(初期値)選択入力          |

|          | IFIWRTH                     | 入力  | データ・キャッシュのライト・バック / ライト・スルー・モード選 |

|          |                             |     | 択入力                              |

|          | IFIUNCH1                    | 入力  | データ・キャッシュ設定入力                    |

|          | IFIUNCH0                    | 入力  | 命令キャッシュ設定入力                      |

|          | PHEVA                       | 入力  | 周辺エバチップ・モード設定入力                  |

|          | IFIROBE                     | 入力  | NEC の予約端子(ロウ・レベルを入力してください)       |

|          | IFIROPR                     | 入力  |                                  |

|          | IFIRASE                     | 入力  |                                  |

|          | IFIRABE                     | 入力  |                                  |

|          | IFIMODE3                    | 入力  |                                  |

|          | IFIMODE2                    | 入力  |                                  |

|          | IFIUSWE                     | 入力  |                                  |

|          | FCOMB                       | 入力  |                                  |

| テスト・モード用 | TBI39-TBI0                  | 入力  | 入力テスト・バス                         |

| 端子       | TBO34-TBO0                  | 出力  | 出力テスト・バス                         |

|          | TEST                        | 入力  | テスト・バス・コントロール入力                  |

|          | BUNRI                       | 入力  | ノーマル / テスト・モード選択入力               |

|          | BUNRIOUT                    | 出力  | テスト・モード・ステータス出力                  |

|          | PHTDO1, PHTDO0 <sup>注</sup> | 入力  | 周辺マクロ・テスト入力                      |

|          | TESEN                       | 出力  | 周辺マクロ・テスト・イネーブル出力                |

|          | VPTCLK                      | 出力  | 周辺マクロ・テスト用クロック出力                 |

|          | PHTDIN1, PHTDIN0            | 出力  | 周辺マクロ・テスト出力                      |

|          | VPRESZ                      | 出力  | 周辺マクロ・リセット出力                     |

|          | PHTEST                      | 出力  | 周辺テスト・モード・ステータス出力                |

|          | TMODE1                      | 出力  | テスト・モード選択出力                      |

|          | TMODE0                      | 出力  | NEC の予約端子(オープンにしてください)           |

| 1        | TBREDZ                      | 出力  |                                  |

注 内部にバス・ホルダが接続されています。

## 2.2 端子機能の説明

## 2. 2. 1 NPB 用端子

#### (1) VPA13-VPA0(出力)

NPB に接続された周辺マクロへのアドレス出力端子です。下位 14 ビットを指定します。

## (2) VPDI15-VPDI0(入力)

NPB に接続された周辺マクロからのデータ入力バスです。

### (3) VPDO15-VPDO0(出力)

NPB に接続された周辺マクロへのデータ出力バスです。

#### (4) VPWRITE (出力)

VPDO15-VPDO0 信号のライト・アクセス・ストローブ出力端子です。 ライト時にハイ・レベルを出力します。

#### (5) VPSTB(出力)

データ・ストローブ出力端子です。

## (6) VPLOCK(出力)

バス・ロック出力端子です。割り込み制御レジスタ(PICn)へのリード・モディファイ・ライト・アクセス実行の途中で割り込み要求が発生した場合に、この割り込み要求が消失してしまうのを防ぐために出力します。

リード・モディファイ・ライト・アクセス時にハイ・レベルを出力します。

この信号がハイ・レベルを出力している間は、割り込み要求が発生しても、PICn レジスタの PIFn フラ グへの転送は行いません(n=0-63)。

#### (7) VPUBENZ(出力)

上位バイト・イネーブル出力端子です。ハーフワード・データ・アクセス時,または奇数アドレスへの バイト・データ・アクセス時にロウ・レベルを出力します。

偶数アドレスへのバイト・アクセス時は, ハイ・レベルを出力します。

### (8) VPRETR(入力)

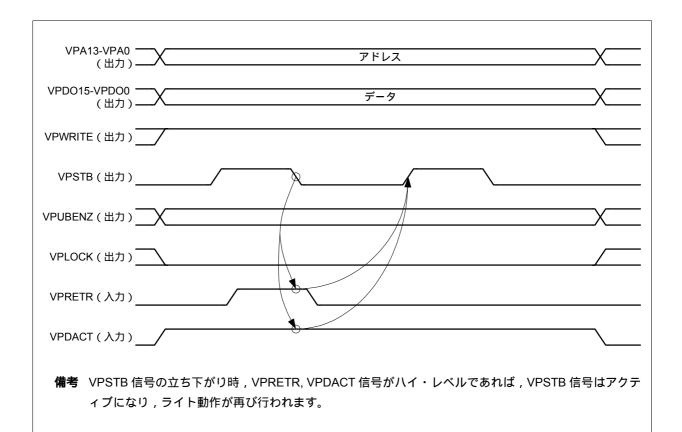

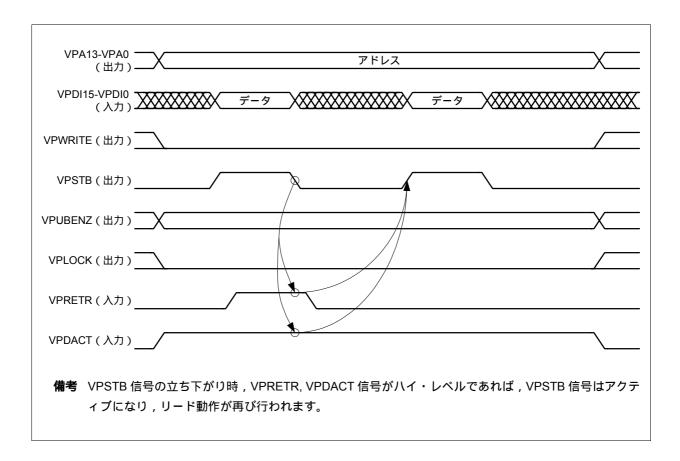

NPB に接続された周辺マクロからのリトライ要求入力端子です。VPSTB 信号の立ち下がり時に,この端子と VPDACT 端子にハイ・レベルが入力されているとリード/ライト動作を再び行います。

## (9) VPDACT (入力)

外部アドレス・デコーダからの入力端子で、リトライ機能を有効にするための端子です。

ハイ・レベルを入力するとリトライ機能が有効となります。

ロウ・レベルが入力されていると, VPRETR 入力によるリトライ要求があっても無視されます。

#### (10) VPDV (出力)

データ出力(VPDO15-VPDO0)制御信号の出力端子です。ライト時にハイ・レベルを出力します。双方向データ・バスを構成する場合に、データ・バスに接続された3ステート・バッファのイネーブル端子に接続してデータの出力制御を行います。

## 2. 2. 2 VSB 用端子

### (1) VAREQ(入力)

外部バス・マスタからのバスの使用権要求を入力する端子です。

#### (2) VAACK (出力)

外部バス・マスタからのバス使用権要求信号(VAREQ)を受け付けたことを示す出力端子です。

#### (3) VAPREQ(出力)

内部バス・マスタ(CPU, DMAC)から外部バス・マスタへのバス使用権要求を出力する端子です。 外部にバス・マスタおよびバス・アービタが存在する場合に使用し、外部のバス・アービタに対して出力します。バス使用権要求が発生すればアクティブ(1)になり、その要求に応じたバス・サイクルが発生した時点でインアクティブ(0)になります。 CPU サイクル中にアクティブ(1)になれば DMA からの要求があることを示し、DMA サイクル中にアクティブ(1)になれば CPU からの要求があることを示します。

## (4) VBDI31-VBDI0 (入力)

VSB に接続されたマクロ用のデータ入力バスです。

### (5) VBDO31-VBDO0(出力)

VSB に接続されたマクロ用のデータ出力バスです。

#### (6) VMA27-VMA0(出力), VSA13-VSA0(入力)

VSB に接続されたマクロ用のアドレス・バスです。

NU85E がバス使用権を持つ場合は VMA27-VMA0 端子を , バス・スレーブとして動作する場合は VSA13-VSA0 端子を使用します。

## (7) VMTTYP1, VMTTYP0(出力)

NU85E がバス使用権を持つ場合に,バス転送タイプを出力する端子です。

VMTTYP1

VMTTYP0

転送タイプ

0

0

アドレス・オンリー転送(データ処理を行わない転送)

1

0

ノンシーケンシャル転送(シングル転送,またはパースト転送)

1

1

シーケンシャル転送 (現在転送されているアドレスが前回転送時のアドレスに関係する転送)

0

1

(将来の機能拡張のための予約)

表2 - 1 VMTTYP1, VMTTYP0信号

備考 0:ロウ・レベル 1:ハイ・レベル

### (8) VMSTZ(出力), VSSTZ(入力)

転送開始を示すロウ・レベル・アクティブの端子です。

NU85E がバス使用権を持つ場合は VMSTZ 端子を,バス・スレーブとして動作する場合は VSSTZ 端子を使用します。

### (9) VMBENZ3-VMBENZ0(出力), VSBENZ1(入力)

データ・バス(VBDI31-VBDI0, VBDO31-VBDO0)を 4 分割したうちの有効となるバイト・データを示すロウ・レベル・アクティブの端子です。

NU85E がバス使用権を持つ場合は VMBENZ3-VMBENZ0 端子を,バス・スレーブとして動作する場合はバス・ブリッジ (BBR) が VPUBENZ 信号を生成するために VSBENZ1 端子を使用します。

| アクティブ(ロウ・レベル)となる信号 | 有効バイト・データ                    |

|--------------------|------------------------------|

| VMBENZ3            | VBDI31-VBDI24, VBDO31-VBDO24 |

| VMBENZ2            | VBDI23-VBDI16, VBDO23-VBDO16 |

| VMBENZ1, VSBENZ1   | VBDI15-VBDI8, VBDO15-VBDO8   |

| VMBENZ0            | VBDI7-VBDI0, VBDO7-VBDO0     |

表2 - 2 VMBENZ3-VMBENZ0, VSBENZ1信号

## (10) VMSIZE1, VMSIZE0(出力)

NU85E がバス使用権を持つ場合に,データ転送サイズを出力する端子です。

|         |         | - , <b>-</b>    |

|---------|---------|-----------------|

| VMSIZE1 | VMSIZE0 | データ転送サイズ        |

| 0       | 0       | バイト(8ビット)       |

| 0       | 1       | ハーフワード(16 ビット)  |

| 1       | 0       | ワード (32 ビット)    |

| 1       | 1       | (将来の機能拡張のための予約) |

表2-3 VMSIZE1, VMSIZE0信号

備考 0:ロウ・レベル 1:ハイ・レベル

### (11) VMWRITE (出力), VSWRITE (入力)

データ転送方向(リード/ライト・ステータス)を示す端子です。ライト・アクセス時にハイ・レベル になります。

NU85E がバス使用権を持つ場合は VMWRITE 端子を,バス・スレーブとして動作する場合は VSWRITE 端子を使用します。

## (12) VMLOCK (出力), VSLOCK (入力)

バス使用権を保持するための端子です。現在の転送と次の転送の間に,ほかのバス・マスタからのアクセスによる中断を禁止するために使用します。

NU85E がバス使用権を持つ場合は VMLOCK 端子を,バス・スレーブとして動作する場合は VSLOCK 端子を使用します。

#### (13) VMCTYP2-VMCTYP0(出力)

NU85E がバス使用権を持つ場合に,現在のバス・サイクルの状態を出力する端子です。

表2-4 VMCTYP2-VMCTYP0信号

| VMCTYP2 | VMCTYP1 | VMCTYP0 | バス・サイクルの状態                |

|---------|---------|---------|---------------------------|

| 0       | 0       | 0       | オペコード・フェッチ                |

| 0       | 0       | 1       | データ・アクセス                  |

| 0       | 1       | 0       | ミス・アライン・アクセス <sup>±</sup> |

| 0       | 1       | 1       | リード・モディファイ・ライト・アクセス       |

| 1       | 0       | 0       | 分岐命令による飛び先アドレスのオペコード・フェッチ |

| 1       | 1       | 0       | DMA の 2 サイクル転送            |

| 1       | 1       | 1       | DMA のフライバイ転送              |

| 1       | 0       | 1       | (将来の機能拡張のための予約)           |

注 IFIMAEN 端子にハイ・レベルが入力されている(ミス・アライン・アクセス許可)とき だけ出力されます。

備考 0:ロウ・レベル 1:ハイ・レベル

## (14) VMSEQ2-VMSEQ0(出力)

NU85E がバス使用権を持つ場合に,バースト転送時の転送サイズを示すシーケンシャル・ステータスを出力する端子です。

バースト転送の開始時には「バースト転送の長さ」を,バースト転送時には「連続」を,バースト転送の最後には「シングル転送」を示します。

次のような場合には, VSB はバースト転送となり, シーケンシャル・ステータスは「連続」を示します。

- VSB が 8 ビット・バス幅で,16/32 ビット・データ転送をしたとき

- VSB が 16 ビット・バス幅で, 32 ビット・データ転送をしたとき

- 命令 / データ・キャッシュからのリフィル

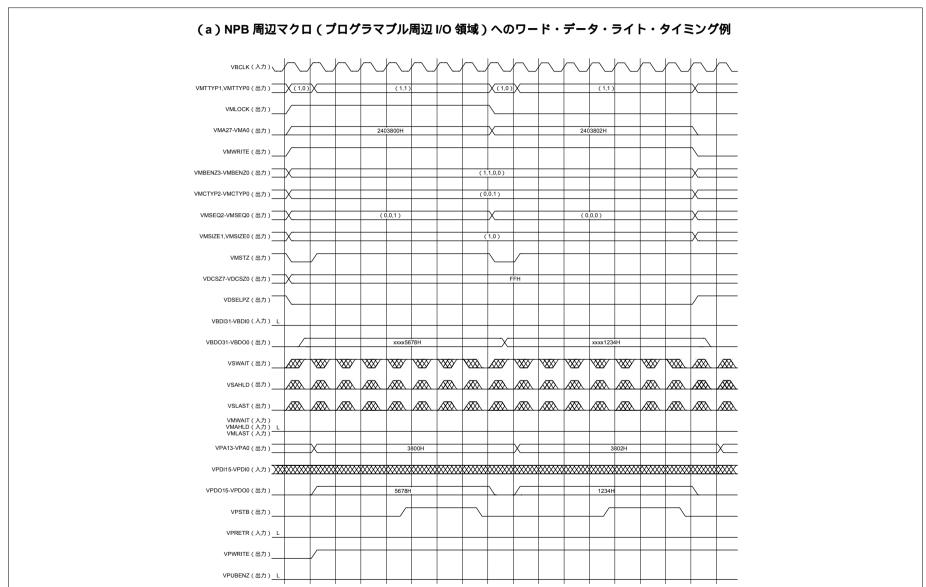

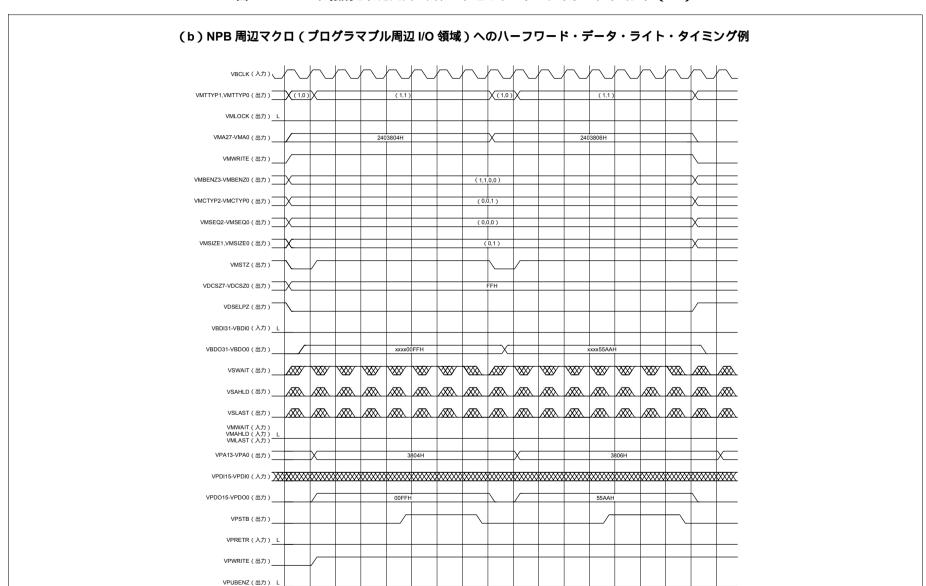

- NPB (16 ビット・データ・バス幅)に接続した周辺マクロへの32 ビット・データ転送

表2-5 VMSEQ2-VMSEQ0信号

| VMSEQ2 | VMSEQ1 | VMSEQ0 | シーケンシャル・ステータス                                     |

|--------|--------|--------|---------------------------------------------------|

| 0      | 0      | 0      | シングル転送                                            |

| 0      | 0      | 1      | 連続 ( 次回の転送アドレスは現在の転送アドレスに関係することを示す ) <sup>注</sup> |

| 0      | 1      | 0      | 連続4回 (バースト転送の長さ:4)                                |

| 0      | 1      | 1      | 連続8回 ( ":8)                                       |

| 1      | 0      | 0      | 連続 16 回 ( ": 16)                                  |

| 1      | 0      | 1      | 連続 32 回 ( ": 32 )                                 |

| 1      | 1      | 0      | 連続 64 回 ( ": 64)                                  |

| 1      | 1      | 1      | 連続 128 回( ": 128)                                 |

注 連続2回, または連続4,8,16,32,64,128回転送の途中で出力されます。

備考 0:ロウ・レベル 1:ハイ・レベル

#### (15) VMBSTR (出力)

NU85E がバス使用権を持ち、外部メモリとして接続された ROM (VSB 経由でアクセス)を使用する場合に、現在の転送が外部 ROM からのオペコード・フェッチであることを示すバースト・リード・ステータスを出力する端子です。アドレス・バスと同じタイミングで動作します。

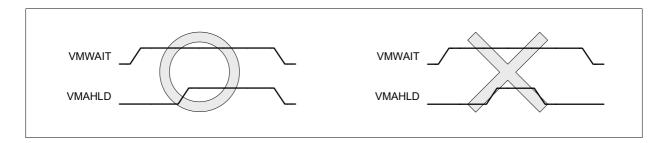

### (16) VMWAIT (入力), VSWAIT (出力)

ウエイト・レスポンス端子です。

選択されたバス・スレーブがデータ出力の準備を完了していないため、さらにバス・サイクルを要求する場合にバス・マスタに対して出力します。この信号がハイ・レベルになると、バス・サイクルはウエイト状態に移行します。

NU85E がバス使用権を持つ場合は VMWAIT 端子を,バス・スレーブとして動作する場合は VSWAIT 端子を使用します。

なお, NU85Eにメモリ・コントローラ (MEMC)を接続している場合は,必ず2クロック以上のアクセス・サイクルになるため, VSB サイクルが発生している間, MEMC から NU85E の VMWAIT 端子に対してハイ・レベルが出力されます。

#### (17) VMLAST (入力), VSLAST (出力)

ラスト・レスポンス端子です。バス・デコーダが、デコード・サイクルを必要とする場合に使用します。 外部に複数のスレーブ・デバイスが接続され、スレーブ選択のためのバス・デコーダを追加しているシステムの場合、通常、バス・スレーブ選択のためのデコードはノンシーケンシャル転送の間に行います。 そのため、バースト転送などのシーケンシャル転送の間にスレーブ・デバイスを変更しようとしても、スレーブ選択のためのデコード・サイクルは発行できません。

このような場合,スレーブ・デバイスはラスト・レスポンスを出力し,スレーブ選択信号が変化することをバス・マスタに伝えます。バス・マスタは,スレーブ・デバイスからのラスト・レスポンスがあると次のバス・サイクルをノンシーケンシャル転送にして,デコード・サイクルの発行を可能にします。

NU85E がバス・マスタとして動作する場合は VMLAST 端子を,バス・スレーブとして動作する場合は VSLAST 端子を使用します。ただし, VSLAST 端子はロウ・レベル固定出力で,アクティブになることは ありません。

### (18) VMAHLD(入力), VSAHLD(出力)

アドレス・ホールド・レスポンス端子です。

選択されたバス・スレーブがデータ出力の準備を完了している状態で,さらにバス・サイクルを要求する場合にバス・マスタに対して出力します。この信号と VxWAIT 信号がハイ・レベルになると,バス・サイクルはアドレス・ホールド状態に移行します。

アドレス・ホールド状態では,データのリード/ライト・サイクルの途中でも,そのデータに対するアドレスが変化しないため,アドレスをラッチする必要がなく,回路を簡素化することができます。

NU85E がバス使用権を持つ場合は VMAHLD 端子を,バス・スレーブとして動作する場合は VSAHLD 端子を使用します。ただし, VSAHLD 端子はロウ・レベル固定出力で,アクティブになることはありません。

また, NU85Eにメモリ・コントローラ (MEMC)を接続している場合, アイドル・ステート挿入時に MEMC から NU85Eに対してハイ・レベルが出力されます。

#### (19) VDSELPZ (出力), VSSELPZ (入力)

バス・マスタが,周辺 I/O 領域,プログラマブル周辺 I/O 領域をアクセスしているときに,バス・スレーブに対してロウ・レベルを出力する端子です。

NU85E がバス使用権を持つ場合は VDSELPZ 端子を,バス・スレーブとして動作する場合は VSSELPZ 端子を使用します。

## (20) VBDC (出力)

データ入力 (VBDI31-VBDI0)制御信号の出力端子です。リード・サイクル時,および外部メモリから I/O への DMA フライバイ転送時にハイ・レベルを出力します。I/O 分離データ・バスと双方向データ・バスを持つバス・スレーブを接続する場合に,データ・バスに接続された3ステート・バッファのイネーブル端子に接続し,データの入力制御を行います。

#### (21) VBDV (出力)

データ出力 (VBDO31-VBDO0) 制御信号の出力端子です。ライト・サイクル時,および I/O から外部 メモリへの DMA フライバイ転送時にハイ・レベルを出力します。双方向データ・バスを構成する場合に,データ・バスに接続された 3 ステート・バッファのイネーブル端子に接続し,データの出力制御を行います。

### (22) VDCSZ7-VDCSZ0(出力)

ロウ・レベル・アクティブのチップ・セレクト出力端子です。詳細については, **4.3 プログラマブ ル・チップ・セレクト機能**を参照してください。

# 2.2.3 システム制御用端子

## (1) DCRESZ(入力)

クロック同期式のシステム・リセット入力端子です。

この端子にロウ・レベルが入力されてから安定した入力クロックの立ち上がりエッジを5回検出すると,端子状態と内部信号は完全に初期化されます(内部信号および各端子の状態が確定するまでに,最も時間がかかる端子で5クロックになります。ノイズ除去は行っていません)。また,ロウ・レベルからハイ・レベルに立ち上がったあと,入力クロックの立ち上がりエッジを4回検出するとパイプラインがクリアされ,メモリの0番地からプログラム実行を開始します。

通常のイニシャライズ/スタートのほかに,パワー・セーブ機能の解除にも使用されます。

注意 DCRESZ 信号は, VBCLK 信号に対するセットアップ / ホールド時間を満たすように入力してください。

#### 図2 - 1 DCRESZ信号の受け付け

NB85E901 を接続して、システム・リセットにより VBCLK の発振を停止させる場合、システム・リセットがロウ・レベルになってから VBCLK を 5 クロック以上入力して、CPU 関係の端子状態と内部信号を完全に初期化してから VBCLK の発振を停止してください。この制限事項を守らない場合は、ディバッガが正常に起動しない可能性があります。

図2-2 システム・リセットによりVBCLKの発振を停止させる場合

# (2) VBCLK (入力)

内部システム・クロック用の外部クロック入力端子です。外部クロック制御回路から 50%デューティの 安定したクロックを入力します。

## (3) CGREL (入力)

外部クロック・ジェネレータ(CG)用のリリース入力端子です。STOP モード解除後,発振安定時間を確保したあと,VBCLK入力開始時にアクティブ・レベル(ハイ・レベル)を1クロック以上入力します(CGREL入力は,VBCLK入力と同時である必要はありません)。

#### (4) SWSTOPRQ(出力)

外部クロック・ジェネレータ(CG)へのソフトウエア STOP モード要求出力端子です。ソフトウエア STOP モードが設定されるとハイ・レベルを出力します。

この信号を使用して CG からの VBCLK 入力を停止します。ソフトウエア STOP モードが解除されると

ロウ・レベルを出力します。

#### (5) HWSTOPRQ(出力)

外部クロック・ジェネレータ(CG)へのハードウエア STOP モード要求出力端子です。DCSTOPZ 入力によりハードウエア STOP モードが設定されるとハイ・レベルを出力します。

この信号を使用して CG からの VBCLK 入力を停止します。ハードウエア STOP モードが解除されるとロウ・レベルを出力します。

## (6) DCSTOPZ(入力)

ハードウエア STOP モード要求入力端子です。ロウ・レベルを入力すると,ハードウエア STOP モードに設定されます。

### (7) STPRQ(出力)

メモリ・コントローラ (MEMC) へのハードウエア / ソフトウエア STOP モード要求出力端子です。

### (8) STPAK (入力)

STPRQ 信号を受け付けたメモリ・コントローラ(MEMC)からのアクノリッジ信号入力端子です。

## 2. 2. 4 DMAC 用端子

## (1) IDMASTP(入力)

DMA 転送強制中断入力端子です。VBCLK 信号の立ち上がりに同期して 2 クロック分のアクティブ・レベル (ハイ・レベル)を入力してください。

転送を再開させる場合は,この端子にロウ・レベルを入力してから DRST レジスタの EN ビットをセット(1)します。

## (2) DMARQ3-DMARQ0(入力)

DMA 転送要求入力端子です。VBCLK 信号の立ち上がりに同期してアクティブ・レベル (ハイ・レベル)を入力し,対応する DMACTVn 信号がハイ・レベルになるまで入力し続けてください (n = 3-0)。

### (3) DMTCO3-DMTCO0(出力)

ターミナル・カウント(DMA 転送完了)出力端子です。最終 DMA 転送時に 1 クロックのハイ・レベルを出力します。VBCLK 信号の立ち上がりに同期して出力されます。

#### (4) DMACTV3-DMACTV0(出力)

DMA アクノリッジ出力端子です。2 サイクル転送の VSB リード・サイクル , VSB ライト・サイクル中 , およびフライバイ転送中にアクティブ ( ハイ・レベル出力 ) になります。

# 2. 2. 5 INTC 用端子

#### (1) DCNMI2-DCNMI0(入力)

ノンマスカブル割り込み要求(NMI)入力端子です。立ち上がりエッジが入力されるとノンマスカブル割り込みが発生します。

## (2) INT63-INT0 (入力)

マスカブル割り込み要求入力端子です。立ち上がりエッジが入力されるとマスカブル割り込みが発生します。

# 2.2.6 VFB 用端子

# (1) IROMA19-IROMA2(出力)

ROM へのアドレス出力バスです。

## (2) IROMZ31-IROMZ0(入力)

ROM からのデータ入力バスです。

#### (3) IROMEN(出力)

ROM へのアクセス・イネーブル出力端子です。VBCLK 信号の立ち下がりに同期して変化します。

## (4) IROMWT(入力)

ROM からのウエイト入力端子です。ウエイト期間中はハイ・レベルを入力します。

# (5) IROMCS, IROMIA, IROMAE(出力)

NEC の予約端子です。オープンにしてください。

# 2.2.7 VDB 用端子

## (1) IRAMA27-IRAMA2(出力)

RAM へのアドレス出力バスです。IRAMA27-IRAMA16 信号は,データ・キャッシュ用に出力されています。したがって,RAM を接続する際にデコードする必要はありません。

## (2) IRAMZ31-IRAMZ0(入力)

RAM からのデータ入力バスです。

# (3) IRAOZ31-IRAOZ0(出力)

RAM へのデータ出力バスです。

## (4) IRAMEN(出力)

RAM へのアクセス・イネーブル出力端子です。VBCLK 信号の立ち下がりに同期して変化します。

#### (5) IRAMWR3-IRAMWR0(出力)

RAM へのライト・イネーブル出力端子です。出力データ・バス(IRAOZ31-IRAOZ0)のうち,有効となるバイト・データを示すハイ・レベル・アクティブの端子です。

表2-6 IRAMWR3-IRAMWR0信号

| アクティブ ( ハイ・レベル出力 ) となる信号 | 有効バイト・データ       |

|--------------------------|-----------------|

| IRAMWR0                  | IRAOZ7-IRAOZ0   |

| IRAMWR1                  | IRAOZ15-IRAOZ8  |

| IRAMWR2                  | IRAOZ23-IRAOZ16 |

| IRAMWR3                  | IRAOZ31-IRAOZ24 |

## (6) IRAMRWB(出力)

RAMへのリード / ライト・ステータス出力端子です。リード時にハイ・レベル,ライト時にロウ・レベルを出力します。

### (7) IRAMWT (入力)

データ・キャッシュからのウエイト入力端子です。ウエイト期間中はハイ・レベルを入力します。

# 2.2.8 命令キャッシュ用端子

## (1) IBDRRQ(入力)

命令キャッシュからのフェッチ要求入力端子です。

NU85Eに対し外部メモリからのフェッチを行う要求信号が入力されます。

# (2) IBEA25-IBEA2 (入力)

命令キャッシュからのフェッチ・アドレス入力バスです。

ミスヒット時に命令キャッシュからリードすべきアドレスが入力されます。

#### (3) IBAACK(出力)

命令キャッシュへのアドレス・アクノリッジ出力端子です。

命令キャッシュから入力された IBEA25-IBEA2 信号を NU85E が認識すると,この信号を出力します。

### (4) IBDRDY(出力)

命令キャッシュへのデータ・レディ出力端子です。

命令キャッシュのミスヒット時に NU85E が外部メモリからリードすべきデータを取り終えると,命令キャッシュに対してリフィルの準備ができたことを示すために出力します。

# (5) IBDLE3-IBDLE0(出力)

命令キャッシュへのデータ・ラッチ・イネーブル出力端子です。

# (6) IBEDI31-IBEDI0(出力)

命令キャッシュへのデータ出力バスです。

命令キャッシュのミスヒット時に命令キャッシュヘリフィルすべきデータを出力します。

#### (7) IIDRRQ(出力)

命令キャッシュへのフェッチ要求出力端子です。

#### (8) IIEA25-IIEA2(出力)

命令キャッシュへのフェッチ・アドレス出力バスです。

フェッチ要求(IIDRRQ)と同時に,外部メモリからフェッチすべきアドレスを出力します。

## (9) IIAACK (入力)

命令キャッシュからのアドレス・アクノリッジ入力端子です。

NU85E から入力されたフェッチ・アドレス (IIEA25-IIEA2) を命令キャッシュが認識すると, NU85E に対してこの信号が入力されます。

# (10) IIDLEF (入力)

命令キャッシュからのデータ・ラッチ・イネーブル入力端子です。

# (11) IIEDI31-IIEDI0(入力)

命令キャッシュからのデータ入力バスです。

命令キャッシュからリードすべきデータが入力されます。

#### (12) IIBTFT (出力)

命令キャッシュへのブランチ・ターゲット・フェッチ・ステータス出力端子です。

分岐命令による飛び先アドレスのフェッチ時にハイ・レベルを出力します。

#### (13) IIRCAN (出力)

命令キャッシュへのコード・キャンセル・ステータス出力端子です。

NU85E がフェッチ要求を命令キャッシュに出力したあと、分岐や割り込みでデータが不要になった場合に、以前の要求をキャンセルするための信号です。

## (14) BCUNCH (出力)

命令キャッシュへのアンキャッシュ・ステータス出力端子です。

キャッシュ・コンフィギュレーション・レジスタ(BHC)で命令キャッシュの設定をキャッシュ可能に 設定した領域をアクセスしたときに、ロウ・レベルを出力します。

## (15) IBBTFT (入力)

NEC の予約端子です。常にロウ・レベルを入力してください。なお、命令キャッシュを使用するときは、命令キャッシュの IBBTFT 端子はオープンにしてください。

# 2.2.9 データ・キャッシュ用端子

## (1) IDDARQ(出力)

データ・キャッシュへのリード/ライト・アクセス要求出力端子です。

## (2) IDAACK(出力)

データ・キャッシュへのアクノリッジ出力端子です。

データ・キャッシュから入力された IDEA27-IDEA0 信号を NU85E が認識すると,この信号が出力されます。

## (3) IDDRRQ, IDDWRQ, IDSEQ4, IDSEQ2(入力)

データ・キャッシュからの動作タイプ設定入力端子です。

表2 - 7 IDDRRQ, IDDWRQ, IDSEQ4, IDSEQ2信号

| IDDRRQ | IDDWRQ | IDSEQ4 | IDSEQ2 | 動作タイプ             |

|--------|--------|--------|--------|-------------------|

| 1      | 0      | 1      | 0      | 4 ワード・シーケンシャル・リード |

| 1      | 0      | 0      | 1      | 2 ワード・シーケンシャル・リード |

| 1      | 0      | 0      | 0      | 1ワード・リード          |

| 0      | 1      | 1      | 0      | 4 ワード・シーケンシャル・ライト |

| 0      | 1      | 0      | 1      | 2 ワード・シーケンシャル・ライト |

| 0      | 1      | 0      | 0      | 1ワード・ライト          |

| 1      | 1      | 1      | 1      | 1ワード・ライト          |

| 1      | 1      | 1      | 0      | 1 ハーフワード・ライト      |

| 1      | 1      | 0      | 0      | 1 バイト・ライト         |

| 上記以外   |        |        |        | 設定禁止              |

**備考** 0:ロウ・レベル入力 1:ハイ・レベル入力

# (a) IDDRRQ(入力)

データ・キャッシュからの VSB リード・オペレーション要求入力端子です。

## (b) IDDWRQ(入力)

データ・キャッシュからの VSB ライト・オペレーション要求入力端子です。

# (c) IDSEQ4, IDSEQ2(入力)

データ・キャッシュからのリード/ライト動作タイプ設定入力端子です。

### (4) IRRSA(出力)

データ・キャッシュへの VDB ホールド・ステータス出力端子です。

VDB が RAM アクセス,またはホールド状態のときにアクティブ・レベル(ハイ・レベル)を出力します。

#### (5) IDRETR (出力)

データ・キャッシュへのリード・リトライ要求出力端子です。

#### (6) IDUNCH(出力)

データ・キャッシュへのアンキャッシュ・ステータス出力端子です。

キャッシュ・コンフィギュレーション・レジスタ(BHC)でデータ・キャッシュの設定をキャッシュ可能に設定した領域をアクセスしたときにロウ・レベルを出力します。

## (7) IDDRDY(出力)

データ・キャッシュへのリード・データ・レディ出力端子です。

データ・キャッシュのミスヒット時に NU85E が外部メモリからリードすべきデータを取り終えると、データ・キャッシュに対してリフィルの準備ができたことを示すために出力します。

#### (8) IDRRDY(入力)

データ・キャッシュからのリード・データ・レディ入力端子です。

#### (9) IDHUM (入力)

データ・キャッシュからのヒット・アンダ・ミスヒット・リード入力端子です。

リード時のミスヒット発生による外部メモリへのアクセス中に,データ・キャッシュに対する次のアクセスが行われ,そのアクセス時にヒットしたデータが外部メモリからのデータに先行して NU85E に入力される場合(ヒット・アンダ・ミスヒット)に,ハイ・レベルが入力されます。

#### (10) IDEA27-IDEA0(入力)

データ・キャッシュからのアドレス入力バスです。

データ・キャッシュのミスヒット時に NU85E に対しアクセスすべきアドレスが入力されます。

# (11) IDED31-IDED0 (入出力)

データ・キャッシュとのデータ入出力バスです。

データ・キャッシュにリフィルするデータやライト・バック・モード時に外部メモリに書き込むデータのやり取りをします。

## (12) IDES (出力)

NEC の予約端子です。

データ・キャッシュを使用するときは、必ずデータ・キャッシュの IDES 端子に接続してください。未使用時はオープンにしてください。

# 2. 2. 10 RCU 用端子

## (1) DBI5-DBI0 (入力)

ディバグ制御入力端子です。RCUの DBI5-DBI0 端子に接続します。

### (2) DBO14-DBO0(出力)

ディバグ制御出力端子です。RCUの DBO14-DBO0 端子に接続します。

#### (3) DBB15-DBB0 (入出力)

ディバグ制御入出力端子です。RCUの DBB15-DBB0 端子に接続します。

# 2. 2. 11 周辺エバチップ・モード用端子

PHEVA 端子にハイ・レベルを入力すると NU85E は周辺エバチップ・モードに設定されます。

周辺エバチップ・モードは、インサーキット・エミュレータを用いてディバグを行う際に NU85E を内蔵した ASIC を周辺エミュレーション用のチップとして使用するためのモードです。

周辺エバチップ・モード用端子は、インサーキット・エミュレータ内のエバチップとのインタフェース用端子で、これらの端子を通じて、エバチップの各信号を NPB 用の信号に変換します。

#### (1) EVASTB (入力)

アドレス・ストローブ入力端子です。エバチップの EPHASTB 端子に接続します。

## (2) EVDSTB (入力)

データ・ストローブ入力端子です。エバチップの EPHDSTB 端子に接続します。

#### (3) EVAD15-EVAD0(入出力)

アドレス / データ・バスです。エバチップの EPHADn 端子に接続します (n = 15-0)。

#### (4) EVIEN(出力)

EVADn バス上の I/O バッファの方向制御を行う入力イネーブル信号です(n = 15-0)。

#### (5) EVOEN(出力)

EVADn バス上の I/O バッファの方向制御を行う出力イネーブル信号です (n = 15-0)。

# (6) EVLKRT (入出力)

ロック / リトライ入出力端子です。エバチップの EPHLKRT 端子に接続します。

#### (7) EVIREL(入力)

スタンバイ・リリース入力端子です。

# (8) EVCLRIP(入力)

ISPR クリア入力端子です。エバチップの ECLRIP 端子に接続します。

#### (9) EVINTAK (入力)

割り込みアクノリッジ入力端子です。エバチップの EINTAK 端子に接続します。

## (10) EVINTRQ(出力)

割り込み要求出力端子です。エバチップの EINTRQ 端子に接続します。

### (11) EVINTLV6-EVINTLV0(出力)

割り込みベクタ出力端子です。エバチップの EINTLV6-EINTLV0 端子に接続します。

# 2.2.12 動作モード設定用端子

NU85Eの動作モードは,次の各端子により指定します。

これらの端子への入力レベルは, NU85E 動作中は固定とし, 動作中に変更しないでください。

### (1) IFIROME (入力)

ROM 領域設定入力端子です。この端子への入力レベルにより,使用する ROM が次のように設定されます。

- ロウ・レベル:外部メモリとして接続された ROM を使用 (VSB 経由)

- ハイ・レベル: VFB に接続された ROM を使用

この端子にロウ・レベルが入力されている場合,システム・リセット解除後に外部メモリのリセット・エントリ・アドレスに分岐して命令処理を開始します。VFBに接続されたROMへの命令フェッチ,データ・アクセスはできません。

ハイ・レベルを入力すると、IFIROB2 端子にロウ・レベルが入力されている場合は、システム・リセット解除後に VFB に接続された ROM のリセット・エントリ・アドレスに分岐し、命令処理を開始します。 IFIROB2 端子にハイ・レベルが入力されている場合は、システム・リセット解除後に外部メモリのリセット・エントリ・アドレスに分岐して命令処理を開始しますが、100000H 番地以降に配置された VFB に接続された ROM へのアクセスが可能です。

#### (2) IFIROB2 (入力)

ROM 領域リロケーション設定入力端子です。ROM 領域を配置する範囲を指定します。この端子への入力レベルにより、ROM 領域の範囲が次のように設定されます。

ロウ・レベル: 000000H-0FFFFFH 番地ハイ・レベル: 100000H-1FFFFFH 番地

詳細は, 3.4.1(1) ROM リロケーション機能を参照してください。

#### (3) IFIRA64, IFIRA32, IFIRA16(入力)

RAM 領域サイズ選択入力端子です。

これらの端子への入力レベルにより,次のようにRAM領域サイズが設定されます。

詳細については,3.4.2 RAM 領域を参照してください。

RAM 領域サイズ IFIRA64 IFIRA32 IFIRA16 4K バイト 0 0 0 12K バイト 0 0 1 任意 28K バイト 0 1 任意 任意 60K バイト 1

表2 - 8 IFIRA64, IFIRA32, IFIRA16信号

**備考** 0:ロウ・レベル入力 1:ハイ・レベル入力

#### (4) IFIMAEN (入力)

ミス・アライン・アクセス設定入力端子です。

この端子への入力レベルにより、ミス・アライン・アクセスの許可/禁止が次のように設定されます。

- ロウ・レベル: ミス・アライン・アクセス禁止

- ハイ・レベル: ミス・アライン・アクセス許可

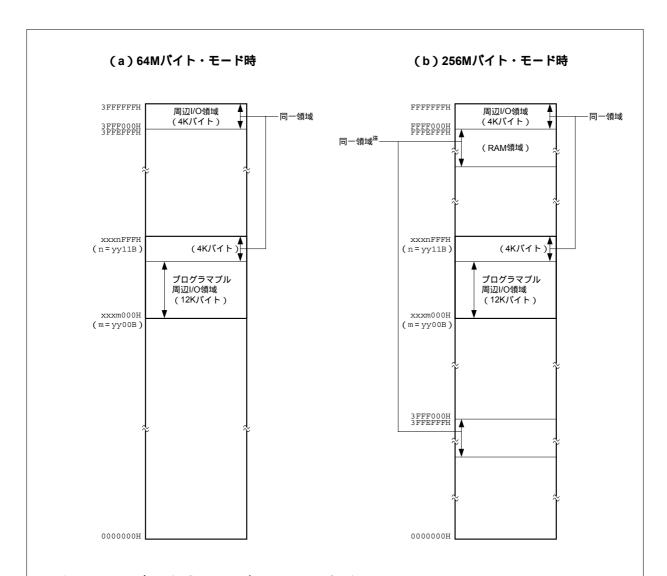

## (5) IFID256(入力)

データ領域設定入力端子です。データ領域のサイズを設定します。

この端子への入力レベルにより、次のように各モードが設定されます。

詳細については,3.3.2 データ領域を参照してください。

• ロウ・レベル: 64M バイト・モード

• ハイ・レベル: 256M バイト・モード

### (6) IFINSZ1, IFINSZ0(入力)

VSB データ・バス・サイズ(初期値)選択入力端子です。

これらの端子への入力レベルにより,次のように VSB のデータ・バス・サイズが設定されます。

| IFINSZ1 | IFINSZ0 | VSB データ・バス・サイズ |

|---------|---------|----------------|

| 0       | 0       | 32 ビット         |

| 0       | 1       | 16 ビット         |

| 1       | 0       | 8ビット           |

| 1       | 1       | 設定禁止           |

表2-9 IFINSZ1, IFINSZ0信号

**備考** 0:ロウ・レベル入力 1:ハイ・レベル入力

なお,リセット後にバス・サイズ・コンフィギュレーション・レジスタ(BSC)により,VSBデータ・バス・サイズを変更した場合は,これらの端子への入力レベルにかかわらず,BSCレジスタの設定が有効となります。

## (7) IFIWRTH(入力)

データ・キャッシュのライト・バック / ライト・スルー・モード選択入力端子です。 データ・キャッシュを使用する場合,データ・キャッシュの IFIWRTH 端子と接続します。

この端子への入力レベルにより、次のように各モードが設定されます。

• ロウ・レベル:ライト・バック・モード

• ハイ・レベル:ライト・スルー・モード

## (8) IFIUNCH1 (入力)

データ・キャッシュ設定入力端子です。

データ・キャッシュを使用する場合,データ・キャッシュの IFIUNCH1 端子と接続します。

この端子への入力レベルにより,データ・キャッシュの許可/禁止が次のように設定されます。

- ロウ・レベル: データ・キャッシュ許可

- ハイ・レベル:データ・キャッシュ禁止

### (9) IFIUNCH0(入力)

命令キャッシュ設定入力端子です。

この端子への入力レベルにより,命令キャッシュの許可/禁止が次のように設定されます。

- ロウ・レベル: 命令キャッシュ許可

- ハイ・レベル: 命令キャッシュ禁止

## (10) PHEVA (入力)

周辺エバチップ・モード設定入力端子です。NU85Eを内蔵した ASIC を周辺エバチップとして使用する場合に,ハイ・レベルを入力します。

(11) IFIROBE, IFIROPR, IFIRASE, IFIRABE, IFIMODE3, IFIMODE2, IFIUSWE, FCOMB (入力)

NEC の予約端子です。常にロウ・レベルを入力してください。

# 2. 2. 13 テスト・モード用端子

(1) TBI39-TBI0 (入力)

入力テスト・バスです。

(2) TBO34-TBO0(出力)

出力テスト・バスです。

(3) TEST (入力)

テスト・バス・コントロール入力端子です。

(4) BUNRI(入力)

ノーマル/テスト・モードを選択する入力端子です。

(5) BUNRIOUT (出力)

テスト・モード状態であることを示すステータス出力端子です。 BUNRI 端子(入力)のレベルがそのまま出力されます。

(6) PHTDO1, PHTDO0 (入力)

周辺マクロ・テスト入力端子です。

(7) TESEN (出力)

周辺マクロをテスト・モードに設定するためのイネーブル出力端子です。

# (8) VPTCLK(出力)

周辺マクロ・テスト用クロック出力端子です。

## (9) PHTDIN1, PHTDIN0(出力)

周辺マクロ・テスト出力端子です。

# (10) VPRESZ(出力)

周辺マクロに対するリセット出力端子です。

注意 VPRESZ 信号は,テスト・モード時だけでなく,通常動作モード時も周辺マクロに対するリセット信号となります。

# (11) PHTEST (出力)

周辺テスト・モード状態であることを示すステータス出力端子です。

# (12) TMODE1(出力)

テスト・モード選択出力端子です。RCUを使用するとき,RCUのTMODE1,TEST端子に接続します。

## (13) TMODEO, TBREDZ(出力)

NEC の予約端子です。オープンにしてください。

# 2.3 未使用端子の処理

(1/2)

|             | 端子名                                             | 入出力 | 推奨接続方法           |

|-------------|-------------------------------------------------|-----|------------------|

| <br>NPB 用端子 | VPA13-VPA0, VPDO15-VPDO0, VPWRITE,              | 出力  | オープンにしてください。     |

| 2 /13/110 3 | VPSTB, VPLOCK, VPUBENZ, VPDV                    | шуу |                  |

|             | VPDI15-VPDI0 <sup>±</sup> , VPRETR <sup>±</sup> | 入力  | ロウ・レベルを入力してください。 |

|             | VPDACT                                          | 入力  | ハイ・レベルを入力してください。 |

| VSB 用端子     | VAREQ                                           | 入力  | ロウ・レベルを入力してください。 |

|             | VAACK, VAPREQ, VBDO31-VBDO0,                    | 出力  | オープンにしてください。     |

|             | VMA27-VMA0, VMTTYP1, VMTTYP0,                   |     |                  |

|             | VMSTZ, VMBENZ3-VMBENZ0, VMSIZE1,                |     |                  |

|             | VMSIZE0, VMWRITE, VMLOCK, VMCTYP2-              |     |                  |

|             | VMCTYP0, VMSEQ2-VMSEQ0, VMBSTR,                 |     |                  |

|             | VDSELPZ, VSWAIT, VSLAST, VSAHLD,                |     |                  |

|             | VBDC, VBDV, VDCSZ7-VDCSZ0                       |     |                  |

|             | VBDI31-VBDI0, VMWAIT, VMLAST, VMAHLD,           | 入力  | ロウ・レベルを入力してください。 |

|             | VSA13-VSA0, VSWRITE, VSLOCK                     |     |                  |

|             | VSSTZ, VSBENZ1, VSSELPZ                         | 入力  | ハイ・レベルを入力してください。 |

| システム        | DCRESZ, VBCLK                                   | 入力  | -                |

| 制御用端子       | CGREL                                           | 入力  | ロウ・レベルを入力してください。 |

|             | SWSTOPRQ, HWSTOPRQ, STPRQ                       | 出力  | オープンにしてください。     |

|             | DCSTOPZ, STPAK                                  | 入力  | ハイ・レベルを入力してください。 |

| DMAC 用端子    | IDMASTP, DMARQ3-DMARQ0                          | 入力  | ロウ・レベルを入力してください。 |

|             | DMTCO3-DMTCO0, DMACTV3-DMACTV0                  | 出力  | オープンにしてください。     |

| INTC 用端子    | DCNMI2-DCNMI0, INT63-INT0                       | 入力  | ロウ・レベルを入力してください。 |

| VFB 用端子     | IROMA19-IROMA2, IROMEN, IROMCS,                 | 出力  | オープンにしてください。     |

|             | IROMIA, IROMAE                                  |     |                  |

|             | IROMZ31-IROMZ0                                  | 入力  | ハイ・レベルを入力してください。 |

|             | IROMWT                                          | 入力  | ロウ・レベルを入力してください。 |

| VDB 用端子     | IRAMA27-IRAMA2, IRAOZ31-IRAOZ0,                 | 出力  | オープンにしてください。     |

|             | IRAMEN, IRAMWR3-IRAMWR0, IRAMRWB                |     |                  |

|             | IRAMZ31-IRAMZ0                                  | 入力  | ハイ・レベルを入力してください。 |

|             | IRAMWT                                          | 入力  | ロウ・レベルを入力してください。 |

| 命令キャッシュ用    | IBDRRQ, IBEA25-IBEA2, IIAACK, IIDLEF,           | 入力  | ロウ・レベルを入力してください。 |

| 端子          | IIEDI31-IIEDI0, IBBTFT                          |     |                  |

|             | IBAACK, IBDRDY, IBDLE3-IBDLE0, IBEDI31-         | 出力  | オープンにしてください。     |

|             | IBEDIO, IIDRRQ, IIEA25-IIEA2, IIBTFT,           |     |                  |

|             | IIRCAN, BCUNCH                                  |     |                  |

| データ・        | IDDARQ, IDAACK, IRRSA, IDRETR,                  | 出力  | オープンにしてください。     |

| キャッシュ用端子    | IDUNCH, IDDRDY, IDES                            |     |                  |

|             | IDDRRQ, IDDWRQ, IDSEQ4, IDSEQ2,                 | 入力  | ロウ・レベルを入力してください。 |

|             | IDRRDY, IDHUM, IDEA27-IDEA0                     |     |                  |

|             | IDED31-IDED0                                    | 入出力 | オープンにしてください。     |

注 一度バッファを介してからロウ・クランプしてください。

(2/2)

|                    | 端子名                                                                               | 入出力 | 推奨接続方法                           |

|--------------------|-----------------------------------------------------------------------------------|-----|----------------------------------|

| RCU 用端子            | DBI5, DBI1                                                                        | 入力  | ハイ・レベルを入力してください。                 |

|                    | DBI4-DBI2, DBI0                                                                   | 入力  | ロウ・レベルを入力してください。                 |

|                    | DBO14-DBO0                                                                        | 出力  | オープンにしてください。                     |

|                    | DBB15-DBB0                                                                        | 入出力 | オープンにしてください。                     |

| 周辺エバチップ・<br>モード用端子 | EVASTB, EVDSTB, EVIREL, EVCLRIP, EVINTAK                                          | 入力  | ロウ・レベルを入力してください。                 |

|                    | EVAD15-EVAD0, EVLKRT                                                              | 入出力 | オープンにしてください。                     |

|                    | EVIEN, EVOEN, EVINTRQ, EVINTLV6-<br>EVINTLV0                                      | 出力  | オープンにしてください。                     |

| 動作モード設定用<br>端子     | IFIROME, IFIRA64, IFIRA32, IFIRA16, IFIMAEN, IFID256, IFINSZ1, IFINSZ0            | 入力  | -                                |

|                    | IFIROB2, IFIWRTH, IFIUNCH0                                                        | 入力  | ロウ・レベル , またはハイ・レベルを入力して<br>ください。 |

|                    | PHEVA, IFIROBE, IFIROPR, IFIRASE, IFIRABE, IFIMODE3, IFIMODE2, IFIUSWE, FCOMB     | 入力  | ロウ・レベルを入力してください。                 |

|                    | IFIUNCH1                                                                          | 入力  | ハイ・レベルを入力してください。                 |

| テスト・モード用           | TBI39-TBI0                                                                        | 入力  | 各セルベース IC ファミリのユーザーズ・マニ          |

| 端子                 | TBO34-TBO0                                                                        | 出力  | ュアルを参照してください。                    |

|                    | TEST, BUNRI                                                                       | 入力  | -                                |

|                    | PHTDO1 <sup>it</sup> , PHTDO0 <sup>it</sup>                                       | 入力  | ロウ・レベルを入力してください。                 |

|                    | BUNRIOUT, TESEN, VPTCLK, PHTDIN1, PHTDIN0, VPRESZ, PHTEST, TMODE1, TMODE0, TBREDZ | 出力  | オープンにしてください。                     |

注 一度バッファを介してからロウ・クランプしてください。

# 2.4 端子状態

出力機能を持つ端子の各動作モードでの状態を次に示します。

表2-10 各動作モードでの端子状態 (1/3)

| 端子名     |            |                   |          | 端子       | <del>-</del> 状態 |         |        |

|---------|------------|-------------------|----------|----------|-----------------|---------|--------|

|         |            | リセット <sup>注</sup> | ソフトウエア   | ハードウエア   | HALT モード        | スタンバイ・  | 単体テスト・ |

|         |            |                   | STOP €-ド | STOP E-F |                 | テスト・モード | モード    |

| NPB 用端子 | VPA13-VPA0 | 不定                | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VPDO15-    | 不定                | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VPD00      |                   |          |          |                 |         |        |

|         | VPWRITE    | 不定                | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VPSTB      | L                 | L        | L        | 動作              | 不定      | 動作     |

|         | VPLOCK     | 不定                | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VPUBENZ    | 不定                | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VPDV       | 不定                | 保持       | 保持       | 動作              | 不定      | 動作     |

| VSB 用端子 | VAACK      | L                 | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VAPREQ     | L                 | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VBDO31-    | L                 | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VBDO0      |                   |          |          |                 |         |        |

|         | VMA27-     | L                 | 保持       | 保持       | 動作              | 不定      | 動作     |

|         | VMA0       |                   |          |          |                 |         |        |