# IDT™ 89HPES24N3A PCI Express® Switch

# **User Manual**

April 2008

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

Printed in U.S.A.

©2008 Integrated Device Technology, Inc.

## GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

## CODE DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

## LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

## **About This Manual**

## Notes

## Introduction

This user manual includes hardware and software information on the 89HPES24N3A, a member of IDT's PRECISE™ family of PCI Express® switching solutions offering the next-generation I/O interconnect standard.

## **Finding Additional Information**

Information not included in this manual such as mechanicals, package pin-outs, and electrical characteristics can be found in the data sheet for this device, which is available from the IDT website (www.idt.com) as well as through your local IDT sales representative.

## **Content Summary**

Chapter 1, "PES24N3A Device Overview," provides a complete introduction to the performance capabilities of the 89HPES24N3A. Included in this chapter is a summary of features for the device as well as a system block diagram and pin description.

Chapter 2, "Clocking, Reset, and Initialization," provides a description of the two differential reference clock inputs that are used internally to generate all of the clocks required by the internal switch logic and the SerDes.

**Chapter 3**, "Theory of Operation," provides basic information on the architecture and operation of the 89HPES24N3A chip.

**Chapter 4, "Link Operation,"** describes the operation of the link feature including polarity inversion, link width negotiation, and lane reversal.

Chapter 4, "Switch Operation," discusses the procedure for forwarding PCle® TLPs between switch ports.

**Chapter 5**, "General Purpose I/O," describes how the 8 General Purpose I/O (GPIO) pins may be individually configured as general purpose inputs, general purpose outputs, or alternate functions.

Chapter 6, "SMBus Interfaces," describes the operation of the 2 SMBus interfaces on the PES24N3A.

**Chapter 7**, "Power Management," describes the power management capability structure located in the configuration space of each PCI-PCI bridge in the PES24N3A.

**Chapter 8**, "Hot-Plug and Hot-Swap," describes the behavior of the hot-plug and hot-swap features in the PES24N3A.

**Chapter 9, "Configuration Registers,"** discusses the base addresses, PCI configuration space, and registers associated with the PES24N3A.

**Chapter 10**, "JTAG Boundary Scan," discusses an enhanced JTAG interface, including a system logic TAP controller, signal definitions, a test data register, an instruction register, and usage considerations.

## Signal Nomenclature

To avoid confusion when dealing with a mixture of "active-low" and "active-high" signals, the terms assertion and negation are used. The term assert or assertion is used to indicate that a signal is active or true, independent of whether that level is represented by a high or low voltage. The term negate or negation is used to indicate that a signal is inactive or false.

To define the active polarity of a signal, a suffix will be used. Signals ending with an 'N' should be interpreted as being active, or asserted, when at a logic zero (low) level. All other signals (including clocks, buses and select lines) will be interpreted as being active, or asserted when at a logic one (high) level.

To define buses, the most significant bit (MSB) will be on the left and least significant bit (LSB) will be on the right. No leading zeros will be included.

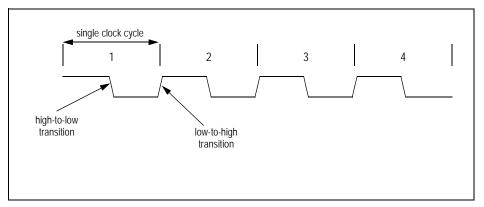

Throughout this manual, when describing signal transitions, the following terminology is used. Rising edge indicates a low-to-high (0 to 1) transition. Falling edge indicates a high-to-low (1 to 0) transition. These terms are illustrated in Figure 1.

Figure 1 Signal Transitions

## **Numeric Representations**

To represent numerical values, either decimal, binary, or hexadecimal formats will be used. The binary format is as follows: 0bDDD, where "D" represents either 0 or 1; the hexadecimal format is as follows: 0xDD, where "D" represents the hexadecimal digit(s); otherwise, it is decimal.

The compressed notation ABC[x|y|z]D refers to ABCxD, ABCyD, and ABCzD.

The compressed notation ABC[x:y]D refers to ABCxD, ABC(x+1)D, ABC(x+2)D,... ABCyD if x < y or to ABCxD, ABC(x-1)D, ABC(x-2)D,... ABCyD if x > y.

## **Data Units**

The following data unit terminology is used in this document.

| Term               | Words | Bytes | Bits |

|--------------------|-------|-------|------|

| Byte               | 1/2   | 1     | 8    |

| Word               | 1     | 2     | 16   |

| Doubleword (Dword) | 2     | 4     | 32   |

| Quadword (Qword)   | 4     | 8     | 64   |

Table 1 Data Unit Terminology

In quadwords, bit 63 is always the most significant bit and bit 0 is the least significant bit. In double-words, bit 31 is always the most significant bit and bit 0 is the least significant bit. In words, bit 15 is always the most significant bit and bit 0 is the least significant bit. In bytes, bit 7 is always the most significant bit and bit 0 is the least significant bit.

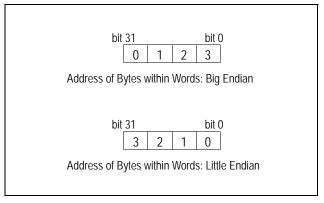

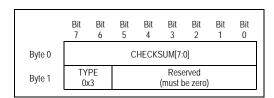

The ordering of bytes within words is referred to as either "big endian" or "little endian." Big endian systems label byte zero as the most significant (leftmost) byte of a word. Little endian systems label byte zero as the least significant (rightmost) byte of a word. See Figure 2.

Figure 2 Example of Byte Ordering for "Big Endian" or "Little Endian" System Definition

## **Register Terminology**

Software in the context of this register terminology refers to modifications made by PCle root configuration writes, writes to registers made through the slave SMBus interface, or serial EEPROM register initialization. See Table 2.

| Туре                 | Abbreviation | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware Initialized | HWINIT       | Register bits are initialized by firmware or hardware mechanisms such as pin strapping or serial EEPROM. (System firmware hardware initialization is only allowed for system integrated devices.) Bits are read-only after initialization and can only be reset (for write-once by firmware) with reset.                                                                                                                                                                                             |

| Read Only and Clear  | RC           | Software can read the register/bits with this attribute. Reading the value will automatically cause the register/bit to be reset to zero. Writing to a RC location has no effect.                                                                                                                                                                                                                                                                                                                    |

| Read Clear and Write | RCW          | Software can read the register/bits with this attribute. Reading the value will automatically cause the register/bits to be reset to zero. Writes cause the register/bits to be modified.                                                                                                                                                                                                                                                                                                            |

| Reserved             | Reserved     | The value read from a reserved register/bit is undefined. Thus, software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back. |

| Read Only            | RO           | Software can only read registers/bits with this attribute. Contents are hardwired to a constant value or are status bits that may be set and cleared by hardware. Writing to a RO location has no effect.                                                                                                                                                                                                                                                                                            |

| Read and Write       | RW           | Software can both read and write bits with this attribute.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 2 Register Terminology (Sheet 1 of 2)

| Туре                         | Abbreviation | Description                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read and Write Clear         | RW1C         | Software can read and write to registers/bits with this attribute. However, writing a value of zero to a bit with this attribute has no effect. A RW1C bit can only be set to a value of 1 by a hardware event. To clear a RW1C bit (i.e., change its value to zero) a value of one must be written to the location. An RW1C bit is never cleared by hardware. |

| Read and Write when Unlocked | RWL          | Software can read the register/bits with this attribute. Writing to register/bits with this attribute will only cause the value to be modified if the REGUNLOCK bit in the SWCTL register is set. When the REGUNLOCK bit is cleared, writes are ignored and the register/bits are effectively read-only                                                        |

| Write Transient              | WT           | The zero is always read from a bit/field of this type. Writing of a one is used to quality the writing of other bits/fields in the same register.                                                                                                                                                                                                              |

| Zero                         | Zero         | A zero register or bit must be written with a value of zero and returns a value of zero when read.                                                                                                                                                                                                                                                             |

Table 2 Register Terminology (Sheet 2 of 2)

## **Use of Hypertext**

In Chapter 9, Tables 9.2 and 9.3 contain register names and page numbers highlighted in blue under the Register Definition column. In pdf files, users can jump from this source table directly to the registers by clicking on the register name in the source table. Each register name in the table is linked directly to the appropriate register in the register section of the chapter. To return to the source table after having jumped to the register section, click on the same register name (in blue) in the register section.

## **Reference Documents**

PCI Express Base Specification, Revision 2.0, PCI Special Interest Group.

PCI Power Management Interface Specification, Revision 1.1, PCI Special Interest Group.

PCI to PCI Bridge Architecture Specification, Revision 1.2, PCI Special Interest Group.

SMBus Specification, Revision 2.0.

## **Revision History**

February 8, 2007: Initial Publication.

May 30, 2007: In Table 1.2, added revision information for ZG silicon. Added Notes to Figure 2.5.

**July 18, 2007**: In Chapter 9, changed bits [10:9] in HPCFGCTL from RO to RW. In Chapter 2, changed references to correctly state SRESET field is in BCTL register, not the SWCTL register.

April 10, 2008: In the About section, Table 2, changed SYSCNTL to SWCTL. In Chapter 9, changed default value for VER field in PCIECAP register from 0x2 to 0x1 and changed 0x0 definition for bit EEPE in SWPERCTL register from "time-out" to "end-to-end parity error".

# **Table of Contents**

| About This Manual                                       |     |

|---------------------------------------------------------|-----|

| Introduction                                            | 1   |

| Content Summary                                         |     |

| Signal Nomenclature                                     |     |

| Numeric Representations                                 |     |

| Data Units                                              |     |

| Register Terminology                                    |     |

| Use of Hypertext                                        |     |

| Reference Documents                                     |     |

| Revision History                                        |     |

| PES24N3A Device Overview                                |     |

| Introduction                                            | 1-1 |

| List of Features                                        |     |

| System Diagrams                                         |     |

| Logic Diagram                                           |     |

| System Identification                                   |     |

| Vendor ID                                               |     |

| Device ID                                               |     |

| Revision ID                                             |     |

| JTAG ID                                                 |     |

| SSID/SSVID                                              | 1-5 |

| Device Serial Number Enhanced Capability                |     |

| Pin Description                                         |     |

| Pin Characteristics                                     | 1-9 |

|                                                         |     |

| Clocking, Reset, and Initialization                     |     |

| Introduction                                            |     |

| Initialization                                          | 2-3 |

| Reset                                                   | 2-4 |

| Fundamental Reset                                       | 2-4 |

| Hot Reset                                               | 2-6 |

| Upstream Secondary Bus Reset                            |     |

| Downstream Secondary Bus Reset                          |     |

| Downstream Port Reset Outputs                           |     |

| Power Enable Controlled Reset Output                    |     |

| Power Good Controlled Reset Output                      |     |

| Hot Reset Controlled Reset Output                       | 2-9 |

| Theory of Operation                                     |     |

| Introduction                                            | 3₋1 |

| Data Paths                                              |     |

| Store-and-Forward vs. Cut-Through Switching and Latency |     |

| Switch Core                                             |     |

| Transaction Routing                                     |     |

| Transaction Reordering                                  |     |

| Scheduling and Port Arbitration                         |     |

| Peer-to-Peer Transactions                     | 3-8        |

|-----------------------------------------------|------------|

| Bus Locking                                   | 3-8        |

| Port Interrupts                               | 3-10       |

| Legacy Interrupt Emulation                    | 3-10       |

| Standard PCIe Error Detection and Handling    |            |

| Physical Layer Errors                         | 3-11       |

| Data Link Layer Errors                        | 3-11       |

| Transaction Layer Errors                      | 3-12       |

| Routing Errors                                | 3-14       |

| Switch Specific Error Detection and Handling  | 3-15       |

| Switch Time-Outs                              | 3-16       |

| End-to-End Parity Checking                    | 3-16       |

| TLP Processing                                | 3-17       |

| Link Operation                                |            |

| Introduction                                  | Д-1        |

| Polarity Inversion                            |            |

| Link Width Negotiation                        |            |

| Lane Reversal                                 |            |

| Link Retraining                               |            |

| Link Down                                     |            |

| Slot Power Limit Support                      |            |

| Upstream Port                                 |            |

| Downstream Port                               |            |

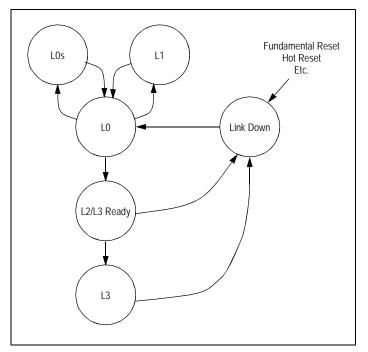

| Link States                                   | 4-5        |

| Active State Power Management                 | 4-6        |

| Link Status                                   |            |

| General Purpose I/O                           |            |

| Introduction                                  | 5 <u>1</u> |

| GPIO Configuration                            |            |

| GPIO Pin Configured as an Input               |            |

| GPIO Pin Configured as an Output              |            |

| GPIO Pin Configured as an Alternate Function  |            |

| · ·                                           |            |

| SMBus Interfaces                              |            |

| Introduction                                  |            |

| Master SMBus Interface                        |            |

| Initialization                                |            |

| Serial EEPROM                                 |            |

| I/O Expanders                                 |            |

| Slave SMBus Interface                         |            |

| Initialization                                |            |

| SMBus Transactions                            | 6-11       |

| Power Management                              |            |

| Introduction                                  | 7-1        |

| PME Messages                                  | 7-2        |

| Power Express Power Management Fence Protocol |            |

| Power Budgeting Canability                    | 7-3        |

| Hot-Plug and Hot-Swap                              |      |

|----------------------------------------------------|------|

| Introduction                                       | 8-1  |

| Hot-Plug I/O Expander                              |      |

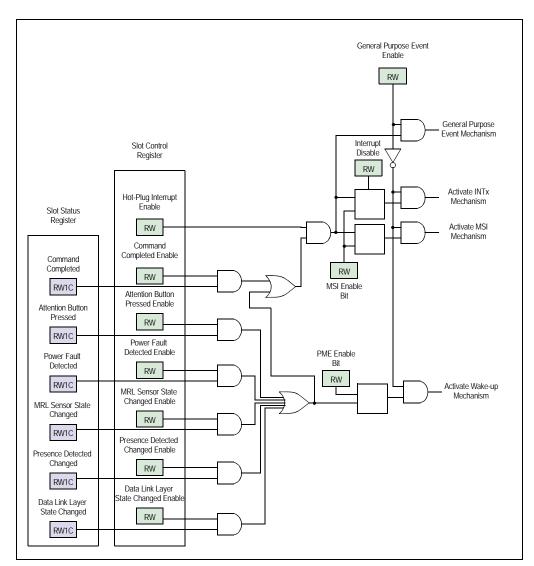

| Hot-Plug Interrupts and Wake-up                    |      |

| Legacy System Hot-Plug Support                     |      |

| Hot-Swap                                           |      |

| Configuration Registers                            |      |

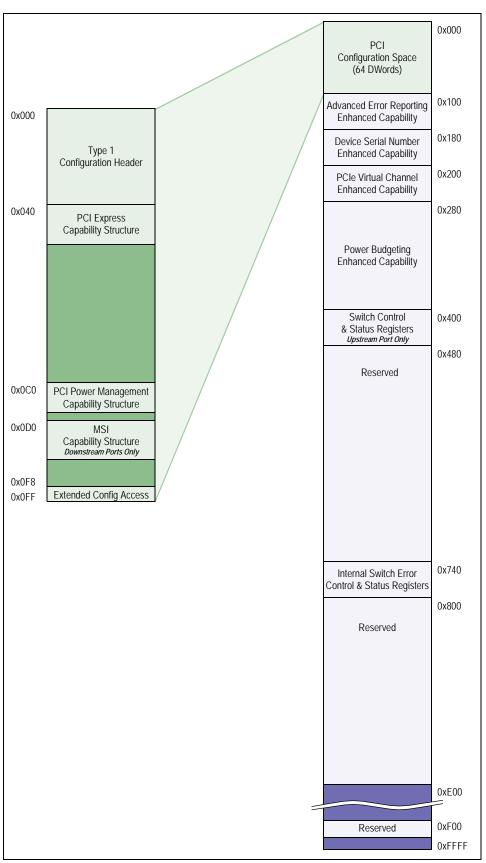

| Introduction                                       | 9-1  |

| Upstream Port (Port 0)                             | 9-3  |

| Downstream Ports (Ports 2 and 4)                   | 9-8  |

| Register Definitions                               | 9-11 |

| Type 1 Configuration Header Registers              | 9-11 |

| PCI Express Capability Structure                   | 9-21 |

| Power Management Capability Structure              | 9-33 |

| Message Signaled Interrupt Capability Structure    | 9-34 |

| Subsystem ID and Subsystem Vendor ID               | 9-36 |

| Extended Configuration Space Access Registers      | 9-36 |

| Advanced Error Reporting (AER) Enhanced Capability | 9-37 |

| Device Serial Number Enhanced Capability           | 9-43 |

| PCI Express Virtual Channel Capability             | 9-43 |

| Power Budgeting Enhanced Capability                | 9-49 |

| Switch Control and Status Registers                | 9-50 |

| Internal Switch Error Control and Status Registers | 9-61 |

| JTAG Boundary Scan                                 |      |

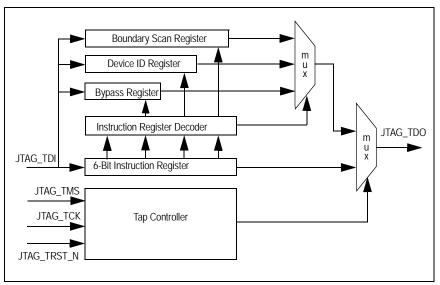

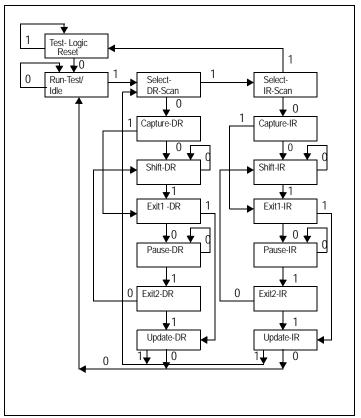

| Introduction                                       | 10-1 |

| Test Access Point                                  | 10-1 |

| Signal Definitions                                 | 10-1 |

| Boundary Scan Chain                                |      |

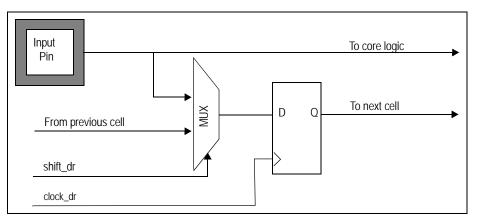

| Test Data Register (DR)                            | 10-4 |

| Boundary Scan Registers                            | 10-4 |

| Instruction Register (IR)                          | 10-6 |

| EXTEST                                             | 10-6 |

| SAMPLE/PRELOAD                                     | 10-7 |

| BYPASS                                             | 10-7 |

| CLAMP                                              | 10-7 |

| IDCODE                                             | 10-7 |

| VALIDATE                                           | 10-8 |

| RESERVED                                           | 10-8 |

| Usage Considerations                               | 10-8 |

# RENESAS IDT Table of Contents **Notes**

# **List of Tables**

| Table 1.1  | PES24N3A Device ID                                      | 1-5  |

|------------|---------------------------------------------------------|------|

| Table 1.2  | PES24N3A Revision ID                                    |      |

| Table 1.3  | PCI Express Interface Pins                              |      |

| Table 1.4  | SMBus Interface Pins                                    |      |

| Table 1.5  | General Purpose I/O Pins                                |      |

| Table 1.6  | System Pins                                             |      |

| Table 1.7  | Test Pins                                               |      |

| Table 1.8  | Power and Ground Pins                                   |      |

| Table 1.9  | Pin Characteristics                                     |      |

| Table 2.1  | Reference Clock Mode Encoding                           |      |

| Table 2.2  | Boot Configuration Vector Signals                       |      |

| Table 3.1  | IFB Buffer Sizes                                        |      |

| Table 3.2  | PES24N3A Buffer Sizes                                   |      |

| Table 3.3  | Bus Decoupler Queue and Insertion Buffer Size           |      |

| Table 3.4  | Latency                                                 |      |

| Table 3.5  | Switch Routing Methods                                  |      |

| Table 3.6  | IFB Transaction Ordering                                |      |

| Table 3.7  | Downstream Port Interrupts                              |      |

| Table 3.8  | PES24N3A Downstream to Upstream Port Interrupt Routing  |      |

| Table 3.9  | Physical Layer Errors                                   |      |

| Table 3.10 | Data Link Layer Errors                                  |      |

| Table 3.11 | Transaction Layer Errors                                |      |

| Table 3.12 | Ingress Malformed TLP Error Checks                      |      |

| Table 3.13 | Egress Malformed TLP Error Checks                       | 3-14 |

| Table 5.1  | General Purpose I/O Pin Alternate Function              | 5-1  |

| Table 5.2  | GPIO Pin Configuration                                  |      |

| Table 6.1  | Serial EEPROM SMBus Address                             |      |

| Table 6.2  | PES24N3A Compatible Serial EEPROMs                      |      |

| Table 6.3  | Serial EEPROM Initialization Errors                     |      |

| Table 6.4  | I/O Expander Function Allocation                        |      |

| Table 6.5  | I/O Expander 0 Signals                                  |      |

| Table 6.6  | I/O Expander 2 Signals                                  |      |

| Table 6.7  | I/O Expander 4 Signals                                  |      |

| Table 6.8  | Slave SMBus Address When a Static Address is Selected   | 6-11 |

| Table 6.9  | Slave SMBus Command Code Fields                         |      |

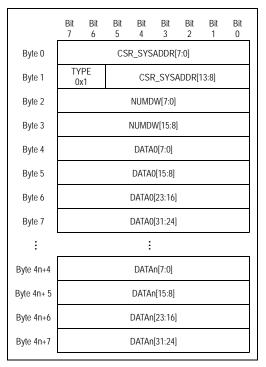

| Table 6.10 | CSR Register Read or Write Operation Byte Sequence      |      |

| Table 6.11 | CSR Register Read or Write CMD Field Description        |      |

| Table 6.12 | Serial EEPROM Read or Write Operation Byte Sequence     |      |

| Table 6.13 | Serial EEPROM Read or Write CMD Field Description       |      |

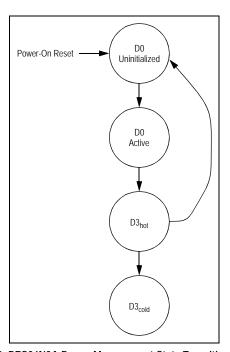

| Table 7.1  | PES24N3A Power Management State Transition Diagram      |      |

| Table 8.1  | Downstream Port Hot-Plug Signals                        |      |

| Table 9.1  | Base Addresses for Port Configuration Space Registers   |      |

| Table 9.2  | Upstream Port 0 Configuration Space Registers           |      |

| Table 9.3  | Downstream Ports 2 and 4 Configuration Space Registers  |      |

| Table 10.1 | JTAG Pin Descriptions                                   |      |

| Table 10.2 | Boundary Scan Chain                                     |      |

| Table 10.3 | Instructions Supported by PES24N3A's JTAG Boundary Scan |      |

| Table 10.4 | System Controller Device Identification Register.       |      |

# RENESAS IDT List of Tables **Notes**

# **List of Figures**

| Figure 1.1  | PES24N3A Architectural Block Diagram                                          | 1-3  |

|-------------|-------------------------------------------------------------------------------|------|

| Figure 1.2  | I/O Expansion Application                                                     |      |

| Figure 1.3  | PES24N3A Logic Diagram                                                        | 1-4  |

| Figure 2.1  | Common Clock on Upstream and Downstream (option to enable or disable Spread   |      |

|             | Spectrum Clock)                                                               | 2-1  |

| Figure 2.2  | Non-Common Clock on Upstream; Common Clock on Downstream (must disable        |      |

|             | Spread Spectrum Clock)                                                        | 2-2  |

| Figure 2.3  | Common Clock on Upstream; Non-Common Clock on Downstream (must disable        |      |

|             | Spread Spectrum Clock)                                                        | 2-2  |

| Figure 2.4  | Non-Common Clock on Upstream and Downstream (must disable Spread Spectrum     |      |

|             | Clock)                                                                        |      |

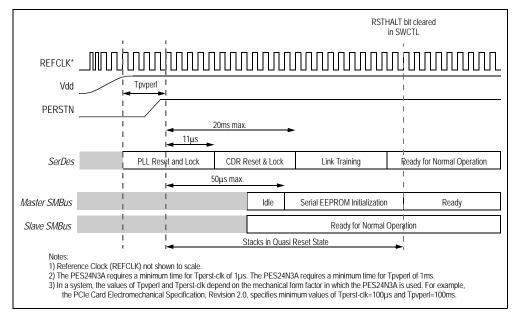

| Figure 2.5  | Fundamental Reset in Transparent Mode with Serial EEPROM initialization       | 2-6  |

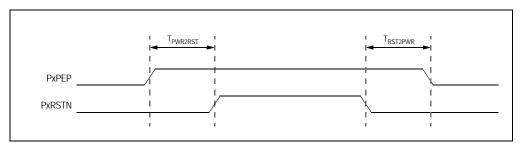

| Figure 2.6  | Power Enable Controlled Reset Output Mode Operation                           |      |

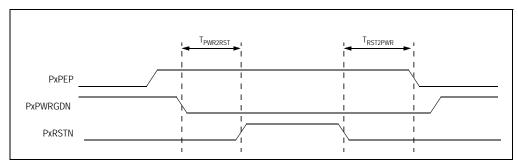

| Figure 2.7  | Power Good Controlled Reset Output Mode Operation                             |      |

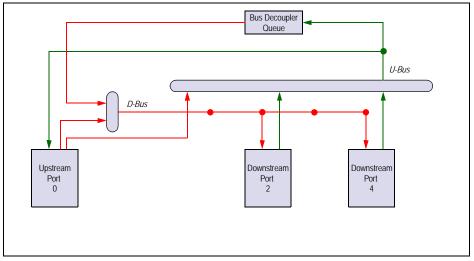

| Figure 3.1  | Simplified Switch Core U-Bus and D-Bus Datapath                               | 3-3  |

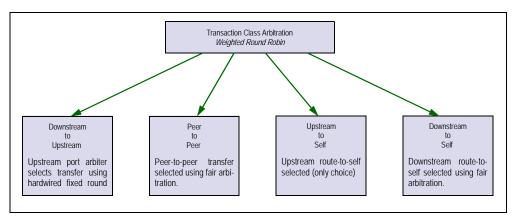

| Figure 3.2  | U-Bus Arbitration                                                             |      |

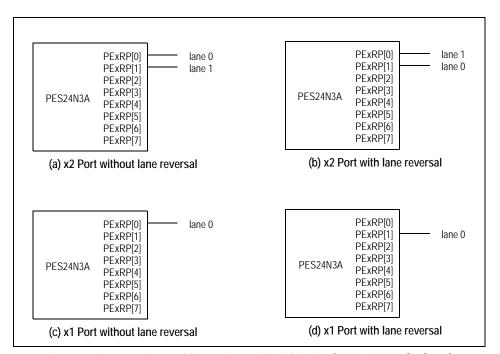

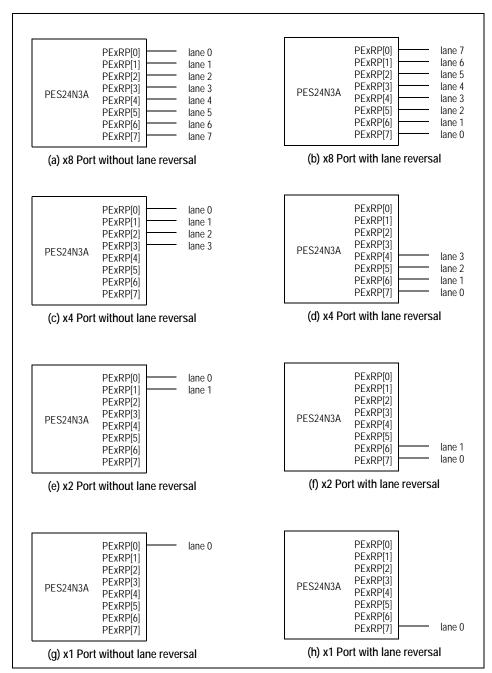

| Figure 4.1  | Port Lane Reversal for Maximum Link Width of x2 (MAXLNKWDTH[5:0]=0x2)         | 4-2  |

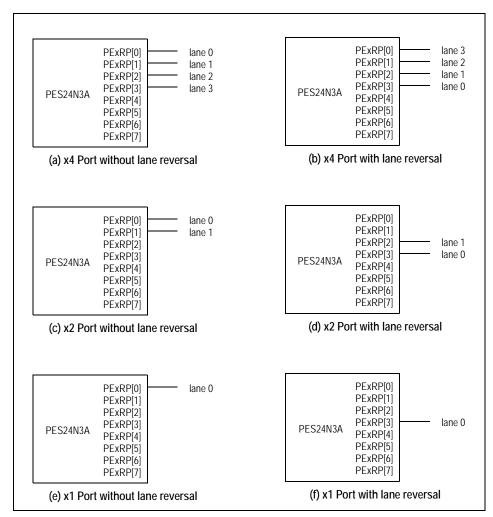

| Figure 4.2  | Port Lane Reversal for Maximum Link Width of x4 (MAXLNKWDTH[5:0]=0x4)         |      |

| Figure 4.3  | Port Lane Reversal for Maximum Link Width of x8 (MAXLNKWDTH[5:0]=0x8)         |      |

| Figure 4.4  | PES24N3A ASPM Link Sate Transitions                                           |      |

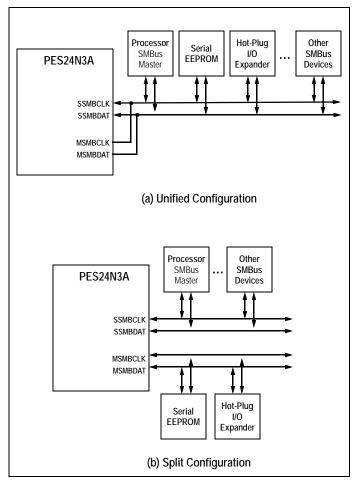

| Figure 6.1  | SMBus Interface Configuration Examples                                        |      |

| Figure 6.2  | Single Double Word Initialization Sequence Format                             |      |

| Figure 6.3  | Sequential Double Word Initialization Sequence Format                         |      |

| Figure 6.4  | Configuration Done Sequence Format                                            |      |

| Figure 6.5  | Slave SMBus Command Code Format                                               |      |

| Figure 6.6  | CSR Register Read or Write CMD Field Format                                   |      |

| Figure 6.7  | Serial EEPROM Read or Write CMD Field Format                                  | 6-15 |

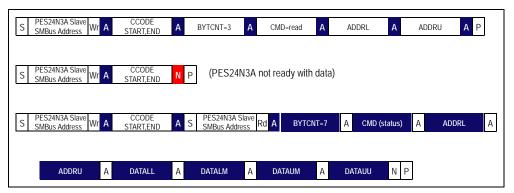

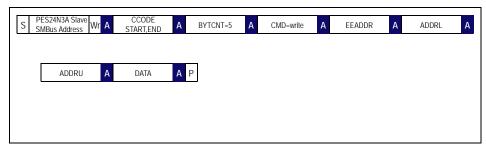

| Figure 6.8  | CSR Register Read Using SMBus Block Write/Read Transactions with PEC          |      |

|             | Disabled                                                                      | 6-16 |

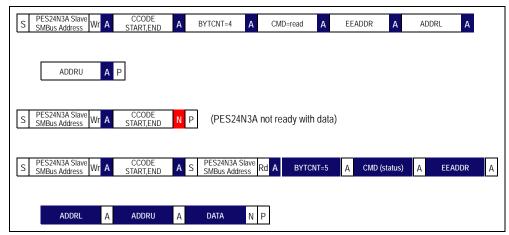

| Figure 6.9  | Serial EEPROM Read Using SMBus Block Write/Read Transactions with PEC         |      |

|             | Disabled                                                                      |      |

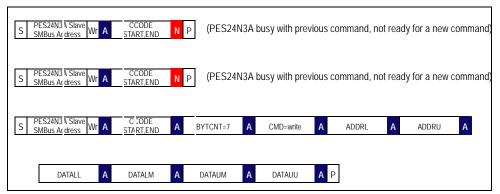

| Figure 6.10 | CSR Register Write Using SMBus Block Write Transactions with PEC Disabled     |      |

| Figure 6.11 | Serial EEPROM Write Using SMBus Block Write Transactions with PEC Disabled    |      |

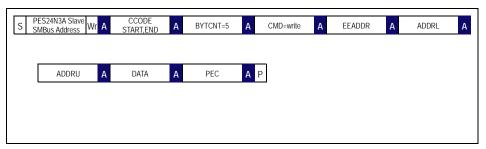

| Figure 6.12 | Serial EEPROM Write Using SMBus Block Write Transactions with PEC Enabled     |      |

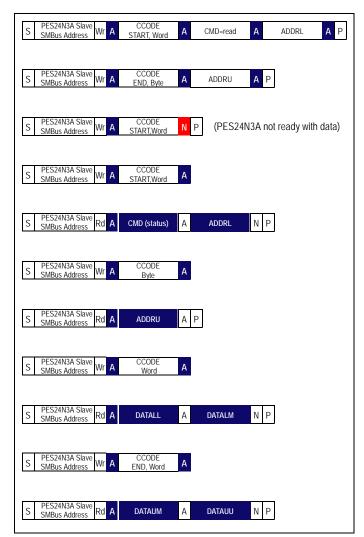

| Figure 6.13 | CSR Register Read Using SMBus Read and Write Transactions with PEC Disabled . |      |

| Figure 7.1  | PES24N3A Power Management State Transition Diagram                            |      |

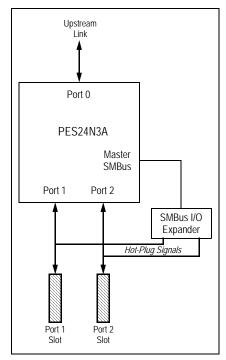

| Figure 8.1  | Hot-Plug on Switch Downstream Slots Application                               |      |

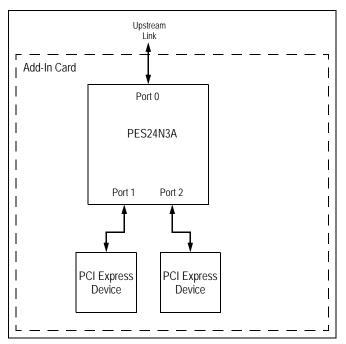

| Figure 8.2  | Hot-Plug with Switch on Add-In Card Application                               | 8-2  |

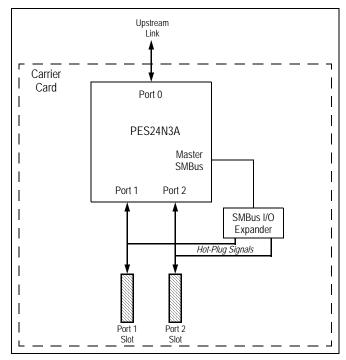

| Figure 8.3  | Hot-Plug with Carrier Card Application                                        | 8-2  |

| Figure 8.4  | PES24N3A Hot-Plug Event Signalling                                            |      |

| Figure 9.1  | Port Configuration Space Organization                                         |      |

| Figure 10.1 | Diagram of the JTAG Logic                                                     | 10-1 |

| Figure 10.2 | State Diagram of PES24N3A's TAP Controller                                    |      |

| Figure 10.3 | Diagram of Observe-only Input Cell                                            |      |

| Figure 10.4 | Diagram of Output Cell                                                        |      |

| Figure 10.5 | Diagram of Bidirectional Cell                                                 | 10-5 |

| Figure 10.6 | Device ID Register Format                                                     | 10-7 |

**Notes** PES24N3A User Manual April 10, 2008

# **Register List**

| AERCAP - AER Capabilities (0x100)                                  | 9-37 |

|--------------------------------------------------------------------|------|

| AERCEM - AER Correctable Error Mask (0x114)                        |      |

| AERCES - AER Correctable Error Status (0x110)                      |      |

| AERCTL - AER Control (0x118)                                       |      |

| AERHL1DW - AER Header Log 1st Doubleword (0x11C)                   |      |

| AERHL2DW - AER Header Log 2nd Doubleword (0x120)                   |      |

| AERHL3DW - AER Header Log 3rd Doubleword (0x124)                   |      |

| AERHL4DW - AER Header Log 4th Doubleword (0x128)                   |      |

| AERUEM - AER Uncorrectable Error Mask (0x108)                      |      |

| AERUES - AER Uncorrectable Error Status (0x104)                    |      |

| AERUESV - AER Uncorrectable Error Severity (0x10C)                 |      |

| BARO - Base Address Register 0 (0x010)                             |      |

| BAR1 - Base Address Register 1 (0x014)                             |      |

| BCTRL - Bridge Control Register (0x03E)                            |      |

| BIST - Built-in Self Test Register (0x00F)                         |      |

| CAPPTR - Capabilities Pointer Register (0x034)                     |      |

| CCODE - Class Code Register (0x009)                                |      |

| CLS - Cache Line Size Register (0x00C)                             |      |

| DARBCTC - D-Bus Arbiter Current Transfer Count (0x464)             |      |

| DARBTC - D-Bus Arbiter Transfer Count (0x460)                      |      |

| DID - Device Identification Register (0x002)                       |      |

| ECFGADDR - Extended Configuration Space Access Address (0x0F8)     |      |

| ECFGDATA - Extended Configuration Space Access Data (0x0FC)        |      |

| EEPROMINTF - Serial EEPROM Interface (0x42C)                       |      |

| EROMBASE - Expansion ROM Base Address Register (0x038)             |      |

| GPECTL - General Purpose Event Control (0x450)                     |      |

| GPESTS - General Purpose Event Status (0x454)                      |      |

| GPIOCFG - General Purpose I/O Configuration (0x41C)                |      |

| GPIOD - General Purpose I/O Data (0x420)                           |      |

| GPIOFUNC - General Purpose I/O Control Function (0x418)            |      |

| GPR - General Purpose Register (0x40C)                             |      |

| HDR - Header Type Register (0x00E)                                 |      |

| HPCFGCTL - Hot-Plug Configuration Control (0x408)                  |      |

| INTRLINE - Interrupt Line Register (0x03C)                         |      |

| INTRPIN - Interrupt PIN Register (0x03D)                           |      |

| IOBASE - I/O Base Register (0x01C)                                 |      |

| IOBASEU - I/O Base Upper Register (0x030)                          |      |

| IOEXPADDRO - SMBus I/O Expander Address 0 (0x434)                  |      |

| IOEXPADDR1 - SMBus I/O Expander Address 1 (0x438)                  |      |

| IOEXPINTF - I/O Expander Interface (0x430)                         |      |

| IOLIMIT - I/O Limit Register (0x01D)                               |      |

| IOLIMITU - I/O Limit Upper Register (0x032)                        | 9-19 |

| MBASE - Memory Base Register (0x020)                               |      |

| MLIMIT - Memory Limit Register (0x022)                             |      |

| MSIADDR - Message Signaled Interrupt Address (0x0D4)               |      |

| MSICAP - Message Signaled Interrupt Capability and Control (0x0D0) |      |

| MSIMDATA - Message Signaled Interrupt Message Data (0x0DC)         |      |

| MSIUADDR - Message Signaled Interrupt Upper Address (0x0D8)        |      |

| PBUSN - Primary Bus Number Register (0x018)                        |      |

| PCICMD - PCI Command Register (0x004)                                  | 9-12 |

|------------------------------------------------------------------------|------|

| PCIECAP - PCI Express Capability (0x040)                               | 9-21 |

| PCIEDCAP - PCI Express Device Capabilities (0x044)                     | 9-21 |

| PCIEDCAP2 - PCI Express Device Capabilities 2 (0x064)                  | 9-31 |

| PCIEDCTL - PCI Express Device Control (0x048)                          | 9-22 |

| PCIEDCTL2 - PCI Express Device Control 2 (0x068)                       | 9-31 |

| PCIEDSTS - PCI Express Device Status (0x04A)                           | 9-23 |

| PCIEDSTS2 - PCI Express Device Status 2 (0x06A)                        | 9-31 |

| PCIELCAP - PCI Express Link Capabilities (0x04C)                       | 9-24 |

| PCIELCAP2 - PCI Express Link Capabilities 2 (0x06C)                    | 9-31 |

| PCIELCTL - PCI Express Link Control (0x050)                            | 9-25 |

| PCIELCTL2 - PCI Express Link Control 2 (0x070)                         | 9-32 |

| PCIELSTS - PCI Express Link Status (0x052)                             | 9-26 |

| PCIELSTS2 - PCI Express Link Status 2 (0x072)                          | 9-32 |

| PCIESCAP - PCI Express Slot Capabilities (0x054)                       | 9-27 |

| PCIESCAP2 - PCI Express Slot Capabilities 2 (0x074)                    | 9-32 |

| PCIESCTL - PCI Express Slot Control (0x058)                            | 9-29 |

| PCIESCTL2 - PCI Express Slot Control 2 (0x078)                         |      |

| PCIESSTS - PCI Express Slot Status (0x05A)                             |      |

| PCIESSTS2 - PCI Express Slot Status 2 (0x07A)                          | 9-33 |

| PCIEVCECAP - PCI Express VC Enhanced Capability Header (0x200)         |      |

| PCISTS - PCI Status Register (0x006)                                   |      |

| PLTIMER - Primary Latency Timer (0x00D)                                |      |

| PMBASE - Prefetchable Memory Base Register (0x024)                     |      |

| PMBASEU - Prefetchable Memory Base Upper Register (0x028)              |      |

| PMCAP - PCI Power Management Capabilities (0x0C0)                      |      |

| PMCSR - PCI Power Management Control and Status (0x0C4)                |      |

| PMLIMIT - Prefetchable Memory Limit Register (0x026)                   |      |

| PMLIMITU - Prefetchable Memory Limit Upper Register (0x02C)            |      |

| PVCCAP1- Port VC Capability 1 (0x204)                                  |      |

| PVCCAP2 - Port VC Capability 2 (0x208)                                 |      |

| PVCCTL - Port VC Control (0x20C)                                       |      |

| PVCSTS - Port VC Status (0x20E)                                        |      |

| PWRBCAP - Power Budgeting Capabilities (0x280)                         |      |

| PWRBD - Power Budgeting Data (0x288)                                   |      |

| PWRBDSEL - Power Budgeting Data Select (0x284)                         |      |

| PWRBDV[07] - Power Budgeting Data Value [07] (0x300)                   |      |

| PWRBPBC - Power Budgeting Power Budget Capability (0x28C)              |      |

| RID - Revision Identification Register (0x008)                         |      |

| SBUSN - Secondary Bus Number Register (0x019)                          |      |

| SECSTS - Secondary Status Register (0x01E)                             |      |

| SLTIMER - Secondary Latency Timer Register (0x01B)                     |      |

| SMBUSCTL - SMBus Control (0x428)                                       |      |

| SMBUSSTS - SMBus Status (0x424)                                        |      |

| SNUMCAP - Serial Number Capabilities (0x180)                           |      |

| SNUMLDW - Serial Number Lower Doubleword (0x184)                       |      |

| SNUMUDW - Serial Number Upper Doubleword (0x188)                       |      |

| SSIDSSVID - Subsystem ID and Subsystem Vendor ID (0x0F4)               |      |

| SSIDSSVIDCAP - Subsystem ID and Subsystem Vendor ID Capability (0x0F0) |      |

| SUBUSN - Subordinate Bus Number Register (0x01A)                       |      |

| SWCTL - Switch Control (0x404)                                         |      |

| SWPECNT - Switch Parity Error Count (0x74C)                            |      |

| SWPECTL - Switch Parity Error Control (0x740)                          |      |

| SWPERCTL - Switch Parity Error Reporting Control (0x748)               |      |

| SWPESTS - Switch Parity Error Status (0x744)                           |      |

|                                                                        |      |

| SWSTS - Switch Status (0x400)                              | 9-50 |

|------------------------------------------------------------|------|

| SWTOCNT - Switch Time-Out Count (0x75C)                    |      |

| SWTOCTL - Switch Time-Out Control (0x750)                  |      |

| SWTORCTL - Switch Time-Out Reporting Control (0x758)       | 9-63 |

| SWTOSTS - Switch Time-Out Status (0x754)                   | 9-62 |

| SWTOTSCTL - Switch Time-Out Time-Stamp Control (0x760)     | 9-64 |

| SWTSCNTCTL - Switch Time-Stamp Counter Control (0x4A8)     | 9-61 |

| UARBCTC - U-Bus Arbiter Current Transfer Count (0x45C)     | 9-60 |

| UARBTC - U-Bus Arbiter Transfer Count (0x458)              |      |

| VCR0CAP- VC Resource 0 Capability (0x210)                  | 9-45 |

| VCR0CTL- VC Resource 0 Control (0x214)                     | 9-46 |

| VCR0STS - VC Resource 0 Status (0x218)                     | 9-46 |

| VCR0TBL0 - VC Resource 0 Arbitration Table Entry 0 (0x220) |      |

| VCR0TBL1 - VC Resource 0 Arbitration Table Entry 1 (0x224) | 9-47 |

| VCR0TBL2 - VC Resource 0 Arbitration Table Entry 2 (0x228) | 9-48 |

| VCR0TBL3 - VC Resource 0 Arbitration Table Entry 3 (0x22C) | 9-48 |

| VID - Vendor Identification Register (0x000)               |      |

# IDT Register List **Notes**

## **PES24N3A Device Overview**

## **Notes**

## Introduction

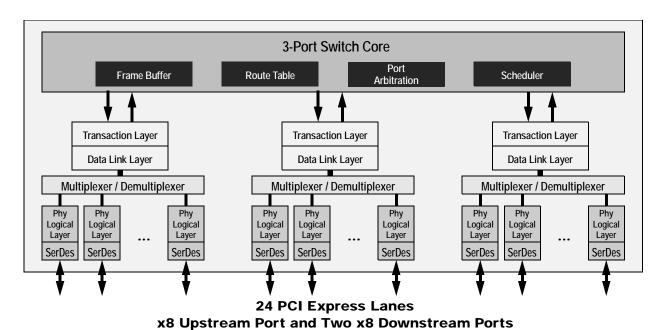

The 89HPES24N3A is a member of the IDT PRECISE™ family of PCI Express® switching solutions. The PES24N3A is a 24-lane, 3-port peripheral chip that performs PCI Express packet switching with a feature set optimized for high performance applications such as servers, storage, and communications/ networking. It provides connectivity and switching functions between a PCI Express upstream port and two downstream ports and supports switching between downstream ports

Utilizing standard PCI Express interconnect, the PES24N3A provides the most efficient I/O connectivity solution for applications requiring high throughput, low latency, and simple board layout with a minimum number of board layers. It provides connectivity for up to 3 ports across 24 integrated serial lanes. Each lane provides 2.5 Gbps of bandwidth in both directions and is fully compliant with PCI Express Base specification revision 1.1.

The PES24N3A is based on a flexible and efficient layered architecture. The PCI Express layers consist of SerDes, Physical, Data Link and Transaction layers. The PES24N3A can operate either as a store and forward switch or a cut-through switch and is designed to switch memory and I/O transactions. It supports eight Traffic Classes (TCs) and one Virtual Channel (VC) with sophisticated resource management to enable efficient switching and I/O connectivity.

## **List of Features**

- ◆ High Performance PCI Express Switch

- Twenty-four 2.5 Gbps PCI Express lanes

- Three switch ports

- Upstream port configurable up to x8

- Downstream ports configurable up to x8

- Low-latency cut-through switch architecture

- Support for Max Payload Size up to 2048 bytes

- One virtual channel

- Eight traffic classes

- PCI Express Base Specification Revision 1.1 compliant

- ◆ Flexible Architecture with Numerous Configuration Options

- Automatic per port link width negotiation to x8, x4, x2 or x1

- Automatic lane reversal on all ports

- Automatic polarity inversion on all lanes

- Ability to load device configuration from serial EEPROM

## Legacy Support

- PCI compatible INTx emulation

- Bus locking

## Highly Integrated Solution

- Requires no external components

- Incorporates on-chip internal memory for packet buffering and queueing

- Integrates twenty-four 2.5 Gbps embedded SerDes with 8B/10B encoder/decoder (no separate transceivers needed)

## **IDT PES24N3A Device Overview**

## **Notes**

## Reliability, Availability, and Serviceability (RAS) Features

- Supports ECRC and Advanced Error Reporting

- Internal end-to-end parity protection on all TLPs ensures data integrity even in systems that do not implement end-to-end CRC (ECRC)

- Supports PCI Express Native Hot-Plug, Hot-Swap capable I/O

- Compatible with Hot-Plug I/O expanders used on PC and server motherboards

## Power Management

- Utilizes advanced low-power design techniques to achieve low typical power consumption

- Supports PCI Power Management Interface specification (PCI-PM 1.1)

- Supports device power management states: D0, D3<sub>hot</sub> and D3<sub>cold</sub>

- Unused SerDes are disabled

## Testability and Debug Features

- Built in Pseudo-Random Bit Stream (PRBS) generator

- Ability to read and write any internal register via the SMBus

- Ability to bypass link training and force any link into any mode

- Provides statistics and performance counters

## ◆ Eight General Purpose Input/Output Pins

- Each pin may be individually configured as an input or output

- Each pin may be individually configured as an interrupt input

- Some pins have selectable alternate functions

- ◆ Packaged in 27x27mm 420 ball BGA with 1mm ball spacing

## **System Diagrams**

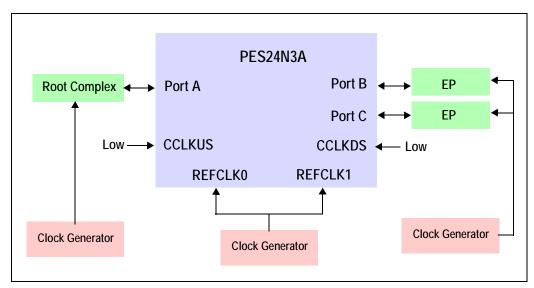

Figure 1.1 PES24N3A Architectural Block Diagram

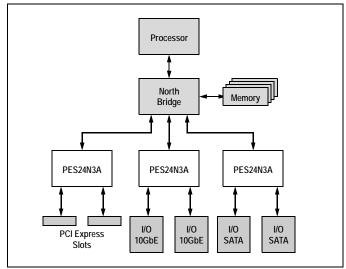

Figure 1.2 I/O Expansion Application

## **Logic Diagram**

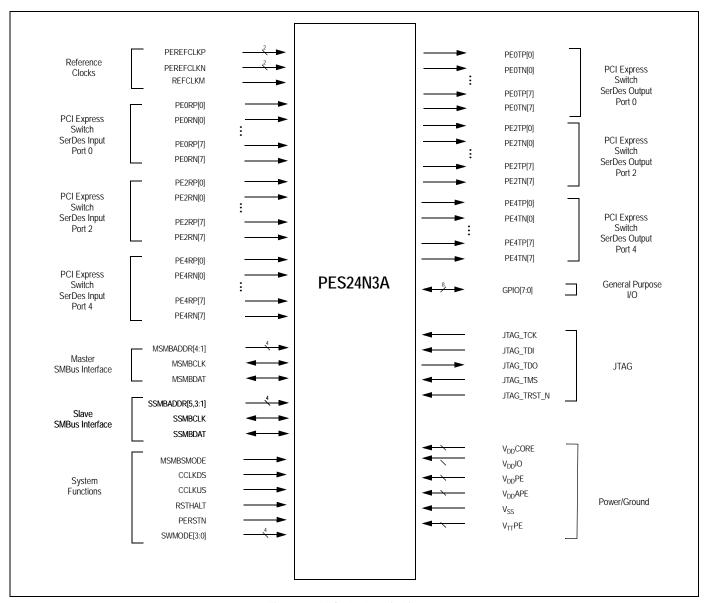

Figure 1.3 PES24N3A Logic Diagram

Note: In the PES24N3A, the two downstream ports are labeled port 2 and port 4.

## **System Identification**

## **Vendor ID**

All vendor ID fields in the device are hardwired to 0x111D which corresponds to Integrated Device Technology, Inc.

## **Device ID**

The PES24N3A device ID is shown in Table 1.1.

| PCIe Device | Device ID |

|-------------|-----------|

| 0x2         | 0x801C    |

Table 1.1 PES24N3A Device ID

## **Revision ID**

The PES24N3A revision ID is shown in Table 1.2.

| Revision ID | Description               |

|-------------|---------------------------|

| 0x0F        | Corresponds to ZA silicon |

| 0x0E        | Corresponds to ZC silicon |

| 0x0D        | Corresponds to ZG silicon |

Table 1.2 PES24N3A Revision ID

## **JTAG ID**

The JTAG ID is:

- Version: Same value as Revision ID. See Table 1.2

- Part number: Same value as base Device ID. See Table 1.1.

- Manufacturer ID: 0x33

- LSB: 0x1

## SSID/SSVID

The PES24N3A contains the mechanisms necessary to implement the PCI-to-PCI bridge Subsystem ID and Subsystem Vendor ID capability structure. However, in the default configuration the Subsystem ID and Subsystem Vendor ID capability structure is not enabled. To enable this capability, the SSID and SSVID fields in the Subsystem ID and Subsystem Vendor ID (SSIDSSVID) register must be initialized with the appropriate ID values. the Next Pointer (NXTPTR) field in one of the other enhanced capabilities should be initialized to point to this capability. Finally, the Next Pointer (NXTPTR) of this capability should be adjusted to point to the next capability if necessary.

## **Device Serial Number Enhanced Capability**

The PES24N3A contains the mechanisms necessary to implement the PCI express device serial number enhanced capability. However, in the default configuration this capability structure is not enabled. To enable the device serial number enhanced capability, the Serial Number Lower Doubleword (SNUMLDW) and the Serial Number Upper Doubleword (SNUMUDW) registers should be initialized. The Next Pointer (NXTPTR) field in one of the other enhanced capabilities should be initialized to point to this capability. Finally, the Next Pointer (NXTPTR) of this capability should be adjusted to point to the next capability if necessary.

## **Pin Description**

The following tables list the functions of the pins provided on the PES24N3A. Some of the functions listed may be multiplexed onto the same pin. The active polarity of a signal is defined using a suffix. Signals ending with an "N" are defined as being active, or asserted, when at a logic zero (low) level. All other signals (including clocks, buses, and select lines) will be interpreted as being active, or asserted, when at a logic one (high) level.

| Signal                           | Туре | Name/Description                                                                                                                                                                                                                                                                                |

|----------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE0RP[7:0]<br>PE0RN[7:0]         | I    | PCI Express Port 0 Serial Data Receive. Differential PCI Express receive pairs for port 0. Port 0 is the upstream port.                                                                                                                                                                         |

| PE0TP[7:0]<br>PE0TN[7:0]         | 0    | PCI Express Port 0 Serial Data Transmit. Differential PCI Express transmit pairs for port 0. Port 0 is the upstream port.                                                                                                                                                                       |

| PE2RP[7:0]<br>PE2RN[7:0]         | I    | PCI Express Port 2 Serial Data Receive. Differential PCI Express receive pairs for port 2.                                                                                                                                                                                                      |

| PE2TP[7:0]<br>PE2TN[7:0]         | 0    | PCI Express Port 2 Serial Data Transmit. Differential PCI Express transmit pairs for port 2.                                                                                                                                                                                                    |

| PE4RP[7:0]<br>PE4RN[7:0]         | I    | PCI Express Port 4 Serial Data Receive. Differential PCI Express receive pairs for port 4.                                                                                                                                                                                                      |

| PE4TP[7:0]<br>PE4TN[7:0]         | 0    | PCI Express Port 4 Serial Data Transmit. Differential PCI Express transmit pairs for port 4.                                                                                                                                                                                                    |

| PEREFCLKP[2:1]<br>PEREFCLKN[2:1] | I    | PCI Express Reference Clock. Differential reference clock pair input. This clock is used as the reference clock by on-chip PLLs to generate the clocks required for the system logic and on-chip SerDes. The frequency of the differential reference clock is determined by the REFCLKM signal. |

| REFCLKM                          | I    | PCI Express Reference Clock Mode Select. This signal selects the frequency of the reference clock input.  0x0 - 100 MHz  0x1 - 125 MHz                                                                                                                                                          |

Table 1.3 PCI Express Interface Pins

| Signal          | Туре | Name/Description                                                                                                                                                                                    |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSMBADDR[4:1]   | I    | <b>Master SMBus Address.</b> These pins determine the SMBus address of the serial EEPROM from which configuration information is loaded.                                                            |

| MSMBCLK         | I/O  | Master SMBus Clock. This bidirectional signal is used to synchronize transfers on the master SMBus. It is active and generating the clock only when the EEPROM or I/O Expanders are being accessed. |

| MSMBDAT         | I/O  | <b>Master SMBus Data</b> . This bidirectional signal is used for data on the master SMBus.                                                                                                          |

| SSMBADDR[5,3:1] | I    | Slave SMBus Address. These pins determine the SMBus address to which the slave SMBus interface responds.                                                                                            |

| SSMBCLK         | I/O  | <b>Slave SMBus Clock</b> . This bidirectional signal is used to synchronize transfers on the slave SMBus.                                                                                           |

| SSMBDAT         | I/O  | Slave SMBus Data. This bidirectional signal is used for data on the slave SMBus.                                                                                                                    |

Table 1.4 SMBus Interface Pins

# RENESAS

| Signal  | Туре | Name/Description                                                                                                                                                                                             |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO[0] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: P2RSTN Alternate function pin type: Output Alternate function: Reset output for downstream port 2 |

| GPIO[1] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: P4RSTN Alternate function pin type: Output Alternate function: Reset output for downstream port 4 |

| GPIO[2] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: IOEXPINTNO Alternate function pin type: Input Alternate function: I/O Expander interrupt 0 input  |

| GPIO[3] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                |

| GPIO[4] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: IOEXPINTN2 Alternate function pin type: Input Alternate function: I/O Expander interrupt 2 input  |

| GPIO[5] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                |

| GPIO[6] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                |

| GPIO[7] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: GPEN Alternate function pin type: Output Alternate function: General Purpose Event (GPE) output   |

Table 1.5 General Purpose I/O Pins

| Signal    | Туре | Name/Description                                                                                                                                                  |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCLKDS    | I    | Common Clock Downstream. When the CCLKDS pin is asserted, it indicates that a common clock is being used between the downstream device and the downstream port.   |

| CCLKUS    | I    | Common Clock Upstream. When the CCLKUS pin is asserted, it indicates that a common clock is being used between the upstream device and the upstream port.         |

| MSMBSMODE | I    | Master SMBus Slow Mode. The assertion of this pin indicates that the master SMBus should operate at 100 KHz instead of 400 KHz. This value may not be overridden. |

Table 1.6 System Pins (Part 1 of 2)

| Signal      | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PERSTN      | I    | Fundamental Reset. Assertion of this signal resets all logic inside PES24N3A and initiates a PCI Express fundamental reset.                                                                                                                                                                                                                                                                                             |

| RSTHALT     | I    | Reset Halt. When this signal is asserted during a PCI Express fundamental reset, PES24N3A executes the reset procedure and remains in a reset state with the Master and Slave SMBuses active. This allows software to read and write registers internal to the device before normal device operation begins. The device exits the reset state when the RSTHALT bit is cleared in the SWCTL register by an SMBus master. |

| SWMODE[3:0] | I    | Switch Mode. These configuration pins determine the PES24N3A switch operating mode.  0x0 - Normal switch mode  0x1 - Normal switch mode with Serial EEPROM initialization  0x2 - through 0xF Reserved                                                                                                                                                                                                                   |

Table 1.6 System Pins (Part 2 of 2)

| Signal      | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG_TCK    | I    | JTAG Clock. This is an input test clock used to clock the shifting of data into or out of the boundary scan logic or JTAG Controller. JTAG_TCK is independent of the system clock with a nominal 50% duty cycle.                                                                                                                                                                                                                                                 |

| JTAG_TDI    | I    | JTAG Data Input. This is the serial data input to the boundary scan logic or JTAG Controller.                                                                                                                                                                                                                                                                                                                                                                    |

| JTAG_TDO    | 0    | JTAG Data Output. This is the serial data shifted out from the boundary scan logic or JTAG Controller. When no data is being shifted out, this signal is tri-stated.                                                                                                                                                                                                                                                                                             |

| JTAG_TMS    | I    | JTAG Mode. The value on this signal controls the test mode select of the boundary scan logic or JTAG Controller.                                                                                                                                                                                                                                                                                                                                                 |

| JTAG_TRST_N | I    | JTAG Reset. This active low signal asynchronously resets the boundary scan logic and JTAG TAP Controller. An external pull-up on the board is recommended to meet the JTAG specification in cases where the tester can access this signal. However, for systems running in functional mode, one of the following should occur:  1) actively drive this signal low with control logic 2) statically drive this signal low with an external pull-down on the board |

Table 1.7 Test Pins

| Signal               | Туре | Name/Description                                                                                      |

|----------------------|------|-------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> CORE | I    | Core V <sub>DD</sub> . Power supply for core logic.                                                   |

| V <sub>DD</sub> IO   | I    | I/O V <sub>DD</sub> . LVTTL I/O buffer power supply.                                                  |

| V <sub>DD</sub> PE   | I    | <b>PCI Express Digital Power</b> . PCI Express digital power used by the digital power of the SerDes. |

Table 1.8 Power and Ground Pins

| Signal              | Туре | Name/Description                                                                              |

|---------------------|------|-----------------------------------------------------------------------------------------------|

| V <sub>DD</sub> APE | I    | <b>PCI Express Analog Power.</b> PCI Express analog power used by the PLL and bias generator. |

| V <sub>TT</sub> PE  | I    | PCI Express Termination Power.                                                                |

| V <sub>SS</sub>     | I    | Ground.                                                                                       |

Table 1.8 Power and Ground Pins

## **Pin Characteristics**

**Note:** Some input pads of the PES24N3A do not contain internal pull-ups or pull-downs. Unused inputs should be tied off to appropriate levels. This is especially critical for unused control signal inputs which, if left floating, could adversely affect operation. Also, any input pin left floating can cause a slight increase in power consumption.

| Function            | Pin Name        | Туре | Buffer  | I/O<br>Type      | Internal<br>Resistor <sup>1</sup> | Notes                            |

|---------------------|-----------------|------|---------|------------------|-----------------------------------|----------------------------------|

| PCI Express         | PE0RN[7:0]      | I    | CML     | Serial link      |                                   |                                  |

| Interface           | PE0RP[7:0]      | I    |         |                  |                                   |                                  |

|                     | PE0TN[7:0]      | 0    |         |                  |                                   |                                  |

|                     | PE0TP[7:0]      | 0    |         |                  |                                   |                                  |

|                     | PE2RN[7:0]      | I    |         |                  |                                   |                                  |

|                     | PE2RP[7:0]      | I    |         |                  |                                   |                                  |

|                     | PE2TN[7:0]      | 0    |         |                  |                                   |                                  |

|                     | PE2TP[7:0]      | 0    |         |                  |                                   |                                  |

|                     | PE4RN[7:0]      | I    |         |                  |                                   |                                  |

|                     | PE4RP[7:0]      | I    |         |                  |                                   |                                  |

|                     | PE4TN[7:0]      | 0    |         |                  |                                   |                                  |

|                     | PE4TP[7:0]      | 0    |         |                  |                                   |                                  |

|                     | PEREFCLKN[2:1]  | I    | LVPECL/ | Diff. Clock      |                                   | Refer to Table 9                 |

|                     | PEREFCLKP[2:1]  | I    | CML     | Input            |                                   | in the<br>PES24N3A Data<br>Sheet |

|                     | REFCLKM         |      | LVTTL   | Input            | pull-down                         |                                  |

| SMBus               | MSMBADDR[4:1]   | I    | LVTTL   | Input            | pull-up                           |                                  |

|                     | MSMBCLK         | I/O  |         | STI <sup>2</sup> |                                   | pull-up on board                 |

|                     | MSMBDAT         | I/O  |         | STI              |                                   | pull-up on board                 |

|                     | SSMBADDR[5,3:1] | I    |         | Input            | pull-up                           |                                  |

|                     | SSMBCLK         | I/O  |         | STI              |                                   | pull-up on board                 |

|                     | SSMBDAT         | I/O  |         | STI              |                                   | pull-up on board                 |

| General Purpose I/O | GPIO[7:0]       | I/O  | LVTTL   | High Drive       | pull-up                           | _                                |

Table 1.9 Pin Characteristics (Part 1 of 2)

| Function     | Pin Name    | Туре | Buffer | I/O<br>Type | Internal<br>Resistor <sup>1</sup> | Notes                  |

|--------------|-------------|------|--------|-------------|-----------------------------------|------------------------|

| System Pins  | CCLKDS      | I    | LVTTL  | Input       | pull-up                           |                        |

|              | CCLKUS      | I    |        |             | pull-up                           |                        |

|              | MSMBSMODE   | I    |        |             | pull-down                         |                        |

|              | PERSTN      | I    |        |             |                                   |                        |

|              | RSTHALT     | I    |        |             | pull-down                         |                        |

|              | SWMODE[3:0] | I    |        |             | pull-down                         |                        |

| EJTAG / JTAG | JTAG_TCK    | I    | LVTTL  | STI         | pull-up                           |                        |

|              | JTAG_TDI    | I    |        | STI         | pull-up                           |                        |

|              | JTAG_TDO    | 0    |        |             |                                   |                        |

|              | JTAG_TMS    | I    |        | STI         | pull-up                           |                        |

|              | JTAG_TRST_N | I    |        | STI         | pull-up                           | External pull-<br>down |

Table 1.9 Pin Characteristics (Part 2 of 2)

$<sup>^{1\</sup>cdot}$  Internal resistor values under typical operating conditions are 54K  $\Omega$  for pull-up and 251K  $\Omega$  for pull-down.

<sup>&</sup>lt;sup>2.</sup> Schmitt Trigger Input (STI).

# Clocking, Reset, and Initialization

## **Notes**

## Introduction

The PES24N3A has two differential reference clock inputs that are used internally to generate all of the clocks required by the internal switch logic and the SerDes. While not required, it is recommended that both reference clock input pairs be driven from a common clock source. The frequency of the reference clock inputs may be selected by the Reference Clock Mode Select (REFCLKM) input.

| REFCLKM | Description                    |

|---------|--------------------------------|

| 0       | 100 MHz reference clock input. |

| 1       | 125 MHz reference clock input. |

Table 2.1 Reference Clock Mode Encoding

Each of the reference clock differential inputs feeds several on-chip PLLs. Each PLL generates a 2.5 GHz clock which is used by several SerDes lanes and produces a 250 MHz core clock.

## **Clock Operation**

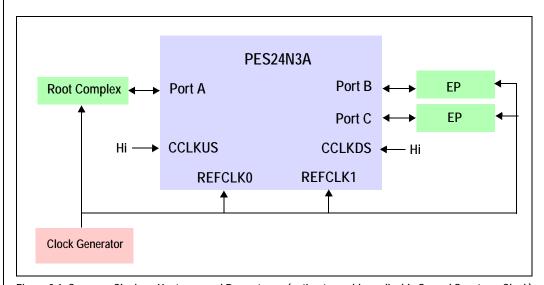

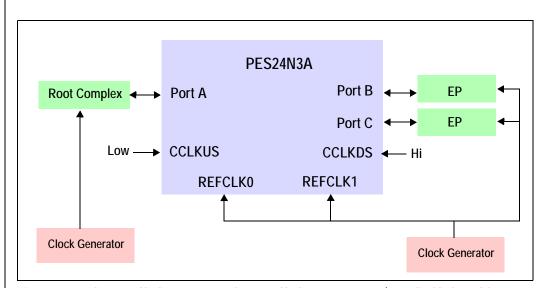

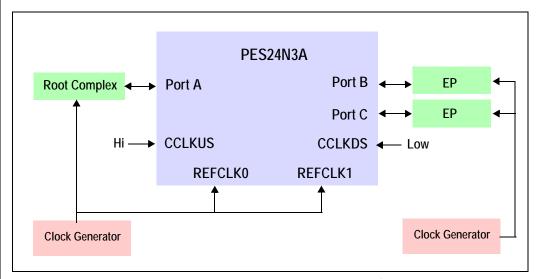

When the CCLKUS and CCLKDS pins are asserted, they indicate that a common clock is being used between the upstream device and the upstream port, as well as between the downstream devices and the downstream ports. The Spread Spectrum Clock (SSC) must be disabled when the non-common clock is used on either the upstream port or downstream port. Figures 2.1 through 2.4 illustrate the operation of the CCLKUS and CCLKDS clocks using a common clock and a non-common clock.

Figure 2.1 Common Clock on Upstream and Downstream (option to enable or disable Spread Spectrum Clock)

Figure 2.2 Non-Common Clock on Upstream; Common Clock on Downstream (must disable Spread Spectrum Clock)

Figure 2.3 Common Clock on Upstream; Non-Common Clock on Downstream (must disable Spread Spectrum Clock)

Figure 2.4 Non-Common Clock on Upstream and Downstream (must disable Spread Spectrum Clock)

## Initialization

A boot configuration vector consisting of the signals listed in Table 2.2 is sampled by the PES24N3A during a fundamental reset when PERSTN is negated. The boot configuration vector defines essential parameters for switch operation. Since the boot configuration vector is sampled only during a fundamental reset sequence, the value of signals which make up the boot configuration vector is ignored during other times and their state outside of a fundamental reset has no effect on the operation of the PES24N3A.

While basic switch operation may be configured using signals in the boot configuration vector, advanced switch features may require configuration via an external serial EEPROM. The external serial EEPROM allows modification of any bit in any software visible register. See Chapter 6, SMBus Interfaces, for more information on the serial EEPROM.

The external serial EEPROM and slave SMBus interface may be used to override the function of some of the signals in the boot configuration vector during a fundamental reset. The signals that may be overridden are noted in Table 2.2. The state of all of the boot configuration signals in Table 2.2 sampled during the most recent cold reset may be determined by reading the SWSTS register.

| Signal    | Туре | Name/Description                                                                                                                                                  |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCLKDS    | I    | Common Clock Downstream. When the CCLKDS pin is asserted, it indicates that a common clock is being used between the downstream device and the downstream port.   |

| CCLKUS    | I    | Common Clock Upstream. When the CCLKUS pin is asserted, it indicates that a common clock is being used between the upstream device and the upstream port.         |

| MSMBSMODE | I    | Master SMBus Slow Mode. The assertion of this pin indicates that the master SMBus should operate at 100 KHz instead of 400 KHz. This value may not be overridden. |

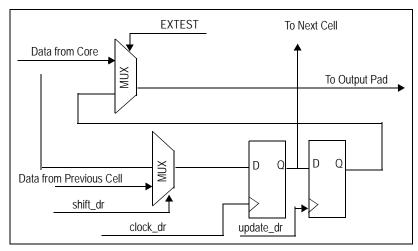

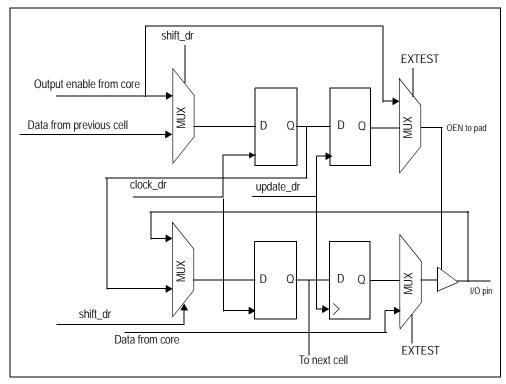

Table 2.2 Boot Configuration Vector Signals (Part 1 of 2)