# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please

confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to

additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

HI7750/4 Renesas Industrial Realtime Operating System Configuration Guide Renesas Microcomputer Development Environment System

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# **Preface**

This guide describes how to configure systems using HI7750/4.

To execute application programs registered as tasks on HI7750/4, the Solution Engine®, the product of Hitachi ULSI Systems Co., Ltd., shall be used as a target board and the HDI of the E10A emulator as a debugger in the initial debug stage. For details about HI7750/4, see the HI7000/4 Series (HI7000/4, HI7700/4, HI7750/4) User's Manual (hereinafter referred to as the HI7000/4 Series User's Manual). To create application programs and link them with HI7750/4, you should use the SuperH<sup>TM</sup> RISC engine C/C++ compiler package (hereinafter referred to as the SHC/C++ compiler) and the Hitachi Embedded Workshop (HEW), which is an integrated development tool, supplied with the SuperH<sup>TM</sup> RISC engine C/C++ compiler package.

This guide describes how to change, add and configure programs before executing the start task on multitasking operating system using the above target board, emulator, and compiler.

#### Related manuals

- HI7000/4 Series (HI7000/4, HI7700/4, HI7750/4) Hitachi Industrial Realtime Operating System User's Manual

- SuperH RISC engine C/C++ Compiler SH-1, SH-2, SH-2E, SH-3, SH3E, SH-4 User's Manual

- SuperH RISC engine C/C++ Compiler Assembler Optimizing Linkage Editor User's Manual

- H Series Linkage Editor, Librarian, and Object Converter User's Manual

- Hitachi Embedded Workshop 2 HEW Debugger User's Manual

- SH7750 Solution Engine<sup>TM</sup> (MS7750SE01) Overview

- The hardware manual and programming manual of the SuperH microcomputer used

Pentium is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

Microsoft® Windows® 95 operating system, Microsoft® Windows NT® operating system and the Windows logo are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

The abbreviation µITRON stands for "Micro Industrial TRON". TRON, in turn, stands for "The Real-time Operating system Nucleus."

Solution Engine® is a registered trademark of Hitachi ULSI Systems Co., Ltd. in Japan.

Other mentioned company and product names are trademarks or registered trademarks of their respective companies.

RENESAS

# Contents

| Sect | tion 1 Introduction                                   | 1  |

|------|-------------------------------------------------------|----|

| 1.1  | Overview                                              | 1  |

| 1.2  | System Configuration                                  | 1  |

| 1.3  | Prerequisites                                         | 2  |

| Sect | tion 2 Creating Application Programs                  | 5  |

| 2.1  | Creating CPU Initialization Routine                   | 6  |

| 2.2  | Creating Tasks                                        | 11 |

|      | 2.2.1 Main Task                                       | 12 |

|      | 2.2.2 LED Task                                        | 14 |

| 2.3  | Creating an Interrupt Handler                         | 14 |

|      | 2.3.1 Creating Initialization Module                  | 17 |

|      | 2.3.2 Creating Interrupt Handler                      | 19 |

| Sect | tion 3 Configuration                                  | 21 |

| 3.1  | Starting Configurator                                 | 22 |

| 3.2  | Interrupt Mask Level                                  | 22 |

| 3.3  | Registering Task                                      | 23 |

| 3.4  | Registering Interrupt Handler                         |    |

| 3.5  | Registering Initialization Routine                    | 28 |

| 3.6  | Registering Event Flag Information                    | 31 |

| 3.7  | Creating Configuration Files                          |    |

| 3.8  | Building the Executable File by HEW                   |    |

|      | 3.8.1 Starting HEW                                    | 34 |

|      | 3.8.2 Defining Configuration File                     | 35 |

|      | 3.8.3 Changing a Linkage Address                      | 37 |

|      | 3.8.4 Build                                           | 41 |

| 3.9  | Disabling Parameter Check Function                    | 42 |

| Sect | tion 4 Downloading and Executing Application Programs | 43 |

| 4.1  | Initializing Solution Engine                          |    |

| 4.2  | Downloading Application Program                       |    |

| 4.3  | Executing Application Program                         |    |

# Section 1 Introduction

#### 1.1 Overview

Follow the procedure below to run application programs on HI7750/4:

- 1. Create application programs.

- 2. Use the configurator to register the application programs to HI7750/4.

- 3. Build the executable file using HEW.

- 4. Install the application programs to the target board, and download and execute them.

This guide describes the above procedure to run the programs on the target board by using a sample program.

# 1.2 System Configuration

This guide describes how to create sample programs of tasks and an interrupt handler and how to run the programs on the target board.

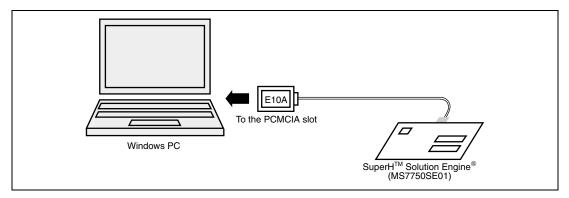

Figure 1.1 shows an example of a hardware configuration.

Figure 1.1 Hardware Configuration Example

Table 1.1 lists software configuration.

**Table 1.1 Software Configuration**

| Program                    | Description                                                                                                         | Туре     | Remarks |

|----------------------------|---------------------------------------------------------------------------------------------------------------------|----------|---------|

| CPU initialization routine | Sets the bus controller.                                                                                            | Non-task |         |

|                            | Initializes the hardware.                                                                                           |          |         |

| Main task                  | Initializes the environment.                                                                                        | Task     |         |

|                            | Waits for an event after initialization by setting the wai_flg flag.                                                |          |         |

|                            | Cancels the wait status by setting the event flag of the timer interrupt handler and starts the LED task (sta_tsk). |          |         |

| LED task                   | Started by the main task to turn the LED on when it is off or turn it off when it is on, and then terminates.       | Task     |         |

| Timer interrupt handler    | Started by the timer interrupt every one second and sets the main task event flag (set_flg).                        | Non-task |         |

# 1.3 Prerequisites

Table 1.2 lists hardware and software required to run the application programs on HI7750/4.

Table 1.2 Required Hardware and Software

| Product Name                       | Product Type   | Manufacturer                   |

|------------------------------------|----------------|--------------------------------|

| Windows® personal computer         | _              | Any manufacturer*1             |

| SuperH™ Solution Engine®           | MS7750SE01     | Hitachi ULSI Systems Co., Ltd. |

| E10A emulator                      | HS7750KCM01H   | Hitachi, Ltd.                  |

| SuperH™ RISC engine C/C++ compiler | P0700CAS6-MWR  | Hitachi, Ltd. *2               |

| HI7750/4                           | HS0700ITI41SRE | Hitachi, Ltd. *3               |

Notes: 1. Hardware environment: PC/AT compatible machine with 486DX2/66 MHz or more (Pentium® or later recommended)

Operating system: Windows®2000, WindowNT®4.0, Windows®98, Windows®95 CD-ROM drive

PCMCIA card slot

Memory: 32 Mbytes or more (For Windows®2000 and WindowNT®4.0, memory with 64 Mbytes or more is recommended.)

Free space required on the hard disk: 8 Mbytes or more

Version. 6.0 AR2 of the compiler shall be used. You may also use the compilers from Hitachi ULSI Systems Co., Ltd. or Hitachi Software Engineering Co., Ltd. HI7750/4 with evaluation license (object) shall be used. You may also use HI7750/4 with mass-production license.

The HDI of the E10A emulator, SuperH™ RISC engine C/C++ compiler package, and HI7750/4 (for SHCV6) must have been installed in the Windows® personal computer beforehand. The SH7750 is a target CPU assumed in this manual.

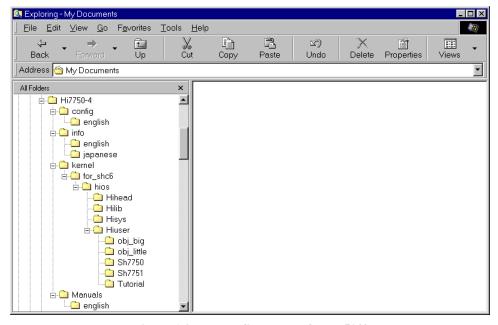

Figure 1.2 shows the folder structure of HI7750/4 that you have just installed.

Figure 1.2 Folder Structure of HI7750/4

The install drive is "D" in this guide, but you may use a desired drive for installing HI7750/4. An install folder is represented as the install folder "folder name" in this manual.

# Section 2 Creating Application Programs

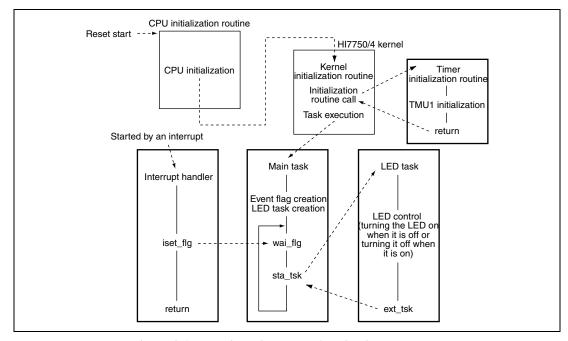

This section describes how to create application programs that run on HI7750/4. Figure 2.1 shows the relationship among application programs. (The programs in the heavy-outline boxes are created in this guide.)

Figure 2.1 Relationship among Application Programs

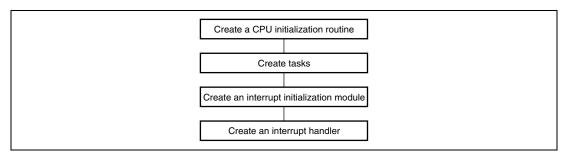

Figure 2.2 shows the programs to be created in this guide.

Figure 2.2 Programs to be Created

# 2.1 Creating CPU Initialization Routine

After the CPU reset, the CPU initialization routine is executed for setting a bus state controller and initializing the hardware.

The ROM monitor supplied with the Solution Engine has already set the bus state controller and initialized the hardware. Thus, this guide omits the description of them.

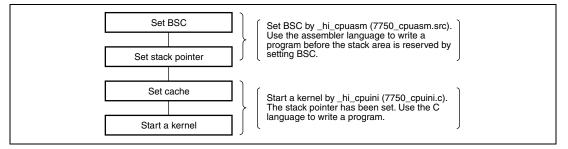

Figure 2.3 shows the procedure to create the CPU initialization routine.

Figure 2.3 Creating a CPU Initialization Routine

In the CPU initialization routine, the stack pointer must be reserved completely before you attempt to execute any program written in the C language. Because the program created by the compiler may locate the stack frame or work area in a stack, you cannot execute it until the stack area is completely reserved.

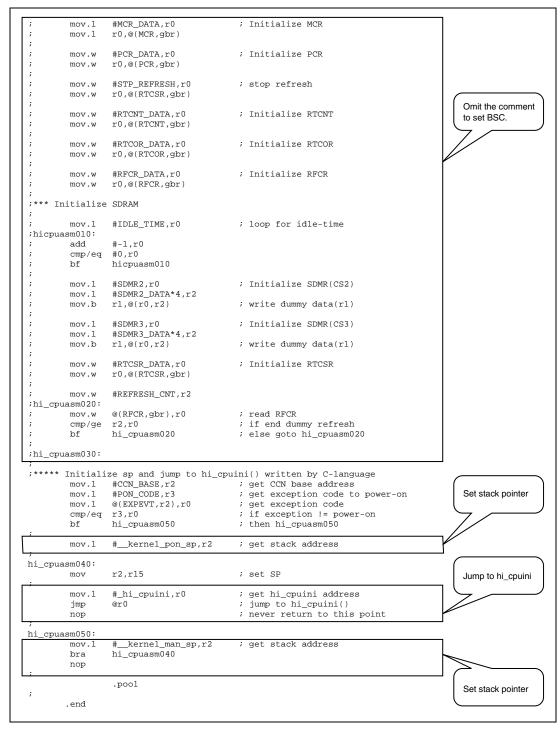

Figures 2.4 to 2.6 show the parts to be changed in of \_hi\_cpuasm (7750\_cpuasm.src).

```

;*

HI7000/4 CPU initialize routine

;*

Copyright (c) Hitachi, Ltd. 2000.

; *;

; *

Licensed Material of Hitachi, Ltd.

; * ;

HI7000/4(HS0700ITI41SR) V1.0

;* FILE = 7612_cpuasm.src;

CPU type = SH7612

.program

_hi_cpuasm

"hi_cpuasm : CPU initialize routine"

.heading

_hi_cpuasm

.export

_hi_cpuini

.section

P_hicpuasm,code,align=4

;* BSC address

.assign h'ffffffc0 ; BSC base address (WCR2)

BSC BASE

.assign h'ffffffe0-BSC_BASE ; BCR1 address offset

CR2

.assign h'ffffffe4-BSC_BASE; BCR2 address offset

.assign h'fffffffc-BSC_BASE; BCR3 address offset

BCR3

.assign h'fffffffe-BSC_BASE; WCR1 address offset

.assign h'fffffffe0-BSC_BASE; WCR2 address offset

.assign h'fffffffe4-BSC_BASE; WCR3 address offset

.assign h'fffffffe0-BSC_BASE; MCR3 address offset

.assign h'fffffff0-BSC_BASE; RTCSR address offset

.assign h'ffffffff0-BSC_BASE; RTCNT address offset

WCR1

WCR3

MCR

RTCSR

RTCNT

.assign h'fffffff8-BSC_BASE ; RTCOR address offset

RTCOR

MD_REG_BASE .assign h'ffff8000

; mode register base address of SDRAM

CMF_BIT

.assign h'0080

; CMF bit in RTCSR

```

Figure 2.4 Parts to be Changed in \_hi\_cpuasm (7750\_cpuasm.src)

```

;* BSC address

BSC_BASE .assign h'ff800000

; BSC

base address

.assign h'ff800000-BSC_BASE ; BCR1

address offset

.assign h'ff800004-BSC_BASE ; BCR2

.assign h'ff800008-BSC_BASE ; WCR1

.assign h'ff80000c-BSC_BASE ; WCR2

address offset

BCR2

address offset address offset

WCR1

WCR 2

.assign h'ff800010-BSC_BASE ; WCR3

address offset

MCB3

.assign h'ff800014-BSC_BASE ; MCR

address offset

address offset

.assign h'ff800018-BSC_BASE ; PCR

PCR

address offset

.assign h'ff80001c-BSC_BASE ; RTCSR

.assign h'ff800020-BSC_BASE ; RTCNT

.assign h'ff800024-BSC_BASE ; RTCOR

RTCSR

RTCNT

address offset

RTCOR

address offset

.assign h'ff800028-BSC BASE ; RFCR

address offset

; SDMR2 address

SDMR 2

.assign h'ff900000

SDMR3

.assign h'ff940000

; SDMR3 address

CMF BIT

.assign h'0080

; CMF bit in RTCSR

;* BSC initial data

After reset, you must initialize BSC for memory(stack) access at first.; *;

Please modify these definition in order to your hardware.

*************************

; BCR1

BCR1_DATA .assign h'00000000

initial data

initial data

; BCR2

BCR2_DATA .assign h'3ffc

WCR1_DATA .assign h'77777777

WCR2_DATA .assign h'fffeefff

; WCR1

; WCR2

initial data initial data

Change the BSC

.assign h'07777777

WCR3 DATA

; WCR3

initial data

value according to

MCR DATA

.assign h'00000000

; MCR

initial data

the hardware

PCR_DATA

.assign

h'0000

; PCR

RTCSR_DATA

.assign

h'a500 + h'00

; RTCSR

RTCNT_DATA

.assign

h'a500 + h'00

; RTCNT

RTCOR_DATA

.assign

h'a500 + h'00

; RTCOR

RFCR_DATA

.assign

h'a400 + h'000

; RFCR

initial data

initial data

initial data

initial data

initial data

STP_REFRESH .assign h'a500

; RTCSR initial data(stop count-up)

.assign h'0230

; SDMR2

SDMR2 DATA

initial data

SDMR3_DATA .assign h'0230

; SDMR3

initial data

IDLE_TIME .assign h'1000

; loop counter for idle-time

; counter for dummy refresh

REFRESH_CNT .assign h'8

= _hi_cpuasm

;*FUNCTION = CPU initialize routine ;

; *;

_hi_cpuasm:

;**** Initialize BSC

mov.1 #BSC_BASE,r0

; set BSC base address to qbr

r0,gbr

mov.l #BCR1_DATA,r0

;

; Initialize BCR1

Omit the comment to

r0,@(BCR1,gbr)

mov.l

set BSC

#BCR2_DATA,r0

; Initialize BCR2

mov.w

mov.w r0,@(BCR2,gbr)

; Initialize WCR1

mov.1

#WCR1_DATA,r0

;

mov.1

r0,@(WCR1,gbr)

mov.1 #WCR2_DATA,r0

; Initialize WCR2

mov.l r0,@(WCR2,gbr)

mov.l

#WCR3_DATA,r0

; Initialize WCR3

;

mov.l

r0,@(WCR3,gbr)

```

Figure 2.5 Parts to be Changed in \_hi\_cpuasm (7750\_cpuasm.src)

Figure 2.6 Parts to be Changed in \_hi\_cpuasm (7750\_cpuasm.src)

Figure 2.7 shows the part to be changed in \_hi\_cpuini (7750\_cpuini.c).

```

HI7750/4 CPU initialize routine

/*

Copyright (c) Hitachi, Ltd. 2001.

Licensed Material of Hitachi, Ltd.

HI7750/4(HS0775ITI41SR) V1.0A

FILE = 7750_cpuini.c;

CPU type = SH7750

#include <machine.h>

#include "itron.h"

#include "kernel.h"

#define CCR DATA 0x0000090d

/* CACHE enable data

/* extern void _INITSCT(void); */ /* section-initialize routine

* /

#pragma section hicpuini

Change from cache

#pragma noregsave(hi_cpuini)

enable to cache

disable

hi_cpuini(void)

{

/*** Initialize <u>Hardware Environment</u> *<u>*</u>*/

vini_cac((UW)CCR_DATA); */

vini_cac((UW)CCR_DATA);

Start a kernel

/*** Initialize Software Environment ***/

_INITSCT();

/* Call section-initialize routine

vsta_knl();

/* Start kernel

```

Figure 2.7 Part to be Changed in \_hi\_cpuini (7750\_cpuini.c)

Set a bus state controller and create a hardware initialization routine for the specific hardware.

# 2.2 Creating Tasks

A task is the main processing of an application program.

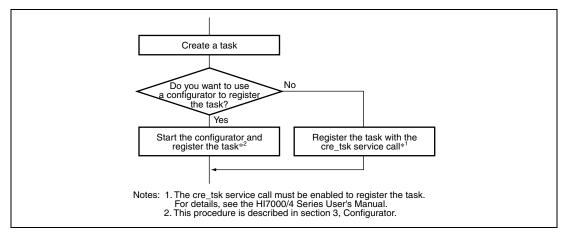

Figure 2.8 shows the procedure to create and register a task.

Figure 2.8 Creating and Registering Task

Create a task by changing the sample (task.c) supplied with HI7750/4. The sample is in the install folder "tutorial".

In this guide, the main task (MainTask) is registered by the configurator and the LED task by the cre\_tsk service call.

#### 2.2.1 Main Task

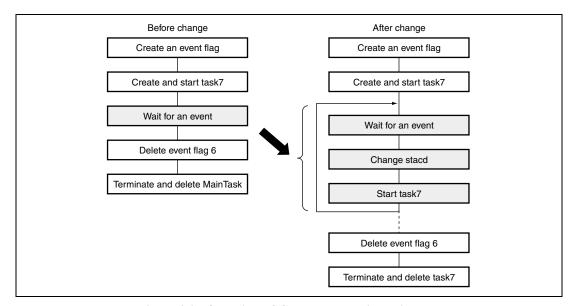

This section describes how to change MainTask contained in the sample program (task.c) supplied with HI7750/4. Figure 2.9 shows the overview of changes made in MainTask. Starting task7 periodically turns the LED on and off.

Figure 2.9 Overview of Changes Made in MainTask

Figure 2.10 shows the parts to be changed in MainTask.

```

Define the include file supplied with the C compiler.

#include <machine.h>

#include "itron.h"

Required when using the HI7750/4 service call.

#include "kernel.h"

#include "kernel_id.h"

Define the LED output port address. For details, see the

#define LED_ADR (UH *)0xb0c00000

Solution Engine Overview Manual.

void MainTask(VP INT exinf);

MainTask and task7 are the main functions for each task.

void task7(VP INT exinf);

Another function never calls them. #pragma noregsave is

valid to suppress the stack area.

#pragma noregsave(MainTask, task7)

* MainTask()

* This task is created and activated by Configurator.

tskid: "ID_MainTask" (defined in kernel_id.h as this task's ID.)

itskori : 6

**************************************

void MainTask(VP_INT exinf)

union CrePacket{

T_CTSK t_ctsk; /* Creation info. for task */

T_CFLG t_cflg; /* Creation info. for event flag */

} packet;

ER ercd;

FLGPTN waiptn, flgptn;

Define the task attribute.

If task7 uses the DSP, use the OR operator to define

/*** Create eventflag-6 ***/

TA COP0.

packet.t_cflg.flgatr = TA_TFIF0 | TA_WSGL | TA_CLR;

(packet.t_ctsk.tskatr = TA_HLNG | TA_ACT | TA_COP0)

packet.t_cflg.iflgptn = 0;

This allows the DSP register to be saved (to guarantee

a kernel) when changing a task.

ercd = cre_flg(6, (T_CFLG *)&packet);

/*** Create task-7 ***/

packet.t_ctsk.tskatr = TA_HLNG | TA_ACT #

packet.t_ctsk.exinf = 0;

packet.t_ctsk.task = (FP)task7;

packet.t_ctsk.itskpri = 7;

Register the task and start it.

packet.t_ctsk.stksz = 0x200;

packet.t ctsk.stk = (VP)NULL;

ercd = cre_tsk(7, (T_CTSK *)&packet);

/*** Wait for eventflag-6 ***/

for(;;) {

waiptn = 0x11111111;

/*** Wait for eventflag-6 ***/

ercd = wai_flg(6, waiptn, TWF_ANDW, &flgptn).

waiptn = 0x11111111;

ercd = wai_flg(6, waiptn, TWF_ANDW, &flgptn);

/*** Delete eventflag-6 ***/

if(exinf == 0x00000000L) {

ercd = del_flg(6);

exinf = 0x0000ff00L;

else

ext_tsk();

exinf = 0x00000000L;

}

ercd = sta_tsk(7,exinf);

Wait for the event flag to set by the interrupt

handler. Change the exinf value and start

task7. At this time, exinf is passed to task7

as a start code.

```

Figure 2.10 Changing MainTask

#### 2.2.2 LED Task

This section describes how to change task7 of the sample program (task.c) supplied with HI7750/4. Figure 2.11 shows the part to be changed in task7.

Figure 2.11 Changing task7

# 2.3 Creating an Interrupt Handler

The interrupt handler is started by an external interrupt that suspends another processing.

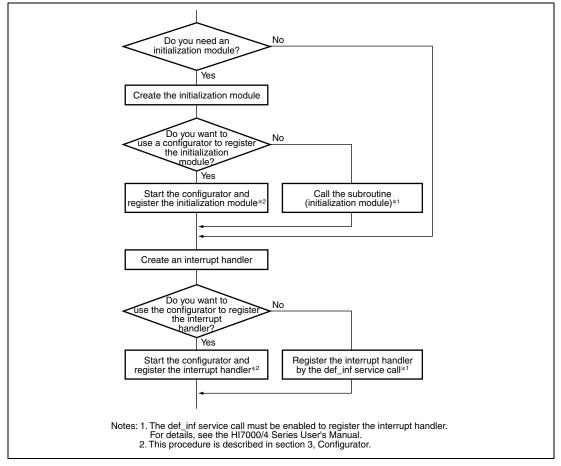

Figure 2.12 shows the procedure to create and register the initialization module and the interrupt handler.

Figure 2.12 Creating and Registering Initialization Module and Interrupt Handler

This guide describes how to use the on-chip TMU1 in the SH7750 to create the interrupt handler and how to use a configurator to register it.

Create the tmu1.c file for the initialization module and the interrupt handler and store the file in the install folder "tutorial".

Table 2.1 lists the interrupt conditions.

# **Table 2.1** Interrupt Conditions

| Item                  | Description                                            | Function | File Name |

|-----------------------|--------------------------------------------------------|----------|-----------|

| Initialization module | Required. Use the configurator to register the module. | TMU1_ini | tmu1.c    |

| Interrupt handler     | Use the configurator to register the handler.          | TMU1_int | tmu1.c    |

| Interrupt cycle       | An interrupt occurs every one second.                  | _        | _         |

| Interrupt level       | 1                                                      | _        |           |

#### 2.3.1 Creating Initialization Module

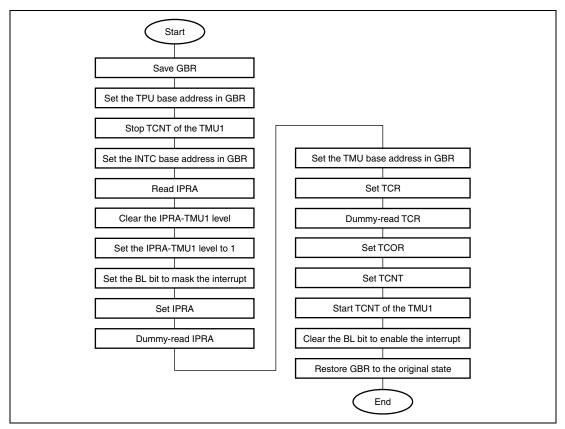

This section describes how to create an initialization module for the on-chip TMU1 in the SH7750. The initialization module initializes the TMU1 and sets the interrupt cycle and level. Figure 2.13 shows the procedure to create the initialization module.

Figure 2.13 Creating Initialization Module

Figures 2.14 and 2.15 show the contents of TMU1\_ini (tmu1.c).

```

#include <machine.h>

#include "itron.h"

#include "kernel.h'

#define BL_BIT 0x10000000

/* BL bit pattern

* /

/* Peripheral Clock (FRQCR set value = H'0E13 (CPU:Bus:P = 200:33:33 MHz)) */

#define PCLK

33333400

/* TSTR set value */

#define TCNT1_STA 0x02

#define TCNT1_STP 0xfd

/* Start TCNT of the TMU1

/* Stop TCNT of the TMU1

/* TCR set value */

#define DIV

#define DIV64

#define UNIE

/* TCNT set value */

#define INTERVAL 1000000

/* 1 second: 1000ms: 1000000us

#define TCNT1_DAT (UW) (((double)INTERVAL/(((double)1000000/(double)PCLK)*(double)DIV))-(double)1)

/* (1 second/ ( (1second/33.3334 MHz)*4))-1 */

/* IPRA set value */

/* TMU1 interrupt level = 1

/* TMU, IPRA I/O address */

/* TMU base address

#define TMU_BASE 0xffd80000

#define TSTR (0xffd80004 - TMU_BASE) /* TMU TSTR

#define TCOR1 (0xffd80014 - TMU_BASE) /* TMU TCOR(ch1)

#define TCNT1 (0xffd80018 - TMU_BASE) /* TMU TCNT(ch1)

#define TCR1 (0xffd8001C - TMU_BASE) /* TMU TCR (ch1)

#define INTC_BASE 0xffd00000 /* INTC base address

#define IPRA (0xffd00004 - INTC_BASE) /* INTC IPR(IPRA:TMU-ch0)

/* NAME = TMU1_ini

/* FUNCTION = initialize the TMU1

void TMU1_ini (void)

gbrsave;

/* GBR save area

UH

/* IPRA retention area

ipra;

gbr and byte(TSTR,TCNT1 STP);

/* Stop the TCNT of the TMU1

/* Dummy-read IPRA

gbr_read_word (IPRA);

set_gbr((VP)TMU_BASE);

/* Set the TPU base address in GBR

gbr_write_word(TCR1,UNIE|DIV4); /* Set TCR

gbr_read_word(TCR1);

/* Dummy-read TCR

* /

set_cr(~BL_BIT & get_cr()); /* Clear the BL bit to enable an interrupt */

set_gbr(gbrsave); /* Restore GRP to the critic ?

```

Figure 2.14 Contents of TMU1\_ini (tmu1.c)

#### 2.3.2 Creating Interrupt Handler

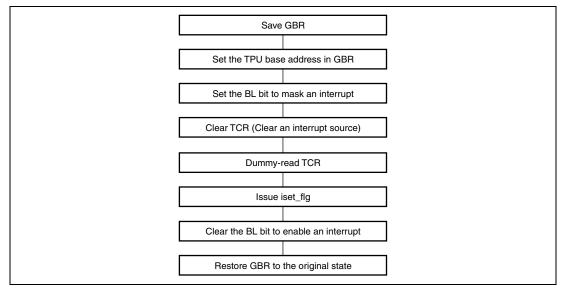

This section describes how to create an interrupt handler for the on-chip TMU1 in the SH7750. The interrupt handler clears an interrupt source of the TMU1 and issues an event flag to task7. Figure 2.15 shows the procedure to create the interrupt handler.

Figure 2.15 Creating Interrupt Handler

Figure 2.17 shows the contents of TMU1\_int (tmu1.c).

```

/* NAME = TMU1_int

* /

/* FUNCTION = TMU1 interrupt handler

void TMU1_int(void)

{

VP

/* GBR save area

*/

gbrsave;

/* Save GBR

/* Set the TPU base address in GBR

/* Set the BL bit to mask an interrupt

gbrsave = get_gbr();

set_gbr((VP)TMU_BASE);

set_cr(BL_BIT | get_cr());

*/

gbr_write_word(TCR1,UNIE|DIV4);

/* Clear UNF

gbr_read_word(TCR1);

/* Dummy-read TCR

* /

iset_flg(6, 0xffffffff);

/* Set an event flag for task7

set_cr(~BL_BIT & get_cr());

/* Clear the BL bit to enable an interrupt */

/* Restore GBR to the original state

set_gbr(gbrsave);

/* ret_int

* /

}

```

Figure 2.17 Contents of TMU1\_int (tmu1.c)

# Section 3 Configuration

Configuration means to register the programs created in section 2 to HI7750/4. HI7750/4 provides a tool that allows easy configuration using GUI and a configurator.

This section describes how to use the configurator to register the application programs.

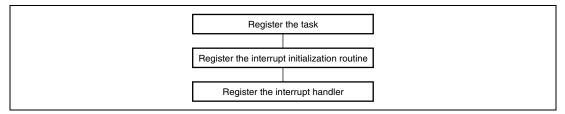

Figure 3.1 shows the programs to be registered in this guide.

Figure 3.1 Programs to be Registered

The defaults are used for programs other than those above.

For details of each program set by the configurator, see the Configurator Help.

RENESAS

# 3.1 Starting Configurator

Double-click the configurator set file (7750.hcf) to start the configurator. The 7750.hcf file is in the install folder "sh7750".

Figure 3.2 shows the Configurator Startup screen.

Figure 3.2 Configurator Startup Screen

# 3.2 Interrupt Mask Level

Table 3.1 lists the interrupt mask levels for the application programs in this guide.

**Table 3.1 Interrupt Mask Levels**

| Туре              | Mask Level | Remarks |  |

|-------------------|------------|---------|--|

| Task              | 0          |         |  |

| Interrupt handler | 1          |         |  |

| Kernel            | 14         | Default |  |

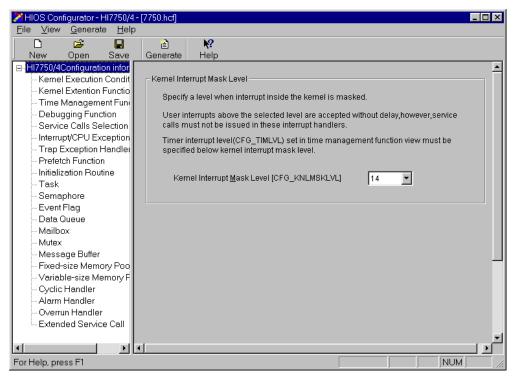

Click kernel operational conditions in the HI7750/4 Configuration Information area on the Configuration Startup screen to view the screen in figure 3.2. In this screen, the mask level for a kernel interrupt can be set. Since the default value (14) is used for the mask level of a kernel interrupt in this guide, you do not need to change the interrupt level.

# 3.3 Registering Task

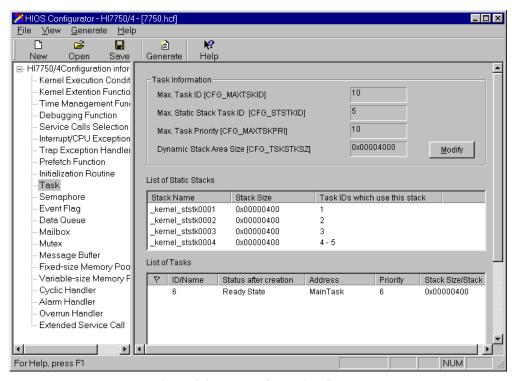

Click Task in the HI7750/4 Configuration Information area on the Configuration Startup screen to view the Task Information screen in figure 3.3.

Figure 3.3 Task Information Screen

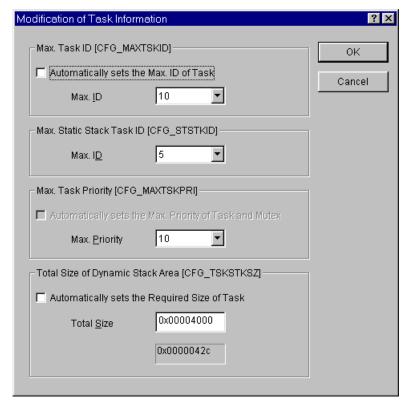

Click the Change button in the Task Information area in figure 3.3 to view the Modification of Task Information screen in figure 3.4.

Figure 3.4 Modification of Task Information Screen

On this screen, you can change the maximum task ID, the maximum task ID using static stacks, maximum task priority, and the total size of the dynamic stack area. For details about differences between static stacks and dynamic stacks, see section 2.6.6, Task Stack, in the HI7000/4 Series User's Manual.

For details about how to calculate the task stack size, see Appendix C, Calculation of Work Area Size, in the HI7000/4 Series User's Manual.

In this guide, the defaults are used for registering the task. You do not need to change the task information.

#### 3.4 Registering Interrupt Handler

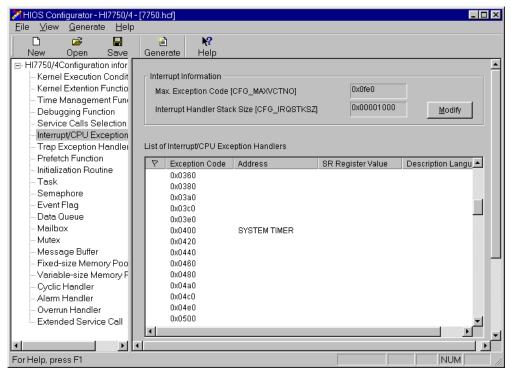

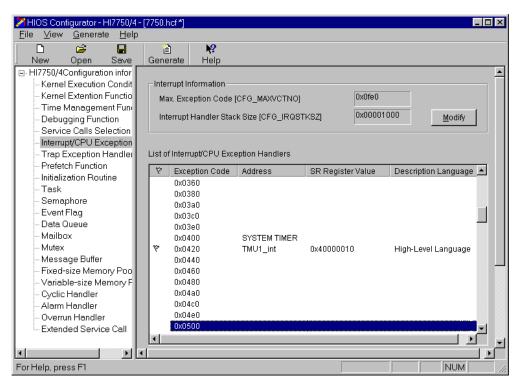

Click Interrupt and CPU Exception Handler in the HI7750/4 Configuration Information area on the Configuration Startup screen to view the List of Interrupt/CPU/Trap Exception Handlers screen in figure 3.5.

Figure 3.5 List of Interrupt/CPU/Trap Exception Handlers Screen

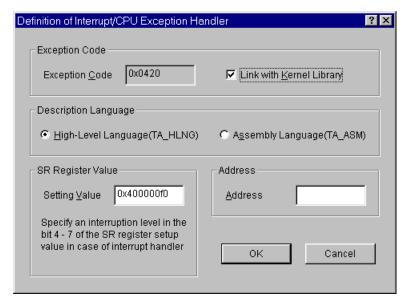

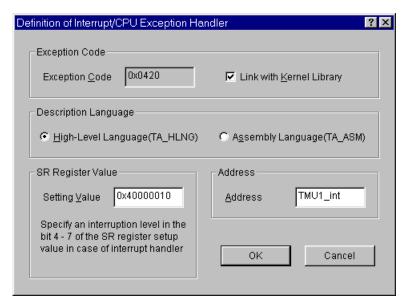

Register the timer interrupt handler in this guide. Use the mouse on the scroll bar on the right of the List of Interrupt/CPU/Trap Exception Handlers to view the exception code around 0x0420. Double click exception code 0x0420 to view the Definition of Interrupt/CPU/Trap Exception Handler screen in figure 3.6.

The exception code, 0x0420, is used for the TMU1 interrupt exception code in this guide. For details of the exception code, see the SH7750 Hardware Manual.

Double click exception code 0x0420 to view the screen shown in figure 3.6.

Figure 3.6 List of Interrupt/CPU/Trap Exception Handlers Screen

Set TMU1\_int in the Address box. The mask level of the interrupt handler in this guide is 1. So change the SR register setting to 0x4000010.

This SR register setting is used as a SR register setting when control is passed to the TMU1\_init interrupt handler. The level should be set to higher than hardware interrupt levels. However, if a service call is issued from the interrupt handler, the level must be set to less than the level of a kernel.

Figures 3.7 and 3.8 show the Definition of Interrupt/CPU/Trap Exception Handler screens after you made definitions.

Figure 3.7 Definition of Interrupt/CPU/Trap Exception Handler Screen

Figure 3.8 Definition of Interrupt/CPU/Trap Exception Handler Screen (after Making Definitions)

## 3.5 Registering Initialization Routine

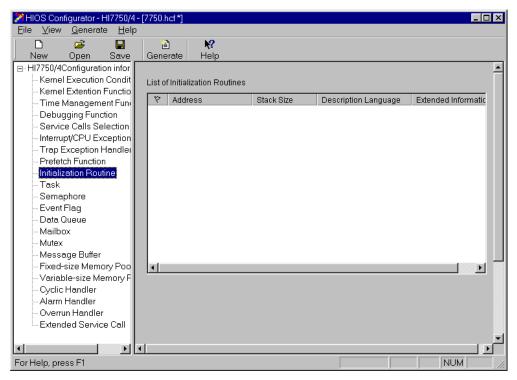

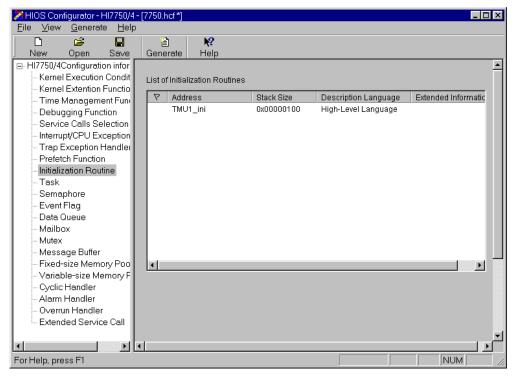

Click Initialization Routine in the HI7750/4 Configuration Information area on the Configurator Startup screen to view the Initialization Routine List screen in figure 3.9.

The initialization routine that is registered on this screen is called immediately after the kernel startup (setup) completes and executed with the kernel mask level (the value set for the kernel operational conditions in the configuration information). This routine differs from the CPU initialization routine that is executed immediately after a reset.

In the initialization routine, the service call of a kernel can be issued.

The issuable service call is the one that can be called from non-task context (system state: N) described in section 3, Service Calls, in the HI7000/4 Series User's Manual.

The initialization routine is used for the following purposes:

- 1. Interrupt initialization

- 2. Initialization routine for task setup

- 3. Event flag, mailbox, or memory pool of which initial setting is to be completed before passing the control to a task or an interrupt handler

Figure 3.9 List of Initialization Routines Screen

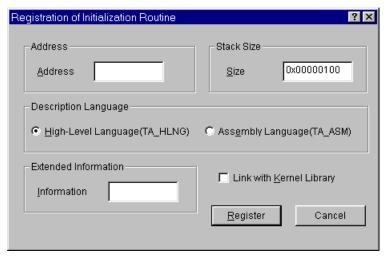

Right click on the blank area of the List of Initialization Routines to view the menu. Then, select Register to view the Registration Initial Routine screen in figure 3.10.

The following explains how to register the initial routine.

Figure 3.10 Registration of Initialization Routine Screen

RENESAS

Set TMU1\_ini in the Address box and click the Register button, and then the Close button. Use the expression below to obtain the stack size.

• TMU1\_ini stack frame size: 8 bytes

• Required size for the initialization routine: 192 + 24 bytes

Total: 224 bytes

For details about how to calculate the stack size, see Appendix C, Calculation of Work Area Size, in the HI7000/4 Series User's Manual. Use the default since the calculated stack size is smaller than it.

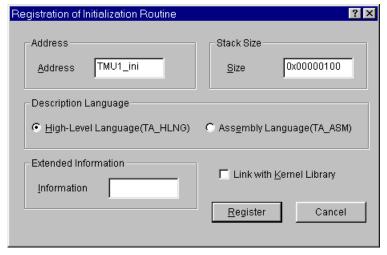

Figure 3.11 shows the Registration of Initialization Routine screen after registration. Figure 3.12 shows the List of Initialization Routines screen after registration.

Figure 3.11 Registration of Initialization Routine Screen (after Registration)

Figure 3.12 List of Initialization Routines Screen (after Registration)

## 3.6 Registering Event Flag Information

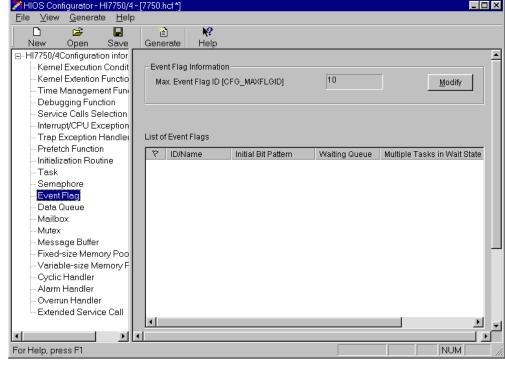

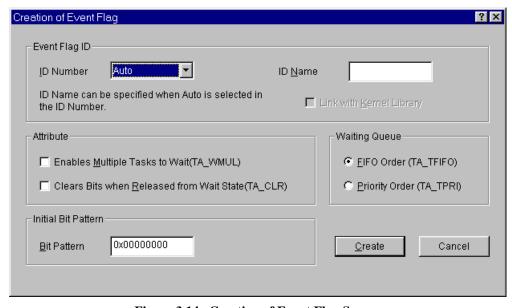

Click Event Flag in the HI7750/4 Configuration Information area on the Configuration Startup screen to view the Event Flag Information screen in figure 3.13.

Click the Change button in the Event Flag Information area to change the maximum event flag ID. Right click on the blank area of the Event Flag List and select Create to view the Creation of Event Flag screen in figure 3.14. For initial creation of an event flag, set the information about the event flag on this screen.

The application implemented in this guide dynamically creates one event flag in the task. Use the default event flag information.

Figure 3.13 Event Flag Information Screen

Figure 3.14 Creation of Event Flag Screen

## 3.7 Creating Configuration Files

Click the Create button on the Configurator Startup screen to create the configuration files required for configuring HI7750/4. For details about the configuration files, see section 5.1.2, Configurator Output File, in the HI7000/4 Series User's manual.

Now, the definition and registration by the configurator are complete. To close 7750.hcf, choose Overwrite or Save As from the File menu to save all the information.

## 3.8 Building the Executable File by HEW

Compile and link the files created by the configurator using HEW supplied with SHC/C++ compiler to create the executable file to be downloaded. This section describes how to build the executable file by HEW.

There are two methods to configure HI7750/4. Table 3.2 lists the type of links.

Table 3.2 Type of Links

| Туре             | Description                                                                                                                                                   |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Whole linkage    | Links the kernel and all configuration files into a single load module (called whole load module).                                                            |  |  |  |

| Separate linkage | Links the kernel code portion (called a kernel load module) and the kernel data portion (called a kernel environment load module) into separate load modules. |  |  |  |

|                  | Application files can be included in a kernel load module, a kernel environment load module, or in an independent application load module.                    |  |  |  |

For details, see section 5, Configuration, in the HI7000/4 Series User's Manual.

This guide describes how to use the whole link method to configure the program in big endian format.

#### 3.8.1 Starting HEW

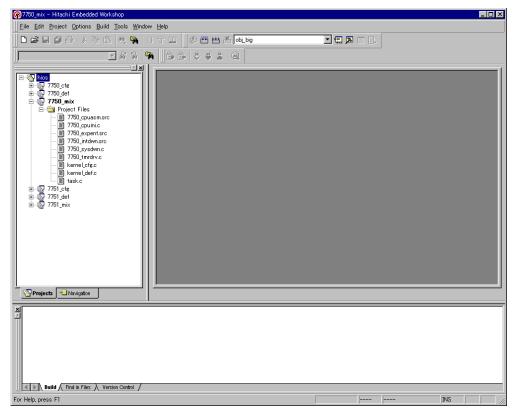

Double click hios.hws in the install folder "hios" to start HEW to build HI7750/4. Figure 3.15 shows the HEW Startup screen.

Figure 3.15 HEW Startup Screen

The standard project file hios.hws contains three sub-projects to configure the program for the target CPU. Table 3.3 lists the type of project files.

Table 3.3 Project Files

| 7750_mix | Project file for creating the whole load module for the whole link method                 |

|----------|-------------------------------------------------------------------------------------------|

| 7750_cfg | Project file for creating the kernel load module for the separate link method             |

| 7750_def | Project file for creating the kernel environment load module for the separate link method |

Select the project file 7750\_mix for creating the whole load module.

## 3.8.2 Defining Configuration File

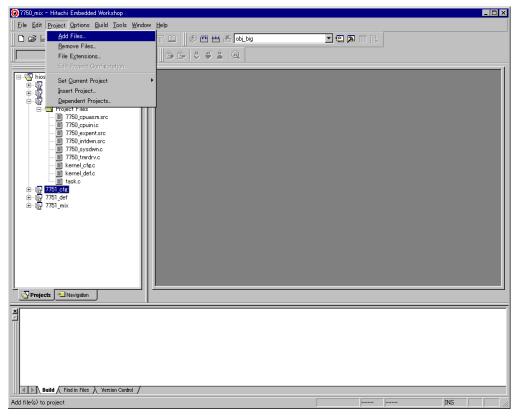

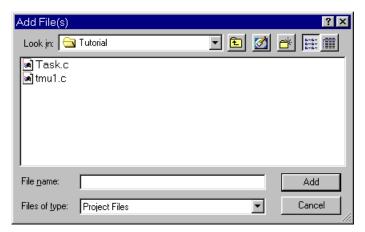

Define each application program created in section 2 as a project file. Use the default project file configuration and define only the timer driver to implement the sample program operation in this guide.

On the Current Project Set screen, select Add Files... from the Project menu to add tmu1.c as a project file. Figures 3.16 and 3.17 show the screen for adding a file.

Figure 3.16 Adding a File

Figure 3.17 Adding a File

Now, defining the configuration files completes.

#### 3.8.3 Changing a Linkage Address

Change the linkage addresses to run the programs on the Solution Engine address map.

The Solution Engine is supplied with 32-Mbyte SDRAM from 0x0C00000 to 0x0FFFFFF. In this guide, 16 Mbytes from 0x0C00000 to 0x0CFFFFFF are used.

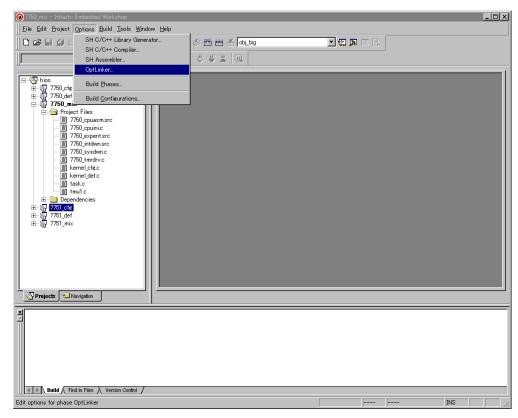

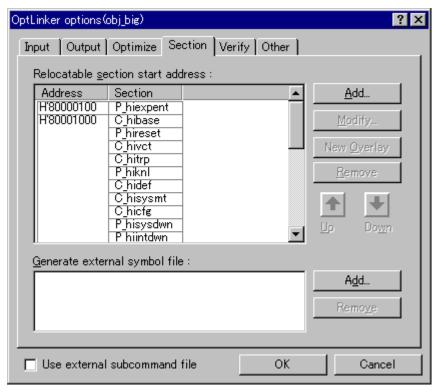

Select OptLinker from the Options menu to view the OptLinker Options screen (figure 3.18).

Figure 3.18 Selecting OptLinker

• Changing a kernel stack pointer

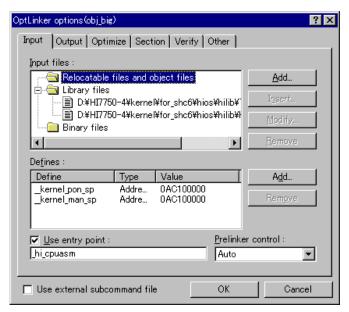

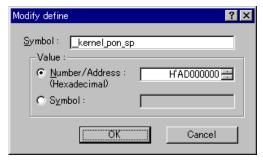

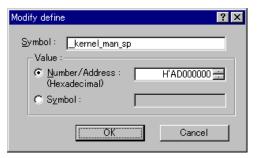

Double click \_kernel\_pon\_sp and \_kernel\_man\_sp in the Input tab and set the value so that the values point to the end address of the RAM mounted on each hardware + 1 (0xAD000000 in P2 space) as shown in figures 3.19 to 3.21.

Figure 3.19 OptLinker options Screen

Figure 3.20 OptLinker options Screen (\_kernel\_pon\_sp)

Figure 3.21 OptLinker options Screen (\_kernel\_man\_sp)

• Changing a section address

Click the Section tab to view the Define Section screen (figure 3.22).

Figure 3.22 Define Section Screen

RENESAS

Click Address for each section to enable the Modify... button. Change the section addresses as listed in table 3.4.

**Table 3.4** Section Addresses

| Section<br>Name | Before<br>Change | After<br>Change | Section<br>Name | Before<br>Change | After<br>Change |

|-----------------|------------------|-----------------|-----------------|------------------|-----------------|

| P_hiexpent      | 80000100         | 8C000100        | B_hiwrk         | 8C000000         | 8C010000        |

| C_hibase        | 80001000         | 8C001000        | B_himpl         | <del></del>      |                 |

| P_hireset       | _                |                 | B_hidystk       | <del></del>      |                 |

| C_hivct         | _                |                 | B_histstk       |                  |                 |

| C_hitrp         | _                |                 | B_hiirqstk      | <del></del>      |                 |

| P_hiknl         | _                |                 | B_hitrcbuf      | <del></del>      |                 |

| C_hidef         | _                |                 | B_hitrcemI      | <del></del>      |                 |

| C_hisysmt       | <del>_</del>     |                 | В               | <u> </u>         |                 |

| C_hicfg         | _                |                 | R               | <del></del>      |                 |

| P_hisysdwn      | _                |                 | P_hicpuasm      | A0000000         | AC000000        |

| P_hiintdwn      | <del>_</del>     |                 | P_hicpuini      | <u> </u>         |                 |

| P_hitmrdrv      | <del>_</del>     |                 |                 |                  |                 |

| Р               | _                |                 |                 |                  |                 |

| С               | _                |                 |                 |                  |                 |

| D               | _                |                 |                 |                  |                 |

#### **3.8.4** Build

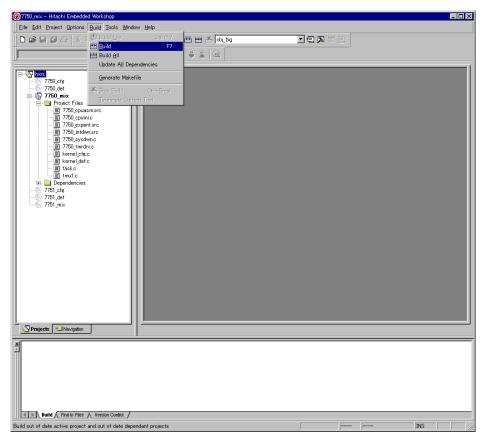

Execute HEW to build an executable file that can be downloaded to the Solution Engine by the E10A emulator. Select Build from the Build menu. Figure 3.23 shows the screen for selecting Build.

Figure 3.23 Selecting Build

The executable file is created by selecting Build. The result of compilation and linkage is shown at the bottom of the window. If a compile error occurs, correct the applicable source and build the file again. The executable file (with the file extension .abs) is created in the install folder "obj\_big".

Now you can download the file to the Solution Engine by the E10A emulator and execute it. For details about how to download and execute the file, see section 4, Downloading and Executing Application Programs.

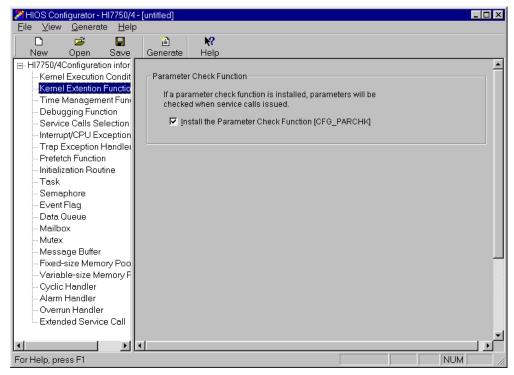

## 3.9 Disabling Parameter Check Function

When debugging the application programs completes and they are ready to be installed into the product, you can disable the parameter check function. This check function is an unnecessary routine performed in the beginning of the service call, in the HI series operating system.

You can use the configurator to disable the parameter check function. Figure 3.24 shows the screen for disabling the parameter check function.

Figure 3.24 Disabling Parameter Check Function

Click Kernel Extended Function on the Configurator Startup screen to view the screen in figure 3.24. Uncheck the Install the Parameter Check Function checkbox and create and build the configuration files. The executable file with the parameter check function disabled is created.

# Section 4 Downloading and Executing Application Programs

This section describes how to use the E10A to download the executable file created in section 3, Configuration, and run it on the Solution Engine.

## 4.1 Initializing Solution Engine

The ROM monitor supplied with the Solution Engine initializes the CPU. In this guide, this monitor is used for the CPU initialization. (When using another board, you must use a specific CPU initialization routine. For details of CPU initialization, see section 2.1, Creating CPU Initialization Routine.)

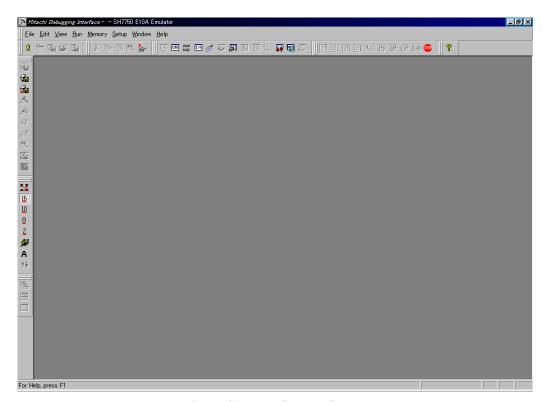

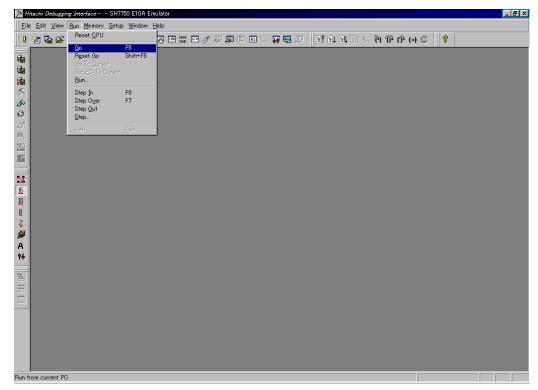

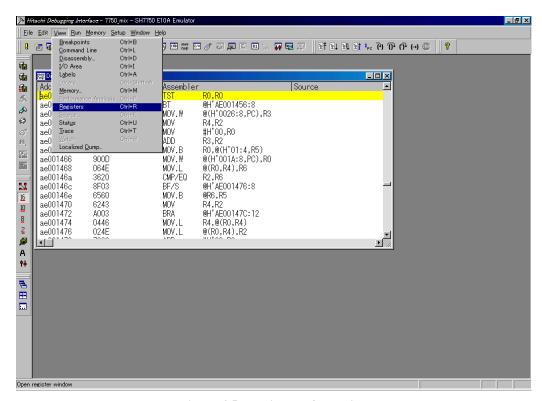

Configure the system as shown in figure 1.1 in section 1, Overview. Start the host computer, turn the Solution Engine on, select HDI for E10A SH7750 from the Windows Start menu to start the HDI. Figure 4.1 shows the HDI Startup screen.

Figure 4.1 HDI Startup Screen

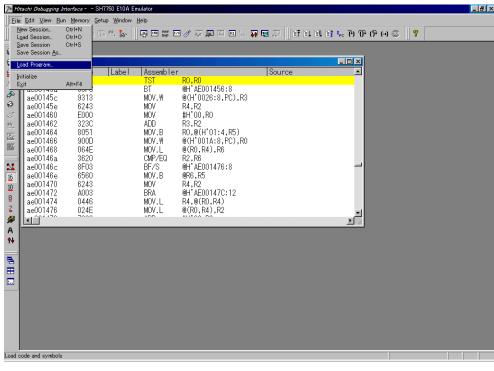

Then, choose Go from the Run menu (figure 4.2).

Figure 4.2 Go menu

After one or two seconds, click the STOP button (red) on the menu bar. Now, initializing the Solution Engine completes and this allows reading from or writing to the SDRAM supplied with the Solution Engine.

## 4.2 Downloading Application Program

Download the executable file created in section 3, Configuration, to the E10A.

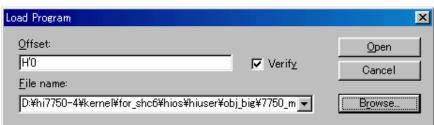

Figure 4.3 shows the screen for downloading the executable file.

Figure 4.3 Downloading Executable File

Select Load Program... from the File menu on the HDI Startup screen. On the Load Program screen in figure 4.3, enter the name of the executable file to download in the File Name box and click the Open button to download it. The executable file is 7750\_mix.abs in the install folder "obj\_big".

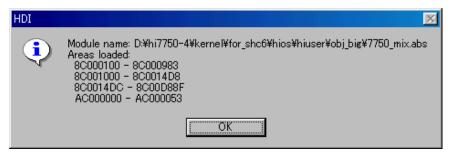

After downloading succeeds, the Complete Download screen in figure 4.4 appears.

Figure 4.4 Complete Download Screen

Click the OK button on the Complete Download screen.

## 4.3 Executing Application Program

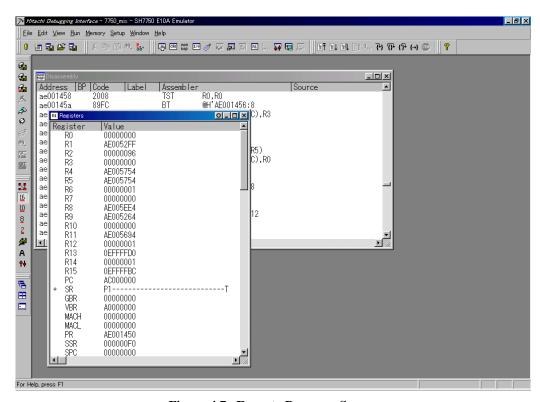

To execute the program, choose Registers from the View menu on the HDI Startup screen to view the register information (figure 4.5).

Figure 4.5 Register Information

Then, change the PC value. Double click the PC value on the Register Information screen to view the Change PC Value screen (figure 4.6).

Rev. 1.0, 03/03, page 46 of 48

Figure 4.6 Change PC Value Screen

Change the PC value to AC000000 as shown in figure 4.6 and click the OK button. This value is the start address of the CPU initialization routine.

Now, you can execute the program. Select Go from the Run menu to execute the program (figure 4.7).

Figure 4.7 Execute Program Screen

## HI7750/4 Hitachi Industrial Realtime Operating System Configuration Guide

Publication Date: 1st Edition, March 2003 Published by: Business Operation Division

Semiconductor & Integrated Circuits

Hitachi, Ltd.

Edited by: Technical Documentation Group

Hitachi Kodaira Semiconductor Co., Ltd.

Copyright © Hitachi, Ltd., 2003. All rights reserved. Printed in Japan.