GreenPAK 2<sup>™</sup> Logic Gates

### **General Description**

Renesas GreenPAK 2 SLG7NT4180 is a low power and small form device. The SoC is housed in a 2.5mm x 2.5mm TDFN package which is optimal for using with small devices.

### **Features**

- Low Power Consumption

- 3.3V Supply Voltage

- RoHS Compliant / Halogen-Free

- Pb-Free TDFN-12 Package

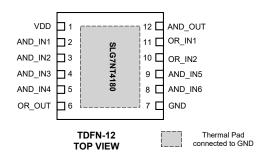

## **Pin Configuration**

### **Output Summary**

• 2 Outputs - Push Pull

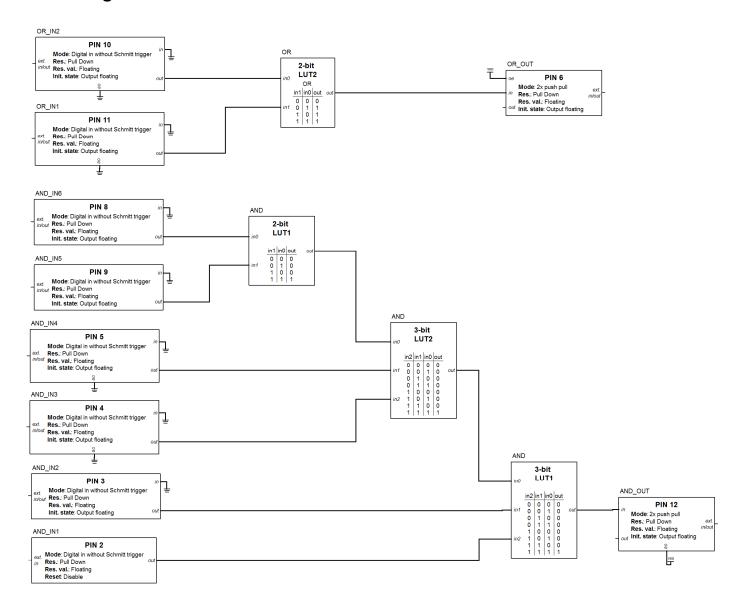

## **Block Diagram**

# Pin Configuration

| Pin#       | Pin Name           | Type   | Pin Description |

|------------|--------------------|--------|-----------------|

| 1          | VDD                | PWR    | Supply Voltage  |

| 2          | AND_IN1            | Input  | Digital Input   |

| 3          | AND_IN2            | Input  | Digital Input   |

| 4          | AND_IN3            | Input  | Digital Input   |

| 5          | AND_IN4            | Input  | Digital Input   |

| 6          | OR_OUT             | Output | Push Pull       |

| 7          | GND                | GND    | Ground          |

| 8          | AND_IN6            | Input  | Digital Input   |

| 9          | AND_IN5            | Input  | Digital Input   |

| 10         | OR_IN0             | Input  | Digital Input   |

| 11         | OR_IN1             | Input  | Digital Input   |

| 12         | AND_OUT            | Output | Push Pull       |

| Exposed    | Exposed Bottom Pad | GND    | Ground          |

| Bottom Pad |                    |        |                 |

**Ordering Information**

| Part Number   | Package Type                             |

|---------------|------------------------------------------|

| SLG7NT4180V   | V = TDFN-12                              |

| SLG7NT4180VTR | VTR = TDFN-12 - Tape and Reel (3k units) |

## **Absolute Maximum Conditions**

| Parameter                 | Min. | Max. | Unit |

|---------------------------|------|------|------|

| V <sub>HIGH</sub> to GND  | -0.3 | 7    | V    |

| Voltage at input pins     | -0.3 | 7    | V    |

| Current at input pin      | -1.0 | 1.0  | mA   |

| Storage temperature range | -65  | 150  | °C   |

| Junction temperature      |      | 150  | °C   |

## **Electrical Characteristics**

(@ 25°C, unless otherwise stated)

| Symbol          | Parameter                                                  | Condition/Note                                            | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| $V_{DD}$        | Supply Voltage                                             |                                                           | 3.0  | 3.3  | 3.6  | V    |

| ΙQ              | Quiescent Current                                          | Static inputs and outputs                                 |      | 1    |      | μΑ   |

| TA              | Operating Temperature                                      |                                                           | -40  | 25   | 85   | °C   |

| lι              | Input Leakage Current                                      | Leakage Current Inputs or outputs in High impedance state | -100 |      | 100  | nA   |

| ViH             | HIGH-Level Input Voltage                                   | Logic Input                                               | 1.8  |      |      | V    |

| VIL             | LOW-Level Input Voltage                                    | Logic Input                                               |      |      | 1.10 | V    |

| V <sub>OH</sub> | HIGH-Level Output Voltage                                  | Push-Pull, I <sub>OH</sub> = 3mA                          | 2.6  |      |      |      |

| Vol             | LOW-Level Output Voltage                                   | Push-Pull, I <sub>OL</sub> = 3mA                          |      |      | 0.32 | V    |

| Vo              | Maximal Voltage Applied to any PIN in High-Impedance State |                                                           |      |      | VDD  | ٧    |

| loL             | LOW-Level Output Current                                   | Push-Pull, VOL = 0.4V, 1X Drive                           | 3.6  |      |      | mA   |

| Tsu             | Start up Time                                              | After VDD reaches 1.6V level                              |      | 7    |      | ms   |

**Logic Gates**

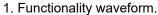

## **SLG7NT4180 Functionality Waveform**

D0 – PIN2 (AND\_IN1)

D1 - PIN3 (AND\_IN2)

D2 – PIN4 (AND\_IN3)

D3 - PIN5 (AND\_IN4)

D4 – PIN9 (AND\_IN5)

D5 – PIN8 (AND\_IN6)

D6 - PIN12 (AND OUT)

D7 – PIN10 (OR\_IN2)

D8 - PIN11 (OR\_IN1)

D9 - PIN6 (OR\_OUT)

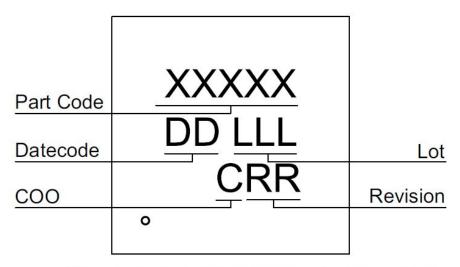

## **Package Top Marking**

XXXXX - Part ID Field: identifies the specific device configuration

DD — Date Code Field: Coded date of manufacture

LLL – Lot Code: Designates Lot #

C – COO: Specifies Country of Origin

RR – Revision Code: Device Revision

| Datasheet<br>Revision | Programming<br>Code Number | Part Code | Revision | Date       |

|-----------------------|----------------------------|-----------|----------|------------|

| 1.01                  | 02                         | 4180V     | AA       | 02/25/2022 |

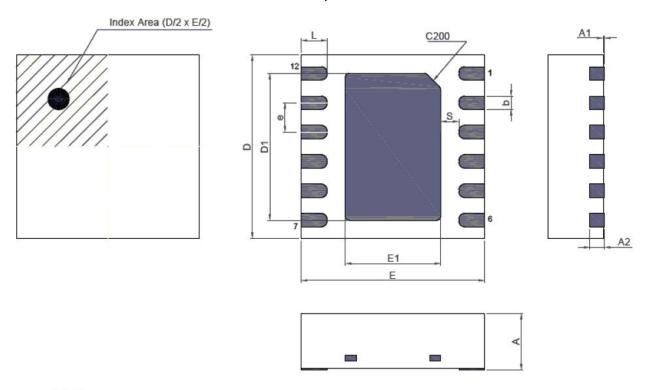

# **Package Drawing and Dimensions**

## 12 Lead TDFN Package JEDEC MO-252, Variation 2525E

### Unit: mm

| Symbol | Min   | Nom. | Max   | Symbol | Min      | Nom. | Max  |

|--------|-------|------|-------|--------|----------|------|------|

| Α      | 0.70  | 0.75 | 0.80  | D1     | 1.95     | 2.00 | 2.05 |

| A1     | 0.005 | -    | 0.060 | E1     | 1.25     | 1.30 | 1.35 |

| A2     | 0.15  | 0.20 | 0.25  | е      | 0.40 BSC |      |      |

| b      | 0.13  | 0.18 | 0.23  | L      | 0.30     | 0.35 | 0.40 |

| D      | 2.45  | 2.50 | 2.55  | S      | 0.18     |      | -    |

| E      | 2.45  | 2.50 | 2.55  |        |          |      |      |

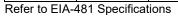

## **Tape and Reel Specification**

|                                     | # of | Nominal              | Max Units |         | Reel &           | Trailer A |                | Leader B |                | Pocket (mm) |       |

|-------------------------------------|------|----------------------|-----------|---------|------------------|-----------|----------------|----------|----------------|-------------|-------|

| Package Type                        | Pins | Package<br>Size (mm) | per reel  | per box | Hub Size<br>(mm) | Pockets   | Length<br>(mm) | Pockets  | Length<br>(mm) | Width       | Pitch |

| TDFN 12L<br>2.5x2.5mm<br>0.4P Green | 12   | 2.5x2.5x0.75         | 3000      | 3000    | 178/60           | 42        | 168            | 42       | 168            | 8           | 4     |

## **Carrier Tape Drawing and Dimensions**

| Package<br>Type                     | Pocket<br>BTM<br>Length<br>(mm) | Pocket<br>BTM Width<br>(mm) | Pocket<br>Depth<br>(mm) | Index Hole<br>Pitch<br>(mm) | Pocket<br>Pitch<br>(mm) | Index Hole<br>Diameter<br>(mm) | Index Hole<br>to Tape<br>Edge<br>(mm) | Index Hole<br>to Pocket<br>Center<br>(mm) | Tape Width (mm) |

|-------------------------------------|---------------------------------|-----------------------------|-------------------------|-----------------------------|-------------------------|--------------------------------|---------------------------------------|-------------------------------------------|-----------------|

|                                     | Α0                              | В0                          | K0                      | P0                          | P1                      | D0                             | E                                     | F                                         | w               |

| TDFN 12L<br>2.5x2.5mm<br>0.4P Green | 2.75                            | 2.75                        | 1.05                    | 4                           | 4                       | 1.55                           | 1.75                                  | 3.5                                       | 8               |

## **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of  $4.6875 \, \text{mm}^3$  (nominal). More information can be found at <a href="https://www.jedec.org"><u>www.jedec.org</u></a>.

# **SLG7NT4180**

# **Datasheet Revision History**

| Date       | Version | Change                        |

|------------|---------|-------------------------------|

| 04/15/2013 | 0.10    | New design                    |

| 04/16/2013 | 0.11    | OR Gate is added              |

| 05/06/2013 | 0.12    | Updated Device Revision Table |

| 06/05/2013 | 1.0     | Production release            |

| 02/25/2022 | 1.01    | Updated Company name and logo |

**Logic Gates**

## Silego Website & Support

### Silego Technology Website

Silego Technology provides online support via our website at <a href="http://www.silego.com/">http://www.silego.com/</a>. This website is used as a means to make files and information easily available to customers.

For more information regarding Silego Green products, please visit:

http://greenpak.silego.com/ http://greenpak2.silego.com/ http://greenfet.silego.com/ http://greenfet2.silego.com/ http://greenclk.silego.com/

Products are also available for purchase directly from Silego at the Silego Online Store at http://store.silego.com/.

### Silego Technical Support

Datasheets and errata, application notes and example designs, user guides, and hardware support documents and the latest software releases are available at the Silego website or can be requested directly at info@silego.com.

For specific GreenPAK design or applications questions and support please send email requests to GreenPAK@silego.com

Users of Silego products can receive assistance through several channels:

### **Contact Your Local Sales Representative**

Customers can contact their local sales representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. More information regarding your local representative is available at the Silego website or send a request to <a href="mailto:info@silego.com">info@silego.com</a>

#### **Contact Silego Directly**

Silego can be contacted directly via e-mail at <a href="mailto:info@silego.com">info@silego.com</a> or user submission form, located at the following URL: <a href="http://support.silego.com/">http://support.silego.com/</a>

#### Other Information

The latest Silego Technology press releases, listing of seminars and events, listings of worldwide Silego Technology offices and representatives are all available at <a href="http://www.silego.com/">http://www.silego.com/</a>

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. SILEGO TECHNOLOGY DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. SILEGO TECHNOLOGY RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.