## 概要

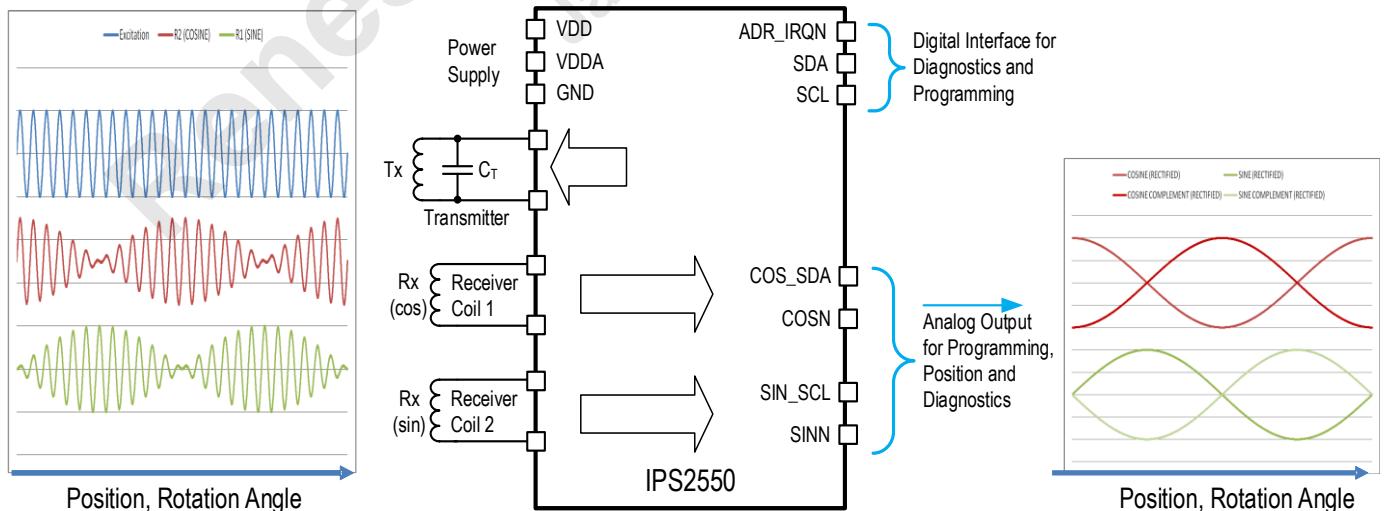

IPS2550 は、磁石を使用しない誘導型位置センサ IC で、自動車、産業用、医療用、および民生用アプリケーションの高速絶対位置センシングに使用できます。IPS2550 は、渦電流の物理原理を使用して、1つの送信コイルと2つの受信コイルで構成された 1 組のコイル上を移動する単純な金属ターゲットの位置を検出します。

3つのコイルは、通常、プリント基板 (PCB) 上に銅箔配線として形成されます。送信コイルは 2 つの受信コイルに二次電圧を誘起するように配置され、二次電圧はコイル上方の金属ターゲットの位置に依存します。

コイル上の金属ターゲットの位置を表す信号は、受信コイルからの二次電圧を復調して処理することによって得られます。ターゲットは、アルミニウム、鉄、または銅箔層を有する PCB のような任意の種類の金属が使用可能です。

IPS2550 は 2 つの個別の出力インターフェースを提供します:

- 復調されたアナログサイン/コサイン生データ出力の形で位置情報を提供する高速アナログインターフェース

- 診断およびプログラミング用の I<sub>2</sub>C デジタルインターフェース

IPS2550 は、600 000 RPMまでの回転速度で作動します (1 回転あたり 1 周期に設計されたコイル使用時)。4 μs の超低伝搬遅延により、高速回転モータのための高いダイナミック制御が得られます。

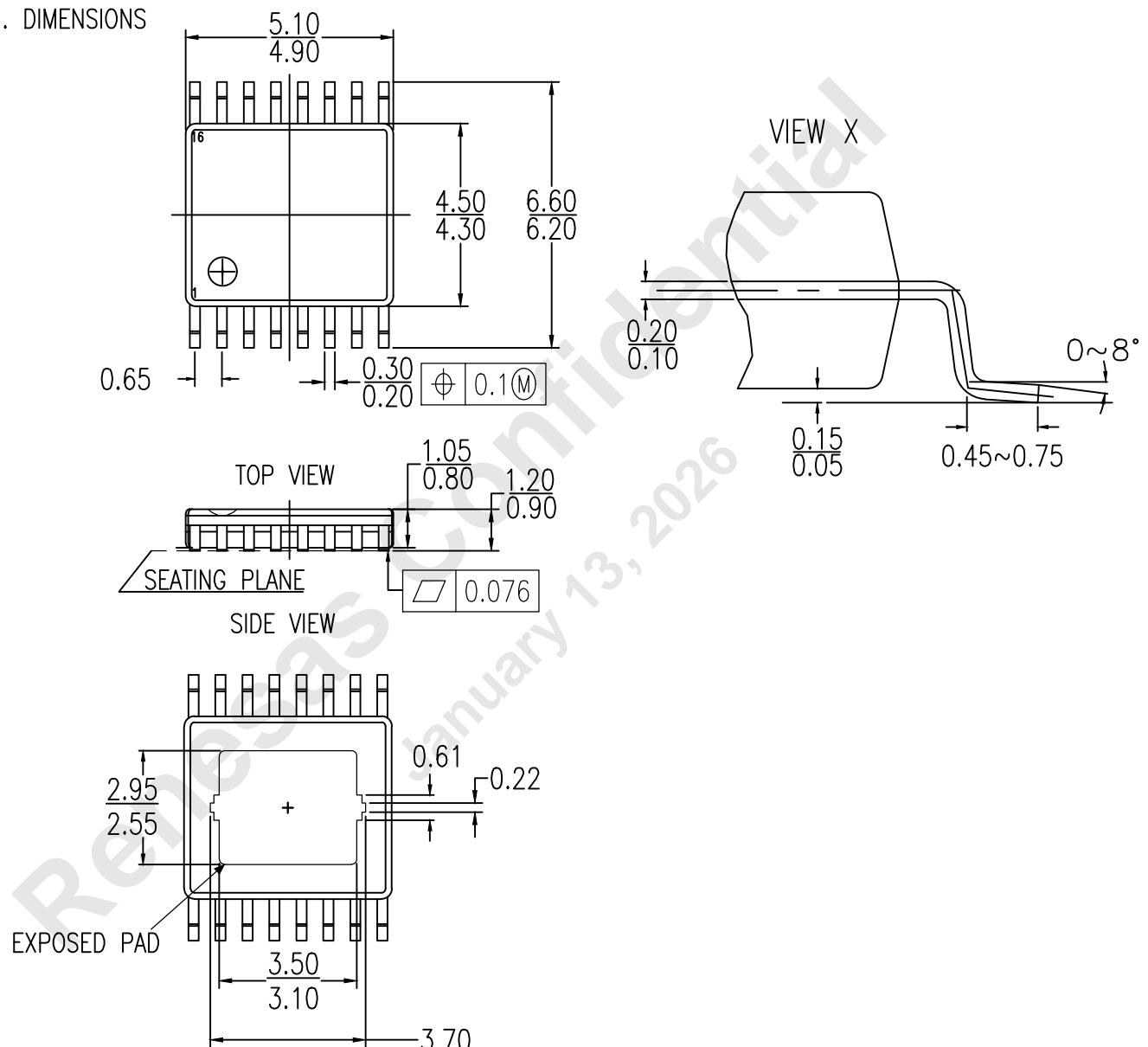

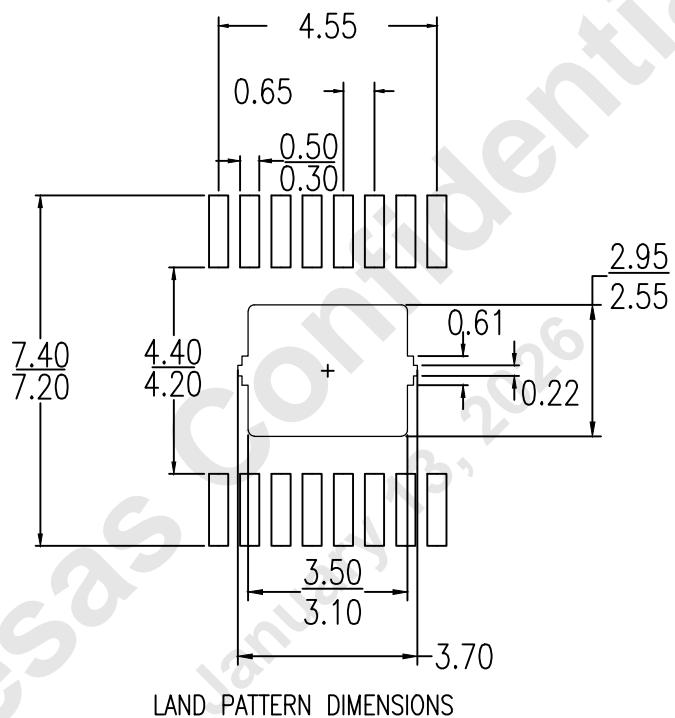

IPS2550 は、ISO26262 に準拠し ASIL C までの安全関連システムでの使用を目的として開発されました。また、ASIL のデコンポジションルール (例えば、ISO 26262.2018 Part 9, Clause 5) または、システム設計者による正しリスク解析により ASIL D レベルのシステム要求に用いることができます。IPS2550 は 16 ピンエクスポートドパッド付き TSSOP パッケージで提供され、-40°C～+160°Cの周囲温度での自動車での使用が認定されています。

## 利用可能なサポート

ルネサスは、IPS2550 回転位置センシングアプリケーションを実現できるリファレンスデザインを提供しています。

## 主な用途

- ブラシレス DC モータ用ロータ位置検出; 任意の極対数に対応

- レゾルバの置き換え

## 特徴

- 誘導原理に基づく位置検知

- 磁石が不要で低コスト

- 磁気浮遊磁界に対して堅牢、シールド不要

- 過酷な環境や極端な温度に適応可能

- 差動およびシングルエンドのサイン/コサイン出力

- プログラマブルリミットによる自動ゲイン制御

- I<sub>2</sub>C インタフェース経由でプログラム可能な不揮発性ユーザ設定メモリ

- アナログまたはデジタルインターフェースでプログラミング可能

- 単体 IC で軸上・軸外回転、直線運動、円弧運動センシングに対応

- コイル設計により、あらゆるフルスケール角度範囲に適応可能

- 高精度:  $\leq 0.1\%$  フルスケール (理想コイル使用時)

- 360° 角レンジまでの回転検知

- 過電圧および逆極性保護: 電源端子、出力端子とも  $\pm 18V$

- 冗長設計要件を容易にする

- ISO26262 に準拠した安全関連システムにおいて、シングル IC では ASIL-C、デュアル IC では ASIL-D までの実装に適しています

- 割り込みピンによる高速診断アラーム

- 広い動作温度: -40°C～+160°C

- 3.3V ± 0.3V または 5.0V ± 0.5V の電源電圧にプログラミング可能

- エクスポートドパッド付き小型 16-TSSOP パッケージ (4.4mm × 5.0mm)

## 応用回路例

## 目次

|                                                             |    |

|-------------------------------------------------------------|----|

| 1. 端子配置 .....                                               | 5  |

| 2. 端子の説明 .....                                              | 5  |

| 3. 受信コイル接続オプション .....                                       | 7  |

| 4. 絶対最大定格 .....                                             | 9  |

| 5. 動作条件 .....                                               | 10 |

| 6. 使用温度範囲 .....                                             | 11 |

| 7. 電気特性 .....                                               | 12 |

| 8. 回路説明 .....                                               | 21 |

| 8.1 概要 .....                                                | 21 |

| 9. サンプリングレート、分解能、出力データレート、および伝搬遅延 .....                     | 24 |

| 10. 出力モード .....                                             | 24 |

| 11. 高速での動作 .....                                            | 25 |

| 12. デジタル診断およびプログラミングインターフェース .....                          | 25 |

| 13. ブロック図 .....                                             | 26 |

| 14. ブロックの詳細説明 .....                                         | 27 |

| 14.1 電源管理 .....                                             | 27 |

| 14.2 LC 発振回路 .....                                          | 27 |

| 14.3 アナログ信号経路 .....                                         | 27 |

| 14.3.1 Rx コイル診断 .....                                       | 27 |

| 14.3.2 受信信号ローパスフィルタ .....                                   | 27 |

| 14.3.3 オフセットとゲイン整合 .....                                    | 28 |

| 14.3.4 復調 .....                                             | 28 |

| 14.3.5 自動ゲインコントロール (AGC) .....                              | 28 |

| 14.4 信号チャンネルの入れ替え .....                                     | 28 |

| 14.5 出力バッファ .....                                           | 28 |

| 14.6 温度センサ .....                                            | 29 |

| 15. ECU 接続オプション .....                                       | 29 |

| 15.1 エンベデッド vs. リモート接続 .....                                | 29 |

| 15.2 電源電圧動作: 3.3V または 5V .....                              | 31 |

| 15.3 I <sup>2</sup> C インタフェース .....                         | 32 |

| 15.3.1 アドレス選択付き I <sup>2</sup> C (デフォルト) .....              | 32 |

| 15.3.2 GND 壊失または VDD 壊失中の ADR IRQN ピンを介した寄生バスの回避 .....      | 33 |

| 15.3.3 割り込み付き I <sup>2</sup> C インタフェース (プログラミングオプション) ..... | 33 |

| 16. 過電圧保護 .....                                             | 34 |

|                                          |    |

|------------------------------------------|----|

| 16.1 入出力保護.....                          | 34 |

| 17. プログラムオプション.....                      | 35 |

| 17.1 もう一方の電源電圧オプションを使用するためのプログラミング ..... | 36 |

| 17.2 ロック機能 (サイバーセキュリティ) .....            | 37 |

| 17.3 プログラムオプション .....                    | 37 |

| 18. 機能安全と診断.....                         | 37 |

| 18.1 機能安全 ASIL および ISO 準拠 .....          | 37 |

| 18.2 アナログ出力による診断モード表示 .....              | 38 |

| 18.2.1 短絡および断線検出 .....                   | 40 |

| 18.3 診断機能 .....                          | 43 |

| 18.4 内部レジスタとメモリエラー .....                 | 45 |

| 18.5 LC 発振回路の周波数外れ .....                 | 45 |

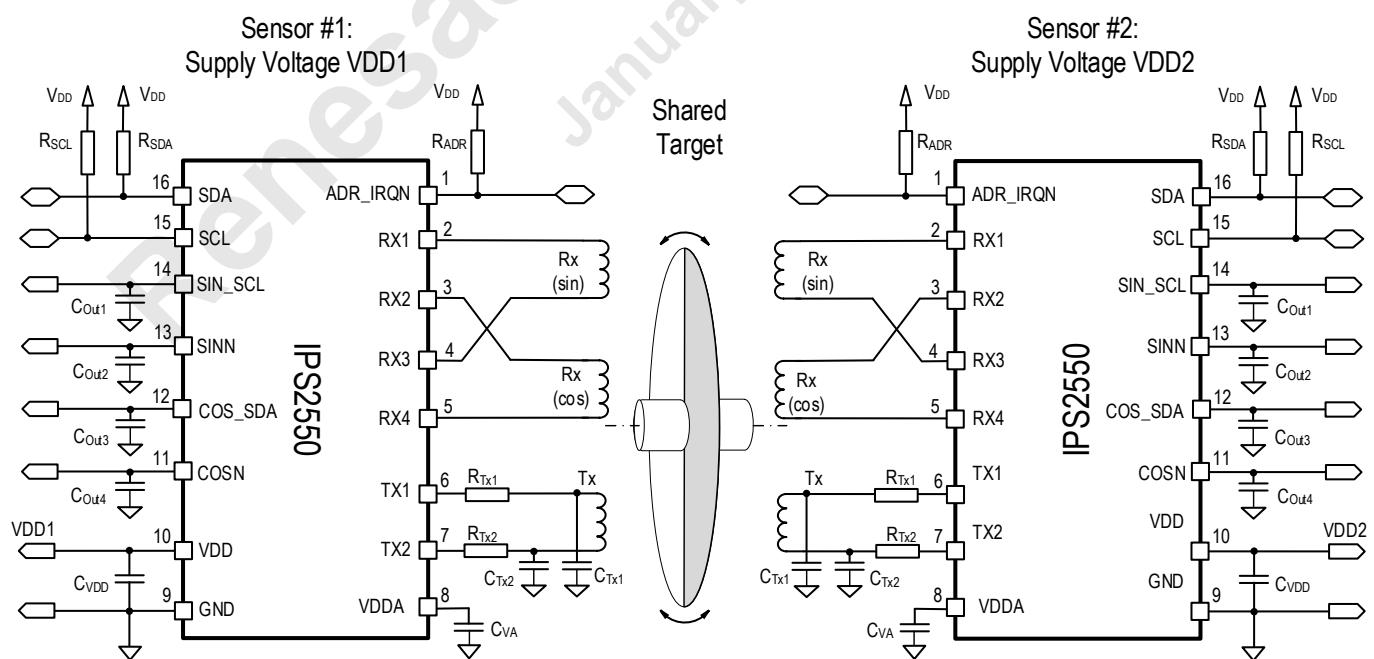

| 19. 冗長化接続.....                           | 45 |

| 20. 応用例 .....                            | 46 |

| 21. 電磁両立性 (EMC) .....                    | 48 |

| 22. 16-TSSOP パッケージ外形図 .....              | 48 |

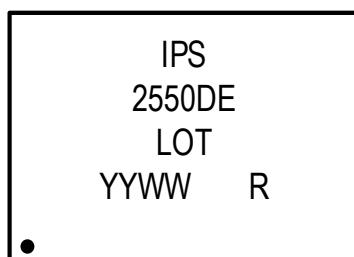

| 23. マーキング図 .....                         | 48 |

| 23.1 生産部品のマーキング .....                    | 48 |

| 24. 発注情報 .....                           | 48 |

| 25. 改訂履歴 .....                           | 49 |

## 図一覧

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| 図 1 16-TSSOP パッケージのピン配置-上面図 .....                                       | 5  |

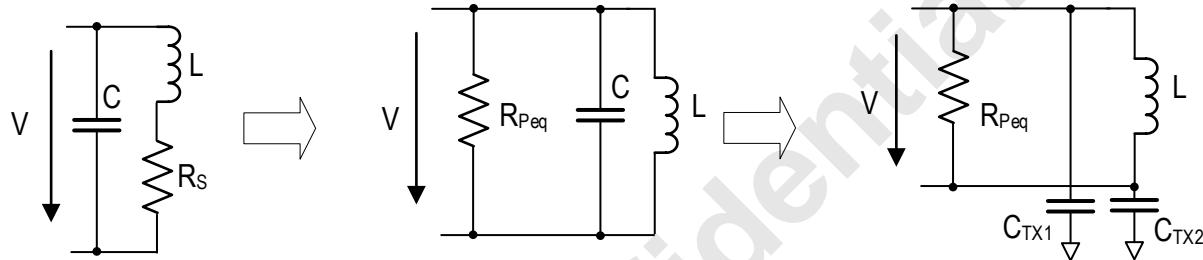

| 図 2 分割 TX コンデンサによる ASIL-C 構成における LC 発振回路接続 .....                        | 7  |

| 図 3 分割 TX コンデンサとの互換モード構成での LC 発振回路接続 .....                              | 8  |

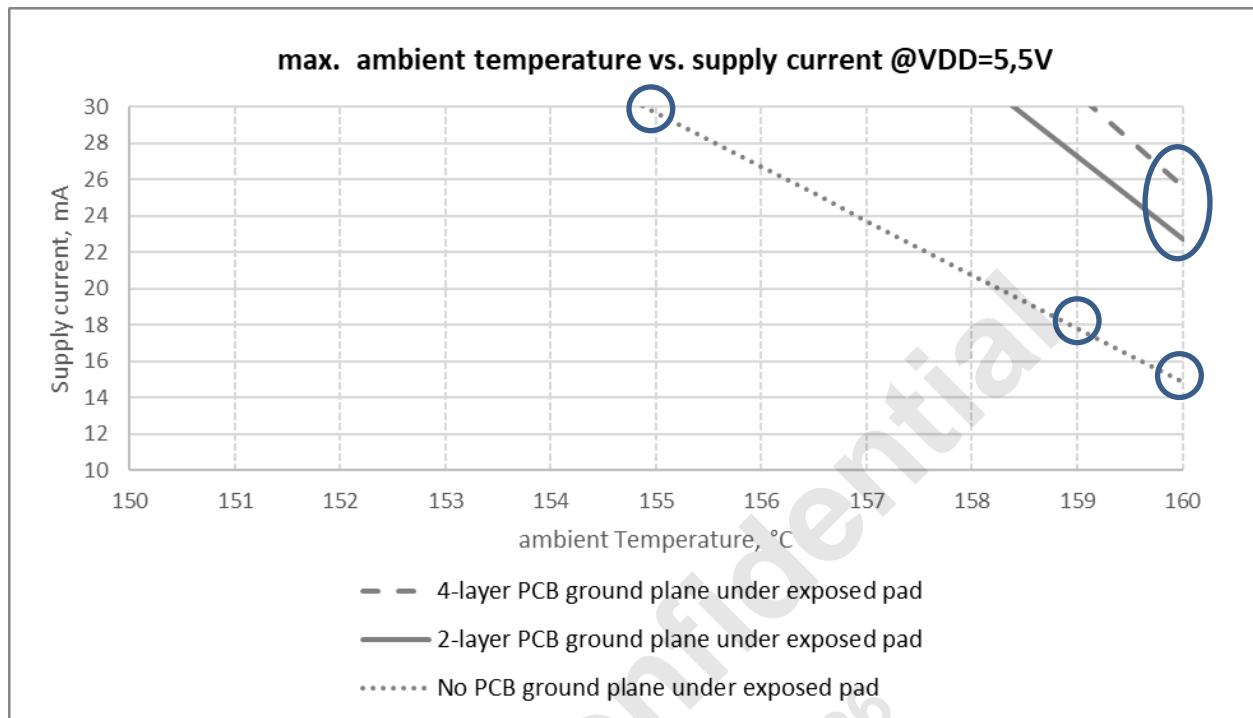

| 図 4 最大消費電流-周囲温度特性 (グランドプレーン有・無) .....                                   | 12 |

| 図 5 並列共振回路 .....                                                        | 14 |

| 図 6 IPS2550 の応答 .....                                                   | 21 |

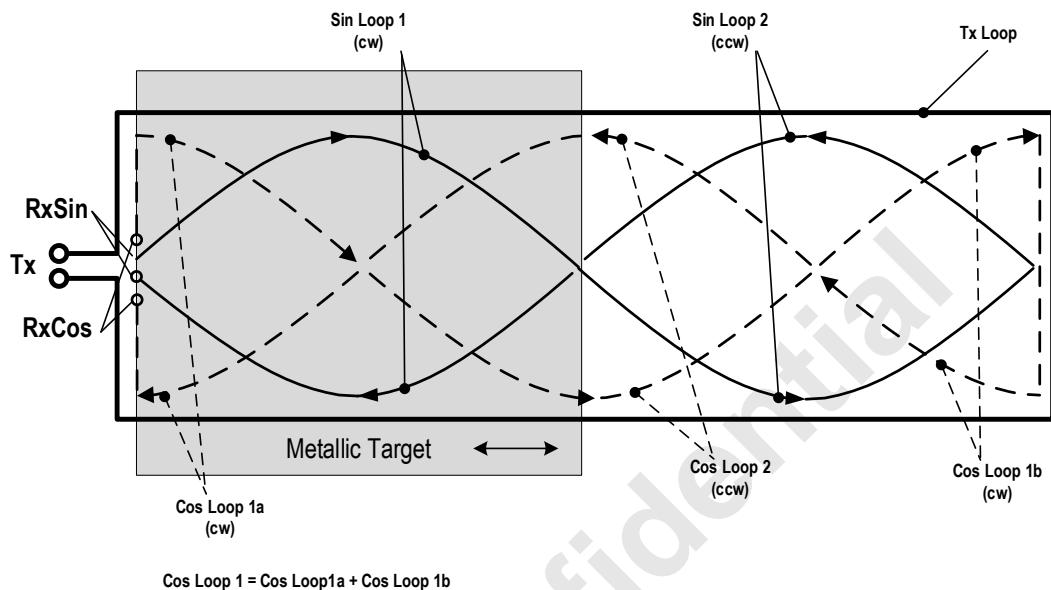

| 図 7 直線運動センサのためのコイル形状 .....                                              | 23 |

| 図 8 360° 回転センサ用のコイル形状 .....                                             | 23 |

| 図 9 出力信号: サインアナログ差動モード .....                                            | 24 |

| 図 10 出力信号: サインアナログシングルエンドモード .....                                      | 24 |

| 図 11 ブロック図 .....                                                        | 26 |

| 図 12 AGC 振幅レンジ .....                                                    | 28 |

| 図 13 エンベデッドアプリケーション: センサと MCU は同じ PCB 上に配置されます .....                    | 30 |

| 図 14 診断用プルアップ抵抗付きリモートアプリケーション .....                                     | 31 |

| 図 15 診断用プルダウン抵抗付きリモートアプリケーション .....                                     | 31 |

| 図 16 I <sub>2</sub> C アドレス選択ビット .....                                   | 33 |

| 図 17 アドレス選択付き I <sub>2</sub> C インタフェース .....                            | 33 |

| 図 18 ADR IRQN ピン用いたハードウェアピン固定によるアドレス選択付き I <sub>2</sub> C インタフェース ..... | 33 |

|      |                                   |    |

|------|-----------------------------------|----|

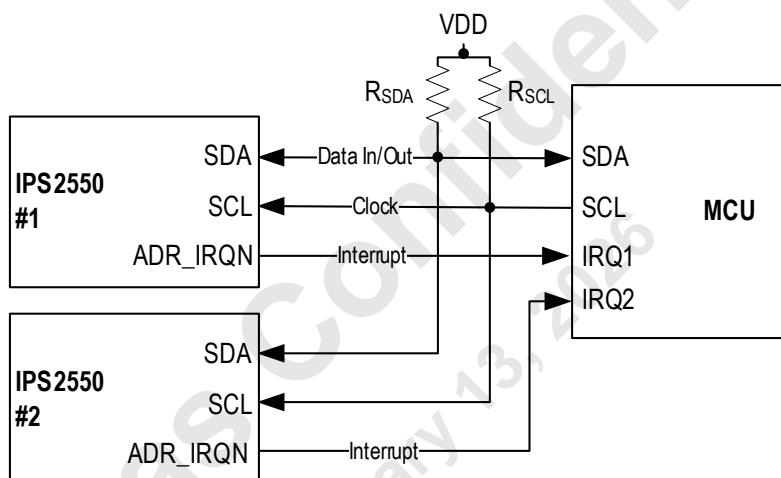

| 図 19 | 1 つのスレーブでの割り込みを使用した I2C インタフェース設定 | 34 |

| 図 20 | マルチスレーブ割込みによる I2C インタフェースの構成      | 34 |

| 図 21 | I2C インタフェースを介した IPS2550 のプログラム    | 35 |

| 図 22 | アナログ出力を通した IPS2550 の製造最終工程でのプログラム | 36 |

| 図 23 | 動作範囲と診断範囲                         | 38 |

| 図 24 | 診断範囲の選択                           | 39 |

| 図 25 | VDD または GND ラインの断線によるアナログ出力の寄生電流  | 41 |

| 図 26 | ADR IRQN 端子、SDA 端子、SCL 端子の寄生電流    | 42 |

| 図 27 | アプリケーション図: デュアルセンサ、デュアル電源         | 45 |

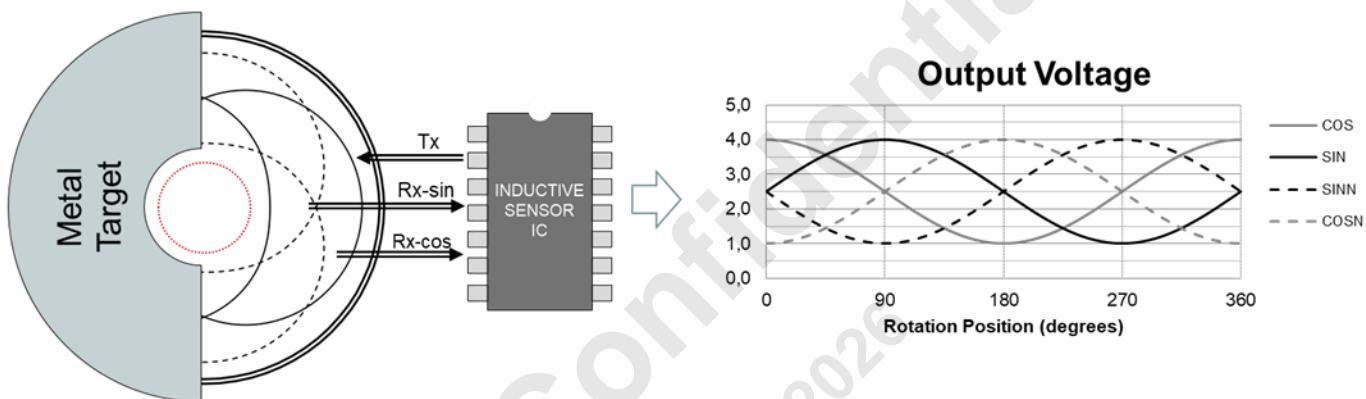

| 図 28 | 360° 回転センサのコイル設計と信号出力             | 46 |

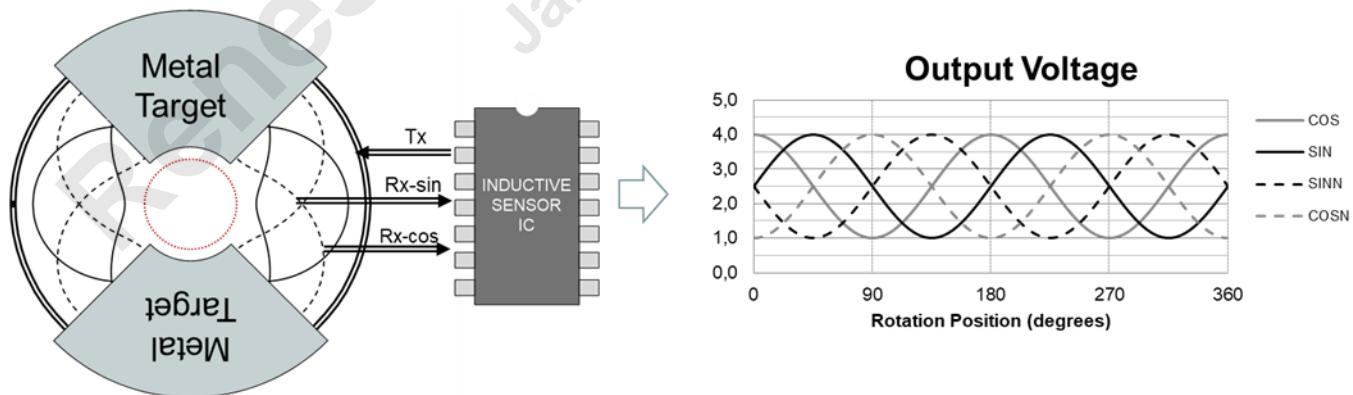

| 図 29 | 2 × 180° ロータリセンサ用のコイル設計と信号出力      | 46 |

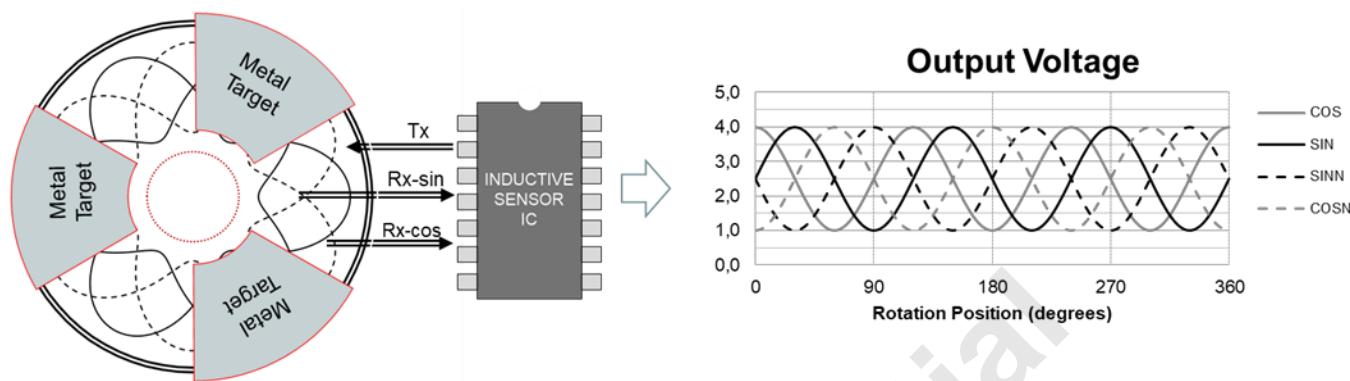

| 図 30 | 3 × 120° ロータリセンサ用のコイル設計と信号出力      | 47 |

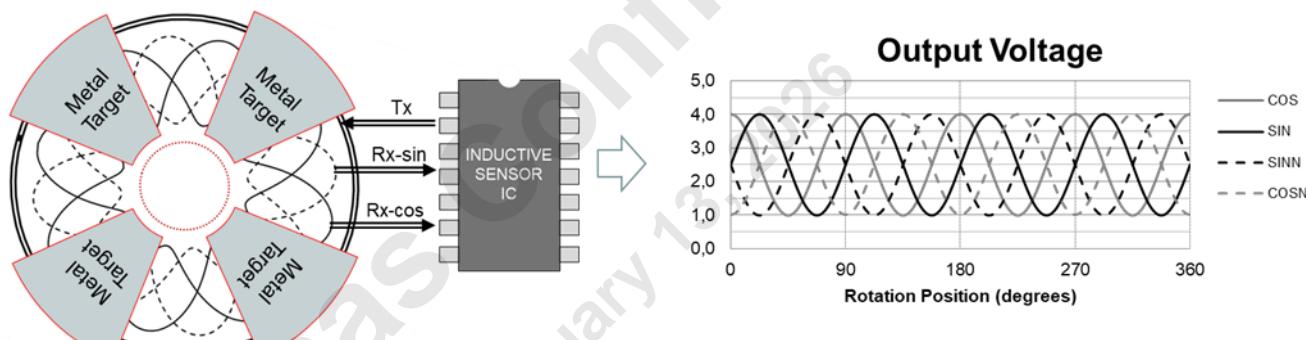

| 図 31 | 4 × 90° ロータリセンサ用のコイル設計と信号出力       | 47 |

## 表一覧

|      |                                           |    |

|------|-------------------------------------------|----|

| 表 1  | 端子の説明                                     | 5  |

| 表 2  | 出力構成                                      | 6  |

| 表 3  | デジタルインターフェースの設定                           | 7  |

| 表 4  | 絶対最大定格                                    | 9  |

| 表 5  | 静電気放電 (ESD)                               | 9  |

| 表 6  | 動作条件                                      | 10 |

| 表 7  | IPS2550 電気的特性、3.3V モード                    | 12 |

| 表 8  | IPS2550 電気的特性、5.0V モード                    | 13 |

| 表 9  | LC 発振回路の仕様                                | 13 |

| 表 10 | コイルレシーバフロントエンド仕様                          | 15 |

| 表 11 | 自動ゲインコントロール (AGC)                         | 16 |

| 表 12 | 診断チェック                                    | 17 |

| 表 13 | バックエンド仕様、アナログ出力 SIN_SCL、SINN、COS_SDA、COSN | 17 |

| 表 14 | デジタル I2C 制御インターフェース、SDA、SCL ピン            | 18 |

| 表 15 | アナログ出力経由の I2C インタフェース                     | 19 |

| 表 16 | デジタル I2C 制御インターフェース、ピン ADR IRQN           | 20 |

| 表 17 | 不揮発性メモリ                                   | 20 |

| 表 18 | 伝搬遅延                                      | 24 |

| 表 19 | 出力モードと最高速度                                | 25 |

| 表 20 | 内部チップ温度センサ特性                              | 29 |

| 表 21 | NVM でのアドレス選択オプション                         | 32 |

| 表 22 | プログラムオプションの概要                             | 37 |

| 表 23 | 配線間のショート検出                                | 40 |

| 表 24 | プルアップ抵抗付きの診断レベル                           | 42 |

| 表 25 | プルダウン抵抗付き診断レベル                            | 42 |

| 表 26 | 診断機能                                      | 43 |

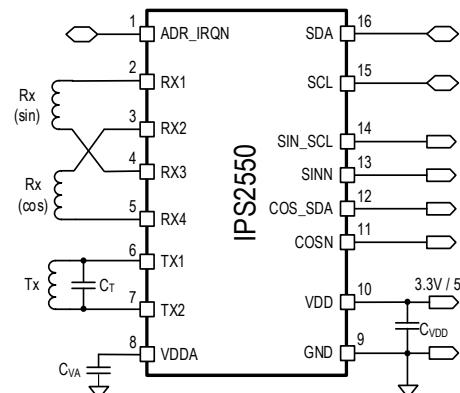

## 1. 端子配置

IPS2550 は周囲温度-40°C ~+160°Cに認定された RoSH 対応エクスポートドパッド付き 16-TSSOP (4.4mm × 5.0mm) です。

図 1 16-TSSOP パッケージのピン配置-上面図

## 2. 端子の説明

表 1 端子の説明

| ピン番号 | ピン名      | 種類                   | 概要                                                                                                                                                                   |  |

|------|----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | ADR IRQN | Digital Input/Output | I2C インタフェースアドレス選択用のアドレス選択デジタル入力。プッシュ/プル割り込み出力 (プログラムオプション、表 3 参照)<br>I2C アドレス選択入力として使用する場合は、プルアップまたはプルダウン抵抗 $R_{ADR}$ (表 14 参照) で I2C アドレスを選択してください。                 |  |

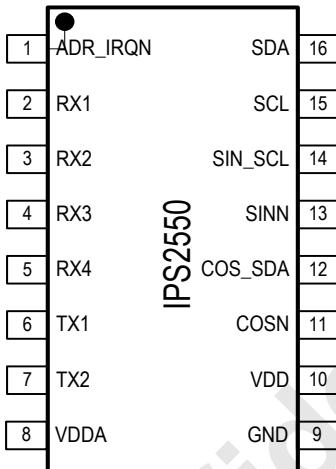

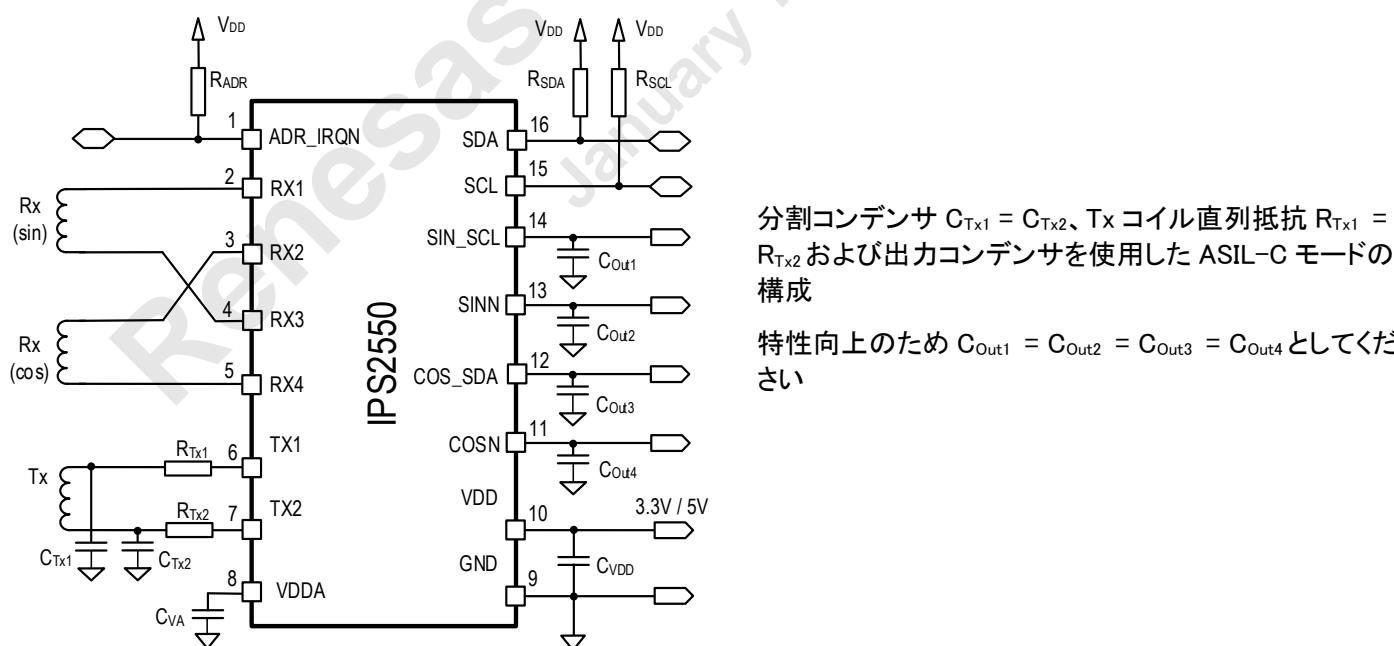

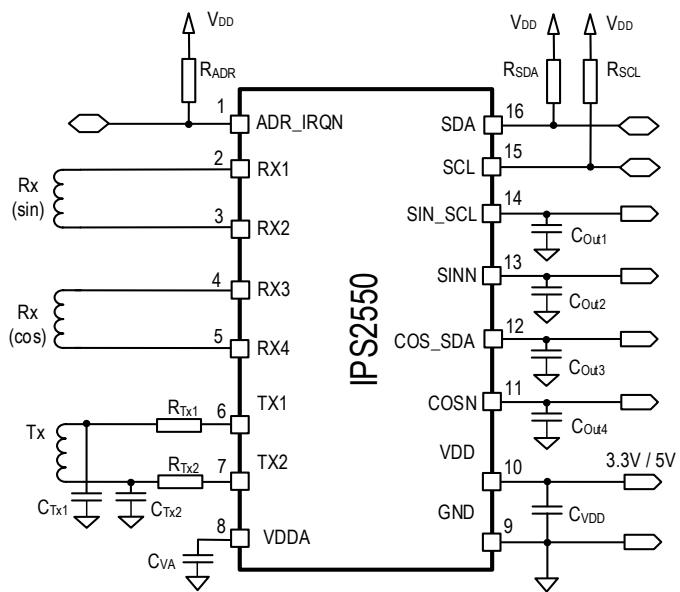

| 2    | RX1      | Analog Input         | ASIL-C 構成モード (デフォルト): 受信コイル 1 (サイン、図 2 参照)<br>互換モード: 受信コイル 1 (サイン、図 3 参照)                                                                                            |  |

| 3    | RX2      |                      | ASIL-C 構成モード (デフォルト): 受信コイル 2 (コサイン、図 2 参照)<br>互換モード: 受信コイル 1 (反転サイン、図 3 参照)                                                                                         |  |

| 4    | RX3      |                      | ASIL-C 構成モード (デフォルト): 受信コイル 1 (反転サイン、図 2 参照)<br>互換モード: 受信コイル 2 (コサイン、図 3 参照)                                                                                         |  |

| 5    | RX4      |                      | ASIL-C 構成モード (デフォルト): 受信コイル 2 (反転コサイン、図 2 参照)<br>互換モード: 受信コイル 2 (反転コサイン、図 3 参照)                                                                                      |  |

| 6    | TX1      | Analog Input/Output  | TX1 ピンと TX2 ピンの間に送信コイルを接続します。共振周波数は、図 2、図 3 に示すように TX1～GND 間のコンデンサ $C_{Tx1}$ 、TX2～GND 間の $C_{Tx2}$ で調整します。 $C_{Tx1}$ と $C_{Tx2}$ は、同じ容量値になるようにしてください。これらは式 3 で計算できます |  |

| 7    | TX2      |                      |                                                                                                                                                                      |  |

| ピン番号 | ピン名         | 種類                              | 概要                                                                                                                                    |

|------|-------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 8    | VDDA        | Supply                          | 内部アナログ電源、選択された VDD モードで変化します。GND 端子との間にコンデンサ $C_{VA}$ (表 6 参照) を接続してください。5V モードでは表 8 の $VDDA_5$ を、3.3V モードでは表 7 の $VDDA_3$ を参照してください。 |

| 9    | GND         | Supply                          | 共通グランド                                                                                                                                |

| 10   | VDD         | Supply                          | 外部電源入力。コンデンサ $C_{VDD}$ (表 6 参照) を GND 端子との間に接続してください                                                                                  |

| 11   | COSN        | Analog Output                   | バッファ付きアナログ出力。表 2 参照                                                                                                                   |

| 12   | COS_SDA     | Analog Output,<br>Digital I/O   | バッファ付きアナログ出力。プログラミングモード中のデジタル I2C データ入出力。表 2 参照                                                                                       |

| 13   | SINN        | Analog Output                   | バッファ付きアナログ出力。表 2 参照                                                                                                                   |

| 14   | SIN_SCL     | Analog Output,<br>Digital Input | バッファ付きアナログ出力。プログラミングモード中のデジタル I2C クロック入力。表 2 参照                                                                                       |

| 15   | SCL         | Digital Input                   | デジタルプログラムおよび診断 I2C インタフェース用のクロック入力<br>プルアップ抵抗 $R_{SCL}$ (表 14 参照) を接続してください                                                           |

| 16   | SDA         | Digital<br>Input/Output         | デジタルプログラムおよび診断 I2C インタフェース用のオーブンドレイン双方向データ I/O ライン<br>プルアップ抵抗 $R_{SDA}$ (表 14 参照) を接続してください                                           |

|      | Exposed Pad | Heat sink                       | ヒートシンク。GND (9 ピン) へ直接接続、または未接続にできます。詳細は<br>図 4 を参照してください<br>エクスポートドパッドは GND 以外の電位に接続しないでください                                          |

表 2 出力構成

| ピン(図 1 参照) |         | モードに応じた出力 |                 |          | 診断状態、プログラムオプション |       |       |       |

|------------|---------|-----------|-----------------|----------|-----------------|-------|-------|-------|

| ピン番号       | 端子名     | アナログ差動    | アナログシングル<br>エンド | プログラミング  | 無効              | Mode1 | Mode2 | Mode3 |

| 14         | SIN_SCL | SIN       | SIN             | SCL      | SIN             | SIN   | Hi-Z  | Hi-Z  |

| 13         | SINN    | SINN      | REF             | Not used | SINN            | Hi-Z  | SINN  | Hi-Z  |

| 12         | COS_SDA | COS       | COS             | SDA      | COS             | COS   | Hi-Z  | Hi-Z  |

| 11         | COSN    | COSN      | REF             | Not used | COSN            | Hi-Z  | COSN  | Hi-Z  |

[a] 表 2 で使用した略語:

- SIN: サインチャネル出力、バイアス電圧=  $VDD/2$

SIN: 反転サインチャネル出力、バイアス電圧=  $VDD/2$

COS: コサインチャネル出力、バイアス電圧=  $VDD/2$

COSN: 反転コサインチャネル出力、バイアス電圧=  $VDD/2$

REF: DC 出力バイアス電圧、 $VDD/2$

SCL: I2C プログラミング用シリアルクロック入力

SDA: I2C プログラミング用シリアル双方向データ I/O ポート

Hi-Z: 出力はハイ・インピーダンス、診断出力は外部のプルアップ抵抗またはプルダウン抵抗で示されます。

表 3 デジタルインターフェースの設定

| ピン(図1参照)   |          | インターフェース Mode に応じた入出力 <sup>[a]</sup> |            |

|------------|----------|--------------------------------------|------------|

| TSSOP ピン番号 | 端子名      | アドレス選択付き I2C                         | 割り込み付き I2C |

| 16         | SDA      |                                      | SDA        |

| 15         | SCL      |                                      | SCL        |

| 1          | ADR_IRQN | ADR                                  | IRQN       |

[a] 表 3 で使用した略語:

ADR\_IRQN: アドレスセレクト入力または、割り込み出力

ADR: I2C モードのハードウェアアドレス選択入力 (ADR\_IRQN ピンのデジタル入力レベルで 2 つのアドレスを選択します)

SDA: I2C モード用シリアル双方向データ I/O ポート

SCL: I2C モード用シリアルクロック入力

IRQN: 割り込み出力

### 3. 受信コイル接続オプション

IPS2550 は、2 つの受信コイル接続方法をユーザー・プログラムモードで設定できます:

- ASIL-C コンフィグレーション・モード(デフォルト)では、2 つの隣接ピン間の短絡による、受信コイルの短絡が回避できるため、チップの故障検出率が向上します。

- 互換モード(プログラムオプション)では、IPS2200 誘導型センサ IC とピン互換になります。

-

図 2 分割 TX コンデンサによる ASIL-C 構成における LC 発振回路接続

分割コンデンサ  $C_{Tx1} = C_{Tx2}$ 、Tx コイル直列抵抗  $R_{Tx1} = R_{Tx2}$  および出力コンデンサを使用した IPS2200 互換モードでの構成

特性向上のため  $C_{Out1} = C_{Out2} = C_{Out3} = C_{Out4}$  としてください

図 3 分割 TX コンデンサとの互換モード構成での LC 発振回路接続

発振周波数は、コイル L、コンデンサ  $C_{Tx1}$ 、 $C_{Tx2}$  の値により以下のように決まります:

発振周波数:

$$f_{TX} = \frac{1}{2\pi \sqrt{\frac{L \times C_{Tx1} \times C_{Tx2}}{C_{Tx1} + C_{Tx2}}}} \quad \text{式 1}$$

$C_{Tx1} = C_{Tx2}$  の場合:

$$f_{TX} = \frac{1}{2\pi \sqrt{L \frac{C_{Tx1}}{2}}} \quad \text{式 2}$$

$$C_{Tx1} = C_{Tx2} = \frac{2}{L(2\pi f_{TX})^2} \quad \text{式 3}$$

ここで、

$f_{TX}$  = 発振周波数 (単位: MHz)

$L$  = コイルインダクタンス (単位:  $\mu$  H)

$C_{Tx1}$ ,  $C_{Tx2}$  = 容量値 (単位:  $\mu$  F)

注:  $R_{Tx1} = R_{Tx2} = 22\Omega$  (標準値)

## 4. 絶対最大定格

絶対最大定格とは、製品に物理的な損傷を与えるかねない定格値です。必ずこの定格値を越えない状態で、製品をご使用ください。各項目のうち 1 項目でも、また一瞬でも絶対最大定格を越えると、製品の品質を損なう恐れがあります。

すべての電圧レベルは GND を基準とします。

表 4 絶対最大定格

| 記号            | パラメータ                                          | 条件                                                                                                     | 最小                                                                                  | 最大      | 単位 |

|---------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------|----|

| $V_{VDDmax}$  | External supply voltage                        | Continuous                                                                                             | -18                                                                                 | 18      | V  |

| $V_{OUT}$     | SIN_SCL, SINN, COS_SDA and COSN output voltage | Continuous                                                                                             | -18                                                                                 | 18      | V  |

| $V_{RX1}$     | Receiver coil pin: RX1                         |                                                                                                        | -12                                                                                 | 12      | V  |

| $V_{RX2}$     | Receiver coil pin: RX2                         |                                                                                                        |                                                                                     |         |    |

| $V_{RX3}$     | Receiver coil pin: RX3                         |                                                                                                        |                                                                                     |         |    |

| $V_{RX4}$     | Receiver coil pin: RX4                         |                                                                                                        |                                                                                     |         |    |

| $V_{DIGITAL}$ | Digital IO pins: SCL, SDA, ADR_IRQN            |                                                                                                        | -0.3                                                                                | VDD+0.3 | V  |

| $V_{TX1\_2}$  | Transmitter pins, TX1, TX2                     |                                                                                                        | -0.3                                                                                | 5.6     | V  |

| $V_{VDDAmax}$ | VDDA internal LDO output                       | VDDA is internally regulated with external capacitor to GND. No other connection to external voltages. | 値について、5V モードでは表 8 の VDDA <sub>5</sub> を、3.3V モードでは表 7 の VDDA <sub>3</sub> を参照してください |         | V  |

表 5 静電気放電 (ESD)

| 記号            | パラメータ                                                                                                                          | 条件                                           | 最小   | 標準 | 最大 | 単位 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|----|----|----|

| $V_{ESD}$     | ESD tolerance for all pins: Human Body Model (HBM) 100pF/1.5kΩ                                                                 | According to AEC-Q100-002 classification H2  | ±2   |    |    | kV |

| $V_{ESD,OUT}$ | ESD tolerance for pins with potential external cable connection: SIN_SCL, COS_SDA, SINN, COSN, ADR_IRQN, VDD (HBM 100pF/1.5kΩ) | According to AEC-Q100-002 classification H3A | ±4   |    |    | kV |

| $V_{CDM}$     | ESD tolerance for all pins: Charged-Device Model (CDM)                                                                         | According to AEC-Q100-011 classification C3B | ±500 |    |    | V  |

| $V_{CDM,C}$   | ESD tolerance for corner pins ADR_IRQN, SDA, VDDA, GND (CDM)                                                                   | According to AEC-Q100-011 classification C3B | ±750 |    |    | V  |

## 5. 動作条件

条件: 特に断りのない限り、VDD = 3.3V±0.3V または 5.0V±0.5V、T<sub>AMB</sub> = -40°C ~+160°C

表 6 動作条件

| 記号                       | パラメータ                                                                                                          | 条件                                                                                                  | 最小                   | 標準    | 最大               | 単位  |

|--------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|-------|------------------|-----|

| T <sub>AMB_TSSOP</sub>   | Ambient temperature                                                                                            | 16-TSSOP package with exposed pad                                                                   | -40                  |       | 160 <sup>1</sup> | °C  |

| T <sub>J</sub>           | Junction temperature                                                                                           |                                                                                                     | -40                  |       | 165              | °C  |

| T <sub>STOR</sub>        | Storage temperature                                                                                            | Unmounted units must be limited to 10 hours at temperatures above 125°C                             | -55                  |       | 160              | °C  |

| R <sub>THJA_TSSOP</sub>  | Thermal resistance junction to ambient: 16-TSSOP package with exposed pad.<br>Velocity = 0m/s<br>JEDEC MO-153. | Copper ground planes under exposed pad on 4 layer PCB, 3x3 thermal vias between layers.             |                      | 35.48 |                  | K/W |

|                          |                                                                                                                | Copper ground planes under exposed pad on 2 layer PCB, 3x3 thermal vias between layers.             |                      | 39.96 |                  |     |

|                          |                                                                                                                | Without PCB ground plane under exposed pad.                                                         |                      | 61.26 |                  |     |

| R <sub>THJC_TSSOP</sub>  | Thermal resistance junction to case                                                                            | Junction to bottom of package                                                                       |                      | 6.42  |                  | K/W |

| t <sub>pup</sub>         | Start-up time                                                                                                  | Power-on reset (POR) to valid output signal                                                         |                      |       | 5                | ms  |

| V <sub>EL</sub>          | Input rotational velocity, Electrical speed; sine or cosine periods                                            | Electrical revolutions per minute                                                                   |                      |       | 600 000          | rpm |

|                          |                                                                                                                | Input frequency                                                                                     |                      |       | 10               | kHz |

| V <sub>VDDA_TH_H</sub>   | Power-on reset (POR), high threshold                                                                           | The device is activated when VDDA increases above this threshold                                    |                      |       | 2.49             | V   |

| V <sub>VDDA_TH_L</sub>   | Power-on reset, low threshold                                                                                  | The device is deactivated when VDDA decreases below this threshold                                  | 2.08                 |       |                  | V   |

| VDDA <sub>POR_HYST</sub> | Power-on reset hysteresis                                                                                      | At VDDA pins                                                                                        |                      | 110   |                  | mV  |

| I <sub>VDDA</sub>        | VDDA short circuit current limitation                                                                          | VDDA must be connected to a capacitor C <sub>VA</sub> . No other external load allowed at this pin. | 40                   |       | 85               | mA  |

| I <sub>cc</sub>          | Current consumption                                                                                            | Without coils, no load                                                                              | 5                    |       | 12               | mA  |

|                          |                                                                                                                | Programmable transmitter coil drive current (depending on inductance of the transmitter coil)       | 値については、表 9 を参照してください |       |                  | mA  |

| C <sub>VA</sub>          | Capacitor from VDDA pin to GND                                                                                 |                                                                                                     |                      | 100   |                  | nF  |

<sup>1</sup>: 周囲温度が 155°Cを超える動作は、デバイス寿命にわたり 120 時間に制限されます。

| 記号           | パラメータ                                                      | 条件                                                                                                                                                                                    | 最小 | 標準 | 最大        | 単位       |

|--------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|-----------|----------|

| $C_{VDD}$    | Capacitor from VDD pin to GND                              | Nominal value<br><br>With ideal sinusoidal input signals, 150mV <sub>pk-pk</sub><br>Differential output mode,<br>Transmitter frequency = 3.5MHz<br>AGC = on<br>Channel swapping = off | 70 |    |           | nF       |

| $INL_{uv3V}$ | Accuracy, 3.3V Mode, VDD=under-voltage alarm level to 3.0V |                                                                                                                                                                                       |    |    | $\pm 0.2$ | % FS [a] |

| $INL_{3V}$   | Accuracy, 3.3V Mode, VDD= 3.0 to 3.6V                      |                                                                                                                                                                                       |    |    | $\pm 0.1$ | % FS     |

| $INL_{ov3V}$ | Accuracy, 3.3V Mode, VDD= 3.6V to over-voltage alarm level |                                                                                                                                                                                       |    |    | $\pm 0.2$ | % FS     |

| $INL_{uv5V}$ | Accuracy, 5V Mode, VDD=under-voltage alarm level to 4.5V   |                                                                                                                                                                                       |    |    | $\pm 0.2$ | % FS     |

| $INL_{5V}$   | Accuracy, 5.0V Mode, VDD= 4.5 to 5.5V                      |                                                                                                                                                                                       |    |    | $\pm 0.1$ | % FS     |

| $INL_{ov5V}$ | Accuracy, 5.0V Mode, VDD= 5.5V to over-voltage alarm level |                                                                                                                                                                                       |    |    | $\pm 0.2$ | % FS     |

[a] % FS = フルスケールのパーセント= 周期あたりの精度 (%) で、100%は 1 電気周期の角度範囲です。

回転式多周期設計の場合、1 電気周期 = 360° (1 フルターン) を 1 回転あたりの周期数で割ったものです。セクション 20 の例を参照してください。

## 6. 使用温度範囲

IPS2550 の最低周囲温度は -40°C です。

最高周囲温度は、以下の要素に依存します:

- 最大ジャンクション温度: 詳細は表 6 を参照してください。

- 電源電流: チップの総消費電力は、電源電圧、内部電源電流、およびユーザがプログラム可能な送信コイル電流に依存します。プログラム可能な送信コイル電流を表 9 に、内部回路の消費電流を表 6 に示します。

- 使用条件でのコイル電流: 一般的には、小さなコイルは多くの送信コイル電流を必要とし、大きなコイルは少ないコイル電流で動作することができます。コイルの直径が 25mm から 30mm の範囲の標準的なコイル設計では、コイル電流は約 3mA から 5mA、電源電流はそれぞれ約 12mA から 14mA を必要とします。IPS2550 は、送信コイル電流を 20mA まで駆動することができます。

- 部品の使用温度範囲: IPS2550 は、-40°C ~ +160°C の周囲温度で認定されています。

- PCB 上のグランドプレーンと組み合わせたパッケージの熱抵抗

VDD = 5.5V での、最大電源電流と、気流冷却が無い場合の異なる層数の PCB の周囲温度の関係を

図 4 の丸囲みに示します。例えば、エクスポーズドパッド下にグランドプレーンがある PCB の場合、 $T_{ambient} = 160^{\circ}\text{C}$  での最大電源電流 (内部電流+送信コイル電流) は、4 層 PCB で 25.6mA、2 層 PCB で 22.8mA です。グランドプレーンは、エクspoーズドパッドと同じ面積で、全層に配置され 3x3 個のビアで接続されていると想定しています。

Note: パッケージ外形図に示されているエクspoーズドパッド両側にある凸部はグランドプレーンとして配置する必要は有りません。

エクspoーズドパッド下にグランドプレーンがない場合、周囲温度 160°C での最大消費電流は 14.8mA となります。最高周囲温度が 155°C よりも低い場合や最大消費電流が 29.7mA より低い場合は PCB のグランドプレーンは必要ありません。最大消費電流が 18mA より低い場合は周囲温度が 159°C まで PCB のグランドプレーンは必要ありません。

図 4 最大消費電流-周囲温度特性(グランドプレーン有・無)

## 7. 電気特性

以下の電気的仕様は、表 6 に規定されている動作条件下で有効です。(T<sub>AMB</sub> は -40°C ~ 160°C です)

表 7 IPS2550 電気的特性、3.3V モード

| 記号                    | パラメータ                                | 条件                                                                                            | 最小   | 標準   | 最大   | 単位 |

|-----------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|----|

| VDD <sub>3</sub>      | Supply voltage                       |                                                                                               | 3.0  | 3.3  | 3.6  | V  |

| V3 <sub>OVR</sub>     | Over-voltage detection, VDD rising   | An over-voltage alarm is created if VDD rises above this limit                                | 3.7  | 3.86 | 4.1  | V  |

| V3 <sub>OVF</sub>     | Over-voltage detection, VDD falling  | An over-voltage alarm is cleared if VDD falls below this limit                                | 3.65 | 3.79 | 4.0  | V  |

| V3 <sub>OVH</sub>     | Over-voltage detection hysteresis    |                                                                                               |      | 70   |      | mV |

| V3 <sub>UVR</sub>     | Under-voltage detection, VDD falling | An under-voltage alarm is created if VDD falls below this limit                               | 2.65 | 2.75 | 2.90 | V  |

| V3 <sub>UVF</sub>     | Under-voltage detection, VDD rising  | An under-voltage alarm is cleared if VDD rises above this limit                               | 2.70 | 2.85 | 3.00 | V  |

| V3 <sub>UVH</sub>     | Under-voltage detection hysteresis   |                                                                                               |      | 100  |      | mV |

| VDDA <sub>3</sub>     | Analog supply voltage                | Internally regulated. Connect capacitor C <sub>VA</sub> = 100nF between VDDA and GND (表 6 参照) | 2.85 | 3.0  | 3.1  | V  |

| V3VDDA <sub>UVF</sub> | VDDA under-voltage detection         | An under-voltage alarm is created if VDDA falls below these limits.                           | 2.59 |      | 2.80 | V  |

| 記号                    | パラメータ                                   | 条件                                                                  | 最小   | 標準 | 最大   | 単位 |

|-----------------------|-----------------------------------------|---------------------------------------------------------------------|------|----|------|----|

| V3VDDA <sub>UVR</sub> | VDDA under-voltage detection            | An under-voltage alarm is cleared if VDDA rises above these limits. | 2.63 |    | 2.85 | V  |

| V3VDDA <sub>UVH</sub> | VDDA Under-voltage detection hysteresis |                                                                     |      | 45 |      | mV |

表 8 IPS2550 電気的特性、5.0V モード

| 記号                    | パラメータ                                   | 条件                                                                                              | 最小   | 標準   | 最大   | 単位 |

|-----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|----|

| VDD <sub>5</sub>      | Supply voltage                          |                                                                                                 | 4.5  | 5.0  | 5.5  | V  |

| V5 <sub>OVR</sub>     | Over-voltage detection, VDD rising      | An over-voltage alarm is created if VDD rises above this limit                                  | 5.60 | 5.84 | 6.10 | V  |

| V5 <sub>OVF</sub>     | Over-voltage detection, VDD falling     | An over-voltage alarm is cleared if VDD falls below this limit                                  | 5.55 | 5.76 | 6.05 | V  |

| V5 <sub>OVH</sub>     | Over-voltage detection hysteresis       |                                                                                                 |      | 80   |      | mV |

| V5 <sub>UVR</sub>     | Under-voltage detection, VDD falling    | An under-voltage alarm is created if VDD falls below this limit                                 | 4.10 | 4.33 | 4.45 | V  |

| V5 <sub>UVF</sub>     | Under-voltage detection, VDD rising     | An under-voltage alarm is cleared if VDD rises above this limit                                 | 4.20 | 4.40 | 4.49 | V  |

| V5 <sub>UVH</sub>     | Under-voltage detection hysteresis      |                                                                                                 |      | 70   |      | mV |

| VDDA <sub>5</sub>     | Analog supply voltage                   | Internally regulated. Connect a capacitor C <sub>VA</sub> = 100nF between VDDA and GND (表 6 参照) | 3.9  | 4.0  | 4.1  | V  |

| V5VDDA <sub>UVF</sub> | VDDA under-voltage detection            | A VDDA under-voltage alarm is triggered when VDDA falls below these limits.                     | 3.50 |      | 3.79 | V  |

| V5VDDA <sub>UVR</sub> | VDDA under-voltage detection            | A VDDA under-voltage alarm is cleared if VDDA rises above these limits.                         | 3.60 |      | 3.87 | V  |

| V5VDDA <sub>UVH</sub> | VDDA Under-voltage detection hysteresis |                                                                                                 |      | 65   |      | mV |

表 9 LC 発振回路の仕様

| 記号                | パラメータ                                                     | 条件                                                                             | 最小  | 標準 | 最大  | 単位              |

|-------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|-----|----|-----|-----------------|

| R <sub>Peq</sub>  | Equivalent parallel resistance of the LC resonant circuit | 式 4 参照                                                                         | 250 |    |     | Ω               |

| f <sub>LC</sub>   | Excitation frequency                                      | LC oscillator frequency is determined by external components L and C.          | 2.0 |    | 5.6 | MHz             |

| V <sub>TX_P</sub> | LC oscillator amplitude                                   | Peak-to-peak voltage; pins TX1 vs. TX2; all modes. Adjustable by coil current. |     | 6  | 11  | V <sub>pp</sub> |

| 記号                 | パラメータ                                       | 条件                                                                                | 最小 | 標準 | 最大 | 単位       |

|--------------------|---------------------------------------------|-----------------------------------------------------------------------------------|----|----|----|----------|

| $I_{LC}$           | Programmable transmitter coil drive current | Equivalent DC current.<br>Programmable, depending on transmitter coil inductance. | 0  | 3  | 20 | mA       |

| $R_{TX1}, R_{TX2}$ | TX Series resistor                          | For reduced EMC emission                                                          |    | 22 |    | $\Omega$ |

図 5 並列共振回路

LC 発振回路の等価並列抵抗  $R_{P\text{eq}}$  は、式 4 を使用して計算できます。安定な動作のために発振回路が駆動できる最小損失抵抗を定義します。

Note: EMC を改善するため、2 つの C の 2 倍の容量値の容量 ( $C_{TX1} = C_{TX2} = 2C$ ) を GND に対して並列に接続する事を推奨します。詳細に付いては図 2 と図 3 も参照してください。

$$R_{P\text{eq}} = \frac{1}{R_S} \times \frac{L}{C} \quad \text{式 4}$$

ここで:

$R_{P\text{eq}}$  LC 発振回路の等価並列抵抗。

$R_S$  送信機周波数における送信コイルの直列抵抗。

$L$  共振周波数におけるコイルのリアクタンス。

$C$  並列コンデンサの静電容量。

C0G、NP0 セラミックコンデンサの場合、コンデンサ損失は無視できるため、式には含まれませんのでご注意ください。

表 10 コイルレシーバフロントエンド仕様

| 記号                      | パラメータ                                                                   | 条件                                                                                                  | 最小    | 標準     | 最大    | 単位               |

|-------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------|--------|-------|------------------|

| $V_{RX}$                | Receiver coil amplitude.                                                | Input signal full range to maintain AGC target levels: 3.0V p-p AGC target, gain boost bit disabled | 25    |        | 1500  | mV <sub>pp</sub> |

|                         |                                                                         | Input signal full range to maintain AGC target levels: 3.0V p-p AGC target, gain boost bit enabled  | 13    |        | 780   |                  |

|                         |                                                                         | Input signal full range to maintain AGC target levels: 1.8V p-p AGC target, gain boost bit disabled | 15    |        | 920   |                  |

|                         |                                                                         | Input signal full range to maintain AGC target levels: 1.8V p-p AGC target, gain boost bit enabled  | 8     |        | 470   |                  |

| $A_{IN\_mm}$            | Maximum amplitude mismatch correction                                   | Programmable individual gain mismatch correction of Receiver coil signals (SIN and COS)             | 13    |        | 20    | %                |

|                         | Amplitude mismatch step size                                            |                                                                                                     | 0.1   |        | 0.15  | %                |

| $A_{IN\_OFFSET\_POS\%}$ | Maximum positive input offset correction.                               | Differential input offsets of sine or cosine signal, percentage of transmitter coil amplitude.      | +0.17 |        | +0.23 | %                |

| $A_{IN\_OFFSET\_NEG\%}$ | Maximum negative input offset correction.                               |                                                                                                     | -0.25 |        | -0.17 | %                |

| $A_{IN\_OFFSET\_mV}$    | Input offset correction range at typical oscillator amplitude (表 9 参照). |                                                                                                     | -7.5  |        | 7.5   | mV               |

| $OFF_{CORR\_RES}$       | Input offset correction step size                                       |                                                                                                     |       | 0.0015 |       | %                |

| $R_{Rx}$                | Coil receiver DC input resistance                                       | Common mode to GND                                                                                  |       | 20     |       | kΩ               |

|                         |                                                                         | Differential                                                                                        |       | 100    |       | kΩ               |

| $C_{RX1}$               | Receiver input filter capacitors                                        | For improved EMC immunity                                                                           |       | 100    |       | pF               |

| $C_{RX2}$               |                                                                         |                                                                                                     |       |        |       |                  |

| $C_{RX3}$               |                                                                         |                                                                                                     |       |        |       |                  |

| $C_{RX4}$               |                                                                         |                                                                                                     |       |        |       |                  |

表 11 自動ゲインコントロール (AGC)

| 記号                   | パラメータ                                                         | 条件                                                                            | 最小  | 標準                     | 最大  | 単位              |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------|-----|------------------------|-----|-----------------|

| VOUT <sub>AGC1</sub> | Output signal amplitude, single ended, AGC enabled            | Program option1, for 3.3V Mode and 5V mode (default)                          | 1.4 | 1.8                    | 2.2 | V <sub>PP</sub> |

| VM <sub>AGC1W</sub>  | AGC1, no-switching window                                     | AGC1 signal magnitude window, in which gain setting is not changed            | 200 | 207                    | 218 | mV              |

| VOUT <sub>AGC2</sub> | Output signal amplitude, single ended, AGC enabled            | Program option2, for 5V mode                                                  | 2.6 | 3.0                    | 3.4 | V <sub>PP</sub> |

| VM <sub>AGC2W</sub>  | AGC2, no-switching window                                     | AGC2 signal magnitude window, in which gain setting is not changed            | 195 | 201                    | 208 | mV              |

| GAIN <sub>AFE</sub>  | Overall gain adjustment range, sine and cosine signal channel | Default setting                                                               | 2   |                        | 120 | V/V             |

|                      |                                                               | With gain boost bit set                                                       | 4   |                        | 240 |                 |

| AGCAttack            | AGC attack time, increase/decrease in same direction          |                                                                               |     | 10                     |     | μs              |

| AGCDecay             | AGC decay time                                                | AGC reversing direction, programmable decay time                              |     | 0<br>30<br>100<br>300  |     | ms              |

| t <sub>swap</sub>    | Channel swapping cadence                                      | Channel swapping functional safety feature enabled, programmable cadence time |     | 10<br>50<br>100<br>200 |     | μs              |

表 12 診断チェック

| 記号                 | パラメータ                                                                                              | 条件                                                                                                                                                                                  | 最小                    | 標準   | 最大         | 単位 |

|--------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------------|----|

| $t_{fail}$         | Failure reaction time, (time to flag an error condition at the ADR_IRQN pin)                       | Chip internal diagnostic checks                                                                                                                                                     |                       |      | 500        | μs |

| $t_{oc\_assert}$   | Debounce time for switching off the analog output amplifiers in case of overcurrent                | Load current on any analog output exceeding the current limit ( $I_{OL}$ ); all four analog outputs are switched off (tri-state) after this time. <sup>[a]</sup>                    | 135                   |      | $t_{fail}$ | μs |

| $t_{cm\_assert}$   | Debounce time for switching off the analog output amplifiers in case of output common mode failure | If the common mode voltage on any analog output exceeds the $V_{CM}$ limit ( $D_{COFF\_AL}$ ); all four analog outputs are switched off (tri-state) after this time. <sup>[b]</sup> | 40                    |      | $t_{fail}$ | μs |

| $t_{oc\_deassert}$ | Debounce time for temporary release of analog outputs after overcurrent failure                    | Following an overcurrent switch-off condition, all outputs are turned on again after this time                                                                                      | 4.61                  | 4.68 | 4.75       | ms |

| $t_{cm\_deassert}$ | Debounce time for temporary release of analog outputs after output common mode failure             | Following an output common mode switch-off condition, all outputs are turned on again after this time                                                                               | $t_{oc\_deassert}$ 参照 |      |            | ms |

| $R_{open\_th}$     | Resistance of Rx coil, open coil detection                                                         | Rx coil error flag activated                                                                                                                                                        | 91                    |      | 154        | kΩ |

| $R_{short\_GND}$   | External resistance from any coil input to GND, short-to-ground detection                          | Rx coil error flag activated                                                                                                                                                        | 68                    |      | 117        | kΩ |

| $R_{short\_VDD}$   | External resistance from any coil input to VDD, short to VDD detection                             | Rx coil error flag activated; VDD = 3.0 to 5.5V                                                                                                                                     | 14                    |      | 233        | kΩ |

| $R_{short\_th}$    | Rx coil error flag cleared                                                                         | Rx coil error flag cleared                                                                                                                                                          | 50                    |      | 130        | kΩ |

| $D_{COFF\_AL}$     | DC common mode output offset alarm limits                                                          | Absolute value relative to VDD/2. Output offset alarm flag activated.                                                                                                               | 75                    |      | 195        | mV |

[a]: このリミット値より短い時間の過電流は無視されます

[b]: このリミット値より短い時間のコモン電圧異常は無視されます

表 13 バックエンド仕様、アナログ出力 SIN\_SCL、SINN、COS\_SDA、COSN

| 記号              | パラメータ                                         | 条件                                 | 最小        | 標準 | 最大        | 単位    |

|-----------------|-----------------------------------------------|------------------------------------|-----------|----|-----------|-------|

| $V_{3OUT}$      | Analog output range, 3.3V option              | $-1.5mA \leq I_{OUT} \leq 1.5mA$   | GND + 0.4 |    | VDD - 0.4 | V     |

| $V_{5OUT}$      | Analog output range, 5V option                | $-2.5mA \leq I_{OUT} \leq 2.5mA$   |           |    |           |       |

| $V_{DDOUT\_CM}$ | Output DC offset voltage, common mode voltage | All modes,<br>Deviation from VDD/2 | -35       | 0  | 35        | mV    |

| $D_{COFFDRIFT}$ | DC offset voltage drift                       | Over temperature range             | -50       |    | 50        | μV/°C |

| 記号                | パラメータ                       | 条件                                                     | 最小 | 標準 | 最大 | 単位               |

|-------------------|-----------------------------|--------------------------------------------------------|----|----|----|------------------|

| I <sub>OUT3</sub> | Output current; 3.3V option | Voltage change $\pm 6\text{mV}$ relative to no load    | -3 |    | +3 | mA               |

| I <sub>OUT5</sub> | Output current; 5V option   | Voltage change $\pm 10\text{mV}$ relative to no load   | -5 |    | +5 | mA               |

| I <sub>OVL</sub>  | Output overload current     | Short circuit current limit                            | 15 |    | 30 | mA               |

| Noise             | Device output noise         | Maximum gain, no output filtering, shorted coil inputs |    | 2  | 5  | mV <sub>ms</sub> |

| C <sub>OUT1</sub> | Output filter capacitors    | For improved EMC immunity, placed close to IC output   |    |    |    |                  |

| C <sub>OUT2</sub> |                             |                                                        |    |    | 47 | nF               |

| C <sub>OUT3</sub> |                             |                                                        |    |    |    |                  |

| C <sub>OUT4</sub> |                             |                                                        |    |    |    |                  |

表 14 デジタル I2C 制御インターフェース、SDA、SCL ピン

| 記号                                     | パラメータ                                                       | 条件                                                                                        | 最小      | 標準  | 最大      | 単位  |

|----------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|-----|---------|-----|

| V <sub>IH</sub>                        | High level input voltage, all modes                         | IRQN address select input,<br>SCL clock input,<br>SDA data input                          | 0.7•VDD |     | VDD+0.3 | V   |

| V <sub>IL</sub>                        | Low level input voltage, all modes                          |                                                                                           | -0.3    |     | 0.3•VDD | V   |

| I <sub>LEAK</sub>                      | Input leakage current                                       | VDD = 0V to 5.5V                                                                          | -8      |     | 1.5     | µA  |

| V <sub>I_STR_hyst</sub>                | Hysteresis of Schmitt trigger input                         | SCL clock input                                                                           | 0.1     |     |         | V   |

| V <sub>OL_SDA</sub>                    | SDA low level output voltage open drain                     | 3mA sink current                                                                          | 0       |     | 0.4     | V   |

| I <sub>OL_SDA</sub>                    | Low level output current                                    | V <sub>OL</sub> = 0.4V, VDD=5.5V, R <sub>P</sub> =2kΩ                                     | 3       |     |         | mA  |

| C <sub>IN</sub>                        | Capacitance of SDA/SCL pin                                  | Pad and ESD protection                                                                    |         |     | 10      | pF  |

| f <sub>SCL</sub>                       | SCL clock frequency                                         |                                                                                           | 0       |     | 100     | kHz |

| t <sub>LOW</sub>                       | LOW period of SCL clock                                     |                                                                                           | 4.7     |     |         | µs  |

| t <sub>HIGH</sub>                      | HIGH period of SCL clock                                    |                                                                                           | 4.0     |     |         | µs  |

| t <sub>R</sub>                         | Rise time SDA/SCL                                           | V <sub>IHmin</sub> to V <sub>ILmax</sub>                                                  |         |     | 1       | µs  |

| t <sub>F</sub>                         | Fall time SDA/SCL                                           | V <sub>IHmax</sub> to V <sub>ILmin</sub>                                                  |         |     | 0.3     | µs  |

| C <sub>B</sub>                         | External capacitive load for each bus line                  |                                                                                           |         |     | 400     | pF  |

| R <sub>SDA</sub> ,<br>R <sub>SCL</sub> | External pull-up resistor at pins SDA and SCL               | Resistor value and capacitive load on these pins are limiting the maximum clock frequency | 1.8     | 4.7 |         | kΩ  |

| R <sub>ADR</sub>                       | External resistor at pin ADR_IRQN for I2C address selection | Pull-up or pull-down, depending on I2C address setting.                                   | 1.8     | 4.7 |         | kΩ  |

表 15 アナログ出力経由の I2C インタフェース

| 記号                 | パラメータ                                                     | 条件                                                       | 最小      | 標準  | 最大      | 単位         |

|--------------------|-----------------------------------------------------------|----------------------------------------------------------|---------|-----|---------|------------|

| $V_{IH}$           | SIN_SCL/COS_SDA High level input voltage                  |                                                          | 0.7·VDD |     | VDD+0.3 | V          |

| $V_{IL}$           | SIN_SCL/COS_SDA Low level input voltage                   |                                                          | -0.3    |     | 0.3·VDD | V          |

| $V_{I\_STR\_hyst}$ | Hysteresis of Schmitt trigger inputs, SIN_SCL and COS_SDA |                                                          | 0.1     |     |         | V          |

| $V_{OL\_COS\_SDA}$ | COS_SDA low level output voltage, open-drain              | 3mA sink current                                         | 0       |     | 0.4     | V          |

| $I_{OL\_COS\_SDA}$ | COS_SDA Low level output current                          | $V_{OL} = 0.4V$ , $VDD=5.5V$ , $R_P=1.8k\Omega$          | 3       |     |         | mA         |

| $I_{IN}$           | SIN_SCL/COS_SDA input leakage current                     | $VDD = 0V$ to $5.5V$                                     | -1.5    |     | 8       | $\mu A$    |

| $C_{IN}$           | Capacitance of SCL and SDA pins                           | Pad and ESD protection                                   |         |     | 10      | pF         |

| $f_{SCL}$          | SCL clock frequency                                       |                                                          | 4       |     | 25      | kHz        |

| $t_{LOW}$          | LOW period of SCL clock                                   |                                                          | 20      |     | 125     | $\mu s$    |

| $t_{HIGH}$         | HIGH period of SCL clock                                  |                                                          | 20      |     | 125     | $\mu s$    |

| $t_F$              | Fall time SIN_SCL/COS_SDA                                 | $V_{IHmin}$ to $V_{ILmax}$                               |         | 0.8 | 1.2     | $\mu s$    |

| $C_B$              | External capacitive load for SIN_SCL and COS_SDA          |                                                          |         |     | 47      | nF         |

| $t_{PEU}$          | Program Entry window after POR                            | First time window to start sending unlock command        | 1.5     |     | 5       | s          |

| $t_{PW}$           | Program Start window after Unlock                         | Second time window to complete first programming command |         |     | 75      | s          |

| $R_{PU}$           | External pull-up resistors                                | Optional; for diagnostic indication                      | 表 24 参照 |     |         | k $\Omega$ |

|                    |                                                           | Optional; during programming on pins SIN_SCL and COS_SDA | 1.8     |     |         | k $\Omega$ |

| $R_{PD}$           | External pull-down resistors                              | Optional; for diagnostic indication                      | 表 25 参照 |     |         | k $\Omega$ |

表 16 デジタル I2C 制御インターフェース、ピン ADR\_IRQN

| 記号                 | パラメータ                              | 条件                                   | 最小      | 標準 | 最大      | 単位      |

|--------------------|------------------------------------|--------------------------------------|---------|----|---------|---------|

| $V_{IH}$           | ADR_IRQN High level input voltage  |                                      | 0.7•VDD |    | VDD+0.3 | V       |

| $V_{IL}$           | ADR_IRQN Low level input voltage   |                                      | -0.3    |    | 0.3•VDD | V       |

| $V_{I\_STR\_hyst}$ | Hysteresis Schmitt trigger input   |                                      | 0.1     |    |         | V       |

| $I_{LEAK}$         | Input leakage current              |                                      | -8      |    | 1.5     | $\mu$ A |

| $V_{OH}$           | ADR_IRQN high level output voltage | ADR_IRQN configured as interrupt pin | 0.8•VDD |    | VDD+0.3 | V       |

| $V_{OL}$           | ADR_IRQN low level output voltage  |                                      | -0.3    |    | 0.2•VDD | V       |

表 17 不揮発性メモリ

| 記号            | パラメータ                    | 条件                                                          | 最小                 | 標準                            | 最大   | 単位               |

|---------------|--------------------------|-------------------------------------------------------------|--------------------|-------------------------------|------|------------------|

| $DR_{NVM}$    | Data retention           | According to AEC Q100                                       |                    | > 100 at 25°C<br>>15 at 100°C |      | Years            |

| $t_{Wr\_NVM}$ | Write temperature        | Allowed ambient temperature range for read and write access | -40                |                               | 135  | °C               |

| $t_{Rd\_NVM}$ | Read temperature         |                                                             | -40                |                               | 160  | °C               |

| $C_{Wr\_NVM}$ | Endurance <sup>[a]</sup> | Over product lifetime                                       |                    |                               | 1000 | NVM Write Cycles |

| $C_{Rd\_NVM}$ | Read Cycles              |                                                             | $5 \times 10^{11}$ | $1 \times 10^{12}$            |      | NVM Read events  |

[a] 検証済みのプログラム/消去サイクル数。2000 サイクルで認定

## 8. 回路説明

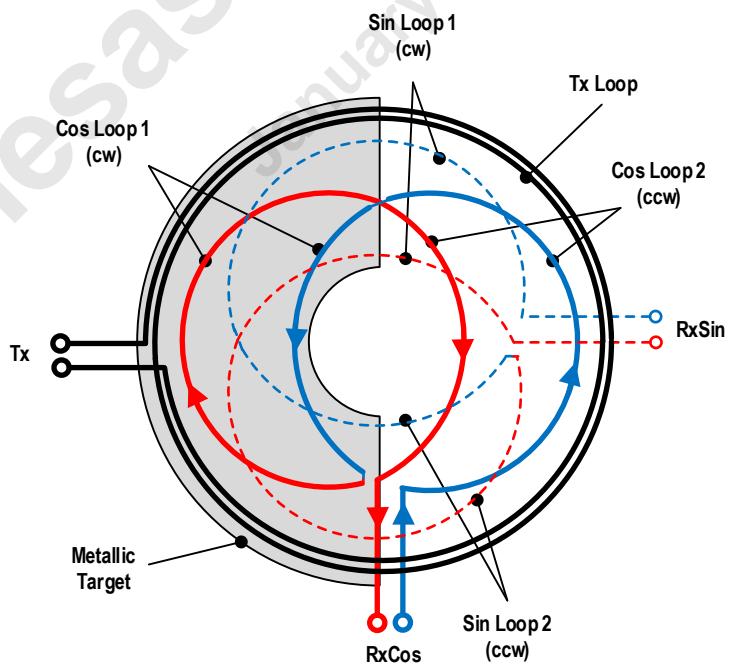

IPS2550 センサ回路は、1 つの送信コイルと 2 つの受信コイルで構成され、通常はプリント回路基板上の薄膜配線として設計されています。2 つの受信コイルはサイン波形状を有し、互いに 90° ずれています。標準的なコイル形状については、図 7 および図 8 を参照してください。金属ターゲットがコイルの上方に配置されます。

回路信号の流れ:

1. IPS2550 は、交流電流で送信コイルを駆動し、交流磁界を生成します。

2. 磁場は受信コイルに電圧を誘起します。金属ターゲットが無い場合、コイルの各セグメントが逆相接続されているために、受信コイル端子での電圧はゼロになります。

3. コイルの上に金属ターゲットが配置されている場合:

- a. 磁場は金属ターゲットの表面に渦電流を誘起します

- b. 渦電流は逆磁場を発生させ、ターゲット下の全磁束密度を減少させます

- c. ターゲット下の受信コイル領域に誘起される電圧が減少し、逆相接続されたコイルのセグメントの電圧に不均衡が生じます

- d. 受信コイル端子に、ターゲット位置に対して振幅と極性が変化する出力電圧が発生します

4. IPS2550 IC は、受信信号の同期復調を行い、その後、フィルタリングして外部信号処理用に出力します。

2 つの受信コイルが 90° 位相シフトしているため、出力信号もターゲット位置に応じて 90° の位相差が有る送信信号に比例したサイン及びコサイン信号を生成します。受信信号は、例えば、 $V_{\sin}$  と  $V_{\cos}$  の Arctangent 演算を行うことによって、絶対位置に変換することができます。

$$\text{Position} = \arctan\left(\frac{V_{\sin}}{V_{\cos}}\right) \quad \text{式 5}$$

### 8.1 概要

図 6 IPS2550 の応答

図 7 に 1 つの送信コイル（送信ループ）と下記の 2 つの受信コイルからなる直線運動センサの例を示します。

$$1. \text{ Sine Loop} = \text{Sin Loop 1} + \text{Sin Loop 2}$$

$$2. \text{ Cosine Loop} = \text{Cos Loop 1} + \text{Cos Loop 2}$$

注: Cosine Loop は Sine Loop と相対的にシフトしているので Cos Loop 1 は以下のように 1/2 に分割されています

$$\text{Cos Loop 1} = \text{Cos Loop 1a} + \text{Cos Loop 1b}$$

ループ内の時計回りと反時計回りに接続されたセグメント（例えばコサイン受信コイルでは 時計回りの Cos Loop1 と反時計回りの Cos Loop2）により、各セグメントの誘導電圧は逆極性になります。

$$V_{\text{Sin Loop 1}} = -V_{\text{Sin Loop 2}}$$

式 6

$$V_{\text{Cos Loop 1}} = -V_{\text{Cos Loop 2}}$$

式 7

ターゲットが存在しない場合、二次電圧は互いに打ち消し合います:

$$V_{\text{Sin}} = V_{\text{Sin Loop 1}} + V_{\text{Sin Loop 2}} = 0V$$

式 8

$$V_{\text{Cos}} = V_{\text{Cos Loop 1}} + V_{\text{Cos Loop 2}} = 0V$$

式 9

コイルの上にターゲットを置くと、カバーされた領域に誘起された二次電圧は、ターゲットが無い場合の二次電圧より低くなります。

$$V_{\text{Sin Loop 1}} \neq -V_{\text{Sin Loop 2}}$$

式 10

$$V_{\text{Cos Loop 1}} \neq -V_{\text{Cos Loop 2}}$$

式 11

これにより、二次電圧セグメントの不均衡が発生し、従って、ターゲットの位置に応じて、 $\neq 0V$  の二次電圧が発生します。

$$V_{\text{Sin}} = V_{\text{Sin Loop 1}} + V_{\text{Sin Loop 2}} \neq 0V$$

式 12

$$V_{\text{Cos}} = V_{\text{Cos Loop 1}} + V_{\text{Cos Loop 2}} \neq 0V$$

式 13

図 7 直線運動センサのためのコイル形状

図 7 で直線運動センサについて示された原理は、図 8 に示されているように、アーケまたは回転センサに適用することができます。

図 8 360° 回転センサ用のコイル形状

## 9. サンプリングレート、分解能、出力データレート、および伝搬遅延

IPS2550 はアナログ信号処理 (ADC を使用しません) を行うため、サンプリング・レートではなく、分解能は事実上無限大です。内部フィルタリングおよび復調工程のため、アナログ入力信号と出力信号の間に短い信号伝搬遅延があります。この遅延は、送信回路の発振周波数とは無関係に、工場出荷時に固定値にトリミングされています。

コイル受信回路は自動的に送信コイル発振器周波数にロックします。これにより、温度変化や、ターゲットとのエアギャップの変化による、LC 発振回路の周波数ドリフトは自動的に補正されます。

表 18 伝搬遅延

| 記号             | パラメータ                                                                           | 条件                                                                       | 最小  | 標準  | 最大   | 単位    |

|----------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-----|------|-------|

| $t_{PD\_trim}$ | Propagation delay of receiver input signals 1 and 2 at Sine and Cosine outputs. | Factory trimmed; at room temperature over specified supply voltage range | 3.8 | 4   | 4.2  | μs    |

| $t_{PD\_tc}$   | Propagation delay temperature drift                                             | over specified operating temperature range                               | 1.8 | 2.2 | 2.65 | ns/°C |

## 10. 出力モード

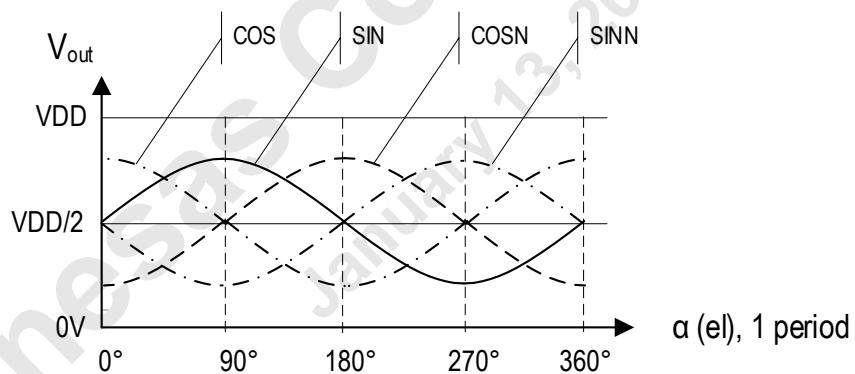

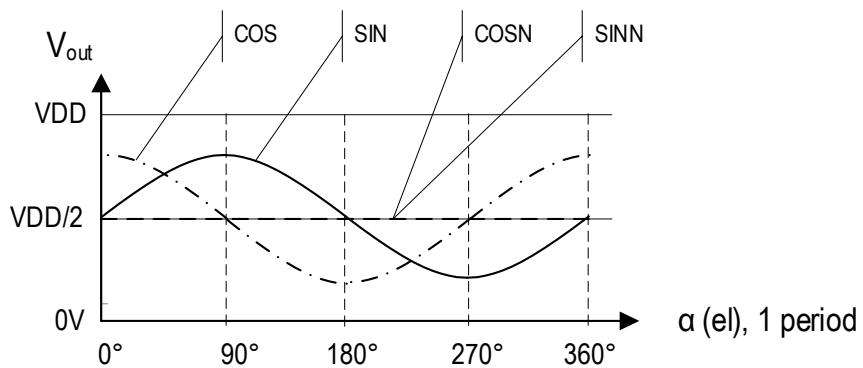

図 9 出力信号: サイン-コサインアナログ差動モード

図 10 出力信号: サイン-コサインアナログシングルエンドモード

## 11. 高速での動作

IPS2550 はアナログ信号処理を使用しているため、入力信号を非常に高速に処理できます。入力信号は、600 000 rpm (1 分間あたりの電気回転数) に相当する最大 10kHz の周波数を処理する事ができます。より高い周波数、すなわち、より高い速度の処理も可能ですが、性能と信号振幅が低下します。

機械回転速度は、式 14 で計算できます：

$$rpm(mech) = \frac{rpm (el)}{coil periods} \quad \text{式 14}$$

ここで

回転数 (mech) ロータ (およびターゲット) の回転速度 (1 分間あたりの回転数)

回転数(el) センサの最大電気入力周波数 (rpm) (電気回転数)

= 600000 電気周期/分 (rpm)

= 10000 電気周期/秒 = 10 kHz

コイル周期 1 ターンあたりの電気的周期数

= 360° 円周あたりのコイル周期数

= 金属ターゲットのセグメント数

例えば、図 30 は、3 周期コイル設計を使用する 6 極モータ (極対数 = 3) のための設計を示します。

このモータの最大機械回転速度は、式 15 に従って計算されます。

$$\frac{600\text{krpm (el)}}{3} = 200\text{krpm (mech)} \quad \text{式 15}$$

表 19 出力モードと最高速度

|                                  | SIN/COS 出力モード                      | ロータ最大速度                     |

|----------------------------------|------------------------------------|-----------------------------|

| Target Design (metal / no metal) | Sine, Cosine Cycles per Revolution | Mechanical Speed            |

| 1 × (180° / 180°)                | 1 × 360°                           | 600krpm                     |

| 2 × (90° / 90°)                  | 2 × 180°                           | 300krpm                     |

| 3 × (60° / 60°)                  | 3 × 120°                           | 200krpm                     |

| 4 × (45° / 45°)                  | 4 × 90°                            | 150krpm                     |

| 6 × (30° / 30°)                  | 6 × 60°                            | 100krpm                     |

| 8 × (22.5° / 22.5°)              | 8 × 45°                            | 75krpm                      |

| 10 × (18° / 18°)                 | 10 × 36°                           | 60krpm                      |

| ...                              | 1 cycle per target                 | 600krpm / targets per wheel |

## 12. デジタル診断およびプログラミングインターフェース

IPS2550 をプログラムし、アナログ高速信号経路を中断することなく高速診断を可能にするために、追加の I2C デジタルシリアルインターフェースが用意されています。

I2C インタフェースは、2 つのモードで動作させることができます：

- アドレスセレクト付き I<sub>2</sub>C インタフェース（デフォルト）

- 割り込み付き I<sub>2</sub>C インタフェース（プログラムオプション）

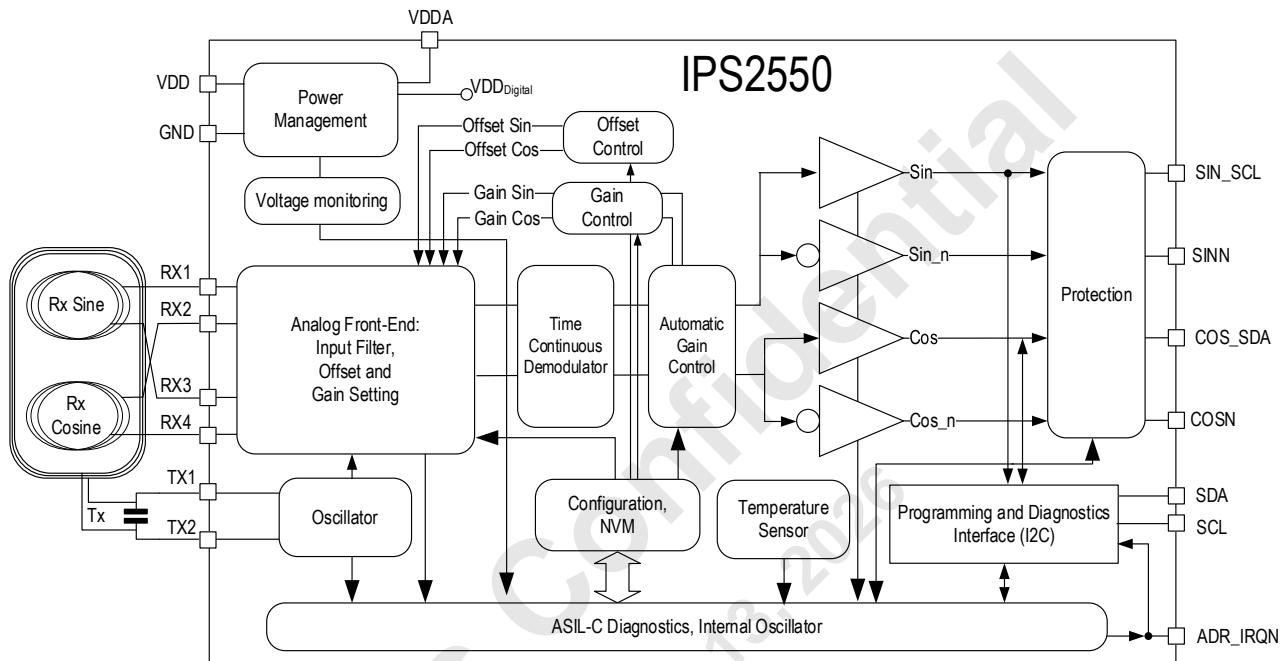

### 13. ブロック図

図 11 に IPS2550 のブロック図を示します。

図 11 ブロック図

主な構成要素には、以下が含まれます:

- Power Management: パワーオンリセット (POR) 回路。アナログおよびデジタル電源用の低損失型レギュレータ (LDO)

- VDD、VDDA、および内部電圧 V<sub>Digital</sub> の過電圧および低電圧監視

- Oscilator: 送信コイル信号の生成

- Analog Front End: 受信信号の入力フィルタ、オフセット、ゲインコントロール

- オフセット制御: レシーバコイル入力 RX1-RX2, RX3-RX4 でのオフセットを補正します

- ゲイン設定: レシーバコイル入力信号 RX1-RX2 と RX3-RX4 の振幅ミスマッチを補正します

- Time Continuous Demodulator: RF 振幅変調位置信号を LF 復調位置信号に変換します

- Gain Control: RX1/RX2, RX3/RX4 入力信号からの振幅ミスマッチを補正します

- Automatic Gain Control: サインおよびコサインチャンネルの全体的ゲインを自動調整します

- Configuration, NVM: 工場出荷時およびユーザーがプログラム可能な設定の不揮発性メモリ

- Programming and Diagnostics Interface: サインおよびコサインアナログ出力インターフェース、または、個別の I<sub>2</sub>C インタフェースを使用できます

- Temperature Sensor: チップ温度の監視

- ASIL-C Diagnosis, Internal Oscillator: 機能安全を確保するための重要な内部診断。工場出荷時にトリミングされた内部オシレータは、チップ内部のタイミングに使用され、送信周波数測定のタイムベースとして使用されます

- 4 個の過電圧保護および逆極性保護機能付きアナログ/デジタル出力バッファ

- SIN\_SCL、SINN、COS\_SDA、および COSN ピンには、3 つのインターフェースオプションがあります（表 2 参照）

- 差動アナログ出力

- リファレンス付きシングルエンドアナログ出力

- プログラム用 I<sub>2</sub>C インタフェース

## 14. ブロックの詳細説明

以下のブロックの図については、図 11 のブロック図を参照してください。

### 14.1 電源管理

IPS2550 は、V<sub>DD</sub> = 3.3V ± 0.3V または V<sub>DD</sub> = 5.0V ± 0.5V のいずれかの電源で動作させることができます。内部 LDO は、アナログ回路とデジタル回路の電源電圧を生成します。アナログ電源（V<sub>DDA</sub>）は、外部コンデンサ C<sub>VA</sub> によってバッファされます。デジタル電源は内部へのみ接続されています。

V<sub>DD</sub> は過電圧および逆接続から保護されており、過電圧または低電圧がないか常に監視されています。

### 14.2 LC 発振回路

LC 発振回路は、センサの RF 磁界を生成し、2MHz～5MHz の周波数帯域で動作します。周波数は、外付け部品 L（送信コイル）と C（外付けコンデンサ）で調整します。詳細は、表 9 を参照してください。

IPS2550 は広範囲なインダクタンスのコイルが使用可能で、コイル駆動電流はユーザがプログラム可能です。

LC 発振回路は、周波数の正しさ、またはオープン/ショートや発振回路の故障などの故障がないかどうか、継続的にチェックされます。

### 14.3 アナログ信号経路

最大速度の場合、IPS2550 は 2 つの並列アナログ信号チャネルを使用します。1 つはサイン用、もう 1 つはコサイン用で、全てアナログ信号処理用です。

#### 14.3.1 Rx コイル診断

レシーバ・コイル Rx Sine および Rx Cosine は、グランドへのオープン/ショート、V<sub>DD</sub>へのショート、および反対側のコイルへのショートがないか、継続的にチェックされます。図 2 および図 3 に示すように、レシーバコイルは次の 2 つの方法で接続できます

- ASIL C 接続:隣接する 2 つのピンのショートによるレシーバコイルの短絡の可能性を防止します。

- 互換接続:産業用 IPS2200 とピン間互換性を提供します。

#### 14.3.2 受信信号ローパスフィルタ

受信信号は振幅変調信号であり、キャリア周波数は LC 発振回路の周波数で、信号振幅は目標位置を表します。回転システムでは、LF 信号はサインおよびコサイン形状であり、LF 信号の 1 周期はコイル形状の 1 周期と等価です。コイル設計の例と対応する LF 信号については、セクション 20 を参照してください。

最初に、振幅変調信号を低域通過フィルタリングして、起り得る RF 電磁擾乱を抑制します。

### 14.3.3 オフセットとゲイン整合

RF 信号はフィルタリングされた後、不完全なコイル設計に由来する可能なオフセットおよび振幅ミスマッチを補正します。オフセットおよび微小ゲイン補正の量は、NVM でユーザーが固定値にプログラムするか、組み込みアプリケーションで動作中に補正することができます。詳細は、セクション 15.1 を参照してください。

### 14.3.4 復調

連続時間復調器は入力信号から搬送波を除去し、復調された LF 信号を生成します。

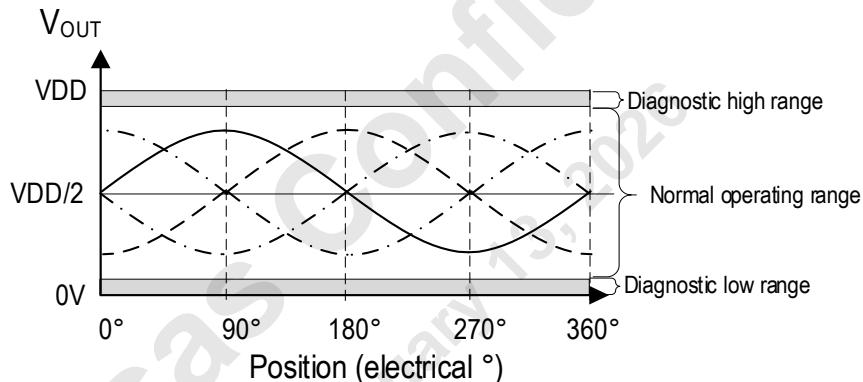

### 14.3.5 自動ゲインコントロール (AGC)

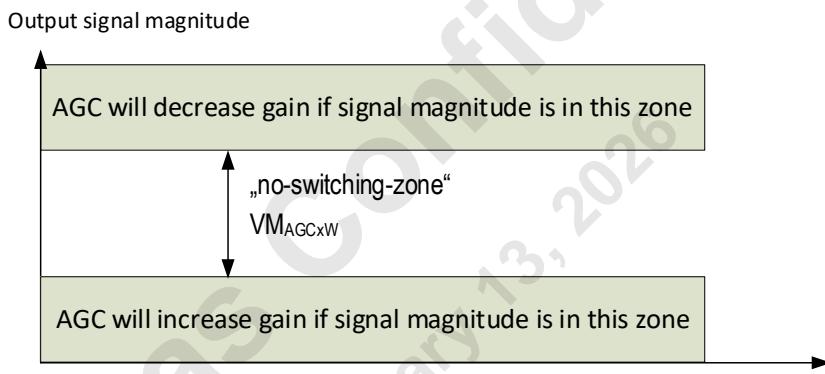

復調された信号の大きさ  $M = \sqrt{V_{sin}^2 + V_{cos}^2}$  は、常時チェックされ、プログラムにより選択可能な定格レベル（表 11 参照）と比較されます。AGC は出力信号の振幅が “no-switching-zone” に入るように受信ゲインを自動的に調整します。

AGC を有効にすることで、ゲインがユーザにプログラムされた範囲を超えた場合、たとえば、入力信号が強すぎるまたは弱すぎる事を示すアラームを生成することができます。

（詳細は表 11 参照）

図 12 AGC 振幅レンジ

### 14.4 信号チャンネルの入れ替え

内部利得誤差の検出を改善する効果的な方法は、設定オプションとして利用可能なルネサス特許出願中の信号チャンネル交換機能です。これを有効にすると、チップは 2 つのアナログ信号経路間でサインおよびコサイン信号チャンネルを周期的に入れ替えます。この方法を適用することで、スタティック（非回転）動作でも、サイン信号チャンネルとコサイン信号チャンネル間のゲインミスマッチをアナログ信号出力で即座に検出できます。

### 14.5 出力バッファ

4 つのアナログ信号（サイン、反転サイン、コサイン、反転コサイン）は、対応する出力ピンで個別にバッファリングされます。バッファ出力は過電圧および逆極性が保護されており、グランドへの短絡、VDDへの短絡、または同相電圧に問題がないか確認されています。診断状態が有効な場合、バッファがオフになり、外部プルアップ抵抗またはプルダウン抵抗を介して外部 MCU への診断表示が可能になります。

## 14.6 温度センサ

IPS2550 は、チップ内部温度センサを搭載しており、温度超過イベントが発生した場合にアラームを発します。温度センサには 2 レベルのアラームがあります：

1. ジャンクション温度が警告しきい値を超えた場合：診断アラームが生成され、SIN\_SCL、COS\_SDA、SINN、COSN の出力バッファがオフになります。消費電力が削減されます。

2. ジャンクション温度がクリティカルアラームレベルを超えた場合：さらに、プログラムオプションとして、LC 発振回路をオフにして、消費電力をさらに削減することができます。

表 20 内部チップ温度センサ特性

| 記号                    | パラメータ                                | 条件 | 最小  | 標準  | 最大  | 単位 |

|-----------------------|--------------------------------------|----|-----|-----|-----|----|

| T <sub>OVT_WARN</sub> | Over-temperature warning threshold   |    | 175 | 180 | 185 | °C |

| T <sub>OVT_ERR</sub>  | Over-temperature error threshold     |    | 180 | 185 | 190 | °C |

| ACC <sub>TS</sub>     | Temperature sensor absolute accuracy |    | -10 |     | +10 | °C |

| T <sub>HYST</sub>     | Temperature hysteresis               |    | 8   | 10  | 12  | °C |

## 15. ECU 接続オプション

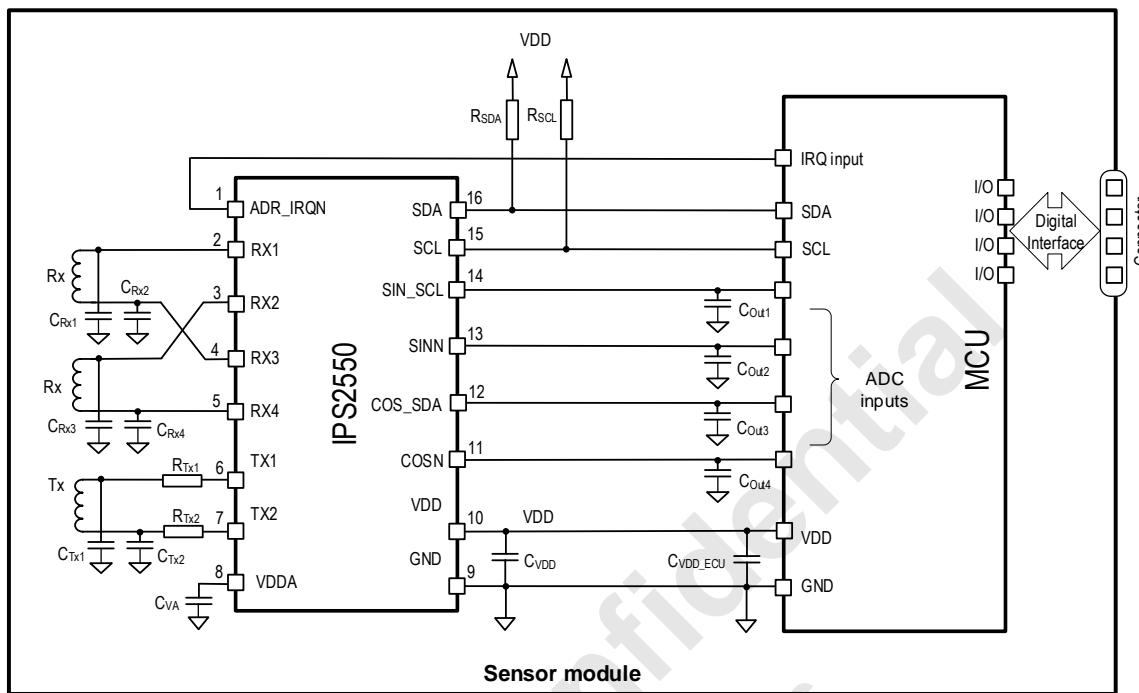

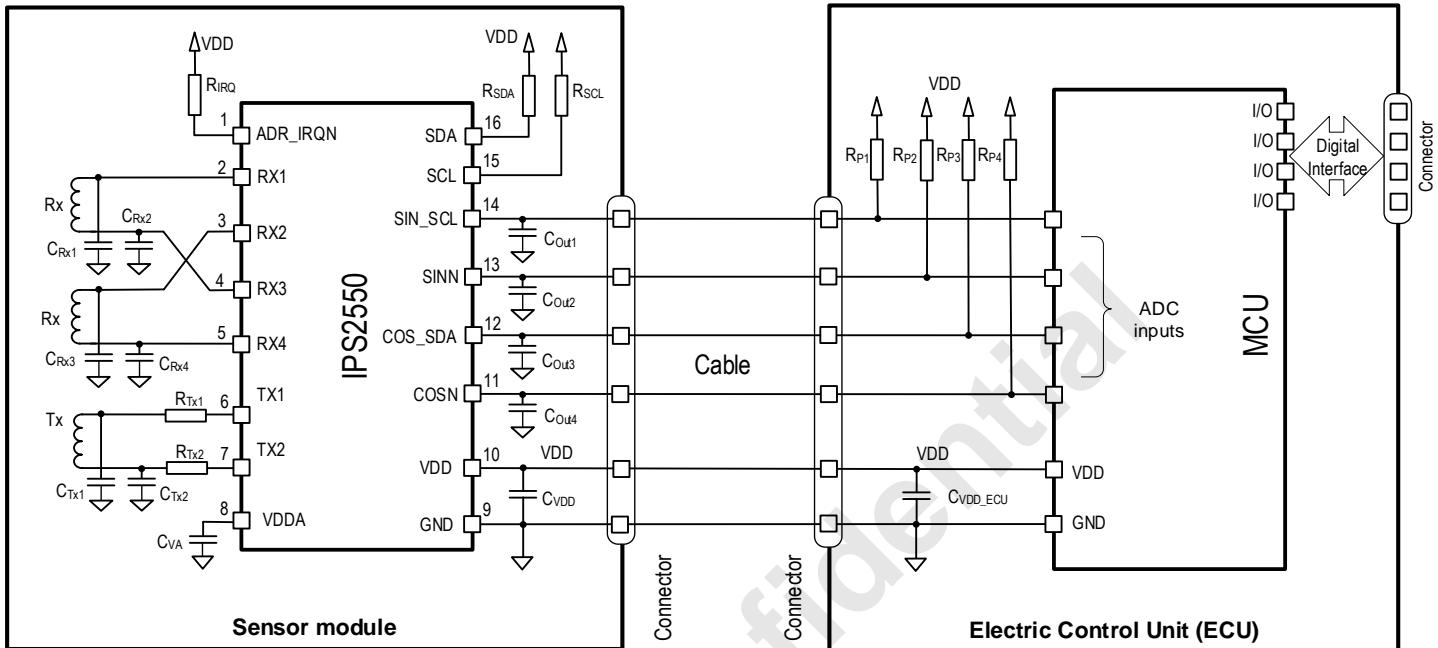

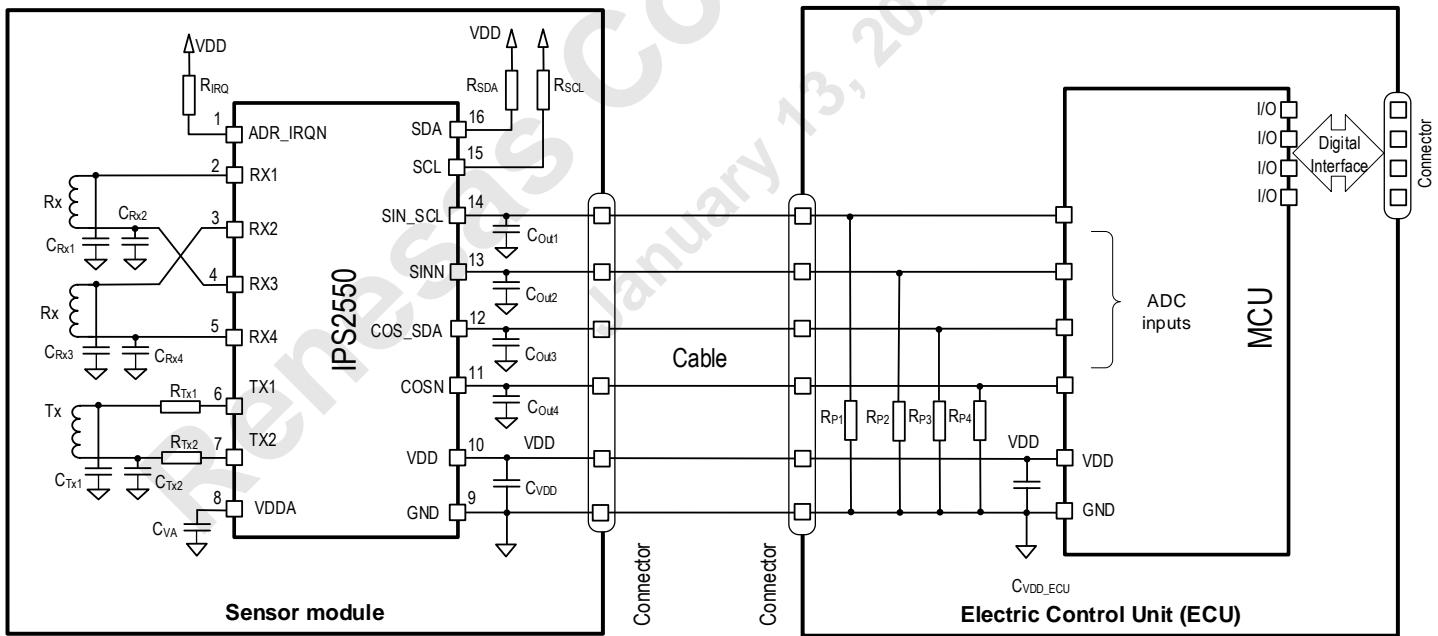

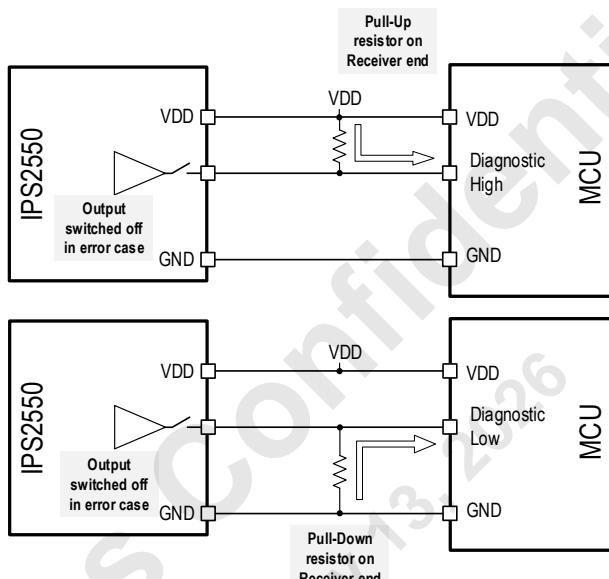

注：図 13、図 14、および図 15 では、IPS2550 と電気制御ユニット（ECU）間のさまざまな接続オプションが示されています。

IPS2550 は、正しい VDD 電圧供給レベル（3.3V または 5.0V）に適合するように適切にプログラムする必要があります。

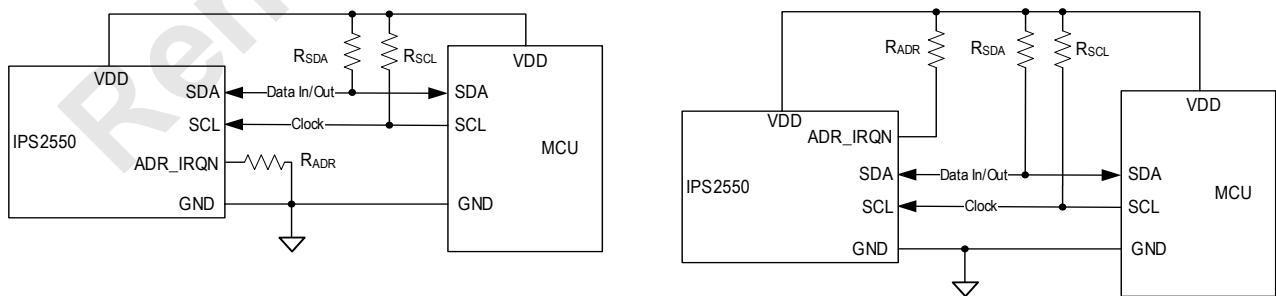

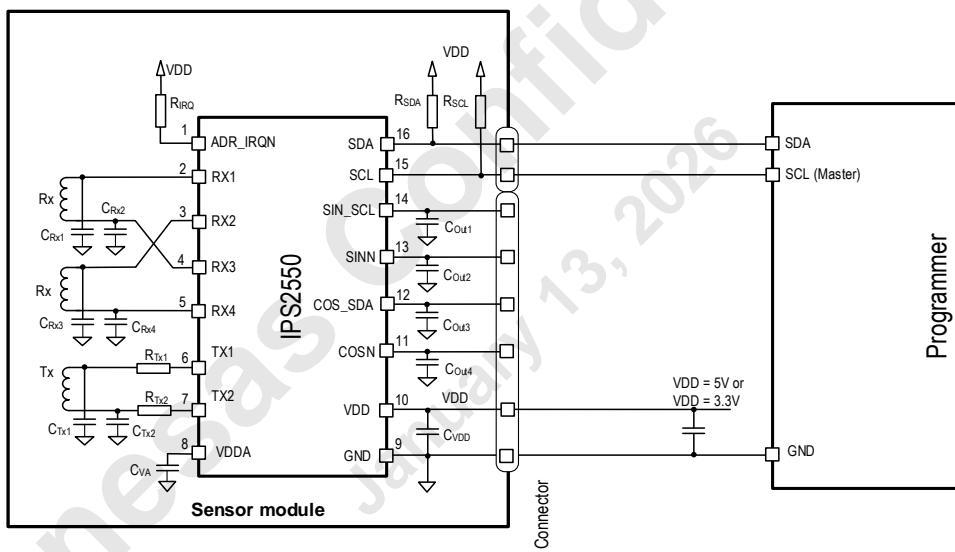

### 15.1 エンベデッド vs. リモート接続

エンベデッド接続では、センサとマイクロコントローラ（MCU）の両方が同じプリント基板基板（PCB）に配置されます。これらのアプリケーションでは、2 つのチップ間の接続数は重要ではありません。MCU は、個別のデジタル I2C インタフェースを利用して、アナログ信号の流れを中断することなく診断レジスタを常時監視したり、オフセットやゲインを動作中に変更したりすることができます。

ADR\_IRQ 端子は、IRQ モードで診断に使用されます。

デジタルインターフェースフェイスピンド、SDA および SCL を使用する場合、IPS2550 および ECU は、デジタルのハイおよびロー信号レベルを一致させるために、同じ VDD 電圧供給レベルを共有する必要があります。

図 13 に示す回路図には、エンベデッド動作で EMC 性能を向上させるために必要な外付け部品が含まれています。

注記：C<sub>Out1</sub>～C<sub>Out4</sub> の容量値は、接続されているマイコンの ADC 入力規格によって異なります。

図 13 エンベデッドアプリケーション: センサと MCU は同じ PCB 上に配置されます

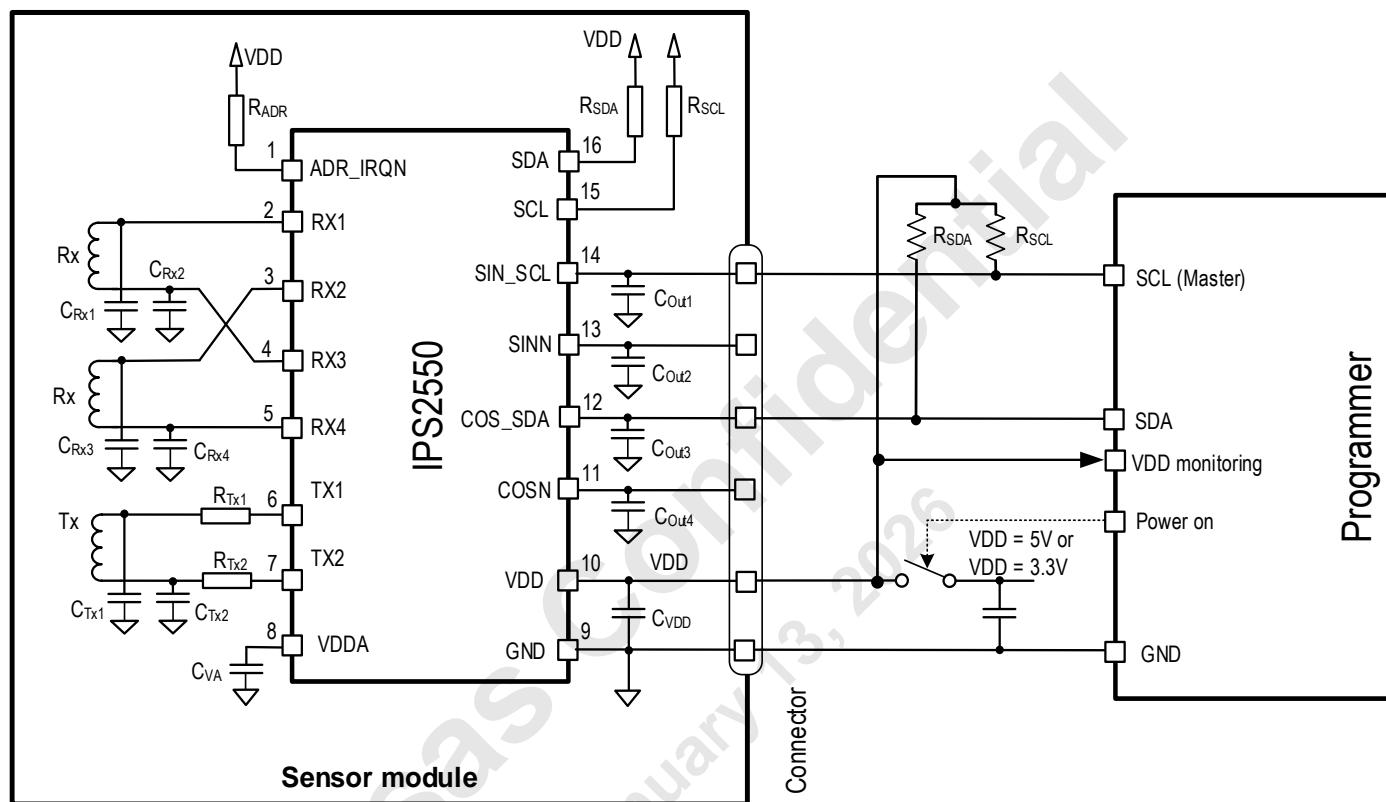

リモートアプリケーションでは、センサモジュールは ECU とは別個になっており、ケーブルで接続されています。コスト効率のために、ケーブル上のワイヤの数とコネクタピンの数はできるだけ少なく保つ必要があります。通常、シングルエンド構成の場合は 4 本のワイヤ (VDD、GND、サイン、コサイン)、差動構成の場合は 6 本のワイヤ (VDD、GND、サイン、反転サイン、コサイン、反転コサイン) が必要です。

エラーの場合、アナログ出力はトライステートモードに切り替わります。診断状態は、プルアップ抵抗を使用して出力電圧を VDD にプルアップするか (図 14 に示すように)、プルダウン抵抗を使用して出力電圧をグランドにプルダウンすることによって示されます (図 15 に示します)。

診断表示の詳細については、セクション 18.2 を参照してください。

図 14 および図 15 に示す回路図には、リモート操作で EMC 性能を向上させるために必要な外付け部品が含まれています。

図 14 診断用プルアップ抵抗付きリモートアプリケーション

図 15 診断用プルダウン抵抗付きリモートアプリケーション

## 15.2 電源電圧動作: 3.3V または 5V

IPS2550 は、 $3.3V \pm 0.3V$  または  $5.0V \pm 0.5V$  の電源電圧のいずれかで動作するようにプログラムできます。デフォルトは 5V です。デフォルトの電源電圧の変更については、セクション 17.1 を参照してください。

### 15.3 I2C インタフェース

IPS2550 には I2C インタフェースが含まれています。I2C アドレスはプログラム可能です。さらに、ADR IRQN ピンは、I2C インタフェースを使用するときに、I2C アドレス選択ピンまたは割り込み出力 (IRQN) ピンのいずれかとしてプログラムできます（表 3 参照）。IPS2550 は I2C スレーブとして構成されています。いくつかのスレーブを I2C バス上で並列接続することができます。プログラム機能の詳細説明は、IPS2550 ユーザープログラミングマニュアルに記載されています。

シリアルデータ (SDA, 16 ピン) とシリアルクロック (SCL, 15 ピン) の 2 本の配線で、バスに接続されたデバイス間で情報を伝達します。SDA と SCL の両方は、外部プルアップ抵抗を介して正の電源電圧 VDD に接続されます。バスがフリーのときは、両方のラインが High になります。ワイヤード AND 機能を使用するには、バスに接続されているデバイスの出力段はオーブンドレインまたはオープンコレクタである必要があります。

外部マスタ（ホストコントローラ）が転送を開始し、クロック信号を生成し、転送を終了します。実装は、マスタによってアドレス指定され、I2C バス仕様バージョン 2.1 をサポートする I2C スレーブ機能をサポートします。

アナログ出力にはパッシブ・フィルタまたは EMC コンデンサが含まれている場合があるため、個別のデジタル I2C インタフェースに比べて立ち上がりおよび立ち下がり時間が長くなることがあります。したがって、アナログ出力で IPS2550 のプログラムを行う場合には I2C クロックレートを調整する必要があります。

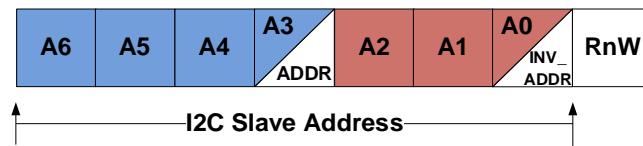

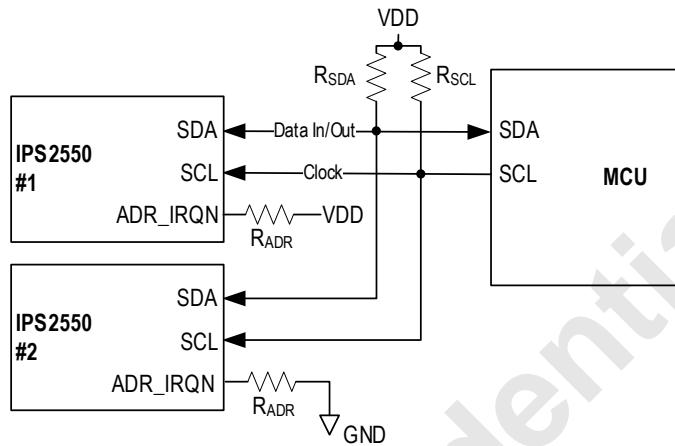

#### 15.3.1 アドレス選択付き I2C (デフォルト)

IPS2550 がアドレス選択付き I2C インタフェースを使用するようにプログラムされている場合、ADR IRQN ピンはハードウェアによって I2C スレーブアドレスを選択するために使用されます。

デフォルトでは ADR IRQN ピンは IPS2550 の I2C スレーブアドレスをハードウェアピン固定によって定義するために用いられます。このピンの状態は 7bit の I2C アドレスの A3 Bit に反映され、状態の反転が I2C アドレスの A0 Bit に反映されます（図 16 を参照してください）。

デフォルトの I2C アドレス設定では A4 は 1 に設定されています。ADR IRQN を GND に固定した場合、IPS2550 のデフォルトスレーブアドレスは 0010001 (Binary) = 0x11 (Hex) に、VDD に接続した場合は I2C アドレスは 0011000 (Binary) = 0x18 (Hex) になります。

ハードウェアピン固定による I2C アドレス選択を無効として NVM アドレスビット A6～A3 で固定の I2C アドレスを定義できます（詳細は『IPS2550 Programming Guide』を参照してください）。

表 21 にそれぞれのアドレス選択オプションでのアドレス選択ピンと NVM アドレス設定の組み合わせを示します。

I2C アドレスビット A3 から A6 は個別の I2C アドレスとして NVM で設定でき、最大 14 デバイスをアドレス指定できます（詳細は当社から入手可能な『IPS2550 Programming Guide』を参照してください）。

表 21 NVM でのアドレス選択オプション

| I2C Address Selection Mode                                    | A6                    | A5 | A4 | A3    | A2 | A1 | A0             |

|---------------------------------------------------------------|-----------------------|----|----|-------|----|----|----------------|

| Default setting                                               | 0                     | 0  | 1  | Pin#1 | 0  | 0  | Pin#1 inverted |

| User programmable range, with I2C address selection by pin #1 | 001 to 110 (binary)   |    |    | Pin#1 | 0  | 0  | Pin#1 inverted |

| User programmable range, with fixed I2C address               | 0001 to 1110 (binary) |    |    |       | 0  | 0  | 0              |

図 16 I2C アドレス選択ビット

図 17 アドレス選択付き I2C インタフェース

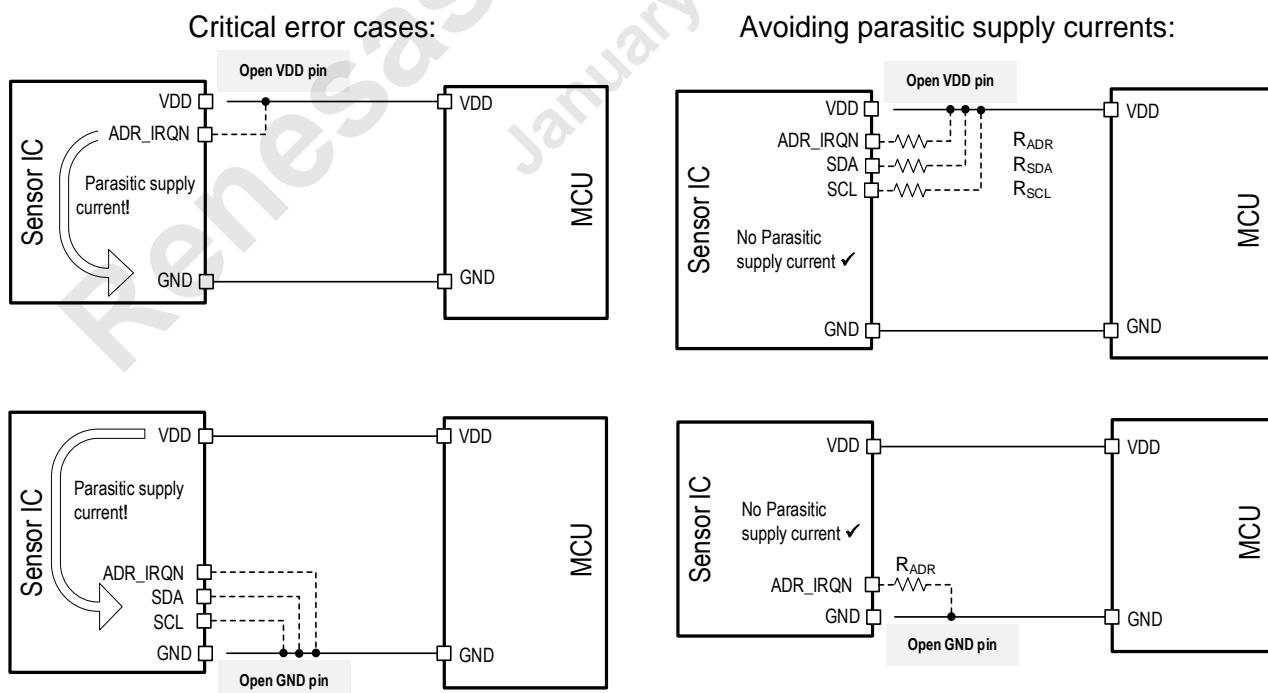

### 15.3.2 GND 喪失または VDD 喪失中の ADR IRQN ピンを介した寄生バスの回避

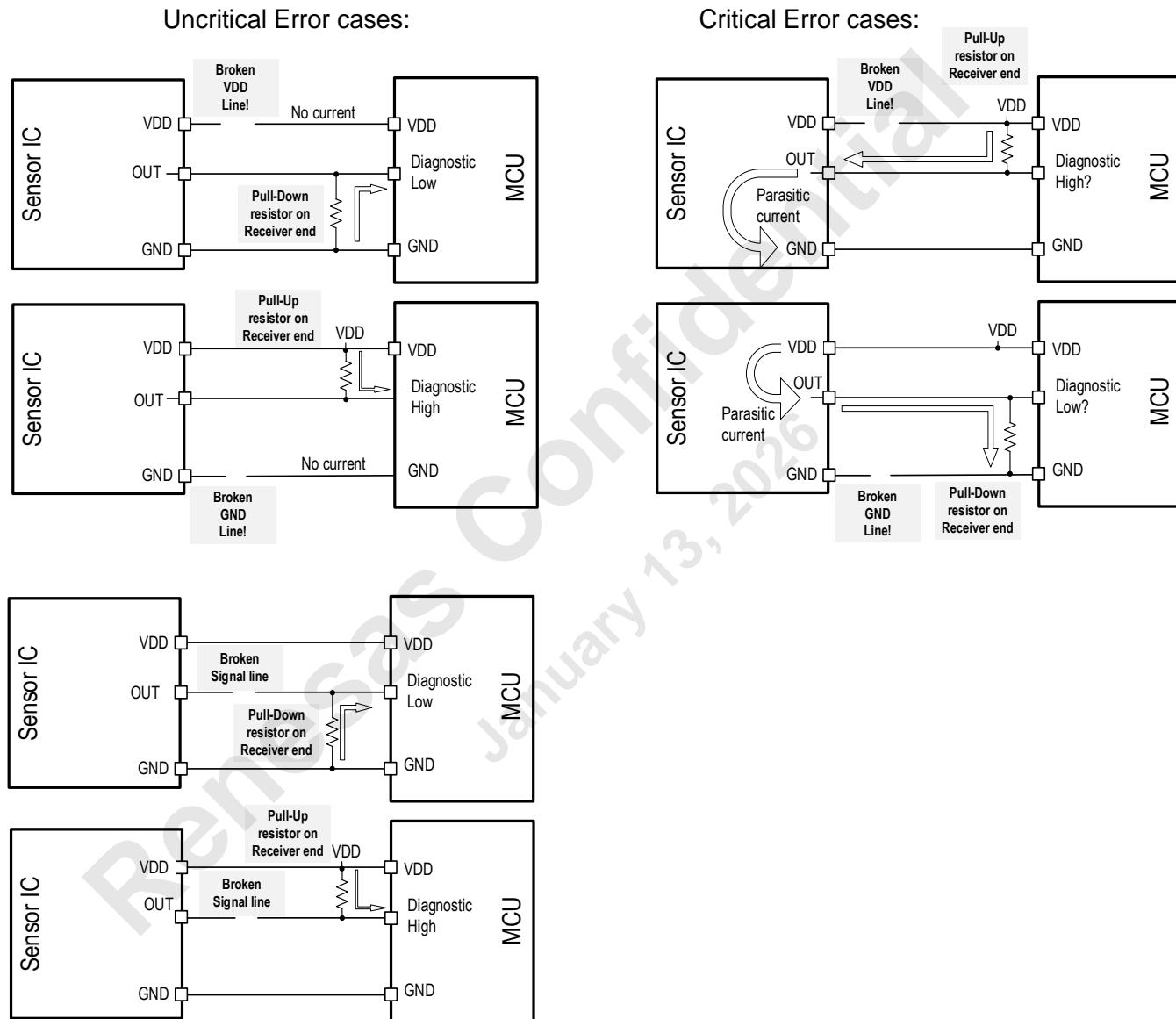

安全上重要なアプリケーションでは、グランドまたはVDDの喪失を監視し、故障が発生した場合に対応する必要があります。リモートアプリケーションでのGNDまたはVDDワイヤの喪失およびそれらの適切な診断構成の場合を図25に示します。

ハードウェアピン固定によってI2Cアドレスを選択するためにADR IRQNピンを使用する場合は、VDDまたはGNDに直接接続しないことを推奨します。チップが不定状態になる可能性のあるGNDまたはVDD配線が断線した場合に、ADR IRQNピン流れる寄生電流を避けるために、R<sub>ADR</sub>を介してVDDまたはGNDに接続して下さい(図18と表14参照)。

図 18 ADR IRQN ピン用いたハードウェアピン固定によるアドレス選択付き I2C インタフェース

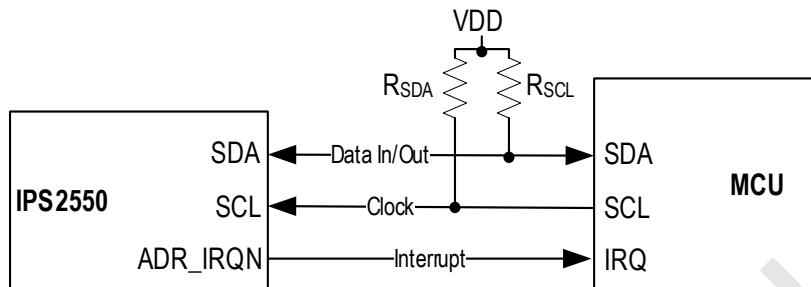

### 15.3.3 割り込み付き I2C インタフェース (プログラミングオプション)

IPS2550は、割込み機能付きのI2Cインターフェースを使用するようにプログラマムされている場合、I2C規格のインターフェースとして動作します。I2Cアドレスはプログラム可能です。また、ADR IRQN端子は、診断イベントの高速信号伝達用の割り込み出力として使用されます。

図 19 1 つのスレーブでの割り込みを使用した I2C インタフェース設定

注: このモードでは、いくつかの I2C スレーブが並列に接続されます。各 I2C スレーブには個別の I2C アドレスが必要です。

図 20 マルチスレーブ割込みによる I2C インタフェースの構成

I2C インタフェースの詳細説明については、『IPS2550 Programming Guide』を参照してください。

## 16. 過電圧保護

### 16.1 入出力保護

出力ピンと電源ピンの両方で過電圧保護と逆極性保護の車載要件を満たすために、IPS2550 にはいくつかの保護と診断機能が含まれています:

1. 出力端子 SIN, SINK, COS, COSN-GND 間または VDD 間の短絡保護

2. 過電圧および逆極性保護:

- a. 電源 VDD を GND 端子に接続

- b. アナログ出力端子 SIN, SINK, COS, COSN が GND に短絡

## 17. プログラムオプション

IPS2550 ファミリには、さまざまなプログラムオプションが用意されています。主なプログラム可能な機能については、表 22 で説明します。

IPS2550 には、次のいずれかの方法でアクセスし、プログラムすることができます:

- I<sub>2</sub>C インタフェースフェイスピン SDA と SCL を使用

- アナログ出力ピン SIN\_SCL と COS\_SDA を介して

注記: プログラミングの詳細については要求に応じて当社から入手可能な『IPS2550 Programming Guide』を参照してください。

SDA および SCL ピンで使用可能な I<sub>2</sub>C インタフェースにより、アナログ出力信号を中断することなく、内部レジスタへのアクセスと、ゲインおよびオフセット設定の動作中の変更を同時に行うことができます。IPS2550 は、I<sub>2</sub>C 規格プロトコルを使用して、このインターフェースを介して同様にプログラムすることもできます。図 21 を参照してください。

なお、SDA、SCL 端子にはプルアップ抵抗は内蔵されていません。このインターフェースを使用する場合は、センサモジュールまたは外部のいずれかに外付けプルアップ抵抗を取り付ける必要があります。

図 21 I<sub>2</sub>C インタフェースを介した IPS2550 のプログラム