# **RENESAS** Low Skew, 1-to-16 Differential-to-LVDS Clock Distribution Chip

# DATASHEET

ICS8516

# **GENERAL DESCRIPTION**

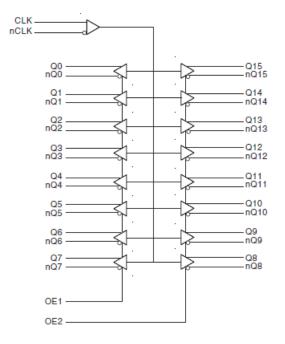

The ICS8516 is a low skew, high performance 1-to-16 Differentialto-LVDS Clock Distribution Chip. The ICS8516 CLK, nCLK pair can accept any differential input levels and translates them to 3.3V LVDS output levels. Utilizing Low Voltage Differential Signaling (LVDS), the ICS8516 provides a low power, low noise, point-to-point solution for distributing clock signals over controlled impedances of  $100\Omega$ .

Dual output enable inputs allow the ICS8516 to be used in a 1-to-16 or 1-to-8 input/output mode.

Guaranteed output and part-to-part skew specifications make the ICS8516 ideal for those applications demanding well defined performance and repeatability.

# **F**EATURES

- Sixteen differential LVDS outputs

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- Maximum output frequency: 700MHz

- Translates any differential input signal (LVPECL, LVHSTL, SSTL, DCM) to LVDS levels without external bias networks

- Translates any single-ended input signal to LVDS with resistor bias on nCLK input

- Multiple output enable inputs for disabling unused outputs in reduced fanout applications

- LVDS compatible

- Output skew: 90ps (maximum)

- Part-to-part skew: 500ps (maximum)

- · Propagation delay: 2.4ns (maximum)

- Additive phase jitter, RMS: 148fs (typical)

- 3.3V operating supply

- 0°C to 70°C ambient operating temperature

- Available in lead-free RoHS compliant package

# **BLOCK DIAGRAM**

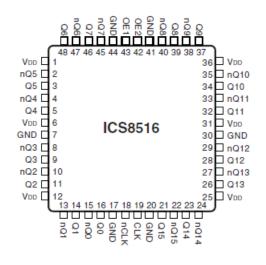

# **PIN ASSIGNMENT**

48-Lead LQFP 7mm x 7mm x 1.4mm body package Y Package Top View

TABLE 1. PIN DESCRIPTIONS

| Number                   | Name            | Туре   |          | Description                                                                                                                           |

|--------------------------|-----------------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6, 12,<br>25, 31, 36  | V <sub>DD</sub> | Power  |          | Positive supply pins.                                                                                                                 |

| 2, 3                     | nQ5, Q5         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 4, 5                     | nQ4, Q4         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 7, 17, 20,<br>30, 41, 44 | GND             | Power  |          | Power supply ground.                                                                                                                  |

| 8, 9                     | nQ3, Q3         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 10, 11                   | nQ2, Q2         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 13, 14                   | nQ1, Q1         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 15, 16                   | nQ0, Q0         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 18                       | nCLK            | Input  | Pullup   | Inverting differential clock input.                                                                                                   |

| 19                       | CLK             | Input  | Pulldown | Non-inverting differential clock input.                                                                                               |

| 21, 22                   | Q15, nQ15       | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 23, 24                   | Q14, nQ14       | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 26, 27                   | Q13, nQ13       | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 28, 29                   | Q12, nQ12       | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 32, 33                   | Q11, nQ11       | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 34, 35                   | Q10, nQ10       | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 37, 38                   | Q9, nQ9         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 39, 40                   | Q8, nQ8         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 42, 43                   | OE2, OE1        | Input  | Pullup   | Output enable. OE2 controls outputs Q8, nQ8 thru Q15, nQ15; OE1 controls outputs Q0, nQ0 thru Q7, nQ7. LVCMOS/LVTTL interface levels. |

| 45, 46                   | nQ7, Q7         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

| 47, 48                   | nQ6, Q6         | Output |          | Differential output pair. LVDS interface levels.                                                                                      |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

## TABLE 2. PIN CHARACTERISTICS

| Symbol                | Parameter                                  | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------|--------------------------------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance                          |                 |         | 4       |         | рF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor                      |                 |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor                    |                 |         | 51      |         | kΩ    |

| C <sub>PD</sub>       | Power Dissipation Capacitance (per output) |                 |         | 4       |         | pF    |

## TABLE 3A. CONTROL INPUT FUNCTION TABLE

| Inputs |     | Outputs |         |        |          |

|--------|-----|---------|---------|--------|----------|

| OE1    | OE2 | Q0:Q7   | nQ0:nQ7 | Q8:Q15 | nQ8:nQ15 |

| 0      | 0   | Hi Z    | Hi Z    | Hi Z   | Hi Z     |

| 1      | 0   | ACTIVE  | ACTIVE  | Hi Z   | Hi Z     |

| 0      | 1   | Hi Z    | Hi Z    | ACTIVE | ACTIVE   |

| 1      | 1   | ACTIVE  | ACTIVE  | ACTIVE | ACTIVE   |

In the active mode, the state of the outputs are a function of the CLK and nCLK inputs as described in Table 3B.

### TABLE 3B. CLOCK INPUT FUNCTION TABLE

| Inp            | uts            | Out    | tputs    | Input to Output Mode         | Polarity      |

|----------------|----------------|--------|----------|------------------------------|---------------|

| CLK            | nCLK           | Q0:Q15 | nQ0:nQ15 |                              | Folanty       |

| 0              | 1              | LOW    | HIGH     | Differential to Differential | Non Inverting |

| 1              | 0              | HIGH   | LOW      | Differential to Differential | Non Inverting |

| 0              | Biased; NOTE 1 | LOW    | HIGH     | Single Ended to Differential | Non Inverting |

| 1              | Biased; NOTE 1 | HIGH   | LOW      | Single Ended to Differential | Non Inverting |

| Biased; NOTE 1 | 0              | HIGH   | LOW      | Single Ended to Differential | Inverting     |

| Biased; NOTE 1 | 1              | LOW    | HIGH     | Single Ended to Differential | Inverting     |

NOTE 1: Please refer to the Application Information section, "Wiring the Differential Input to Accept Single Ended Levels".

### ABSOLUTE MAXIMUM RATINGS

| 4.6V                            |

|---------------------------------|

| -0.5V to V $_{\rm DD}$ + 0.5 V  |

| -0.5V to $V_{\text{DD}}$ + 0.5V |

| 47.9°C/W (0 lfpm)               |

| -65°C to 150°C                  |

|                                 |

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| TABLE 4A. POWER SUPPLY DC CHARACTERISTICS, | , V <sub>DD</sub> = 3.3V±5%, Та = 0°С то 70°С |

|--------------------------------------------|-----------------------------------------------|

|--------------------------------------------|-----------------------------------------------|

| Symbol                                      | Parameter                   | Test Conditions  | Minimum | Typical | Maximum | Units |

|---------------------------------------------|-----------------------------|------------------|---------|---------|---------|-------|

| V <sub>DD</sub>                             | Positive Supply Voltage     |                  | 3.135   | 3.3     | 3.465   | V     |

|                                             | Statia Dowar Supply Surrant | $RL = 100\Omega$ |         | 135     | 165     | mA    |

| I <sub>DD</sub> Static Power Supply Current | No Load                     |                  | 60      | 75      | mA      |       |

TABLE 4B. LVCMOS/LVTTL DC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol          | Parameter          |          | Test Conditions                                      | Minimum | Typical | Maximum               | Units |

|-----------------|--------------------|----------|------------------------------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage | OE1, OE2 |                                                      | 2       |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input Low Voltage  | OE1, OE2 |                                                      | -0.3    |         | 0.8                   | V     |

| I <sub>IH</sub> | Input High Current | OE1, OE2 | $V_{_{DD}} = V_{_{IN}} = 3.465V$                     |         |         | 5                     | μA    |

| I <sub>IL</sub> | Input Low Current  | OE1, OE2 | $V_{_{DD}} = 3.465 \text{V}, V_{_{IN}} = 0 \text{V}$ | -150    |         |                       | μA    |

| Symbol           | Parameter                     |             | Test Conditions                                      | Minimum   | Typical | Maximum                | Units |

|------------------|-------------------------------|-------------|------------------------------------------------------|-----------|---------|------------------------|-------|

|                  | Input High Current            | CLK         | $V_{IN} = V_{DD} = 3.465V$                           |           |         | 150                    | μA    |

| 'н               |                               | nCLK        | $V_{IN} = V_{DD} = 3.465V$                           |           |         | 5                      | μA    |

|                  | Input Low Current             | CLK         | $V_{_{DD}} = 3.465 \text{V}, V_{_{IN}} = 0 \text{V}$ | -5        |         |                        | μA    |

| I'IL             |                               | nCLK        | $V_{DD} = 3.465 V, V_{IN} = 0 V$                     | -150      |         |                        | μA    |

| V <sub>PP</sub>  | Peak-to-Peak Voltag           | je          |                                                      | 0.15      |         | 1.3                    | V     |

| V <sub>CMR</sub> | Common Mode Inpu<br>NOTE 1, 2 | ut Voltage; |                                                      | GND + 0.5 |         | V <sub>DD</sub> - 0.85 | V     |

NOTE 1: For single ended applications, the maximum input voltage for CLK, nCLK is  $V_{DD} + 0.3V$ . NOTE 2: Common mode voltage is defined ast  $V_{IH}$ .

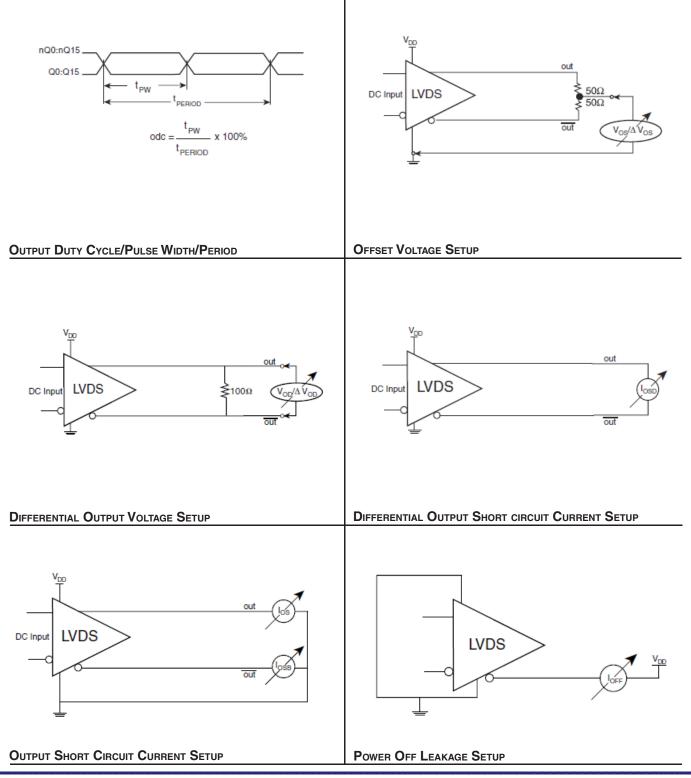

| Symbol                            | Parameter                                 | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------------------|-------------------------------------------|-----------------|---------|---------|---------|-------|

| V <sub>OD</sub>                   | Differential Output Voltage               |                 | 250     | 400     | 600     | mV    |

| $\Delta V_{OD}$                   | V <sub>od</sub> Magnitude Change          |                 |         |         | 50      | mV    |

| V <sub>os</sub>                   | Offset Voltage                            |                 | 1.125   | 1.4     | 1.6     | V     |

| $\Delta V_{OS}$                   | V <sub>os</sub> Magnitude Change          |                 |         |         | 50      | mV    |

| I <sub>oz</sub>                   | High Impedance Leakage Current            |                 | -10     |         | +10     | μA    |

| I <sub>OFF</sub>                  | Power Off Leakage                         |                 | -1      |         | +1      | μA    |

| I <sub>OSD</sub>                  | Differential Output Short Circuit Current |                 |         |         | -5.5    | mA    |

| I <sub>os</sub> /I <sub>osb</sub> | Output Short Circuit Current              |                 |         |         | -12     | mA    |

## Table 4D. LVDS DC Characteristics, $V_{_{DD}}$ = 3.3V±5%, Ta = 0°C to 70°C

### Table 5. AC Characteristics, $V_{DD} = 3.3V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol                              | Parameter                                                                    | Test Conditions                     | Minimum | Typical | Maximum | Units |

|-------------------------------------|------------------------------------------------------------------------------|-------------------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub>                    | Output Frequency                                                             |                                     |         |         | 700     | MHz   |

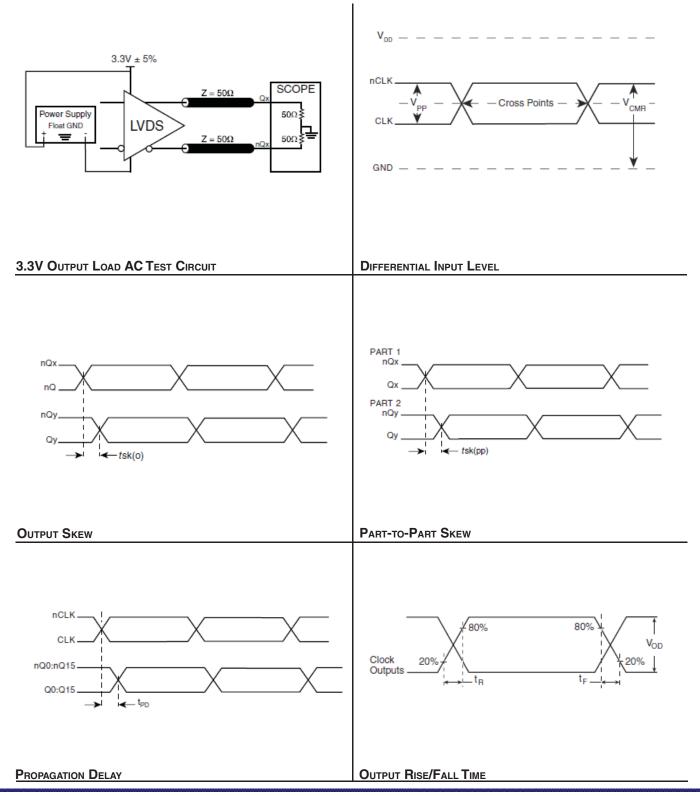

| t <sub>PD</sub>                     | Propagation Delay; NOTE 1                                                    |                                     | 1.6     | 2.0     | 2.4     | ns    |

| <i>t</i> sk(o)                      | Output Skew; NOTE 2, 4                                                       |                                     |         |         | 90      | ps    |

| <i>t</i> sk(pp)                     | Part-to-Part Skew; NOTE 3, 4                                                 |                                     |         |         | 500     | ps    |

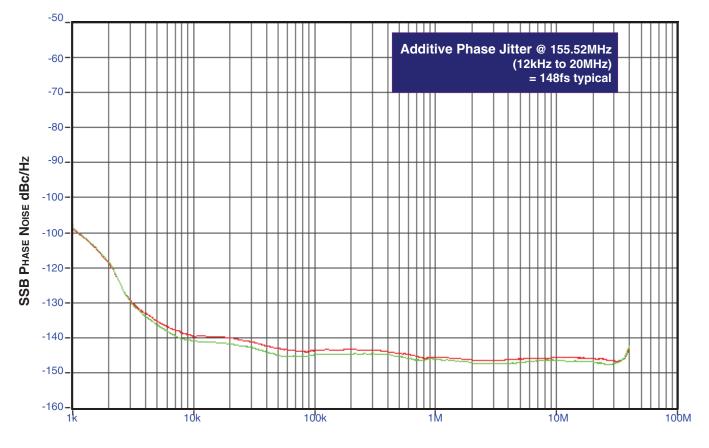

| <i>t</i> jit                        | Buffer Additive Phase Jitter, RMS;<br>refer to Additive Phase Jitter Section | Integration Range:<br>12kHz - 20MHz |         | 148     |         | fs    |

| t <sub>R</sub> /t <sub>F</sub>      | Output Rise/Fall Time                                                        | 20% to 80%                          | 100     |         | 550     | ps    |

| odc                                 | Output Duty Cycle                                                            |                                     | 45      | 50      | 55      | %     |

| $t_{_{PZL}}, t_{_{PZH}}$            | Output Enable Time; NOTE 5                                                   |                                     |         |         | 5       | ns    |

| t <sub>PLZ</sub> , t <sub>PHZ</sub> | Output Disable Time; NOTE 5                                                  |                                     |         |         | 5       | ns    |

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: Defined as skew between outputs at the same supply voltages and with equal load conditions. Measured at the output differential cross points.

NOTE 3: Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

NOTE 4: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 5: These parameters are guaranteed by characterization. Not tested in production.

# Additive Phase Jitter

The spectral purity in a band at a specific offset from the fundamental compared to the power of the fundamental is called the *dBc Phase Noise*. This value is normally expressed using a Phase noise plot and is most often the specified plot in many applications. Phase noise is defined as the ratio of the noise power present in a 1Hz band at a specified offset from the fundamental frequency to the power value of the fundamental. This ratio is expressed in decibels (dBm) or a ratio of the power in

the 1Hz band to the power in the fundamental. When the required offset is specified, the phase noise is called a *dBc* value, which simply means dBm at a specified offset from the fundamental. By investigating jitter in the frequency domain, we get a better understanding of its effects on the desired application over the entire time record of the signal. It is mathematically possible to calculate an expected bit error rate given a phase noise plot.

**OFFSET FROM CARRIER FREQUENCY (Hz)**

As with most timing specifications, phase noise measurements have issues. The primary issue relates to the limitations of the equipment. Often the noise floor of the equipment is higher than the noise floor of the device. This is illustrated above. The device meets the noise floor of what is shown, but can actually be lower. The phase noise is dependant on the input source and measurement equipment.

# **PARAMETER MEASUREMENT INFORMATION**

# **APPLICATION** INFORMATION

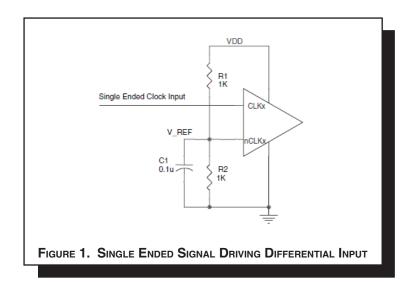

### WIRING THE DIFFERENTIAL INPUT TO ACCEPT SINGLE ENDED LEVELS

*Figure 1* shows how the differential input can be wired to accept single ended levels. The reference voltage V\_REF =  $V_{DD}/2$  is generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio

of R1 and R2 might need to be adjusted to position the V\_REF in the center of the input voltage swing. For example, if the input clock swing is only 2.5V and  $V_{DD}$ = 3.3V, V\_REF should be 1.25V and R2/R1 = 0.609.

### **RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS**

### **INPUTS:**

#### LVCMOS CONTROL PINS:

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

#### **OUTPUTS:**

#### LVDS – Like OUTPUT

All unused LVDS output pairs can be either left floating or terminated with  $100\Omega$  across. If they are left floating, we recommend that there is no trace attached.

# RENESAS

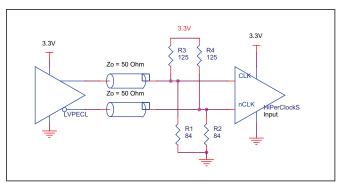

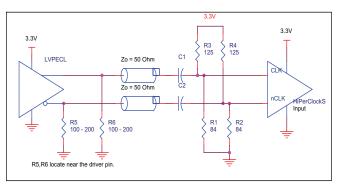

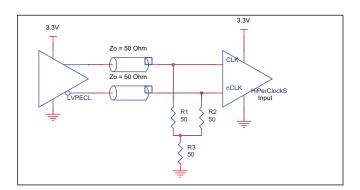

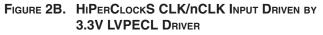

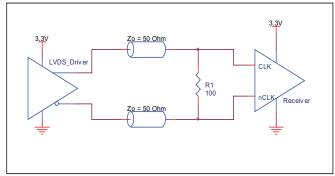

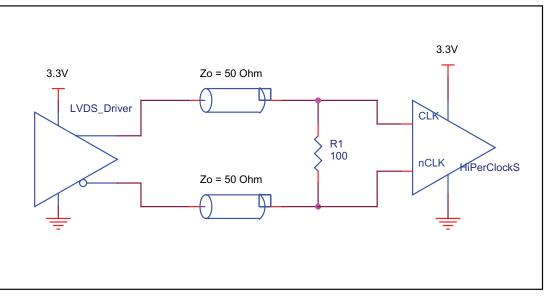

## DIFFERENTIAL CLOCK INPUT INTERFACE

The CLK /nCLK accepts LVDS, LVPECL, LVHSTL, SSTL, HCSL and other differential signals. Both VSWING and VOH must meet the VPP and VCMR input requirements. Figures 2A to 2E show interface examples for the HiPerClockS CLK/nCLK input driven by the most common driver types. The input interfaces suggested

3.3V 1.8\ Zo = 50 Ohm CLK Δ Zo = 50 Ohm nCLK TiPerClockS Ф VHSTI Input R1 50 R2 50 HiPerClockS LVHSTL Driver

FIGURE 2A. HIPERCLOCKS CLK/nCLK INPUT DRIVEN BY ICS HIPERCLOCKS LVHSTL DRIVER

FIGURE 2C. HIPERCLOCKS CLK/nCLK INPUT DRIVEN BY 3.3V LVPECL DRIVER

FIGURE 2E. HIPERCLOCKS CLK/NCLK INPUT DRIVEN BY 3.3V LVPECL DRIVER WITH AC COUPLE

DIFFERENTIAL-TO-LVDS CLOCK DISTRIBUTION CHIP

FIGURE 2D. HIPERCLOCKS CLK/nCLK INPUT DRIVEN BY 3.3V LVDS DRIVER

## LVDS DRIVER TERMINATION

A general LVDS interface is shown in *Figure 3*. In a  $100\Omega$  differential transmission line environment, LVDS drivers require a matched load termination of  $100\Omega$  across near the receiver

input. For a multiple LVDS outputs buffer, if only partial outputs are used, it is recommended to terminate the un-used outputs.

FIGURE 3. TYPICAL LVDS DRIVER TERMINATION

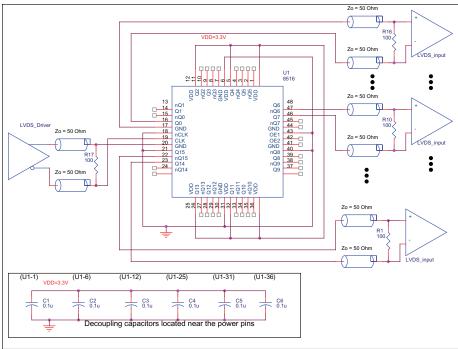

### SCHEMATIC EXAMPLE

Figure 4 shows a schematic example of ICS8516. In this example, the input is driven by an LVDS driver. For LVDS buffer, it is recommended to terminate the unused outputs for better

signal integrity. The decoupling capacitors should be physically located near the power pin.

FIGURE 4. ICS8516 LVDS BUFFER SCHEMATIC EXAMPLE

# **R**ELIABILITY INFORMATION

# Table 6. $\boldsymbol{\theta}_{JA} \text{vs.}$ Air Flow Table for 48 Lead LQFP

| θ <sub>JA</sub> by Velocity (Linear Feet per Minute)                                                                                                    |                                                         |                                                  |                                                         |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------|--|

| Single-Layer PCB, JEDEC Standard Test Boards<br>Multi-Layer PCB, JEDEC Standard Test Boards<br><b>NOTE:</b> Most modern PCB designs use multi-layered b | <b>0</b><br>67.8°C/W<br>47.9°C/W<br>boards. The data in | 200<br>55.9°C/W<br>42.1°C/W<br>the second row pe | 500<br>50.1°C/W<br>39.4°C/W<br>ertains to most designs. |  |

### TRANSISTOR COUNT

The transistor count for ICS8516 is: 1821

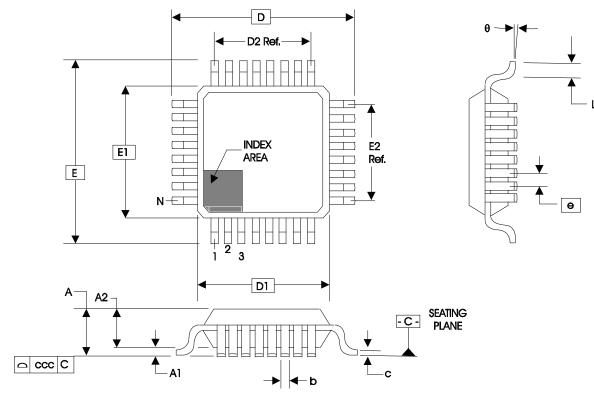

PACKAGE OUTLINE - Y SUFFIX FOR 48 LEAD LQFP

TABLE 7. PACKAGE DIMENSIONS

| JEDEC VARIATION<br>ALL DIMENSIONS IN MILLIMETERS |            |         |            |  |

|--------------------------------------------------|------------|---------|------------|--|

| SYMBOL                                           | BBC        |         |            |  |

|                                                  | MINIMUM    | NOMINAL | MAXIMUM    |  |

| N                                                | 48         |         |            |  |

| A                                                |            |         | 1.60       |  |

| A1                                               | 0.05       |         | 0.15       |  |

| A2                                               | 1.35       | 1.40    | 1.45       |  |

| b                                                | 0.17       | 0.22    | 0.27       |  |

| с                                                | 0.09       |         | 0.20       |  |

| D                                                | 9.00 BASIC |         |            |  |

| D1                                               | 7.00 BASIC |         |            |  |

| D2                                               | 5.50 Ref.  |         |            |  |

| E                                                | 9.00 BASIC |         |            |  |

| E1                                               | 7.00 BASIC |         |            |  |

| E2                                               | 5.50 Ref.  |         |            |  |

| е                                                | 0.50 BASIC |         |            |  |

| L                                                | 0.45       | 0.60    | 0.75       |  |

| θ                                                | 0°         |         | <b>7</b> ° |  |

| ccc                                              |            |         | 0.08       |  |

Reference Document: JEDEC Publication 95, MS-026

## TABLE 8. ORDERING INFORMATION

| Part/Order Number | Marking     | Package                  | Shipping Packaging | Temperature |

|-------------------|-------------|--------------------------|--------------------|-------------|

| ICS8516FYLF       | ICS8516FYLF | 48 Lead "Lead-Free" LQFP | tray               | 0°C to 70°C |

| ICS8516FYLFT      | ICS8516FYLF | 48 Lead "Lead-Free" LQFP | tape & reel        | 0°C to 70°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

|     | REVISION HISTORY SHEET |      |                                                                                   |         |  |

|-----|------------------------|------|-----------------------------------------------------------------------------------|---------|--|

| Rev | Table                  | Page | Description of Change                                                             | Date    |  |

| Α   | T1                     | 2    | Pin Description table - added pins 47 thru 48.                                    | 3/31/03 |  |

|     |                        | 8    | Added LVDS Driver Termination in the Application Information section.             | 3/31/03 |  |

| Α   | T1                     | 2    | Pin Description Table - switched pin names for 45, 46 & 47,48                     | 5/6/03  |  |

|     | T2                     | 3    | Pin Characteristics Table - changed C <sub>IN</sub> from 4pF max. to 4pF typical. |         |  |

| A   |                        | 9    | Updated Differential Clock Input Interface section.                               | 7/30/04 |  |

|     | T8                     | 12   | Ordering Information Table - added Lead-Free part numbers.                        |         |  |

|     |                        | 1    | Feature Section - added Additive Phase Jitter bullet.                             |         |  |

| в   | T5                     | 5    | AC Characteristics Table - added Additive Phase Jitter.                           | 2/21/06 |  |

|     |                        | 6    | Added Additive Phase Jitter section.                                              | 2/21/00 |  |

|     |                        | 9    | Added Recommendations for Unused Input and Output Pins                            |         |  |

|     |                        | 1    | Features Section - removed reference to leaded devices.                           |         |  |

| В   | T8                     | 17   | Ordering Information - removed leaded devices.                                    | 6/12/15 |  |

|     |                        |      | Updated data sheet format.                                                        |         |  |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.