### **Description**

The 6V49R904-167 is a programmable clock generator with fixed ROM code intended for high-performance automotive applications.

There are four internal PLLs, each individually programmed, allowing for four unique non-integer-related frequencies. The frequencies are generated from a single reference clock.

### **Typical Applications**

Automotive applications

#### **Features**

- Factory programmed with "6V49R904-167" programming code

- Nine programmable outputs

- Four internal PLLs

- Two of the PLLs support spread spectrum generation capability

- Four independently controlled V<sub>DDO</sub> (1.8V–3.3V)

- I/O Standards:

- Outputs: 3.3V LVTTL / LVCMOS

- Inputs: 3.3V LVTTL / LVCMOS

- Redundant clock inputs with auto and manual switchover options

- Individual output enable/disable

- Power-down mode

- 3.3V core V<sub>DD</sub>

- 5 × 5 mm 32-VFQFPN package

- -40° to +85°C industrial temperature operation

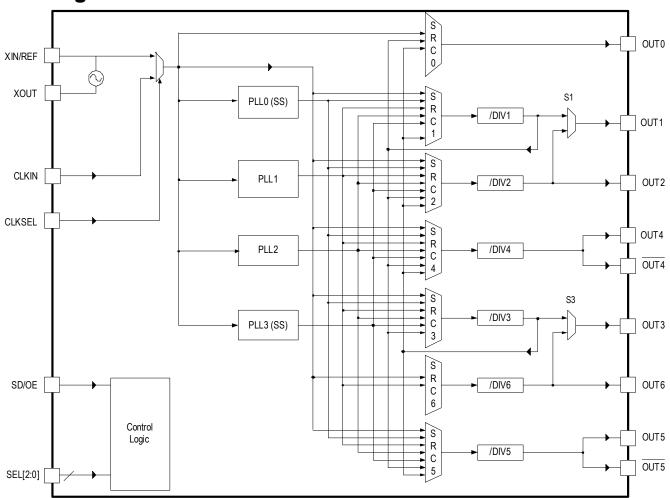

### **Block Diagram**

### **Contents**

| Description                                       | . 1 |

|---------------------------------------------------|-----|

| Typical Applications                              | . 1 |

| Features                                          | . 1 |

| Block Diagram                                     | . 1 |

| Pin Assignments                                   | . 3 |

| Pin Descriptions                                  |     |

| Output Selection                                  |     |

| Mask ROM                                          |     |

| Absolute Maximum Ratings                          |     |

| Thermal Characteristics                           | . 6 |

| Recommended Operating Conditions                  | . 6 |

| Capacitance                                       | . 7 |

| DC Electrical Characteristics                     | . 7 |

| Power Supply Characteristics for PLLs and Outputs | . 8 |

| AC Electrical Characteristics                     |     |

| Test Circuits and Conditions                      |     |

| Package Outline Drawings                          |     |

| Marking Diagram                                   |     |

| Ordering Information                              |     |

| Revision History                                  |     |

|                                                   |     |

### **Pin Assignments**

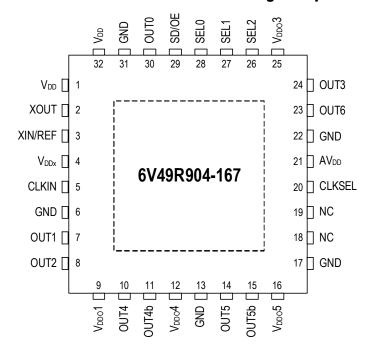

Figure 1. Pin Assignments for 5 x 5 × 0.90 mm 32-VFQFPN Package – Top View

## **Pin Descriptions**

**Table 1. Pin Descriptions**

| Number | Name               | I/O | Туре                    | Description                                                                                                                 |

|--------|--------------------|-----|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1      | $V_{DD}$           |     | Power                   | Device power supply. Connect to 3.3V.                                                                                       |

| 2      | XOUT               | 0   | LVTTL                   | CRYSTAL_OUT – reference crystal feedback.                                                                                   |

| 3      | XIN/REF            | I   | LVTTL                   | CRYSTAL_IN – reference crystal input or external reference clock input.                                                     |

| 4      | V <sub>DDx</sub>   |     | Power                   | Crystal oscillator power supply. Connect to 3.3V through $5\Omega$ resistor. Use filtered analog power supply if available. |

| 5      | CLKIN              | I   | LVTTL                   | Input clock. Weak internal pull-down resistor.                                                                              |

| 6      | GND                |     | Power                   | Connect to ground.                                                                                                          |

| 7      | OUT1               | 0   | Adjustable              | Configurable clock output 1. Output levels controlled by V <sub>DDO</sub> 1.                                                |

| 8      | OUT2               | 0   | Adjustable              | Configurable clock output 2. Output levels controlled by V <sub>DDO</sub> 1.                                                |

| 9      | V <sub>DDO</sub> 1 |     | Power                   | Device power supply. Connect to 1.8V to 3.3V. Sets output voltage levels for OUT1 and OUT2.                                 |

| 10     | OUT4               | 0   | Adjustable <sup>1</sup> | Configurable clock output 4. Output levels controlled by V <sub>DDO</sub> 4.                                                |

| 11     | OUT4b              | 0   | Adjustable <sup>1</sup> | Configurable clock output 4b. Output levels controlled by V <sub>DDO</sub> 4.                                               |

| 12     | V <sub>DDO</sub> 4 |     | Power                   | Device power supply. Connect to 1.8V to 3.3V. Sets output voltage levels for OUT4 and OUT4b.                                |

| 13     | GND                |     | Power                   | Connect to ground.                                                                                                          |

| 14     | OUT5               | 0   | Adjustable <sup>1</sup> | Configurable clock output 5. Output levels controlled by V <sub>DDO</sub> 5.                                                |

| 15     | OUT5b              | 0   | Adjustable <sup>1</sup> | Configurable clock output 5b. Output levels controlled by V <sub>DDO</sub> 5.                                               |

| 16     | V <sub>DDO</sub> 5 |     | Power                   | Device power supply. Connect to 1.8V to 3.3V. Sets output voltage levels for OUT5 and OUT5b.                                |

Table 1. Pin Descriptions (Cont.)

| Number | Name               | I/O | Туре       | Description                                                                                                         |

|--------|--------------------|-----|------------|---------------------------------------------------------------------------------------------------------------------|

| 17     | GND                |     | Power      | Connect to ground.                                                                                                  |

| 18     | NC                 |     | _          | No connect.                                                                                                         |

| 19     | NC                 |     | _          | No connect.                                                                                                         |

| 20     | CLKSEL             | I   | LVTTL      | Input clock selector. Weak internal pull-down resistor.                                                             |

| 21     | $AV_{DD}$          |     | Power      | Device analog power supply. Connect to 3.3V. Use filtered analog power supply if available.                         |

| 22     | GND                |     | Power      | Connect to ground.                                                                                                  |

| 23     | OUT6               | 0   | Adjustable | Configurable clock output 6. Output levels controlled by V <sub>DDO</sub> 3.                                        |

| 24     | OUT3               | 0   | Adjustable | Configurable clock output 3. Output levels controlled by V <sub>DDO</sub> 3.                                        |

| 25     | V <sub>DDO</sub> 3 |     | Power      | Device power supply. Connect to 1.8V to 3.3V. Sets output voltage levels for OUT3 and OUT6.                         |

| 26     | SEL2               | I   | LVTTL      | Configuration select pin. Weak internal pull-down resistor.                                                         |

| 27     | SEL1               | I   | LVTTL      | Configuration select pin. Weak internal pull-down resistor.                                                         |

| 28     | SEL0               | I   | LVTTL      | Configuration select pin. Weak internal pull-down resistor.                                                         |

| 29     | SD/OE              | I   | LVTTL      | Enables/disables the outputs or powers down the chip. See Output Selection table. Weak internal pull-down resistor. |

| 30     | OUT0               | 0   | LVTTL      | Configurable clock output 0. 3.3V LVTTL levels.                                                                     |

| 31     | GND                |     | Power      | Connect to ground.                                                                                                  |

| 32     | $V_{DD}$           |     | Power      | Device power supply. Connect to 3.3V.                                                                               |

|        | EPAD               |     | Power      | Connect to ground.                                                                                                  |

<sup>&</sup>lt;sup>1</sup> When only an individual single-ended clock output is required, tie OUTx and OUTxb together.

$<sup>^{2}\,\</sup>mathrm{Analog}$  power plane should be isolated from a 3.3V power plane through a ferrite bead.

$<sup>^3</sup>$  Each power pin should have a dedicated 0.01 $\mu$ F de-coupling capacitor. Digital  $V_{DD}$ s may be tied together.

<sup>&</sup>lt;sup>4</sup> Unused clock inputs (REFIN or CLKIN) must be pulled high or low – they cannot be left floating. If the crystal oscillator is not used, XOUT must be left floating.

# **Output Selection**

#### **Table 2. Output Selection**

| SD/ | SEL C                | onfig S           | etting | laat          | Input              | OUT0       | OUT1               | OUT2       | OUT3       | OUT4       | OUT4b      | OUT5       | OUT5b      | OUT6  | Spread           | Modulation |

|-----|----------------------|-------------------|--------|---------------|--------------------|------------|--------------------|------------|------------|------------|------------|------------|------------|-------|------------------|------------|

| OE  | 2                    | 1                 | 0      | Input         | Frequency<br>(MHz) | (MHz)      | (MHz)              | (MHz)      | (MHz)      | (MHz)      | (MHz)      | (MHz)      | (MHz)      | (MHz) | · %              | Frequency  |

| 0   | 0                    | 0                 | 0      | Crystal<br>XO | 37.007             | OFF        | OFF                | 37.007000  | OFF        | OFF        | OFF        | OFF        | OFF        | OFF   | Center<br>±2.0%  | 36.28kHz   |

| 0   | 0                    | 0                 | 1      | Crystal<br>XO | 37.007             | OFF        | OFF                | 37.007000  | OFF        | OFF        | OFF        | OFF        | OFF        | OFF   | Center<br>±1.5%  | 36.28kHz   |

| 0   | 0                    | 1                 | 0      | Crystal<br>XO | 37.007             | OFF        | OFF                | 37.007000  | OFF        | OFF        | OFF        | OFF        | OFF        | OFF   | Center<br>±1.0%  | 36.28kHz   |

| 0   | 0                    | 1                 | 1      | Crystal<br>XO | 37.007             | OFF        | OFF                | 37.007000  | OFF        | OFF        | OFF        | OFF        | OFF        | OFF   | Center<br>±0.5%  | 36.28kHz   |

| 0   | 1                    | 0                 | 0      | Crystal<br>XO | 37.007             | OFF        | OFF                | 37.007000  | OFF        | OFF        | OFF        | OFF        | OFF        | OFF   | Center<br>±0.25% | 36.28kHz   |

| 0   | 1                    | 0                 | 1      | Xtal/<br>XO   | 37.007             | OFF        | OFF                | 37.007000  | OFF        | OFF        | OFF        | OFF        | OFF        | OFF   | _                | _          |

| 1   | (                    | 000–10            | 1      |               | 37.007             | OFF        | OFF                | OFF        | OFF        | OFF        | OFF        | OFF        | OFF        | OFF   | _                | _          |

| Χ   | X 110–111            |                   |        |               |                    |            |                    | N/A        |            |            |            |            |            |       |                  |            |

|     | Drive                | er Type           |        | N/A           | N/A                | LVTTL      | LVTTL              | LVTTL      | LVTTL      | LVTTL      | LVTTL      | LVTTL      | LVTTL      | LVTTL | _                | _          |

|     | V <sub>DE</sub>      | <sub>00</sub> (V) |        | N/A           | N/A                | 3.3        | 3.3                | 3.3        | 3.3        | 3.3        | 3.3        | 3.3        | 3.3        | 3.3   | _                | _          |

|     | V <sub>DDO</sub> Pin |                   | N/A    | N/A           | $V_{\mathrm{DD}}$  | $V_{DDO}1$ | V <sub>DDO</sub> 1 | $V_{DDO}3$ | $V_{DDO}4$ | $V_{DDO}4$ | $V_{DDO}5$ | $V_{DDO}5$ | $V_{DDO}3$ | _     | _                |            |

#### **Mask ROM**

On power-up of the 6V49R904-167, an automatic restore is performed to load the Mask ROM contents into the internal programming registers. The 6V49R904-167 configurations can be selected by hardware select pins SEL[2:0].

### **Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the 6V49R904-167 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Table 3. Absolute Maximum Ratings**

| Symbol           | Parameter                                        | Minimum | Maximum               | Unit |

|------------------|--------------------------------------------------|---------|-----------------------|------|

| V <sub>DD</sub>  | Internal Power Supply Voltage                    | -0.5    | +4.6                  | V    |

| V <sub>I</sub>   | Input Voltage <sup>1</sup>                       | -0.5    | +4.6                  | V    |

| V <sub>O</sub>   | Output Voltage (not to exceed 4.6V) <sup>1</sup> | -0.5    | V <sub>DD</sub> + 0.5 | V    |

| T <sub>J</sub>   | Junction Temperature                             |         | 150                   | °C   |

| T <sub>STG</sub> | Storage Temperature                              | -65     | 150                   | °C   |

<sup>&</sup>lt;sup>1</sup> Input negative and output voltage ratings may be exceeded if the input and output current ratings are observed.

#### **Thermal Characteristics**

**Table 4. Thermal Characteristics**

| Symbol        | Parameter                              | Conditions      | Value | Unit |

|---------------|----------------------------------------|-----------------|-------|------|

| $\theta_{JA}$ |                                        | Still air.      | 34    | °C/W |

| $\theta_{JA}$ | Thermal Resistance Junction to Ambient | 1 m/s air flow. | 29    | °C/W |

| $\theta_{JA}$ |                                        | 3 m/s air flow. | 27    | °C/W |

| $\theta_{JC}$ | Thermal Resistance Junction to Case    |                 | 32    | °C/W |

## **Recommended Operating Conditions**

**Table 5. Recommended Operating Conditions**

| Symbol                | Parameter                                                                                                        |       | Typical | Maximum | Unit |

|-----------------------|------------------------------------------------------------------------------------------------------------------|-------|---------|---------|------|

| V <sub>DD</sub>       | Power Supply Voltage for V <sub>DD</sub> pins supporting core and outputs                                        | 3.135 | 3.3     | 3.465   | V    |

| $V_{DDX}$             | Power Supply Voltage for Crystal Oscillator. Use filtered analog power supply if available.                      | 3.135 | 3.3     | 3.465   | V    |

| AV <sub>DD</sub>      | Analog Power Supply Voltage. Use filtered analog power supply if available.                                      | 3.135 | 3.3     | 3.465   | V    |

| V <sub>DDOX</sub>     | V <sub>DDO</sub> Range                                                                                           | 3.0   | 3.3     | 3.465   | V    |

| T <sub>A</sub>        | Operating Temperature, Ambient                                                                                   | -40   |         | +85     | °C   |

| C <sub>LOAD_OUT</sub> | Maximum Load Capacitance (3.3V LVTTL only)                                                                       |       |         | 15      | pF   |

| F                     | External Reference Crystal                                                                                       |       | 37.007  |         | MHz  |

| F <sub>IN</sub>       | External Reference Clock CLKIN                                                                                   |       | 37.007  |         | MHz  |

| t <sub>PU</sub>       | Power-up Time for all $\ensuremath{V_{DD}} s$ to reach minimum specified voltage (power ramps must be monotonic) | 0.05  |         | 5       | ms   |

February 7, 2023

# **Capacitance**

#### Table 6. Capacitance

$T_A = 25$ °C

| Symbol               | Parameter                                          | Minimum | Typical | Maximum | Unit |

|----------------------|----------------------------------------------------|---------|---------|---------|------|

| C <sub>IN</sub>      | Input Capacitance (CLKIN, CLKSEL, SD/OE, SEL[2:0]) |         | 3       | 7       | pF   |

| Pull-down Resistor   | Pull-down Resistor CLKIN, CLKSEL, SD/OE, SEL[2:0]  |         | 180     |         | kΩ   |

|                      | Crystal Specifications                             |         |         |         |      |

| XTAL_FREQ            | Crystal Frequency                                  |         | 37.007  |         | MHz  |

| XTAL_MIN             | Minimum Crystal Load Capacitance                   | 3.5     |         |         | pF   |

| XTAL_MAX             | Maximum Crystal Load Capacitance                   |         |         | 35.5    | pF   |

| XTAL_V <sub>PP</sub> | Voltage Swing (peak-to-peak, nominal)              | 1.5     | 2.3     | 3.2     | V    |

#### **DC Electrical Characteristics**

#### Table 7. DC Electrical Characteristics for 3.3V LVTTL <sup>1</sup>

| Symbol            | Parameter              | Conditions                                                  | Minimum | Typical | Maximum  | Unit |

|-------------------|------------------------|-------------------------------------------------------------|---------|---------|----------|------|

| V <sub>OH</sub>   | Output HIGH Voltage    |                                                             | 2.4     |         | $V_{DD}$ | V    |

| V <sub>OL</sub>   | Output LOW Voltage     |                                                             |         |         | 0.4      | V    |

| $V_{IH}$          | Input HIGH Voltage     |                                                             | 2       |         |          | V    |

| $V_{IL}$          | Input LOW Voltage      |                                                             |         |         | 0.8      | V    |

| I <sub>OZDD</sub> | Output Leakage Current | 3-state outputs. $V_O = V_{DD}$ or GND, $V_{DD} = 3.465V$ . |         |         | 10       | μA   |

<sup>&</sup>lt;sup>1</sup> See Recommended Operating Conditions table.

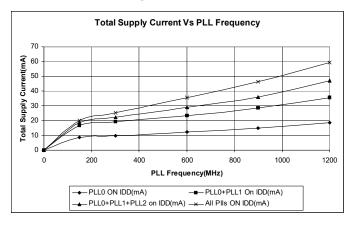

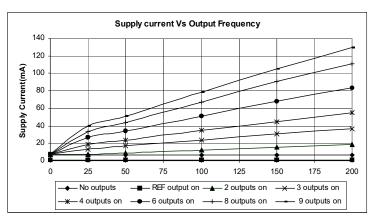

## **Power Supply Characteristics for PLLs and Outputs**

#### **AC Electrical Characteristics**

#### **Table 8. AC Timing Electrical Characteristics**

(Spread spectrum generation = Off)

| Symbol                       | Parameter                 | Conditions                                                                                            | Minimum | Typical | Maximum | Unit |

|------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| <b>£</b> 1                   | Innut Fraguency           | Input frequency limit (CLKIN).                                                                        |         | 37.007  |         | MHz  |

| f <sub>IN</sub> <sup>1</sup> | Input Frequency           | Input frequency limit (XIN/REF).                                                                      |         | 37.007  |         | MHz  |

| t2                           | Input Duty Cycle          | Duty cycle for input.                                                                                 | 40      |         | 60      | %    |

| 10                           | Outrot Duty Ovala         | Measured at V <sub>DD</sub> /2, all outputs except reference output.                                  | 45      |         | 55      | %    |

| t3                           | Output Duty Cycle         | Measured at V <sub>DD</sub> /2, reference output.                                                     | 40      |         | 60      | %    |

| t4 <sup>2</sup>              | Slew Rate, SLEW[1:0] = 00 | Single-ended 3.3V LVCMOS output clock rise and fall time, 20% to 80% of $V_{DD}$ (output load = 5pF). |         | 2.5     |         | V/ns |

| t5                           | Clock Jitter              | Peak-to-peak period jitter, 1PLL, multiple output frequencies switching.                              |         | 80      | 100     | ps   |

| ເວ                           |                           | Peak-to-peak period jitter, LVCMOS, 3.3V ±5%, -40°C to +85°C.                                         |         | 40      | 300     |      |

| t6                           | Output Skew               | Skew between output to output on the same bank.                                                       |         |         | 75      | ps   |

| t7                           | Lock Time                 | PLL lock time from power-up.                                                                          |         | 10      | 20      | ms   |

| t8 <sup>3</sup>              | Lock Time                 | PLL lock time from shutdown mode.                                                                     |         |         | 2       | ms   |

| t <sub>R</sub>               | Rise Time                 | Single-ended 3.3V LVTTL rise time, 20% to 80%.                                                        |         | 825     |         | ps   |

| t <sub>F</sub>               | Fall Time                 | Single-ended 3.3V LVTTL fall time, 80% to 20%.                                                        |         | 825     |         | ps   |

<sup>&</sup>lt;sup>1</sup> Practical lower frequency is determined by loop filter settings.

<sup>&</sup>lt;sup>2</sup> A slew rate of 2.75V/ns or greater should be selected for output frequencies of 100MHz or higher.

<sup>&</sup>lt;sup>3</sup> Actual PLL lock time depends on the loop configuration.

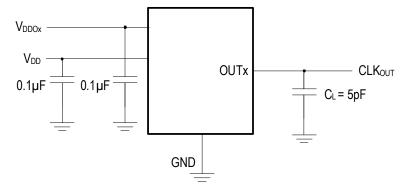

#### **Test Circuits and Conditions**

Figure 2. Test Circuits for DC Outputs

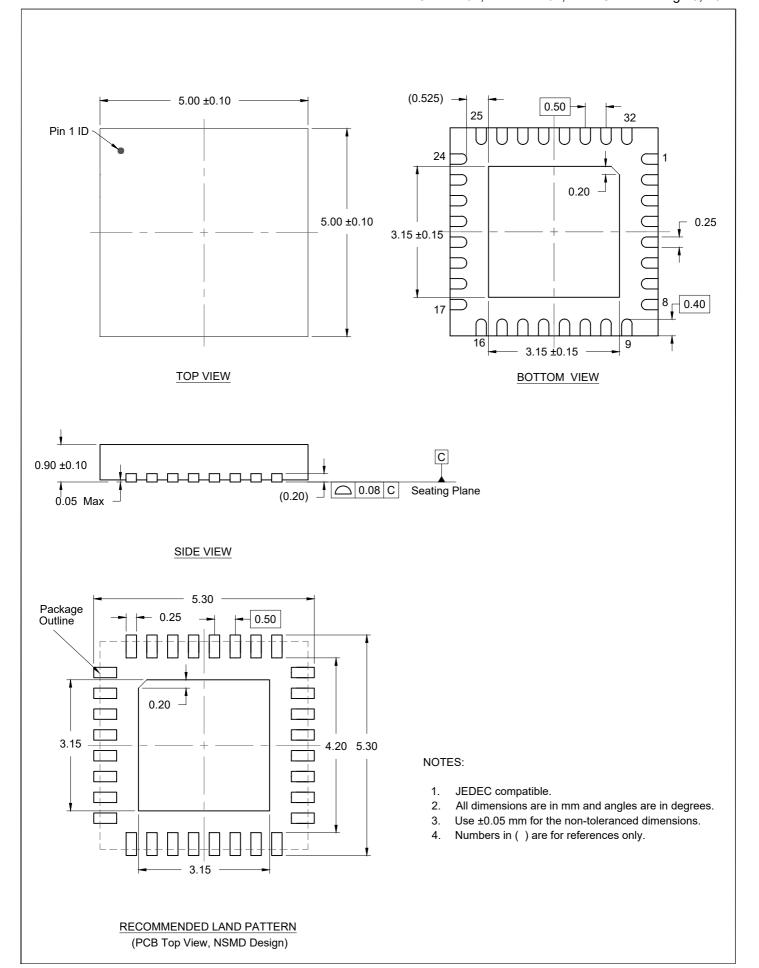

### **Package Outline Drawings**

The package outline drawings are located at the end of this document and are accessible from the Renesas website (see Ordering Information for POD links). The package information is the most current data available and is subject to change without revision of this document.

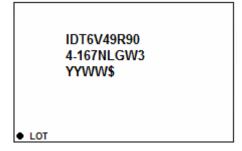

### **Marking Diagram**

- Lines 1 and 2 indicate the part number.

- Line 3 indicates the following:

- "YY" is the last two digits of the year; "WW" is the work week number when the part was assembled.

- "\$" denotes the mark code.

- "LOT" denotes the lot number.

### **Ordering Information**

|   | Orderable Part Number | Package                                   | Carrier Type  | Temperature Range |

|---|-----------------------|-------------------------------------------|---------------|-------------------|

| ſ | 6V49R904-167NLGW3     | 5.0 × 5.0 × 0.9 mm, 0.5mm pitch 32-VFQFPN | Tray          | -40° to +85°C     |

| Ī | 6V49R904-167NLGW38    | 5.0 × 5.0 × 0.9 mm, 0.5mm pitch 32-VFQFPN | Tape and Reel | -40° to +85°C     |

# **Revision History**

| Date              | Description                                                    |

|-------------------|----------------------------------------------------------------|

| February 7, 2023  | Updated POD links and disclaimer.                              |

| November 12, 2021 | Updated Marking Diagram and Package Outline Drawings sections. |

| October 4, 2021   | Replaced disclaimer with Renesas.                              |

| November 9, 2018  | Initial release.                                               |

Package Code:NLG32P1 32-VFQFPN 5.0 x 5.0 x 0.9 mm Body, 0.5mm Pitch PSC-4171-01, Revision: 04, Date Created: Aug 15, 2022

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.