# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# H8/300L SLP シリーズ

# インプットキャプチャ機能によるパルスの周期測定

## 要旨

タイマ G インプットキャプチャ機能を使用して,インプットキャプチャ入力端子(TMIG)に入力されたパルスの周期を測定します。測定可能なパルスの最大周期は 3.277ms で,精度は  $12.8~\mu$  s です。

## 動作確認デバイス

H8/38024

## 目次

| 1. | 仕様       | . 2 |

|----|----------|-----|

|    | 使用機能説明   |     |

| 3. | 動作説明     | . 4 |

| 4. | ソフトウェア説明 | . 5 |

| 5. | フローチャート  | . 8 |

#### 1. 仕様

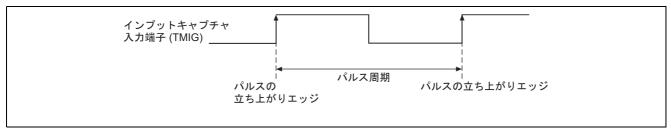

- (1) タイマ G インプットキャプチャ機能を使用して,インプットキャプチャ入力端子 (TMIG) に入力されたパルスの周期を測定します。

- (2) パルス立ち上がリエッジ間をタイマカウンタ G ( TCG ) でカウントし,RAM に格納します。この時の値からパルスの周期を測定します。

- (3) 測定可能なパルスの最大周期は 3.277ms で , 精度は 12.8 µ s です。

図1 入力パルスの周期測定

#### 2. 使用機能説明

- (1) 本タスク例では,タイマ G インプットキャプチャ機能を使用して,インプットキャプチャ入力端子 (TMIG)に入力されたパルスの周期を測定します。

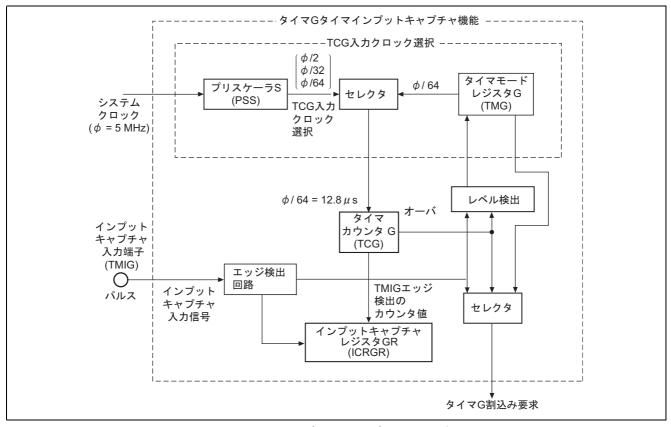

- (a) 図 2 にタイマ G インプットキャプチャ機能のブロック図を示します。以下にタイマ G インプットキャプチャ機能のブロック図について説明します。

- システムクロック( )は 5MHz で, CPU および周辺機能を動作させるための基準クロックです。

- プリスケーラ S (PSS) は , を入力とする 13 ビットのカウンタで , 1 サイクルごとにカウントアップします。

- タイマカウンタ G (TCG) は,8 ビットのリード/ライト不可なアップカウンタで,入力する内部クロック/外部クロックによりカウントアップされます。入力するクロックは,システムクロックの2分周,32分周,64分周および外部クロックの計4種類のクロックを選択可能です。本タスク例では,TCGの入力クロックにシステムクロックの64分周を選択しています。

- タイマモードレジスタ G (TMG) は,8 ビットのリード/ライト可能なレジスタで,TCG の入力クロックの選択,カウンタクリアの選択,インプットキャプチャ入力信号による割り込み要求のエッジ選択,オーバフローによる割り込み要求の許可/禁止を制御,およびオーバフローフラグの表示を行ないます。

- インプットキャプチャレジスタ GR (ICRGR) は,8 ビットのリード専用のレジスタで,インプットキャプチャ入力信号の立ち上がリエッジが検出されると,そのときの TCG の値が ICRGR に転送されます。このとき,IRR2の IRRTG が"1"ならば CPU に割込みを要求します。

- 周波数測定対象のパルスは,インプットキャプチャ入力信号として,インプットキャプチャ入力端子(TMIG)から入力します。

- 以下に本タスク例におけるパルス周期の計算方法を示します。ただし, TCG がオーバフローする と, 周期測定が正確に行なえないので, パルスの周期は TCG のオーバフロー周期(3.277ms)より 小さくしなければなりません。

- プログラム起動後,最初のパルス立ち上がりエッジをキャプチャした後,TCG がオーバフローすると,PDRHL に H'FF を格納します。

パルスの周期 = (PDRHL に格納された TCG のカウンタ値)×(TCG 入力クロック周期)

= (PDRHL に格納された TCG のカウンタ値) × 12.8 µs(1/(:5MHz/PSS:64))

図 2 タイマ G インプットキャプチャ機能ブロック図

(2) 表 1 に本タスク例の機能割付けを示します。表 1 に示すように機能を割付け,タイマ G インプットキャプチャ機能による周波数測定を行ないます。

機能 機能割付け システムクロックを入力とする 13 ビットのカウンタ **PSS** インプットキャプチャ入力信号による割り込みエッジの選択, TCG のオーバフローによる割 **TMG** 込みの許可, TCG入力クロックの設定 システムクロックの 64 分周を入力とする 8 ビットのアップカウンタ **TCG** インプットキャプチャ入力信号の立ち上がりエッジの検出により、その時の TCG のカウンタ **ICRGR** 値を格納 NCS インプットキャプチャ入力信号のノイズ除去機能を使わない **IENTG** インプットキャプチャ入力信号の立ち上がりエッジによる割込み要求の許可 **IRRTG** インプットキャプチャ入力信号の立ち上がりエッジによる割込みフラグ **TMIG** 周波数測定対象のパルスを入力

表 1 機能割付け

## 3. 動作説明

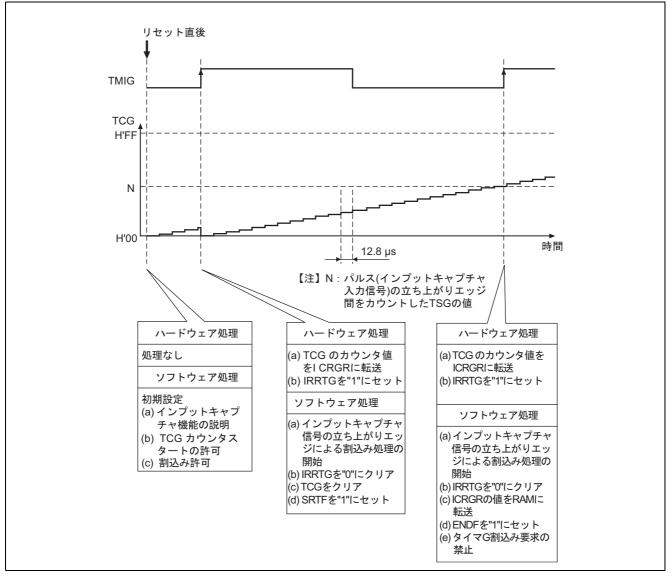

(1) 図 3 に動作説明を示します。図 3 に示すようなハードウェア処理,およびソフトウェア処理により,タイマ G インプットキャプチャ機能によるパルスの周期測定を行います。

図3 タイマGインプットキャプチャ機能によるパルスの周期測定の動作説明

## 4. ソフトウェア説明

## (1) モジュール説明

本タスク例のモジュールを表2に示します。

## 表2 モジュール説明

| モジュール名  | ラベル名  | 機能                                                                                                                                |  |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------|--|

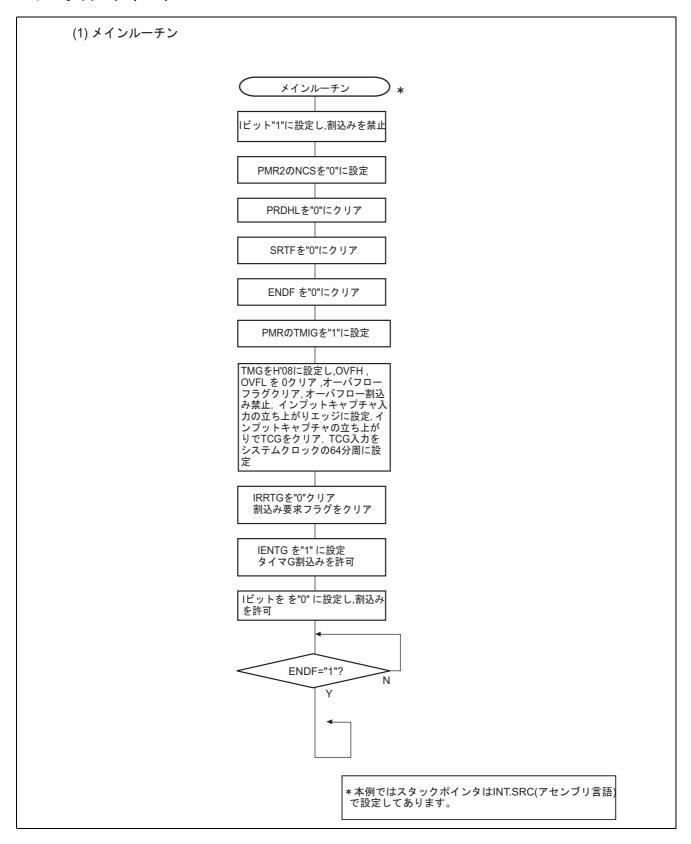

| メインルーチン | main  | タイマ G インプットキャプチャ機能の設定,割込みの許可を行なう。                                                                                                 |  |

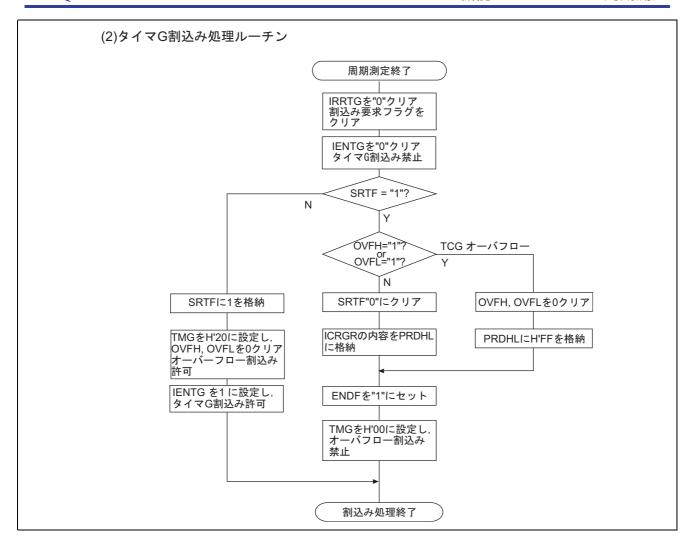

| 周期測定終了  | tgint | タイマ G 割込み処理ルーチン。1 回目の IRRTG による割込みでは ,TCG を H'00 にクリア , 2 回目の IRRTG による割込みでは , TCG が転送された ICRGR の内容を RAM に格納し , タイマ G 割込み要求を禁止する。 |  |

## (2) 引数の説明

本タスク例の引数を表3に示します。

## 表3 引数の説明

| 引数名   | 機能                                                | 使用モジュール名 | データ長 | 入出力 |

|-------|---------------------------------------------------|----------|------|-----|

| PRDHL | パルス(インプットキャプチャ入力信号)の立ち上がりエッジ間をカウントした TCG の値を格納する。 | メインルーチン  | 1バイト | 出力  |

## (3) 使用内部レジスタ説明

本タスク例の使用内部レジスタを表4に示します。

表 4 使用内部レジスタ説明

| レジスタ名                                                                                                                                         |                                                                                                                           | 機能                                                                                                                                                    |                          | 設定値                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|

|                                                                                                                                               | OVFH                                                                                                                      | タイマモードレジスタG(タイマオーバフローフラグH)<br>: OVFH="0"のとき,インプットキャプチャ入力信号が<br>High レベルで TCG がオーバフローしていない<br>: OVFH="1"のとき,インプットキャプチャ入力信号が<br>High レベルで TCG がオーバフローした | H'FFBC<br>ビット 7          | 0                      |

|                                                                                                                                               | OVFL                                                                                                                      | タイマモードレジスタ G(タイマオーバフローフラグ L)<br>: OVFL="0"のとき,インプットキャプチャ入力信号が<br>Low レベルで TCG がオーバフローしていない<br>: OVFL="1"のとき,インプットキャプチャ入力信号が<br>Low レベルで TCG がオーバフローした | H'FFBC<br>ビット 6          | 0                      |

| TMG                                                                                                                                           | OVIE                                                                                                                      | タイマモードレジスタ G<br>(タイマオーバフローインタラプトイネーブル)<br>: OVIE="0"のとき , TCG のオーバフローによる割込み要求を<br>禁止<br>: OVIE="1"のとき , TCG のオーバフローによる割込み要求を<br>許可                    | H'FFBC<br>ビット 5          | 0                      |

|                                                                                                                                               | IIEGS                                                                                                                     | タイマモードレジスタ G<br>(インプットキャプチャインタラプトエッジセレクト)<br>: IIEGS="0"のとき,インプットキャプチャ入力信号の立ち上がりエッジで割込みを発生<br>: IIEGS="1"のとき,インプットキャプチャ入力信号の立ち下がりエッジで割込みを発生           | H'FFBC<br>ビット 4          | 0                      |

|                                                                                                                                               | CCLR1<br>CCLR0                                                                                                            | タイマモードレジスタ G(カウンタクリア 1,0)<br>:CCLR1="1",CCLR0="0"のとき,インプットキャプチャ入<br>力信号の立ち上がりエッジにより TCG をクリア                                                          | H'FFBC<br>ビット3<br>ビット2   | CCLR1 = 1<br>CCLR0 = 0 |

|                                                                                                                                               | CKS1<br>CKS0                                                                                                              | タイマモードレジスタ G(クロックセレクト 1 , 0)<br>: CKS1="0" , CKS0="0"のとき TCG の入力カウントを /64<br>に設定                                                                      | H'FFBC<br>ビット 1<br>ビット 0 | CKS1 = 0<br>CKS0 = 0   |

| ICRGR                                                                                                                                         |                                                                                                                           | インプットキャプチャレジスタ GR<br>~8 ビットのリード専用レジスタで , インプットキャプチャ<br>入力信号の立ち上がリエッジが検出されると , そのときの<br>TCG の値が転送される。                                                  | H'FFBE                   | -                      |

| ポートモードレジスタ 1(P13/TMIG 端子機能切り替え)<br>: TMIG="0"のとき, P13/TMIG 端子は P13 入出力端子として<br>PMR1 TMIG 機能<br>: TMIG="1"のとき, P13/TMIG 端子は TMIG 入力端子として<br>機能 |                                                                                                                           | H'FFC8<br>ビット3                                                                                                                                        | 1                        |                        |

| PMR2                                                                                                                                          | 機能 ポートモードレジスタ 2 (TMIG ノイズキャンセラセレクト) : NCS="0"のとき , インプットキャプチャ入力信号のノイズ NCS 除去機能なし : NCS="1"のとき , インプットキャプチャ入力信号のノイズ 除去機能あり |                                                                                                                                                       | H'FFC9<br>ビット1           | 0                      |

# 表 4 使用内部レジスタ説明(つづき)

| レジスタ名 |       | 機能                                                                                                                              | アドレス            | 設定値 |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|

| IENR2 | IENTG | 割込み許可レジスタ 2(タイマ G 割込みイネーブル)<br>~タイマ G 割込み要求の許可/禁止を制御します。<br>:IENTG="0"のとき,タイマ G 割込み要求を禁止<br>:IENTG="1"のとき,タイマ G 割込み要求を許可        | H'FFF4<br>ビット 4 | 1   |

| IRR2  | IRRTG | 割込み要求レジスタ 2(タイマ G 割込み要求フラグ)<br>~ タイマ G 割込み要求の有無を反映します。<br>: IRRTG="0"のとき,タイマ G 割込みが要求されていない<br>: IRRTG="1"のとき,タイマ G 割込みが要求されている | H'FFF7<br>ビット 4 | 0   |

## (4) 使用 RAM 説明

本タスク例の使用 RAM を表 5 に示します。

表 5 使用 RAM 説明

| ラベル名  |      | 機能                                                   | アドレス            | 使用モジュール名          |

|-------|------|------------------------------------------------------|-----------------|-------------------|

| PRDHL |      | パルス(インプットキャプチャ入力信号)の立ち上がり<br>エッジ間をカウントした TCG の値を格納する |                 | 周期測定終了            |

| USRF  | SRTF | 2 回目のタイマ G 割込みか否かを判定するフラグ                            | H'FB81<br>ビット 1 | 周期測定終了            |

| USKF  | ENDF | 周期測定が終了したか否かを判定するフラグ                                 | H'FB81<br>ビット 0 | メインルーチン<br>周期測定終了 |

## 5. フローチャート

# 5.1 INIT.SRC (プログラムリスト)

```

.EXPORT _INIT

.IMPORT _main

;

.SECTION P,CODE

_INIT:

MOV.W #H'FF80,R7

LDC.B #B'10000000,CCR

JMP @_main

;

.END

```

```

/* H8/300L Super Low Power Series

* /

-H8/38024 Series-

* /

/* Application Note

/*

/* 'Pulse Period Measurement by Input

Caputure Function'

/*

/* Function

/* : Timer G Input Capture

/*

/* External Clock : 10MHz

/* Internal Clock : 5MHz

/* Sub Clock : 32.768kHz

#include <machine.h>

/* Symbol Definition

struct BIT {

unsigned char b7:1; /* bit7 */

unsigned char b6:1;

/* bit6 */

/* bit5 */

unsigned char b5:1;

unsigned char b4:1;

/* bit4 */

unsigned char b3:1;

/* bit3 */

unsigned char

b2:1;

/* bit2 */

/* bit1 */

unsigned char b1:1;

unsigned char b0:1;

/* bit0 */

};

#define TMG *(volatile unsigned char *)0xFFBC /* Timer Mode Register G

#define TMG_BIT (*(struct BIT *)0xFFBC)

/* Timer Mode Register G

#define OVFH

TMG_BIT.b7

/* Timer Overflow Flag H

#define OVFL

TMG_BIT.b6

/* Timer Overflow Flag L

/* Timer Overflow Interrupt Enable */

#define OVIE

TMG_BIT.b5

#define IIEGS

TMG_BIT.b4

/* Input Caputure Interrupt Edge Select */

#define CCLR1

TMG_BIT.b3

/* Counter Clear 1

#define CCLR0

/* Counter Clear 0

* /

TMG BIT.b2

#define CKS1

* /

/* Clock Select 1

TMG_BIT.b1

#define CKS0

TMG_BIT.b0

/* Clock Select 0

```

# インプットキャプチャ機能によるパルスの周期測定

```

#define

ICRGR

*(volatile unsigned char *)0xFFC8 /* Port Mode Register 1

* /

#define PMR1

#define PMR1_BIT (*(struct BIT *)0xFFC8) /* Port Mode Register 1

* /

#define TMIG PMR1_BIT.b3 /* P13/TMIG Input Select #define PMR2 *(volatile unsigned char *)0xFFC9 /* Port Mode Register 2

/* P13/TMIG Input Select

#define PMR2_BIT (*(struct BIT *)0xFFC9) /* Port Mode Register 2

* /

/* TMIG Noise Canceller Select

#define NCS PMR2_BIT.b1

/* Interrupt Enable Register 2

#define IENR2_BIT (*(struct BIT *)0xFFF4)

#define IENTG IENR2_BIT.b4

/* Timer G Interrupt Enable

/* Interrupt Request Register 2 */

#define IRR2_BIT (*(struct BIT *)0xFFF7)

#define IRRTG IRR2_BIT.b4

/* Timer G Interrupt Request Flag */

#pragma interrupt (tgint)

/* Function define

extern void INIT ( void );

* /

/* SP Set

void main ( void );

void

tgint ( void );

unsigned char PRDHL;

/* Period Higher&Lower

* /

unsigned char USRF;

/* User Flag Area

#define USRF_BIT (*(struct BIT *)&USRF)

#define SRTF USRF_BIT.b1

#define ENDF USRF_BIT.b0

/* Start Flag

/* End Flag

/* Vector Address

#pragma section V1

/* VECTOR SECTOIN SET

void (*const VEC_TBL1[])(void) = {

/* 0x00 - 0x0f */

INIT

/* 00 Reset

* /

#pragma section V2

/* VECTOR SECTOIN SET

void (*const VEC_TBL2[])(void) = {

/* 20 Timer G Interrupt

taint

};

#pragma section

/* Main Program

void main ( void )

int tmp;

set_imask_ccr(1);

/* Interrupt Disable

/* No Noise Cancellation circuit

* /

NCS = 0;

PRDHL = 0;

/* Caputure Data Ramcopy

SRTF = 0;

```

```

ENDF = 0;

TMIG = 1;

/* P13/TMIG input selectb

tmp = TMG;

/* Dummy Read for Flag Clear

TMG = 0x08;

/* Timer Mode Register Set

/* Clear IRRTG

IRRTG = 0;

/* Timer G Interrupt Enable

IENTG = 1;

/* Interrupt Enable

* /

set_imask_ccr(0);

/* ENDF = 1 ?

while(ENDF != 1){

;

while(1){

;

}

}

/* Timer G Interrupt

void tgint ( void )

int tmp;

IRRTG = 0;

/* Clear IRRTG

/* Timer G Interrupt Disable

IENTG = 0;

if ( SRTF == 1 ){

if((OVFH == 1)|(OVFL == 1)){

tmp = TMG;

/* Dummy Read for Flag Clear

TMG = 0;

/* Timer Mode Register Set

PRDHL = 0xFF;

}

else{

SRTF = 0;

/* Clear SRTF

PRDHL = ICRGR;

/* Caputure Data Ramcopy

ENDF = 1;

/* Set ENDF

/* Overflow Interrupt Disable

TMG = 0;

else{

SRTF = 1;

/* Set SRTF

tmp = TMG;

/* Dummy Read for Flag Clear

TMG = 0x20;

/* Overflow Interrupt Enable

IENTG = 1;

/* Timer G Interrupt Enable

}

}

```

# リンクアドレス指定

| セクション名 | アドレス   |

|--------|--------|

| CV1    | H'0000 |

| CV2    | H'0020 |

| Р      | H'0100 |

| В      | H'FB80 |

# 改訂記録

|      |            | 改訂内容 |      |  |

|------|------------|------|------|--|

| Rev. | 発行日        | ページ  | ポイント |  |

| 1.00 | 2003.12.19 | _    | 初版発行 |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

|      |            |      |      |  |

#### 安全設計に関するお願い =

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

#### ■ 本資料ご利用に際しての留意事項 ■

- 1. 本資料は、お客様が用途に応じた適切なルネサステクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサステクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサステクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起 因する損害がお客様に生じた場合には、ルネサステクノロジはその責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサステクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサステクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサステクノロジ、ルネサス販売または特約店までご照会ください。