R01AN0301EJ0101

# SH7670 Group

Rev. 1.01 Example of Setting for Automatic Negotiation by Ethernet PHY-LSI Oct. 15, 2010

## Summary

This application note describes an example of settings for automatic negotiation with partners in communications when an Ethernet PHY-LSI chip has been connected to an SH7670, SH7671, SH7672 or SH7673.

# **Target Device**

SH7670 MCU

#### Contents

| 1. | Introduction                          | 2    |

|----|---------------------------------------|------|

| 2. | Description of the Sample Application | 3    |

| 3. | Sample Program Listing                | . 12 |

| 4. | References                            | . 29 |

# 1. Introduction

#### 1.1 Specifications

- In this sample application, results of automatic negotiation when an Ethernet PHY-LSI chip has been connected to the SH7670 are acquired. The obtained connection mode (full-duplex and half-duplex modes) is specified as EtherC transfer method.

- An RTL8201 manufactured by Realtek Semiconductor Corp. is employed as the Ethernet PHY-LSI.

- Automatic negotiation function is used to establish the link with the Ethernet PHY-LSI.

#### 1.2 Module Used

- Pin function controller (PFC)

- Ethernet controller (EtherC)

## 1.3 Applicable Conditions

| MCU                    | SH7670                                                                                                                               |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Operating Frequency    | Internal clock: 200 MHz                                                                                                              |

|                        | Bus clock: 66.6 MHz                                                                                                                  |

|                        | Peripheral clock: 33.3 MHz                                                                                                           |

| Integrated Development | Renesas Electronics                                                                                                                  |

| Environment            | High-performance Embedded Workshop Ver.4.03.00                                                                                       |

| C Compiler             | Renesas Electronics SuperH RISC engine Family                                                                                        |

|                        | C/C++ compiler package Ver.9.01 Release 01                                                                                           |

| Compiler Options       | Default setting in the High-performance Embedded Workshop                                                                            |

|                        | (-cpu=sh2afpu -fpu=single -debug -gbr=auto -global_volatile=0 -opt_range=all<br>-infinite_loop=0 -del_vacant_loop=0 -struct_alloc=1) |

#### 1.4 Related Application Notes

For more information, refer to the following application notes:

- SH7670 Group Example of Initialization

- SH7670 Group Example of Setting for Transmission of Ethernet Frames

- SH7670 Group Example of Setting for Reception of Ethernet Frames

## 2. Description of the Sample Application

This sample application employs an Ethernet PHY-LSI chip to perform automatic negotiation with a partner in communications. The result of automatic negotiation is read out via the PHY interface register (PIR) of the EtherC module.

## 2.1 Operational Overview of Module Used

Link processing on the physical layer is one function of an Ethernet PHY-LSI chip. The on-chip EtherC module of an SH7670 MCU can obtain the result of link processing by reading values from the Ethernet PHY chip. In this sample application, the PHY-LSI pins are set up to enable the function of automatic negotiation. For details on the functions of the Ethernet PHY-LSI, see the datasheet for the product.

The interface between the EtherC module and the Ethernet PHY-LSI is a Media Independence Interface (MII) compliant with IEEE802.3. Figure 1 shows an example of the connections between an SH7670 MCU and RTL8201CP.

The results of automatic negotiation are stored in the Ethernet PHY-LSI register, and are read out by using the serial interface between the MDC and MDIO pins. The SH7670 MCU can read or write both pins by using the PIR register. For the procedure to access to the registers of the PHY-LSI, see the next section 2.2, Procedure for Access to the MII Registers.

| MII (Media Independent Interface) |          |     |           |  |  |

|-----------------------------------|----------|-----|-----------|--|--|

| _                                 | SH7670   |     | RTL8201CP |  |  |

|                                   | TX-ER    |     | TX-ER     |  |  |

|                                   | MII_TXD3 |     | TXD3      |  |  |

|                                   | MII_TXD2 |     | TXD2      |  |  |

|                                   | MII_TXD1 |     | TXD1      |  |  |

|                                   | MII_TXD0 |     | TXD0      |  |  |

|                                   | TX-EN    |     | TXEN      |  |  |

|                                   | TX-CLK   | •   | ТХС       |  |  |

|                                   | MDC      |     | MDC       |  |  |

|                                   | MDIO     | ◄ ► | MDIO      |  |  |

|                                   | MII_RXD3 | •   | RXD3      |  |  |

|                                   | MII_RXD2 |     | RXD2      |  |  |

|                                   | MII_RXD1 | •   | RXD1      |  |  |

|                                   | MII_RXD0 | •   | RXD0      |  |  |

|                                   | RX-CLK   | •   | RXC       |  |  |

|                                   | CRS      | •   | CRS       |  |  |

|                                   | COL      |     | COL       |  |  |

|                                   | RX-DV    | •   | RXDV      |  |  |

|                                   | RX-ER    |     | RXER/FXEN |  |  |

| l                                 |          |     | -         |  |  |

Figure 1 Example of Connecting an MCU to the RTL8201CP

## 2.2 Procedure for Access to the MII registers

This section describes the procedure for access to the MII registers of the Ethernet PHY-LSI register.

The MII operates through two pins, MDC and MDIO (both are the pin names on the EtherC side). The MDC pin is for the synchronizing clock signal, while data are input and output through the MDIO pin. The state of each pin can be referred or changed by the PIR register of EtherC. The MII must output data as specified in the standard format (the MII management frame) as it has no control pins. Figure 2 shows the MII management frame. In this sample program, Z is output over one bit period in the idle state. This is required because, while there is no reference to clock input in the IEEE802.3 standard, correct connection with some PHY-LSI circuits is not otherwise possible. This precautionary operation avoids such situations.

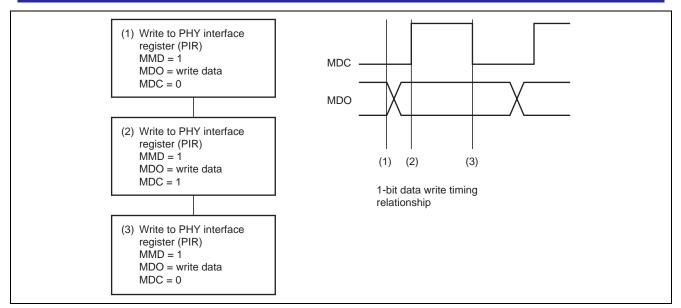

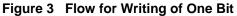

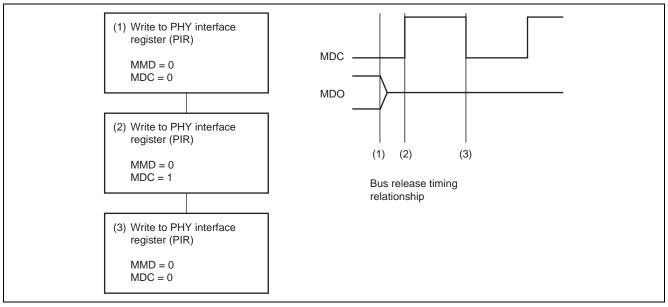

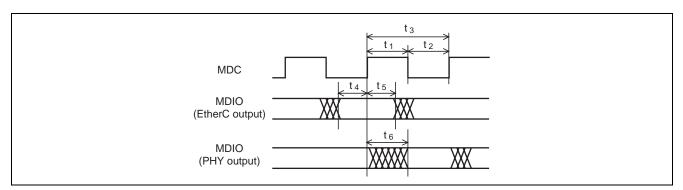

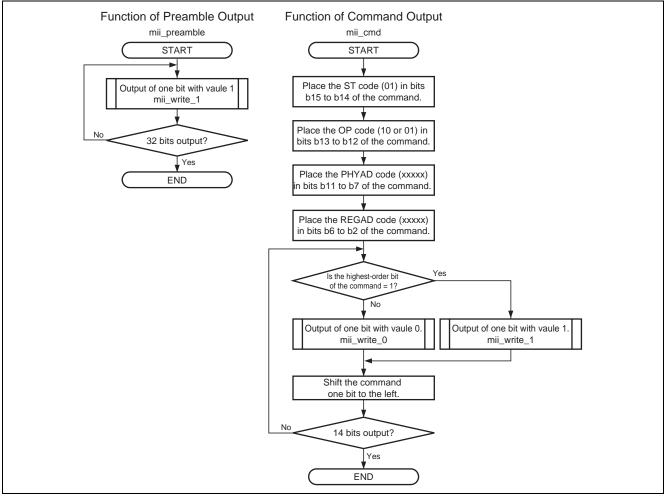

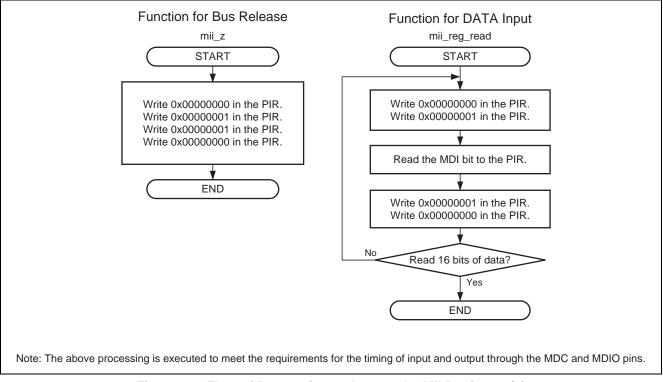

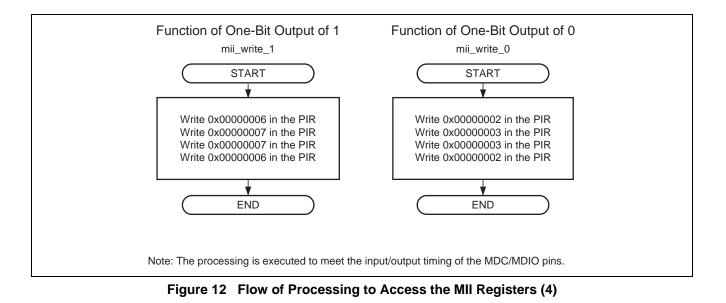

An MII management frame is input or output in one-bit units, in order from the preamble. Figures 3 to 5 depict the flow of input and output of the one-bit units. The timing of input and output on the MDC and MDIO pins must conform with the IEEE802.3 standard. Table 1 and Figure 6 show the standard's specifications for the timing of input and output.

| ·                                                                                        |              |                                                                                                                                                                                                                                                                                 |                                                  |              |             |            |             | 1          |  |

|------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------|-------------|------------|-------------|------------|--|

| Access Type                                                                              |              | MII mangement frame                                                                                                                                                                                                                                                             |                                                  |              |             |            |             |            |  |

| Item                                                                                     | PRE          | ST                                                                                                                                                                                                                                                                              | OP                                               | PHYAD        | REGAD       | TA         | DATA        | IDLE       |  |

| Number of bits                                                                           | 32           | 2                                                                                                                                                                                                                                                                               | 2                                                | 5            | 5           | 2          | 16          | 1          |  |

| Read                                                                                     | 11           | 01                                                                                                                                                                                                                                                                              | 10                                               | AAAAA        | RRRRR       | Z0         | DD          | Z          |  |

| Write                                                                                    | 11           | 01                                                                                                                                                                                                                                                                              | 01                                               | AAAAA        | RRRRR       | 10         | DD          | Z          |  |

| [Legend]         PRE (preamble):       32 consecutive 1s are output for synchronization. |              |                                                                                                                                                                                                                                                                                 |                                                  |              |             |            |             |            |  |

| ST (start of fram                                                                        | ie):         | 01 is ou                                                                                                                                                                                                                                                                        | 01 is output to indicate the start of the frame. |              |             |            |             |            |  |

| OP (operation co                                                                         | ode):        | Output to specify reading or writing; 10 indicates reading, 01 indicates writing.                                                                                                                                                                                               |                                                  |              |             |            |             |            |  |

| PHYAD (PHY address):                                                                     |              | The address to distinguish one amoung multiple PHY-LSIs.<br>The address is often specified by the levels on PHY-LSI pins.<br>This is output from the MSB.                                                                                                                       |                                                  |              |             |            |             |            |  |

| REGAD (Registe                                                                           | er address): | Specifies the number of MII registers. This is output from the MSB.                                                                                                                                                                                                             |                                                  |              |             |            |             |            |  |

| TA (turn around):                                                                        |              | <ul> <li>Switches the transmission source of the MDIO pin to avoid collision of signals.</li> <li>(a) Reading: The bus is released over one bit period (Z output).<br/>As 0 is output from the PHY module, the notation is "Z0".</li> <li>(b) Writing: 10 is output.</li> </ul> |                                                  |              |             |            |             |            |  |

| DATA (data):                                                                             |              | 16-bit value read from or to be written to the register. Writing or reading proceeds in order from the MSB.                                                                                                                                                                     |                                                  |              |             |            |             |            |  |

| IDLE (IDLE condition):                                                                   |              | Wait fo                                                                                                                                                                                                                                                                         | r further in                                     | out in the M | 111 manager | nent forma | at. The bus | is release |  |

|                                                                                          |              |                                                                                                                                                                                                                                                                                 |                                                  |              |             |            |             |            |  |

Figure 2 MII Management Frame Format

Figure 4 Flow of Bus Release (Z-output)

#### Figure 5 Flow for Reading of One Bit

#### Table 1 MDC/MDIO Input/Output Timing

| Item                       | Symbol         | Min | Max | Unit |  |

|----------------------------|----------------|-----|-----|------|--|

| MDC high-level pulse width | t <sub>1</sub> | 160 |     | ns   |  |

| MDC low-level pulse width  | t <sub>2</sub> | 160 |     | ns   |  |

| MDC cycle time             | t <sub>3</sub> | 400 |     | ns   |  |

| MDIO setup time            | t <sub>4</sub> | 10  |     | ns   |  |

| MDIO hold time             | t <sub>5</sub> | 10  |     | ns   |  |

| MDIO output delay time     | t <sub>6</sub> | 0   | 300 | ns   |  |

| Figure 6 | MDC/MDIO | Input/Output | Timing |

|----------|----------|--------------|--------|

|----------|----------|--------------|--------|

# 2.3 Description of Settings in the Sample Program

This sample program is in two files of source code, main.c and phy.c, and the files for initialization created in the application note "Example of Initialization" for the SH7670 (REJ06B0799).

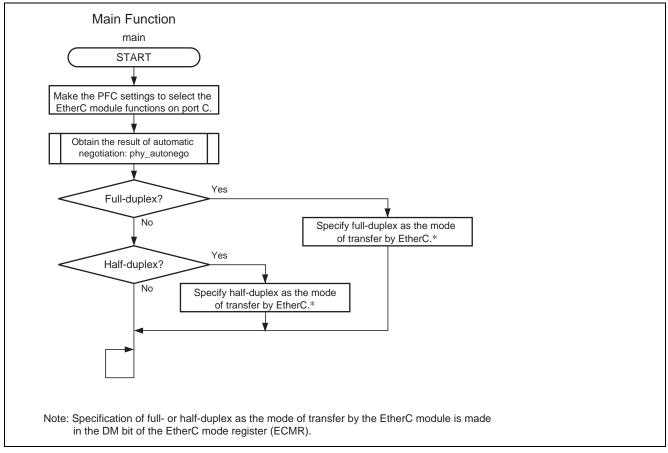

#### • main.c

This contains the definition of the main function, and obtains the result of automatic negotiation. Figure 7 shows the flow of processing by the main function.

#### • phy.c

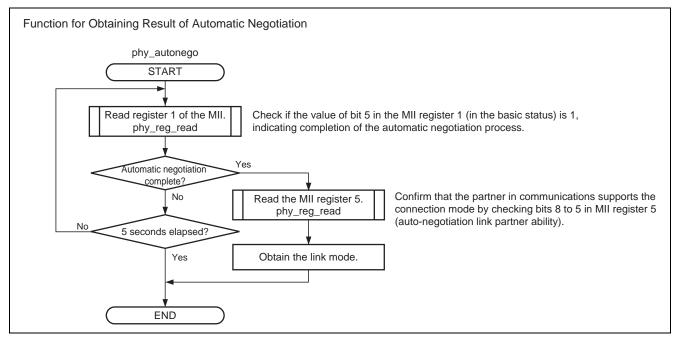

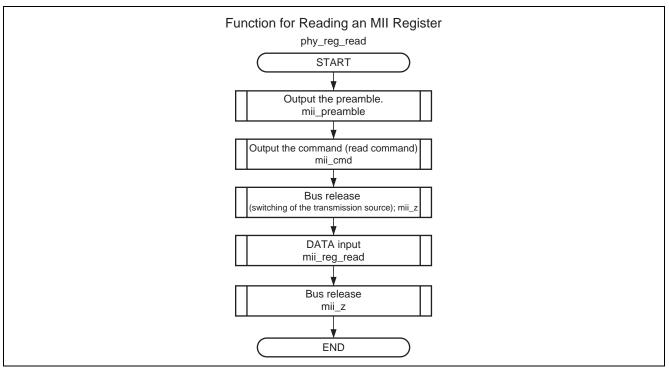

This contains the definition of the function for obtaining the result of automatic negotiation (function phy\_autonego). Figure 8 shows the flow of processing by the phy\_autonego function. Figures 9 to 12 show the flows of processing by the MII register-read function (function phy\_reg\_read) that is called by the phy\_autonego function, and of functions lower in the hierarchy of calls.

Figure 7 Flow of Processing by the main Function

Figure 8 Flow of Processing by the Function for Obtaining the Result of Automatic Negotiation

Figure 9 Flow of Processing to Access the MII Registers (1)

Figure 10 Flow of Processing to Access the MII Registers (2)

Figure 11 Flow of Processing to Access the MII Registers (3)

# 2.4 Description of Settings in the Sample Program

Table 2 is a list of the settings in the sample program.

#### Table 2 Settings in the Sample Program

| Item                      | Description                                                                      |

|---------------------------|----------------------------------------------------------------------------------|

| PHY used                  | RTL8201CP manufactured by Realtek Semiconductor Corp.                            |

| Link mode                 | 100 Mbps (full- and half-duplex modes) and 10 Mbps (full- and half-duplex modes) |

| Link determination method | Automatic negotiation (auto-negotiation)                                         |

| MII registers used        | Basic mode register (address: 01h)                                               |

|                           | Auto-negotiation link partner ability (address: 05h)                             |

## 2.5 Notes on Using the Sample Program

- The automatic negotiation mode is assumed to be the method by which linking of the PHY chip is detected in this sample program.

- When the partner is also in the automatic negotiation mode, the link is established in accord with the order of priority shown in table 3.

- The completion of automatic negotiation usually takes a couple of seconds, but the phy\_autonego function allows up to 5 seconds for the completion of negotiations in the sample program.

| Order of Priority                 |   | Link                       |

|-----------------------------------|---|----------------------------|

| High 1 Full-duplex mode, 100 Mbps |   | Full-duplex mode, 100 Mbps |

|                                   | 2 | Half-duplex mode, 100 Mbps |

|                                   | 3 | Full-duplex mode, 10 Mbps  |

| Low                               | 4 | Half-duplex mode, 10 Mbps  |

#### Table 3 Link Type Priorities

#### 3. Sample Program Listing

#### 3.1 Sample program list "main.c" (1)

```

1

2

DISCLAIMER

3

This software is supplied by Renesas Electronics Corporation and is only

4

intended for use with Renesas products. No other uses are authorized.

5

6

7

This software is owned by Renesas Electronics Corporation and is protected under

all applicable laws, including copyright laws.

8

9

10

*

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

DISCLAIMED.

15

16

TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

* ELECTRONICS CORPORATION NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

17

18

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

* FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

19

20

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

*

22

Renesas reserves the right, without notice, to make changes to this

23

software and to discontinue the availability of this software.

24

* By using this software, you agree to the additional terms and

25

* conditions found by accessing the following link:

* http://www.renesas.com/disclaimer

26

****

27

28

* Copyright (C) 2007(2010) Renesas Electronics Corporation. All rights reserved.

29

30

System Name : SH7671 Sample Program

* File Name : main.c

31

32

* Abstract : Acquiring Ethernet PHY automatic negotiation results

* Version

: 1.01.01

33

* Device

: SH7671

34

Tool-Chain : High-performance Embedded Workshop (Ver.4.03.00).

35

36

*

: C/C++ compiler package for the SuperH RISC engine family

*

37

:

(Ver.9.01 Release01).

* OS

38

: None

39

H/W Platform: M3A-HS71(CPU board)

40

Description :

41

History

42

: Jul.04,2007 ver.1.00.00

43

: Sep.18,2007 ver.1.01.00 support for revised board DK30686-A

: May 12,2010 ver.1.01.01 Changed the company name and device name

44

45

#include "iodefine.h"

46

47

#include "defs.h"

48

#include "phy.h"

49

50

/* ==== Prototype declaration ==== */

51

void main(void);

```

#### 3.2 Sample program list "main.c" (2)

52

```

53

54

* ID

:

* Outline

55

: Main function of acquiring PHY-LSI automatic negotiation results

56

*_____

57

* Include

: #include "iodefine.h"

58

*_____

* Declaration : void main(void)

59

60

*_____

61

* Function : PHY link mode is determined by PHY-LSI automatic negotiation function.

62

: This sample reads out the results.

63

: Normally the automatic negotiation is compleded in 1200 ms, and

*

: uatomatic negotiation acquisition function checks negotiation completion

64

for 5 s max.

65

*

: The results of full-duplex or half-duplex is set in EtherC.

66

*_____

67

* Argument : void

*-----

68

* ReturnValue : void

69

70

*_____

71

* Notice

:

72

73

void main(void)

74

{

75

int link;

76

/* ==== PFC setting ==== */

77

/* Setting when DK30686 board is used */

78

//PORT.PBCRL1.BIT.PB6MD = 1;

/* EtherC function */

PORT.PCCRH1.WORD = 0x0155;

79

80

PORT.PCCRL1.WORD = 0x5555;

/* PHY-LSI operates independently; this is for PHY

register access */

81

PORT.PCCRL2.WORD = 0x5555;

/* Necessary for using MII control interface */

82

83

/* ==== Acquire PHY negotiation results ==== */

84

link=phy_autonego();

85

/* ==== EtherC duplex mode setting ==== */

86

87

if( link == FULL_TX || link == FULL_10M ){

EtherC.ECMR.BIT.DM = 1;

/* Full duplex */

88

89

}

else if(link == HALF_TX || link == HALF_10M){

90

91

EtherC.ECMR.BIT.DM = 0;

/* Half duplex */

92

}

93

else{

94

;/* Link failed */

95

}

96

/* ==== Main loop ==== */

97

98

while(1){

99

;

100

}

101

}

102

103

/* End of file */

```

#### 3.3 Sample program list "phy.c" (1)

```

1

DISCLAIMER

2

3

This software is supplied by Renesas Electronics Corporation and is only

4

5

intended for use with Renesas products. No other uses are authorized.

6

7

This software is owned by Renesas Electronics Corporation and is protected under

all applicable laws, including copyright laws.

8

9

10

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

12

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

13

14

DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

* ELECTRONICS CORPORATION NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

18

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

19

20

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

* Renesas reserves the right, without notice, to make changes to this

22

\ast software and to discontinue the availability of this software.

23

* By using this software, you agree to the additional terms and

24

25

* conditions found by accessing the following link:

* http://www.renesas.com/disclaimer

26

27

28

* Copyright (C) 2007(2010) Renesas Electronics Corporation. All rights reserved.

29

30

*

System Name : SH7671 Sample Program

* File Name : phy.c

31

32

* Abstract : Obtaining the result of automatic negotiation by the Ethernet PHY

* Version

: 1.00.01

33

Device

: SH7671

34

35

*

Tool-Chain : High-performance Embedded Workshop (Ver.4.03.00).

: C/C++ compiler package for the SuperH RISC engine family

36

37

:

(Ver.9.01 Release01).

* OS

38

: None

* H/W Platform: M3A-HS71(CPU board)

39

* Description :

40

41

: Jul.13,2007 ver.1.00.00

42

Historv

: May 12,2010 ver.1.00.01 Changed the company name and device name

43

44

45

#include "iodefine.h"

46

#include "defs.h"

47

#include "phy.h"

48

49

/* **** Prototype declaration **** */

50

static unsigned short phy_reg_read (unsigned short reg_addr);

51

static void phy_reg_write (unsigned short reg_addr, unsigned short data);

52

static void mii_preamble (void);

static void mii_cmd (unsigned short reg_addr, int option);

53

static void mii_tal0 (void);

54

```

```

3.4 Sample program list "phy.c" (2)

```

```

55

static void mii_reg_read (unsigned short *data);

56

static void mii_reg_write (unsigned short data);

57

static void mii_write_1 (void);

58

static void mii_write_0 (void);

59

static void mii_z (void);

60

61

/* **** Macro definition **** */

62

63

/* PHY register */

64

#define BASIC_MODE_CONTROL_REG 0

65

#define BASIC_MODE_STATUS_REG 1

66

#define PHY_IDENTIFIER1_REG 2

67

#define PHY_IDENTIFIER2_REG 3

#define AN_ADVERTISEMENT_REG 4

68

69

#define AN_LINK_PARTNER_ABILITY_REG 5

70

#define AN_EXPANSION_REG 6

71

/* PHY address */

#define PHY_ADDR 1 /* Confirm the pin connection of the PHY-LSI */

72

73

/* For accessing the MII management interface */

74

#define PHY_ST 1

75

#define PHY_WRITE 1

#define PHY_READ 2

76

77

#define MDC_WAIT 3 /* 400 ns/4 < (P\phi*2)*MDC_WAIT */

78

79

80

81

* ID

82

* Outline

: Detection of the result of automatic negotiation of the PHY link

83

*_____

84

* Include

: "iodefine.h", "defs.h"

*_____

85

86

* Declaration : int phy_autonego(void);

*_____

87

* Description : The result of automatic negotiation is read out by using the MII

88

89

: management interface, and indicated in the return value.

90

: The PHY chip used with this sample program supports all of the listed

: transfer modes, including full-duplex connection at 100 Mbps.

91

92

: If the target of the link supports automatic negotiation,

93

: it chooses its top-performance link mode for connection.

94

: If it does not, the parallel detection function detects the link speed;

95

: in that case, half-duplex mode is specified. Although automatic

: negotiation is usually completed in about 1,200 ms,

96

97

: this function allows up to 5 seconds for completion of the negotiation.

*_____

98

99

* Argument

: void

100

*_____

* Return Value : 4(FULL_TX) :100 Mbps in full-duplex mode

101

: 3(HALF_TX) :100 Mbps in half-duplex mode

102

103

: 2(FULL_10M) :10 Mbps in full-duplex mode

104

: 1(HALF_10M) :10 Mbps in half-duplex mode

105

: 0(NEGO_FAIL) :Failure in negotiation

*_____

106

107

* Note

: The parallel detection function is not considered in this sample program.

108

```

```

3.5 Sample program list "phy.c" (3)

```

109

```

110

int phy_autonego (void)

111

{

112

unsigned short data;

113

int link = NEGO_FAIL;

114

volatile int t;

115

int i;

116

117

/*=== Loop to wait for completion of automatic negotiation (for up to 5 seconds)==== */

118

for(i=0; i<500; i++){</pre>

119

/* ==== Wait for 10 ms to set up a benchmark for measurement of elapsed-time ==== */

120

t = LOOP_{100us*100};

121

while( --t){

122

;

123

}

124

/* ==== Confirm completion of automatic negotiation==== */

data = phy_reg_read(BASIC_MODE_STATUS_REG);

125

if( data & 0x0020 ){ /* PHY register 1 :Basic status *

126

\ast bit 5 :(1) completion of automatic negotiation process \ast

127

128

:(0) non-completion of automatic negotiation process */

129

/* ---- The capability of the partner as determined

130

on completion of automatic negotiation. ---- */

131

data = phy_reg_read(AN_LINK_PARTNER_ABILITY_REG);

132

/* PHY register 5 :Auto-nego link partner ability *

133

* bit 8 :(1)100 Mbps/full-duplex mode is possible *

134

* bit 7 :(1)100 Mbps/half-duplex mode is possible *

135

* bit 6 :(1) 10 Mbps/full-duplex mode is possible *

* bit 5 :(1) 10 Mbps/half-duplex mode is possible */

136

137

/* ---- Break on completion of negotiation following detection of results ---- */

138

if( data&0x0100 ){

139

link = FULL_TX;

140

}

else if (data&0x0080){

141

142

link = HALF_TX;

143

}

else if (data&0x0040){

144

link = FULL_10M;

145

146

}

else if (data&0x0020){

147

link = HALF_10M;

148

149

}

150

else{

151

link = NEGO_FAIL;

152

}

153

/* ---- Processing to detect the result of automatic negotiation is complete. ---- ^{*/}

154

break;

155

}

156

}

157

return link;

158

}

```

# 3.6 Sample program list "phy.c" (4)

| /*""FUNC COMMENT""***********************************                         |

|-------------------------------------------------------------------------------|

| * ID :                                                                        |

| * Outline : Reading of a PHY module register                                  |

| *                                                                             |

| * Include :                                                                   |

| *                                                                             |

| * Declaration : static unsigned short phy_reg_read (unsigned short reg_addr); |

| *                                                                             |

| * Description : Obtains the value from a register of the PHY module.          |

| *                                                                             |

| * Argument : unsigned short reg_addr ; I : Address of the PHY register        |

| * : from which value is to be read.                                           |

| *                                                                             |

| * Return Value : The obtained register value                                  |

| *                                                                             |

| * Note :                                                                      |

| *""FUNC COMMENT END""***********************************                      |

| static unsigned short phy_reg_read (unsigned short reg_addr)                  |

| {                                                                             |

| unsigned short data;                                                          |

|                                                                               |

| <pre>mii_preamble();</pre>                                                    |

| <pre>mii_cmd (reg_addr, PHY_READ);</pre>                                      |

| mii_z();                                                                      |

| <pre>mii_reg_read (&amp;data);</pre>                                          |

| mii_z();                                                                      |

|                                                                               |

| return data;                                                                  |

| }                                                                             |

#### 3.7 Sample program list "phy.c" (5)

```

188

* ID

189

:

190

* Outline

: Writing to a PHY module register

*_____

191

* Include

192

:

193

*_____

194

* Declaration : static void phy_reg_write (unsigned short reg_addr,

*

195

:

unsigned short data);

196

*_____

* Description : Set the value in the PHY module register

197

198

*_____

* Argument : unsigned short reg_addr ; I : Address of the PHY register to which

199

200

the value is to be written

201

*

: unsigned short data ; I : Value to be set in the PHY register

202

*_____

203

* Return Value : void

*-----

204

205

* Note

:

206

207

void phy_reg_write (unsigned short reg_addr, unsigned short data)

208

{

209

mii_preamble();

210

mii_cmd (reg_addr, PHY_WRITE);

211

mii_ta10();

212

mii_reg_write (data);

213

mii_z();

214

215

}

```

#### 3.8 Sample program list "phy.c" (6)

```

216

* ID

217

:

* Outline

218

: Preparation to access a PHY module register

*_____

219

* Include

:

220

221

*_____

222

* Declaration : static void mii_preamble (void);

223

*_____

224

* Description : As preliminary preparation for access to the PHY module register,

225

*

: 1 is output via the MII management interface.

226

*_____

: void

* Argument

227

228

*_____

------

229

* Return Value : void

230

*_____

231

* Note

:

232

233 static void mii_preamble (void)

234

{

235

short i;

236

i = 32;

237

while( i > 0 ) {

238

239

/* 1 is output via the MII (Media Independent Interface) block */

240

mii_write_1();

i--;

241

}

242

243

}

```

#### 3.9 Sample program list "phy.c" (7)

```

244

245

* ID

: Setting of the register mode of the PHY module

246

* Outline

247

*_____

* Include

248

:

*_____

249

250

* Declaration : static void mii_cmd (unsigned short reg_addr, int option );

251

*_____

252

* Description : Placing the PHY module register in read or write mode

*_____

253

254

* Argument

: unsigned short reg_addr ; I : Address of the PHY register

255

: int option ; I : Specification of reading or writing

256

*_____

257

* Return Value : void

258

*_____

259

* Note

:

260

261 static void mii_cmd (unsigned short reg_addr, int option)

262

{

263

int i;

264

unsigned short data;

265

266

data = 0;

data = (PHY_ST << 14); /* ST code */

267

268

if (option == PHY_READ) {

269

data |= (PHY_READ << 12); /* OP code(RD) */</pre>

270

}

271

else {

272

data |= (PHY_WRITE << 12); /* OP code(WT) */</pre>

273

}

274

data |= (PHY_ADDR << 7); /* PHY Address */</pre>

data |= (reg_addr << 2); /* Reg Address */

275

276

277

for(i=14; i>0; i--){

278

if ((data & 0x8000) == 0) {

279

mii_write_0();

280

}

281

else {

282

mii_write_1();

283

}

284

data <<= 1;

285

}

286

}

```

#### 3.10 Sample program list "phy.c" (8)

```

287

288

* ID

289

* Outline

: Obtaining the register value from the PHY module

*_____

290

* Include

291

292

*_____

293

* Declaration : static void mii_reg_read (unsigned short *data);

294

*_____

295

* Description : Obtains the value of the PHY module register bit by bit.

296

: Signals are input/output in accord with the following conditions;

297

: MDC-high pulse width:160 ns (min)

298

: MDC-low pulse width:160 ns (min)

299

: MDC-cycle time: 400 ns (min)

300

: MDIO-output delay time (from PHY): 300 ns (max).

301

*_____

302

* Argument

: unsigned short *data ; O : Address where obtained values are to be stored

303

*_____

* Return Value : void

304

305

*_____

306

* Note

: The wait time may require adjustment to suit the system in use.

307

308

static void mii_reg_read (unsigned short *data)

309

{

310

int i,j;

311

unsigned short reg_data;

312

313

/* Data are read in one bit at a time */

314

reg_data = 0;

315

for (i=16; i>0; i--){

316

for(j=MDC_WAIT; j>0; j--){

317

EtherC.PIR.LONG = 0x0000000;

318

}

for(j=MDC_WAIT; j>0; j--){

319

320

EtherC.PIR.LONG = 0x0000001;

321

}

322

reg_data <<= 1;

323

reg_data |= (EtherC.PIR.LONG & 0x0000008) >> 3; /* MDI read */

324

325

for(j=MDC_WAIT; j>0; j--){

EtherC.PIR.LONG = 0x00000001;

326

327

}

328

for(j=MDC_WAIT; j>0; j--){

329

EtherC.PIR.LONG = 0x0000000;

330

}

331

}

332

*data = reg_data;

333 }

```

#### 3.11 Sample program list "phy.c" (9)

```

334

* ID

335

:

336

* Outline

: Setting of a value in a PHY module register

*_____

337

* Include

338

:

339

*_____

340

* Declaration : static void mii_reg_write (unsigned short data );

341

*_____

342

* Description : The value of the PHY module register is set one bit at a time.

*_____

343

344

* Argument : unsigned short data ; I : The value to be set in the register

345

*_____

346

* Return Value : void

347

*_____

* Note : The wait time may require adjustment to suit the system in use.

348

349

350

static void mii_reg_write (unsigned short data)

351 {

int i;

352

353

354

/* Data are written one bit at a time.*/

for(i=16; i>0; i--){

355

356

if( (data & 0x8000) == 0 ) {

357

mii_write_0();

358

}

359

else {

360

mii_write_1();

361

}

362

data <<= 1;

363

}

364 }

```

#### 3.12 Sample program list "phy.c" (10)

```

365

366

* ID

:

367

* Outline

: Bus release for access to the register of the PHY module

*_____

368

* Include

369

:

370

*_____

371

* Declaration : static void mii_z (void);

372

*_____

373

* Description : Reading is selected as the direction of access to the PHY module.

374

: Signals are input/output in accord with the following conditions;

375

*

: MDC-high pulse width: 160 ns (min)

376

: MDC-low pulse width: 160 ns (min)

377

+

: MDC-cycle time: 400 ns (min)

: MDIO-setup time: 10 ns (min)

378

379

: MDIO-hold time: 10 ns (min).

380

*_____

* Argument

381

: void

*_____

382

* Return Value : void

383

384

*_____

385

* Note

: The wait time may require adjustment to suit the system in use.

386

387 static void mii_z (void)

388 {

int j;

389

for(j=MDC_WAIT; j>0; j--){

390

391

EtherC.PIR.LONG = 0x0000000;

392

}

for(j=MDC_WAIT; j>0; j--){

393

394

EtherC.PIR.LONG = 0x00000001;

395

}

for(j=MDC_WAIT; j>0; j--){

396

397

EtherC.PIR.LONG = 0x0000001;

398

}

for(j=MDC_WAIT; j>0; j--){

399

400

EtherC.PIR.LONG = 0x0000000;

401

}

402 }

```

#### 3.13 Sample program list "phy.c" (11)

```

403

* ID

404

:

405

* Outline

: Output of the TA(10) bits for access to the register of the PHY module

*_____

406

* Include

407

:

408

*_____

409

* Declaration : static void mii_tal0 (void);

*_____

410

411

* Description : Outputs 1 or 0 to the MII management interface of the PHY module.

412

*_____

: void

413

* Argument

*_____

414

415

* Return Value : void

416

*_____

* Note

417

:

418

419

static void mii_tal0 (void)

420

{

421

mii_write_1();

422

mii_write_0();

423

}

```

#### 3.14 Sample program list "phy.c" (12)

```

424

* ID

425

426

* Outline

: Output of one bit (1) during access to the register of the PHY module

*_____

427

* Include

428

:

429

*_____

430

* Declaration : static void mii_write_1 (void);

*_____

431

432

* Description : 1 is output to the MII management interface of the PHY module.

433

: Signals are output in accord with the following conditions;

434

*

: MDC-high pulse width: 160 ns (min)

: MDC-low pulse width:160 ns (min)

435

436

+

: MDC-cycle time: 400 ns (min)

437

: MDIO-setup time:10 ns (min)

438

: MDIO-hold time:10 ns (min)

439

*_____

* Argument

440

: void

*_____

441

* Return Value : void

442

443

*_____

444

* Note

: The wait time may require adjustment to suit the system in use.

445

446 static void mii_write_1 (void)

447 {

int j;

448

for(j=MDC_WAIT; j>0; j--){

449

450

EtherC.PIR.LONG = 0x0000006;

451

}

for(j=MDC_WAIT; j>0; j--){

452

453

EtherC.PIR.LONG = 0x00000007;

454

}

for(j=MDC_WAIT; j>0; j--){

455

456

EtherC.PIR.LONG = 0x0000007;

457

}

for(j=MDC_WAIT; j>0; j--){

458

EtherC.PIR.LONG = 0 \times 00000006;

459

460

}

461 }

```

#### 3.15 Sample program list "phy.c" (13)

```

462

463

* ID

464

* Outline

: Output of one bit (0) during access to the register of the PHY module

*_____

465

* Include

466

:

467

*_____

468

* Declaration : static void mii_write_0 (void);

*_____

469

470

* Description : 0 is output to the MII management interface of the PHY module.

471

: Signals are output in accord with the following conditions;

472

*

: MDC-high pulse width: 160 ns (min)

473

: MDC-low pulse width:160 ns (min)

474

: MDC-cycle time: 400 ns (min)

475

: MDIO-setup time:10 ns (min)

476

: MDIO-hold time:10 ns (min)

477

*_____

478

* Argument

: void

*_____

479

* Return Value : void

480

481

*_____

482

* Note

: The wait time may require adjustment to suit the system in use.

483

484 static void mii_write_0 (void)

485 {

int j;

486

for(j=MDC_WAIT; j>0; j--){

487

488

EtherC.PIR.LONG = 0x0000002;

489

}

for(j=MDC_WAIT; j>0; j--){

490

491

EtherC.PIR.LONG = 0x0000003;

492

}

for(j=MDC_WAIT; j>0; j--){

493

494

EtherC.PIR.LONG = 0x0000003;

495

}

for(j=MDC_WAIT; j>0; j--){

496

EtherC.PIR.LONG = 0x0000002;

497

498

}

499

}

500 /* End of File */

```

```

3.16 Sample program list "phy.h" (1)

```

```

1

2

DISCLAIMER

3

This software is supplied by Renesas Electronics Corporation and is only

4

intended for use with Renesas products. No other uses are authorized.

5

б

7

*

This software is owned by Renesas Electronics Corporation and is protected under

8

all applicable laws, including copyright laws.

9

10

*

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11

REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

12

*

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

*

13

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

*

DISCLAIMED.

15

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

16

ELECTRONICS CORPORATION NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

17

18

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

19

*

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

20

21

2.2

* Renesas reserves the right, without notice, to make changes to this

software and to discontinue the availability of this software.

23

By using this software, you agree to the additional terms and

24

25

conditions found by accessing the following link:

26

http://www.renesas.com/disclaimer

27

28

* Copyright (C) 2007(2010) Renesas Electronics Corporation. All rights reserved.

*""FILE COMMENT""********* Technical reference data ******************************

29

System Name : SH7671 Sample Program

30

File Name : phy.h

31

Abstract

32

: Example of Setting for Automatic Negotiation by Ethernet PHY-LSI

33

Version : 1.00.01

* Device

: SH7671

34

* Tool-Chain : High-performance Embedded Workshop (Ver.4.03.00).

35

*

36

: C/C++ compiler package for the SuperH RISC engine family

37

:

(Ver.9.01 Release01).

* OS

38

: None

H/W Platform: M3A-HS71(CPU board)

39

40

Description :

41

* History

42

: Jul.04,2007 ver.1.00.00

*

: May 12,2010 ver.1.00.01 Changed the company name and device name

43

44

```

#### Sample program list "phy.h" (2) 3.17

| 45 | #ifndef _PHY_H                       |

|----|--------------------------------------|

| 46 | #define _PHY_H                       |

| 47 |                                      |

| 48 | #define NEGO_FAIL 0                  |

| 49 | #define HALF_10M 1                   |

| 50 | #define FULL_10M 2                   |

| 51 | #define HALF_TX 3                    |

| 52 | #define FULL_TX 4                    |

| 53 |                                      |

| 54 | <pre>int phy_autonego( void );</pre> |

| 55 |                                      |

| 56 | #endif                               |

| 57 |                                      |

| 58 | /* End of File */                    |

|    |                                      |

#### 4. References

- Software Manual SH-2A/SH2A-FPU Software Manual Rev. 3.00 The latest version of the software manual can be downloaded from the Renesas Electronics website.

- Hardware Manual SH7670 Group Hardware Manual Rev. 2.00 The latest version of the hardware user's manual can be downloaded from the Renesas Electronics website.

#### Website and Support

Renesas Electronics Website http://www.renesas.com/

Inquiries

http://www.renesas.com/inquiry

All trademarks and registered trademarks are the property of their respective owners.

# **Revision Record**

|      |           | Descript | ion                                                                     |

|------|-----------|----------|-------------------------------------------------------------------------|

| Rev. | Date      | Page     | Summary                                                                 |

| 1.00 | Dec.24.08 | —        | First edition issued                                                    |

| 1.01 | Oct.15.10 |          | Changed the sample program ( AC Switching Characteristics are removed ) |

# General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

- 1. Handling of Unused Pins

- Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do not access

these addresses; the correct operation of LSI is not guaranteed if they are accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

#### Notice

1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application categorized as "Specific" or for which it is not intended without the prior written consent of Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics graduat" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronics appliances; machine tools;

- personal electronic equipment; and industrial robots. "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

Refer to "http://www.renesas.com/" for the latest and detailed information

#### SALES OFFICES

#### **Renesas Electronics Corporation**

http://www.renesas.com

Renesas Electronics America Inc. 2880 Scott Boulevard Santa Clara, CA 95050-2554, U.S.A. Tel: +1-408-588-6000, Fax: +1-408-588-6130 Renesas Electronics Canada Limited 1101 Nicholson Road, Newmarkeit, Ontario L3Y 9C3, Canada Tel: +1-905-989-5441, Fax: +1-905-989-3220 Renesas Electronics Europe Limited Dukes Meadow, Millozard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1528-585-100, Fax: +44-1528-585-900 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Dusseldorf, Germany Tel: +49-211-6503-0, Fax: +44-1528-585-900 Renesas Electronics Curope Chinal Co., Ltd. 7th Floor, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100083, P.R.China Tel: +86-21-55, Fax: +86-10-8235-7679 Renesas Electronics (Shanghal) Co., Ltd. Unit 204, 205, AZIA Center, No.1233 Lujiazul Ring Fd., Pudong District, Shanghai 200120, China Tel: +86-27-587-1818, Fax: +86-22-6887-7858 Renesas Electronics Hong Kong Limited Unit 1201-1613, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +86-24-175-9800, Fax: +885-2886-9022/9044 Renesas Electronics Taiwan Co., Ltd. Tr, No. 363 Fu Shing North Road Taipei, Taiwan, R.O.C. Tel: +882-28175-9900, Fax: +885-2886-9022/9044 Renesas Electronics Taiwan Co., Ltd. 1 harbourFront Avenue, #06-10, keppel Bay Tower, Singapore 098632 Tel: +65-213-0200, Fax: +885-28175-9670 Renesas Electronics Taiwan Co., Ltd. 1 harbourFront Avenue, #06-10, keppel Bay Tower, Singapore 098632 Tel: +65-213-0200, Fax: +885-28175-9670 Renesas Electronics Taiwan Co., Ltd. 1 harbourFront Avenue, #06-10, keppel Bay Tower, Singapore 098632 Tel: +65-213-0200, Fax: +885-298-001 Tel: +60-3795-9390, Fax: +805-29850, Fax: +805-29850, Fax: 1 Hey -55-9390, Fax: +805-29850, Fax: +805-29850, Fax: 1 Hey -72 Cy Veoksam-Dong, Kangnam-Ku, Seoul 135-080, Korea Tel: +62-2-730 Fax: +700-792 Yeoksam-Dong, Kangnam-Ku, Seoul 135-080, Korea Tel: +22-258-3737, Fax: +82-2-558-5141