# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **SH7262/SH7264 Group**

# Example of Initialization

# **Summary**

This application note gives an example of configuration items to activate the SH7262/SH7264 Microcomputers.

# **Target Device**

SH7264 MCU (In this document, SH7262/SH7264 are described as "SH7264".)

#### **Contents**

| 1. | Introduction           | 2    |

|----|------------------------|------|

| 2. | Applications           | 3    |

| 3. | Sample Program Listing | 7    |

| 4. | References             | . 28 |

#### 1. Introduction

#### 1.1 Specifications

Configure the clock pulse generator (CPG), bus state controller (BSC), pin function controller (PFC), and cache after the reset is canceled.

#### 1.2 Modules Used

- Clock pulse generator (CPG)

- Bus state controller (BSC)

- Pin Function Controller (PFC)

- Cache

#### 1.3 Applicable Conditions

MCU SH7262/SH7264

Operating Frequency Internal clock: 144 MHz

Bus clock: 72 MHz

Peripheral clock: 36 MHz

Integrated

Development

Renesas Technology Corp.

Environment

High-performance Embedded Workshop Ver.4.07.00

C compiler Renesas Technology SuperH RISC engine Family

C/C++ compiler package Ver.9.03 Release 00

Compiler options Default setting in the High-performance Embedded Workshop

(-cpu=sh2afpu -fpu=single

-object="\$(CONFIGDIR)\\$(FILELEAF).obj" -debug -gbr=auto -chgincpath -errorpath -global\_volatile=0 -opt\_range=all -infinite loop=0 -del vacant loop=0 -struct alloc=1 -nologo)

#### 1.4 Related Application Note

Refer to the related application notes as follows:

- SH7262/SH7264 Group SDRAM Interface Setting

- SH7262/SH7264 Group Connecting the NOR Flash Memory

#### 2. Applications

Configuration program for the minimum hardware setup is required to execute the main function created in C code. This application note describes the configuration example for the configuration program.

All of the SH7264 application notes assume to use the sample program described in this application note as the configuration program.

## 2.1 Sample Program

The configuration program consists of several source files such as the resetprg.c, describing the PowerON\_Reset\_PC function, and the hwsetup.c, describing the hardware setup function. Main source files are as follows:

#### · resetprg.c

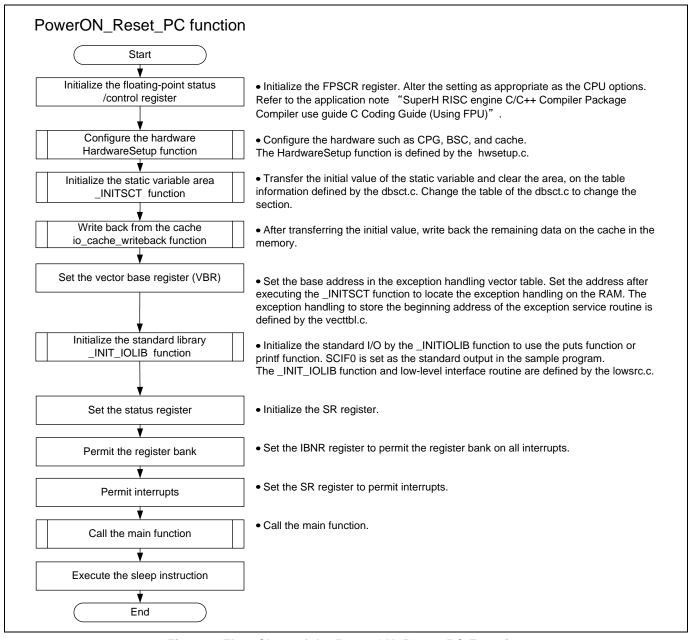

This is a source file created on the file automatically generated by the High-performance Embedded Workshop, and describes the PowerON\_Reset\_PC function. The PowerON\_Reset\_PC function is initially executed after the reset is canceled. Beginning address of the function is set in the reset vector defined by the vecttbl.c. Figure 1 shows the flow chart of the PowerON\_Reset\_PC function.

#### • hwsetup.c

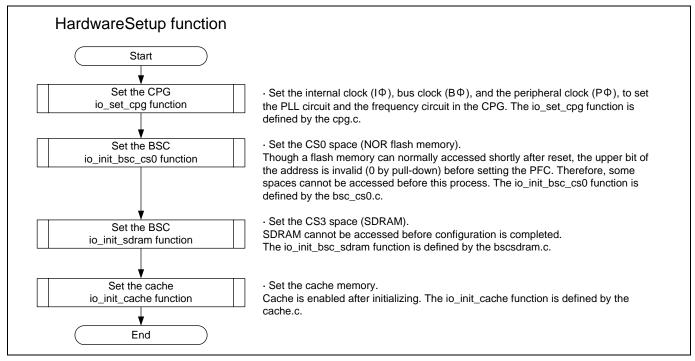

This source file describes the HardwareSetup function called by the PowerON\_Reset\_PC function. The HardwareSetup function calls the function to set the CPG, BSC, and cache to configure the hardware at minimum requirements.

Figure 2 shows the flow chart of the HardwareSetup function.

Figure 1 Flow Chart of the PowerON\_Reset\_PC Function

Figure 2 Flow Chart of the HardwareSetup Function

## 2.2 Setting in the Sample Program

Table 1 shows the setting in the sample program.

**Table 1 Sample Program Setting**

| Module | Setting                                                     |  |  |

|--------|-------------------------------------------------------------|--|--|

| FPU    | Single-precision                                            |  |  |

| FFO    | Round to zero                                               |  |  |

|        | Internal clock: 144 MHz                                     |  |  |

| CPG    | Bus clock: 72 MHz                                           |  |  |

| CFG    | Peripheral clock: 36 MHz                                    |  |  |

|        | (Clockin = 18 MHz)                                          |  |  |

|        | CS0: Flash memory                                           |  |  |

|        | Data bus width: 16 bits                                     |  |  |

|        | Number of access wait cycles: 6                             |  |  |

| BSC    | CS3: SDRAM                                                  |  |  |

| BSC    | Data bus width: 16 bits                                     |  |  |

|        | Row address bits: 12                                        |  |  |

|        | Column address bits: 9                                      |  |  |

|        | CAS latency: 2 cycles                                       |  |  |

| F.C.   | Sets the address bus, data bus, and bus control pin used in |  |  |

| PFC    | the CS0 and CS3 spaces.                                     |  |  |

| acho   | Instruction cache enabled                                   |  |  |

| Cache  | Operand cache enabled                                       |  |  |

|        | Set as the standard output                                  |  |  |

| SCIF   | Channel 0                                                   |  |  |

| SCIF   | Asynchronous, 8-bit data, no parity, 1 stop bit             |  |  |

|        | • 57600 bps                                                 |  |  |

#### 2.3 Notes on Using the Sample Program

- The SDRAM must be initialized before being accessed.

- The sample program uses the SDRAM space after configuring the BSC. When using the SDRAM that is not configured, the sample program does not work correctly.

- Do not locate the S section (the stack space) on the SDRAM.

- The initial value of the stack pointer (R15) is set as the value in the reset vector (End address of the S section + 1). The sample program locates the S section on the internal memory. When locating the S section on the SDRAM, the sample program accidentally accesses the SDRAM that is not configured upon calling the function in the configuration program.

- Access the static variable area after executing the \_INITSCT function.

The static variable area in C code is initialized by executing the \_INITSCT function. When accessing the static variable area before executing the function, the value is undetermined.

#### 3. Sample Program Listing

#### 3.1 Supplement to the Sample Program

As the capacity of the SH7264 large-capacity internal RAM varies as 1 MB or 640 KB, depending on the MCU type, the section alignment and register setting must be partly altered. To support both MCU types, this application note provides two types of sample programs (workspaces) for 1-MB RAM and 640-KB RAM.

As the MCU with 640-KB RAM must be write-enabled before writing data in the data-retention RAM, the System control register 5 (SYSCR5) is set to write-enable the RAM in the sample program for 640-KB RAM.

Review your product and use the appropriate workspace.

#### 3.2 Sample Program Listing "resetprg.c" (1/3)

```

DISCLAIMER

This software is supplied by Renesas Technology Corp. and is only

5

intended for use with Renesas products. No other uses are authorized.

6

7

This software is owned by Renesas Technology Corp. and is protected under

8

all applicable laws, including copyright laws.

9

10

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

13

14

DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

* TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

17

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

18

19

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

2.0

21

\mbox{\scriptsize \star} \mbox{\scriptsize Renesas} reserves the right, without notice, to make changes to this

22

* software and to discontinue the availability of this software.

24

* By using this software, you agree to the additional terms and

25

conditions found by accessing the following link:

26

http://www.renesas.com/disclaimer

*******************

27

* Copyright (C) 2008(2009). Renesas Technology Corp., All Rights Reserved.

28

*""FILE COMMENT""******* Technical reference data ******************************

29

* System Name : SH7264 Sample Program

* File Name : resetprg.c

31

* Abstract : Reset Program

32

* Version : 1.01.00

33

* Device : SH7262/SH7264

34

* Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

35

36

: C/C++ compiler package for the SuperH RISC engine family

37

(Ver.9.03 Release00).

* OS

38

: None

* H/W Platform: M3A-HS64G50(CPU board)

39

40

Description :

********************

41

* History

42

: Dec.03,2008 Ver.1.00.00

: Jun.29,2009 Ver.1.01.00 Changed FILE FORMAT

43

```

#### 3.3 Sample Program Listing "resetprg.c" (2/3)

```

#include <machine.h>

46

#include <_h_c_lib.h>

47

#include "stacksct.h"

48

#include "iodefine.h"

49

50

#define FPSCR_Init 0x00040001

51

52

#define SR_Init 0x000000F0

53

#define INT_OFFSET 0x10

54

55

extern unsigned int INT_Vectors;

56

void PowerON Reset PC(void);

57

void Manual_Reset_PC(void);

58

59

extern void main(void);

60

extern void HardwareSetup(void);

61

extern void io_cache_writeback(void);

62

extern void _INIT_IOLIB(void);

63

64

66

//extern void srand(unsigned int); // Remove the comment when you use rand()

// Remove the comment when you use strtok()

67

//extern char * slptr;

68

69

/*==== Switch section name to ResetPRG ====*/

70

#pragma section ResetPRG

71

72

/*==== Specify the entry function ====*/

73

#pragma entry PowerON_Reset_PC

74

75

76

77

* Outline

: CPU initialization function

79

: iodefine.h

81

* Declaration : void PowerON_Reset_PC(void);

82

*_____

83

* Description : It is the CPU initialization process to register the power on

84

: reset exception vector table.

85

: This function is firstly executed after power on reset.

86

: Enable the processes that are commented depending on its needs.

87

88

* Argument

: void

90

* Return Value : void

91

92

93

```

## 3.4 Sample Program Listing "resetprg.c" (3/3)

```

void PowerON_Reset_PC(void)

94

95

96

set_fpscr(FPSCR_Init);

97

98

/*==== HardwareSetup function====*/

99

HardwareSetup();

// Use Hardware Setup

100

/*==== B and D sections initialization ====*/

101

102

_INITSCT();

103

io_cache_writeback();

104

/*==== Vector base register (VBR) setting ====*/

105

set_vbr((void *)((char *)&INT_Vectors - INT_OFFSET));

106

107

// Use stdio I/O

108

_INIT_IOLIB();

109

110

//errno=0;

// Remove the comment when you use errno

111

//srand(1);

// Remove the comment when you use rand()

112

//_s1ptr=NULL;

// Remove the comment when you use strtok()

113

114

/*==== Status register setting ====*/

set_cr(SR_Init);

116

nop();

117

118

/* ==== Bank number register setting ==== */

119

INTC.IBNR.BIT.BE = 0x01; /* Use the register bank in all interrupts */

120

121

/* ==== Interrupt mask level change ==== */

122

set_imask(0);

123

124

/*=== Function call of main function ====*/

125

main();

127

/*==== sleep instruction execution ====*/

128

sleep();

129

}

130

131

... additional information deleted ...

```

## 3.5 Sample Program Listing "hwsetup.c" (1/4)

```

1

2

DISCLAIMER

3

* This software is supplied by Renesas Technology Corp. and is only

4

5

intended for use with Renesas products. No other uses are authorized.

6

7

* This software is owned by Renesas Technology Corp. and is protected under

8

all applicable laws, including copyright laws.

10

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

12

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

13

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

* TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

20

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

* Renesas reserves the right, without notice, to make changes to this

23

software and to discontinue the availability of this software.

24

* By using this software, you agree to the additional terms and

25

* conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

27

************************

2.8

* Copyright (C) 2009. Renesas Technology Corp., All Rights Reserved.

29

*""FILE COMMENT""******* Technical reference data ******************************

30

* System Name : SH7264 Sample Program

31

File Name : hwsetup.c

32

* Abstract : Hardware initialization function

33

* Version : 1.01.00

* Device : SH7262/SH7264

34

35

* Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

36

: C/C++ compiler package for the SuperH RISC engine family

37

(Ver.9.03 Release00).

38

: None

39

* H/W Platform: M3A-HS64G50(CPU board)

40

* Description:

***************************

41

History

: Jan.13,2009 Ver.1.00.00

43

: Jun.29,2009 Ver.1.01.00 Changed FILE FORMAT

44

45

#include "iodefine.h"

```

#### 3.6 Sample Program Listing "hwsetup.c" (2/4)

```

/* ==== Prototype declaration ==== */

47

void HardwareSetup(void);

48

49

/* ==== referenced external Prototype declaration ==== */

50

extern void io_set_cpg(void);

51

extern void io_init_bsc_cs0(void);

52

extern void io_init_sdram(void);

53

extern void io_init_cache(void);

54

static void init_puram_section(void);

55

void set_acswr(void);

56

57

#pragma section ResetPRG

58

59

* ID

60

: Hardware initialization function

61

*-----

62

* Include

: iodefine.h

*_____

63

* Declaration : void HardwareSetup(void);

65

*_____

* Description : The initial settings of CPG, PFC, and BSC (Flash memory

67

: access control and SDRAM initialization) are processed.

68

69

* Argument

: void

70

71

* Return Value : void

72

73

: None

74

75

void HardwareSetup(void)

76

77

/*====CPG setting====*/

78

io_set_cpg();

79

/*====CSO initialization====*/

80

81

io_init_bsc_cs0();

82

83

/*====SDRAM area initialization====*/

84

/* ---- Switches AC characteristics ---- */

85

init_puram_section();

set_acswr();

87

io_init_sdram();

89

/*====Cache setting====*/

91

io_init_cache();

92

}

93

```

## 3.7 Sample Program Listing "hwsetup.c" (3/4)

```

* ID

95

: URAM section transfer from ROM to internal RAM

96

*-----

98

: iodefine.h

*_____

99

* Declaration : static void init_puram_section(void);

100

101

*-----

\mbox{\scriptsize *} Description \mbox{\scriptsize :} Transfers the program in the URAM section from

102

103

: ROM to internal RAM.

104

: Transfer must be executed before setting the SDRAM.

: This function transfers the URAM section separately before

105

106

: initializing other sections.

107

108

* Argument

: void

109

*-----

* Return Value : void

110

111

112 * Note : None

113

static void init_puram_section(void)

115

116

unsigned long *src, *end, *dst;

117

118

src = (unsigned long *)__sectop("PURAM");

119

end = (unsigned long *)__secend("PURAM");

120

dst = (unsigned long *)__sectop("RPURAM");

121

122

while(src < end){

*dst++ = *src++;

124

}

125

}

```

#### 3.8 Sample Program Listing "hwsetup.c" (4/4)

```

* ID

127

: URAM section transfer from ROM to internal RAM

128

*-----

129

130

: iodefine.h

*-----

131

132

* Declaration : static void init_puram_section(void);

*_____

\mbox{\scriptsize *} Description \mbox{\scriptsize :} Transfers the program in the URAM section from

134

135

: ROM to internal RAM.

136

: Transfer must be executed before setting the SDRAM.

: This function transfers the URAM section separately before

137

138

: initializing other sections.

139

140

* Argument

: void

141

*-----

* Return Value : void

142

143

144 * Note : None

145

static void init_puram_section(void)

147

148

unsigned long *src, *end, *dst;

149

150

src = (unsigned long *)__sectop("PURAM");

151

end = (unsigned long *)__secend("PURAM");

152

dst = (unsigned long *)__sectop("RPURAM");

153

154

while(src < end){

*dst++ = *src++;

156

}

157

}

```

#### 3.9 Sample Program Listing "cpg.c" for 1 MB (1/2)

```

2

DISCLAIMER

3

4

* This software is supplied by Renesas Technology Corp. and is only

5

intended for use with Renesas products. No other uses are authorized.

6

7

* This software is owned by Renesas Technology Corp. and is protected under

8

all applicable laws, including copyright laws.

9

10

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

13

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

2.0

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

22

* Renesas reserves the right, without notice, to make changes to this

23

* software and to discontinue the availability of this software.

24

* By using this software, you agree to the additional terms and

25

conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

27

28

* Copyright (C) 2008(2009). Renesas Technology Corp., All Rights Reserved.

*""FILE COMMENT""******** Technical reference data **********************

29

30

* System Name : SH7264 Sample Program

* File Name : cpg.c

31

32

Abstract : CPG setting process

33

* Version : 1.01.00

34

* Device : SH7262/SH7264

35

Tool-Chain : High-performance Embedded Workshop (Ver. 4.07.00).

36

: C/C++ compiler package for the SuperH RISC engine family

(Ver.9.03 Release00).

37

* OS

38

: None

39

H/W Platform: M3A-HS64G50(CPU board)

40

* Description:

**************************

41

42

* History : Oct.28,2008 Ver.1.00.00

: Jun.29,2009 Ver.1.01.00 Changed FILE FORMAT

44

45

#include "iodefine.h"

46

47

48

/* ==== Prototype Declaration ==== */

void io_set_cpg(void);

```

#### 3.10 Sample Program Listing "cpg.c" for 1 MB (2/2)

```

50

#pragma section ResetPRG

51

52

* ID :

53

* Outline : CPG settings

54

*-----

55

* Include

: iodefine.h

*-----

57

* Declaration : void io_set_cpg(void);

59

* Description : Clock pulse generator (CPG) is set to set to the internal clock

60

: (I Clock), peripheral clock (P Clock), bus clock (B Clock), and

61

: I Clock = 144MHz, B Clock = 72MHz, P Clock = 36MHz.

62

: This setting example is the case that the function's input clock

63

: is 18MHz and clock mode is 2.

64

65

* Argument

: void

66

*_____

67

* Return Value : void

68

69

: None

70

71

void io_set_cpg(void)

72

73

/* ==== CPG Setting ==== */

74

CPG.FRQCR.WORD = 0x1003u;

/* PLL1(x8),I:B:P= 8:4:2

75

* CKIO:Output at time usually,Output when bus right is

76

* opened, output at standby "L"

77

* Clockin = 18MHz, CKIO = 72MHz

78

* I Clock = 144MHz, B Clock = 72MHz,

79

* P Clock = 36MHz

80

81

83

/* ---- The clock of all modules is permitted. ---- */

84

CPG.STBCR3.BYTE = 0x02u; /* Port level is keep in standby mode

* /

85

/* IEBus, MTU2, SDHI0, SDHI1, A/D, [1], RTClock

* /

CPG.STBCR4.BYTE = 0x00u; /* SCIF0, SCIF1, SCIF2, SCIF3, SCIF4, SCIF5, SCIF6, SCIF7*/

86

87

CPG.STBCR5.BYTE = 0x10u; /* I2C30, I2C31, I2C32, [1], RCAN0, RCAN1, RSPI0, RSPI1 */

88

CPG.STBCR6.BYTE = 0x00u; /* SSI0, SSI1, SSI2, SSI3, CD-ROMDEC, SRC0, SRC1, USB */

89

CPG.STBCR7.BYTE = 0x2au; /* SIOF, RSPDIF, [1], VDC3, [1], CMT, [1], NAND

* /

CPG.STBCR8.BYTE = 0x7eu; /* PWM, [1], [1], [1], [1], [1], DECOMP

90

* /

91

92

93

94

/* End of File */

```

## 3.11 Sample Program Listing "cpg.c" for 640 KB (1/2)

```

2

DISCLAIMER

3

4

* This software is supplied by Renesas Technology Corp. and is only

5

intended for use with Renesas products. No other uses are authorized.

6

7

* This software is owned by Renesas Technology Corp. and is protected under

8

all applicable laws, including copyright laws.

9

10

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

2.0

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

22

* Renesas reserves the right, without notice, to make changes to this

* software and to discontinue the availability of this software.

24

* By using this software, you agree to the additional terms and

25

conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

27

28

* Copyright (C) 2009. Renesas Technology Corp., All Rights Reserved.

*""FILE COMMENT""******* Technical reference data ******************

29

30

* System Name : SH7264 Sample Program

* File Name : cpg.c

31

32

Abstract : CPG setting process

33

* Version : 1.00.00

34

* Device : SH7262(640KB)/SH7264(640KB)

35

Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

36

: C/C++ compiler package for the SuperH RISC engine family

37

(Ver.9.03 Release00).

* OS

38

: None

39

H/W Platform: M3A-HS64G60(CPU board)

40

* Description:

*************************

41

42

* History : Jun.30,2009 Ver.1.00.00

44

#include "iodefine.h"

45

46

47

/* ==== Prototype Declaration ==== */

48

void io_set_cpg(void);

49

```

#### 3.12 Sample Program Listing "cpg.c" for 640 KB (2/2)

```

#pragma section ResetPRG

51

52

* ID

:

53

* Outline : CPG settings

54

* Include

55

: iodefine.h

56

*-----

57

* Declaration : void io_set_cpg(void);

58

*-----

* Description : Clock pulse generator (CPG) is set to set to the internal clock

60

: (I Clock), peripheral clock (P Clock), bus clock (B Clock), and

61

: I Clock = 144MHz, B Clock = 72MHz, P Clock = 36MHz.

62

: This setting example is the case that the function's input clock

63

: is 18MHz and clock mode is 2.

64

65

* Argument

: void

66

67

* Return Value : void

68

: None

69

70

71

void io_set_cpg(void)

72

73

/* ==== CPG Setting ==== */

74

CPG.FRQCR.WORD = 0 \times 1003 u;

/* PLL1(x8), I:B:P= 8:4:2

75

* CKIO:Output at time usually,Output when bus right is

76

* opened, output at standby "L"

77

* Clockin = 18MHz, CKIO = 72MHz

78

* I Clock = 144MHz, B Clock = 72MHz,

79

* P Clock = 36MHz

80

* /

81

82

83

/* ---- The clock of all modules is permitted. ---- */

84

CPG.STBCR3.BYTE = 0x02u; /* Port level is keep in standby mode

* /

85

* /

/* IEBus, MTU2, SDHI0, SDHI1, A/D, [1], RTClock

86

CPG.STBCR4.BYTE = 0x00u; /* SCIF0, SCIF1, SCIF2, SCIF3, SCIF4, SCIF5, SCIF6, SCIF7*/

87

CPG.STBCR5.BYTE = 0x10u; /* I2C30, I2C31, I2C32, [1], RCAN0, RCAN1, RSPI0, RSPI1 */

88

CPG.STBCR6.BYTE = 0x00u; /* SSI0, SSI1, SSI2, SSI3, CD-ROMDEC, SRC0, SRC1, USB

*/

89

CPG.STBCR7.BYTE = 0x2au; /* SIOF, RSPDIF, [1], VDC3, [1], CMT, [1], NAND

* /

90

CPG.STBCR8.BYTE = 0x7eu; /* PWM, [1], [1], [1], [1], [1], DECOMP

* /

91

/* ---- Writing to large-capacity RAM is enabled. ---- */

93

CPG.SYSCR5.BYTE = 0x0fu;

94

95

96

/* End of File */

```

## 3.13 Sample Program Listing "bsc\_cs0.c" (1/3)

```

2

DISCLAIMER

3

4

* This software is supplied by Renesas Technology Corp. and is only

5

intended for use with Renesas products. No other uses are authorized.

6

7

* This software is owned by Renesas Technology Corp. and is protected under

8

all applicable laws, including copyright laws.

9

10

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11

* REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

* INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

13

14

* DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

* FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

* FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

2.0

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

21

2.2

* Renesas reserves the right, without notice, to make changes to this

23

* software and to discontinue the availability of this software.

24

* By using this software, you agree to the additional terms and

25

conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

27

28

* Copyright (C) 2008(2009). Renesas Technology Corp., All Rights Reserved.

*""FILE COMMENT""******* Technical reference data ******************

29

30

* System Name : SH7264 Sample Program

* File Name : bsc_cs0.c

31

32

Abstract : SH7264 Initial Settings

33

* Version : 1.01.00

34

* Device : SH7262/SH7264

35

Tool-Chain : High-performance Embedded Workshop (Ver. 4.07.00).

36

: C/C++ compiler package for the SuperH RISC engine family

(Ver.9.03 Release00).

37

* OS

38

: None

39

H/W Platform: M3A-HS64G50(CPU board)

40

* Description:

**************************

41

42

* History : Dec.11,2008 Ver.1.00.00

: Jun.29,2009 Ver.1.01.00 Changed FILE FORMAT

44

#include "iodefine.h"

46

/* CS0 PAGEMODE setting */

47

//#define PAGEMODE

48

/* ==== Prototype Declaration ==== */

void io_init_bsc_cs0(void);

```

## 3.14 Sample Program Listing "bsc\_cs0.c" (2/3)

```

#pragma section ResetPRG

51

52

* ID

53

* Outline : CSO setting

* Include

: iodefine.h

55

*-----

56

57

* Declaration : void io_init_bsc_cs0(void);

58

*_____

59

* Description : Pin function controller (PFC) and bus state controller (BSC)

60

: are set, and the access timing to the Flash Memory of CSO space

61

: is set.

62

: The PFC setting is set by bit manipulation not to change the PFC

63

: set value which is set by other process.

64

65

* Argument

: void

66

*_____

67

* Return Value : void

68

69

: None

70

71

void io_init_bsc_cs0(void)

72

73

/* ==== PFC settings ==== */

74

PORT.PBCR5.BIT.PB21MD = 1u; /* Set A21 */

75

PORT.PBCR5.BIT.PB20MD = 1u; /* Set A20 */

76

PORT.PCCRO.BIT.PC3MD = 1u; /* Set WE0# */

77

78

79

#ifdef PAGEMODE

80

/* ==== CSOWCR settings ==== */

82

BSC.CSOWCR.BROM_ASY.LONG = 0x002303c0ul;

83

/* Number of Burst: 4-4 or 2-4-2

84

/* Number of Burst Wait Cycles: 3 cycles */

85

/* Number of Access Wait Cycles: 8 cycles */

86

87

88

89

/* ==== CS0BCR settings ==== */

90

BSC.CSOBCR.LONG = 0x30001400ul;

91

/* Idle Cycles between Write-read Cycles */

92

/* and Write-write Cycles: 4 idle cycles */

93

/* Type: Burst ROM (ASY)

* /

/* Data Bus Size: 16-bit

* /

95

96

#else /* PAGEMODE */

97

```

# 3.15 Sample Program Listing "bsc\_cs0.c" (3/3)

```

98

/* ==== CSOWCR settings ==== */

BSC.CSOWCR.NORMAL.LONG = 0x00000b41ul;

100

101

/* Number of Delay Cycles from Address, */

/* CS0# Assertion to RD#,WEn Assertion */

102

103

/* : 1.5 cycles

/* Number of Access Wait Cycles: 6 cycles

104

105

/* Delay Cycles from RD,WEn# negation to */

106

/* Address, CSn# negation: 1.5 cycles

107

108

/* ==== CS0BCR settings ==== */

109

110

BSC.CSOBCR.LONG = 0x12400400ul;

111

/* Idle Cycles between Write-read Cycles */

112

/* and Write-write Cycles : 1 idle cycle */

/* and read-write Cycles : 1 idle cycle */

113

/* Data Bus Size: 16-bit

114

115

116

#endif /* PAGEMODE */

117

118

119 /* End of File */

120

```

#### 3.16 Sample Program Listing "bscsdram.c" (1/3)

```

2

DISCLAIMER

3

This software is supplied by Renesas Technology Corp. and is only

5

intended for use with Renesas products. No other uses are authorized.

6

7

This software is owned by Renesas Technology Corp. and is protected under

8

all applicable laws, including copyright laws.

9

10

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11

REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

13

14

DISCLAIMED.

15

16

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

2.0

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

22

* Renesas reserves the right, without notice, to make changes to this

software and to discontinue the availability of this software.

24

By using this software, you agree to the additional terms and

conditions found by accessing the following link:

26

* http://www.renesas.com/disclaimer

2.7

Copyright (C) 2008(2009). Renesas Technology Corp., All Rights Reserved.

29

*""FILE COMMENT""******* Technical reference data *******************************

* System Name : SH7264 Sample Program

File Name : bscsdram.c

31

32

Abstract : SH7264 Initial Settings

33

Version : 1.01.00

* Device

: SH7262/SH7264

Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

35

36

: C/C++ compiler package for the SuperH RISC engine family

(Ver.9.03 Release00).

37

38

* OS

: None

39

H/W Platform: M3A-HS64G50(CPU board)

40

* Description:

**************************

* History : Feb.02,2008 Ver.1.00.00

42

: Jun.29,2009 Ver.1.01.00 Changed FILE FORMAT

44

#include "iodefine.h"

46

/* ==== Macro name definition ==== */

47

/* The address when writing in a SDRAM mode register */

48

#define SDRAM_MODE

(*(volatile unsigned short *)(0xfffc5040))

49

/* ==== Prototype Declaration ==== */

50

void io_init_sdram(void);

```

# 3.17 Sample Program Listing "bscsdram.c" (2/3)

```

51

#pragma section ResetPRG

52

53

* ID :

54

* Outline : SDRAM 16 bit bus width connection settings

55

*-----

56

* Include

: iodefine.h

57

*_____

58

* Declaration : void io_init_sdram(void);

60

* Description : A connection setup to SDRAM of CS3 space.

: The PFC setting is set by bit manipulation not to change the PFC

61

62

: set value which is set by other process.

63

64

65

*-----

66

* Return Value : void

67

* Note : None

69

70

void io_init_sdram(void)

71

volatile int j = 133;

/* 200usec wait count */

72

73

74

/* ==== PFC settings ==== */

75

PORT.PCCR2.BIT.PC8MD = 1u;

/* CS3#

* /

76

/* CKE

PORT.PCCR1.BIT.PC7MD = 1u;

* /

77

PORT.PCCR1.BIT.PC6MD = 1u;

/* CAS#

78

PORT.PCCR1.BIT.PC5MD = 1u;

/* RAS#

* /

79

* /

PORT.PCCR1.BIT.PC4MD = 1u;

/* DQMU#

80

PORT.PCCR0.BIT.PC3MD = 1u;

/* DQML#

* /

PORT.PCCR0.BIT.PC2MD = 1u;

/* RD/WR# */

82

83

/* ==== 200us interval elapsed ? ==== */

84

while(j-- > 0){

85

/* wait */

86

}

87

88

/* ==== CS3BCR settings ==== */

89

BSC.CS3BCR.LONG = 0 \times 00004400ul;

90

91

Idle Cycles between Write-read Cycles

and Write-write Cycles : 0 idle cycles

93

Memory type :SDRAM

94

Data Bus Size : 16-bit

95

96

```

## 3.18 Sample Program Listing "bscsdram.c" (3/3)

```

/* ==== CS3WCR settings ==== */

98

BSC.CS3WCR.SDRAM.LONG = 0 \times 00000288aul;

99

100

Precharge completion wait cycles: 1 cycle

101

Wait cycles between ACTV command

102

and READ(A)/WRITE(A) command : 2 cycles

103

CAS latency for Area 3 : 2 cycles

104

Auto-precharge startup wait cycles : 1 cycle

105

Idle cycles from REF command/self-refresh

106

Release to ACTV/REF/MRS command

107

: 5 cycles

108

109

110

111

/* ==== SDCR settings ==== */

112

BSC.SDCR.LONG = 0 \times 000000809ul;

113

114

Refresh Control : Refresh

115

RMODE : Auto-refresh is performed

116

BACTV : Auto-precharge mode

117

Row address for Area 3 : 12-bit

118

Column Address for Area 3 : 9-bit

119

120

121

/* ==== RTCOR settings ==== */

122

BSC.RTCOR.LONG = 0xa55a0046ul;

123

15.625us/222ns

124

= 70(0x46)cycles per refresh

125

126

127

128

129

/* ==== RTCSR settings ==== */

131

BSC.RTCSR.LONG = 0xa55a0010ul;

132

133

Initialization sequence start

134

Clock select B-phy/16

135

Refresh count :Once

136

137

138

/* ==== Written in SDRAM Mode Register ==== */

139

SDRAM_MODE = 0;

140

The writing data is arbitrary

141

SDRAM mode register setting CS3 space

142

Burst read (burst length 1)./Burst write

143

144

145

/* End of File */

```

## 3.19 Sample Program Listing "cache.c" (1/3)

```

2

DISCLAIMER

3

This software is supplied by Renesas Technology Corp. and is only

5

intended for use with Renesas products. No other uses are authorized.

6

7

This software is owned by Renesas Technology Corp. and is protected under

8

all applicable laws, including copyright laws.

9

10

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

11

REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

13

14

DISCLAIMED.

15

16

TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

17

TECHNOLOGY CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

2.0

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

22

Renesas reserves the right, without notice, to make changes to this

software and to discontinue the availability of this software.

24

By using this software, you agree to the additional terms and

25

conditions found by accessing the following link:

26

http://www.renesas.com/disclaimer

27

Copyright (C) 2008(2009). Renesas Technology Corp., All Rights Reserved.

29

*""FILE COMMENT""******* Technical reference data *******************************

System Name : SH7264 Sample Program

File Name : cache.c

31

32

Abstract : sample of cache register

33

Version : 1.01.00

Device

: SH7262/SH7264

Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

35

36

: C/C++ compiler package for the SuperH RISC engine family

37

(Ver.9.03 Release00).

38

* OS

: None

39

H/W Platform: M3A-HS64G50(CPU board)

40

* Description:

*************************

* History : Dec.03,2008 Ver.1.00.00

42

: Jun.29,2009 Ver.1.01.00 Changed FILE FORMAT

44

45

#include <machine.h>

46

#include "iodefine.h"

47

/* ==== Prototype Declaration ==== */

48

void io_init_cache(void);

49

int io_cache_writeback(void);

```

#### 3.20 Sample Program Listing "cache.c" (2/3)

```

50

#pragma section CACHE

/* It is placed in the CSO cache-disabled space */

51

* ID

53

: Cache initialization

* Outline

54

*_____

55

* Include

: iodefine.h

56

*_____

57

* Declaration : void io_init_cache(void);

59

* Description : Instruction/operand cache are flushed and enabled.

: The section name of this function is changed to be placed in

60

61

: the cache-disabled.

62

: When this function is used only in the state of interrupt level 15,

63

: the setting and clearing of interrupt mask need not be processed.

64

*-----

65

* Argument

: void

66

*_____

67

* Return Value : void

68

69

* Note

: None

70

71

void io_init_cache(void)

72

73

volatile unsigned long reg;

74

int mask;

75

76

/* ==== Interrupt mask setting ==== */

77

mask = get_imask();

78

set_imask(15);

/* Set to the level 15 */

79

80

/* ==== Cache register setting ==== */

81

CCNT.CCR1.LONG = 0x0909ul; /* Write back ON */

83

84

ICF=1:Instruction cache flushed

85

ICE=1:Instruction cache enabled

86

OCF=1:Operand cache flushed

87

OCE=1:Operand cache enabled

88

89

/* ==== Reading cache register ==== */

90

reg = CCNT.CCR1.LONG ;

92

/* ==== Clearing interrupt mask ==== */

set_imask(mask);

/* Set to the original level */

94

95

}

96

```

#### 3.21 Sample Program Listing "cache.c" (3/3)

```

97

98

* ID

* Outline : Write-back of cache

100

*_____

101

: iodefine.h

102

*_____

103

* Declaration : int io_cache_writeback(void);

104

*_____

105

* Description : All lines of operand cache are disabled, and the contents of

106

: cache memory are written back to the external memory.

107

: It has nothing to do with the write-through mode.

108

109

* Argument

: void

110

*_____

111

* Return Value : 0 : Normal completion

*-----

112

113

* Note

: None

114

115

int io_cache_writeback(void)

116

117

volatile unsigned long *arry;

unsigned int i,j;

118

119

int mask;

120

121

/* ==== Interrupt mask setting ==== */

122

mask = get_imask();

123

set_imask(15);

/* Set to the level 15 */

124

125

/* ==== All entries disabled ==== */

126

for(i=0u; i <4u; i++){

127

for(j=0u; j < 128u; j++){

128

/* ---- Creating an address array address ---- */

129

arry = (volatile unsigned long *)(0xf0800000 \mid (i << 11) \mid (j << 4));

130

/* ---- Write U=0 and V=0 in the address array ---- */

131

132

}

133

}

134

135

/* ==== Interrupt mask recovery ==== */

136

/* Set to the original level */

set_imask(mask);

137

138

return 0;

139

}

140

141

142

/* End of File */

143

```

#### 4. References

- Software Manual SH-2A/SH-2A-FPU Software Manual Rev. 3.00 (Download the latest version from the Renesas website.)

- Hardware Manual SH7262 Group, SH7264 Group Hardware Manual Rev. 2.00 (Download the latest version from the Renesas website.)

# **Website and Support**

Renesas Technology Website <a href="http://www.renesas.com/">http://www.renesas.com/</a>

Inquiries

http://www.renesas.com/inquiry csc@renesas.com

# **Revision History**

| _   | -   |      |          |

|-----|-----|------|----------|

| Des | cri | ntia | nn.      |

| レモコ |     | Nui  | <i>-</i> |

| Rev. | Date       | Page | Summary                             |

|------|------------|------|-------------------------------------|

| 1.00 | Mar.05, 09 | _    | First edition issued                |

| 1.01 | Oct.09, 09 | _    | Sample program for 640-KB RAM added |

All trademarks and registered trademarks are the property of their respective owners.

#### Notes regarding these materials

- 1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out

of the use of any information in this document, including, but not limited to, product data, diagrams, charts,

programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

© 2009. Renesas Technology Corp., All rights reserved.