## **RL78/I1D**

R01AN3528JJ0100 Rev.1.00

2017.01.31

CPU クロックの切り替えとスタンバイ設定(C言語編) CC-RL

## 要旨

本アプリケーションノートでは、RL78/IIDのCPUクロックの切り替えとスタンバイ設定(動作モードの切り替え)を説明します。

本アプリケーションでは、スイッチ入力により、CPU クロックと動作モードの切り替えを行います。5つのLED 点灯を制御し、CPU クロックの状態と動作モードを表します。

## 対象デバイス

**RL78/I1D**

本アプリケーションノートを他のマイコンへ適用する場合、そのマイコンの仕様にあわせて変更し、十分評価してください。

## 目次

| 1.    | 仕様       |                                              | . 4 |

|-------|----------|----------------------------------------------|-----|

| 1.1   | CPU      | クロックの切り替え                                    | . 7 |

| 1.1.1 |          | 高速オンチップ・オシレータ・クロックから中速オンチップ・オシレータ・クロックへの切り替え | . 8 |

| 1.1.2 | <u> </u> | 高速オンチップ・オシレータ・クロックから低速オンチップ・オシレータ・クロックへの切り替え | . 9 |

| 1.1.3 | 3        | 高速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え        | 10  |

| 1.1.4 | ļ        | 高速オンチップ・オシレータ・クロックからサブ・クロックへの切り替え            | 12  |

| 1.1.5 | 5        | 中速オンチップ・オシレータ・クロックから高速オンチップ・オシレータ・クロックへの切り替え | 13  |

| 1.1.6 | 3        | 中速オンチップ・オシレータ・クロックから低速オンチップ・オシレータ・クロックへの切り替え | 14  |

| 1.1.7 | 7        | 中速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え        | 15  |

| 1.1.8 | }        | 中速オンチップ・オシレータ・クロックからサブ・クロックへの切り替え            | 17  |

| 1.1.9 | )        | 低速オンチップ・オシレータ・クロックから高速オンチップ・オシレータ・クロックへの切り替え | 18  |

| 1.1.1 | 0        | 低速オンチップ・オシレータ・クロックから中速オンチップ・オシレータ・クロックへの切り替え | 19  |

| 1.1.1 | 1        | 低速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え        | 20  |

| 1.1.1 | 2        | 高速システム・クロックから高速オンチップ・オシレータ・クロックへの切り替え        |     |

| 1.1.1 | 3        | 高速システム・クロックから中速オンチップ・オシレータ・クロックへの切り替え        |     |

| 1.1.1 | 4        | 高速システム・クロックから低速オンチップ・オシレータ・クロックへの切り替え        |     |

| 1.1.1 |          | 高速システム・クロックからサブ・クロックへの切り替え                   |     |

| 1.1.1 | -        | サブ・クロックから高速オンチップ・オシレータ・クロックへの切り替え            |     |

| 1.1.1 | -        | サブ・クロックから中速オンチップ・オシレータ・クロックへの切り替え            |     |

| 1.1.1 |          | サブ・クロックから高速システム・クロックへの切り替え                   |     |

|       | -        | を認条件                                         |     |

|       |          | 崔認条件                                         |     |

|       |          |                                              |     |

|       |          | ドウエア説明                                       |     |

|       |          | ドウエア構成例                                      |     |

|       |          | <b>耑子一覧</b>                                  |     |

| 5.    | ソフ       | トウエア説明                                       | 31  |

|       |          | 既要                                           |     |

| 5.2   | オプ       | ション・バイトの設定一覧                                 | 34  |

| 5.3   | 変数-      | - 覧                                          | 34  |

| 5.4   | 関数       | (サブルーチン) 一覧                                  | 35  |

| 5.5   | 関数       | (サブルーチン) 仕様                                  | 37  |

| 5.6   | フロ-      | - チャート                                       | 47  |

| 5.6.1 |          | 初期化設定関数                                      | 47  |

| 5.6.2 | <u> </u> | システム関数                                       | 48  |

| 5.6.3 | 3        | 入出力ポート設定                                     | 49  |

| 5.6.4 | ļ        | クロック発生回路の設定                                  | 50  |

| 5.6.5 | 5        | 外部割り込みの設定                                    | 55  |

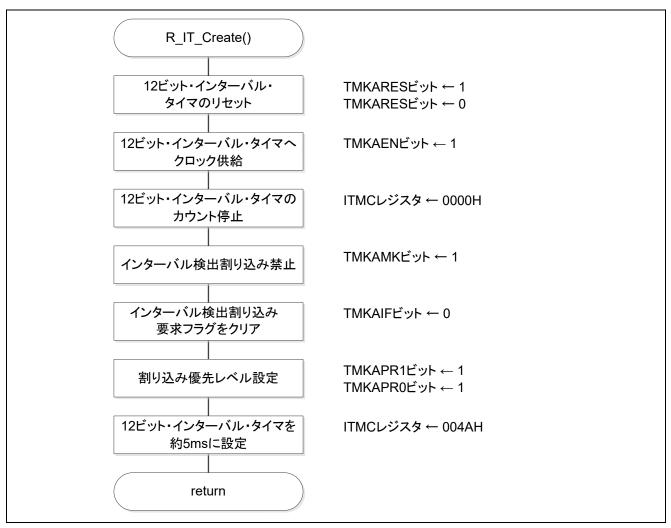

| 5.6.6 | 3        | 12 ビット・インターバル・タイマの設定                         | 57  |

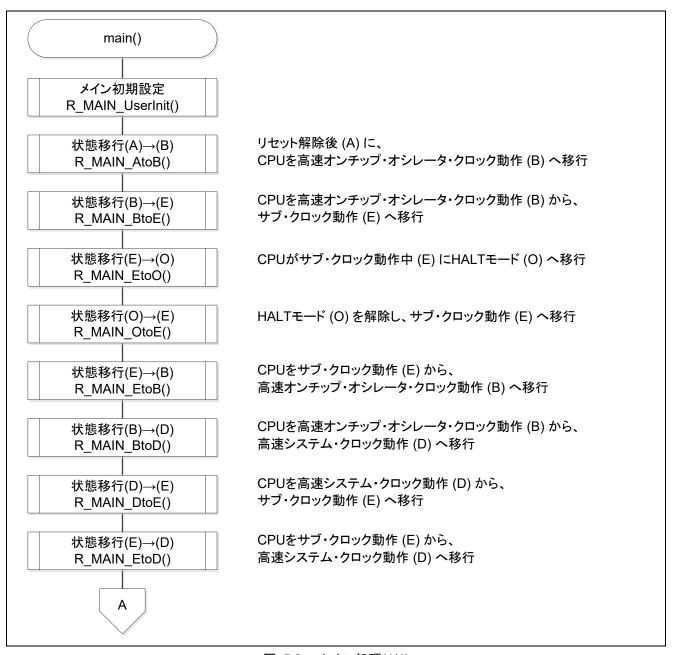

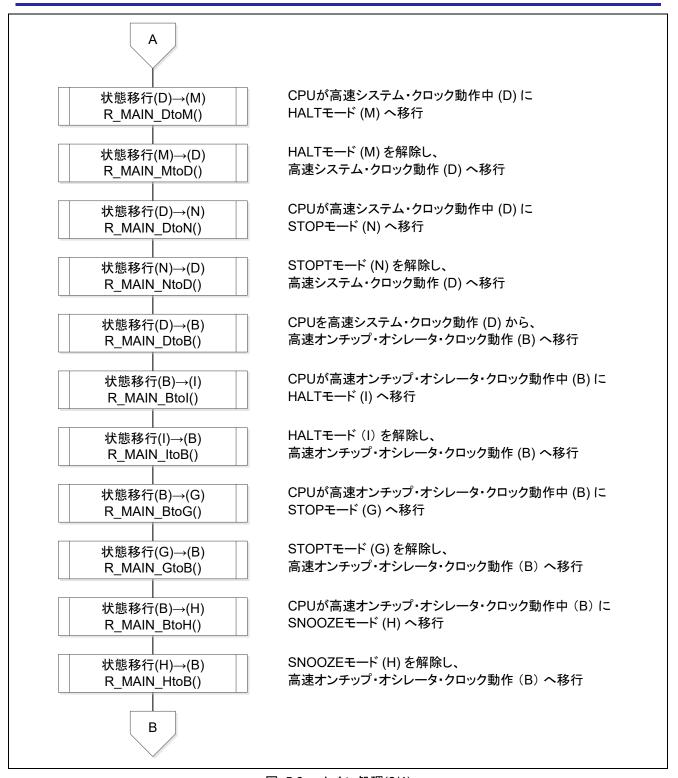

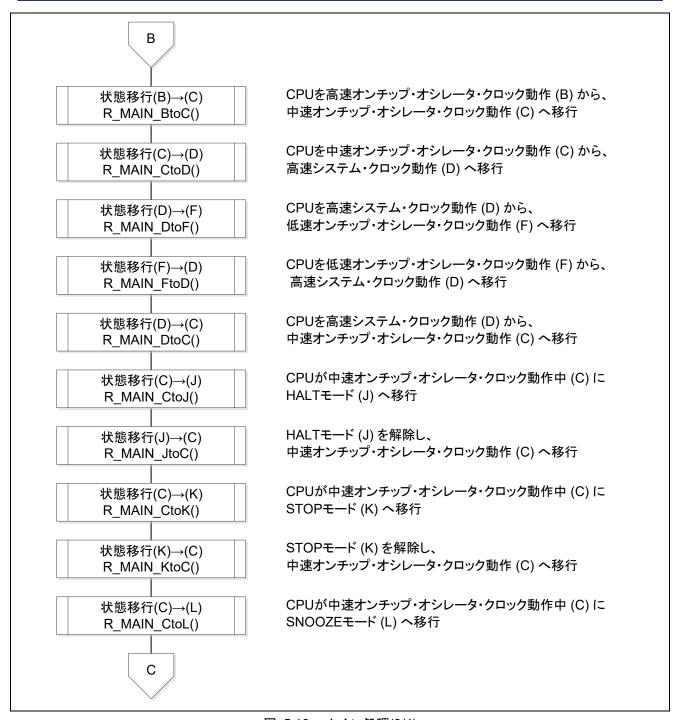

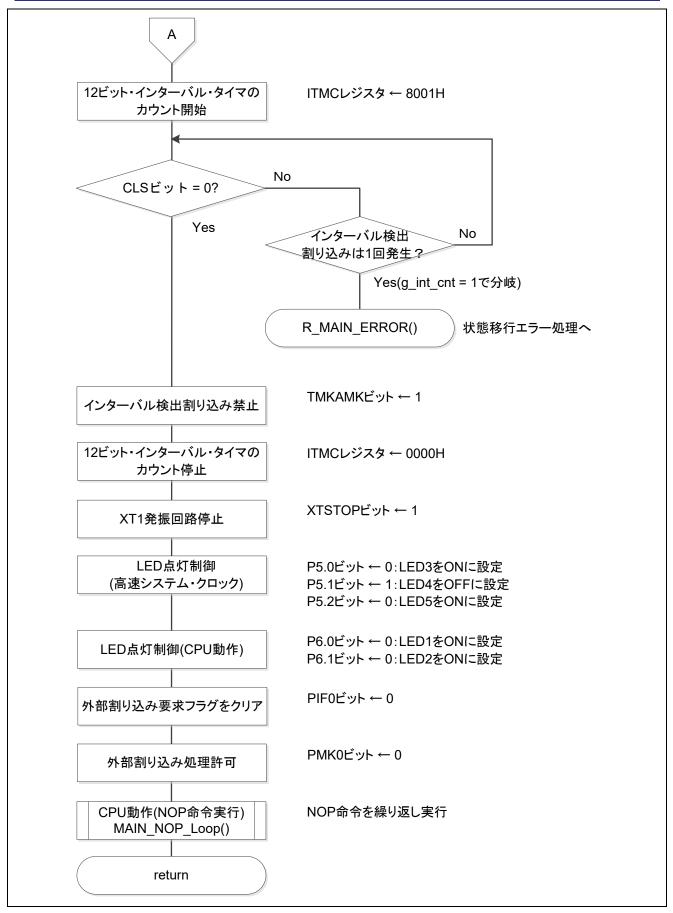

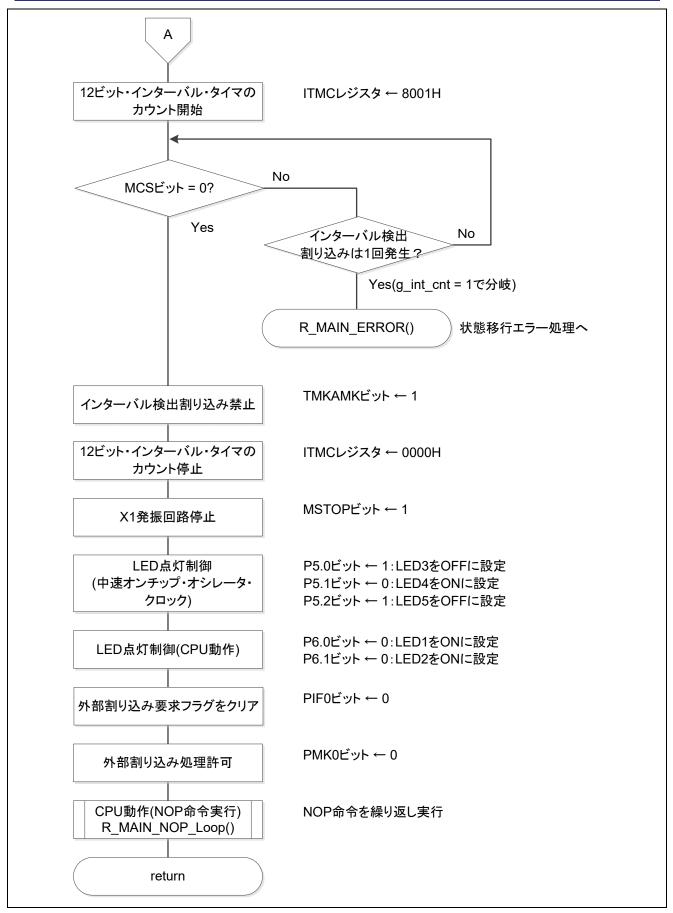

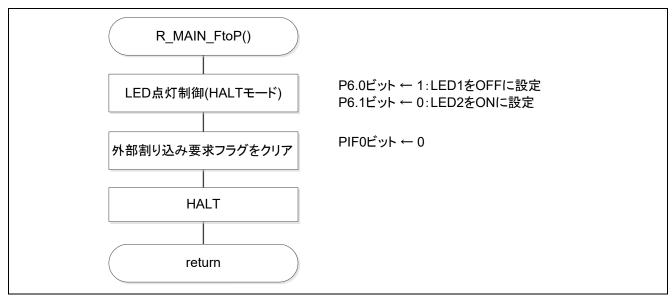

| 5.6.7 | 7        | メイン処理                                        |     |

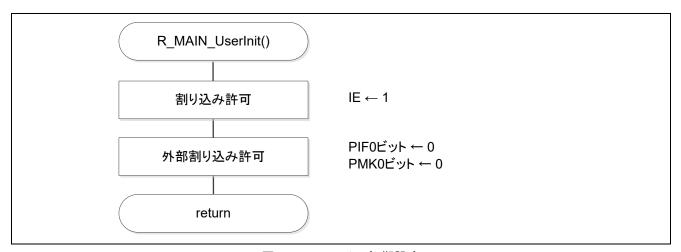

| 5.6.8 | 3        | メイン初期設定                                      | 64  |

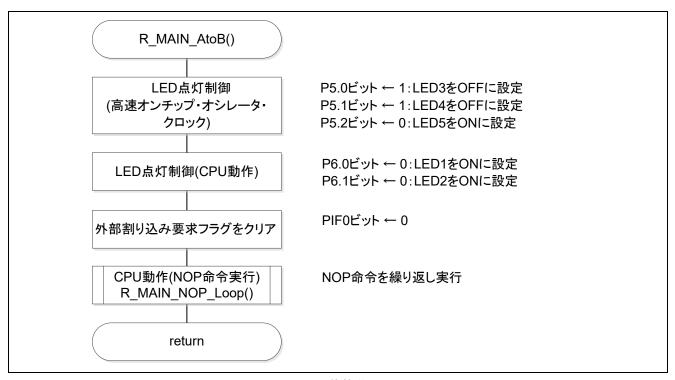

| 5.6.9 | )        | 状態移行 AtoB                                    | 65  |

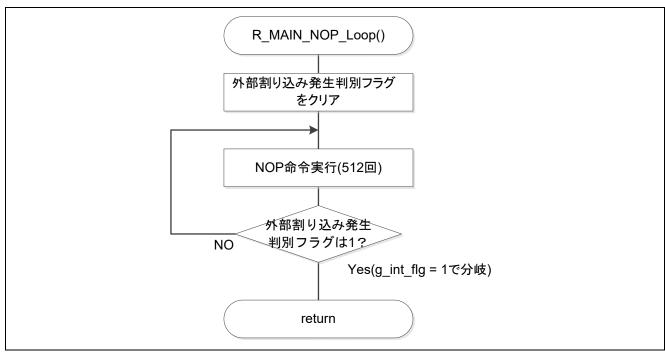

| 5.6.1 | 0        | CPU 動作(NOP 命令実行)                             | 65  |

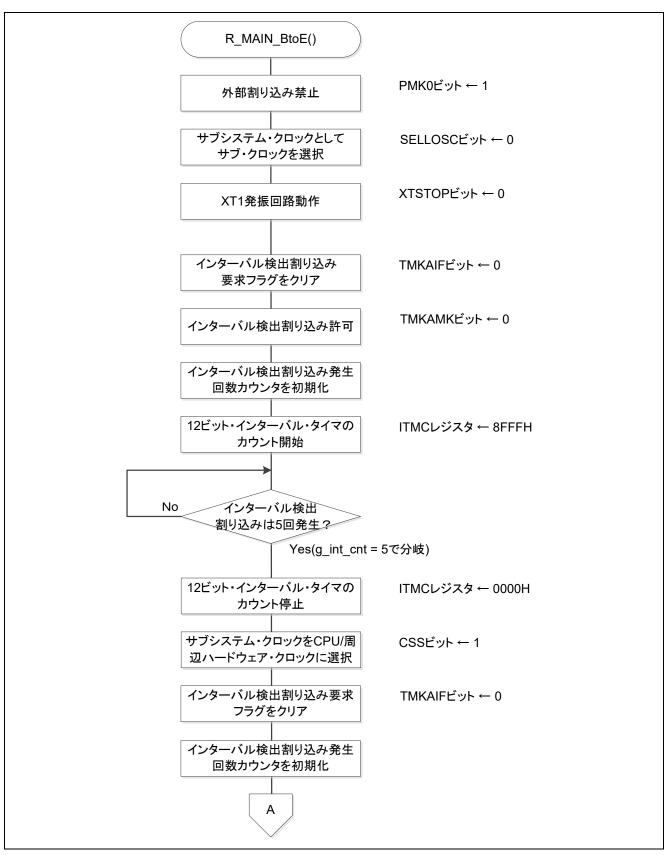

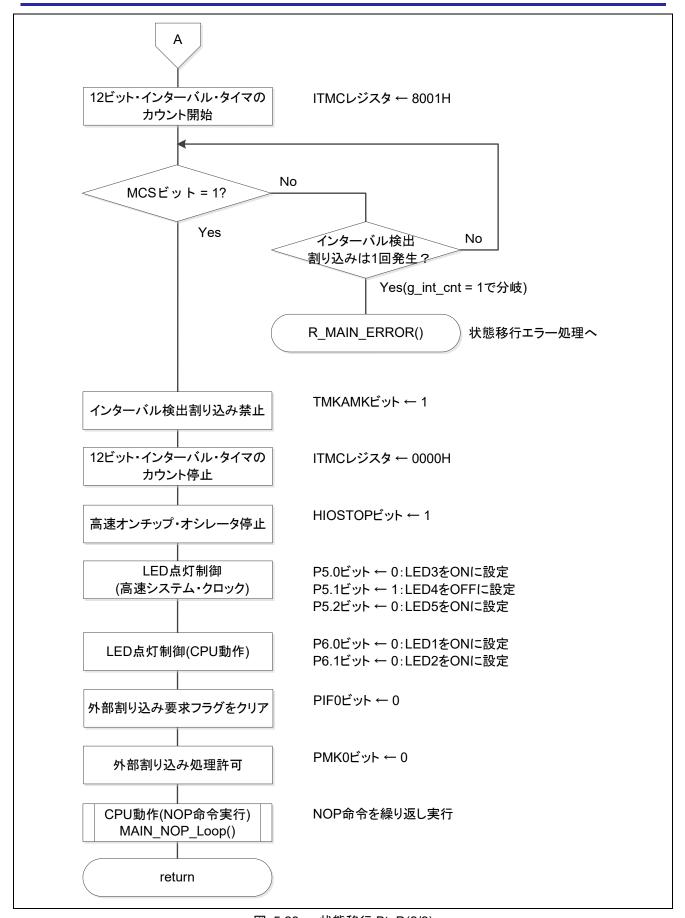

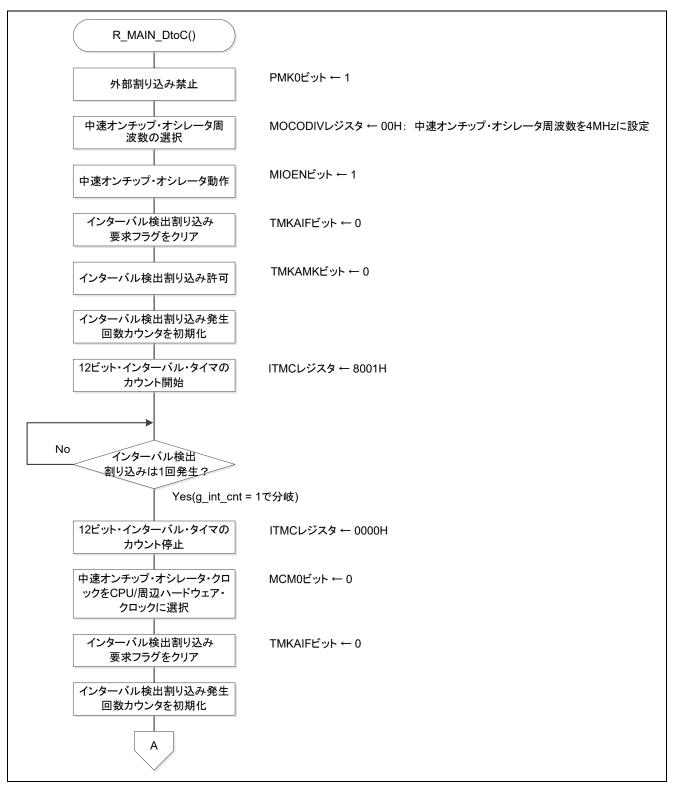

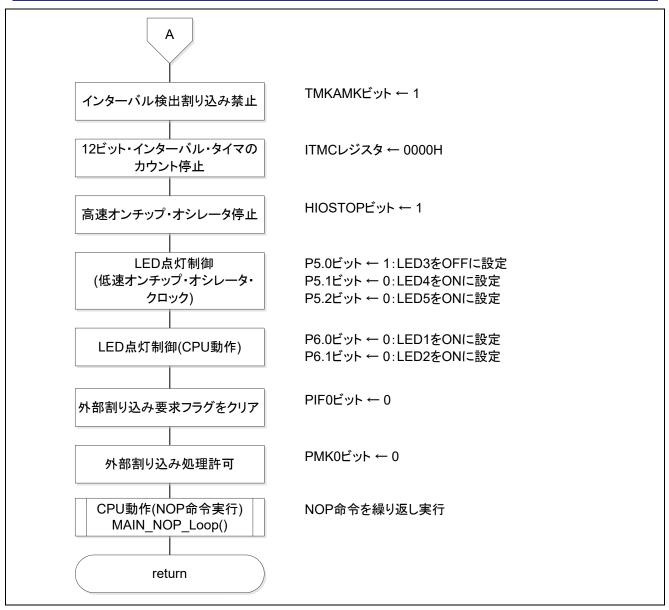

| 5.6.1 |          | 状態移行 BtoE                                    |     |

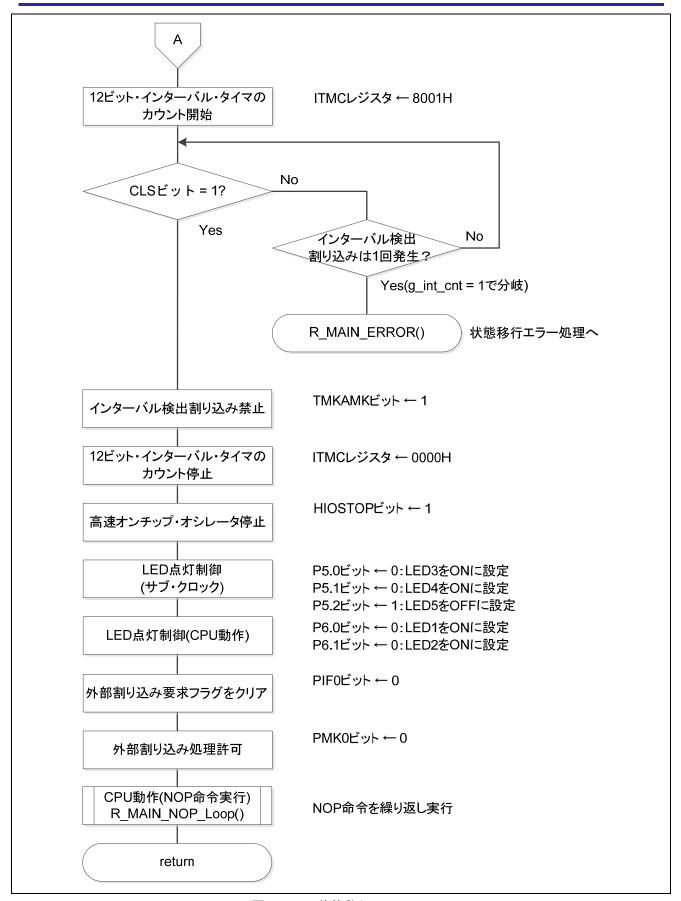

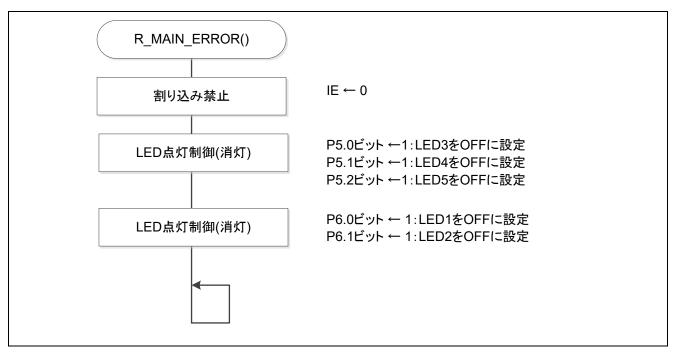

| 5.6.1 | 2        | 状態移行エラー処理                                    | 68  |

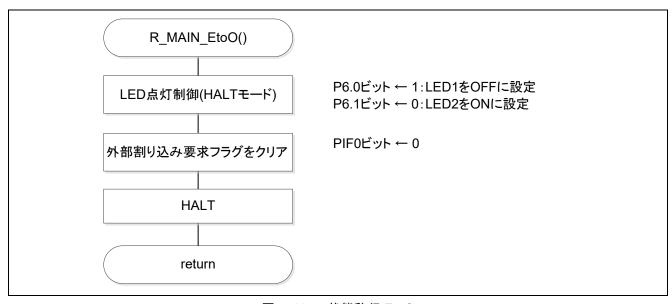

| 5.6.1 | 3        | 状態移行 EtoO                                    | 68  |

| 5.6.1 | 4        | 状態移行 OtoE                                    | 69  |

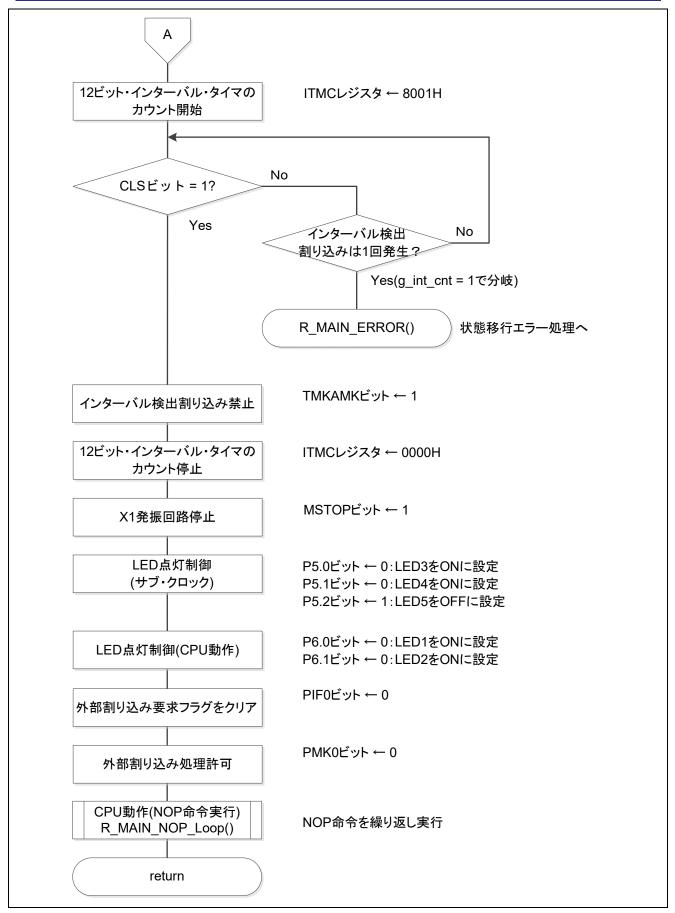

| 5.6.1 |          | 状態移行 EtoB                                    |     |

| 5.6.1 |          | 状態移行 BtoD                                    |     |

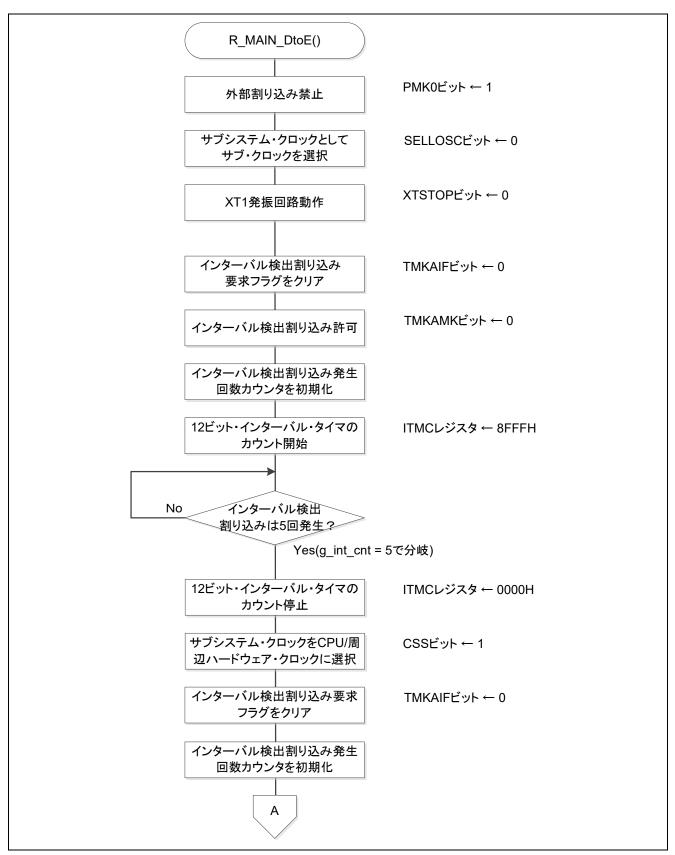

| 5.6.1 |          | 状態移行 DtoE                                    |     |

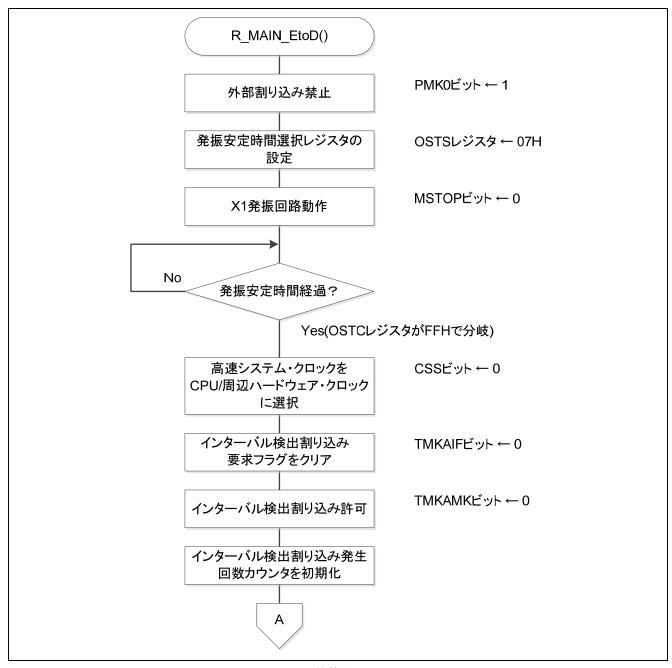

| 5.6.1 |          | 状態移行 EtoD                                    |     |

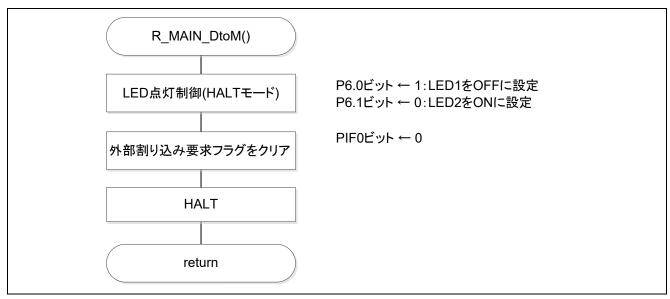

| 5.6.1 |          | 状態移行 DtoM                                    |     |

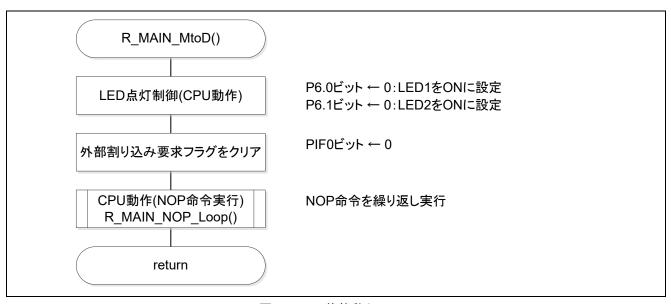

| 5.6.2 |          | 状態移行 MtoD                                    |     |

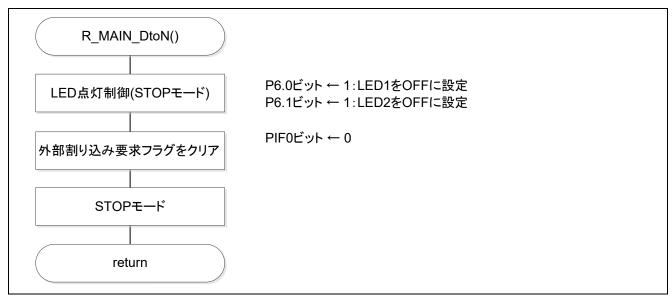

| 5.6.2 |          | 状態移行 DtoN                                    |     |

| 5.6.2 |          | 状態移行 NtoD                                    |     |

| 5.6.2 |          | 状態移行 DtoB                                    |     |

|       |          |                                              |     |

| 5.6.24 | 状態移行 Btol               | 82  |

|--------|-------------------------|-----|

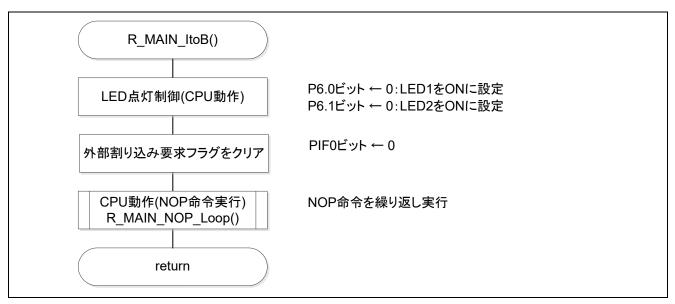

| 5.6.25 | 状態移行 ItoB               | 82  |

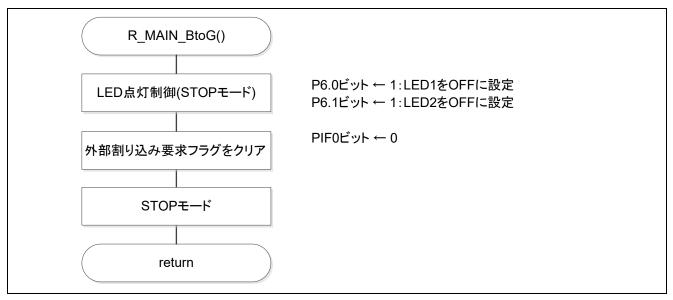

| 5.6.26 | 状態移行 BtoG               | 83  |

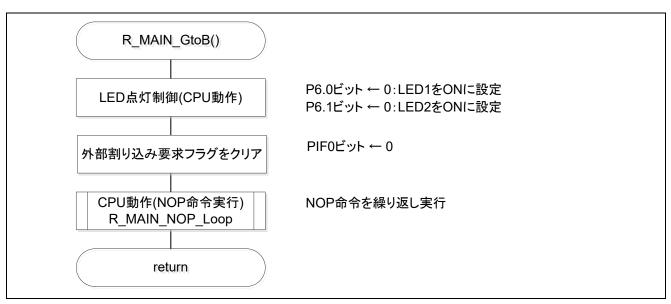

| 5.6.27 | 状態移行 GtoB               | 83  |

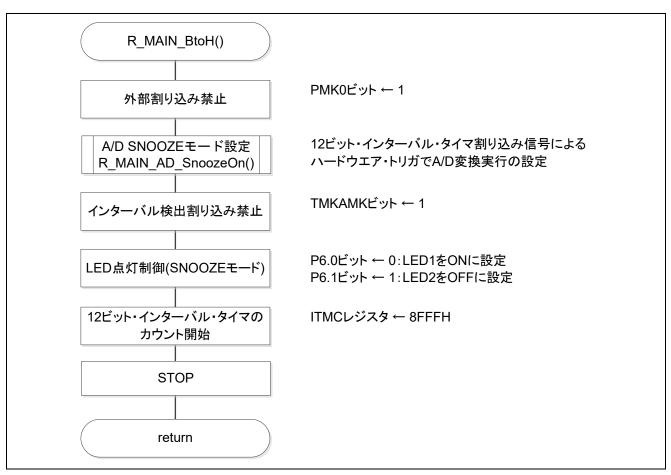

| 5.6.28 | 状態移行 BtoH               | 84  |

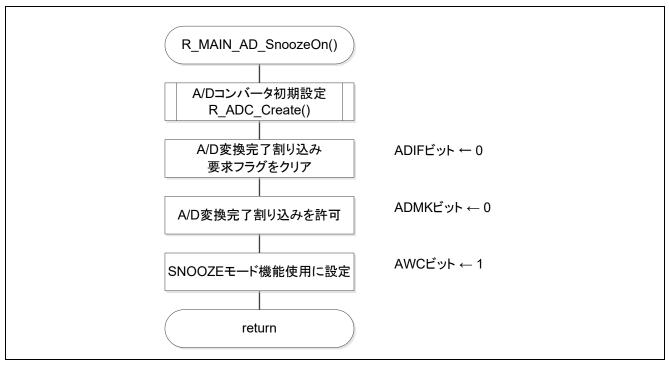

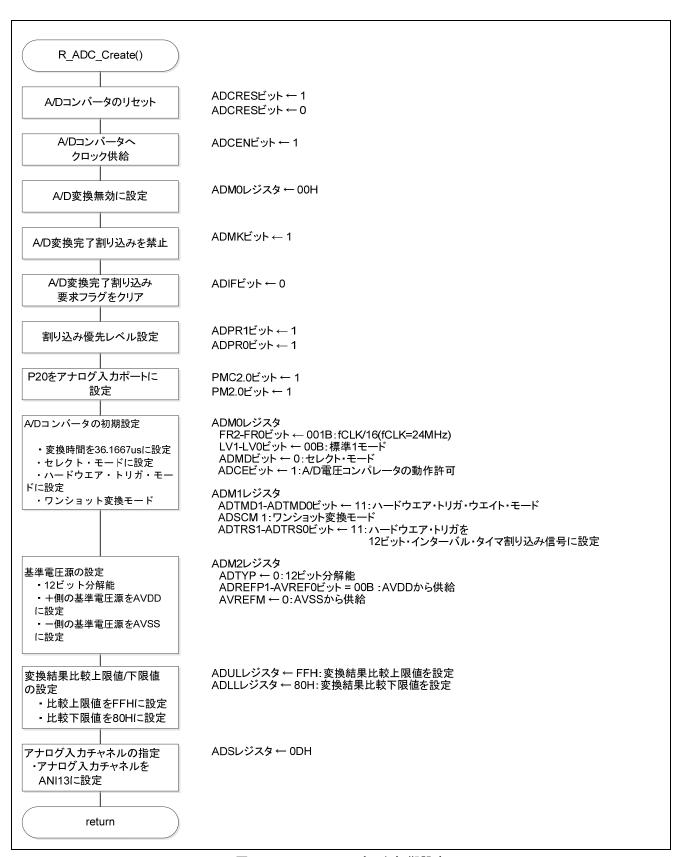

| 5.6.29 | A/D コンバータ設定             | 85  |

| 5.6.30 | A/D コンバータ初期設定           | 86  |

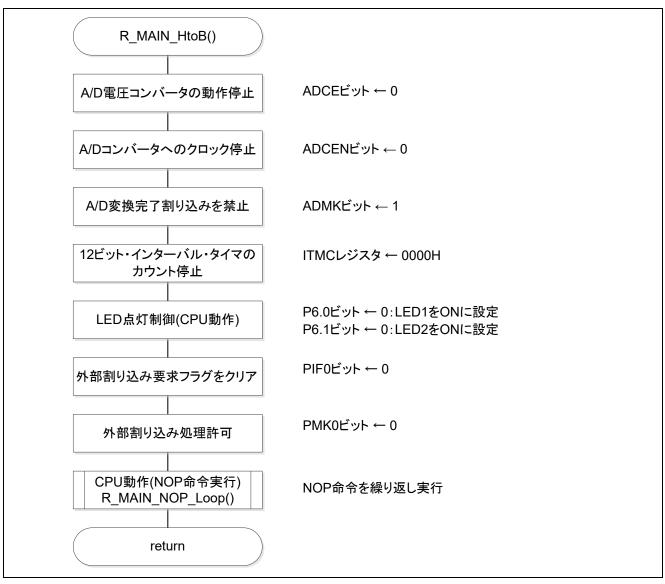

| 5.6.31 | 状態移行 HtoB               | 91  |

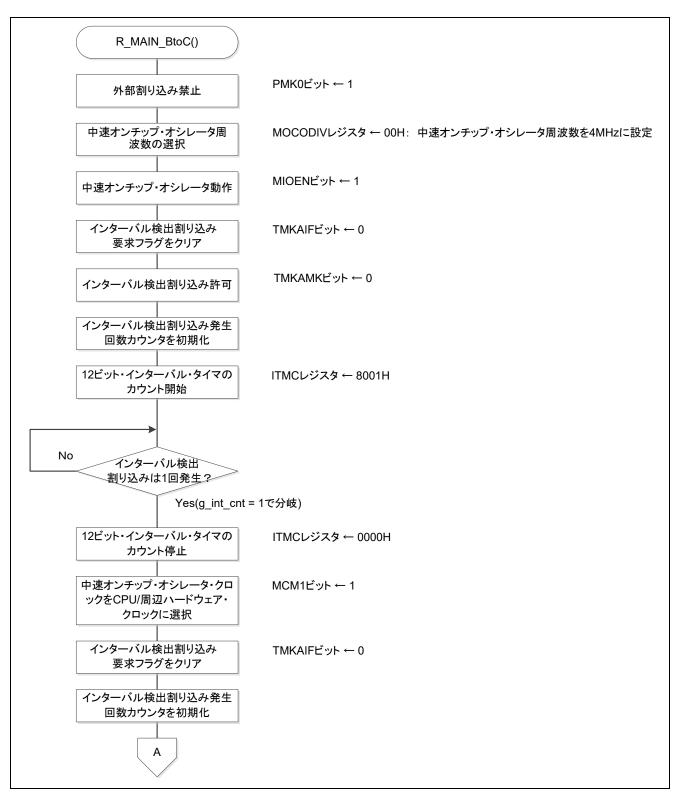

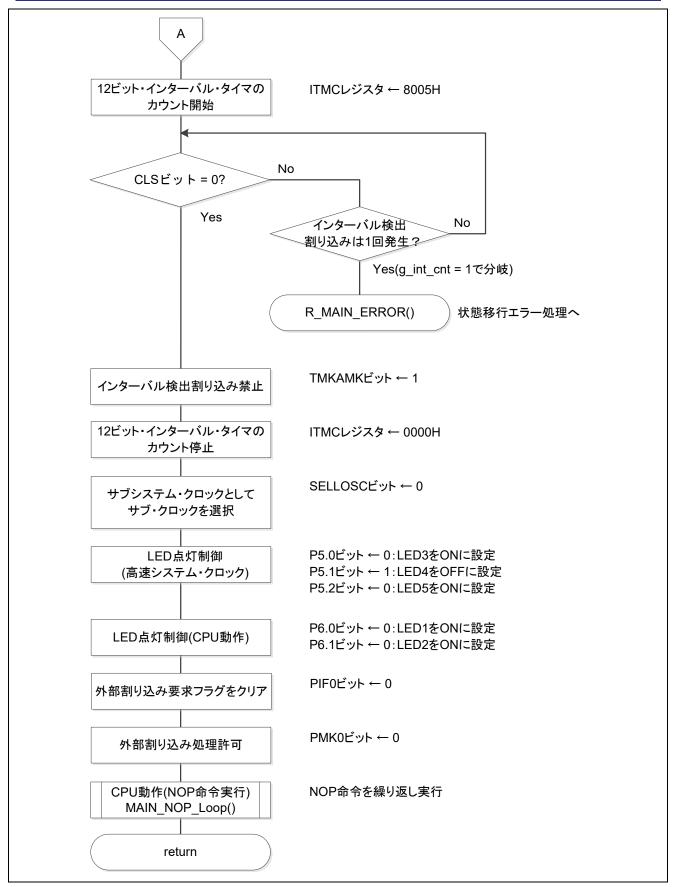

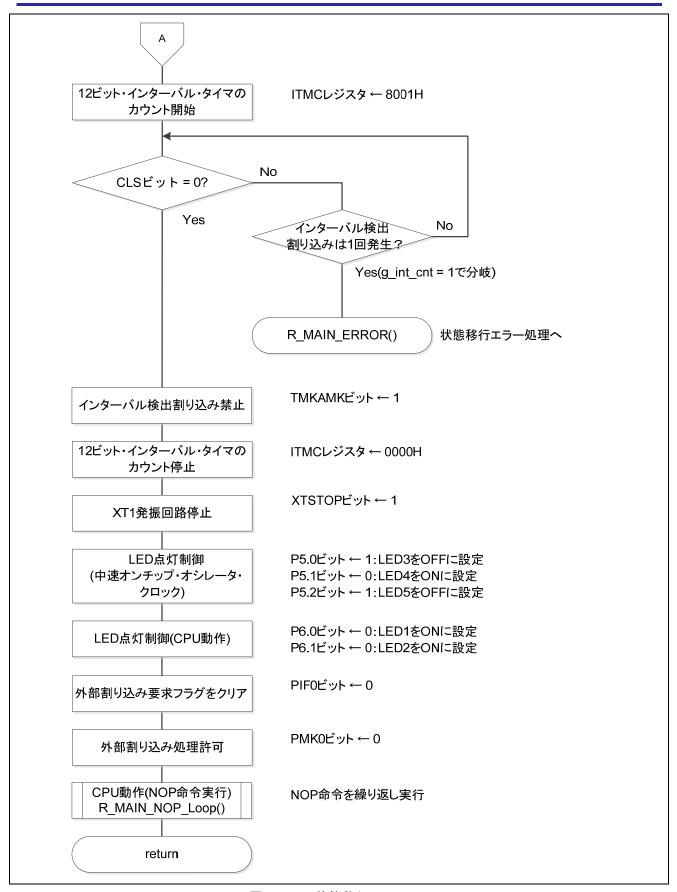

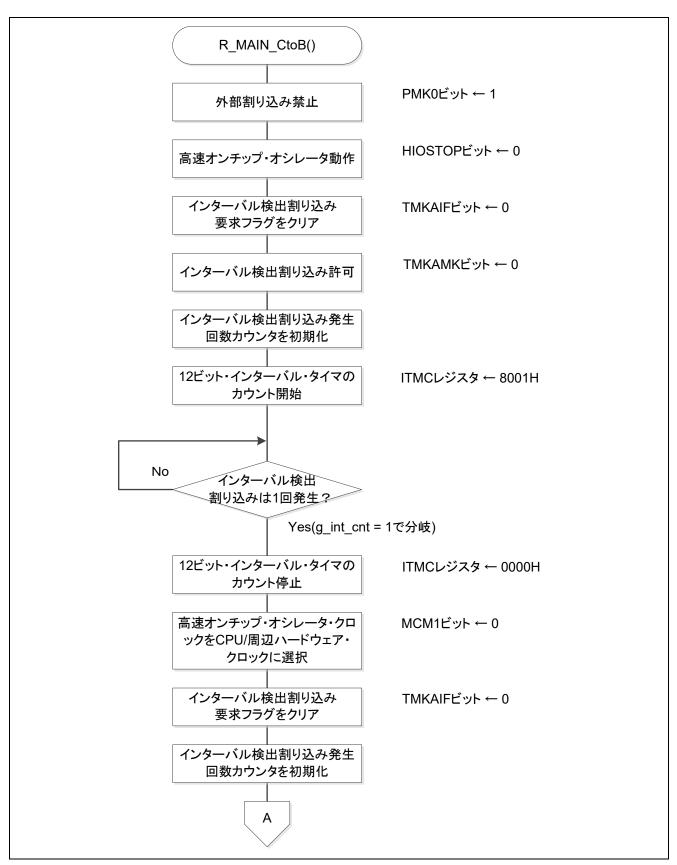

| 5.6.32 | 状態移行 BtoC               | 92  |

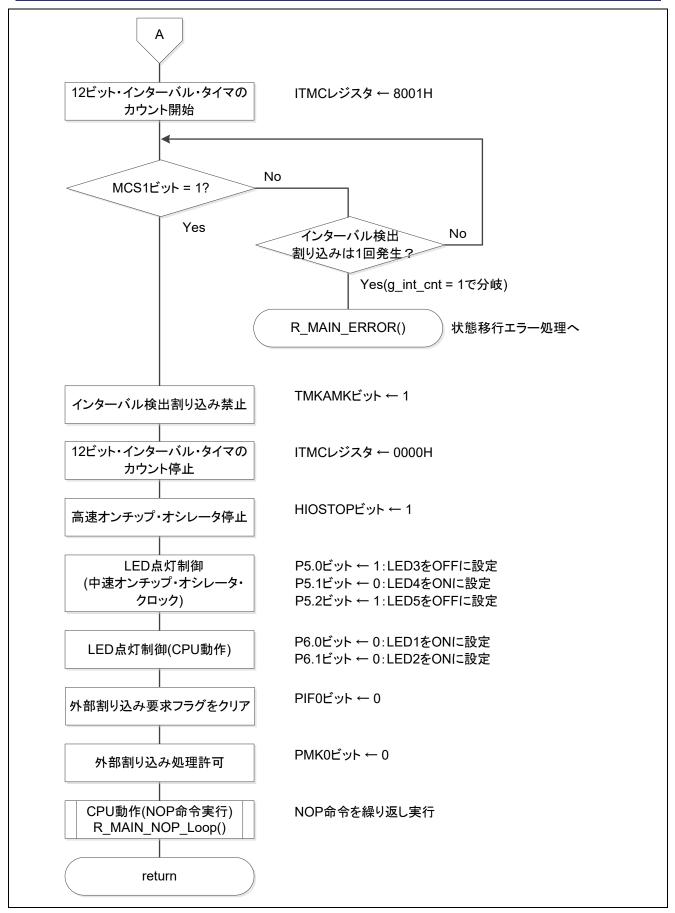

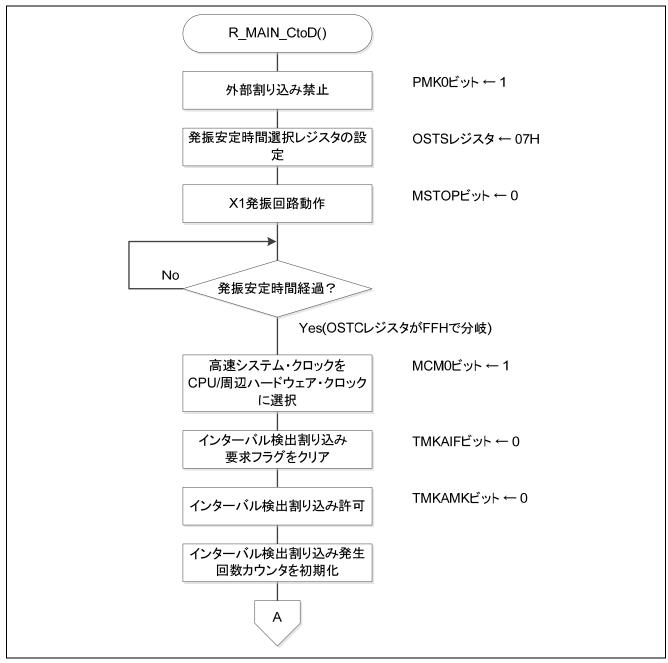

| 5.6.33 | 状態移行 CtoD               | 94  |

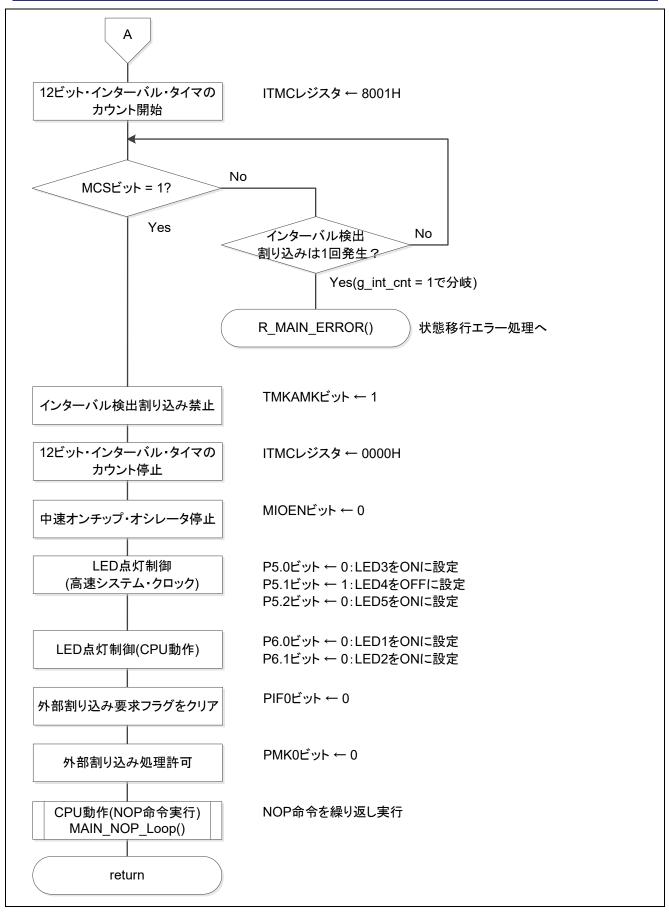

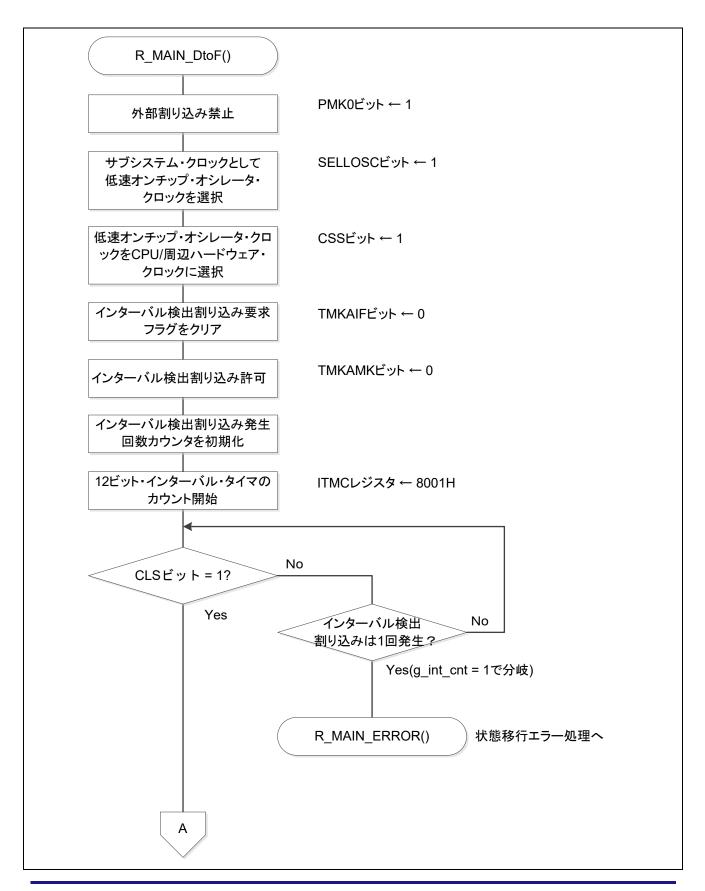

| 5.6.34 | 状態移行 DtoF               | 96  |

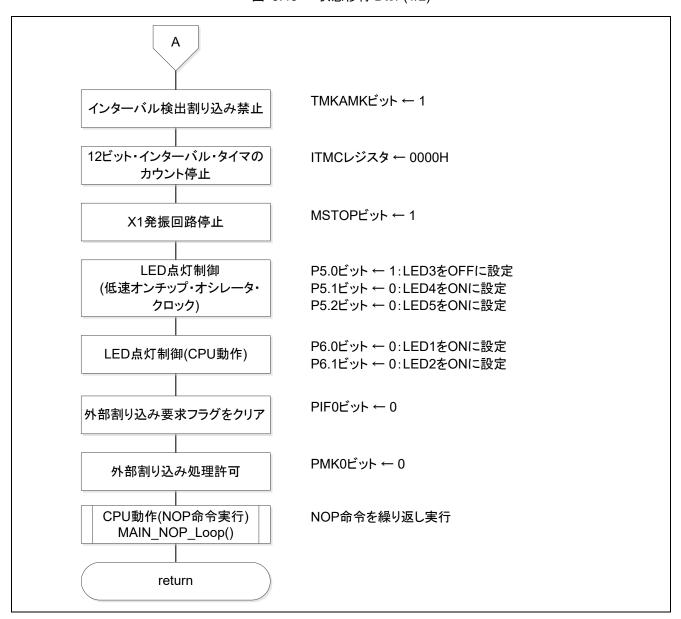

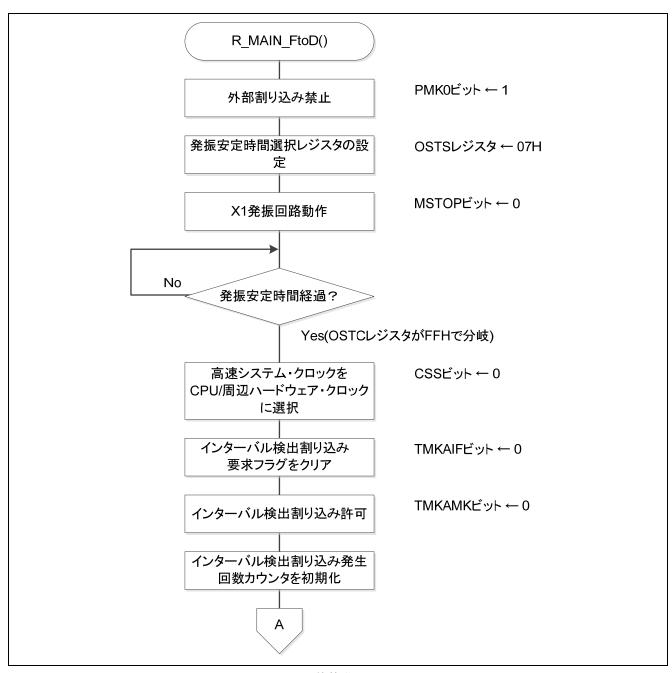

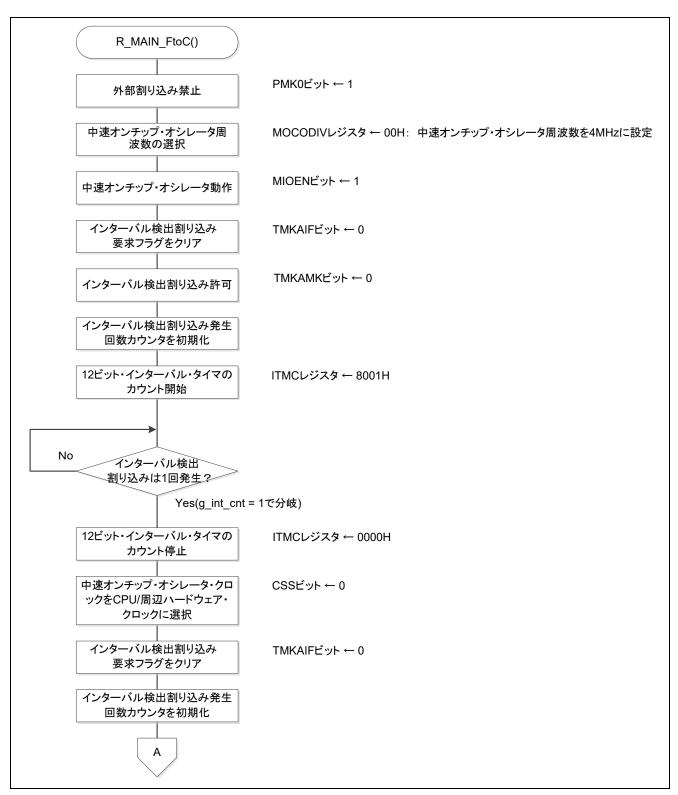

| 5.6.35 | 状態移行 FtoD               | 98  |

| 5.6.36 | 状態移行 DtoC               | 100 |

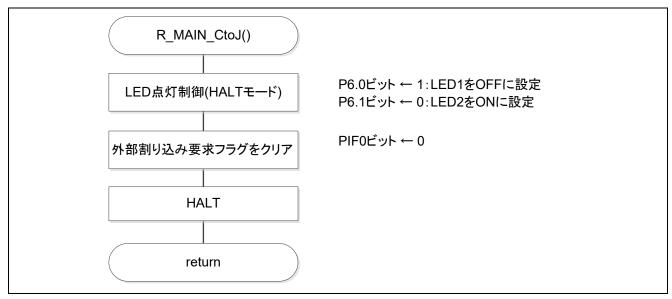

| 5.6.37 | 状態移行 CtoJ               | 102 |

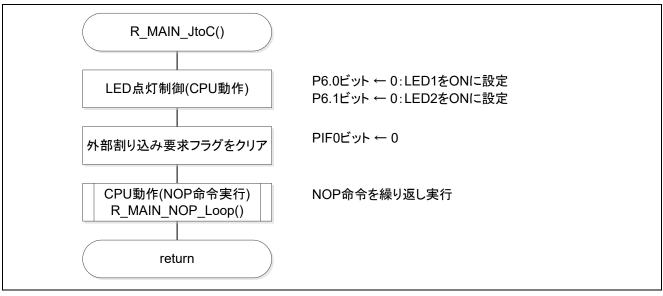

| 5.6.38 | 状態移行 JtoC               | 102 |

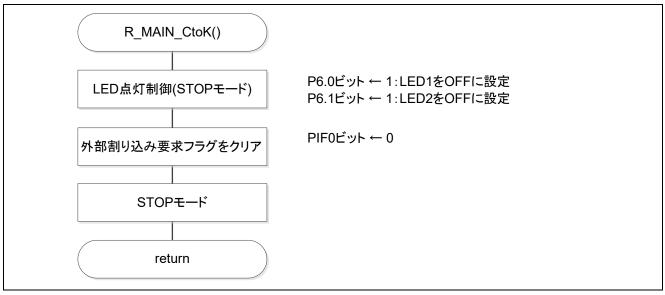

| 5.6.39 | 状態移行 CtoK               | 103 |

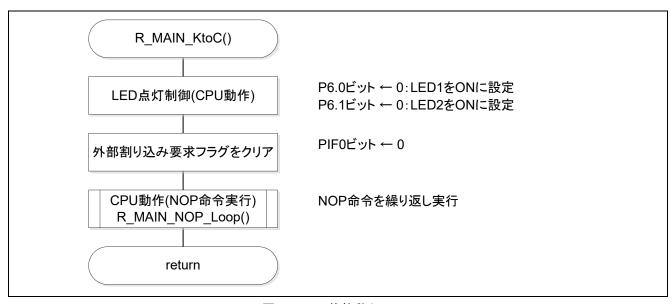

| 5.6.40 | 状態移行 KtoC               | 103 |

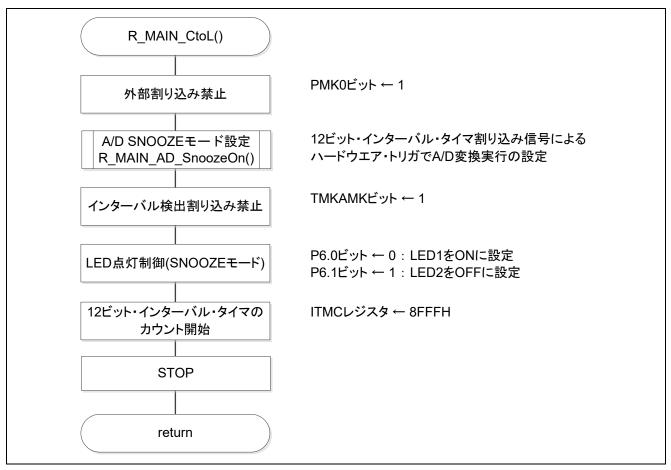

| 5.6.41 | 状態移行 CtoL               | 104 |

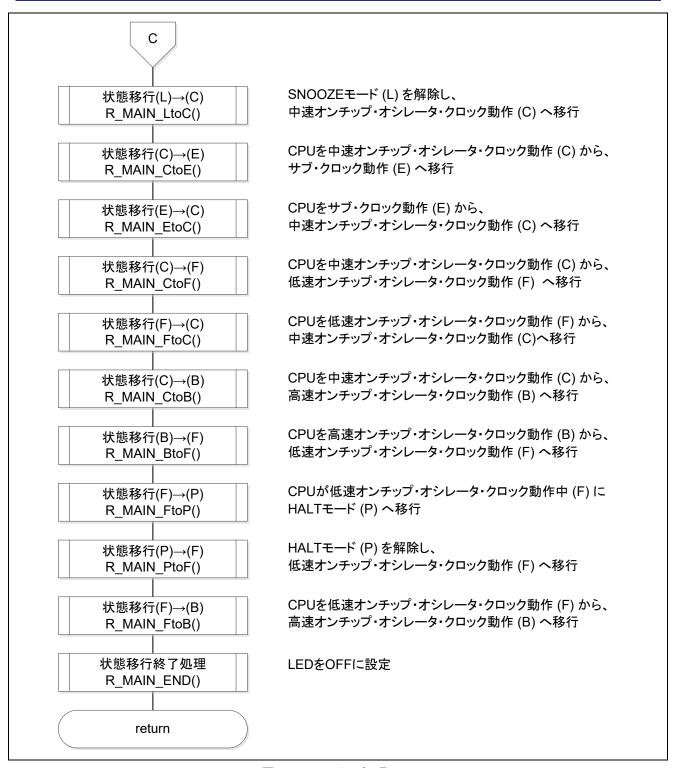

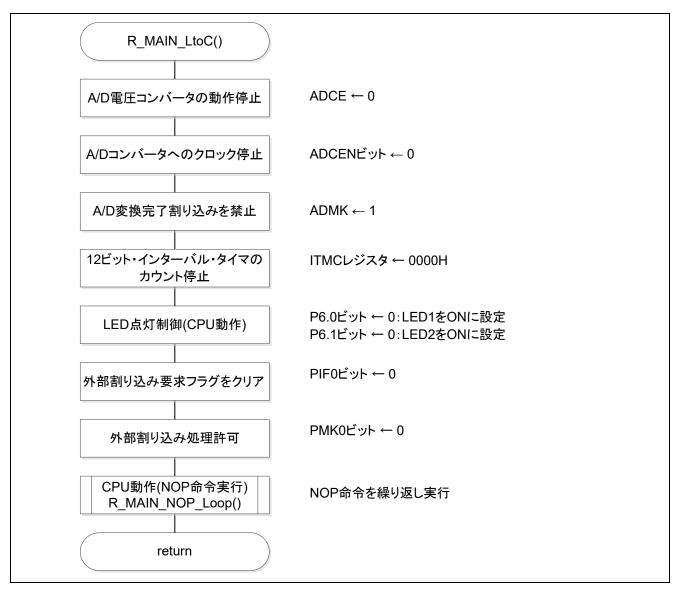

| 5.6.42 | 状態移行 LtoC               | 105 |

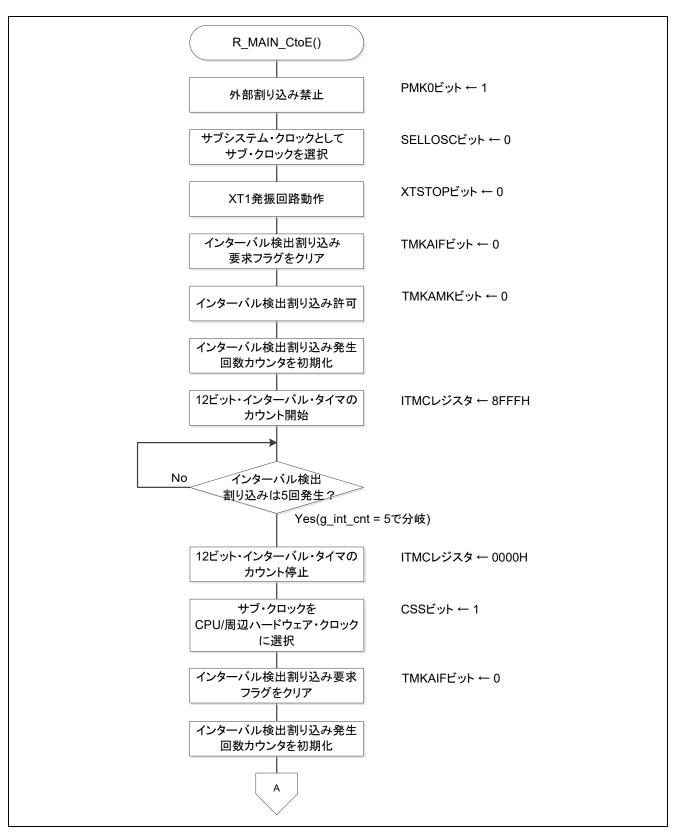

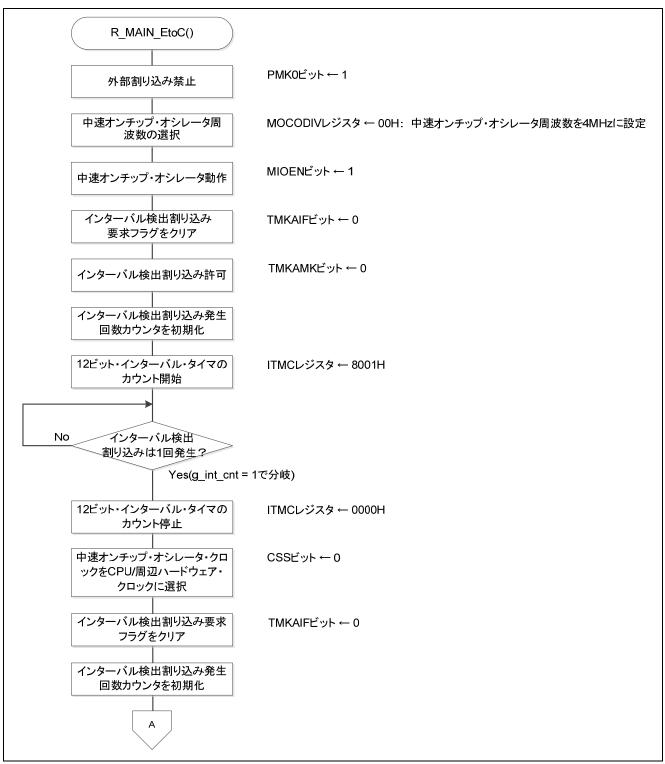

| 5.6.43 | 状態移行 CtoE               | 106 |

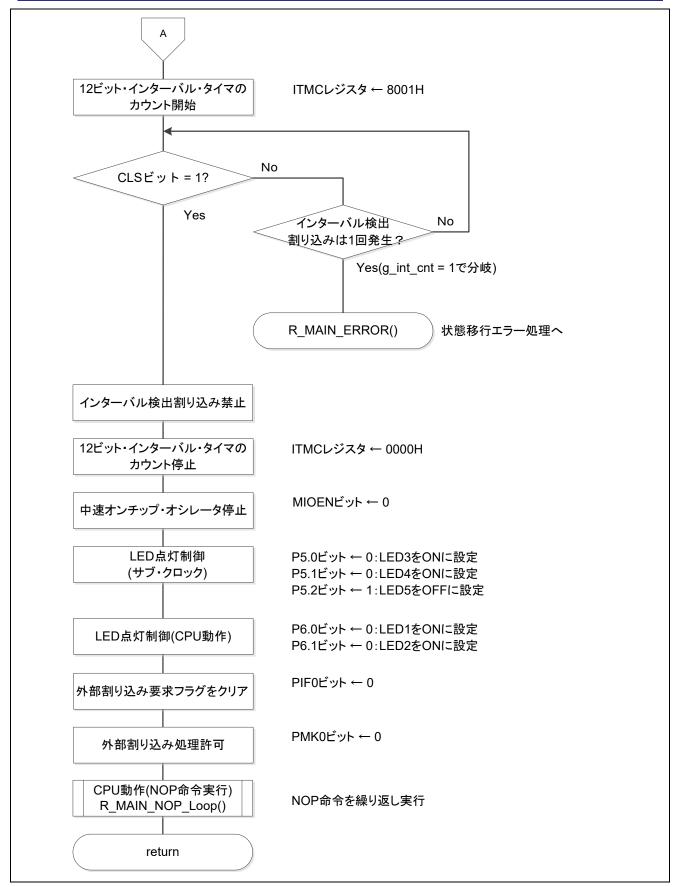

| 5.6.44 | 状態移行 EtoC               | 108 |

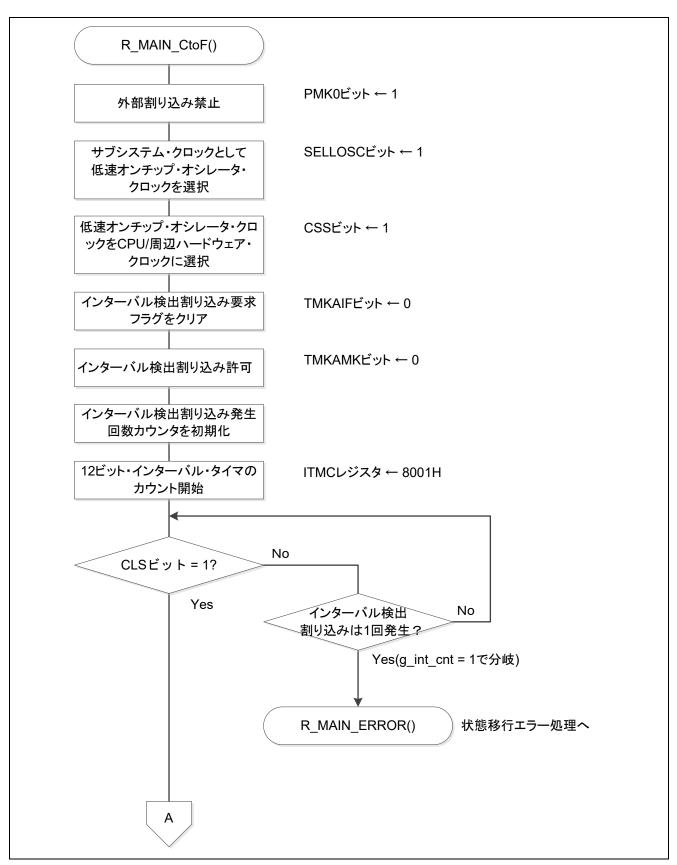

| 5.6.45 | 状態移行 CtoF               | 110 |

| 5.6.46 | 状態移行 FtoC               | 112 |

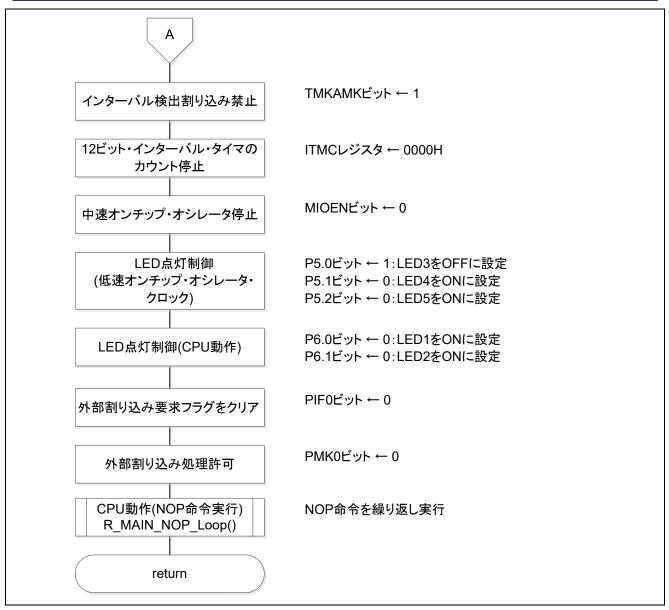

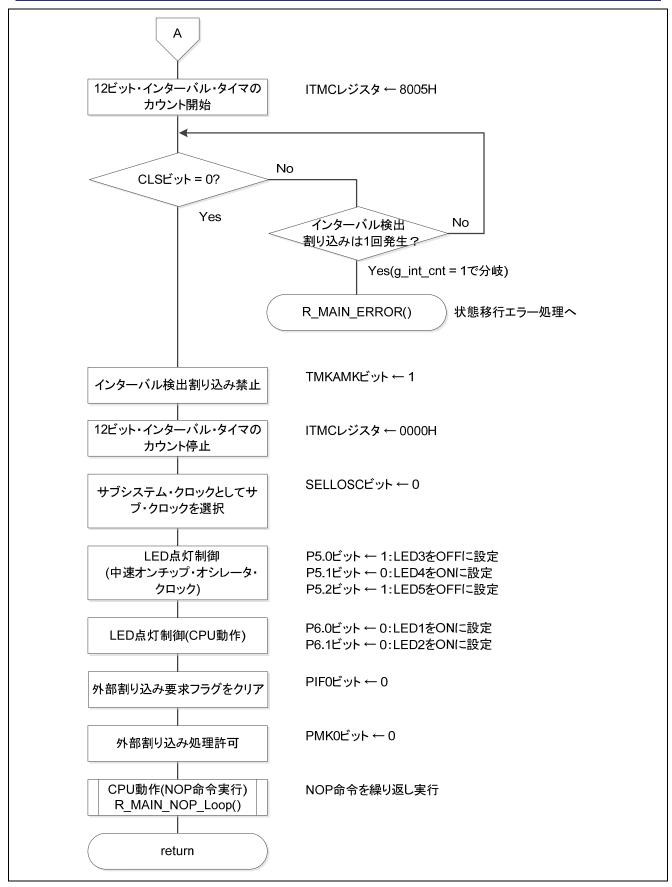

| 5.6.47 | 状態移行 CtoB               | 114 |

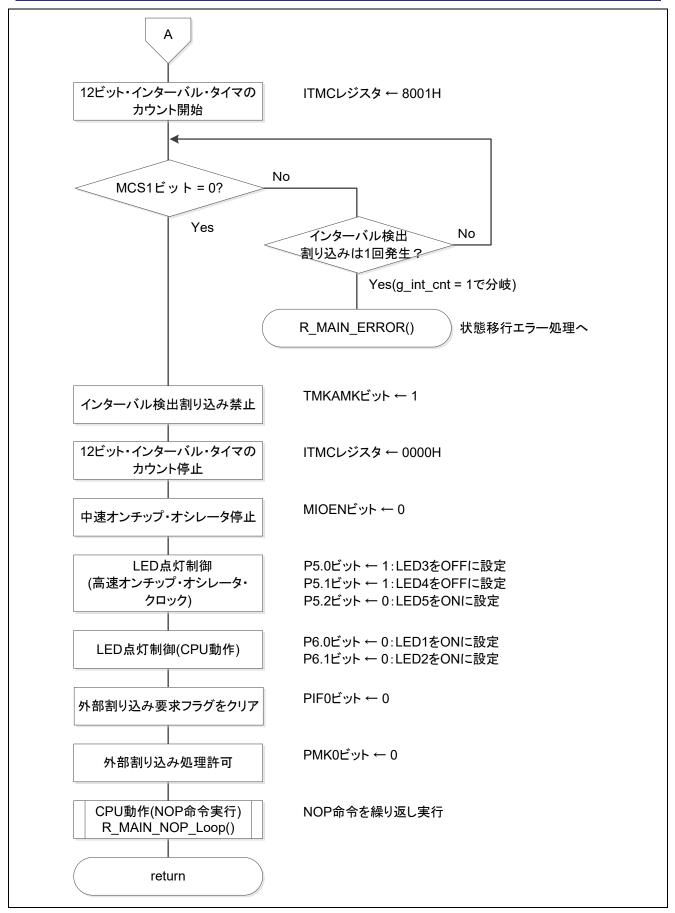

| 5.6.48 | 状態移行 BtoF               | 116 |

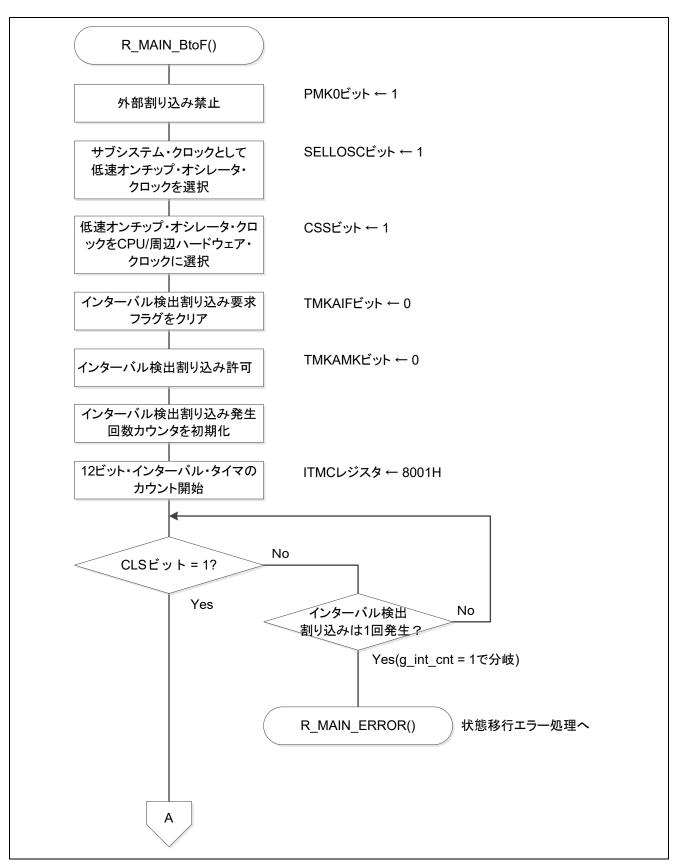

| 5.6.49 | 状態移行 FtoP               | 118 |

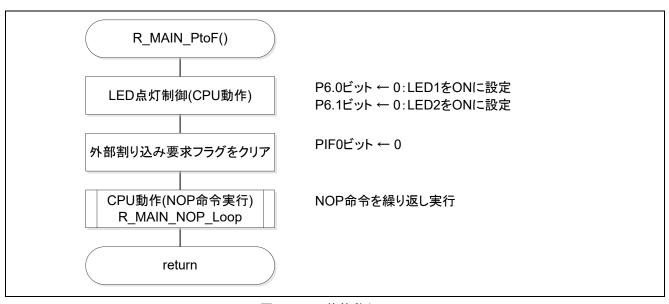

| 5.6.50 | 状態移行 PtoF               | 118 |

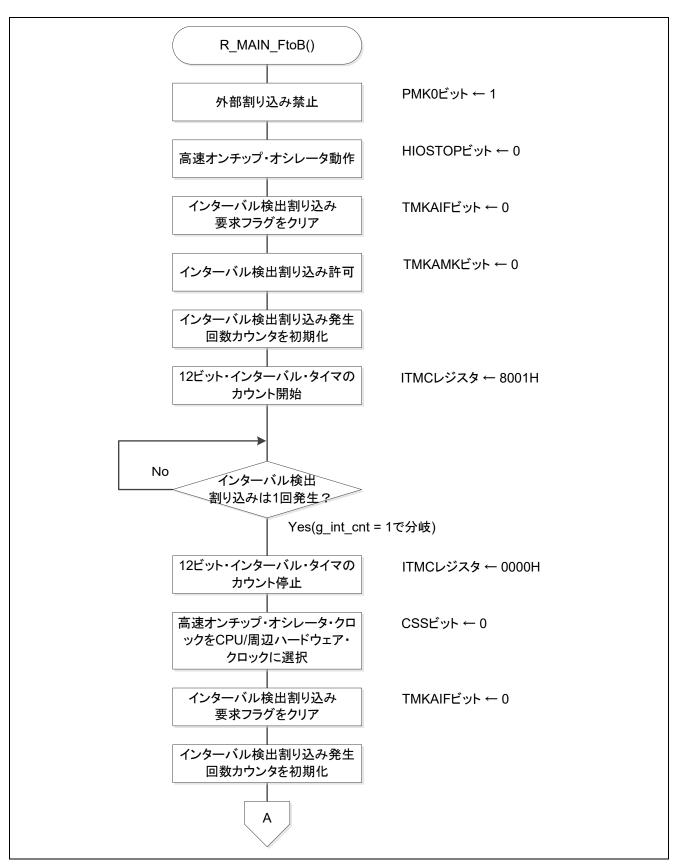

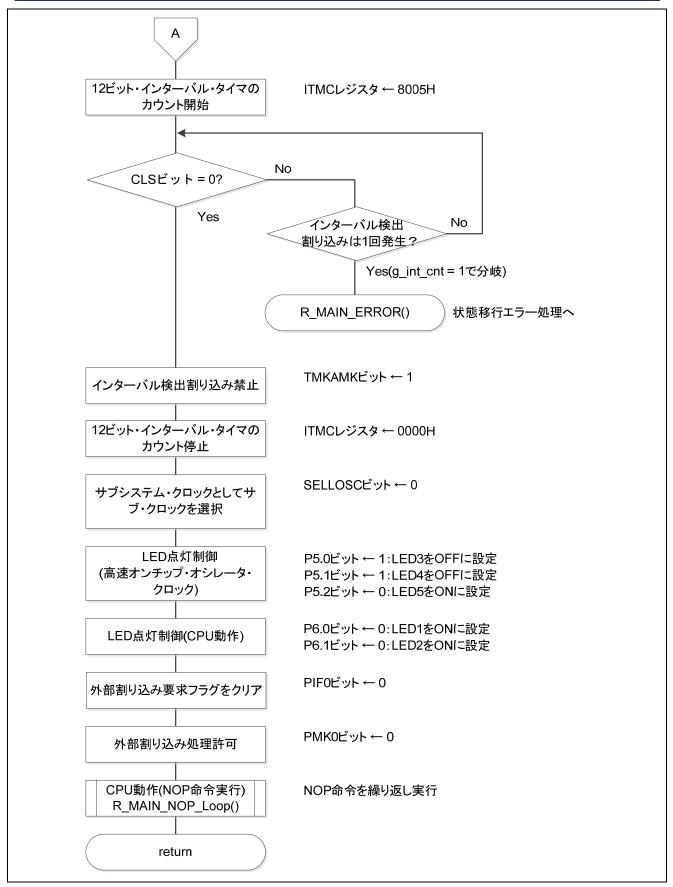

| 5.6.51 | 状態移行 FtoB               | 119 |

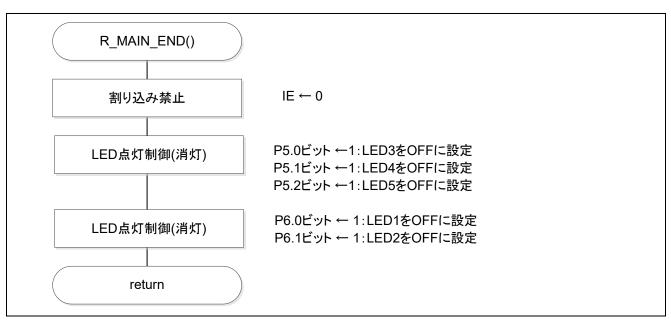

| 5.6.52 | 状態移行終了処理                | 121 |

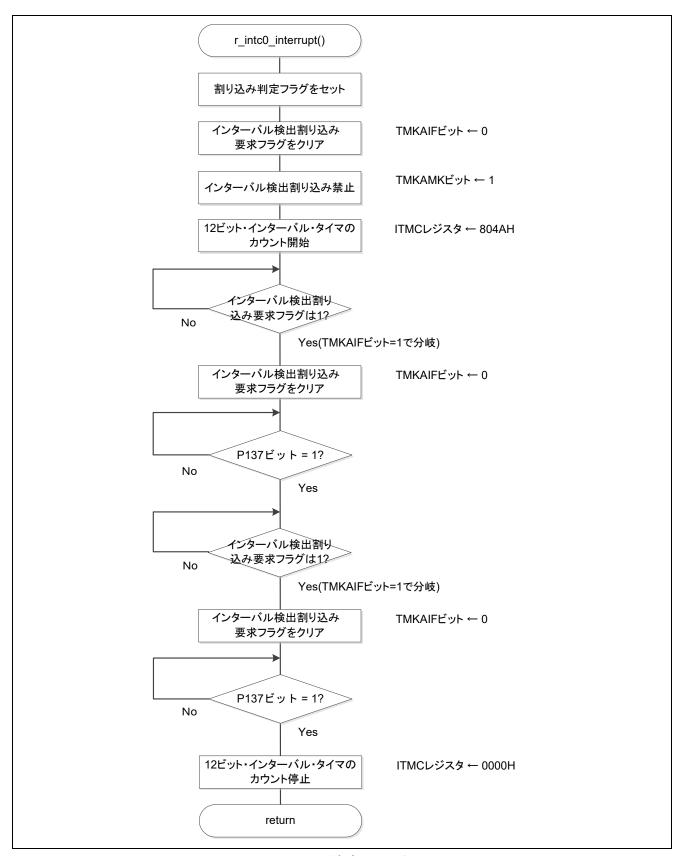

| 5.6.53 | 外部割り込み処理                |     |

| 5.6.54 | 12 ビット・インターバル・タイマ割り込み処理 | 123 |

| 5.6.55 | A/D 変換終了割り込み処理          | 123 |

| 6. サン  | ンプルコード                  | 124 |

|        | セドナ - J - I             |     |

## 1. 仕様

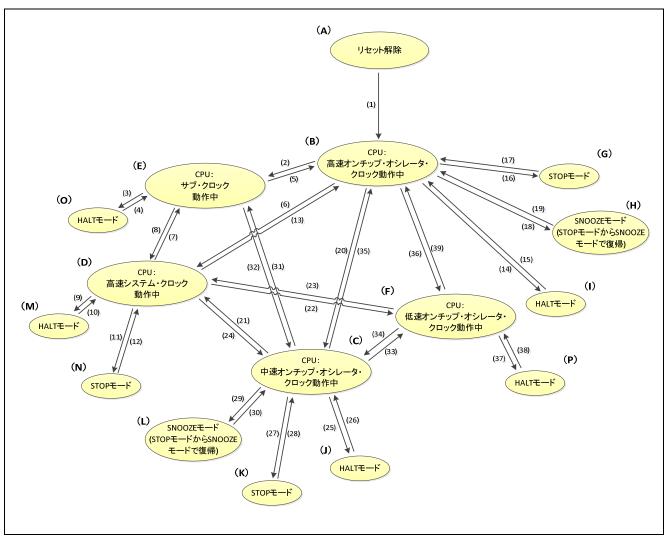

本アプリケーションノートでは、スイッチ入力によって図 1.1 動作モード状態移行図に沿った CPU クロックと動作モードの切り替えを行います。

また、CPU クロックと動作モードの状態に合わせ、5つの LED 点灯を制御します。

使用する周辺機能と用途、動作モード状態移行図、動作モードと LED 表示の関係をそれぞれ表 1.1、図 1.1、表 1.2に示します。

表 1.1 使用する周辺機能と用途

| <b>五</b>          | が同と一般化と一方を                       |

|-------------------|----------------------------------|

| 周辺機能              | 用途                               |

| ポート出力             | P50、P51、P52、P60、P61 端子に接続された LED |

|                   | の点灯制御(LED1-LED5)                 |

| 外部割り込み            | スイッチ入力(SW1)による端子入力エッジ検出の         |

|                   | 割り込み(INTP0)                      |

| 12 ビット・インターバル・タイマ | 12 ビット・インターバル・タイマのインターバル         |

|                   | 信号検出の割り込み(INTIT)                 |

| A/D コンバータ         | P20/ANI13 端子のアナログ信号入力レベルを変換す     |

|                   | <b></b>                          |

図 1.1 動作モード状態移行図

LED 表示 CPU/周辺ハードウエア・クロック(fclk) 動作モード LED1 LED2 LED3 LED4 LED5 通常動作モード 点灯 点灯 点灯 消灯 消灯 HALT モード 高速オンチップ・オシレータ・ 消灯 点灯 消灯 消灯 点灯 クロック(f<sub>IH</sub>) SNOOZE モード 点灯 消灯 消灯 消灯 点灯 STOP モード 消灯 消灯 消灯 消灯 点灯 通常動作モード 点灯 点灯 消灯 点灯 消灯 点灯 中速オンチップ・オシレータ・ HALT モード 消灯 点灯 消灯 消灯 SNOOZE モード クロック(f<sub>IM</sub>) 点灯 消灯 消灯 点灯 消灯 STOP モード 消灯 消灯 点灯 消灯 消灯 低速オンチップ・オシレータ・ 通常動作モード 点灯 点灯 消灯 点灯 点灯 HALT モード クロック(f<sub>L</sub>) 消灯 消灯 点灯 点灯 消灯 通常動作モード 点灯 点灯 点灯 点灯 消灯 高速システム・クロック(f<sub>MX</sub>) HALT モード 点灯 消灯 点灯 消灯 点灯 STOP モード 消灯 点灯 消灯 点灯 消灯 点灯 点灯 消灯 通常動作モード 点灯 点灯 サブ・クロック(fsx) HALT モード 点灯 消灯 消灯 点灯 点灯

表 1.2 動作モードと LED 表示の関係

注意 1 端子に流れる電流が 8mA 以下となるようにしてください。端子に流せる電流については、 RL78/I1D ユーザーズマニュアルの電気的特性をご参照ください。

### 1.1 CPU クロックの切り替え

つぎの CPU クロックの切り替えについて、特殊機能レジスタ (SFR) の設定手順を説明します。

- ・高速オンチップ・オシレータ・クロックから中速オンチップ・オシレータ・クロックへの切り替え

- ・高速オンチップ・オシレータ・クロックから低速オンチップ・オシレータ・クロックへの切り替え

- ・高速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え

- ・高速オンチップ・オシレータ・クロックからサブ・クロックへの切り替え

- ・中速オンチップ・オシレータ・クロックから高速オンチップ・オシレータ・クロックへの切り替え

- ・中速オンチップ・オシレータ・クロックから低速オンチップ・オシレータ・クロックへの切り替え

- ・中速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え

- ・中速オンチップ・オシレータ・クロックからサブ・クロックへの切り替え

- ・低速オンチップ・オシレータ・クロックから高速オンチップ・オシレータ・クロックへの切り替え

- ・低速オンチップ・オシレータ・クロックから中速オンチップ・オシレータ・クロックへの切り替え

- ・低速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え

- ・高速システム・クロックから高速オンチップ・オシレータ・クロックへの切り替え

- ・高速システム・クロックから中速オンチップ・オシレータ・クロックへの切り替え

- ・高速システム・クロックから低速オンチップ・オシレータ・クロックへの切り替え

- ・高速システム・クロックからサブ・クロックへの切り替え

- ・サブ・クロックから高速オンチップ・オシレータ・クロックへの切り替え

- ・サブ・クロックから中速オンチップ・オシレータ・クロックへの切り替え

- サブ・クロックから高速システム・クロックへの切り替え

# 1.1.1 高速オンチップ・オシレータ・クロックから中速オンチップ・オシレータ・クロック への切り替え

CPU クロックを高速オンチップ・オシレータ・クロックから中速オンチップ・オシレータ・クロックに変更する場合、クロック動作ステータス制御レジスタ(CSC)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で中速オンチップ・オシレータ・クロックを $f_{CLK}$ に設定します。

メイン・オンチップ・オシレータ・クロックのステータスが中速オンチップ・オシレータ・クロックに切り替わったのを確認し、高速オンチップ・オシレータを停止します。

① CSC レジスタの MIOEN ビットをセット(1)して中速オンチップ・オシレータを動作させます。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | Х      | 0 | 0 | 0 | 0 | 1     | 0       |

- ② 中速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 4us) はタイマ機能などを用いてカウントします。

- ③ CKC レジスタの MCM1 ビットをセット(1)して中速オンチップ・オシレータ・クロックをメイン・オンチップ・オシレータ・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 0   | 0   | 0    | 0 | 0 | 0    | 1    |

④ CKC レジスタの MCS1 ビットが 1 になったことを確認して、HIOSTOP をセット(1)し、高速オンチップ・オシレータを停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | Х      | 0 | 0 | 0 | 0 | 1     | 1       |

レジスタ図の設定値

## 1.1.2 高速オンチップ・オシレータ・クロックから低速オンチップ・オシレータ・クロック への切り替え

CPU クロックを高速オンチップ・オシレータ・クロックから低速オンチップ・オシレータ・クロックに変更する場合、サブシステム・クロック選択レジスタ(CKSEL)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で低速オンチップ・オシレータ・クロックをfclkに設定します。CPU/周辺ハードウエア・クロックのステータスがサブシステム・クロックに切り替わったのを確認し、高速オンチップ・オシレータを停止します。

① CKSEL レジスタの SELLOSC ビットをセット(1)して低速オンチップ・オシレータを動作させます。

|       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| CKSEL | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SELLOSC |

|       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1       |

- ② 低速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 210µs) はタイマ機能などを用いてカウントします。本アプリケーションノートでは、常時低速オンチップ・オシレータを動作させているため、発振の安定待ちを行っておりません。

- ③ CKC レジスタの CSS ビットをセット(1)してサブシステム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 1   | 0   | 0    | 0 | 0 | 0    | 0    |

④ CKC レジスタの CLS ビットが 1 になったことを確認して、HIOSTOP をセット(1)し、高速オンチップ・オシレータを停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | X      | 0 | 0 | 0 | 0 | Х     | 1       |

レジスタ図の設定値

## 1.1.3 高速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え

CPU クロックを高速オンチップ・オシレータ・クロックから高速システム・クロックに変更する場合、クロック動作モード制御レジスタ(CMC)、発振安定時間選択レジスタ(OSTS)、クロック動作ステータス制御レジスタ(CSC)で発振回路の設定と発振開始を行います。次に、発振安定時間カウンタ状態レジスタ(OSTC)で発振の安定待ちを行います。

発振安定時間経過後、システム・クロック制御レジスタ(CKC)で高速システム・クロックを fclk に設定します。

メイン・システム・クロックのステータスが高速システム・クロックに切り替わったのを確認し、高速オンチップ・オシレータを停止します。

① CMC レジスタの OSCSEL ビットをセット(1)し、fx > 10MHz の場合は AMPH ビットをセット(1)して X1 発振回路を動作させます。外部クロックを使用される場合は EXCLK ビットと OSCSEL ビットをセット(1)してください。

| _   | 7     | 6      | 5      | 4       | 3 | 2      | 1      | 0    |

|-----|-------|--------|--------|---------|---|--------|--------|------|

| CMC | EXCLK | OSCSEL | EXCLKS | OSCSELS | 0 | AMPHS1 | AMPHS0 | AMPH |

|     | 0/1   | 1      | Х      | Х       | 0 | Х      | Х      | 0/1  |

AMPH ビット: X1 発振クロックが 10 MHz 以下の場合は 0 を設定してください。

② OSTS レジスタで X1 発振回路の発振安定時間を選択します。外部クロックでは設定不要です。 例)10MHz の発振子で 102µs 以上までウエイトする場合は、以下の値に設定してください。

|      | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|------|---|---|---|---|---|-------|-------|-------|

| OSTS | 0 | 0 | 0 | 0 | 0 | OSTS2 | OSTS1 | OSTS0 |

|      | 0 | 0 | 0 | 0 | 0 | 0     | 1     | 0     |

③ CSC レジスタの MSTOP ビットをクリア(0)して X1 発振回路の発振を開始します。外部クロック使用 時は、MSTOP ビットをクリア(0)する前に外部クロック信号を入力してください。

| _   | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | X      | 0 | 0 | 0 | 0 | Χ     | 0       |

④ OSTC レジスタで X1 発振回路の発振安定待ちを行います。外部クロックでは発振安定待ちは不要です。

例) 10MHz の発振子で 102μs 以上までウエイトする場合は、以下の値になるまでウエイトしてください。

| ,    | 7     | 6     | 5      | 4      | 3      | 2      | 1      | 0      |

|------|-------|-------|--------|--------|--------|--------|--------|--------|

| OSTC | MOST8 | MOST9 | MOST10 | MOST11 | MOST13 | MOST15 | MOST17 | MOST18 |

|      | 1     | 1     | 1      | 0      | 0      | 0      | 0      | 0      |

⑤ CKC レジスタの MCM0 ビットをセット(1)して高速システム・クロックをメイン・システム・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 0   | 0   | 1    | 0 | 0 | 0    | 0    |

レジスタ図の設定値

⑥ CKC レジスタの MCS ビットが 1 になったことを確認して、HIOSTOP をセット(1)し、高速オンチップ・オシレータを停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | Χ      | 0 | 0 | 0 | 0 | Χ     | 1       |

レジスタ図の設定値

#### 1.1.4 高速オンチップ・オシレータ・クロックからサブ・クロックへの切り替え

CPU クロックを高速オンチップ・オシレータ・クロックからサブ・クロックに変更する場合、サブシステム・クロック供給モード制御レジスタ(OSMC)、クロック動作モード制御レジスタ(CMC)、クロック動作ステータス制御レジスタ(CSC)で発振回路の設定と発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)でサブ・クロックを $f_{CLK}$ に設定します。CPU/周辺ハードウエア・クロックのステータスがサブシステム・クロックに切り替わったのを確認し、高速オンチップ・オシレータを停止します。

① 本アプリケーションノートでは、サブシステム・クロック用発振子の発振安定時間を 12 ビット・インターバル・タイマでカウントします。12 ビット・インターバル・タイマのカウント・クロックに低速オンチップ・オシレータ・クロックを使用するため、WUTMMCK0 ビットに1を設定します。なお、STOPモード時または HALT モード時(サブシステム・クロックで CPU 動作中の場合)にリアルタイム・クロック、12 ビット・インターバル・タイマのみサブシステム・クロックで動作させる場合は RTCLPCビットに1を設定します。

|      | 7      | 6 | 5 | 4        | 3 | 2 | 1 | 0 |

|------|--------|---|---|----------|---|---|---|---|

| OSMC | RTCLPC | 0 | 0 | WUTMMCK0 | 0 | 0 | 0 | 0 |

|      | Χ      | Х | Χ | 1        | 0 | Х | Х | Χ |

② CMC レジスタの OSCSELS ビットをセット(1)して XT 発振回路を動作させます。外部クロックを使用される場合は EXCLKS ビットと OSCSELS ビットをセット(1)してください。

|     | 7     | 6      | 5      | 4       | 3 | 2      | 1      | 0    |

|-----|-------|--------|--------|---------|---|--------|--------|------|

| CMC | EXCLK | OSCSEL | EXCLKS | OSCSELS | 0 | AMPHS1 | AMPHS0 | AMPH |

|     | Х     | Х      | 0/1    | 1       | 0 | 0/1    | 0/1    | Χ    |

③ CSC レジスタの XTSTOP ビットをクリア(0)して XT1 発振回路の発振を開始します。外部クロック使用時は、XTSTOP ビットをクリア(0)する前に外部クロック信号を入力してください。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Χ     | 0      | 0 | 0 | 0 | 0 | Χ     | 0       |

- ④ サブシステム・クロック用発振子の発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間)はタイマ機能などを用いてカウントします。本アプリケーションノートでは12 ビット・インターバル・タイマを用いてカウントします。外部クロックでは発振安定待ちは不要です。

- ⑤ CKC レジスタの CSS ビットをセット(1)してサブシステム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 1   | 0   | 0    | 0 | 0 | 0    | 0    |

⑥ CKC レジスタの CLS ビットが 1 になったことを確認して、HIOSTOP をセット(1)し、高速オンチップ・オシレータを停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | 0      | 0 | 0 | 0 | 0 | X     | 1       |

レジスタ図の設定値

# 1.1.5 中速オンチップ・オシレータ・クロックから高速オンチップ・オシレータ・クロック への切り替え

CPU クロックを中速オンチップ・オシレータ・クロックから高速オンチップ・オシレータ・クロックに変更する場合、クロック動作ステータス制御レジスタ(CSC)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で高速オンチップ・オシレータ・クロックをfclkに設定します。

メイン・オンチップ・オシレータ・クロックのステータスが高速オンチップ・オシレータ・クロックに切り替わったのを確認し、中速オンチップ・オシレータを停止します。

① CSC レジスタの HIOSTOP ビットをクリア(0)して高速オンチップ・オシレータを動作させます。

| -   | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | X      | 0 | 0 | 0 | 0 | 1     | 0       |

- ② 高速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 65µs) はタイマ機能などを用いてカウントします。

- ③ CKC レジスタの MCM1 ビットをクリア(0)して高速オンチップ・オシレータ・クロックをメイン・オンチップ・オシレータ・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 0   | 0   | 0    | 0 | 0 | 1    | 0    |

④ CKC レジスタの MCS1 ビットが 0 になったことを確認して、MIOEN をクリア(0)し、中速オンチップ・オシレータを停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | Х      | 0 | 0 | 0 | 0 | 0     | 0       |

レジスタ図の設定値

1.1.6 中速オンチップ・オシレータ・クロックから低速オンチップ・オシレータ・クロック への切り替え

CPU クロックを中速オンチップ・オシレータ・クロックから低速オンチップ・オシレータ・クロックに変更する場合、サブシステム・クロック選択レジスタ(CKSEL)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で低速オンチップ・オシレータ・クロックを $f_{CLK}$ に設定します。CPU/周辺ハードウエア・クロックのステータスがサブシステム・クロックに切り替わったのを確認し、中速オンチップ・オシレータを停止します。

① CKSEL レジスタの SELLOSC ビットをセット(1)して低速オンチップ・オシレータを動作させます。

|       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| CKSEL | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SELLOSC |

|       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1       |

- ② 低速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 210µs) はタイマ機能などを用いてカウントします。本アプリケーションノートでは、常時低速オンチップ・オシレータを動作させているため、発振の安定待ちを行っておりません。

- ③ CKC レジスタの CSS ビットをセット(1)してサブシステム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | мсм0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 1   | 0   | 0    | 0 | 0 | 1    | 1    |

④ CKC レジスタの CLS ビットが 1 になったことを確認して、MIOEN をクリア(0)し、中速オンチップ・オシレータを停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | X     | X      | 0 | 0 | 0 | 0 | 0     | Х       |

レジスタ図の設定値

## 1.1.7 中速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え

CPU クロックを中速オンチップ・オシレータ・クロックから高速システム・クロックに変更する場合、クロック動作モード制御レジスタ(CMC)、発振安定時間選択レジスタ(OSTS)、クロック動作ステータス制御レジスタ(CSC)で発振回路の設定と発振開始を行います。次に、発振安定時間カウンタ状態レジスタ(OSTC)で発振の安定待ちを行います。

発振安定時間経過後、システム・クロック制御レジスタ(CKC)で高速システム・クロックを fclk に設定します。

メイン・システム・クロックのステータスが高速システム・クロックに切り替わったのを確認し、中速オンチップ・オシレータを停止します。

① CMC レジスタの OSCSEL ビットをセット(1)し、fx > 10MHz の場合は AMPH ビットをセット(1)して X1 発振回路を動作させます。外部クロックを使用される場合は EXCLK ビットと OSCSEL ビットをセット(1)してください。

|     | 7     | 6      | 5      | 4       | 3 | 2      | 1      | 0    |

|-----|-------|--------|--------|---------|---|--------|--------|------|

| CMC | EXCLK | OSCSEL | EXCLKS | OSCSELS | 0 | AMPHS1 | AMPHS0 | AMPH |

|     | 0/1   | 1      | Χ      | X       | 0 | X      | Х      | 0/1  |

AMPH ビット: X1 発振クロックが 10 MHz 以下の場合は 0 を設定してください。

② OSTS レジスタで X1 発振回路の発振安定時間を選択します。外部クロックでは設定不要です。 例)10MHz の発振子で 102µs 以上までウエイトする場合は、以下の値に設定してください。

|      | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|------|---|---|---|---|---|-------|-------|-------|

| OSTS | 0 | 0 | 0 | 0 | 0 | OSTS2 | OSTS1 | OSTS0 |

|      | 0 | 0 | 0 | 0 | 0 | 0     | 1     | 0     |

③ CSC レジスタの MSTOP ビットをクリア(0)して X1 発振回路の発振を開始します。外部クロック使用 時は、MSTOP ビットをクリア(0)する前に外部クロック信号を入力してください。

| _   | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | X      | 0 | 0 | 0 | 0 | 1     | Х       |

④ OSTC レジスタで X1 発振回路の発振安定待ちを行います。外部クロックでは発振安定待ちは不要です。

例) 10MHz の発振子で 102μs 以上までウエイトする場合は、以下の値になるまでウエイトしてください。

| ,    | 7     | 6     | 5      | 4      | 3      | 2      | 1      | 0      |

|------|-------|-------|--------|--------|--------|--------|--------|--------|

| OSTC | MOST8 | MOST9 | MOST10 | MOST11 | MOST13 | MOST15 | MOST17 | MOST18 |

|      | 1     | 1     | 1      | 0      | 0      | 0      | 0      | 0      |

⑤ CKC レジスタの MCM0 ビットをセット(1)して高速システム・クロックをメイン・システム・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 0   | 0   | 1    | 0 | 0 | 1    | 1    |

レジスタ図の設定値

⑥ CKC レジスタの MCS ビットが 1 になったことを確認して、MIOEN をクリア(0)し、中速オンチップ・オシレータを停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | Χ      | 0 | 0 | 0 | 0 | 0     | Х       |

レジスタ図の設定値

#### 1.1.8 中速オンチップ・オシレータ・クロックからサブ・クロックへの切り替え

CPU クロックを中速オンチップ・オシレータ・クロックからサブ・クロックに変更する場合、サブシステム・クロック供給モード制御レジスタ(OSMC)、クロック動作モード制御レジスタ(CMC)、クロック動作ステータス制御レジスタ(CSC)で発振回路の設定と発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)でサブ・クロックを $f_{CLK}$ に設定します。CPU/周辺ハードウエア・クロックのステータスがサブシステム・クロックに切り替わったのを確認し、中速オンチップ・オシレータを停止します。

① 本アプリケーションノートでは、サブシステム・クロック用発振子の発振安定時間を 12 ビット・インターバル・タイマでカウントします。12 ビット・インターバル・タイマのカウント・クロックに低速オンチップ・オシレータ・クロックを使用するため、WUTMMCK0 ビットに1を設定します。なお、STOPモード時または HALT モード時(サブシステム・クロックで CPU 動作中の場合)にリアルタイム・クロック、12 ビット・インターバル・タイマのみサブシステム・クロックで動作させる場合は RTCLPCビットに1を設定します。

|      | 7      | 6 | 5 | 4        | 3 | 2 | 1 | 0 |

|------|--------|---|---|----------|---|---|---|---|

| OSMC | RTCLPC | 0 | 0 | WUTMMCK0 | 0 | 0 | 0 | 0 |

|      | Х      | Х | Х | 1        | 0 | Х | Х | Х |

② CMC レジスタの OSCSELS ビットをセット(1)して XT 発振回路を動作させます。外部クロックを使用される場合は EXCLKS ビットと OSCSELS ビットをセット(1)してください。

|     | 7     | 6      | 5      | 4       | 3 | 2      | 1      | 0    |

|-----|-------|--------|--------|---------|---|--------|--------|------|

| CMC | EXCLK | OSCSEL | EXCLKS | OSCSELS | 0 | AMPHS1 | AMPHS0 | AMPH |

|     | Х     | Х      | 0/1    | 1       | 0 | 0/1    | 0/1    | Х    |

③ CSC レジスタの XTSTOP ビットをクリア(0)して XT1 発振回路の発振を開始します。外部クロック使用時は、XTSTOP ビットをクリア(0)する前に外部クロック信号を入力してください。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |  |

|-----|-------|--------|---|---|---|---|-------|---------|--|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |  |

|     | Х     | 0      | 0 | 0 | 0 | 0 | 1     | Х       |  |

- ④ サブシステム・クロック用発振子の発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間)はタイマ機能などを用いてカウントします。本アプリケーションノートでは12 ビット・インターバル・タイマを用いてカウントします。外部クロックでは発振安定待ちは不要です。

- ⑤ CKC レジスタの CSS ビットをセット(1)してサブシステム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 1   | 0   | 0    | 0 | 0 | 1    | 1    |

⑥ CKC レジスタの CLS ビットが 1 になったことを確認して、MIOEN をクリア(0)し、中速オンチップ・オシレータを停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | 0      | 0 | 0 | 0 | 0 | 0     | Χ       |

レジスタ図の設定値

# 1.1.9 低速オンチップ・オシレータ・クロックから高速オンチップ・オシレータ・クロック への切り替え

CPU クロックを低速オンチップ・オシレータ・クロックから高速オンチップ・オシレータ・クロックに変更する場合、クロック動作ステータス制御レジスタ(CSC)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で高速オンチップ・オシレータ・クロックをfclkに設定します。

CPU/周辺ハードウエア・クロックのステータスがメイン・システム・クロックに切り替わったのを確認し、低速オンチップ・オシレータを停止します。

① CSC レジスタの HIOSTOP ビットをクリア(0)して高速オンチップ・オシレータを動作させます。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | X     | X      | 0 | 0 | 0 | 0 | X     | 0       |

- ② 高速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 65µs) はタイマ機能などを用いてカウントします。

- ③ CKC レジスタの CSS ビットをクリア(0)してメイン・システム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 1   | 0   | 0   | 0    | 0 | 0 | 0    | 0    |

④ CKC レジスタの CLS ビットが 0 になったことを確認して、サブシステム・クロック選択レジスタ (CKSEL)の SELLOSC をクリア(0)し、低速オンチップ・オシレータを停止します。本アプリケーション ノートでは、サブシステム・クロック供給モード制御レジスタ(OSMC)の WUTMMCK0 ビットが 1 となっている為、低速オンチップ・オシレータは停止しません。

| ·     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| CKSEL | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SELLOSC |

|       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0       |

注 CPU/周辺ハードウエア・クロックがサブシステム・クロックで動作中に MCMO ビットの値を変更することは禁止です。

レジスタ図の設定値

# 1.1.10 低速オンチップ・オシレータ・クロックから中速オンチップ・オシレータ・クロックへの 切り替え

CPU クロックを低速オンチップ・オシレータ・クロックから中速オンチップ・オシレータ・クロックに変更する場合、クロック動作ステータス制御レジスタ(CSC)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で中速オンチップ・オシレータ・クロックを $f_{CLK}$ に設定します。

CPU/周辺ハードウエア・クロックのステータスがメイン・システム・クロックに切り替わったのを確認し、低速オンチップ・オシレータを停止します。

① CSC レジスタの MIOEN ビットをセット(1)して中速オンチップ・オシレータを動作させます。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | Х      | 0 | 0 | 0 | 0 | 1     | Х       |

- ② 中速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 4us) はタイマ機能などを用いてカウントします。

- ③ CKC レジスタの CSS ビットをクリア(0)してメイン・システム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 1   | 0   | 0   | 0    | 0 | 0 | 1    | 1    |

④ CKC レジスタの CLS ビットが 0 になったことを確認して、サブシステム・クロック選択レジスタ (CKSEL)の SELLOSC をクリア(0)し、低速オンチップ・オシレータを停止します。本アプリケーション ノートでは、サブシステム・クロック供給モード制御レジスタ(OSMC)の WUTMMCK0 ビットが 1 となっている為、低速オンチップ・オシレータは停止しません。

|       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| CKSEL | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SELLOSC |

|       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0       |

注 CPU/周辺ハードウエア・クロックがサブシステム・クロックで動作中に MCMO ビットの値を変更することは禁止です。

レジスタ図の設定値

## 1.1.11 低速オンチップ・オシレータ・クロックから高速システム・クロックへの切り替え

CPU クロックを低速オンチップ・オシレータ・クロックから高速システム・クロックに変更する場合、ク ロック動作モード制御レジスタ(CMC)、発振安定時間選択レジスタ(OSTS)、クロック動作ステータス制御レ ジスタ(CSC)で発振回路の設定と発振開始を行います。次に、発振安定時間カウンタ状態レジスタ(OSTC)で 発振の安定待ちを行います。

発振安定時間経過後、システム・クロック制御レジスタ(CKC)で高速システム・クロックを fclk に設定 します。

CPU/周辺ハードウエア・クロックのステータスがメイン・システム・クロックに切り替わったのを確認 し、低速オンチップ・オシレータを停止します。

① CMC レジスタの OSCSEL ビットをセット(1)し、fx > 10MHz の場合は AMPH ビットをセット(1)して X1 発振回路を動作させます。外部クロックを使用される場合は EXCLK ビットと OSCSEL ビットを セット(1)してください。

|     | 7     | 6      | 5      | 4       | 3 | 2      | 1      | 0    |

|-----|-------|--------|--------|---------|---|--------|--------|------|

| CMC | EXCLK | OSCSEL | EXCLKS | OSCSELS | 0 | AMPHS1 | AMPHS0 | AMPH |

|     | 0/1   | 1      | Χ      | X       | 0 | Х      | Х      | 0/1  |

AMPH ビット: X1 発振クロックが 10 MHz 以下の場合は 0 を設定してください。

② OSTS レジスタで X1 発振回路の発振安定時間を選択します。外部クロックでは設定不要です。 例) 10MHz の発振子で 102μs 以上までウエイトする場合は、以下の値に設定してください。

|      | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|------|---|---|---|---|---|-------|-------|-------|

| OSTS | 0 | 0 | 0 | 0 | 0 | OSTS2 | OSTS1 | OSTS0 |

|      | 0 | 0 | 0 | 0 | 0 | 0     | 1     | 0     |

③ CSC レジスタの MSTOP ビットをクリア(0)して X1 発振回路の発振を開始します。外部クロック使用 時は、MSTOP ビットをクリア(0)する前に外部クロック信号を入力してください。

| _   | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | X      | 0 | 0 | 0 | 0 | Χ     | Х       |

④ OSTC レジスタで X1 発振回路の発振安定待ちを行います。外部クロックでは発振安定待ちは不要で

例) 10MHz の発振子で 102μs 以上までウエイトする場合は、以下の値になるまでウエイトしてくだ さい。

|      | 1     | 1     | 1      | 0      | 0      | 0      | 0      | 0      |

|------|-------|-------|--------|--------|--------|--------|--------|--------|

| OSTC | MOST8 | MOST9 | MOST10 | MOST11 | MOST13 | MOST15 | MOST17 | MOST18 |

|      | 7     | 6     | 5      | 4      | 3      | 2      | 1      | 0      |

⑤ CKC レジスタの CSS ビットをクリア(0)してメイン・システム・クロックを CPU/周辺ハードウエア・ クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 1   | 0   | 1   | 1    | 0 | 0 | 0    | 0    |

レジスタ図の設定値

⑥ CKC レジスタの CLS ビットが 0 になったことを確認して、サブシステム・クロック選択レジスタ (CKSEL)の SELLOSC をクリア(0)し、低速オンチップ・オシレータを停止します。本アプリケーション ノートでは、サブシステム・クロック供給モード制御レジスタ(OSMC)の WUTMMCK0 ビットが 1 となっている為、低速オンチップ・オシレータは停止しません。

| ·     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| CKSEL | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SELLOSC |

|       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0       |

注 CPU/周辺ハードウエア・クロックがサブシステム・クロックで動作中に MCM0 ビットの値を変更することは禁止です。

レジスタ図の設定値

## 1.1.12 高速システム・クロックから高速オンチップ・オシレータ・クロックへの切り替え

CPU クロックを高速システム・クロックから高速オンチップ・オシレータ・クロックに変更する場合、クロック動作ステータス制御レジスタ(CSC)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で高速オンチップ・オシレータ・クロックを  $f_{CLK}$ に設定します。

メイン・システム・クロックのステータスがメイン・オンチップ・オシレータ・クロックに切り替わったのを確認し、X1 発振回路を停止します。

① CSC レジスタの HIOSTOP ビットをクリア(0)して高速オンチップ・オシレータを動作させます。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | Х      | 0 | 0 | 0 | 0 | Х     | 0       |

- ② 高速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 65μs) はタイマ機能などを用いてカウントします。

- ③ CKC レジスタの MCM0 ビットをクリア(0)してメイン・オンチップ・オシレータ・クロックをメイン・システム・クロックに設定します。

| _   | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 0   | 1   | 0    | 0 | 0 | 0    | 0    |

④ CKC レジスタの MCS ビットが 0 になったことを確認して、MSTOP をセット(1)し、X1 発振回路を 停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 1     | Χ      | 0 | 0 | 0 | 0 | Х     | 0       |

レジスタ図の設定値

## 1.1.13 高速システム・クロックから中速オンチップ・オシレータ・クロックへの切り替え

CPU クロックを高速システム・クロックから中速オンチップ・オシレータ・クロックに変更する場合、クロック動作ステータス制御レジスタ(CSC)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で中速オンチップ・オシレータ・クロックを $f_{CLK}$ に設定します。

メイン・システム・クロックのステータスがメイン・オンチップ・オシレータ・クロックに切り替わったのを確認し、X1発振回路を停止します。

① CSC レジスタの MIOEN ビットをセット(1)して中速オンチップ・オシレータを動作させます。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | Х      | 0 | 0 | 0 | 0 | 1     | X       |

- ② 中速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間4µs)はタイマ機能などを用いてカウントします。

- ③ CKC レジスタの MCM0 ビットをクリア(0)してメイン・オンチップ・オシレータ・クロックをメイン・システム・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 0   | 1   | 0    | 0 | 0 | 1    | 1    |

④ CKC レジスタの MCS ビットが 0 になったことを確認して、MSTOP をセット(1)し、X1 発振回路を 停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 1     | X      | 0 | 0 | 0 | 0 | 1     | X       |

レジスタ図の設定値

## 1.1.14 高速システム・クロックから低速オンチップ・オシレータ・クロックへの切り替え

CPU クロックを高速システム・クロックから低速オンチップ・オシレータ・クロックに変更する場合、サブシステム・クロック選択レジスタ(CKSEL)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で低速オンチップ・オシレータ・クロックを fclk に設定します。CPU/周辺ハードウエア・クロックのステータスがサブシステム・クロックに切り替わったのを確認し、X1発振回路を停止します。

① CKSEL レジスタの SELLOSC ビットをセット(1)して低速オンチップ・オシレータを動作させます。

|       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| CKSEL | 0 | 0 | 0 | 0 | 0 | 0 | 0 | SELLOSC |

|       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1       |

- ② 低速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 210µs) はタイマ機能などを用いてカウントします。本アプリケーションノートでは、常時低速オンチップ・オシレータを動作させているため、発振の安定待ちを行っておりません。

- ③ CKC レジスタの CSS ビットをセット(1)してサブシステム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 1   | 1   | 1    | 0 | 0 | 0    | 0    |

④ CKC レジスタの CLS ビットが 1 になったことを確認して、MSTOP をセット(1)し、X1 発振回路を停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 1     | Χ      | 0 | 0 | 0 | 0 | Х     | X       |

レジスタ図の設定値

## 1.1.15 高速システム・クロックからサブ・クロックへの切り替え

CPU クロックを高速システム・クロックからサブ・クロックに変更する場合、サブシステム・クロック供給モード制御レジスタ(OSMC)、クロック動作モード制御レジスタ(CMC)、クロック動作ステータス制御レジスタ(CSC)で発振回路の設定と発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)でサブ・クロックを $f_{CLK}$ に設定します。CPU/周辺ハードウエア・クロックのステータスがサブシステム・クロックに切り替わったのを確認し、X1発振回路を停止します。

① 本アプリケーションノートでは、サブシステム・クロック用発振子の発振安定時間を 12 ビット・インターバル・タイマでカウントします。12 ビット・インターバル・タイマのカウント・クロックに低速オンチップ・オシレータ・クロックを使用するため、WUTMMCK0 ビットに1を設定します。なお、STOPモード時または HALT モード時(サブシステム・クロックで CPU 動作中の場合)にリアルタイム・クロック、12 ビット・インターバル・タイマのみサブシステム・クロックで動作させる場合は RTCLPCビットに1を設定します。

|      | 7      | 6 | 5 | 4        | 3 | 2 | 1 | 0 |

|------|--------|---|---|----------|---|---|---|---|

| OSMC | RTCLPC | 0 | 0 | WUTMMCK0 | 0 | 0 | 0 | 0 |

|      | X      | Х | Χ | 1        | 0 | Χ | X | X |

② CSC レジスタの XTSTOP ビットをクリア(0)して XT1 発振回路の発振を開始します。外部クロック使用時は、XTSTOP ビットをクリア(0)する前に外部クロック信号を入力してください。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | 0      | 0 | 0 | 0 | 0 | Х     | Х       |

- ③ サブシステム・クロック用発振子の発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間)はタイマ機能などを用いてカウントします。本アプリケーションノートでは12 ビット・インターバル・タイマを用いてカウントします。外部クロックでは発振安定待ちは不要です。

- ④ CKC レジスタの CSS ビットをセット(1)してサブシステム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 0   | 1   | 1   | 1    | 0 | 0 | 0    | 0    |

⑤ CKC レジスタの CLS ビットが 1 になったことを確認して、MSTOP をセット(1)し、高速オンチップ・オシレータを停止します。

| _   | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 1     | 0      | 0 | 0 | 0 | 0 | Χ     | X       |

レジスタ図の設定値

#### 1.1.16 サブ・クロックから高速オンチップ・オシレータ・クロックへの切り替え

CPU クロックをサブ・クロックから高速オンチップ・オシレータ・クロックに変更する場合、クロック動作ステータス制御レジスタ(CSC)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で高速オンチップ・オシレータ・クロックをfclkに設定します。

CPU/周辺ハードウエア・クロックのステータスがメイン・システム・クロックに切り替わったのを確認し、XT1発振回路を停止します。

① CSC レジスタの HIOSTOP ビットをクリア(0)して高速オンチップ・オシレータを動作させます。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | X     | 0      | 0 | 0 | 0 | 0 | Χ     | 0       |

- ② 高速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 65µs) はタイマ機能などを用いてカウントします。

- ③ CKC レジスタの CSS ビットをクリア(0)してメイン・システム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 1   | 0   | 0   | 0    | 0 | 0 | 0    | 0    |

④ CKC レジスタの CLS ビットが 0 になったことを確認して、XTSTOP をセット(1)し、XT1 発振回路を 停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | 1      | 0 | 0 | 0 | 0 | Х     | 0       |

注 CPU/周辺ハードウエア・クロックがサブシステム・クロックで動作中に MCMO ビットの値を変更することは禁止です。

レジスタ図の設定値

#### 1.1.17 サブ・クロックから中速オンチップ・オシレータ・クロックへの切り替え

CPU クロックをサブ・クロックから中速オンチップ・オシレータ・クロックに変更する場合、クロック動作ステータス制御レジスタ(CSC)で発振開始を行います。次に、タイマ等で発振の安定待ちを行います。発振安定時間経過後、システム・クロック制御レジスタ(CKC)で中速オンチップ・オシレータ・クロックをfclkに設定します。

CPU/周辺ハードウエア・クロックのステータスがメイン・システム・クロックに切り替わったのを確認し、XT1発振回路を停止します。

① CSC レジスタの MIOEN ビットをセット(1)して中速オンチップ・オシレータを動作させます。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | X     | 0      | 0 | 0 | 0 | 0 | 1     | Х       |

- ② 中速オンチップ・オシレータの発振が安定するまでソフトウエアでウエイトします。ウエイト時間(発振安定時間 4µs) はタイマ機能などを用いてカウントします。

- ③ CKC レジスタの CSS ビットをクリア(0)してメイン・システム・クロックを CPU/周辺ハードウエア・クロックに設定します。

|     | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 1   | 0   | 0   | 0    | 0 | 0 | 1    | 1    |

④ CKC レジスタの CLS ビットが 0 になったことを確認して、XTSTOP をセット(1)し、XT1 発振回路を 停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | Х     | 1      | 0 | 0 | 0 | 0 | 1     | Х       |

注 CPU/周辺ハードウエア・クロックがサブシステム・クロックで動作中に MCM0 ビットの値を変更することは禁止です。

レジスタ図の設定値

## 1.1.18 サブ・クロックから高速システム・クロックへの切り替え

CPU クロックをサブ・クロックから高速システム・クロックに変更する場合、クロック動作モード制御レジスタ(CMC)、発振安定時間選択レジスタ(OSTS)、クロック動作ステータス制御レジスタ(CSC)で発振回路の設定と発振開始を行います。次に、発振安定時間カウンタ状態レジスタ(OSTC)で発振の安定待ちを行います。

発振安定時間経過後、システム・クロック制御レジスタ(CKC)で高速システム・クロックを fclk に設定します。

CPU/周辺ハードウエア・クロックのステータスがメイン・システム・クロックに切り替わったのを確認し、XT1 発振回路を停止します。

① OSTS レジスタで X1 発振回路の発振安定時間を選択します。外部クロックでは設定不要です。 例)10MHz の発振子で 102µs 以上までウエイトする場合は、以下の値に設定してください。

|      | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|------|---|---|---|---|---|-------|-------|-------|

| OSTS | 0 | 0 | 0 | 0 | 0 | OSTS2 | OSTS1 | OSTS0 |

|      | 0 | 0 | 0 | 0 | 0 | 0     | 1     | 0     |

② CSC レジスタの MSTOP ビットをクリア(0)して X1 発振回路の発振を開始します。外部クロック使用 時は、MSTOP ビットをクリア(0)する前に外部クロック信号を入力してください。

| _   | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | 0      | 0 | 0 | 0 | 0 | Х     | X       |

③ OSTC レジスタで X1 発振回路の発振安定待ちを行います。外部クロックでは発振安定待ちは不要です。

例) 10MHz の発振子で 102μs 以上までウエイトする場合は、以下の値になるまでウエイトしてください。

|      | 7     | 6     | 5      | 4      | 3      | 2      | 1      | 0      |

|------|-------|-------|--------|--------|--------|--------|--------|--------|

| OSTC | MOST8 | MOST9 | MOST10 | MOST11 | MOST13 | MOST15 | MOST17 | MOST18 |

|      | 1     | 1     | 1      | 0      | 0      | 0      | 0      | 0      |

④ CKC レジスタの CSS ビットをクリア(0)してメイン・システム・クロックを CPU/周辺ハードウエア・クロックに設定します。

| _   | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

|-----|-----|-----|-----|------|---|---|------|------|

| CKC | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|     | 1   | 0   | 1   | 1    | 0 | 0 | 0    | 0    |

⑤ CKC レジスタの CLS ビットが 0 になったことを確認して、XTSTOP をセット(1)し、XT1 発振回路を 停止します。

|     | 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-----|-------|--------|---|---|---|---|-------|---------|

| CSC | MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

|     | 0     | 1      | 0 | 0 | 0 | 0 | Х     | Х       |

注 CPU/周辺ハードウエア・クロックがサブシステム・クロックで動作中に MCMO ビットの値を変更することは禁止です。

レジスタ図の設定値

## 2. 動作確認条件

本アプリケーションノートのサンプルコードは、下記の条件で動作を確認しています。

表 2.1 動作確認条件

| 項目                 | 内容                                                     |

|--------------------|--------------------------------------------------------|

| 使用マイコン             | RL78/I1D (R5F117GC)                                    |

| 動作周波数              | ● 高速オンチップ・オシレータ・クロック:24MHz                             |

|                    | ● 中速オンチップ・オシレータ・クロック:4MHz                              |

|                    | ● 低速オンチップ・オシレータ・クロック:15kHz                             |

|                    | ● 高速システム・クロック: 20MHz                                   |

|                    | ● サブシステム・クロック: 32.768KHz                               |

|                    | ● CPU/周辺ハードウエア・クロック:                                   |

|                    | 24MHz/20MHz/4MHz/32.768kHz/15kHz <sup>注</sup>          |

| 動作電圧               | 3.3V (2.9V~5.5V で動作可能)                                 |

|                    | LVD 動作(V <sub>LVD</sub> ):リセット・モード 2.81V (2.76V~2.87V) |

| 統合開発環境 (CS+)       | ルネサス エレクトロニクス製                                         |

|                    | CS+ for CC V4.01.00                                    |

| C コンパイラ (CS+)      | ルネサス エレクトロニクス製                                         |

|                    | CC-RL V1.02.00                                         |

| 統合開発環境 (e² studio) | ルネサス エレクトロニクス製                                         |

|                    | e <sup>2</sup> studio V5.2.0.020                       |

| Cコンパイラ (e² studio) | ルネサス エレクトロニクス製                                         |

|                    | CC-RL V1.02.00                                         |

| 使用ボード              | ルネサス エレクトロニクス製                                         |

|                    | RL78/I1D Target board(RTE5117GC0TGB0000R)              |

注 アプリケーションでは、CPU/周辺ハードウエア・クロックの設定を切替えています。

## 3. 動作確認条件

本アプリケーションノートに関連するアプリケーションノートを以下に示します。併せて参照してください。

RL78/I1D オペレーション・ステートの切り替え CC-RL (R01AN3095J) アプリケーションノート

## 4. ハードウエア説明

#### 4.1 ハードウエア構成例

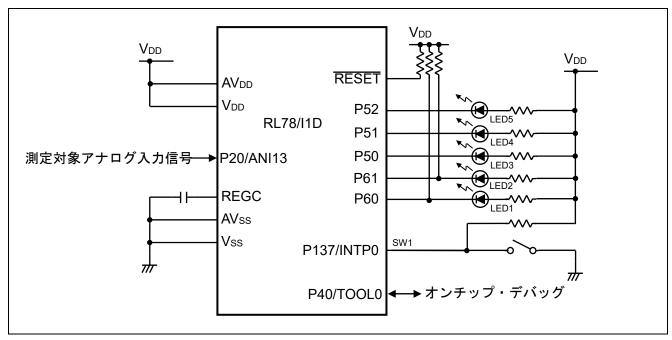

図 4.1に本アプリケーションノートで使用するハードウエア構成例を示します。

図 4.1 ハードウエア構成

- 注意 1 この回路イメージは接続の概要を示す為に簡略化しています。実際に回路を作成される場合は、端子処理などを適切に行い、電気的特性を満たすように設計してください(入力専用ポートは個別に抵抗を介して  $V_{DD}$  又は  $V_{SS}$  に接続して下さい)。

- 2  $EV_{SS}$ で始まる名前の端子がある場合には  $V_{SS}$ に、 $EV_{DD}$ で始まる名前の端子がある場合には  $V_{DD}$ に それぞれ接続してください。

- 3  $V_{DD}$ は LVD にて設定したリセット解除電圧  $(V_{LVD})$  以上にしてください。

- 4 P60,P61 は N-ch オープン・ドレイン出力となり、Hi-Z では貫通電流が流れる可能性がありますので、 抵抗を介して VDD に接続してください。

## 4.2 使用端子一覧

表 4.1に使用端子と機能を示します。

| 端子名        | 入出力 | 内容                  |

|------------|-----|---------------------|

| P137/INTP0 | 入力  | スイッチ(SW1)入力ポート      |

| P20/AIN13  | 入力  | A/D コンバータ アナログ入力ポート |

| P60        | 出力  | LED 点灯(LED1)制御ポート   |

| P61        | 出力  | LED 点灯(LED2)制御ポート   |

| P50        | 出力  | LED 点灯(LED3)制御ポート   |

| P51        | 出力  | LED 点灯(LED4)制御ポート   |

| P52        | 出力  | LED 点灯(LED5)制御ポート   |

表 4.1 使用端子と機能

#### 5. ソフトウエア説明

#### 5.1 動作概要

本アプリケーションノートでは、スイッチ入力により、CPU クロックと動作モードを切り替えます。 CPU クロックと動作モードの切り替えは、図 1.1 動作モード状態移行図の 1 から 39 の順に行います。

- (1) 入出力ポートの初期設定を行います。

- ・ P50-P52、P60-P61 端子: 出力ポートに設定(LED 点灯制御で使用します)。

- P137/INTP0 端子:入力ポートに設定(スイッチ入力で使用します)。

- P20/ANI13 端子: アナログ入力ポートに設定(A/D 変換のアナログ入力チャネルとして使用します)。

- (2) クロック発生回路の初期設定を行います。

#### <設定条件>

- フラッシュの動作モードを HS(高速メイン)モードに設定します (ユーザ・オプション・バイト (000C2H/010C2H)で設定します)。

- 高速オンチップ・オシレータ・クロックの周波数を 24MHz に設定します。

- サブシステム・クロック端子の動作モードを XT1 発振モードに設定し、XT1/123 端子および XT2/EXCLKS/P124 端子に水晶振動子を接続します。

- XT1 発振回路の発振モードを超低消費発振に設定します (接続する発振子に最適な発振モードを選択します)。

- 高速システム・クロック端子の動作モードを X1 発振モードに設定し、X1/P121 端子および X2/EXCLK/P122 端子に水晶振動子を接続します。

- CPU/周辺ハードウエア・クロック( $f_{CLK}$ )にメイン・システム・クロック( $f_{MAIN}$ )を選択します。

- (3) 割り込み処理の初期設定を行います。

- INTPO 端子の有効エッジを立ち下がりエッジに設定し、スイッチ入力を有効にします。

- ・ スイッチ入力の判定には、12 ビット・インターバル・タイマを使用します。約5ms 間隔で端子の 電圧レベルを確認し、電圧レベルが2回連続で一致した場合、有効なスイッチ入力であると判断し ます(チャタリング除去)。

(4) スイッチ押下による P137/INTP0 端子の立ち下がりエッジを検出する毎に、CPU クロックと動作モード を切り替えます。

下記にスイッチ押下後の CPU クロックと動作モード、LED 表示を示します。

表 5.1 スイッチ押下後の LED 表示(1/2)

|       | CPUクロック                | 動作モード       | LED1    | LED2    | LED3   | LED4    | LED5   |

|-------|------------------------|-------------|---------|---------|--------|---------|--------|

| (1)   | 高速オンチップ・オシレータ・         | 通常動作モード     | 点灯      | 点灯      | 消灯     | 消灯      | 点灯     |

|       | クロック                   |             |         |         |        |         |        |

| (2)   | サブ・クロック                | 通常動作モード     | 点灯      | 点灯      | 点灯     | 点灯      | 消灯     |

| (3)   | サブ・クロック                | HALTモード     | 消灯      | 点灯      | 点灯     | 点灯      | 消灯     |

| (4)   | サブ・クロック                | 通常動作モード     | 点灯      | 点灯      | 点灯     | 点灯      | 消灯     |

| (5)   | 高速オンチップ・オシレータ・         | 通常動作モード     | 点灯      | 点灯      | 消灯     | 消灯      | 点灯     |

|       | クロック                   |             |         |         |        |         |        |

| (6)   | 高速システム・クロック            | 通常動作モード     | 点灯      | 点灯      | 点灯     | 消灯      | 点灯     |

| (7)   | サブ・クロック                | 通常動作モード     | 点灯      | 点灯      | 点灯     | 点灯      | 消灯     |

| (8)   | 高速システム・クロック            | 通常動作モード     | 点灯      | 点灯      | 点灯     | 消灯      | 点灯     |

| (9)   | 高速システム・クロック            | HALTモード     | 消灯      | 点灯      | 点灯     | 消灯      | 点灯     |

| (10)  | 高速システム・クロック            | 通常動作モード     | 点灯      | 点灯      | 点灯     | 消灯      | 点灯     |

| (11)  | 高速システム・クロック            | STOPモード     | 消灯      | 消灯      | 点灯     | 消灯      | 点灯     |

| (12)  | 高速システム・クロック            | 通常動作モード     | 点灯      | 点灯      | 点灯     | 消灯      | 点灯     |

| (13)  | 高速オンチップ・オシレータ・         | 通常動作モード     | 点灯      | 点灯      | 消灯     | 消灯      | 点灯     |

|       | クロック                   |             |         |         |        |         |        |

| (14)  | 高速オンチップ・オシレータ・         | HALTモード     | 消灯      | 点灯      | 消灯     | 消灯      | 点灯     |

| (4.5) | クロック                   |             | 1.1.    | 1.1.    | SMA L. | 2214.1  | 1.1.   |

| (15)  | 高速オンチップ・オシレータ・         | 通常動作モード     | 点灯      | 点灯      | 消灯     | 消灯      | 点灯     |

| (40)  | クロック                   | OTOD~ 18    | 201/12  | W. Int  | W/ Int | W 1=    | H lar  |

| (16)  | 高速オンチップ・オシレータ・         | STOPモード     | 消灯      | 消灯      | 消灯     | 消灯      | 点灯     |

| (17)  | クロック<br>高速オンチップ・オシレータ・ | マ帝科ルマード     | .E.Jer  | .E.Jer  | अप क्र | अप रस   | Je Jee |

| (17)  |                        | 通常動作モード     | 点灯      | 点灯      | 消灯     | 消灯      | 点灯     |

| (18)  | クロック<br>高速オンチップ・オシレータ・ | SNOOZEモード   | 点灯      | 消灯      | 消灯     | 消灯      | 点灯     |

| (10)  | 向述オンテック・オンレータ・<br>クロック | SNOOZE      | 思知      | 刊为      | (月久)   | (月次]    | 思知     |

| (19)  | 高速オンチップ・オシレータ・         | <br>通常動作モード | 点灯      | 点灯      | 消灯     | 消灯      | 点灯     |

| (13)  | クロック                   |             | W.V1    | WV1     | 11171  | 11171   | W.V.1  |

| (20)  | 中速オンチップ・オシレータ・         | 通常動作モード     | 点灯      | 点灯      | 消灯     | 点灯      | 消灯     |

| ()    | クロック                   | ~           | 71117-1 | 21177-1 | 1147.4 | 111/2-1 | 1147.4 |

| (21)  | 高速システム・クロック            | 通常動作モード     | 点灯      | 点灯      | 点灯     | 消灯      | 点灯     |

| (22)  | 低速オンチップ・オシレータ・         | 通常動作モード     | 点灯      | 点灯      | 消灯     | 点灯      | 点灯     |

|       | クロック                   |             |         |         |        |         |        |

| (23)  | 高速システム・クロック            | 通常動作モード     | 点灯      | 点灯      | 点灯     | 消灯      | 点灯     |

| (24)  | 中速オンチップ・オシレータ・         | 通常動作モード     | 点灯      | 点灯      | 消灯     | 点灯      | 消灯     |

|       | クロック                   |             |         |         |        |         |        |

表 5.2 スイッチ押下後の LED 表示(2/2)

|       | CPUクロック                                            | 動作モード                                   | LED1  | LED2   | LED3     | LED4  | LED5     |

|-------|----------------------------------------------------|-----------------------------------------|-------|--------|----------|-------|----------|

| (25)  | 中速オンチップ・オシレータ・                                     | HALTモード                                 | 消灯    | 点灯     | 消灯       | 点灯    | 消灯       |

|       | クロック                                               |                                         |       |        |          |       |          |

| (26)  | 中速オンチップ・オシレータ・                                     | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 点灯    | 消灯       |

|       | クロック                                               |                                         |       |        |          |       |          |

| (27)  | 中速オンチップ・オシレータ・                                     | STOPモード                                 | 消灯    | 消灯     | 消灯       | 点灯    | 消灯       |

| (0.0) | クロック                                               | > > > > > > > > > > > > > > > > > > > > | 1.1.  | 1.1.   | 2214.1   | 1.1.  | No.      |

| (28)  | 中速オンチップ・オシレータ・                                     | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 点灯    | 消灯       |

| (00)  | クロック                                               | 2112222                                 | L     | 22/4 [ | 2216 1-4 | h 1-  | 22/4 (   |

| (29)  | 中速オンチップ・オシレータ・                                     | SNOOZEモード                               | 点灯    | 消灯     | 消灯       | 点灯    | 消灯       |

| (20)  | クロック                                               | 文学和 <i>作</i> 之 10                       | H.Jar | H.Jar  | 2017 Jan | H.Jar | 2017 Jee |

| (30)  | 中速オンチップ・オシレータ・                                     | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 点灯    | 消灯       |

| (31)  | クロック<br>サブ・クロック                                    | 通常動作モード                                 | 点灯    | 点灯     | 点灯       | 点灯    | 消灯       |

| (32)  | リノ・クロック<br>  中速オンチップ・オシレータ・                        |                                         |       |        |          |       |          |

| (32)  | 中述オンテック・オンレータ・<br>  クロック                           | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 点灯    | 消灯       |

| (33)  | <u>  ´^ ピ ン /                                 </u> | <br>- 通常動作モード                           | 点灯    | 点灯     | 消灯       | 点灯    | 点灯       |

| (00)  |                                                    |                                         | W.V.1 | W.V.1  | 11171    | W.V.1 | WV1      |

| (34)  | 中速オンチップ・オシレータ・                                     | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 点灯    | 消灯       |

|       | クロック                                               |                                         | 21117 | 77117  | 1147 3   | 711.7 | 1147.4   |

| (35)  | 高速オンチップ・オシレータ・                                     | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 消灯    | 点灯       |

|       | クロック                                               |                                         |       |        |          |       |          |

| (36)  | 低速オンチップ・オシレータ・                                     | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 点灯    | 点灯       |

|       | クロック                                               |                                         |       |        |          |       |          |

| (37)  | 低速オンチップ・オシレータ・                                     | HALTモード                                 | 消灯    | 点灯     | 消灯       | 点灯    | 点灯       |

|       | クロック                                               |                                         |       |        |          |       |          |

| (38)  | 低速オンチップ・オシレータ・                                     | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 点灯    | 点灯       |

|       | クロック                                               |                                         |       |        |          |       |          |

| (39)  | 高速オンチップ・オシレータ・                                     | 通常動作モード                                 | 点灯    | 点灯     | 消灯       | 消灯    | 点灯       |

|       | クロック                                               |                                         |       |        |          |       |          |

上記1から39までのCPUクロックと動作モード切り替え後、スイッチ押下によるP137/INTP0端子の立ち下がりエッジを検出すると、LEDをすべて消灯し、HALTモードへ移行します(スタンバイ復帰はRESET入力のみです)。

また、CPU クロックが水晶発振子の発振不良などによって、一定時間内に状態移行できない場合は、エラー処理として LED を全てオフにし、状態移行を終了します。

注意 デバイス使用上の注意事項については、RL78/IID ユーザーズマニュアル を参照してください。

## 5.2 オプション・バイトの設定一覧

表 5.3 にオプション・バイト設定を示します。

表 5.3 オプション・バイト設定

| アドレス          | 設定値       | 内容                               |

|---------------|-----------|----------------------------------|

| 000C0H/010C0H | 01101110B | ウォッチドッグ・タイマ 動作停止                 |

|               |           | (リセット解除後、カウント停止)                 |

| 000C1H/010C1H | 01111111B | LVD リセット・モード 2.81V (2.76V~2.87V) |

| 000C2H/010C2H | 11100000B | HS モード、                          |

|               |           | 高速オンチップ・オシレータ・クロック:24MHz         |

| 000C3H/010C3H | 10000100B | オンチップ・デバッグ許可                     |

## 5.3 変数一覧

表 5.4 にグローバル変数を示します。

表 5.4 変数

| Туре  | Variable Name | Contents             | Function Used     |

|-------|---------------|----------------------|-------------------|

| 8 ビット | g_int_cnt     | 12 ビット・インターバル・タイマのイン | R_MAIN_BtoE,      |

|       |               | ターバル信号検出割り込み回数       | R_MAIN_EtoB,      |

|       |               |                      | R_MAIN_BtoD,      |

|       |               |                      | R_MAIN_DtoE,      |

|       |               |                      | R_MAIN_EtoD,      |

|       |               |                      | R_MAIN_DtoB,      |

|       |               |                      | R_MAIN_BtoC,      |

|       |               |                      | R_MAIN_CtoD,      |

|       |               |                      | R_MAIN_DtoF,      |

|       |               |                      | R_MAIN_FtoD,      |

|       |               |                      | R_MAIN_DtoC,      |

|       |               |                      | R_MAIN_CtoE,      |

|       |               |                      | R_MAIN_EtoC,      |

|       |               |                      | R_MAIN_CtoB,      |

|       |               |                      | R_MAIN_BtoF,      |

|       |               |                      | R_MAIN_FtoB,      |

|       |               |                      | R_MAIN_CtoF,      |

|       |               |                      | R_MAIN_FtoC,      |

|       |               |                      | r_it_interrupt    |

| 8 ビット | g_int_flg     | 外部割り込み発生判別フラグ        | R_MAIN_NOP_Loop,  |

|       |               |                      | r_intc0_interrupt |

## 5.4 関数(サブルーチン)一覧

表 5.5、表 5.6 に関数 (サブルーチン) を示します。

表 5.5 関数(1/2)

| 関数名         | 概要              | 動作モード状態 |

|-------------|-----------------|---------|

|             |                 | 移行図の番号  |

| R_MAIN_AtoB | (A)から(B)へ状態移行処理 | (1)     |

| R_MAIN_BtoE | (B)から(E)へ状態移行処理 | (2)     |

| R_MAIN_EtoO | (E)から(O)へ状態移行処理 | (3)     |

| R_MAIN_OtoE | (O)から(E)へ状態移行処理 | (4)     |

| R_MAIN_EtoB | (E)から(B)へ状態移行処理 | (5)     |

| R_MAIN_BtoD | (B)から(D)へ状態移行処理 | (6)     |

| R_MAIN_DtoE | (D)から(E)へ状態移行処理 | (7)     |

| R_MAIN_EtoD | (E)から(D)へ状態移行処理 | (8)     |

| R_MAIN_DtoM | (D)から(M)へ状態移行処理 | (9)     |

| R_MAIN_MtoD | (M)から(D)へ状態移行処理 | (10)    |

| R_MAIN_DtoN | (D)から(N)へ状態移行処理 | (11)    |

| R_MAIN_NtoD | (N)から(D)へ状態移行処理 | (12)    |

| R_MAIN_DtoB | (D)から(B)へ状態移行処理 | (13)    |

| R_MAIN_Btol | (B)から(I)へ状態移行処理 | (14)    |

| R_MAIN_ItoB | (I)から(B)へ状態移行処理 | (15)    |

| R_MAIN_BtoG | (B)から(G)へ状態移行処理 | (16)    |

| R_MAIN_GtoB | (G)から(B)へ状態移行処理 | (17)    |

| R_MAIN_BtoH | (B)から(H)へ状態移行処理 | (18)    |

| R_MAIN_HtoB | (H)から(B)へ状態移行処理 | (19)    |

| R_MAIN_BtoC | (B)から(C)へ状態移行処理 | (20)    |

| R_MAIN_CtoD | (C)から(D)へ状態移行処理 | (21)    |

| R_MAIN_DtoF | (D)から(F)へ状態移行処理 | (22)    |

| R_MAIN_FtoD | (F)から(D)へ状態移行処理 | (23)    |

| R_MAIN_DtoC | (D)から(C)へ状態移行処理 | (24)    |

| R_MAIN_CtoJ | (C)から(J)へ状態移行処理 | (25)    |

| R_MAIN_JtoC | (J)から(C)へ状態移行処理 | (26)    |

| R_MAIN_CtoK | (C)から(K)へ状態移行処理 | (27)    |

| R_MAIN_KtoC | (K)から(C)へ状態移行処理 | (28)    |

| R_MAIN_CtoL | (C)から(L)へ状態移行処理 | (29)    |

| R_MAIN_LtoC | (L)から(C)へ状態移行処理 | (30)    |

| R_MAIN_CtoE | (C)から(E)へ状態移行処理 | (31)    |

| R_MAIN_EtoC | (E)から(C)へ状態移行処理 | (32)    |

| R_MAIN_CtoF | (C)から(F)へ状態移行処理 | (33)    |

| R_MAIN_FtoC | (F)から(C)へ状態移行処理 | (34)    |

| R_MAIN_CtoB | (C)から(B)へ状態移行処理 | (35)    |

| R_MAIN_BtoF | (B)から(F)へ状態移行処理 | (36)    |

| R_MAIN_FtoP | (F)から(P)へ状態移行処理 | (37)    |

| R_MAIN_PtoF | (P)から(F)へ状態移行処理 | (38)    |

| R_MAIN_FtoB | (F)から(B)へ状態移行処理 | (39)    |

## 表 5.6 関数(2/2)

| R_MAIN_NOP_Loop     | NOP 命令繰り返し実行処理         | - |

|---------------------|------------------------|---|

| R_MAIN_END          | 状態移行終了処理               | _ |

| R_MAIN_ERROR        | 状態移行エラー処理              | _ |

| R_MAIN_Set_SnoozeOn | A/D コンバータ設定            | - |

| r_intc0_interrupt   | 外部割り込み発生判別フラグ更新処理      | - |

| r_it_interrupt      | 12 ビット・インターバル・タイマのインター | _ |

|                     | バル信号検出割り込み回数カウント処理     |   |

| r_adc_interrupt     | SNOOZE モード解除処理         | _ |

# 5.5 関数 (サブルーチン) 仕様

サンプルコードの関数 (サブルーチン) 仕様を示します。

# [関数名] R\_MAIN\_AtoB

概要 (A)から(B)へ状態移行処理 宣言 void R\_MAIN\_AtoB(void) 説明 LED 点灯制御を行います。

(CPU クロック:高速オンチップ・オシレータ・クロック)

引数 なし リターン値 なし 備者 なし

#### [関数名] R MAIN BtoE

概要 (B)から(E)へ状態移行処理 宣言 void R\_MAIN\_BtoE(void)

説明 CPU クロックを高速オンチップ・オシレータ・クロックからサブ・クロックへ切り

替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備者 なし

# [関数名] R\_MAIN\_EtoO

概要 (E)から(O)へ状態移行処理

宣言 void R\_MAIN\_EtoO(void)

説明 LED 点灯制御後、HALT モードへ移行します。

(CPU クロック停止(サブ・クロック選択時))

引数 なし リターン値 なし 備考 なし

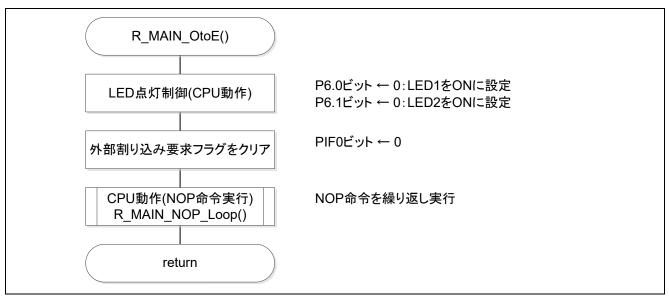

#### [関数名] R MAIN OtoE

概要 (O)から(E)へ状態移行処理 宣言 void R\_MAIN\_OtoE(void)

説明 LED 点灯制御を行います。

(CPU クロック: サブ・クロック)

引数 なし リターン値 なし 備者 なし

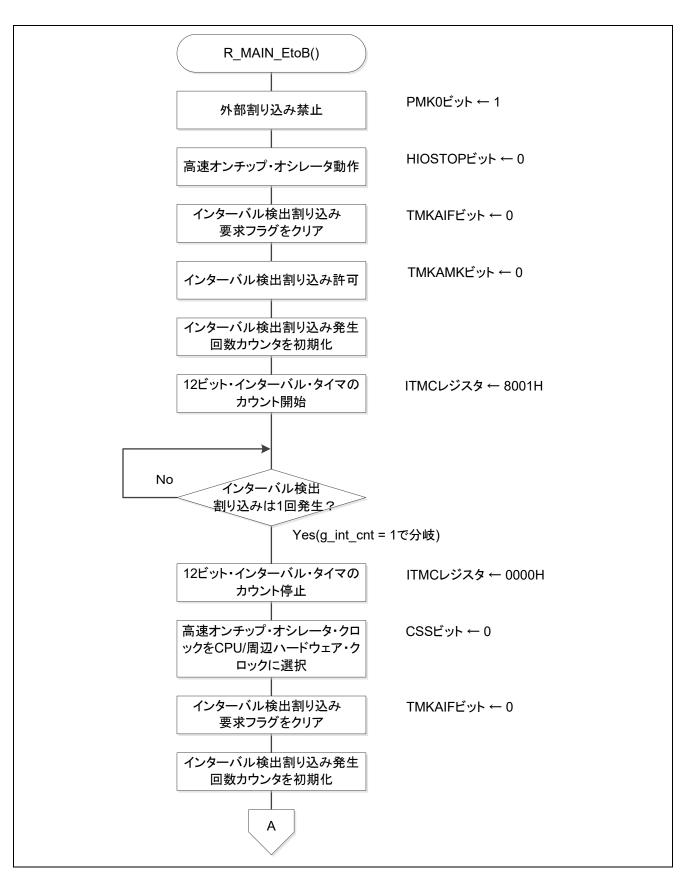

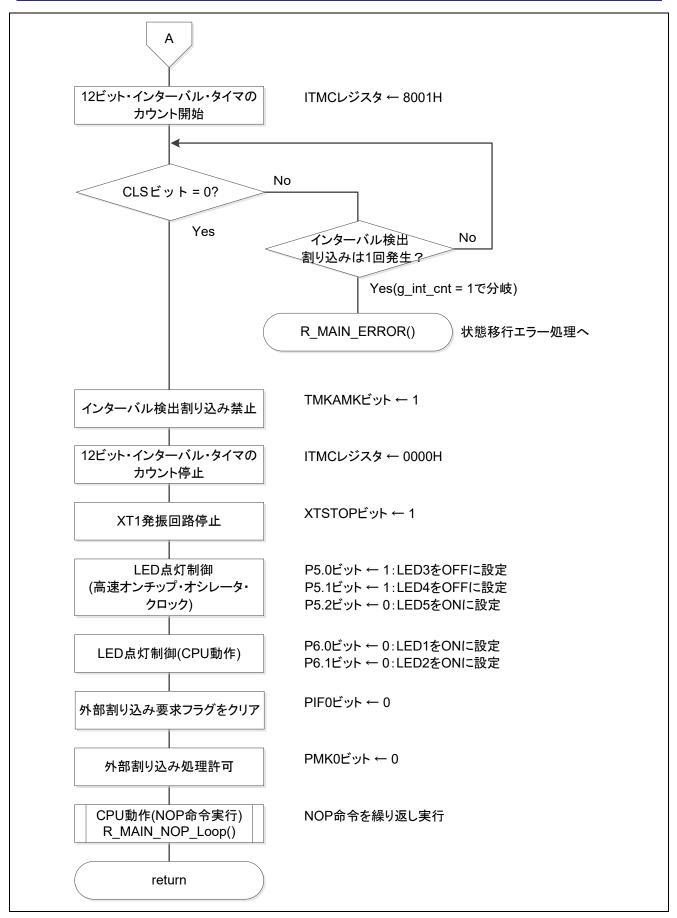

#### [関数名] R MAIN EtoB

概要 (E)から(B)へ状態移行処理 宣言 void R MAIN EtoB(void)

説明 CPU クロックをサブ・クロックから高速オンチップ・オシレータ・クロックへ切り

替えます。クロック切り替え後、LED 点灯制御を行います。

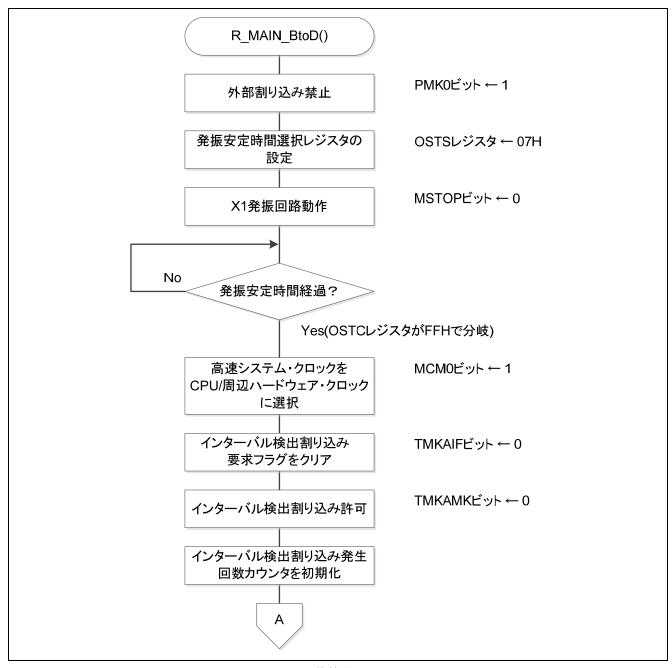

#### [関数名] R MAIN BtoD

概要 (B)から(D)へ状態移行処理 宣言 void R\_MAIN\_BtoD(void)

説明 CPU クロックを高速オンチップ・オシレータ・クロックから高速システム・クロッ

ク動作へ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN DtoE

概要 (D)から(E)へ状態移行処理 宣言 void R\_MAIN\_DtoE(void)

説明 CPU クロックを高速システム・クロックからサブ・クロックへ切り替えます。クロッ

ク切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN EtoD

概要 (E)から(D)へ状態移行処理 宣言 void R\_MAIN\_EtoD(void)

説明 CPU クロックをサブ・クロックから高速システム・クロックへ切り替えます。クロッ

ク切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備者 なし

# [関数名] R\_MAIN\_DtoM

概要 (D)から(M)へ状態移行処理 宣言 void R MAIN DtoM(void)

説明 LED 点灯制御後、HALT モードへ移行します。

(CPU クロック停止(高速システム・クロック選択時))

引数 なし リターン値 なし 備考 なし

# [関数名] R\_MAIN\_MtoD

概要 (M)から(D)へ状態移行処理 宣言 void R\_MAIN\_MtoD(void) 説明 LED 点灯制御を行います。

(CPU クロック:高速システム・クロック)

#### [関数名] R MAIN DtoN

概要 (D)から(N)へ状態移行処理 宣言 void R\_MAIN\_DtoN(void)

説明 LED 点灯制御後、STOP モードへ移行します。

(CPU クロック停止(高速システム・クロック選択時))

引数 なし リターン値 なし 備考 なし

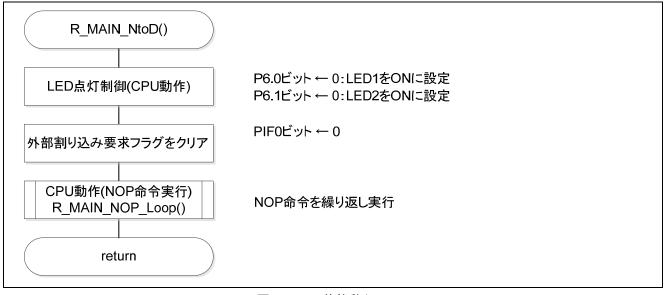

# [関数名] R MAIN NtoD

概要 (N)から(D)へ状態移行処理 宣言 void R\_MAIN\_NtoD(void) 説明 LED 点灯制御を行います。

(CPU クロック:高速システム・クロック)

引数 なし リターン値 なし 備考 なし

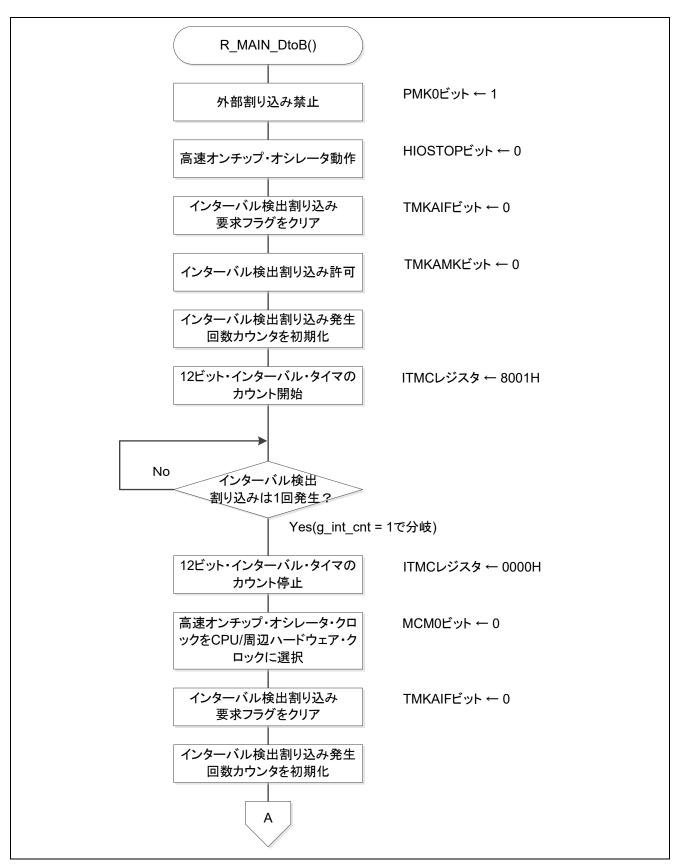

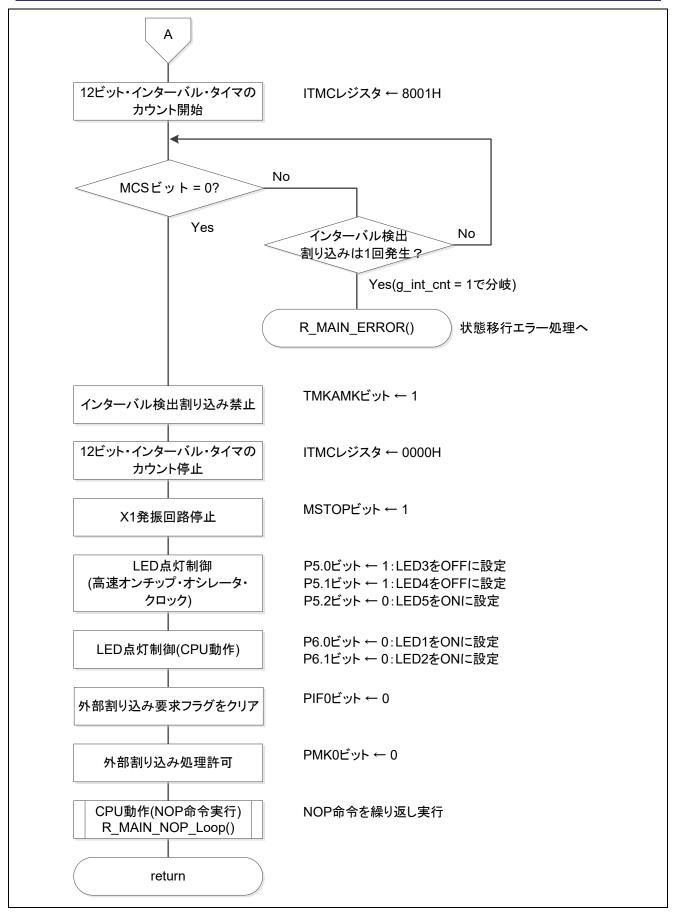

# [関数名] R MAIN DtoB

概要 (D)から(B)へ状態移行処理 宣言 void R\_MAIN\_DtoB(void)

説明 CPU クロックを高速システム・クロックから高速オンチップ・オシレータ・クロッ

クへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備者 なし

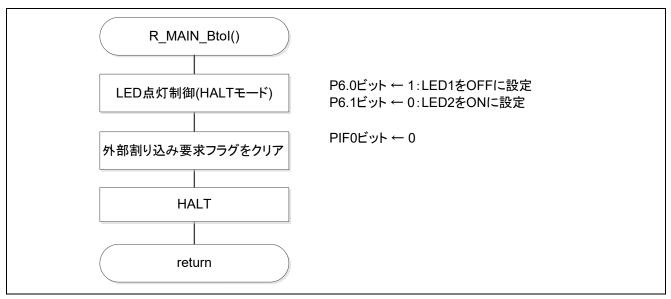

# [関数名] R\_MAIN\_Btol

概要 (B)から(I)へ状態移行処理 宣言 void R MAIN Btol(void)

説明 LED 点灯制御後、HALT モードへ移行します。

(CPU クロック停止(高速オンチップ・オシレータ・クロック選択時))

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN ItoB

概要 (I)から(B)へ状態移行処理 宣言 void R\_MAIN\_ItoB(void) 説明 LED 点灯制御を行います。

(CPU クロック:高速オンチップ・オシレータ・クロック)

#### [関数名] R MAIN BtoG

概要 (B)から(G)へ状態移行処理 宣言 void R\_MAIN\_BtoG(void)

説明 LED 点灯制御後、STOP モードへ移行します。

(CPU クロック停止(高速オンチップ・オシレータ・クロック選択時))

引数 なし リターン値 なし 備者 なし

# [関数名] R MAIN GtoB

概要 (G)から(B)へ状態移行処理 宣言 void R\_MAIN\_GtoB(void) 説明 LED 点灯制御を行います。

(CPU クロック:高速オンチップ・オシレータ・クロック)

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN BtoH

概要 (B)から(H)へ状態移行処理 宣言 void R\_MAIN\_BtoH(void)

説明 A/D コンバータ設定と LED 点灯制御を行います。

その後、SNOOZE モードへ移行します。

引数 なし リターン値 なし 備者 なし

#### [関数名] R\_MAIN\_HtoB

概要 (H)から(B)へ状態移行処理 宣言 void R\_MAIN\_HtoB(void)

説明 A/D コンバータ設定と LED 点灯制御を行います。

その後、SNOOZE モードへ移行します。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN BtoC

概要 (B)から(C)へ状態移行処理 宣言 void R\_MAIN\_BtoC(void)

説明 CPU クロックを高速オンチップ・オシレータ・クロックから中速オンチップ・オシ

レータ・クロックへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

#### [関数名] R MAIN CtoD

概要 (C)から(D)へ状態移行処理 宣言 void R\_MAIN\_CtoD(void)

説明 CPU クロックを中速オンチップ・オシレータ・クロックから高速システム・クロッ

クへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN DtoF

概要 (D)から(F)へ状態移行処理 宣言 void R MAIN DtoF(void)

説明 CPU クロックを高速システム・クロックから低速オンチップ・オシレータ・クロッ

クへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN FtoD

概要 (F)から(D)へ状態移行処理 宣言 void R\_MAIN\_FtoD(void)

説明 CPU クロックを低速オンチップ・オシレータ・クロックから高速システム・クロッ

クへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備者 なし

# [関数名] R MAIN DtoC

概要 (D)から(C)へ状態移行処理

宣言 void R\_MAIN\_DtoC(void)

説明 CPU クロックを高速システム・クロックから中速オンチップ・オシレータ・クロッ

クへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN CtoJ

概要 (C)から(J)へ状態移行処理

宣言 void R\_MAIN\_CtoJ(void)

説明 LED 点灯制御後、HALT モードへ移行します。

(CPU クロック停止(中速オンチップ・オシレータ・クロック選択時))

#### [関数名] R MAIN JtoC

概要 (J)から(C)へ状態移行処理 宣言 void R\_MAIN\_JtoC(void) 説明 LED 点灯制御を行います。

(CPU クロック:中速オンチップ・オシレータ・クロック)

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN CtoK

概要 (C)から(K)へ状態移行処理 宣言 void R\_MAIN\_CtoK(void)

説明 LED 点灯制御後、STOP モードへ移行します。

(CPU クロック停止(中速オンチップ・オシレータ・クロック選択時))

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN KtoC

概要 (K)から(C)へ状態移行処理 宣言 void R\_MAIN\_KtoC(void) 説明 LED 点灯制御を行います。

(CPU クロック:中速オンチップ・オシレータ・クロック)

引数 なし リターン値 なし 備者 なし

# [関数名] R\_MAIN\_CtoL

概要 (C)から(L)へ状態移行処理 宣言 void R\_MAIN\_CtoL(void)

説明 A/D コンバータ設定と LED 点灯制御を行います。

その後、SNOOZE モードへ移行します。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN LtoC

概要 (L)から(C)へ状態移行処理 宣言 void R\_MAIN\_LtoC(void)

説明 SNOOZE 解除設定と A/D コンバータ停止を行います。

その後、LED 点灯制御を行います。

#### [関数名] R MAIN CtoE

概要 (C)から(E)へ状態移行処理 宣言 void R MAIN CtoE(void)

説明 CPU クロックを中速オンチップ・オシレータ・クロックからサブ・クロックへ切り

替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備者 なし

#### [関数名] R MAIN EtoC

概要 (E)から(C)へ状態移行処理

宣言 void R\_MAIN\_EtoC(void)

説明 CPU クロックをサブ・クロックから中速オンチップ・オシレータ・クロックへ切り

替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R\_MAIN\_CtoF

概要 (C)から(F)へ状態移行処理

宣言 void R MAIN CtoF(void)

説明 CPU クロックを中速オンチップ・オシレータ・クロックから低速オンチップ・オシ

レータ・クロックへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R\_MAIN\_FtoC

概要 (F)から(C)へ状態移行処理

宣言 void R\_MAIN\_FtoC(void)

説明 CPU クロックを低速オンチップ・オシレータ・クロックから中速オンチップ・オシ

レータ・クロックへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

#### [関数名] R\_MAIN\_CtoB

概要 (C)から(B)へ状態移行処理

宣言 void R\_MAIN\_CtoB(void)

説明 CPU クロックを中速オンチップ・オシレータ・クロックから高速オンチップ・オシ

レータ・クロックへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

#### [関数名] R MAIN BtoF

概要 (B)から(F)へ状態移行処理 宣言 void R\_MAIN\_BtoF(void)

説明 CPU クロックを高速オンチップ・オシレータ・クロックから低速オンチップ・オシ

レータ・クロックへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備者 なし

# [関数名] R MAIN FtoP

概要 (F)から(P)へ状態移行処理 宣言 void R\_MAIN\_FtoP(void)

説明 LED 点灯制御後、HALT モードへ移行します。

(CPU クロック停止(低速オンチップ・オシレータ・クロック選択時))

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN PtoF

概要 (P)から(F)へ状態移行処理 宣言 void R\_MAIN\_PtoF(void) 説明 LED 点灯制御を行います。

(CPU クロック:低速オンチップ・オシレータ・クロック)

引数 なし リターン値 なし 備者 なし

# [関数名] R\_MAIN\_FtoB

概要 (F)から(B)へ状態移行処理 宣言 void R MAIN FtoB(void)

説明 CPU クロックを低速オンチップ・オシレータ・クロックから高速オンチップ・オシ

レータ・クロックへ切り替えます。クロック切り替え後、LED 点灯制御を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN NOP Loop

概要 NOP 命令繰り返し実行処理 宣言 void R\_MAIN\_NOP\_Loop(void)

説明 NOP 命令を繰り返し実行します。外部割り込み発生判別フラグがセットされると、

処理を終了します。

#### [関数名] R MAIN END

概要 状態移行終了処理

宣言 void R\_MAIN\_END(void)

説明 割り込みの禁止処理を行います。

その後、LED の消灯処理を行います。

引数 なし リターン値 なし 備考 なし

# [関数名] R MAIN ERROR

状態移行終了処理 概要

宣言 void R\_MAIN\_ERROR(void)

説明 割り込みの禁止処理を行い、LED の消灯処理を行います。

その後、関数内でループ処理を行います(復帰はリセット入力のみです)。

引数 なし リターン値 なし 備考 なし

# [関数名] R\_MAIN\_AD\_SnoozeOn

概要 A/D コンバータ設定

void R\_MAIN\_AD\_SnoozeOn(void) 宣言

12 ビット・インターバル・タイマ割り込み信号によるハードウエア・トリガ・ウエ 説明

イト・モードに A/D コンバータを設定します。また、SNOOZE モードを許可にして

A/D 変換待機状態にします。

なし 引数 リターン値 なし 備考 なし

# [関数名] r\_intc0\_interrupt

概要 外部割り込み発生判別フラグ更新処理

宣言 static void \_\_near r\_intc0\_interrupt(void)

説明 外部割り込み発生により、外部割り込み発生判別フラグをセットします。

また、スイッチの入力レベルがハイ・レベルとなったことを確認し、処理を終了しま

す。

引数 なし リターン値 なし なし

備考

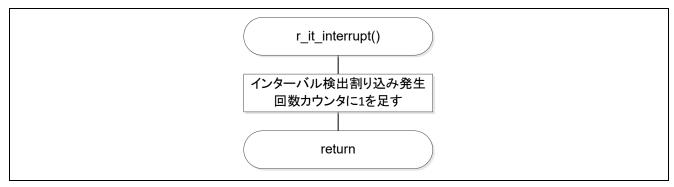

# [関数名] r\_it\_interrupt

12 ビット・インターバル・タイマのインターバル信号検出割り込み回数カウント 概要

処理

宣言 static void near r it interrupt(void)

説明 12 ビット・インターバル・タイマのインターバル信号検出割り込み発生の度に、

g int cnt をインクリメントします。

なし 引数 リターン値 なし なし 備考

# [関数名] r\_adc\_interrupt

| <del>//////                                 </del> |                                           |

|----------------------------------------------------|-------------------------------------------|

| 概要                                                 | SNOOZE モード解除処理                            |

| 宣言                                                 | static voidnear r_adc_interrupt(void)     |

| 説明                                                 | ADM2 レジスタの AWC ビットをクリアし、SNOOZE モードを解除します。 |

| 引数                                                 | なし                                        |

| リターン値                                              | なし                                        |

| 備考                                                 | なし                                        |

| リターン値                                              | なし                                        |

# 5.6 フローチャート

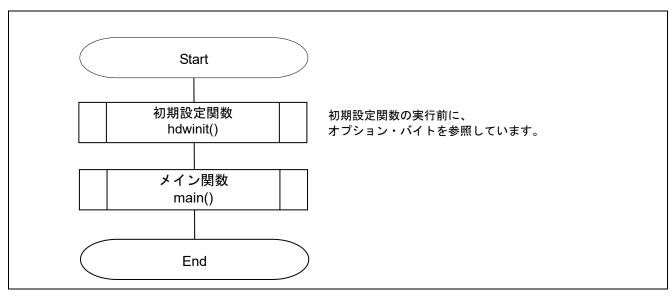

図 5.1 に本アプリケーションノートの全体フローを示します。

図 5.1 全体フロー

# 5.6.1 初期化設定関数

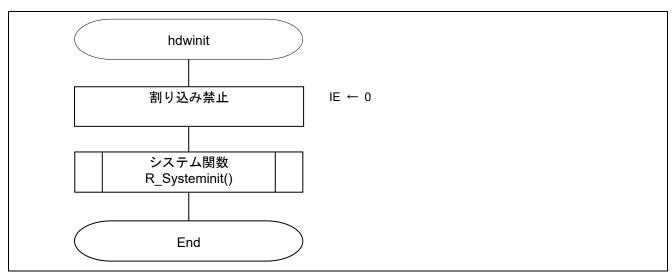

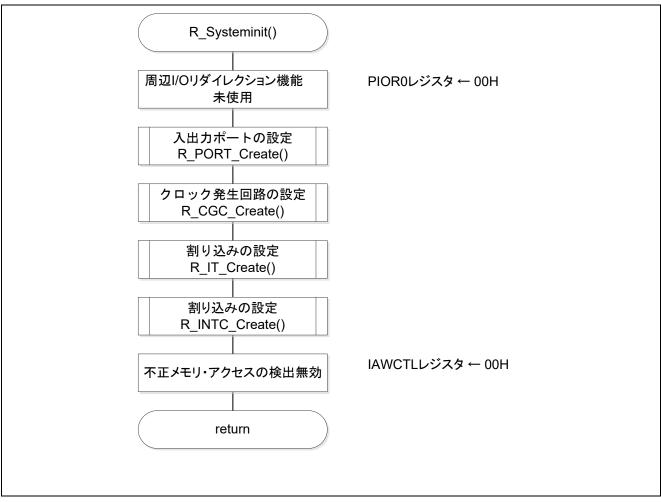

図 5.2 に初期化設定関数のフローチャートを示します。

図 5.2 初期化設定関数

# 5.6.2 システム関数

図 5.3 にシステム関数のフローチャートを示します。

図 5.3 システム関数

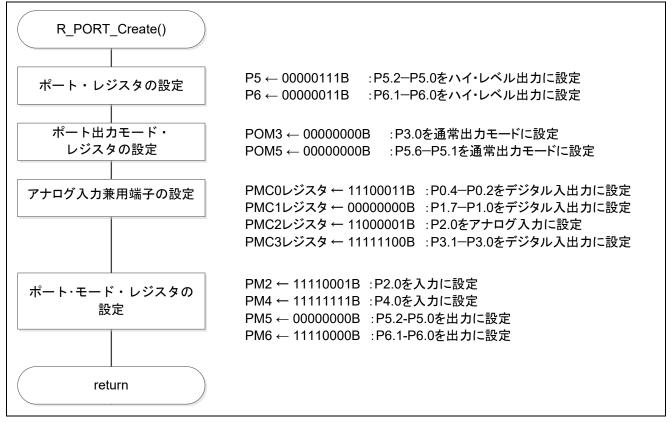

#### 5.6.3 入出カポート設定

図 5.4 に入出力ポート設定のフローチャートを示します。

図 5.4 入出力ポート設定

- 注 未使用ポートの設定については、RL78/G13 初期設定 (R01AN2575J) アプリケーションノート"フローチャート"を参照して下さい。

- 注意 未使用のポートは、端子処理などを適切に行い、電気的特性を満たすように設計してください。また、 未使用の入力専用ポートは個別に抵抗を介して $V_{DD}$ 又は $V_{SS}$ に接続してください。

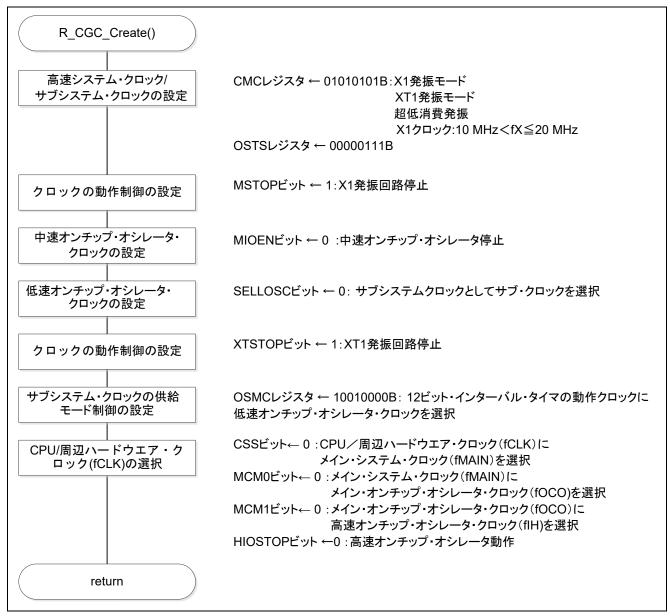

#### 5.6.4 クロック発生回路の設定

図 5.5 にクロック発生回路の設定のフローチャートを示します。

図 5.5 クロック発生回路の設定

#### クロック動作モードの設定

・クロック動作モード制御レジスタ(CMC)

高速システム・クロック端子の動作モード : X1 発振モード サブシステム・クロック端子の動作モード : XT1 発振モード

XT1 発振回路の発振モード : 超低消費発振

X1 クロック発信周波数の制御 :  $10MHz < f_X \le 20MHz$

略号:CMC

| ľ | 0     | 1      | 0      | 1       | 0 | 1      | 0      | 1    |

|---|-------|--------|--------|---------|---|--------|--------|------|

| I | EXCLK | OSCSEL | EXCLKS | OSCSELS | 0 | AMPHS1 | AMPHS0 | AMPH |

|   | 7     | 6      | 5      | 4       | 3 | 2      | 1      | 0    |

# ビット7-6

| EXCLK | OSCSEL | 高速システム・クロック端子の<br>動作モード | X1/P121 端子    | X2/EXCLK/P122 端子 |  |  |

|-------|--------|-------------------------|---------------|------------------|--|--|

| 0     | 0      | 入力ポート・モード               | 入力ポート         |                  |  |  |

| 0     | 1      | X1 発振モード                | 水晶/セラミック発振子接続 |                  |  |  |

| 1     | 0      | 入力ポート・モード               | 入力ポート         |                  |  |  |

|       |        | 外部クロック入力モード             | 入力ポート         | 外部クロック入力         |  |  |

# ビット5-4

| EXCLKS | OSCSELS | サブシステム・クロック端子の<br>動作モード | 子の XT1/P123 端子 XT2/EXCLKS/P12 |          |  |

|--------|---------|-------------------------|-------------------------------|----------|--|

| 0      | 0       | 入力ポート・モード               | 入力ポート                         |          |  |

| 0      | 1       | XT1 発振モード               | 水晶振動子接続                       |          |  |

| 1      | 0       | 入力ポート・モード               | 入力ポート                         |          |  |

| 1      | 1       | 外部クロック入力モード             | 入力ポート                         | 外部クロック入力 |  |

# ビット2-1

| AMPHS1 | AMPHS0 | XT1 発振回路の発振モード選択 |  |  |  |

|--------|--------|------------------|--|--|--|

| 0      | 0      | 低消費発振(デフォルト)     |  |  |  |

| 0      | 1      | 通常発振             |  |  |  |

| 1      | 0      | 超低消費発振           |  |  |  |

| 1      | 1      | 設定禁止             |  |  |  |

#### ビット0

| AMPH | X1 クロック発振周波数の制御          |

|------|--------------------------|

| 0    | $1MHz \le f_X \le 10MHz$ |

| 1    | $10MHz < f_X \leq 20MHz$ |

注意 レジスタ設定の詳細については、RL78/IID ユーザーズマニュアル ハードウエア編を参 照してください。

#### 各クロックの動作制御

・クロック動作ステータス制御レジスタ(CSC)

高速システム・クロックの動作制御 : X1 発振回路停止 サブシステム・クロックの動作制御 : XT1 発振回路停止

中速オンチップ・オシレータ・クロックの動作制御 : 中速オンチップ・オシレータ停止 高速オンチップ・オシレータ・クロックの動作制御 : 高速オンチップ・オシレータ動作

#### 略号: CSC

| 7     | 6      | 5 | 4 | 3 | 2 | 1     | 0       |

|-------|--------|---|---|---|---|-------|---------|

| MSTOP | XTSTOP | 0 | 0 | 0 | 0 | MIOEN | HIOSTOP |

| 1     | 1      | 0 | 0 | 0 | 0 | 0     | 0       |

#### ビット7

| MCTOD | 高速システム・クロックの動作制御 |               |            |  |  |  |

|-------|------------------|---------------|------------|--|--|--|

| MSTOP | X1 発振モード時        | 外部クロック入力モード時  | 入力ポート・モード時 |  |  |  |

| 0     | X1 発振回路動作        | EXCLK 端子からの外部 |            |  |  |  |

| U     | AI 光振凹始割作        | クロック有効        | 入力ポート      |  |  |  |

| 4     | V4 発振同略度。L       | EXCLK 端子からの外部 |            |  |  |  |

| 1     | X1 発振回路停止        | クロック無効        |            |  |  |  |

# ビット6

| VICTOR | サブシステム・クロックの動作制御 |                |            |  |  |  |

|--------|------------------|----------------|------------|--|--|--|

| XTSTOP | XT1 発振モード時       | 外部クロック入力モード時   | 入力ポート・モード時 |  |  |  |

| 0      | XT1 発振回路動作       | EXCLKS 端子からの外部 |            |  |  |  |

| 0      | ATT 光派回路到下       | クロック有効         | 入力ポート      |  |  |  |

| 1      | XT1 発振回路停止       | EXCLKS 端子からの外部 | スパルート      |  |  |  |

| 1      | 人口光板凹始存止         | クロック無効         |            |  |  |  |

#### ビット1

| MIOEN | 中速オンチップ・オシレータ・クロックの動作制御 |

|-------|-------------------------|

| 0     | 中速オンチップ・オシレータ停止         |

| 1     | 中速オンチップ・オシレータ動作         |

# ビット0

| HIOSTOP | 高速オンチップ・オシレータ・クロックの動作制御 |

|---------|-------------------------|

| 0       | 高速オンチップ・オシレータ動作         |

| 1       | 高速オンチップ・オシレータ停止         |

注意 レジスタ設定の詳細については、RL78/IID ユーザーズマニュアル ハードウエア編を参 照してください。

# CPU/周辺ハードウエア・クロック(fclk)の設定

・システム・クロック制御レジスタ (CKC)

$f_{CLK}$  のステータス : メイン・システム・クロック

$f_{CLK}$ の選択 : 高速オンチップ・オシレータ・クロック  $(f_{IH})$

略号: CKC

| ŀ | 0   | 0   | 0   | 0    | 0 | 0 | 0    | 0    |

|---|-----|-----|-----|------|---|---|------|------|

| I | CLS | CSS | MCS | MCM0 | 0 | 0 | MCS1 | MCM1 |

|   | 7   | 6   | 5   | 4    | 3 | 2 | 1    | 0    |

# ビット7

| CLS | CPU/周辺ハードウエア・クロック(f <sub>CLK</sub> )のステータス |  |  |  |  |  |

|-----|--------------------------------------------|--|--|--|--|--|

| 0   | メイン・システム・クロック(f <sub>MAIN</sub> )          |  |  |  |  |  |

| 1   | サブシステム・クロック(f <sub>SUB</sub> )             |  |  |  |  |  |

# ビット6

| CSS | CPU/周辺ハードウエア・クロック(f <sub>CLK</sub> )の選択 |

|-----|-----------------------------------------|

| 0   | メイン・システム・クロック(f <sub>MAIN</sub> )       |

| 1   | サブシステム・クロック(f <sub>SUB</sub> )          |

# ビット5

| MCS | メイン・システム・クロック(f <sub>MAIN</sub> )のステータス |  |  |  |  |  |

|-----|-----------------------------------------|--|--|--|--|--|

| 0   | イン・オンチップ・オシレータ・クロック(f <sub>oco</sub> )  |  |  |  |  |  |

| 1   | 高速システム・クロック(f <sub>MX</sub> )           |  |  |  |  |  |

#### ビット4

| МСМ0 | メイン・システム・クロック(f <sub>MAIN</sub> )の動作制御                                           |  |  |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|      | メイン・システム・クロック(f <sub>MAIN</sub> )にメイン・オンチップ・オシレータ・<br>クロック(f <sub>OCO</sub> )を選択 |  |  |  |  |  |  |  |  |

| 1    | メイン・システム・クロック(f <sub>MAIN</sub> )に高速システム・クロック(f <sub>MX</sub> )を選択               |  |  |  |  |  |  |  |  |

# ビット1

| MCS1 | メイン・オンチップ・オシレータ・クロック(f∞)のステータス       |  |  |  |  |  |  |

|------|--------------------------------------|--|--|--|--|--|--|

| 0    | §速オンチップ・オシレータ・クロック(f <sub>H</sub> )  |  |  |  |  |  |  |

| 1    | 中速オンチップ・オシレータ・クロック(f <sub>IM</sub> ) |  |  |  |  |  |  |

# ビット0

| MCM1 | メイン・オンチップ・オシレータ・クロック(f <sub>oo</sub> )の動作制御 |

|------|---------------------------------------------|

| 0    | 高速オンチップ・オシレータ・クロック(f <sub>H</sub> )         |

| 1    | 中速オンチップ・オシレータ・クロック(f <sub>IM</sub> )        |

注意 レジスタ設定方法の詳細については、RL78/IID ユーザーズマニュアル ハードウエア編を参照してください。

#### サブシステム・クロック供給モードの制御

・サブシステム・クロック供給モード制御レジスタ(OSMC)

STOP モード時およびサブシステム・クロックで CPU 動作中の HALT モード時の設定

: リアルタイム・クロック 2, 12 ビット・インターバル・タイマ, 8 ビット・インターバル・タイマ, クロック出力/ブザー出力制御回路以外の周辺機能へのサブシステム・クロック供給停止

リアルタイム・クロック、インターバル・タイマの動作クロックの選択

: 低速オンチップ・オシレータ・クロック

略号: OSMC

| 7      | 6 | 5 | 4        | 3 | 2 | 1 | 0 |

|--------|---|---|----------|---|---|---|---|

| RTCLPC | 0 | 0 | WUTMMCK0 | 0 | 0 | 0 | 0 |

| 1      | 0 | 0 | 1        | 0 | 0 | 0 | 0 |

#### ビット7

| RTCLPC | STOP モード時およびサブシステム・クロックで CPU 動作中の                                                                    |

|--------|------------------------------------------------------------------------------------------------------|

| KICLFC | HALT モード時の設定                                                                                         |

| 0      | 周辺機能へのサブシステム・クロックの供給許可                                                                               |

| 1      | リアルタイム・クロック 2, 12 ビット・インターバル・タイマ, 8 ビット・イン<br>ターバル・タイマ, クロック出力/ブザー出力制御回路以外の周辺機能への<br>サブシステム・クロック供給停止 |

#### ビット4

| WUTMMCK0 | リアルタイム・クロック 2, 12 ビット・インターバル・タイマ, 8 ビット・インターバル・タイマ, クロック出力/ブザー出力制御回路の動作クロックの選択 |

|----------|--------------------------------------------------------------------------------|

| 0        | サブシステム・クロック                                                                    |

| 1        | 低速オンチップ・オシレータ・クロック                                                             |

# サブシステム・クロック選択

・サブシステム・クロック選択レジスタ(CKSEL)

サブシステム・クロックの選択

: 低速オンチップ・オシレータ・クロックを選択

略号: CKSEL

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|---|---|---|---|---|---|---|---------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | SELLOSC |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0       |

#### ビット0

| SELLOSC | サブ・クロック/低速オンチップ・オシレータ・クロック選択 |

|---------|------------------------------|

| 0       | サブ・クロック                      |

| 1       | 低速オンチップ・オシレータ・クロック           |

注 サブ・クロック( $f_{SX}$ ,  $f_{SXR}$ )動作時は SELLOSC = 1 の設定は禁止です。

注意 レジスタ設定方法の詳細については、RL78/I1D ユーザーズマニュアル ハードウエ ア編を参照してください。

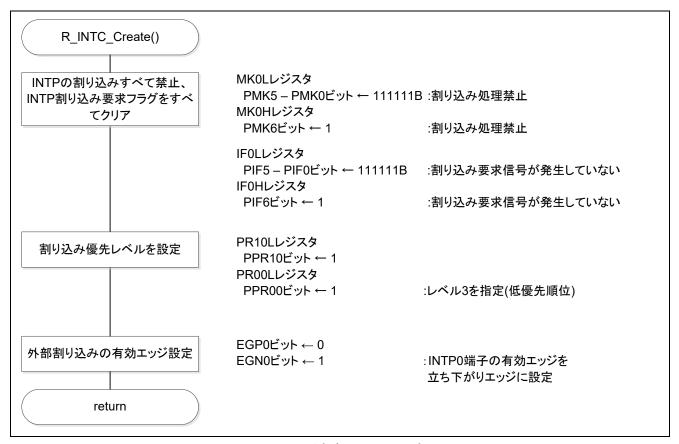

# 5.6.5 外部割り込みの設定

図 5.6 に外部割り込みの設定のフローチャートを示します。

図 5.6 外部割り込みの設定

# 外部割り込みの有効エッジを制御

・外部割り込み立ち上がりエッジ許可レジスタ(EGP0) INTP0 端子の有効エッジの選択

略号:EGP0

| 7 | 6    | 5    | 4    | 3    | 2    | 1    | 0    |