### ClockMatrix™

### Mapping Clock Device Pins to Clock Numbers in the 8A34005

#### Abstract

This document explains the mapping between the device pins used for input clocks (CLK and GPIO) and the internal names (CLK) used by the firmware to configure these input clocks in the ClockMatrix 8A34005.

### Contents

| 1. | Pin Mapping to Clock Names | . 2 |

|----|----------------------------|-----|

| 2. | Revision History           | . 3 |

# Figures

Figure 1. Input Signal Routing on ClockMatrix for Differential, Single-Ended via CLK[m] and nCLK[m]/CLK[m+8]2 Figure 2. Input Signal Routing on ClockMatrix for Alternate Frequency Input via GPIO[j] Pin for CLK[m+8].......3

## Tables

| Table 1. Clock Naming on 8A34005                        | .2 |

|---------------------------------------------------------|----|

| Table 2. Register Names for Input Clock Routing Control | .3 |

# **Related Information**

For more information, visit our website: <u>ClockMatrix™ Timing Solutions</u>

### 1. Pin Mapping to Clock Names

In addition to the CLK and nCLK pins on the 8A34005, the GPIO inputs on the device can also be used as frequency-only input clocks. Multiplexors in the device direct the clock signals from the clock and GPIO pins to different functional blocks in the 8A34005. The clock name corresponding to each clock or GPIO pin changes depending on the configuration. These names are used to determine the correct registers for input configuration.

For more information, see the 8A34005 Datasheet and the 8A3xxxx Family Programming Guide v5.2. In addition, the corresponding version of firmware can be downloaded from the <u>8A34005</u> product page.

Each pair of clock input pins can be used as a differential pair or two single-ended references. In addition, a GPIO can be used instead of the second single-ended reference clock. In the GUI, the clock is labeled with a differential, single-ended, or GPIO name, but all share common resources in the frequency input blocks. A GPIO alternate clock can be used with either a single-ended or differential clock on the CLK/nCLK pins. The clock names are listed in Table 1.

For example, when CLK1/nCLK1 is used as two single-ended clocks they will be configured as CLK1 and CLK9 (for the clock on pin nCLK1). For the 8A34005, the clock input numbers are not shared between CLK/nCLK and GPIO pins.

| Pin Name, Differential<br>Clock Number [m] | Primary Single-ended<br>Clock Number [m] | Secondary Single-ended<br>Clock Number [m+8] | GPIO Pin for Alternate<br>Clock Input [j] |

|--------------------------------------------|------------------------------------------|----------------------------------------------|-------------------------------------------|

| CLK0                                       | CLK0                                     |                                              |                                           |

| nCLK0                                      |                                          | CLK8                                         | NA                                        |

| CLK1                                       | CLK1                                     |                                              |                                           |

| nCLK1                                      |                                          | CLK9                                         | NA                                        |

|                                            |                                          | CLK13                                        | GPIO0                                     |

|                                            |                                          | CLK15                                        | GPIO3                                     |

#### Table 1. Clock Naming on 8A34005

Note: This mapping is for the 8A34005. For the 8A34005, only two of the GPIO pins can act as references. Other ClockMatrix devices may have a slightly different mapping.

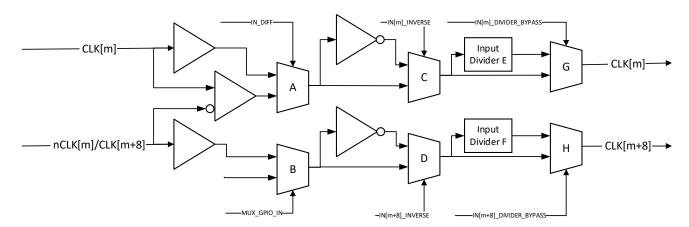

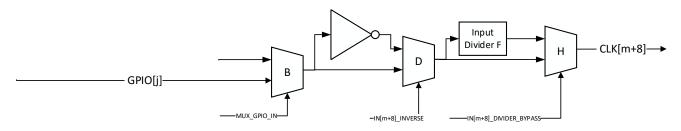

The clock routing within the 8A34005 is shown in Figure 1 for the CLK input pins, and Figure 2 for the GPIO pins. The internal structures in both figures are related and use some of the same registers for configuration. The details of the control of the multiplexors in the figure are shown in Table 2. Mux B must be set to match the available inputs in each figure (the multiplexor must use nCLK for clock inputs and GPIO for GPIO inputs).

Figure 1. Input Signal Routing on ClockMatrix for Differential, Single-Ended via CLK[m] and nCLK[m]/CLK[m+8]

Figure 2. Input Signal Routing on ClockMatrix for Alternate Frequency Input via GPIO[j] Pin for CLK[m+8]

The multiplexors in the diagrams are explained in the following table using CLK0 and CLK8.

| Mux | Function                                                      | Register in<br>Programmer's Guide  | Register in GUI                                         | Function when 0                                          | Function when 1                                          |

|-----|---------------------------------------------------------------|------------------------------------|---------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|

| A   | Primary single-ended or differential                          | INPUT_0.IN_MODE.<br>IN_DIFF[5]     | IN0_DIFF (or set<br>indirectly via "Input<br>protocol") | Use CLK as first single-<br>ended input                  | Use CLK/nCLK as first differential input                 |

| В   | Secondary single-ended<br>clock source (from nCLK<br>or GPIO) | INPUT_0.IN_MODE.<br>MUX_GPIO_IN[6] | IN0_MUX_GPIO_IN                                         | Use nCLK as second<br>single-ended input                 | Use GPIO as second<br>single-ended input                 |

| С   | Diff/primary single-<br>ended invert                          | INPUT_0.IN_MODE.<br>IN_INVERSE[3]  | IN0_INVERSE                                             | Use Primary single-<br>ended or differential<br>normally | Use Primary single-<br>ended or differential<br>inverted |

| D   | Secondary clock invert                                        | INPUT_8.IN_MODE.<br>IN_INVERSE[3]  | IN8_INVERSE                                             | Use Secondary Single-<br>ended or GPIO clock<br>normally | Use Secondary Single-<br>ended or GPIO clock<br>inverted |

| G   | Primary clock divider<br>bypass                               | INPUT_0.IN_DIV                     | IN0_DIV                                                 | When Divider E is set to 0 or 1, bypass divider          |                                                          |

| Н   | Secondary clock divider bypass                                | INPUT_8.IN_DIV                     | IN8_DIV                                                 | When Divider F is set to 0                               | or 1, bypass divider                                     |

| Table 2. Register | Names for In | put Clock Routin | g Control |

|-------------------|--------------|------------------|-----------|

Note: E and F are dividers controlled in this example by Programmer's Guide registers INPUT\_0.IN\_DIV for multiplexor G and INPUT\_8.IN\_DIV for multiplexor H.

Note: An "[n]" in a register name refers to a bit within the register. For example, INPUT\_0.IN\_MODE.IN\_DIFF[5] refers to module INPUT\_0, register IN\_MODE, bit 5.

### 2. Revision History

| Revision | Date     | Description      |

|----------|----------|------------------|

| 1.0      | Feb.1.21 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.