# RA6T1 グループ RA6T2 グループ

RA6T1 グループと RA6T2 グループの相違点

#### 要旨

本アプリケーションノートは、RA6T1 グループ、RA6T2 グループにおける周辺機能、ピン配置の差分等をまとめています。双方のデバイスを開発する際のソフトウェア資産の共通化や開発効率を向上させることを目的とした参考資料です。特に記載のない箇所については、それぞれのマイコンの最大仕様として、RA6T1 グループの 100 ピンパッケージと RA6T2 グループの 100 ピンパッケージについて記載しています。電気的特性、注意事項、設定手順等の詳細な仕様差分についてはユーザーズマニュアルをご確認ください。

#### 対象デバイス

RA6T1 グループ、RA6T2 グループ

# 目次

| 1.   | RA6T1 グループと RA6T2 グループの搭載機能比較 | 5   |

|------|-------------------------------|-----|

| 2.   | 仕様の概要比較                       | 6   |

| 2.1  | CPU                           |     |

| 2.2  | アドレス空間                        |     |

| 2.3  | リセット                          |     |

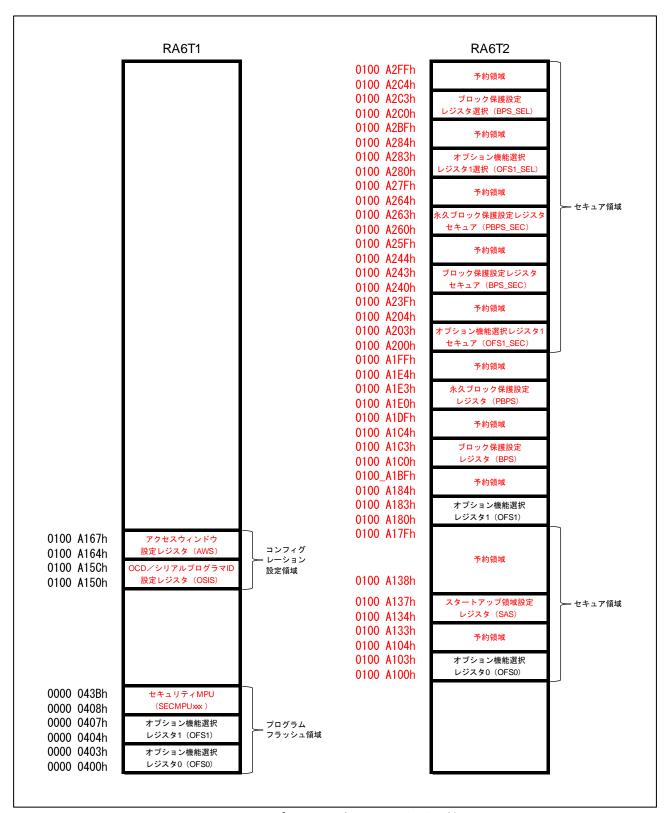

| 2.4  | オプション設定メモリ                    | 24  |

| 2.5  | 低電圧検出回路                       |     |

| 2.6  | クロック発生回路                      | 28  |

| 2.7  | クロック周波数精度測定回路                 | 32  |

| 2.8  | 低消費電力モード                      | 33  |

| 2.9  | レジスタライトプロテクション                | 45  |

| 2.10 | 割り込みコントローラユニット                | 46  |

| 2.11 | バス                            | 48  |

| 2.12 | メモリプロテクションユニット                | 50  |

| 2.13 | DMA コントローラ                    | 52  |

| 2.14 | データトランスファコントローラ               | 54  |

| 2.15 | イベントリンクコントローラ                 | 56  |

| 2.16 | i l/O ポート                     | 57  |

| 2.17 | GPT 用ポートアウトプットイネーブル           | 60  |

| 2.18 | · 汎用 PWM タイマ                  | 62  |

| 2.19 | PWM 遅延生成回路                    | 67  |

| 2.20 | 低消費電力非同期汎用タイマ/非同期汎用タイマ        | 68  |

| 2.21 | ウォッチドッグタイマ                    | 70  |

| 2.22 | : 独立ウォッチドッグタイマ                | 71  |

| 2.23 | シリアルコミュニケーションインタフェース          | 73  |

| 2.24 | - I <sup>2</sup> C バスインタフェース  | 78  |

| 2.25 | CAN モジュール/CAN フレキシブルデータレート    | 80  |

| 2.26 | シリアルペリフェラルインタフェース             | 83  |

| 2.27 | 巡回冗長検査演算器                     | 86  |

| 2.28 | セキュア暗号エンジン                    | 87  |

| 2.29 | 12 ビット A/D コンバータ              | 89  |

| 2.30 | 12 ビット D/A コンバータ              | 94  |

| 2.31 | 温度センサ回路                       | 95  |

| 2.32 | 高速アナログコンパレータ                  | 96  |

| 2.33 | データ演算回路                       | 99  |

| 2.34 | SRAM                          | 100 |

| 2.35 | フラッシュメモリ                      | 101 |

| 2.36 | 内部電圧レギュレータ                    | 106 |

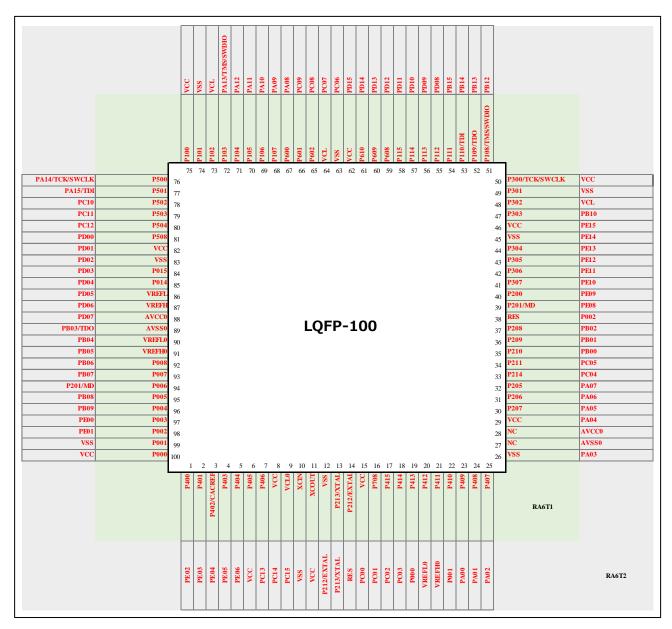

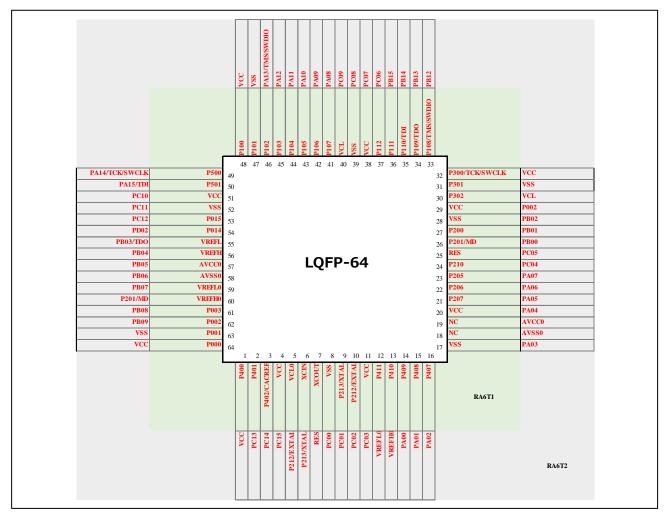

| 3.   | ピン配置の比較                       |     |

| 3.1  | 100 ピンパッケージ                   |     |

| 3.2  | 64 ピンパッケージ                    | 108 |

| 4.   | 移行の際の留意点                      | 109 |

| 4.1    | 機能設計の留意点                                           | 109 |

|--------|----------------------------------------------------|-----|

| 4.1.1  | メインクロック発振器駆動能力自動切り替え機能                             | 109 |

| 4.1.2  | レジスタアクセス                                           | 109 |

| 4.1.3  | スヌーズモードにおける SCI0 の UART の使用                        | 112 |

| 4.1.4  | スヌーズモードにおける ELC イベント                               | 113 |

| 4.1.5  | モジュールストップビット書き込みタイミング                              | 113 |

| 4.1.6  | キャッシュラインコンフィグレーションレジスタ                             | 113 |

| 4.1.7  | コヒーレンシ                                             | 113 |

| 4.1.8  | セキュリティ MPU                                         | 113 |

| 4.1.9  | DMA 転送中のレジスタアクセスについて                               | 114 |

| 4.1.10 | )DMA 転送再開時                                         | 114 |

| 4.1.11 | ELC イベント要求の間隔                                      | 114 |

| 4.1.12 | 2 端子機能の設定手順                                        | 114 |

| 4.1.13 | s ポートグループ入力の使用手順                                   | 115 |

| 4.1.14 | ・アナログ機能使用時                                         | 115 |

| 4.1.15 | i ポート mn 端子機能選択 PmnPFS レジスタ設定                      | 115 |

| 4.1.16 | ; GPT 用ポートアウトプットイネーブルの出力停止要求の 2 重化                 | 116 |

| 4.1.17 | 'GPT のモジュールストップ機能の設定                               | 116 |

| 4.1.18 | : GPT のイベントごとの優先順位                                 | 116 |

| 4.1.19 | )GPT の割り込み要求の間隔                                    | 116 |

| 4.1.20 | ) PWM 遅延生成回路への GTIOCnm 信号入力                        | 117 |

| 4.1.21 | PWM 遅延生成回路のレジスタ書き込み間隔                              | 117 |

| 4.1.22 | ! AGT/AGTW のカウント動作の開始および停止制御                       | 117 |

| 4.1.23 | 3 AGT/AGTW の出力端子の設定                                | 117 |

| 4.1.24 | - AGT/AGTW の I/O レジスタのリセット                         | 117 |

| 4.1.25 | ; AGT/AGTW のカウントソースに PCLKB、PCLKB/8、または PCLKB/2 を選択 | 118 |

| 4.1.26 | ;AGT/AGTW のカウントソースに AGTSCLK または AGTLCLK を選択        | 118 |

| 4.1.27 | 'ICU イベントリンク設定レジスタ n(IELSRn)の設定                    | 119 |

| 4.1.28 | 3 低消費電力状態での SCI の動作                                | 119 |

| 4.1.29 | ) SCI のブレークの検出と処理について                              | 120 |

| 4.1.30 | ) SCI の受信エラーフラグと送信動作(クロック同期式モードおよび簡易 SPI モード)      | 120 |

| 4.1.31 | TDR へのデータ書き込み                                      | 120 |

| 4.1.32 | !SCI のクロック同期式送信に関する制限事項(クロック同期式モード、簡易 SPI モード)     | 120 |

| 4.1.33 | SCI の DMAC または DTC 使用時の制限事項                        | 121 |

| 4.1.34 | SCI のクロック同期式モードおよび簡易 SPI モードにおける外部クロック入力           | 121 |

| 4.1.35 | 。 SCI の簡易 SPI モードに関する制限事項                          | 121 |

| 4.1.36 | i SCI の送信許可ビット                                     | 122 |

| 4.1.37 | 'SCIの動作クロックがバスクロックより長い場合のレジスタアクセス                  | 122 |

|        | S SCI 動作の割り込み                                      |     |

| 4.1.39 | )SCI 共通コントロールレジスタ CCR3.BPEN ビットの設定                 | 122 |

| 4.1.40 | IIC の転送開始                                          | 123 |

| 4.1.41 | IIC の動作クロックの設定                                     | 123 |

|        | ! CAN の動作クロックの設定                                   |     |

| 4.1.43 | : バウンダリスキャン機能                                      | 123 |

|        | · A/D 変換動作中の動作設定変更の禁止                              |     |

| 4.1.45 | i A/D 変換動作の強制停止                                    | 125 |

| 4.1.46 | ;A/D データレジスタ                                       | 126 |

| 4.1.47 | ADC/ADC12 の低消費電力状態への遷移および解除に関する制限   | 126 |

|--------|-------------------------------------|-----|

| 4.1.48 | PGA が接続されたアナログチャネルの使用               | 127 |

| 4.1.49 | ADC12 の動作モードおよびステータスビット             | 127 |

| 4.1.50 | ADC12 入力使用時のポート設定                   | 127 |

| 4.1.51 | ADC12(ユニット 0 およびユニット 1)と ACMPHS の関係 | 128 |

|        | ADC の同期動作                           |     |

| 4.1.53 | 複数の A/D コンバータ間で共有されているアナログチャネル      | 129 |

| 4.1.54 | A/D 変換開始トリガ                         | 129 |

|        | D/A 変換と A/D 変換の干渉低減有効時の制限事項         |     |

| 4.1.56 | 内部モジュールへの DAC 出力の初期化手順              | 129 |

| 4.1.57 | TSN の制限事項                           | 129 |

|        | SRAM 領域からの命令フェッチ                    |     |

|        | SRAM のストアバッファ                       |     |

| 4.1.60 | プログラム/イレース中のサスペンド                   | 130 |

| 4.1.61 | プログラム/イレースまたはブランクチェック中の禁止項目         | 130 |

|        | プログラム/イレース中の異常終了                    |     |

| 4.1.63 | Low-speed モードでのプログラム/イレース           | 131 |

| 4.1.64 | エミュレータ接続                            | 131 |

|        |                                     | 400 |

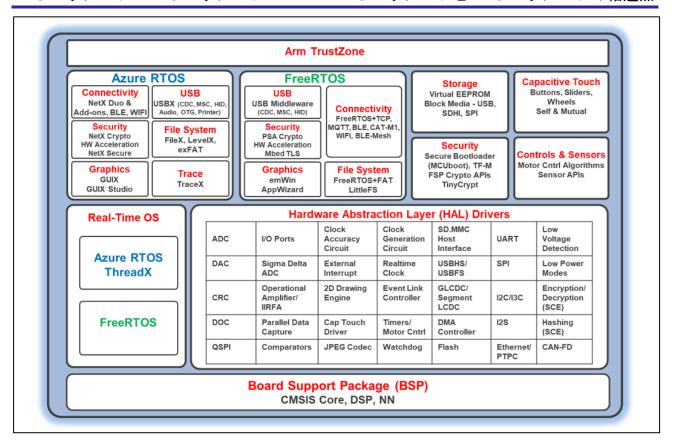

| 5. F   | SP 概要                               | 132 |

| 6. 参   | き考ドキュメント                            | 134 |

|        |                                     |     |

## 1. RA6T1 グループと RA6T2 グループの搭載機能比較

RA6T1 グループと RA6T2 グループの搭載機能比較を以下に示します。機能の詳細については「2.仕様の 概要比較」および「6.参考ドキュメント」を参照してください。

表 1.1 に RA6T1/RA6T2 搭載機能比較を示します。

表 1.1 RA6T1/RA6T2 搭載機能比較

| 製品名         |                | RA6T1  |                      | RA6T2                            |                                                |              | 機能<br>相違                       |    |

|-------------|----------------|--------|----------------------|----------------------------------|------------------------------------------------|--------------|--------------------------------|----|

| パッケージ       |                | LQFP64 | LQFP100              | LQFP48<br>QFN48                  | LQFP64<br>QFN64                                | LQFP100      | あり                             |    |

| CPU         |                |        | Arm Co               | ortex-M4                         | P                                              | rm Cortex-M3 | 33                             | あり |

| コードフラッ      | シュメモリ          |        | 512KB.               | . 256KB                          | ţ                                              | 512KB、256K   | В                              | なし |

| データフラッ      | シュメモリ          |        | 81                   | KB                               | 16KB                                           |              |                                | あり |

| SRAM        |                |        | パリティ                 | r : 64KB                         |                                                | ECC: 64KB    |                                |    |

| スタンバイ SF    | RAM            |        | _                    | _                                |                                                | パリティ:1K      | В                              | あり |

| システム        | CPU クロッ        | ク      | 最高 1                 | 20MHz                            |                                                | 最高 240MHz    | 2                              | あり |

|             | CPU クロッ        | ク      | MOSC, SOS            |                                  | MOSC, H                                        | OCO, MOCO    | )、LOCO、                        | あり |

|             | ソース            |        | MOCO, L              | OCO、PLL                          |                                                | PLL          |                                |    |

|             | CAC            |        | Y                    | es                               |                                                | Yes          |                                | あり |

|             | バックアッ?<br>レジスタ | プ      | 51                   | 2B                               |                                                | _            |                                | あり |

|             | ICU            |        | Y                    | es                               |                                                | Yes          |                                | あり |

|             | WDT/IWDT       |        | Y                    | es                               |                                                | Yes          |                                | あり |

|             | KINT           |        | 8                    | ch                               |                                                | 8ch          |                                | なし |

| イベントリ<br>ンク | ELC            |        | あ                    | ) ()                             | あり                                             |              |                                | あり |

| DMA         | DTC            |        | 1ch                  |                                  | 1ch                                            |              |                                | あり |

|             | DMAC           |        | 8ch                  |                                  | 8ch                                            |              |                                | あり |

| タイマ         | GPT            |        | (高分解能出               | x13ch<br>引力 x 4ch) <sup>(注</sup> | 32bit x 10ch<br>(高分解能出力 x 4ch) <sup>(注1)</sup> |              |                                | あり |

|             | AGT            |        | 16bit                | x 2ch                            | 32bit x 2ch                                    |              |                                | あり |

| 通信          | SCI            |        | 7ch                  |                                  | 6ch                                            |              | あり                             |    |

|             | IIC            |        | 2ch                  |                                  | 2ch                                            |              |                                | あり |

|             | SPI            |        | 2ch                  |                                  | 2ch                                            |              | あり                             |    |

|             | CAN/CANFD      |        | 1ch (CAN)            |                                  | 1ch (CANFD)                                    |              | あり                             |    |

| アナログ        | ADC12          | Unit 0 | 7ch <sup>(注 2)</sup> | 11ch <sup>(注 2)</sup>            | 6ch                                            | 10ch         | 12ch +<br>9ch <sup>(注 3)</sup> | あり |

|             |                | Unit 1 | 3ch <sup>(注 2)</sup> | 8ch <sup>(注 1)</sup>             | 4ch                                            | 8ch          | 8ch +<br>9ch <sup>(注 3)</sup>  |    |

|             | 3ch-S/H        | Unit 0 | 1(3ch)               | 1(3ch)                           | 1(3ch)                                         | 1(3ch)       | 1(3ch)                         | あり |

|             |                | Unit 1 | _                    | 1(3ch)                           | 1(2ch)                                         | 1(3ch)       | 1(3ch)                         |    |

|             | DAC12          |        | 2                    | ch                               | 2ch 4ch                                        |              | あり                             |    |

|             | ACMPHS         |        | 6                    | ch                               | 3ch                                            | 4            | ch                             | あり |

|             | PGA            | Unit 0 | 3ch                  | 3ch                              | 3ch                                            | 3ch          | 3ch                            | あり |

|             |                | Unit 1 | _                    | 3ch                              | _                                              | 1ch          | 1ch                            |    |

|             | TSN            |        | あ                    | 9                                |                                                | あり           |                                | あり |

| 製品名    |       | RA6T1 | RA6T2           | 相違 |

|--------|-------|-------|-----------------|----|

| データ処理  | CRC   | あり    | あり              | あり |

|        | DOC   | あり    | あり              | あり |

| アクセラ   | TFU   | _     | あり              | あり |

| レータ    | IIRFA | _     | あり              | あり |

| セキュリティ |       | SCE7  | SCE5、TrustZone、 | あり |

|        |       |       | ライフサイクルマネジメント   |    |

- 注1. 使用できる端子はピン数によります。詳細はそれぞれのユーザーズマニュアルを参照ください。

- 注2. 各 ADC ユニットの入力チャネル(AN005/AN105、AN006/AN106)が、同一ポートにアサインされており、2 ユニットでそれら端子を同時に使うことはできません。

- 注3. UNITO と UNIT1 の共有端子。

#### 2. 仕様の概要比較

以下に概要の比較を示します。

概要の比較では、いずれかのグループにしか存在しない、または両方のグループに存在するが相違点がある項目は赤字にしています。なお、概要比較の説明文は各グループのユーザーズマニュアルに記載どおりの内容になっており、同じ機能概要でも表現が異なる場合があります。

#### 2.1 CPU

表 2.1 に CPU の概要比較を示します。

表 2.1 CPU の概要比較

| 項目  | RA6T1                                         | RA6T2                                                      |  |  |  |

|-----|-----------------------------------------------|------------------------------------------------------------|--|--|--|

| CPU | Arm Cortex-M4                                 | Arm Cortex-M33                                             |  |  |  |

|     | — リビジョン : r0p1-01rel0                         | — リビジョン : r0p4-00rel1                                      |  |  |  |

|     | — Armv7E-M アーキテクチャプロファイル                      | — Armv8-M アーキテクチャプロファイル                                    |  |  |  |

|     | — 単精度浮動小数点ユニット<br>(ANSI/IEEE 規格 754-2008 に準拠) | ANSI/IEEE Std 754-2008 準拠の単精度浮<br>動小数点ユニット                 |  |  |  |

|     |                                               | ● SAU(セキュリティ属性ユニット): 0 領域                                  |  |  |  |

|     |                                               | ● IDAU(実装定義属性ユニット):8 領域                                    |  |  |  |

|     |                                               | コードフラッシュ(セキュア/非セキュ                                         |  |  |  |

|     |                                               | アコーラブル/非セキュア)                                              |  |  |  |

|     |                                               | <ul><li>データフラッシュ(セキュア/非セキュア)</li></ul>                     |  |  |  |

|     |                                               | <ul><li>SRAMO(セキュア/非セキュアコーラブ<br/>ル/非セキュア)</li></ul>        |  |  |  |

|     | ● メモリプロテクションユニット(MPU)                         | ● メモリプロテクションユニット(MPU)                                      |  |  |  |

|     | — Armv7 保護メモリシステムアーキテク<br>チャ                  | — Armv8 保護メモリシステムアーキテク<br>チャ(PMSAv8)                       |  |  |  |

|     | — 8 つのメモリ保護領域                                 | — セキュア MPU(MPU_S): 8 領域                                    |  |  |  |

|     |                                               | — 非セキュア MPU(MPU_NS):8 領域                                   |  |  |  |

|     | <ul><li>SysTick タイマ</li></ul>                 | ● SysTick タイマ                                              |  |  |  |

|     |                                               | <ul><li>2個の SysTick タイマ:セキュア、および<br/>非セキュアインスタンス</li></ul> |  |  |  |

|     | — SYSTICCLK(LOCO)またはICLKにより駆動                 | — SysTick タイマクロック(SYSTICCLK)<br>またはシステムクロック(ICLK)による<br>駆動 |  |  |  |

| 項目    |   | RA6T1                                                      |   | RA6T2                                           |

|-------|---|------------------------------------------------------------|---|-------------------------------------------------|

| デバッグ  | • | Arm CoreSight™ ETM-M4                                      | • | Arm <sup>®</sup> CoreSight <sup>™</sup> ETM-M33 |

|       |   | — リビジョン : r0p1-00rel0                                      |   | — リビジョン : r0p2-00rel0                           |

|       |   | Arm ETM アーキテクチャバージョン 3.5                                   |   | — ARM ETM アーキテクチャバージョン 4.2                      |

|       | • | CoreSight 計装トレースマクロセル(ITM)                                 | • | 計装トレースマクロセル(ITM)                                |

|       |   | データウォッチポイント&トレース(DWT)<br>ユニット                              | • | データウォッチポイント&トレースユニット<br>(DWT)                   |

|       |   | <ul><li>一 ウォッチポイントとトリガ用の4つのコンパレータ</li></ul>                |   | <ul><li>一 ウォッチポイントとトリガ用の4つのコンパレータ</li></ul>     |

|       | • | フラッシュパッチ&ブレークポイント<br>(FPB)ユニット                             | • | ブレークポイントユニット(BPU)                               |

|       |   | <ul><li>フラッシュパッチ(リマップ)機能は使用できない。ブレークポイント機能のみ使用可能</li></ul> |   | ブレークポイント機能を使用できます。                              |

|       |   | — 6 つの命令コンパレータ                                             |   | ─ 8 つの命令コンパレータ                                  |

|       |   | — 2つのリテラルコンパレータ                                            |   | リテラルコンパレータなし                                    |

|       | • | CoreSight タイムスタンプジェネレータ<br>(TSG)                           | • | タイムスタンプジェネレータ(TSG)                              |

|       |   | — ETM および ITM 用タイムスタンプ                                     |   | — ETM および ITM 用タイムスタンプ                          |

|       |   | CPU クロックによる駆動                                              |   | — CPU クロックによる駆動                                 |

|       | • | デバッグレジスタモジュール(DBGREG)                                      | • | デバッグレジスタモジュール(DBGREG)                           |

|       |   | ― リセットコントロール                                               |   | — リセット制御                                        |

|       |   | ― 停止コントロール                                                 |   | — 停止制御                                          |

|       | • | CoreSight デバッグアクセスポート(DAP)                                 | • | デバッグアクセスポート(DAP)                                |

|       |   | — JTAG デバッグポート(JTAG-DP)                                    |   | — JTAG デバッグポート (JTAG-DP)                        |

|       |   | <ul><li>シリアルワイヤデバッグポート<br/>(SW-DP)</li></ul>               |   | — シリアルワイヤデバッグポート<br>(SW-DP)                     |

|       | • | Cortex-M4 トレースポートインタフェースユニット(TPIU)                         | • | Cortex-M33 トレースポートインタフェースユニット(TPIU)             |

|       |   | — 4 ビット TPIU フォーマッタ出力                                      |   | — 4 ビット TPIU フォーマッタ出力                           |

|       |   | — シリアルワイヤ出力                                                |   | <b>―</b> シリアルワイヤ出力                              |

|       |   |                                                            | • | クロストリガインタフェース(CTI)                              |

|       | • | CoreSight エンベデッドトレースバッファ<br>(ETB)                          | • | エンベデッドトレースバッファ(ETB)                             |

|       |   | — CoreSight トレースメモリコントローラ<br>(ETB コンフィグレーション内蔵)            |   | — ETB 構成の CoreSight トレースメモリコ<br>ントローラ           |

|       |   | — バッファサイズ:2KB                                              |   | — バッファサイズ : 2KB                                 |

| 動作周波数 | • | CPU:最大120MHz                                               | • | CPU コア:最高 <mark>240MHz</mark>                   |

|       | • | 4 ビット TPIU トレースインタフェース:最<br>大 60MHz                        | • | 4 ビット TPIU トレースインタフェース:最<br>高 60MHz             |

|       | • | シリアルワイヤ出力(SWO)トレースインタ<br>フェース:最大 60MHz                     | • | シリアル書き込み出力(SWO)トレースイン<br>タフェース:最高 60MHz         |

|       | • | ジョイントテストアクショングループ<br>(JTAG)インタフェース:最大 25MHz                | • | ジョイントテストアクショングループ<br>(JTAG)インタフェース:最高 25MHz     |

|       | • | シリアルワイヤデバッグ(SWD)インタ<br>フェース:最大 25MHz                       | • | シリアルワイヤデータ(SWD)インタフェー<br>ス:最高 25MHz             |

# 2.2 アドレス空間

図 2.1 にメモリマップ比較を示します。

|            | RA6T1                               |            | RA6T2                          |

|------------|-------------------------------------|------------|--------------------------------|

| FFFF FFFFh | Cortox® M4田シスニノ谷は                   | FFFF FFFFh | Conton® M22⊞3.7 = /            |

| E000 0000h | Cortex <sup>®</sup> -M4用システム領域      | E000 0000h | Cortex <sup>®</sup> -M33用システム  |

|            |                                     |            |                                |

|            | 予約領域 <sup>(注1)</sup>                |            | 予約領域 <sup>(注1)</sup>           |

| 4080 0000h |                                     | 4080 0000h |                                |

| 407F C000h | フラッシュI/Oレジスタ                        | 407F C000h | フラッシュI/Oレジスタ                   |

| 407F B1A0h | 予約領域 <sup>(注1)</sup>                |            |                                |

| 407F B17Ch | 内蔵フラッシュ(オプション設定メモリ)<br>(注2)         |            | 予約領域 <sup>(注1)</sup>           |

| 407F 0000h | 予約領域 <sup>(注1)</sup>                | 407F 0000h |                                |

| 407E 0000h | フラッシュI/Oレジスタ                        | 407E 0000h | フラッシュl/Oレジスタ                   |

| 4010 2000h | 予約領域 <sup>(注1)</sup>                | 4018 0000h | 予約領域 <sup>(注1)</sup>           |

| 4010 0000h | 内蔵フラッシュ(データフラッシュ)                   |            | 周辺I/Oレジスタ                      |

| 4000 0000h | 周辺I/Oレジスタ                           | 4000 0000h | 周辺110レクスタ                      |

|            |                                     | 2800 0400h | 予約領域 <sup>(注1)</sup>           |

|            | 予約領域 <sup>(注1)</sup>                | 2800 0000h | スタンパイSRAM                      |

|            | J / 市以 取民 + 以                       | 2001 0000h | 予約領域 (注1)                      |

| 1FFF 0000h |                                     | 2000 0000h | SRAM0                          |

| 1FFE 0000h | SRAMHS領域                            |            | 予約領域 <sup>(注1)</sup>           |

|            |                                     | 0800 4000h | 學。與此一學                         |

|            | 予約領域 <sup>(注1)</sup>                | 0800 0000h | 内蔵フラッシュ(データフラッシュ)              |

| 0280 0000h |                                     |            |                                |

| 0200 0000h | メモリマッピング領域                          |            | 予約領域 <sup>(注1)</sup>           |

| 0100 A168h | 予約領域 <sup>(注1)</sup>                | 0100 A300h |                                |

| 0100 A150h | 内蔵フラッシュ(オプション設定メモリ)                 | 0100 A100h | 内蔵フラッシュ(オプション設定メモリ)            |

|            | 予約領域 <sup>(注1)</sup>                | 0100 81B4h | 予約領域 <sup>(注1)</sup>           |

| 0100 8000h | %◆564 Fub. 1:                       | 0100 80F0h | 内蔵フラッシュ(ファクトリフラッシュ)            |

| 0100 7000h | 内蔵フラッシュ(オプション設定メモリ)                 |            | 予約領域 <sup>(注1)</sup>           |

| 0008 0000h | 予約領域 (注1)                           | 0008 0000h | 1. 42 het-set                  |

| 0000 0000h | 内蔵フラッシュ(プログラムフラッシュ)<br>(読み出しのみ)     | 0000 0000h | 内蔵フラッシュ (コードフラッシュ)<br>(読み出し専用) |

|            | アクセス禁止です。<br>h~407F B19Bhはアクセス禁止です。 | o          |                                |

図 2.1 メモリマップ比較

Nov.28.22

#### 2.3 リセット

表 2.2 にリセットの名称と要因比較を、表 2.3 にリセット要因ごとの初期化対象リセット検出フラグ比較 を、表 2.4 にリセット要因ごとの初期化対象モジュール関連レジスタ比較を、表 2.5 にリセット発生時のク ロックの状態比較を示します。

表 2.2 リセットの名称と要因比較

| 項目                | RA6T1                            | RA6T2                                |

|-------------------|----------------------------------|--------------------------------------|

| RES 端子リセット        | RES 端子への入力電圧が Low                | RES 端子への入力電圧が Low                    |

| パワーオンリセット         | VCC の上昇(監視電圧:V <sub>POR</sub> )  | VCC 端子電圧の上昇(監視電圧:V <sub>POR</sub> )  |

| 独立ウォッチドッグタイマ      | IWDT のアンダーフロー                    | IWDT のアンダーフロー                        |

| リセット              | リフレッシュエラー                        | リフレッシュエラーの発生                         |

| ウォッチドッグタイマ        | WDT のアンダーフロー                     | WDT のアンダーフロー                         |

| リセット              | リフレッシュエラー                        | リフレッシュエラーの発生                         |

| 電圧監視 0 リセット       | VCC の下降(監視電圧:V <sub>det0</sub> ) | VCC 端子電圧の下降(監視電圧:V <sub>det0</sub> ) |

| 電圧監視 1 リセット       | VCC の下降(監視電圧:V <sub>det1</sub> ) | VCC 端子電圧の下降(監視電圧:V <sub>det1</sub> ) |

| 電圧監視2リセット         | VCC の下降(監視電圧:V <sub>det2</sub> ) | VCC 端子電圧の下降(監視電圧:V <sub>det2</sub> ) |

| SRAM パリティエラー      | SRAM パリティエラー検出                   | SRAM パリティエラー検出                       |

| リセット              |                                  |                                      |

| SRAM ECC エラー      | _                                | SRAM ECC エラー検出                       |

| リセット              |                                  |                                      |

| バスマスタ MPU エラー     | バスマスタ MPU エラー検出                  | バスマスタ MPU エラーの検出                     |

| リセット              |                                  |                                      |

| バススレーブ MPU エラー    | バススレーブ MPU エラー検出                 | _                                    |

| リセット              |                                  |                                      |

| スタックポインタエラー       | スタックポインタエラー検出                    | _                                    |

| リセット              |                                  |                                      |

| TrustZone エラーリセット | _                                | TrustZone エラー検出                      |

| キャッシュパリティエラー      | _                                | キャッシュパリティエラー検出                       |

| リセット              |                                  |                                      |

| ディープソフトウェア        | 割り込みによるディープソフトウェアス               | 割り込みによるディープソフトウェアス                   |

| スタンバイリセット         | タンバイモードの解除                       | タンバイモードの解除                           |

| ソフトウェアリセット        | レジスタ設定                           | レジスタ設定                               |

|                   | (Arm®ソフトウェアリセットビット、              | (ソフトウェアリセットビット:                      |

|                   | AIRCR.SYSRESETREQ を使用)           | AIRCR.SYSRESETREQ を使用)               |

Nov.28.22

### 表 2.3 リセット要因ごとの初期化対象リセット検出フラグ比較

| 項目         | RA6T1                                                          | RA6T2                                                        |

|------------|----------------------------------------------------------------|--------------------------------------------------------------|

| RES 端子リセット | ● パワーオンリセット検出フラグ                                               | ● パワーオンリセット検出フラグ                                             |

|            | (RSTSR0.PORF)                                                  | (RSTSR0.PORF)                                                |

|            | ● 電圧監視 0 リセット検出フラグ<br>(RSTSR0.LVD0RF)                          | ● 電圧監視 0 リセット検出フラグ<br>(RSTSR0.LVD0RF)                        |

|            | ● 独立ウォッチドッグタイマリセット検<br>出フラグ(RSTSR1.IWDTRF)                     | ● 独立ウォッチドッグタイマリセット検<br>出フラグ(RSTSR1.IWDTRF)                   |

|            | ● ウォッチドッグタイマリセット検出フラグ(RSTSR1.WDTRF)                            | ● ウォッチドッグタイマリセット検出フ<br>ラグ(RSTSR1.WDTRF)                      |

|            | ● 電圧監視 1 リセット検出フラグ<br>(RSTSR0.LVD1RF)                          | ● 電圧監視 1 リセット検出フラグ<br>(RSTSR0.LVD1RF)                        |

|            | ● 電圧監視 2 リセット検出フラグ<br>(RSTSR0.LVD2RF)                          | ● 電圧監視 2 リセット検出フラグ<br>(RSTSR0.LVD2RF)                        |

|            | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                             | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                           |

|            | SRAM パリティエラーリセット検出フラグ(RSTSR1.RPERF)                            | SRAM パリティエラーリセット検出フラグ(RSTSR1.RPERF)                          |

|            |                                                                | <ul><li>SRAM ECC エラーリセット検出フラ<br/>グ(RSTSR1.REERF)</li></ul>   |

|            | <ul><li>バススレーブ MPU エラーリセット検<br/>出フラグ (RSTSR1.BUSSRF)</li></ul> |                                                              |

|            | <ul><li>バスマスタ MPU エラーリセット検出<br/>フラグ (RSTSR1.BUSMRF)</li></ul>  | <ul><li>バスマスタ MPU エラーリセット検出<br/>フラグ(RSTSR1.BUSMRF)</li></ul> |

|            | • スタックポインタエラーリセット検出<br>フラグ(RSTSR1.SPERF)                       |                                                              |

|            |                                                                | <ul><li>TrustZone エラーリセット検出フラグ<br/>(RSTSR1.TZERF)</li></ul>  |

|            |                                                                | ● キャッシュパリティエラーリセット検<br>出フラグ(RSTSR1.CPERF)                    |

|            | ● ディープソフトウェアスタンバイリ<br>セット検出フラグ<br>(RSTSR0.DPSRSTF)             | ● ディープソフトウェアスタンバイリ<br>セット検出フラグ<br>(RSTSR0.DPSRSTF)           |

| パワーオンリセット  | ◆ 電圧監視 0 リセット検出フラグ<br>(RSTSR0.LVD0RF)                          | 電圧監視 0 リセット検出フラグ<br>(RSTSR0.LVD0RF)                          |

|            | ● 独立ウォッチドッグタイマリセット検<br>出フラグ(RSTSR1.IWDTRF)                     | ● 独立ウォッチドッグタイマリセット検<br>出フラグ(RSTSR1.IWDTRF)                   |

|            | <ul><li>ウォッチドッグタイマリセット検出フ</li></ul>                            | <ul><li>ウォッチドッグタイマリセット検出フ</li></ul>                          |

|            | ラグ(RSTSR1.WDTRF)<br>● 電圧監視 1 リセット検出フラグ                         | ラグ(RSTSR1.WDTRF)<br>● 電圧監視 1 リセット検出フラグ                       |

|            | (RSTSR0.LVD1RF)                                                | (RSTSR0.LVD1RF)                                              |

|            | ● 電圧監視 2 リセット検出フラグ<br>(RSTSR0.LVD2RF)                          | ● 電圧監視 2 リセット検出フラグ<br>(RSTSR0.LVD2RF)                        |

|            | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                             | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                           |

|            | ● SRAM パリティエラーリセット検出フラグ(RSTSR1.RPERF)                          | ● SRAM パリティエラーリセット検出フラグ(RSTSR1.RPERF)                        |

|            |                                                                | <ul><li>SRAM ECC エラーリセット検出フラ<br/>グ (RSTSR1.REERF)</li></ul>  |

|            | <ul><li>バススレーブ MPU エラーリセット検<br/>出フラグ (RSTSR1.BUSSRF)</li></ul> |                                                              |

| 項目                                        | RA6T1                                                          | RA6T2                                                         |

|-------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------|

| パワーオンリセット                                 | ● バスマスタ MPU エラーリセット検出                                          | ● バスマスタ MPU エラーリセット検出                                         |

|                                           | フラグ(RSTSR1.BUSMRF)                                             | フラグ(RSTSR1.BUSMRF)                                            |

|                                           | <ul><li>スタックポインタエラーリセット検出</li></ul>                            |                                                               |

|                                           | フラグ(RSTSR1.SPERF)                                              |                                                               |

|                                           |                                                                | <ul><li>TrustZone エラーリセット検出フラグ<br/>(RSTSR1.TZERF)</li></ul>   |

|                                           |                                                                | ● キャッシュパリティエラーリセット検<br>出フラグ(RSTSR1.CPERF)                     |

|                                           | <ul><li>ディープソフトウェアスタンバイリ</li></ul>                             | <ul><li>ディープソフトウェアスタンバイリ</li></ul>                            |

|                                           | セット検出フラグ                                                       | セット検出フラグ                                                      |

|                                           | (RSTSR0.DPSRSTF)                                               | (RSTSR0.DPSRSTF)                                              |

|                                           | ● コールドスタート/ウォームスタート<br>************************************    | ● コールドスタート/ウォームスタート                                           |

| 独立ウォッチドッグタイマ                              | 判別フラグ(RSTSR2.CWSF)  ● 初期化対象フラグなし                               | 判別フラグ (RSTSR2.CWSF)  • 初期化対象フラグなし                             |

| リセット                                      | ・ 初州に対象ノブグなし                                                   | 切別に対象ノブラなし                                                    |

| ウォッチドッグタイマ                                | ● 初期化対象フラグなし                                                   | ● 初期化対象フラグなし                                                  |

| リセット                                      |                                                                |                                                               |

| 電圧監視 0 リセット                               | ● 独立ウォッチドッグタイマリセット検                                            | ● 独立ウォッチドッグタイマリセット検                                           |

|                                           | 出フラグ(RSTSR1.IWDTRF)                                            | 出フラグ(RSTSR1.IWDTRF)                                           |

|                                           | ● ウォッチドッグタイマリセット検出フラグ(RSTSR1.WDTRF)                            | ● ウォッチドッグタイマリセット検出フラグ(RSTSR1.WDTRF)                           |

|                                           | ● 電圧監視 1 リセット検出フラグ<br>(RSTSR0.LVD1RF)                          | ● 電圧監視 1 リセット検出フラグ<br>(RSTSR0.LVD1RF)                         |

|                                           | ● 電圧監視 2 リセット検出フラグ<br>(RSTSR0.LVD2RF)                          | ● 電圧監視 2 リセット検出フラグ<br>(RSTSR0.LVD2RF)                         |

|                                           | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                             | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                            |

|                                           | SRAM パリティエラーリセット検出フラグ(RSTSR1.RPERF)                            | ● SRAM パリティエラーリセット検出フラグ(RSTSR1.RPERF)                         |

|                                           | , , , , , , , , , , , , , , , , , , ,                          | <ul> <li>SRAM ECC エラーリセット検出フラ<br/>グ (RSTSR1.REERF)</li> </ul> |

|                                           | <ul><li>バススレーブ MPU エラーリセット検<br/>出フラグ (RSTSR1.BUSSRF)</li></ul> | , (NOTORTINEERIT)                                             |

|                                           | ● バスマスタ MPU エラーリセット検出<br>フラグ(RSTSR1.BUSMRF)                    | ● バスマスタ MPU エラーリセット検出<br>フラグ(RSTSR1.BUSMRF)                   |

|                                           | ● スタックポインタエラーリセット検出<br>フラグ(RSTSR1.SPERF)                       |                                                               |

|                                           |                                                                | <ul><li>TrustZone エラーリセット検出フラグ<br/>(RSTSR1.TZERF)</li></ul>   |

|                                           |                                                                | <ul><li>キャッシュパリティエラーリセット検<br/>出フラグ(RSTSR1.CPERF)</li></ul>    |

|                                           | <ul><li>ディープソフトウェアスタンバイリ</li></ul>                             | <ul><li>ディープソフトウェアスタンバイリ</li></ul>                            |

|                                           | セット検出フラグ                                                       | セット検出フラグ                                                      |

| 高广联·4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 | (RSTSR0.DPSRSTF)                                               | (RSTSR0.DPSRSTF)                                              |

| 電圧監視1リセット                                 | ● 初期化対象フラグなし                                                   | <ul><li>初期化対象フラグなし</li></ul>                                  |

| 電圧監視2リセット                                 | ● 初期化対象フラグなし                                                   | ● 初期化対象フラグなし                                                  |

| SRAM パリティエラー<br>リセット                      | ● 初期化対象フラグなし                                                   | ● 初期化対象フラグなし                                                  |

| SRAM ECC エラー                              | _                                                              | <ul><li>◆ 初期化対象フラグなし</li></ul>                                |

| リセット                                      |                                                                | ,533,123,33,7 7 7 10 C                                        |

| _ · _ • ·                                 | <u> </u>                                                       | <u>l</u>                                                      |

| 項目                                      | RA6T1                                               | RA6T2                                                       |

|-----------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|

| バスマスタ MPU エラー                           | ● 初期化対象フラグなし                                        | ● 初期化対象フラグなし                                                |

| リセット                                    |                                                     |                                                             |

| バススレーブ MPU エラー                          | ● 初期化対象フラグなし                                        | _                                                           |

| リセット                                    |                                                     |                                                             |

| スタックポインタエラー                             | ● 初期化対象フラグなし                                        | _                                                           |

| リセット                                    |                                                     |                                                             |

| TrustZone エラーリセット                       | _                                                   | ● 初期化対象フラグなし                                                |

| キャッシュパリティエラー                            | _                                                   | ● 初期化対象フラグなし                                                |

| リセット                                    |                                                     |                                                             |

| ディープソフトウェア                              | ● 独立ウォッチドッグタイマリセット検                                 | ● 独立ウォッチドッグタイマリセット検                                         |

| スタンバイリセット                               | 出フラグ(RSTSR1.IWDTRF)                                 | 出フラグ(RSTSR1.IWDTRF)                                         |

| (DEEPCUT[0] = 0)                        | ● ウォッチドッグタイマリセット検出フラグ(RSTSR1.WDTRF)                 | ● ウォッチドッグタイマリセット検出フ<br>ラグ(RSTSR1.WDTRF)                     |

|                                         | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                  | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                          |

|                                         | SRAM パリティエラーリセット検出フラグ(RSTSR1.RPERF)                 | SRAM パリティエラーリセット検出フラグ(RSTSR1.RPERF)                         |

|                                         |                                                     | ● SRAM ECC エラーリセット検出フラ                                      |

|                                         |                                                     | グ(RSTSR1.REERF)                                             |

|                                         | ● バススレーブ MPU エラーリセット検                               |                                                             |

|                                         | 出フラグ(RSTSR1.BUSSRF)                                 |                                                             |

|                                         | ● バスマスタ MPU エラーリセット検出                               | ● バスマスタ MPU エラーリセット検出                                       |

|                                         | フラグ(RSTSR1.BUSMRF)                                  | フラグ(RSTSR1.BUSMRF)                                          |

|                                         | <ul><li>スタックポインタエラーリセット検出</li></ul>                 |                                                             |

|                                         | フラグ(RSTSR1.SPERF)                                   |                                                             |

|                                         |                                                     | <ul><li>TrustZone エラーリセット検出フラグ<br/>(RSTSR1.TZERF)</li></ul> |

|                                         |                                                     | ● キャッシュパリティエラーリセット検<br>出フラグ(RSTSR1.CPERF)                   |

| ディープソフトウェア<br>スタンバイリセット                 | ● 独立ウォッチドッグタイマリセット検<br>出フラグ(RSTSR1.IWDTRF)          | 独立ウォッチドッグタイマリセット検<br>出フラグ(RSTSR1.IWDTRF)                    |

| (DEEPCUT[0] = 1)                        | <ul><li>ウォッチドッグタイマリセット検出フラグ(RSTSR1.WDTRF)</li></ul> | ● ウォッチドッグタイマリセット検出フ<br>ラグ(RSTSR1.WDTRF)                     |

|                                         | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                  | ● ソフトウェアリセット検出フラグ<br>(RSTSR1.SWRF)                          |

|                                         | ● SRAM パリティエラーリセット検出フ                               | ● SRAM パリティエラーリセット検出フ                                       |

|                                         | ラグ(RSTSR1.RPERF)                                    | ラグ(RSTSR1.RPERF)<br>● SRAM ECC エラーリセット検出フラ                  |

|                                         |                                                     | グ(RSTSR1.REERF)                                             |

|                                         | ● バススレーブ MPU エラーリセット検                               |                                                             |

|                                         | 出フラグ(RSTSR1.BUSSRF)                                 |                                                             |

|                                         | ● バスマスタ MPU エラーリセット検出                               | ● バスマスタ MPU エラーリセット検出                                       |

|                                         | フラグ(RSTSR1.BUSMRF)                                  | フラグ(RSTSR1.BUSMRF)                                          |

|                                         | • スタックポインタエラーリセット検出<br>フラグ(RSTSR1.SPERF)            |                                                             |

|                                         |                                                     | <ul><li>TrustZone エラーリセット検出フラグ<br/>(RSTSR1.TZERF)</li></ul> |

|                                         |                                                     | ● キャッシュパリティエラーリセット検<br>出フラグ(RSTSR1.CPERF)                   |

| ソフトウェアリセット                              | <ul><li>● 初期化対象フラグなし</li></ul>                      | <ul><li>■ 初期化対象フラグなし</li></ul>                              |

| / / / / / / / / / / / / / / / / / / / / | ▼70分に対象ノノノなし                                        | ▼「別物」山外家ノノノなし                                               |

表 2.4 リセット要因ごとの初期化対象モジュール関連レジスタ比較

| 項目         | RA6T1                                                                                                                                                                       | RA6T2                                                                                                                                                                                                                                                                      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RES 端子リセット | -                                                                                                                                                                           | 独立ウォッチドッグタイマのレジスタ<br>(IWDTRR、IWDTSR)                                                                                                                                                                                                                                       |

|            | <ul> <li>ウォッチドッグタイマのレジスタ<br/>(WDTRR、WDTCR、WDTSR、<br/>WDTRCR、WDTCSTPR)</li> <li>電圧監視機能1のレジスタ<br/>(LVD1CR0、LVCMPCR.LVD1E、<br/>LVDLVLR.LVD1LVL、<br/>LVD1CR1/LVD1SR)</li> </ul> | <ul> <li>ウォッチドッグタイマのレジスタ<br/>(WDTRR、WDTCR、WDTSR、<br/>WDTRCR、WDTCSTPR)</li> <li>電圧監視機能1のレジスタ<br/>(LVD1CR0、LVD1CMPCR、<br/>LVD1CR1/LVD1SR)</li> </ul>                                                                                                                         |

|            | ● 電圧監視機能 2 のレジスタ<br>(LVD2CR0、LVCMPCR.LVD2E、<br>LVDLVLR.LVD2LVL、<br>LVD2CR1/LVD2SR)                                                                                          | <ul> <li>電圧監視機能2のレジスタ<br/>(LVD2CR0、LVD2CMPCR、<br/>LVD2CR1/LVD2SR)</li> </ul>                                                                                                                                                                                               |

|            | <ul><li>LOCO のレジスタ (LOCOCR)</li></ul>                                                                                                                                       | ● LOCO レジスタ(LOCOCR)                                                                                                                                                                                                                                                        |

|            | ● MOSC のレジスタ(MOMCR)                                                                                                                                                         | ● MOSC レジスタ (MOMCR)                                                                                                                                                                                                                                                        |

|            | ● MPU のレジスタ                                                                                                                                                                 | <ul> <li>バス、MPU および TrustZone エラー<br/>レジスタ (BUS_ERROR_ADDRESS<br/>レジスタ、BUS_ERROR_STATUS レ<br/>ジスタ) (注4)</li> </ul>                                                                                                                                                         |

|            | ● 端子状態(XCIN/XCOUT 端子以外)                                                                                                                                                     | ● 端子状態                                                                                                                                                                                                                                                                     |

|            | ● 低消費電力機能のレジスタ<br>(DPSBYCR、DPSIER0~<br>DPSIER3、DPSIFR0~DPSIFR3、<br>DPSIEGR0~DPSIEGR2)                                                                                       | ● 低消費電力機能のレジスタ<br>(DPSBYCR、DPSIER0~<br>DPSIER2、DPSIFR0~DPSIFR2、<br>DPSIEGR0~DPSIEGR2)                                                                                                                                                                                      |

|            |                                                                                                                                                                             | <ul> <li>セキュリティ属性のレジスタ<br/>(CPUDSAR、RSTSAR、LVDSAR、<br/>CGFSAR、LPMSAR、DPFSAR、<br/>ICUSARX、BUSSARA、BUSSARB、<br/>CSAR、MMPUSARA、MMPUSARB、<br/>DMACSAR、DTCSAR、ELCSARA、<br/>ELCSARB、PMSAR、SRAMSAR、<br/>STBRAMSAR、FSAR、PSARB、<br/>PSARC、PSARD、PSARE、<br/>MSSAR、TZFSAR)</li> </ul> |

|            | <ul> <li>その他レジスタ <sup>(注1)</sup> 、CPU、および<br/>内部状態</li> </ul>                                                                                                               | ● その他レジスタ <sup>(注 2)</sup> 、CPU、および<br>内部状態                                                                                                                                                                                                                                |

| パワーオンリセット  |                                                                                                                                                                             | ● 独立ウォッチドッグタイマのレジスタ<br>(IWDTRR、IWDTSR)                                                                                                                                                                                                                                     |

|            | ● ウォッチドッグタイマのレジスタ<br>(WDTRR、WDTCR、WDTSR、<br>WDTRCR、WDTCSTPR)                                                                                                                | ● ウォッチドッグタイマのレジスタ<br>(WDTRR、WDTCR、WDTSR、<br>WDTRCR、WDTCSTPR)                                                                                                                                                                                                               |

|            | <ul> <li>電圧監視機能1のレジスタ<br/>(LVD1CR0、LVCMPCR.LVD1E、<br/>LVDLVLR.LVD1LVL、<br/>LVD1CR1/LVD1SR)</li> </ul>                                                                       | <ul> <li>電圧監視機能1のレジスタ<br/>(LVD1CR0、LVD1CMPCR、<br/>LVD1CR1/LVD1SR)</li> </ul>                                                                                                                                                                                               |

|            | <ul> <li>電圧監視機能2のレジスタ<br/>(LVD2CR0、LVCMPCR.LVD2E、<br/>LVDLVLR.LVD2LVL、<br/>LVD2CR1/LVD2SR)</li> </ul>                                                                       | ● 電圧監視機能 2 のレジスタ<br>(LVD2CR0、LVD2CMPCR、<br>LVD2CR1/LVD2SR)                                                                                                                                                                                                                 |

|            | <ul><li>SOSC のレジスタ (SOSCCR)</li></ul>                                                                                                                                       |                                                                                                                                                                                                                                                                            |

| 項目                   | RA6T1                                                                                                           | RA6T2                                                                                                                                                                                                                                                                      |

|----------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| パワーオンリセット            | ● LOCO のレジスタ(LOCOCR、                                                                                            | ● LOCO レジスタ(LOCOCR、                                                                                                                                                                                                                                                        |

|                      | LOCOUTCR)  • MOSC のレジスタ (MOMCR)                                                                                 | LOCOUTCR)  • MOSC レジスタ (MOMCR)                                                                                                                                                                                                                                             |

|                      | AGT のレジスタ     (MONICR)                                                                                          | WIOSC DDX (WIOWICK)                                                                                                                                                                                                                                                        |

|                      | ● MPUのレジスタ                                                                                                      | バス、MPU および TrustZone エラー                                                                                                                                                                                                                                                   |

|                      | IVII O O) D D D D                                                                                               | レジスタ(BUS ERROR ADDRESS                                                                                                                                                                                                                                                     |

|                      |                                                                                                                 | レジスタ、BUS_ERROR_STATUS レ                                                                                                                                                                                                                                                    |

|                      |                                                                                                                 | ジスタ) <sup>(注 4)</sup>                                                                                                                                                                                                                                                      |

|                      | ● 端子状態(XCIN/XCOUT 端子以外)                                                                                         | ● 端子状態                                                                                                                                                                                                                                                                     |

|                      | <ul> <li>低消費電力機能のレジスタ<br/>(DPSBYCR、DPSIER0~<br/>DPSIER3、DPSIFR0~DPSIFR3、<br/>DPSIEGR0~DPSIEGR2)</li> </ul>      | <ul> <li>低消費電力機能のレジスタ<br/>(DPSBYCR、DPSIER0~<br/>DPSIER2、DPSIFR0~DPSIFR2、<br/>DPSIEGR0~DPSIEGR2、<br/>SYOCDCR)</li> </ul>                                                                                                                                                    |

|                      |                                                                                                                 | <ul> <li>セキュリティ属性のレジスタ<br/>(CPUDSAR、RSTSAR、LVDSAR、<br/>CGFSAR、LPMSAR、DPFSAR、<br/>ICUSARX、BUSSARA、BUSSARB、<br/>CSAR、MMPUSARA、MMPUSARB、<br/>DMACSAR、DTCSAR、ELCSARA、<br/>ELCSARB、PMSAR、SRAMSAR、<br/>STBRAMSAR、FSAR、PSARB、<br/>PSARC、PSARD、PSARE、<br/>MSSAR、TZFSAR)</li> </ul> |

|                      | <ul> <li>その他レジスタ <sup>(注1)</sup> 、CPU、および<br/>内部状態</li> </ul>                                                   | <ul> <li>その他レジスタ <sup>(注2)</sup> 、CPU、および<br/>内部状態</li> </ul>                                                                                                                                                                                                              |

| 独立ウォッチドッグタイマ<br>リセット |                                                                                                                 | 独立ウォッチドッグタイマのレジスタ<br>(IWDTRR、IWDTSR)                                                                                                                                                                                                                                       |

|                      | ● ウォッチドッグタイマのレジスタ<br>(WDTRR、WDTCR、WDTSR、<br>WDTRCR、WDTCSTPR)                                                    | ● ウォッチドッグタイマのレジスタ<br>(WDTRR、WDTCR、WDTSR、<br>WDTRCR、WDTCSTPR)                                                                                                                                                                                                               |

|                      | <ul> <li>電圧監視機能1のレジスタ<br/>(LVD1CR0、LVCMPCR.LVD1E、<br/>LVDLVLR.LVD1LVL、<br/>LVD1CR1/LVD1SR)</li> </ul>           | <ul> <li>電圧監視機能 1 のレジスタ<br/>(LVD1CR0、LVD1CMPCR、<br/>LVD1CR1/LVD1SR)</li> </ul>                                                                                                                                                                                             |

|                      | <ul> <li>電圧監視機能2のレジスタ<br/>(LVD2CR0、LVCMPCR.LVD2E、<br/>LVDLVLR.LVD2LVL、<br/>LVD2CR1/LVD2SR)</li> </ul>           | ● 電圧監視機能 2 のレジスタ<br>(LVD2CR0、LVD2CMPCR、<br>LVD2CR1/LVD2SR)                                                                                                                                                                                                                 |

|                      | ● LOCO のレジスタ(LOCOCR)                                                                                            | ● LOCO レジスタ(LOCOCR)                                                                                                                                                                                                                                                        |

|                      | MOSC のレジスタ(MOMCR)                                                                                               | ● MOSC レジスタ (MOMCR)                                                                                                                                                                                                                                                        |

|                      | ● MPU のレジスタ                                                                                                     | <ul> <li>バス、MPU および TrustZone エラー<br/>レジスタ (BUS_ERROR_ADDRESS<br/>レジスタ、BUS_ERROR_STATUS レ<br/>ジスタ) (注4)</li> </ul>                                                                                                                                                         |

|                      | ● 端子状態(XCIN/XCOUT 端子以外)                                                                                         | ● 端子状態                                                                                                                                                                                                                                                                     |

|                      | <ul> <li>低消費電力機能のレジスタ<br/>(DPSBYCR、DPSIER0~</li> <li>DPSIER3、DPSIFR0~DPSIFR3、<br/>DPSIEGR0~DPSIEGR2)</li> </ul> | <ul> <li>低消費電力機能のレジスタ<br/>(DPSBYCR、DPSIER0~<br/>DPSIER2、DPSIFR0~DPSIFR2、<br/>DPSIEGR0~DPSIEGR2)</li> </ul>                                                                                                                                                                 |

| 項目                   | RA6T1                                                                                                                                                                                                                                                                                                                                           | RA6T2                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 独立ウォッチドッグタイマ<br>リセット |                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>セキュリティ属性のレジスタ<br/>(CPUDSAR、RSTSAR、LVDSAR、<br/>CGFSAR、LPMSAR、DPFSAR、<br/>ICUSARX、BUSSARA、BUSSARB、<br/>CSAR、MMPUSARA、MMPUSARB、<br/>DMACSAR、DTCSAR、ELCSARA、<br/>ELCSARB、PMSAR、SRAMSAR、<br/>STBRAMSAR、FSAR、PSARB、<br/>PSARC、PSARD、PSARE、<br/>MSSAR、TZFSAR)</li> </ul>                                                                                                                |

|                      | <ul><li>その他レジスタ <sup>(注 1)</sup> 、CPU、および<br/>内部状態</li></ul>                                                                                                                                                                                                                                                                                    | <ul><li>その他レジスタ <sup>(注2)</sup> 、CPU、および<br/>内部状態</li></ul>                                                                                                                                                                                                                                                                                                                               |

| ウォッチドッグタイマリセット       | <ul> <li>ウォッチドッグタイマのレジスタ<br/>(WDTRR、WDTCR、WDTSR、<br/>WDTRCR、WDTCSTPR)</li> <li>電圧監視機能1のレジスタ<br/>(LVD1CR0、LVCMPCR.LVD1E、<br/>LVDLVLR.LVD1LVL、<br/>LVD1CR1/LVD1SR)</li> <li>電圧監視機能2のレジスタ<br/>(LVD2CR0、LVCMPCR.LVD2E、<br/>LVDLVLR.LVD2LVL、<br/>LVD2CR1/LVD2SR)</li> <li>LOCOのレジスタ (LOCOCR)</li> <li>MOSCのレジスタ (MOMCR)</li> <li>MPUのレジスタ</li> </ul> | <ul> <li>独立ウォッチドッグタイマのレジスタ (IWDTRR、IWDTSR)</li> <li>ウォッチドッグタイマのレジスタ (WDTRR、WDTCR、WDTSR、WDTRCR、WDTCSTPR)</li> <li>電圧監視機能 1 のレジスタ (LVD1CR0、LVD1CMPCR、LVD1CR1/LVD1SR)</li> <li>電圧監視機能 2 のレジスタ (LVD2CR0、LVD2CMPCR、LVD2CR1/LVD2SR)</li> <li>LOCO レジスタ (LOCOCR)</li> <li>MOSC レジスタ (MOMCR)</li> <li>バス、MPU および TrustZone エラーレジスタ (BUS_ERROR_ADDRESS レジスタ、BUS_ERROR_STATUS レジスタ) (注4)</li> </ul> |

|                      | <ul> <li>端子状態 (XCIN/XCOUT 端子以外)</li> <li>低消費電力機能のレジスタ<br/>(DPSBYCR、DPSIER0~<br/>DPSIER3、DPSIFR0~DPSIFR3、<br/>DPSIEGR0~DPSIEGR2)</li> </ul>                                                                                                                                                                                                      | <ul> <li>端子状態</li> <li>低消費電力機能のレジスタ<br/>(DPSBYCR、DPSIER0~<br/>DPSIER2、DPSIFR0~DPSIFR2、DPSIEGR0~DPSIEGR2)</li> <li>セキュリティ属性のレジスタ<br/>(CPUDSAR、RSTSAR、LVDSAR、CGFSAR、LPMSAR、DPFSAR、ICUSARX、BUSSARA、BUSSARB、CSAR、MMPUSARB、DMACSAR、DTCSAR、ELCSARA、ELCSARA、ELCSARB、PMSAR、SRAMSAR、STBRAMSAR、FSAR、PSARB、PSARC、PSARD、PSARE、MSSAR、TZFSAR)</li> <li>その他レジスタ (注2)、CPU、および</li> </ul>                  |

|                      | 内部状態                                                                                                                                                                                                                                                                                                                                            | 内部状態                                                                                                                                                                                                                                                                                                                                                                                      |

| 項目          | RA6T1                                                                                                                                                                                                 | RA6T2                                                                                                                                                                                                                                                                      |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 電圧監視 0 リセット |                                                                                                                                                                                                       | ● 独立ウォッチドッグタイマのレジスタ                                                                                                                                                                                                                                                        |

|             | <ul> <li>ウォッチドッグタイマのレジスタ<br/>(WDTRR、WDTCR、WDTSR、<br/>WDTRCR、WDTCSTPR)</li> <li>電圧監視機能 1 のレジスタ<br/>(LVD1CR0、LVCMPCR.LVD1E、<br/>LVDLVLR.LVD1LVL、<br/>LVD1CR1/LVD1SR)</li> <li>電圧監視機能 2 のレジスタ</li> </ul> | <ul> <li>(IWDTRR、IWDTSR)</li> <li>ウォッチドッグタイマのレジスタ<br/>(WDTRR、WDTCR、WDTSR、WDTRCR、WDTCSTPR)</li> <li>電圧監視機能 1 のレジスタ<br/>(LVD1CR0、LVD1CMPCR、LVD1CR1/LVD1SR)</li> <li>電圧監視機能 2 のレジスタ</li> </ul>                                                                                |

|             | (LVD2CR0、LVCMPCR.LVD2E、<br>LVDLVLR.LVD2LVL、<br>LVD2CR1/LVD2SR)  ■ LOCO のレジスタ(LOCOCR、                                                                                                                  | (LVD2CR0、LVD2CMPCR、<br>LVD2CR1/LVD2SR)  ■ LOCOのレジスタ(LOCOCR、                                                                                                                                                                                                                |

|             | LOCOUTCR)                                                                                                                                                                                             | LOCOUTCR)                                                                                                                                                                                                                                                                  |

|             | <ul><li>MOSC のレジスタ (MOMCR)</li><li>AGT のレジスタ</li></ul>                                                                                                                                                | ● MOSC レジスタ(MOMCR)                                                                                                                                                                                                                                                         |

|             | ● MPU のレジスタ                                                                                                                                                                                           | <ul> <li>バス、MPU および TrustZone エラー<br/>レジスタ (BUS_ERROR_ADDRESS<br/>レジスタ、BUS_ERROR_STATUS レ<br/>ジスタ) (注4)</li> </ul>                                                                                                                                                         |

|             | ● 端子状態(XCIN/XCOUT 端子以外)                                                                                                                                                                               | ● 端子状態                                                                                                                                                                                                                                                                     |

|             | <ul> <li>低消費電力機能のレジスタ<br/>(DPSBYCR、DPSIER0~</li> <li>DPSIER3、DPSIFR0~DPSIFR3、<br/>DPSIEGR0~DPSIEGR2)</li> </ul>                                                                                       | <ul><li>低消費電力機能のレジスタ<br/>(DPSBYCR、DPSIER0~<br/>DPSIER2、DPSIFR0~DPSIFR2、<br/>DPSIEGR0~DPSIEGR2)</li></ul>                                                                                                                                                                   |

|             |                                                                                                                                                                                                       | <ul> <li>セキュリティ属性のレジスタ<br/>(CPUDSAR、RSTSAR、LVDSAR、<br/>CGFSAR、LPMSAR、DPFSAR、<br/>ICUSARX、BUSSARA、BUSSARB、<br/>CSAR、MMPUSARA、MMPUSARB、<br/>DMACSAR、DTCSAR、ELCSARA、<br/>ELCSARB、PMSAR、SRAMSAR、<br/>STBRAMSAR、FSAR、PSARB、<br/>PSARC、PSARD、PSARE、<br/>MSSAR、TZFSAR)</li> </ul> |

|             | <ul> <li>その他レジスタ <sup>(注 1)</sup> 、CPU、および<br/>内部状態</li> </ul>                                                                                                                                        | <ul> <li>その他レジスタ <sup>(注2)</sup> 、CPU、および<br/>内部状態</li> </ul>                                                                                                                                                                                                              |

| 電圧監視 1 リセット |                                                                                                                                                                                                       | ● 独立ウォッチドッグタイマのレジスタ<br>(IWDTRR、IWDTSR)                                                                                                                                                                                                                                     |

|             | ● ウォッチドッグタイマのレジスタ<br>(WDTRR、WDTCR、WDTSR、<br>WDTRCR、WDTCSTPR)                                                                                                                                          | ● ウォッチドッグタイマのレジスタ<br>(WDTRR、WDTCR、WDTSR、<br>WDTRCR、WDTCSTPR)                                                                                                                                                                                                               |

|             | <ul><li>LOCO のレジスタ (LOCOCR、<br/>LOCOUTCR)</li></ul>                                                                                                                                                   | <ul><li>LOCO のレジスタ (LOCOCR、<br/>LOCOUTCR)</li></ul>                                                                                                                                                                                                                        |

|             | <ul><li>MOSC のレジスタ (MOMCR)</li><li>AGT のレジスタ</li></ul>                                                                                                                                                | MOSC レジスタ (MOMCR)                                                                                                                                                                                                                                                          |

|             | <ul><li>AGT のレジスタ</li><li>MPU のレジスタ</li></ul>                                                                                                                                                         | <ul> <li>バス、MPU および TrustZone エラー<br/>レジスタ (BUS_ERROR_ADDRESS<br/>レジスタ、BUS_ERROR_STATUS レ<br/>ジスタ) (注4)</li> </ul>                                                                                                                                                         |

|             | ● 端子状態(XCIN/XCOUT 端子以外)                                                                                                                                                                               | ● 端子状態                                                                                                                                                                                                                                                                     |

| 項目                   | RA6T1                                                                                                                                                                                                                                                                                    | RA6T2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |