# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# H8SX Family

# $\Delta\Sigma$ A/D Converter User's Guide

# Introduction

This application note describes the basic principles of  $\Delta\Sigma$  A/D converter and the main features of the  $\Delta\Sigma$  A/D converter integrated in the H8SX family.

# Contents

| 1. | Basic Principles of the Delta Sigma Architecture                    | 2  |

|----|---------------------------------------------------------------------|----|

| 2. | $\Delta\Sigma$ A/D Converter                                        | 7  |

| 3. | Filter                                                              | 11 |

| 4. | Errors and Methods of Correction                                    | 17 |

| 5. | Functional Description of the H8SX Family $\Delta\Sigma$ Conversion | 21 |

| 6. | Recommended External Circuit and Considerations                     | 35 |

| 7. | Documents for Reference                                             | 38 |

# RENESAS

# 1. Basic Principles of the $\Delta \Sigma$ A/D Converters

# 1.1 Difference from Successive-Approximation-Type A/D Converters

#### 1.1.1 Successive-Approximation-Type A/D Converters

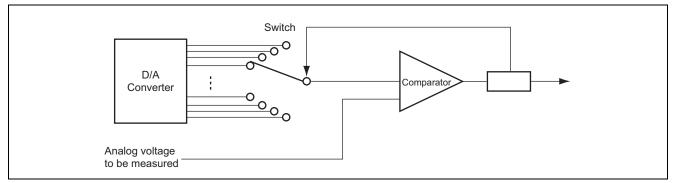

Measurement in this method proceeds by comparing the values of the analog voltage to be measured with a variable reference voltage generated by a D/A converter (DAC). The operation can be summarized as follows.

- 1. The output of the DAC is set to the central value of its output range and compared with the voltage to be measured.

- 2. According to whether the analog voltage to be measured is less or greater than the central value, the output of the DAC is set to the central value of the lower or upper half of its output range and the voltage are again compared.

- 3. The above step is performed up to n + 1 times (resolution is assumed to be n bits) to complete the comparison.

This may be compared to measuring an object by using rulers with various lengths and determining which most closely matches the length of the object to be measured.

Figure 1.1 A/D Converter of the Successive-Approximation Type

#### 1.1.2 $\Delta\Sigma$ -Type A/D Converter

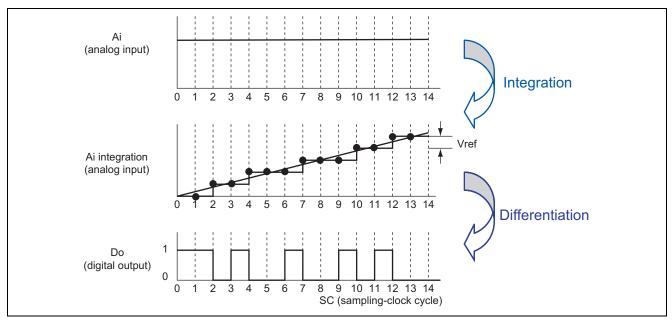

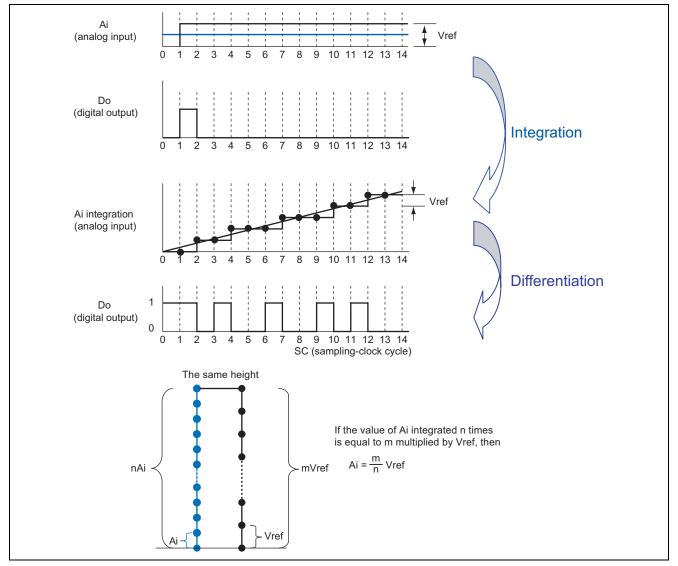

In an A/D converter of the delta-sigma ( $\Delta\Sigma$ ) type, the voltage to be measured is sampled and integrated. It is then compared (differentiated) with a constant reference voltage and converted to digital values.

This is similar to measuring the length of an object by counting the number of 1 inch units and then multiplying the result by 1 inch. Since this method of analog-to-digital conversion includes both differentiation and integration, it is called the delta-sigma (or sigma-delta) technique.

Figure 1.2 Principle of a  $\Delta\Sigma$ -Type A/D Converter

### **1.2** Overview of the $\Delta \Sigma$ A/D Converter

An example of measuring a direct current (DC) voltage is described here for simplicity. When the analog input (Ai) is compared without integration, the measurement is proceeded as follows.

- When SC\* = 1, the digital output is 1 since the voltage being compared with the analog input was 0 V and thus 0 < Ai when SC = 0. A voltage Vref is then added to the reference voltage.

- When SC = 2, Vref is compared with Ai. The digital output is 0 since Vref > Ai. The same voltage value is thus used in the next round of measurement.

- When SC = 3, Vref is again compared with Ai. The digital output is 0 since Vref > Ai. The same voltage value is again to be used in the next round of measurement.

However many times the above procedure is repeated, the result will be a digital output made up of a single 1 for the first measurement and successive 0s for subsequent measurements, leaving the value of Ai unchanged.

Note: \* SC indicates sampling clocks for  $\Delta\Sigma$  A/D Conversion as shown in fig 1.3.

Figure 1.3 Comparison of the Integrated Value and Vref

# RENESAS

Now, let us compare the integrated value with Vref as shown in figure 1.3.

- When SC = 1, Ai has only been integrated once and Vref remains 0 V. The digital output is 1 since Vf is less than or equal to Ai and therefore Vref is added to the above 0 V.

- When SC = 2, Ai has been integrated twice. Vf is compared with 2Ai. The digital output is now 0 since Vref > 2Ai. The same voltage (Vref) is used in the next round of measurement.

- When SC = 3, Ai has been integrated three times. Vf is compared with 3Ai. The digital output is 1 since Vref < 3Ai. Vref is again added to the voltage for use in the next measurement (the result being 2Vref).

- When SC = 4, Ai has been integrated four times. Thus 2Vref is compared with 4Ai. In figure 1.3, the digital output is 0 since 2Vref > 4Ai. The same voltage (2Vref) is then used in the next round of measurement.

The above procedure is repeated several times.

Ai is periodically integrated and the resulting slope represents Ai. The integral is compared with Vf to check the relation between the magnitudes of the two values. Addition is repeated and if the result is greater than Vf, Vref is again added to Vf on the next round, and the comparison is repeated. That is, Vf is compared with Ai represented as a slope. Each increase in Ai produced by integration is smaller than Vref.

Ai integration is repeated several times with the result compared to Vf until the result of integration has become greater than Vf. Then another Vref unit is then added to Vf, which is again compared with the integral of Ai. Sampling twice is better than sampling once, and sampling three times is better than sampling twice, and in this way we can see how the precision improves with repeated sampling. In other words, more samples correspond to greater accuracy.

# 1.3 Advantages of the $\Delta \Sigma$ A/D Converter

#### 1.3.1 Successive-Approximation-Type A/D Converter

- The speed of conversion is high yet devices with lower resolutions are relatively cheap to implement.

- Obtaining N bits of resolution requires the inclusion of 2<sup>n</sup> on-chip resistors. Process variation limits the precision of resistors formed on silicon wafer. This approach is thus not suitable for high resolution. That is, due to the limitation imposed on resolution by variation in process accuracy, a new method is necessary for high resolution.

#### 1.3.2 $\Delta\Sigma$ -Type A/D Converter

- Converters of the  $\Delta\Sigma$  type have lower conversion speeds than those of the successive-approximation type but higher conversion speeds than those of the double-integrating type.

- This method is suitable for high resolution.

| Item            | Successive-Approximation Type | ΔΣ Τуре                   |

|-----------------|-------------------------------|---------------------------|

| Method          | Sample and hold               | Sampling                  |

| Module size     | Large                         | Fitting                   |

| Conversion time | Fast (5.33 μs)                | Slow (91.5 μs)            |

|                 | (H8SX/1622)                   | (H8SX/1622)               |

| High resolution | No                            | Yes                       |

| Frequency band  | Without constraint            | Depends on digital filter |

| Noise immunity  | Low                           | High (noise shaping)      |

#### Table 1.1 Comparison of Characteristics of Successive Approximation and $\Delta\Sigma$ Converters

# 2. $\Delta \Sigma A/D$ Converter

## 2.1 Configuration

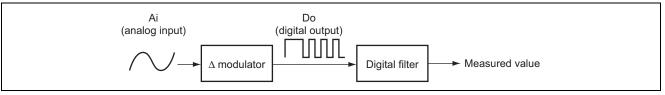

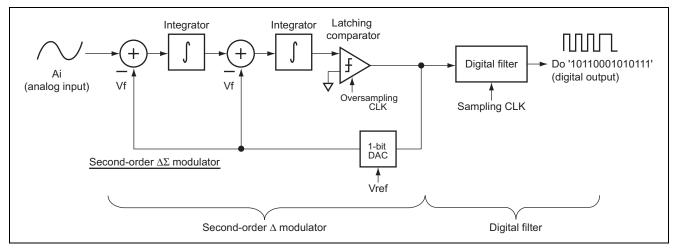

A  $\Delta\Sigma$  A/D converter consists of one or more integrators, a delta modulator, and a digital filter. The delta modulator modulates the analog input signal to produce a digital signal. The digital filter subsequently eliminates noise to produce the measured data.

Figure 2.1 Configuration of a  $\Delta\Sigma$  A/D Converter

# **2.2** $\triangle$ Modulator

The digital values are produced by comparing an analog input (Ai) with the output of the integrator (Vf). The flow of operations is as follows.

- 1. The adder determines the difference between the integrator's output (Vf) of the result of D/A-conversion in the previous clock cycle and the analog input signal (Ai).

- 2. The comparator compares the adder's output with 0 V. According to the result the comparator outputs a digital value of 1 if Ai > Vf or 0 if Ai < Vf.

The above procedure is repeated to convert the analog input into a stream of digital values.

Disadvantages of the  $\Delta$  modulator necessitate a countermeasure as follows:

[Conversion]

The digital output is a signal obtained by differentiating the analog signal.

[Disadvantages]

- 1. Direct current voltages cannot be converted.

- 2. Slope overload\* is not supported and precise conversion of high-frequency signal is difficult.

- Note: \* Slope overload means the situation where the signal rapidly changes by such a large amount (high voltage and rapid change) that the change is faster than the speed of integration.

[Countermeasure]

Integrate the analog input before it is input to the  $\Delta$  modulator.

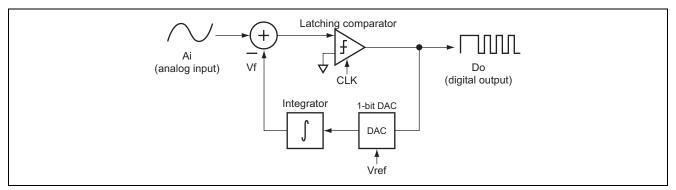

Figure 2.2 △ Modulator

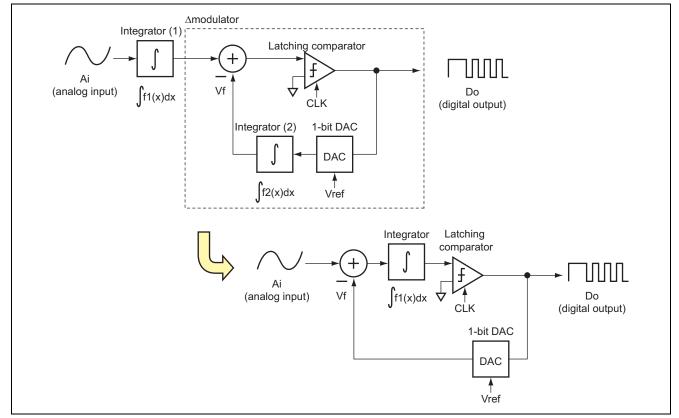

# **2.3** $\Delta \Sigma$ Modulator (Integrator + $\Delta$ Modulator)

For conversion of direct-current voltages, an integrator is added to the input circuit of the modulator. A  $\Delta$  modulator at the input of which an integrator has been included is called a  $\Delta\Sigma$  modulator.

#### $\Delta \Sigma$ modulator: Integrator + $\Delta$ modulator

Since the two integrators can be treated as a single integrator according to the approach shown below, the integrator is placed after the adder.

$$\int f1(x)dx + \int f2(x)dx$$

$$= \int (f1(x) + f2(x)) dx$$

$$= \int f(x)dx$$

Figure 2.3 Input-Stage Integrator + △ Modulator

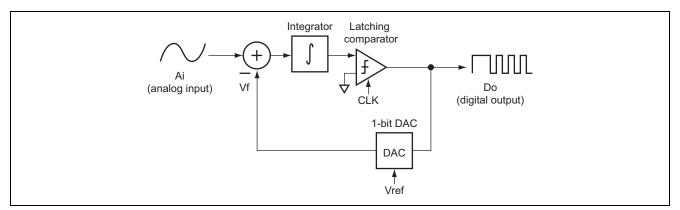

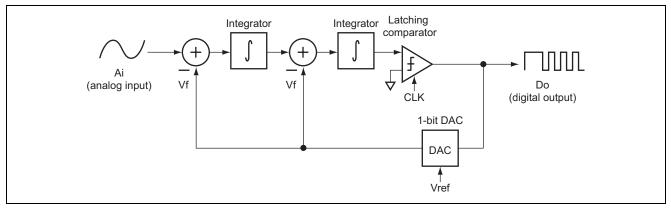

# **2.4** First- and Second-Order $\Delta \Sigma$ Modulators

The first-order  $\Delta\Sigma$  modulator has a single integrator while the second-order  $\Delta\Sigma$  modulator has two. The second-order  $\Delta\Sigma$  modulator is superior to the first-order  $\Delta\Sigma$  modulator in terms of noise-shaping effect.

Figure 2.4 First-Order  $\Delta \Sigma$  Modulator

Figure 2.5 Second-Order  $\Delta\Sigma$  Modulator

### **2.5** Second-Order $\Delta \Sigma$ A/D Converter

The operation of the second-order  $\Delta\Sigma$  A/D converter is summarized as follows:

- 1. The analog input is integrated twice.

- 2. Differentiation is performed twice in two loops (although the principles of operation would have differentiation twice, the result of expanding the formula is their unification as a single comparator in the circuit).

- 3. Since differentiation and integration are each other's reverse functions, differentiation and integration ultimately restore the original. In addition, we have now obtained a digital signal.

- 4. Digital filtering removes the noise introduced by sampling.

Figure 2.6 Second-Order  $\Delta\Sigma$  A/D Converter

# 3. Filter

# 3.1 Digital Filter

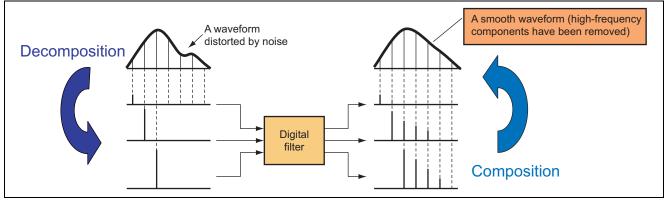

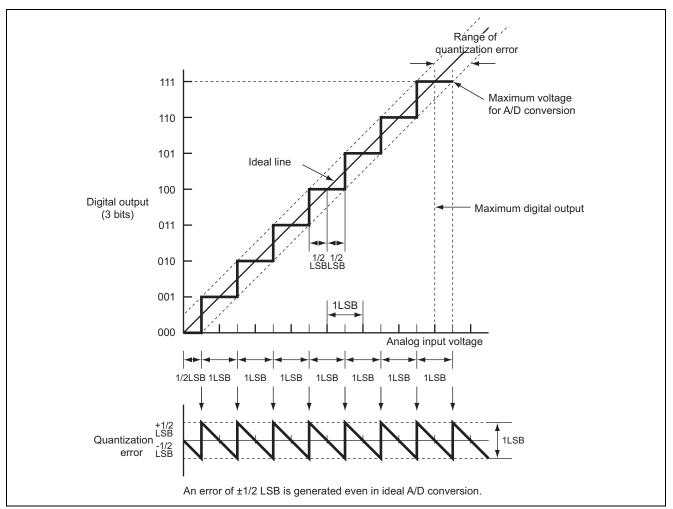

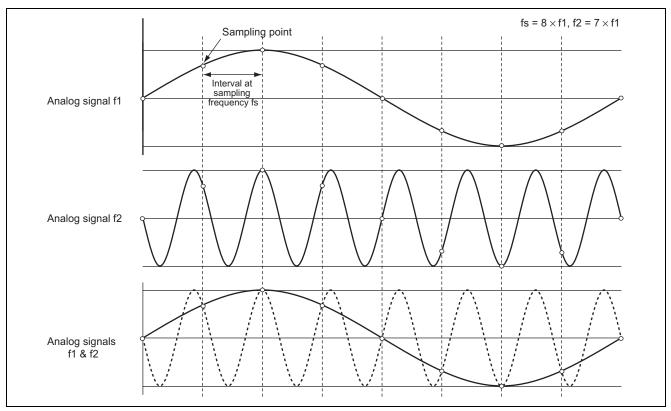

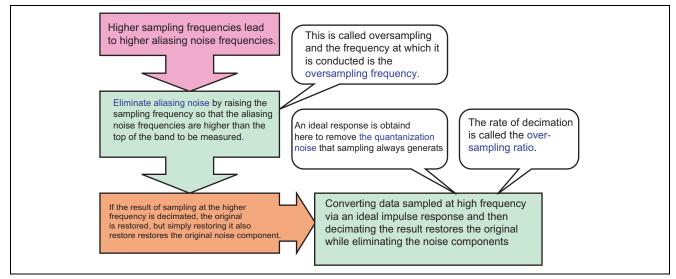

The digital output of the  $\Delta\Sigma$  modulator contains two types of noise from sampling: quantization error (figure 3.2) and aliasing noise (figure 3.3). The characteristics of a digital filter are handled by impulse responses. That is, by the calculating digital values in real time, we can perform interpolation and decimation to remove noise components. Decimation is the operation of converting a higher sampling frequency to a lower sampling frequency.

Figure 3.1 Digital Filter

# 3.2 Quantization Error

Figure 3.2 Quantization Error

# 3.3 Aliasing Noise

When analog signals f1 and f2 (f1 multiplied by 7) below are sampled at eight times the frequency of f1, the sampling points in analog signals of f1 and f2 become identical. The sampling points thus have a frequency component of f2, and f2 is called an aliasing noise of f1.

Figure 3.3 Aliasing Noise

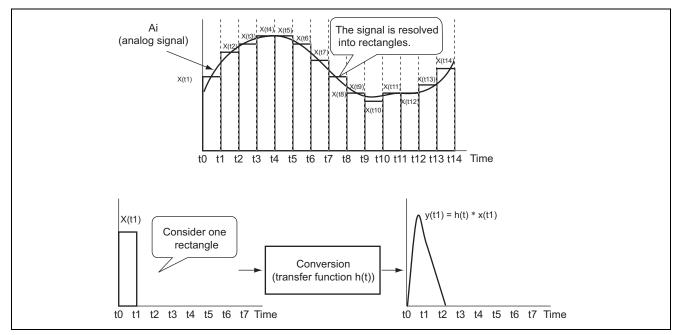

# 3.4 Impulse Response

The impulse response is one way to analyze a continuous analog signal. The impulse response is a response generated when a unit impulse is input to a system.

- 1. The continuous analog signal is decomposed into impulses, since it is difficult to analyze the signal without modification.

- 2. Given a transfer function h(t), the waveform in response to a single impulse is obtained by y(t) = h(t) \* x(t).

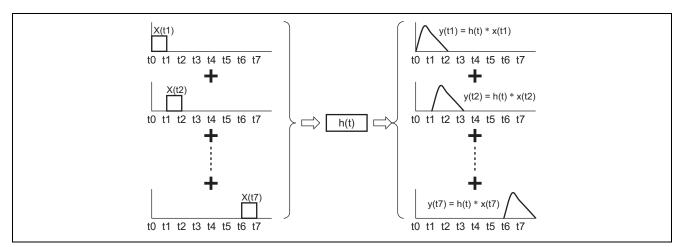

- 3. By definition, the principle of superposition is valid in a linear system. Consequently, the superposition of the waveforms in response to the individual pulses is ultimately the waveform in response to the overall input signal.

Figure 3.4 Impulse Responses

Figure 3.5 Definition of Superposition

# 3.5 Noise Reduction by Digital Filtering

Figure 3.6 Procedure for Noise Reduction by Digital Filtering

### 3.6 Methods of Digital Filtering

The role of the digital filter is to convert sampled data into a stream of ideal impulse responses. To be specific the conversion is achieved by multiplying the input impulses by a transfer function. There are two methods, which differ according to how multiplication by the transfer function is achieved.

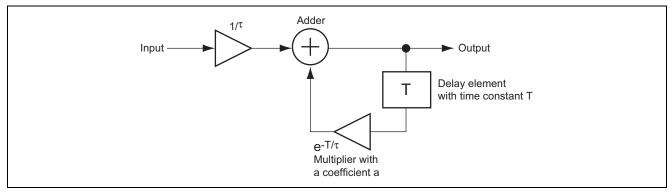

1. IIR (Infinite Impulse Response) Filter

This is a method that combines an adder and a delay element to form a feedback loop. This kind of filter is referred to as an infinite impulse response filter because the output waveform in response to an impulse is dampened but continues indefinitely.

Figure 3.7 IIR (Infinite Impulse Response) Filter

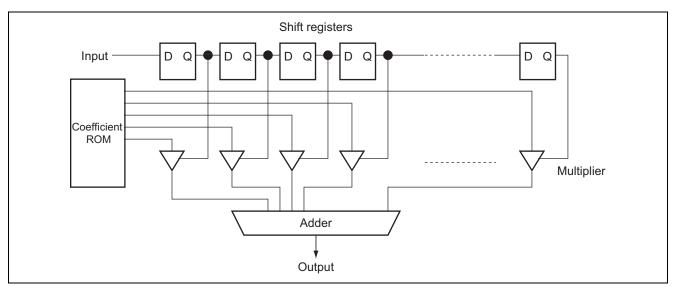

2. FIR (Finite Impulse Response) Filter

An FIR filter consists of shift registers, multipliers which multiply output of the registers by data, and an adder. The data here are coefficients calculated from impulse response of an ideal filter.

Figure 3.8 FIR (Finite Impulse Response) Filter

# 4. Errors and Methods of Correction

#### 4.1 Errors in A/D Converters

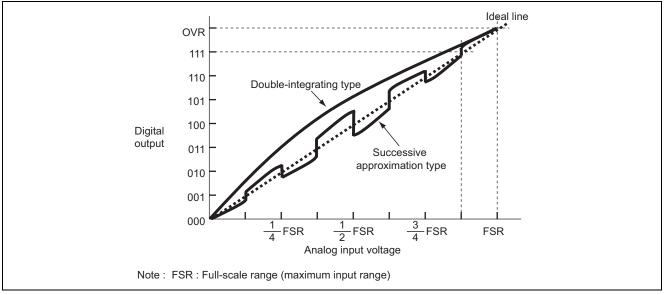

#### 4.1.1 Successive Approximation A/D Converter

Major errors are readily generated in the output characteristics at point where output values change, such as 1/2 FSR and 1/4 FSR. Differential nonlinearity is a major portion of the error and reaches its maximum where all bits change at 1/2 FSR.

#### 4.1.2 Double-Integrating A/D Converter

The output characteristic has no sharp changes, integral nonlinearity produces a large error, and the curve produced is smooth.

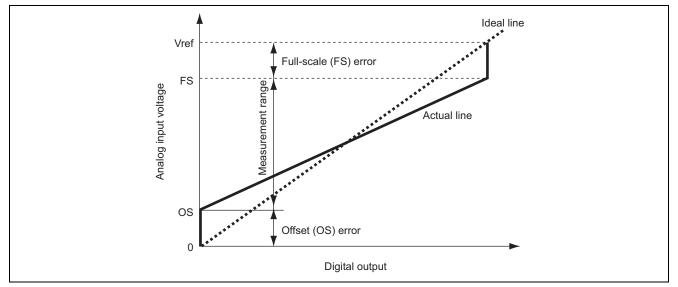

#### 4.1.3 $\Delta\Sigma$ -Type A/D Converter

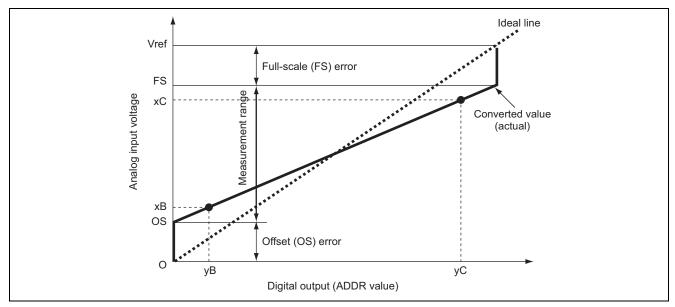

Since offset (OS) error and full-scale (FS) error are produced, the range of measurement becomes OS to FS. Once offset and full-scale correction have been applied, an output characteristic with superior linearity is obtained.

Figure 4.1 Errors in Successive Approximation and Double-Integrating Type Converters

Figure 4.2 Errors in  $\Delta\Sigma$  A/D Converters

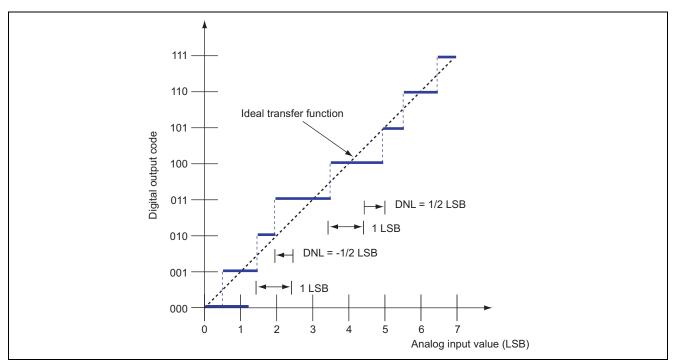

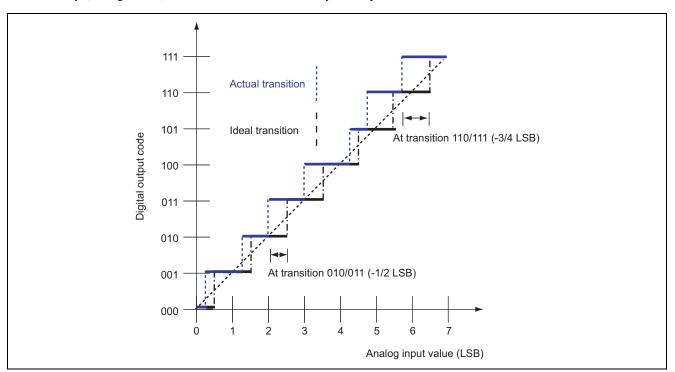

#### 4.1.4 Differential Nonlinearity Error

The differential nonlinearity error, as shown in figure 4.3, is the differences between the ideal value corresponding to one LSB and the actual analog step sizes. When the step size is exactly equivalent to the ideal value for one LSB, the differential nonlinearity error is zero. When the differential nonlinearity exceeds one LSB, the proportionality of output to input is further reduced. Furthermore, code loss may occur. That is, the converter becomes incapable of producing one or more of the 2n codes.

Figure 4.3 Differential Nonlinearity Error

### 4.1.5 Integral Nonlinearity Error

The deviation of the actual result of conversion from the value given by the ideal line is referred to as integral nonlinearity (see figure 4.4). This deviation is measured by the step.

Figure 4.4 Integral Nonlinearity Error

# 4.2 Correction of Offset and Full-Scale Errors

#### 4.2.1 Approach to Correction

Figure 4.5 shows the relation between digital values (ADDR values) and analog values (to be measured) of the  $\Delta\Sigma$  A/D converter.

The response of an ideal A/D converter, as shown as a dashed line in figure 5.5, is linear from the origin to the fullscale voltage. Since offset (OS) error and full-scale (FS) error are produced, the actual relation is portrayed by the solid line. Consequently, offset/full-scale error correction should be applied to derive more accurate values from the measured digital values.

Figure 4.5 Relation of Analog Value (to be Measured) and Digital Value (ADDR Value)

The following equations describe the relations between x and y in the solid line of Fig 4.5.

| lsb = (xC - xB) / (yC - yB)          | (1) |

|--------------------------------------|-----|

| x = (xC - xB) / (yC - yB) * y + OS   | (2) |

| OS = xB - (xC - xB) / (yC - yB) * yB | (3) |

and from (1), (2), and (3), we have:

x = Isb \* y + xB - Isb \* yB = Isb \* (y - yB) + xB

#### 4.2.2 Correcting Offset and Full-Scale Errors

The procedure for offset/full-scale error correction is as follows.

- 1. Measure x and y values at the four points A, B, C, and D shown in figure 4.5.

- 2. Calculate the slope (lsb) by determining x and y values at points B and C.

- 3. Calculate the target value from the digital value (the value in ADDR).

Target value = Slope (lsb) \* (ADDR value - yB) + xB

# 5. Functional Description of the H8SX Family $\Delta\Sigma$ A/D

# 5.1 Basic Operations

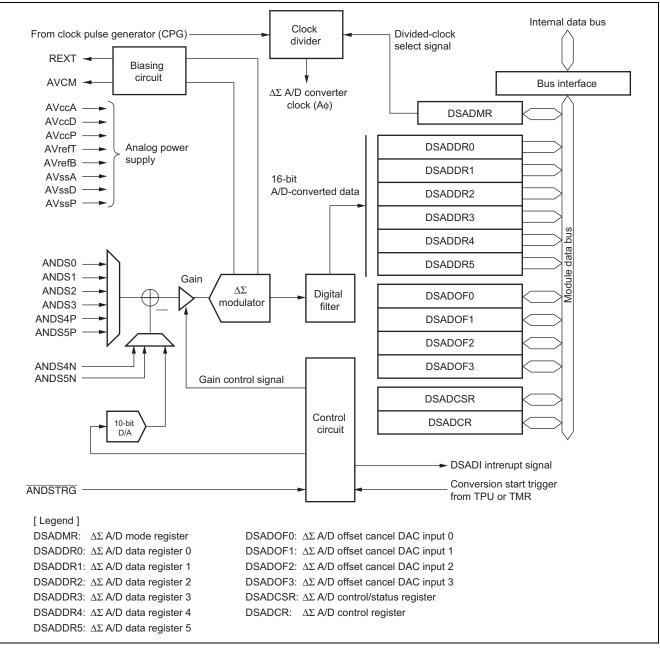

The  $\Delta\Sigma$  A/D converter of the H8SX Family uses a  $\Delta\Sigma$  modulator to convert analog input voltages within the range specified by the voltages on the AVrefT and AVrefB pins into digital values with a resolution of 16-bits. The  $\Delta\Sigma$  A/D converter is composed of an analog block with a  $\Delta\Sigma$  modulator as the main component, and a digital filter, and a control blocks.

In the analog block, the DS modulator amplifies the input signals (eight-fold when the GAIN1 and GAIN0 bits in DSADCR is set to B'11) and converts them. During this process, the  $\Delta\Sigma$  offsets of the signals input from the singleended input signal pins (ANDS0, ANDS1, ANDS2, ANDS3) are cancelled by setting offset values in the DSADOF0 to DSADOF3 registers. In addition differential input are supported on pins (ANDS4P, ANDS4N and ANDS5P, ANDS5N). The voltage of a selected analog input signal is sampled at the A $\phi$ /8 clock frequency (oversampling frequency) and converted to a series of digital values by the second-order  $\Delta\Sigma$  modulator. The result of conversion is passed through a decimation filter (digital filter) and stored in the corresponding  $\Delta\Sigma$  A/D data register as a 16-bit signed binary number (two's complement).

The  $\Delta\Sigma$  A/D converter operates in either single mode or scan mode. Multiple channels are specified by selecting multiple A/D conversion channel-selection bits.

Figure 5.1 shows a block diagram of the  $\Delta\Sigma$  A/D converter and table 5.1 shows its pin configuration.

Figure 5.1 Block Diagram of the  $\Delta\Sigma$  A/D Converter

# RENESAS

#### Table 5.1 Pin Configuration

| Pin Name                                                    | Abbreviation         | I/O    | Function                                                                                            |

|-------------------------------------------------------------|----------------------|--------|-----------------------------------------------------------------------------------------------------|

| Analog input pin 0                                          | ANDS0                | Input  | Analog input pins: Single-ended input                                                               |

| Analog input pin 1                                          | ANDS1                | Input  | _                                                                                                   |

| Analog input pin 2                                          | ANDS2                | Input  | _                                                                                                   |

| Analog input pin 3                                          | ANDS3                | Input  | _                                                                                                   |

| Analog input pin 4-P                                        | ANDS4P               | Input  | Analog input pins: Differential input                                                               |

| Analog input pin 4-N                                        | ANDS4N               | Input  | _                                                                                                   |

| Analog input pin 5-P                                        | ANDS5P               | Input  | Analog input pins: Differential input                                                               |

| Analog input pin 5-N                                        | ANDS5N               | Input  | _                                                                                                   |

| External trigger input pin for $\Delta\Sigma$ A/D converter | ANDSTRG              | Input  | External trigger input pin for starting $\Delta\Sigma$ A/D conversion                               |

| Analog power supply pin                                     | AVccA* <sup>1</sup>  | Input  | Power supply pin for the analog section of the $\Delta\Sigma$ A/D converter                         |

| Analog power supply pin                                     | AVccD* <sup>1</sup>  | Input  | Power supply pin for the control circuit of the $\Delta\Sigma$ A/D converter                        |

| Analog power supply pin                                     | AVccP* <sup>1</sup>  | Input  | Power supply pin for the input pin control circuit of the $\Delta\Sigma$ A/D converter              |

| Analog ground pin                                           | AVssA                | Input  | Ground pin for the analog section of the $\Delta\Sigma$ A/D converter                               |

| Analog ground pin                                           | AVssD                | Input  | Ground pin for the control circuit of the $\Delta\Sigma$ A/D converter                              |

| Analog ground pin                                           | AVssP                | Input  | Ground pin for the input pin control circuit of the $\Delta\Sigma$ A/D converter                    |

| $\Delta\Sigma$ reference voltage (high)                     | AVrefT* <sup>2</sup> | Input  | Stabilizing capacitors connected (between                                                           |

| $\Delta\Sigma$ reference voltage (low)                      | AVrefB* <sup>2</sup> | Input  | $^{-}$ AV <sub>ref</sub> B and AV <sub>ref</sub> T; 10 $\mu$ F + 0.1 $\mu$ F)                       |

| Reference voltage pin                                       | AVCM                 | Output | Stabilizing capacitor connected (0.1 $\mu$ F between AVCM and AV <sub>SS</sub> A)                   |

| Reference current pin                                       | REXT                 | Output | External resistor connected between REXT and AV <sub>SS</sub> A. (51 k $\Omega$ with ±1% tolerance) |

Notes: 1. Always ensure that AVccA = AVccD = AvccP holds.

2. Furthermore ensure that AVccA = AVrefT, AVrefT > AVrefB, AVrefB = AVssA hold.

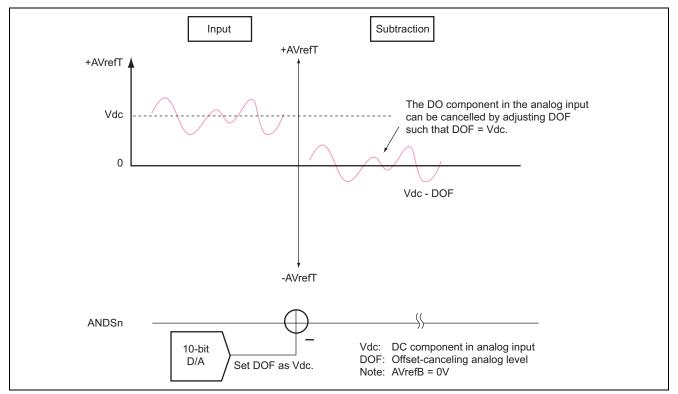

# 5.2 Offset Cancellation Function

For single-ended input signal, the DC component in the analog signal can be cancelled (subtracted) by setting the offset canceling value in the internal registers of DSADOF0 to DSADOF3. Be aware that this function does not cancel offset error in A/D conversion or offset in the amplifier.

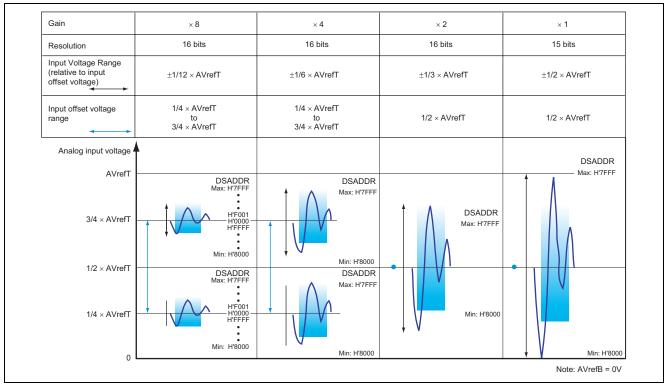

The offset-canceling analog level corresponding to the register setting can be illustrated as in the figure below. The possible offset-canceling analog level varies depending on the GAIN setting. Table 5.2 shows the corresponding relation between GAIN and DSADOFn settings.

#### Table 5.2 Setting Values of Gain and DSADOFn

|              | DSADOFn (n = 0 to 3) |                          |  |  |

|--------------|----------------------|--------------------------|--|--|

| GAIN1, GAIN0 | Settable Range       | Remarks                  |  |  |

| B'00         | H'0200               | Always set to H'0200.    |  |  |

| B'01         | H'0200               | Always set to H'0200.    |  |  |

| B'10         | H'0000 to H'03FE     | Bit 0 must be clear to 0 |  |  |

| B'11         | H'0000 to H'03FF     | _                        |  |  |

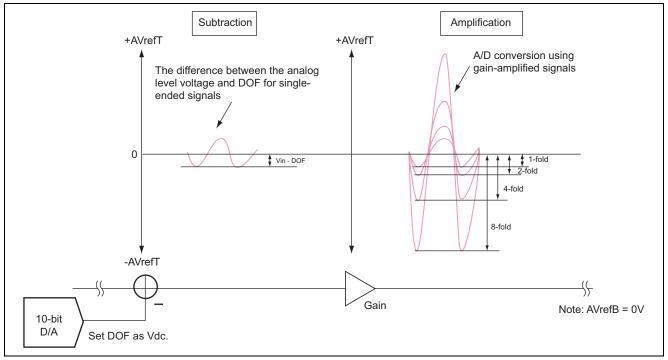

#### Figure 5.2 Offset Cancellation Function

# 5.3 Gain Function

An analog signal is amplified and input to the  $\Delta\Sigma A/D$  converter by setting the gain level (8-, 4-, 2-, or 1-fold) in the GAIN1 and GAIN0 bits of DSADCR internal register.

Figure 5.3 GAIN Function (For Single-Ended Inputs)

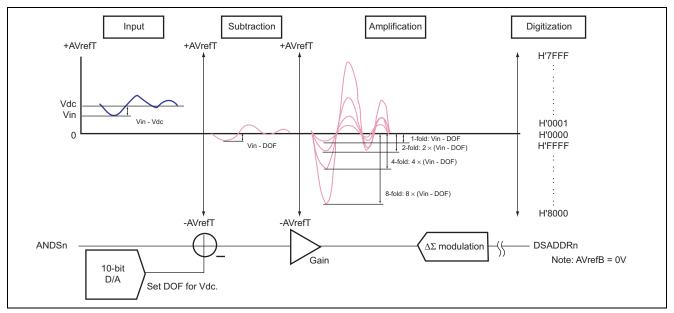

# 5.4 Single-Ended Input

For single-ended input, one analog level Vin (pin name: ANDS0, ANDS1, ANDS2, or ANDS3) and the offsetcanceling analog level DOF that is set in the DSADOFn corresponding to an analog input channel are used. The  $\Delta\Sigma$ ADC performs the subtraction "Vin – DOF" and uses the voltage difference between the analog level and DOF as the input signal.

Then, the input signal is amplified according to the gain setting (8- to 1-fold) to be input to the  $\Delta\Sigma$  modulator.

The  $\Delta\Sigma$  modulator converts the analog voltage within the range determined by the AVrefT and AVrefB pins into a digital value with 16-bit resolution. The A/D conversion result should be a positive value (H'0000 to H'7FFF) if Vin – DOF  $\geq 0$  (V), and be a negative value (H'FFFF to H'8000) if Vin – DOF < 0 (V).

Figure 5.4 Single-Ended Input

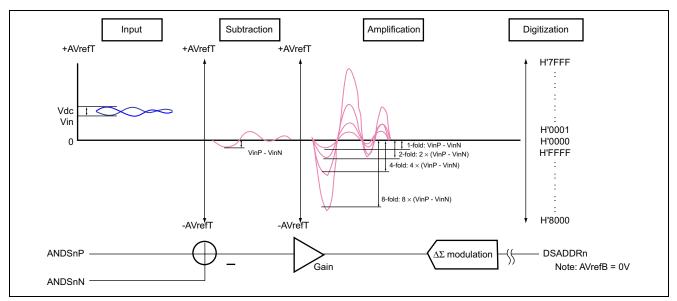

# 5.5 Differential Input

For differential input, two analog levels VinP – VinN (pin name: ANDS4P–ANDS4N, ANDS5P–ANDS5N) are used.

The  $\Delta\Sigma$ ADC performs the subtraction "VinP – VinN" and uses the voltage difference between the ANDSnP and ANDSnN analog levels as the input signal.

Then, the input signal is amplified according to the gain setting (8- to 1-fold) to be input to the  $\Delta\Sigma$  modulator.

The  $\Delta\Sigma$  modulator converts the analog voltage range determined by the AVrefT and AVrefB pins into a digital value with 16-bit resolution. The A/D conversion result should be a positive value (H'0000 to H'7FFF) if VinP – VinN  $\geq 0$  (V), and be a negative value (H'FFFF to H'8000) if VinP – VinN < 0 (V).

Figure 5.5 Differential Input

# 5.6 Operating Modes

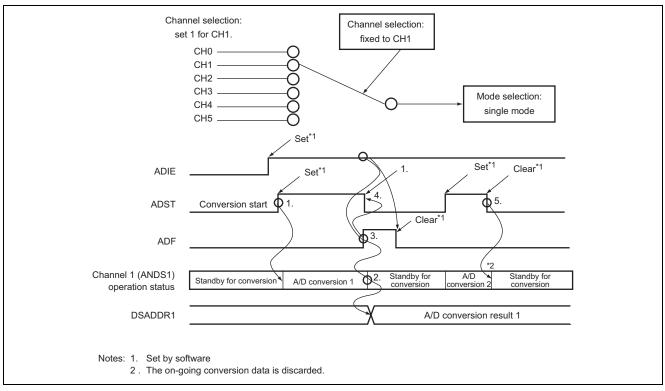

#### 5.6.1 Single Mode (Single Channel)

The operation in single mode is described below. Figure 5.6 shows an example of  $\Delta\Sigma$  A/D converter operation in single mode (single-value channel: channel 1 selected).

[Operating Conditions]

- Use channel 1.

- Enable  $\Delta \Sigma$  A/D interrupts

- Generate  $\Delta\Sigma$  A/D conversion complete interrupt requests (DSADI) \* (starting DMA by DSADI is disabled)

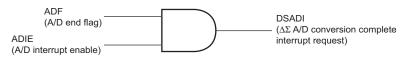

Note: \* The source of DSADI is as follows:

- 1. When the A/D start (ADST) bit in the  $\Delta\Sigma$  A/D control/status register (DSADCSR) is set to 1 by software or the trigger selected in the timer trigger select (TRGS1, TRGS0) bits of DSADCSR, A/D conversion on the selected channel is started.

- 2. When the A/D conversion is complete, the A/D conversion result data is transferred to the  $\Delta\Sigma$  A/D data register (DSADDR1) that corresponds to channel 1.

- 3. When the A/D conversion result is transferred to the register and the  $\Delta\Sigma$  A/D converter stops, the ADF bit in DSADCSR is set to 1. At this time, a DSADI interrupt request is generated (by clearing the ADF flag during the interrupt) since the ADIE bit is set to 1.

- 4. The ADST bit holds 1 during A/D conversion and is cleared automatically when the conversion is complete. Subsequently when the ADST bit is set to 1, A/D conversion on the selected channel is started again.

- 5. When the ADST bit is cleared during A/D conversion, the A/D conversion is aborted and the  $\Delta\Sigma$  A/D converter enters the standby state.

Figure 5.6 Example of  $\Delta\Sigma$  A/D Converter Operation in Single Mode (Single Channel: Channel 1 Selected)

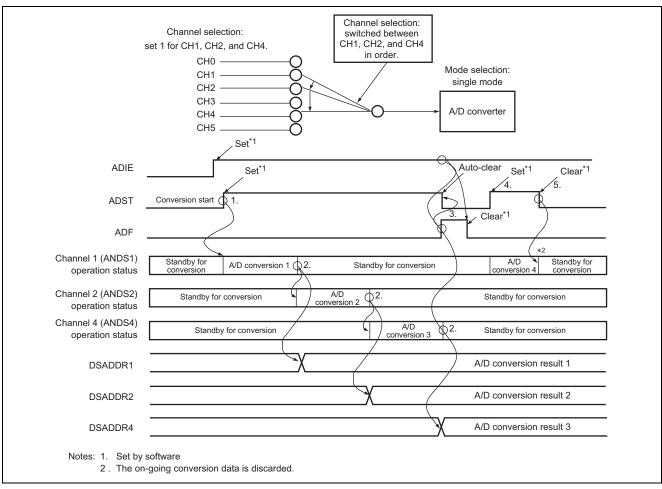

### 5.6.2 Single Mode (Multiple Channels)

The operation in single mode is described below. Figure 5.7 shows an example of  $\Delta\Sigma$  A/D converter operation in single mode (multiple channels: channels 1, 2, 4 selected).

[Operating Conditions]

- Use channels 1, 2, and 4.

- Enable  $\Delta \Sigma$  A/D interrupts

- Generate  $\Delta\Sigma$  A/D conversion complete interrupt requests (DSADI) \* (starting DMA by DSADI is disabled).

Note: \* Refer to section 5.6.1 for Operating Conditions for the source of DSADI.

- 1. When the ADST bit in DSADCSR is set to 1 by software or the trigger selected in the timer trigger select (TRGS1, TRGS0) bits of DSADCSR, A/D conversions on channels 1, 2 and 4 starts. The start of A/D conversion on the individual channels is in accord with the order of execution for the channel, with selection proceeding in an order of precedence from channel1.

- 2. When the A/D conversion on each channel is complete, the A/D conversion result data is transferred to the  $\Delta\Sigma$  A/D data register (DSADDRn: n = 1, 2, 4).

- 3. When the A/D conversions on all selected channels are complete, the ADF bit is set to 1. At this time, a DSADI interrupt request is generated (by clearing the ADF flag during the interrupt) since the ADIE bit is set to 1.

- 4. The ADST bit holds 1 during A/D conversion and is cleared automatically when the conversion is complete. Subsequently when the ADST bit is set to 1, A/D conversion is started on the selected channel from channel 1 according to the order of channel execution.

- 5. When the ADST bit is cleared to 0during A/D conversion, the A/D conversion is aborted and the  $\Delta\Sigma$  A/D converter enters the standby state.

Figure 5.7 Example of  $\Delta\Sigma$  A/D Converter Operation in Single Mode (Multiple Channels: Channel 1, 2, 4 Selected)

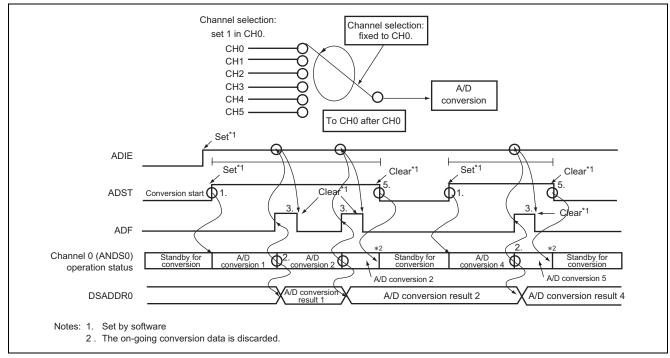

#### 5.6.3 Scan Mode (Single Channel)

The operation in scan mode is described below. Figure 5.8 shows an example of  $\Delta\Sigma$  A/D converter operation in scan mode (channel 0 selected).

The operating conditions are simplified as follows for more understandable description of the scan mode. Normally, it is recommended that starting DMA by DSADI should be enabled when the A/D conversion data is expanded into RAM.

[Operating Conditions]

- Use channel 0.

- Enable  $\Delta \Sigma$  A/D interrupts.

- Generate  $\Delta\Sigma$  A/D conversion complete interrupt requests (DSADI) \*(starting DMA by DSADI is disabled).

Note: \* Refer to section 5.6.1 for Operating Conditions of the source of DSADI.

- 1. When the ADST bit in the DSADCSR is set to 1 by software or the trigger selected in the timer trigger select (TRGS1, TRGS0) bits of DSADCSR, A/D conversion is started.

- 2. When the A/D conversion on channel 0 is complete, the A/D conversion result data is transferred to the  $\Delta\Sigma$ A/D data register (DSADDR0.

- 3. When the A/D conversion on channel 0 is complete, the ADF bit is set to 1. At this time, a DSADI interrupt request is generated (by clearing the ADF flag in the interrupt) since the ADIE bit is set to 1.

- 4. The  $\Delta\Sigma A/D$  converter performs A/D conversion on channel 0 again. The ADST bit is not cleared automatically and the steps from 2 to 4 are repeated while it is set to 1.

- 5. When the ADST bit is cleared to 0, the A/D conversion is aborted and the  $\Delta\Sigma$ A/D converter enters the standby state. After that, then the ADST bit is set to 1, A/D conversion is started on channel 0 again.

Figure 5.8 Example of ΔΣΑ/D Converter Operation in Scan Mode (Single Channel: Channel 0)

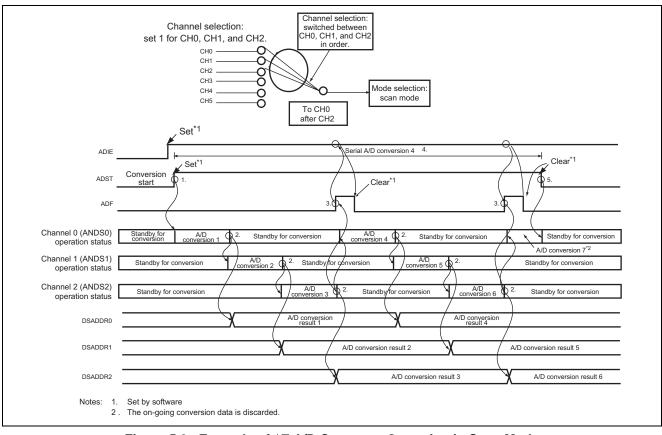

#### 5.6.4 Scan Mode (Multiple Channels)

The operation in the scan mode is described below. Figure 5.9 shows an example of  $\Delta\Sigma A/D$  converter operation in the scan mode (channels 0 to 2 selected).

The operating conditions are as follows for more understandable description of the scan mode. Normally, it is recommended that starting DMA by DSADI should be enabled if the A/D conversion data is expanded into RAM.

[Operating Conditions]

- Use channels 0 to 2.

- Enable  $\Delta \Sigma$  A/D interrupts.

- Generate  $\Delta\Sigma$  A/D conversion complete interrupt requests (DSADI) \*(starting DMA by DSADI is disabled).

Note: \* Refer to section 5.6.1 for Operating Conditions on the source of DSADI.

- 1. When the ADST in DSADCSR is set to 1 by software or the trigger selected in the timer trigger select (TRGS1, TRGS0) bits of DSADCSR, A/D conversion is started. The channel on which A/D conversion is started is selected in accord with the order of execution for the channel with selection proceeding in an order of precedence from channel 0.

- 2. When the A/D conversion on each channel is complete, the A/D conversion result data is transferred to the  $\Delta\Sigma$  A/D data register (DSADDRn: n = 0-2).

- 3. When the A/D conversions on all selected channels are complete, the ADF bit is set to 1. At this time, a DSADI interrupt request is generated (by clearing the ADF flag in the interrupt) since the ADIE bit is set to 1.

- 4. The  $\Delta\Sigma$  A/D converter performs A/D conversion on the selected channel from channel 0 in the order of channel execution again. The ADST bit is not cleared automatically and the steps from 2 to 4 are repeated while it is set to 1.

- 5. When the ADST bit is cleared to 0, the A/D conversion is aborted and the  $\Delta\Sigma$  A/D converter enters the standby state. After that, when the ADST bit is set to 1, A/D conversion on selected channel is started from channel 0 in the order of channel execution again.

# RENESAS

# 6. Recommended External Circuit and Considerations

#### 6.1 Recommended External Circuit (Single-Ended Input, Differential Input)

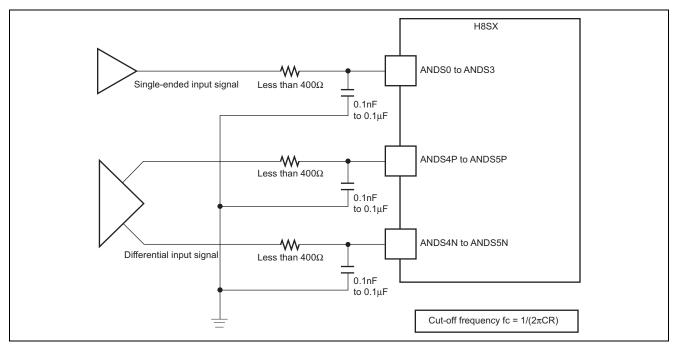

Figure 6.1 shows an example of external circuit for the H8SX family  $\Delta\Sigma$  A/D converter (single-ended input, differential input). When you design boards, note that a voltage drop may occur in analog signals based on the relationship between the resistance value in the low pass filter and the input impedance.

Figure 6.1 Example of External Circuit for ΔΣ A/D Converter (Single-Ended Input, Differential Input)

# 6.2 Recommended External Circuit (Power Supply)

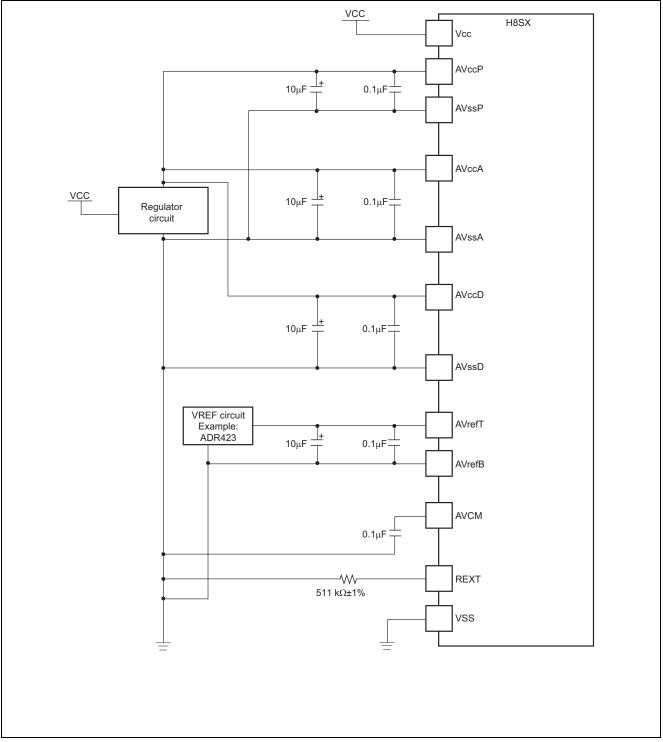

Figure 6.2 shows an example of external circuit (power supply) for the H8SX family  $\Delta\Sigma$  A/D converter. Make sure to provide stable voltage levels to each power supply and ground pins. When you design boards, extra care for AVrefT–AVrefB must be taken because it is used as the  $\Delta\Sigma$  reference voltage.

# 6.3 Considerations

To use the  $\Delta\Sigma$  A/D converter with better accuracy, consider the followings:

Notes on designing boards

- 1. For noise reason, separate the VCC layer from the GND layer in a multi-layer board to reduce noise on input lines.

- 2. Separate the analog power supplies (AvccD, AvccP, AVrefT) from the digital power supply so far as cost and board space permits.

- 3. Note that locating digital circuit patterns below the analog circuit may cause mutual interference.

Setting ranges for analog power supply pins and others

Using the LSI with voltages outside the following ranges may degrade the reliability of the LSI.

- AvccA = AvccD = AvccP, AvssA = AvssD = AVssP must always hold.

- AvccA = AVrefT, AVrefT > AvrefB, AvrefB = 0V must always hold.

# 7. Documents for Reference

# 7.1 Calculation Formula for A/D Conversion Result

The  $\Delta\Sigma$  A/D converter stores the results of A/D conversion in 16-bit data registers. For single-ended inputs, the setting for offset canceling DAC and gain selection are involved when the result value of A/D conversion is represented in a calculation formula. For differential inputs, the result of A/D conversion is obtained by calculation, so the error in the precision of conversion generates errors in the actual result of A/D conversion.

In the calculation formula, the variables shown in the following table are used.

| Variable | Unit             | Range           | Description                                              | Setting                              |

|----------|------------------|-----------------|----------------------------------------------------------|--------------------------------------|

| gain     | Time             | 1 to 8          | Amplification ratio selected by the gain setting         | Bits GAIN1 and GAIN0 in<br>DSADCR    |

| DSADOFn  | Hex              | H'000 to H'3FFF | Offset canceling DAC input                               | DSADOFn corresponding to the channel |

| DOF      | V                | 0 to AvrefT (V) | Analog level set by<br>DSADOFn                           | Set by DSADOFn and AVrefT            |

| ANDSn    | V                | 0 to AvrefT (V) | Single-ended analog input<br>level                       | ANDSn pin for the channel            |

| ANDSnP   | V                | 0 to AvrefT (V) | Positive side of differential<br>analog input            | ANDSnP pin for the channel           |

| ANDSnN   | V                | 0 to AvrefT (V) | Negative side of differential<br>analog input            | ANDSnN pin for the channel           |

| result   | Numeric<br>value | Up to ±262144   | The result of A/D conversion<br>on the channel (integer) | Values in the formula                |

#### Table 7.1 List of Variables in the Calculation Formula

#### 7.1.1 For Single-Ended Inputs

For single-ended inputs, DOF is obtained by integrating the voltage level of AVrefT over DSADOFn/1024. A/D conversion is of the analog level obtained by subtracting DOF from the analog input level on the ANDSn pin and multiplying the result by the gain.

$$DOF = \frac{DSADOFn}{1024} \times (AVrefT - AVrefB)$$

$\label{eq:result} \text{result} = \frac{(\text{ANDSn - DOF}) \times \text{gain}}{\text{AVrefT} - \text{AVrefB}} \times 2^{15}$

Note: AVrefB = 0V

### 7.1.2 For Differential Input

For differential input, the analog level of the ANDSnP pin is subtracted from that of the ANDSnN pin. This voltage level difference is amplified by gain times and then the resulting level is A/D converted.

result =

$$\frac{(ANDSnP - ANDSnN) \times gain}{AVrefT - AVrefB} \times 2^{15}$$

Note: AVrefB = 0V

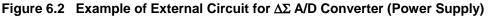

#### 7.1.3 Storing the Calculated Value in the Register

The result can be either positive or negative. It is stored in DSADDRn as a 16-bit signed binary number (two's complement). When the result exceeds the maximum positive value, +32767 (H'7FFF) is stored in DSADDRn. Similarly, when the result exceeds the negative range of 16-bit values, -32768 (H'8000) is stored in DSADDRn.

When result > +32768: DSADDRn = H'7FFF

When +32768 > result > 0: DSADDRn = result

When 0 > result > -32768 : DSADDRn = result + 65536

When -32768 > result: DSADDRn = H'8000

Figure 7.1 Storing the Calculated Value in the Register

# 7.2 Setting the Divided Clock for the $\Delta\Sigma$ A/D Converter

There is a limitation on the oversampling frequency (fos) for the  $\Delta\Sigma$  A/D converter as follows:

Min: 2.5 MHz to Max: 3.3 MHz

Use the following table to set  $A\phi$  according to the EXTAL input clock.

#### Table 7.2 $\Delta\Sigma$ A/D Converter Clock (A $\phi$ ) Frequency against EXTAL Frequency

| EXTAL                          |                | _                               |                    |            |

|--------------------------------|----------------|---------------------------------|--------------------|------------|

| Input Clock<br>Frequency (MHz) | ACK2–0 Setting | Multiplication Factor           | A¢ Frequency (MHz) | fos (MHz)  |

| 8.0 to 9.9                     | B'011          | EXTAL $\times$ 8 $\times$ (1/3) | 21.3 to 26.4       | 2.7 to 3.3 |

| 10.0 to 13.2                   | B'010          | EXTAL $\times$ 8 $\times$ (1/4) | 20.0 to 26.4       | 2.5 to 3.3 |

| 13.2 to 16.5                   | B'001          | EXTAL $\times$ 8 $\times$ (1/5) | 21.1 to 26.4       | 2.6 to 3.3 |

| 16.5 to 18.0                   | B'000          | $EXTAL \times 8 \times (1/6)$   | 22.0 to 26.4       | 2.8 to 3.3 |

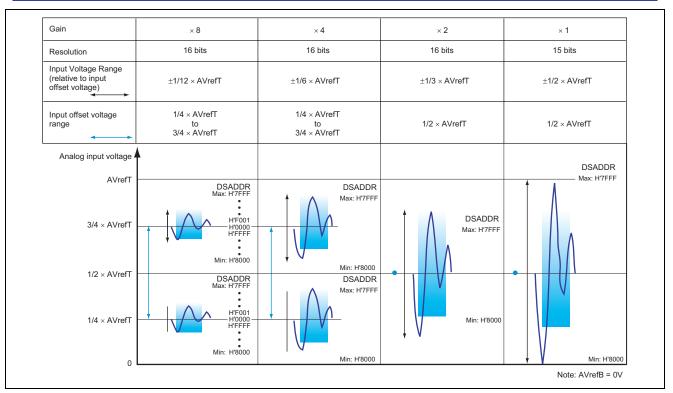

# 7.3 Recommended Input Range and Digital Values

The following figure shows the recommended input range in which the  $\Delta\Sigma$  A/D converter can perform conversion with a high accuracy.

Figure 7.2 Recommended Input Range and Digital Values (Single-Ended Inputs)

Figure 7.3 Recommended Input Range and Digital Values (Differential Inputs)

# Website and Support

Renesas Technology Website <u>http://www.renesas.com/</u>

Inquiries

http://www.renesas.com/inquiry csc@renesas.com

# **Revision Record**

|      |            | Description | ۱                    |  |

|------|------------|-------------|----------------------|--|

| Rev. | Date       | Page        | Summary              |  |

| 1.00 | May 20, 08 | _           | First edition issued |  |

|      |            |             |                      |  |

|      |            |             |                      |  |

|      |            |             |                      |  |

|      |            |             |                      |  |

|      |            |             |                      |  |

All trademarks and registered trademarks are the property of their respective owners.

#### Notes regarding these materials

- 1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

**RENESAS**

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

© 2008. Renesas Technology Corp., All rights reserved.