# Application Note

## DA9061 / NXP i.MX 6Solo Power Connections

**AN-PM-081**

### **Abstract**

*This document describes the connectivity between the Dialog DA9061 Power Management Integrated Circuit (PMIC) and NXP i.MX 6Solo and 6DualLite system application processors.*

## DA9061 / NXP i.MX 6Solo Power Connections

### Contents

|                                                                       |   |

|-----------------------------------------------------------------------|---|

| <b>Abstract</b> .....                                                 | 1 |

| <b>Contents</b> .....                                                 | 2 |

| <b>Figures</b> .....                                                  | 2 |

| <b>Tables</b> .....                                                   | 2 |

| <b>1 Terms and Definitions</b> .....                                  | 3 |

| <b>2 References</b> .....                                             | 3 |

| <b>3 Introduction</b> .....                                           | 4 |

| <b>4 i.MX 6Solo/6DualLite Power Requirements</b> .....                | 4 |

| 4.1 i.MX 6Solo Power Rails .....                                      | 4 |

| 4.2 Power-up Sequence .....                                           | 6 |

| 4.3 Power-down Sequence .....                                         | 7 |

| 4.4 I <sup>2</sup> C Interface .....                                  | 7 |

| 4.5 Recommended External Components .....                             | 7 |

| <b>5 Scalable Power Management Solutions</b> .....                    | 7 |

| <b>6 Software Driver</b> .....                                        | 7 |

| <b>7 Development Support Tools and PMIC Configuration Files</b> ..... | 8 |

| <b>8 Device Identification and Ordering</b> .....                     | 8 |

| <b>Revision History</b> .....                                         | 8 |

### Figures

|                                                  |   |

|--------------------------------------------------|---|

| Figure 1: DA9061 Connections to i.MX 6Solo ..... | 5 |

| Figure 2: DA9061 Power-up Sequence .....         | 7 |

### Tables

|                                                        |   |

|--------------------------------------------------------|---|

| Table 1: i.MX 6Solo to DA9061 Power Rail Mapping ..... | 4 |

| Table 2: i.MX 6Solo Sequencer Requirements .....       | 6 |

| Table 3: Product Part Numbers .....                    | 8 |

## DA9061 / NXP i.MX 6Solo Power Connections

### 1 Terms and Definitions

|      |                                            |

|------|--------------------------------------------|

| GUI  | Graphical User Interface                   |

| PMIC | Power Management Integrated Circuit        |

| DVC  | Dynamic Voltage Control                    |

| DVS  | Dynamic Voltage Scaling. Analogous to DVC. |

| POR  | Power-On Reset                             |

| RTC  | Real-Time Clock                            |

### 2 References

- [1] i.MX 6Solo/6DualLite Applications Processors for Industrial Products, Datasheet, IMX6SDLIEC Rev. 5, 06/2015, NXP.

- [2] i.MX 6Solo/6DualLite Applications Processor Reference Manual, IMX6SDLRM, Rev. 2, 04/2015, NXP

- [3] Common Hardware Design for i.MX 6Dual/6Quad and i.MX 6Solo/6DualLite, AN4397, Rev. 2, 07/2015, NXP

- [4] Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors, IMX6DQ6SDLHDG, Rev 1, 06/2013, NXP

- [5] DA9061, Datasheet, Dialog Semiconductor

- [6] Schematic, DA9061\_iMX6S\_schematic\_2v0.pdf, Dialog Semiconductor

- [7] The Linux Kernel Archives, <https://kernel.org/> (DA9061 software driver) [accessed 30/3/2016]

## DA9061 / NXP i.MX 6Solo Power Connections

### 3 Introduction

The NXP™ i.MX 6Solo™ and 6DualLite™ processors require dedicated power management for a stable and reliable system. The Dialog DA9061 PMIC provides a convenient and flexible solution that meets the processor power requirements. Although system power consumptions vary due to the differing demands of peripherals, processor, and so on, the DA9061 has sufficient headroom to meet the power requirements of most i.MX 6Solo systems. The features of DA9061 enable significant power saving, such as Dynamic Voltage Control (DVC) which intelligently manages voltage changes. The DA9061 significantly reduces system cost and size compared to an equivalent discrete solution.

This document provides details of integrating the DA9061 into an i.MX 6Solo system. As discussed in [3], the information should be equally applicable to an i.MX 6DualLite design. General guidance can be found in the NXP references listed in Section 2.

### 4 i.MX 6Solo/6DualLite Power Requirements

All power domains of an i.MX 6 processor require precise power management to ensure reliable system operation. The main domains are:

|             |                                                                                |

|-------------|--------------------------------------------------------------------------------|

| VDD_ARM_IN  | supplies the internal ARM™ cores                                               |

| VDD_SOC_IN  | supplies the internal peripherals                                              |

| VDD_HIGH_IN | supplies PLLs, DDR pre-drivers, PHY and miscellaneous circuitry                |

| VDD_SNVS_IN | supplies the SNVS regulator for the RTC and SNVS (Secure Non Volatile Storage) |

Additional supplies may be required for DDR memory, peripherals, I/O interfaces, USB, and so on. The power management system must also comply with the processor power-up and power-down sequence requirements.

#### 4.1 i.MX 6Solo Power Rails

Table 1 summarizes the supply rails of the NXP i.MX 6Solo/6Duallite processor and the corresponding regulator outputs from the DA9061.

To optimize systems without a coin cell, VDD\_SNVS\_IN and VDD\_HIGH\_IN are tied together and supplied by LDO2 at 3.0 V. These rails are powered up first in the sequence.

**Table 1: i.MX 6Solo to DA9061 Power Rail Mapping**

| i.MX 6S Rails/System Rails  | DA9061 Regulator | Voltage (V) | Sequence Slot | Notes                                                            |

|-----------------------------|------------------|-------------|---------------|------------------------------------------------------------------|

| VDD_HIGH_IN,<br>VDD_SNVS_IN | LDO2             | 3.0/3.3     | 1             | Switchable via GPIO3 between 3.0 V and 3.3 V                     |

| VDD_ARM_IN                  | BUCK1            | 1.35        | 2             |                                                                  |

| VDD_SOC_IN                  | BUCK1            | 1.35        | 2             |                                                                  |

| NVCC_DRAM<br>(VDDQ_DDR)     | BUCK3            | 1.5/1.35    | 3             | Switchable via GPIO2 to support DDR3 and DDR3L                   |

| NVCC<x>                     | BUCK2            | 3.3         | 4             | The NVCC-<x> digital I/O supply grouping is application specific |

| Peripherals                 | LDO3             | 1.8         | 5             | General purpose rail, for example, supply for RGMII I/O group    |

| Peripherals                 | LDO4             | 1.2         | 6             | General purpose rail                                             |

| Peripherals                 | LDO1             | 2.5         | 7             | General purpose rail                                             |

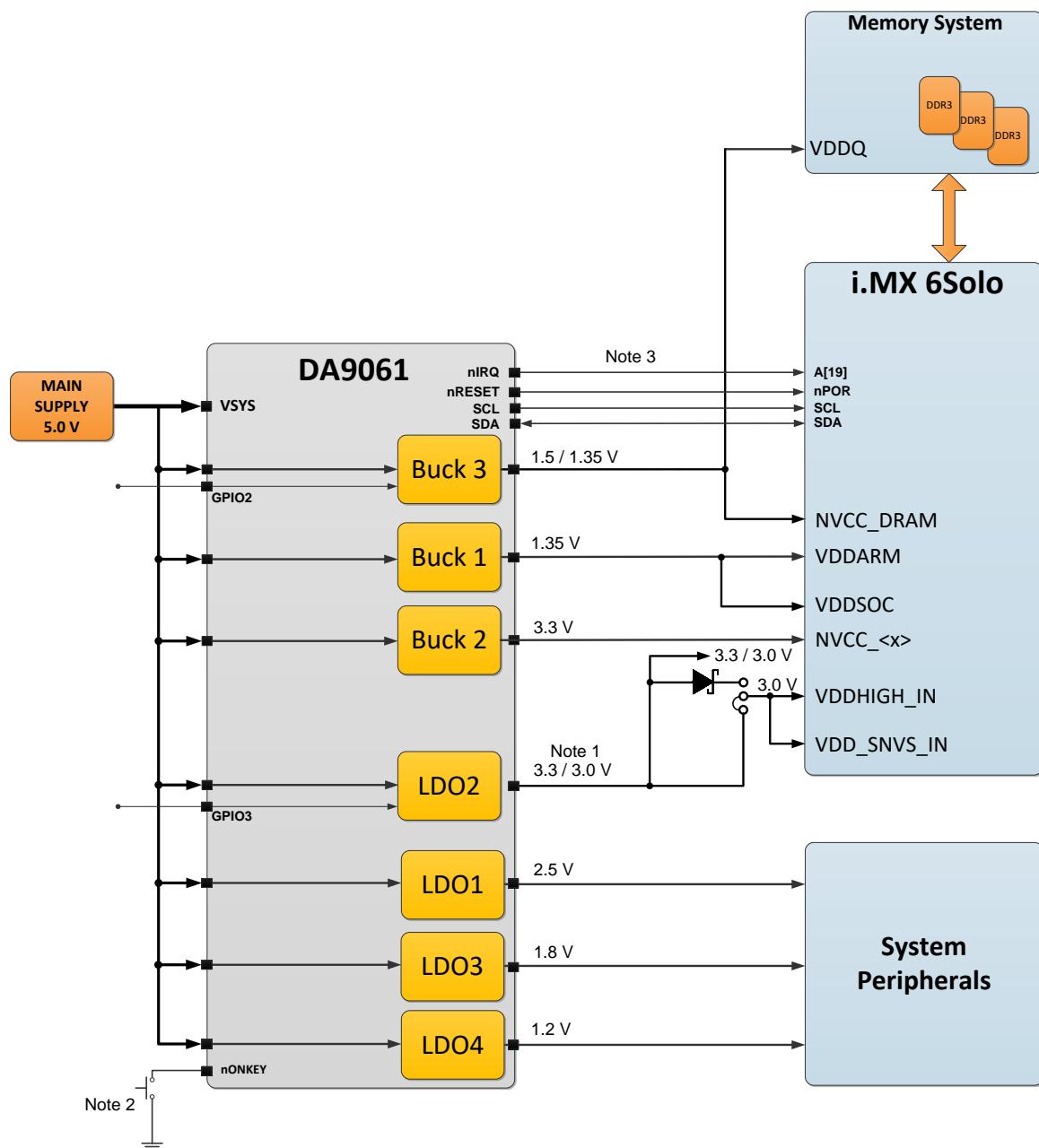

The above mapping is illustrated in the interconnect block diagram of Figure 1.

## DA9061 / NXP i.MX 6Solo Power Connections

Figure 1: DA9061 Connections to i.MX 6Solo

**Note 1** LDO2 is switchable between 3.0 V and 3.3 V based on GPIO3 level. Since no battery is used, VDD\_SNVS\_IN is shorted to VDDHIGH\_IN, as described in [1] Section 4.2.1. If LDO2 is set to 3.3 V (for example to drive a system peripheral), then the diode is required to reduce the voltage on VDDHIGH\_IN/VDD\_SNVS\_IN.

**Note 2** DA9061-62 has the autoboot function enabled in OTP. The DA9061-63 has autoboot disabled and is therefore suited for systems requiring an ONKEY wake-up.

**Note 3** Pull-up resistors for open-drain lines are not shown.

The voltage for VDD\_ARM\_IN and VDD\_SOC\_IN has been set in OTP as 1.35 V. For PCB layouts that have significant ohmic drops along these supply rails, the losses can be compensated for by increasing the level, to 1.38 V for example. This is achieved by an I<sup>2</sup>C software write to DA9061 control VBUCK1\_A immediately after system power-up.

## DA9061 / NXP i.MX 6Solo Power Connections

## 4.2 Power-up Sequence

The sequence used by the DA9061 standard variants, DA9061-62 and DA9061-63, conforms to the requirements described in the i.MX 6Solo datasheet [1] and Reference Manual [2], with specific details highlighted in Table 2.

Table 2: i.MX 6Solo Sequencer Requirements

| Requirements in i.MX 6Solo Datasheet [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DA9061 Configuration Notes                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD_SNVS_IN supply must be turned on before any other power supply or be connected (shorted) with VDD_HIGH_IN supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VDD_SNVS_IN must be supplied by a coin cell or shorted to VDD_HIGH_IN. In either case, VDD_SNVS should be turned on before any other supply. LDO2 is sequenced in Slot 1 to support this.                                                                                                                                     |

| If a coin cell is used to power VDD_SNVS_IN, then ensure that it is connected before any other supply is switched on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No resulting requirement for DA9061.                                                                                                                                                                                                                                                                                          |

| If the external SRC_POR_B signal is used to control the processor POR, SRC_POR_B must remain low (asserted) until the VDD_ARM_CAP and VDD_SOC_CAP supplies are stable. VDD_ARM_IN and VDD_SOC_IN may be applied in either order with no restrictions.                                                                                                                                                                                                                                                                                                                                      | For 6Solo, ARM_IN and SOC_IN are shorted and the delay for the POR_B pin is required. The delay is provided by the DA9061 sequencer delay for nRESET (register RESET at address 0x99).                                                                                                                                        |

| If the external SRC_POR_B signal is not used (always held high or left unconnected), the processor defaults to the internal POR function (where the PMU controls generation of the POR based on the power supplies). If the internal POR function is used, the following power supply requirements must be met: <ul style="list-style-type: none"> <li>• VDD_ARM_IN and VDD_SOC_IN may be supplied from the same source, or, VDD_SOC_IN can be supplied before VDD_ARM_IN with a maximum delay of 1 ms.</li> <li>• VDD_ARM_CAP must not exceed VDD_SOC_CAP by more than +50 mV.</li> </ul> | The DA9061 reference design does use POR_B, so this is irrelevant.                                                                                                                                                                                                                                                            |

| NOTE: The SRC_POR_B input (if used) must be immediately asserted at power-up and remain asserted until after the last power rail reaches its working voltage. In the absence of an external reset feeding the SRC_POR_B input, the internal POR module takes control. See the i.MX 6Solo/6DualLite Reference Manual for further details and to ensure that all necessary requirements are being met.                                                                                                                                                                                       | The DA9061 design uses POR_B with a delay, as mentioned above.<br>POR_B is asserted by the DA9061 immediately when system power is supplied. It is released after all sequenced supplies reach their final stable voltages. Other system components may also assert POR_B, as illustrated in the schematic [6] as wdog2_WDOG. |

| NOTE: Need to ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).                                                                                                                                                                                                                                                                                                                                                                                 | No resulting requirement for DA9061.                                                                                                                                                                                                                                                                                          |

| NOTE: USB_OTG_VBUS and USB_H1_VBUS are not part of the power supply sequence and may be powered at any time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No resulting requirement for DA9061.                                                                                                                                                                                                                                                                                          |

## DA9061 / NXP i.MX 6Solo Power Connections

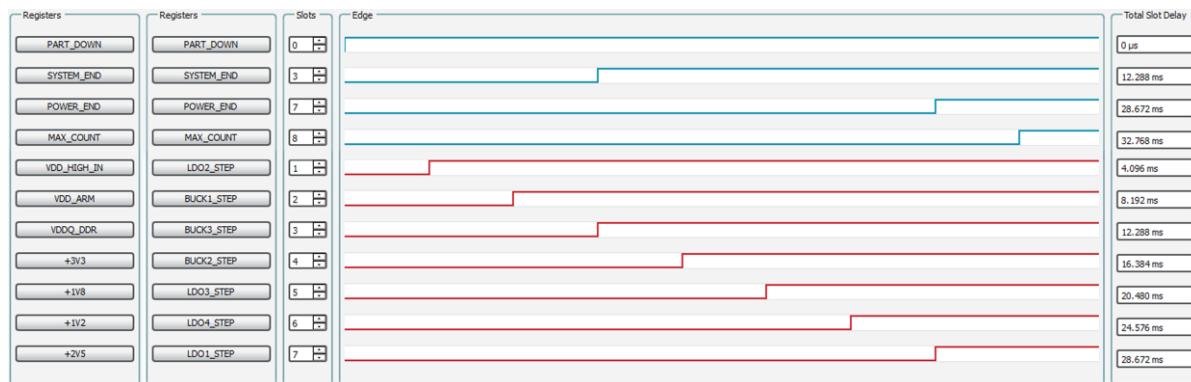

Figure 2 shows the power-up sequence generated by the DA9061-62, which meets the i.MX 6Solo start-up requirements.

Figure 2: DA9061 Power-up Sequence

### 4.3 Power-down Sequence

There are no requirements specific to power-down. Restrictions for other supplies are discussed in [1].

### 4.4 I<sup>2</sup>C Interface

An I<sup>2</sup>C interface between the i.MX 6 and the DA9061 device allows software, including the operating system kernel, to access the internal PMIC registers for control and monitoring. The slave address of the DA9061 is 0xB0.

### 4.5 Recommended External Components

For a list of recommended external components, please refer to the schematic [6] and the DA9061 datasheet [5]. The recommended values of inductors and capacitors must be used at the output of all bucks and LDOs to guarantee the closed-loop stability and optimum efficiency of the supplies.

## 5 Scalable Power Management Solutions

Some systems require more regulators than available from the DA9061. This is frequently due to the demands of the peripherals. In these circumstances, other Dialog PMICs in the same family (for example, DA9062, DA9063 and DA9063L) are likely to provide suitable solutions. The DA9062 is pin-compatible with the DA9061 and provides additional features often required by i.MX 6 systems such as a real-time clock (RTC), a dual-phase (5 A) buck configuration, DDR memory termination (DA9062 VTT supply) and VTTR memory reference voltage.

## 6 Software Driver

After the DA9061 has started the i.MX 6 system, software can read and write to the PMIC via the I<sup>2</sup>C bus. This can be used for further PMIC configuration, such as the GPIOs, interrupt servicing, DVC, watchdog 'keep-alive' writes, and so on. Dialog drivers for Linux™ are available in the Linux kernel from <https://kernel.org> [7] or, if interim assistance is required, from your Dialog Sales representative.

## DA9061 / NXP i.MX 6Solo Power Connections

### 7 Development Support Tools and PMIC Configuration Files

To assist with hardware and software development, Dialog provides the following:

- DA9061 Evaluation Kit

- This contains motherboard and daughterboard for hardware evaluation and software development. It also includes the SmartCanvas GUI software.

- SmartCanvas GUI

- This is PC-driven software to provide easy access to a device under test (DUT). The GUI is used to exercise the DUT using the I<sup>2</sup>C interface. Control or measurement of analog and digital pins is supported. SmartCanvas supports the Dialog PMIC OTP configuration file format – .ini files.

- OTP configuration .ini files

- These files define the configuration of the DA9061 at boot and define the different variants such as the -62 and -63. The following ini files are available from the Dialog Support Site:

- DA9061-62\_IMX6S\_AUTOBOOT\_0v1\_E61A.ini (autoboot enabled)

- DA9061-63\_IMX6S\_NO\_AUTOBOOT\_0v1\_40D5.ini (autoboot disabled)

These files are opened using the SmartCanvas GUI.

- Design schematic [\[6\]](#) with details of PMIC to processor interconnections.

- Linux software driver, see [Section 6](#).

### 8 Device Identification and Ordering

DA9061-62 has the autoboot feature enabled in OTP. The DA9061-63 has autoboot disabled and is therefore suited for systems requiring an ONKEY wake-up. If the DA9061-62 and DA9061-63 prove unsuitable for your target i.MX 6Solo/6DualLite design, please contact your Dialog sales representative to discuss custom variants. (Minimum order quantities apply for custom variants.)

**Table 3: Product Part Numbers**

| Part Number    | Description ( <a href="#">Note 1</a> )    |

|----------------|-------------------------------------------|

| DA9061-62AMx   | Autoboot. Industrial grade                |

| DA9061-62AMx-A | Autoboot. Automotive AEC-Q100 Grade 3     |

| DA9061-63AMx   | Non-autoboot. Industrial grade            |

| DA9061-63Mx-A  | Non-autoboot. Automotive AEC-Q100 Grade 3 |

**Note 1** See the DA9061 datasheet [\[5\]](#) for further information regarding part ordering. All parts are available in tray (x = 1) or Tape & Reel (x = 2).

### Revision History

| Revision | Date        | Description                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 21-Apr-2016 | First release                                                                                                                                                                                                                                                                                                                                                                      |

| 2.0      | 18-Jul-2016 | Section <a href="#">2</a> : Updated the reference to the revised schematic (2v0).<br>Clarified LDO2 options in <a href="#">Figure 1</a> and in the supporting notes.<br>Changed the sequence to have LDO2 start VDD_SNVS_IN first in Slot 1.<br>Replaced DA9061-60 with DA9061-62 to reflect the above changes.<br>Replaced DA9061-61 with DA9061-63 to reflect the above changes. |

| 3.0      | 18-Feb-2022 | File was rebranded with new logo, copyright and disclaimer                                                                                                                                                                                                                                                                                                                         |

## DA9061 / NXP i.MX 6Solo Power Connections

### Status Definitions

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

### RoHS Compliance

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).